(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3892867号

(P3892867)

(45) 発行日 平成19年3月14日(2007.3.14)

(24) 登録日 平成18年12月15日(2006.12.15)

(51) Int.C1.

F 1

|                          |              |         |

|--------------------------|--------------|---------|

| HO 1 L 21/8242 (2006.01) | HO 1 L 27/10 | 6 2 1 C |

| HO 1 L 27/108 (2006.01)  | HO 1 L 27/10 | 6 8 1 F |

| HO 1 L 21/3205 (2006.01) | HO 1 L 21/88 | K       |

| HO 1 L 21/768 (2006.01)  | HO 1 L 21/90 | A       |

| HO 1 L 27/10 (2006.01)   | HO 1 L 27/10 | 4 6 1   |

請求項の数 7 (全 37 頁)

(21) 出願番号 特願2004-335811 (P2004-335811)

(22) 出願日 平成16年11月19日 (2004.11.19)

(62) 分割の表示 特願平9-350537の分割

原出願日 平成9年12月19日 (1997.12.19)

(65) 公開番号 特開2005-101647 (P2005-101647A)

(43) 公開日 平成17年4月14日 (2005.4.14)

審査請求日 平成16年12月14日 (2004.12.14)

早期審査対象出願

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 福田 琢也

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体事業部内

(72) 発明者 大路 譲

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体事業部内

(72) 発明者 小林 伸好

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体事業部内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板の主面のメモリセルアレイ領域にメモリセル選択用MISFETが、前記半導体基板の周辺回路領域に周辺回路用MISFETがそれぞれ形成され、

前記メモリセル選択用MISFETと情報蓄積用容量素子とでDRAMのメモリセルが構成され、

前記メモリセル選択用MISFETおよび前記周辺回路用MISFETを覆い、かつその表面が平坦化された第1絶縁膜が形成され、

前記メモリセルアレイ領域の前記第1絶縁膜上にピット線が、前記周辺回路領域の前記第1絶縁膜上に前記ピット線と同一の材料からなる第1層配線が形成され、

前記ピット線および前記第1層配線を覆い、かつその表面が平坦化された第2絶縁膜が前記メモリセルアレイ領域および前記周辺回路領域上に形成され、

ストッパ膜が前記メモリセルアレイ領域および前記周辺回路領域の前記第2絶縁膜の上部に形成され、

前記ストッパ膜上に絶縁膜が形成され、

前記絶縁膜により、前記情報蓄積用容量素子の下部電極、容量絶縁膜および上部電極が覆われるよう形成され、

前記絶縁膜は、前記情報蓄積用容量素子を覆うように形成され、かつ前記情報蓄積用容量素子上および前記周辺回路領域上に表面が平坦化されて形成され、

前記周辺回路領域において、前記絶縁膜上に第2層配線が形成され、

10

20

前記周辺回路領域の前記絶縁膜、前記ストップ膜および前記第2絶縁膜に溝が前記第1層配線を露出するように形成され、

前記溝内に導電層からなる導電部が、前記第2層配線および前記第1層配線に接続するように形成され、かつ前記導電部は前記溝内で一体に形成され、

前記ストップ膜は前記下部電極を形成する際のエッティングストップとして機能し、

前記下部電極は内面及び外面を有する側壁を有し、

前記下部電極の下には前記ストップ膜が存在せず、前記下部電極の側壁に接する領域に前記ストップ膜が存在し、

前記下部電極の側壁の内面及び外面上に容量絶縁膜、前記容量絶縁膜上に前記上部電極が形成され、

前記第1絶縁膜に前記メモリセル選択用MISFETの一方の半導体領域に接続される第1プラグが形成され、

前記ビット線は、前記第1プラグに接続され、

前記第1絶縁膜に、前記周辺回路用MISFETの半導体領域を露出する第1接続孔が形成され、前記第1層配線は前記第1接続孔を介して前記周辺回路用MISFETの半導体領域に接続されることを特徴とする半導体集積回路装置。

#### 【請求項2】

請求項1において、

前記第1絶縁膜に、前記メモリセル選択用MISFETの他方の半導体領域に接続されるシリコン膜からなる第2プラグが形成され、

前記第2プラグは前記下部電極に接続されることを特徴とする半導体集積回路装置。

#### 【請求項3】

請求項1において、

前記ストップ膜は窒化シリコン膜であることを特徴とする半導体集積回路装置。

#### 【請求項4】

半導体基板の主面のメモリセルアレイ領域にメモリセル選択用MISFETを、前記半導体基板の周辺回路領域に周辺回路用MISFETをそれぞれ形成する工程、

前記メモリセル選択用MISFETおよび前記周辺回路用MISFETを覆い、かつその表面が平坦化された第1絶縁膜を形成する工程、

前記メモリセルアレイ領域の前記第1絶縁膜上にビット線を、前記周辺回路領域の前記第1絶縁膜上に前記ビット線と同一の材料からなる第1層配線を形成する工程、

前記ビット線および前記第1層配線を覆い、かつその表面が平坦化された第2絶縁膜を前記メモリセルアレイ領域および前記周辺回路領域上に形成する工程、

ストップ膜を前記メモリセルアレイ領域および前記周辺回路領域の前記第2絶縁膜の上部に形成する工程、

前記ストップ膜上に第3絶縁膜を形成する工程、

前記メモリセルアレイ領域の前記第3絶縁膜および前記ストップ膜をエッティングして溝を形成する工程、

前記溝の内壁および底部上に情報蓄積用容量素子の下部電極を形成する工程、

前記ストップ膜をエッティングストップとして前記第3絶縁膜をエッティングして前記下部電極を露出させる工程、

前記下部電極を覆う容量絶縁膜および上部電極を形成する工程、

前記情報蓄積用容量素子上および前記周辺回路領域上に、表面が平坦化された第4絶縁膜を形成する工程、

前記周辺回路領域において、前記平坦化された前記第4絶縁膜、前記ストップ膜および前記第2絶縁膜に他の溝を前記第1層配線を露出するように形成し、前記他の溝の内部を含む前記第4絶縁膜上に導電層を堆積し、前記第4絶縁膜の表面上の前記導電層を除去して、前記他の溝内に前記導電層からなる導電部を、前記第1層配線に接続するように形成する工程、

を含み、

前記メモリセル選択用MISFETと前記情報蓄積用容量素子とでDRAMのメモリセルが構成され、

前記周辺回路領域において、前記第4絶縁膜上に第2層配線が形成され、

前記導電部は前記他の溝内で一体に形成され、かつ前記第2層配線および前記第1層配線に接続され、

前記下部電極の下には前記ストップ膜が存在せず、前記下部電極の側壁に接する領域に前記ストップ膜が存在し、

前記第1絶縁膜に前記メモリセル選択用MISFETの一方の半導体領域に接続される第1プラグが形成され、

前記ピット線は、前記第1プラグに接続され、

10

前記第1絶縁膜に、前記周辺回路用MISFETの半導体領域を露出する第1接続孔が形成され、前記第1層配線は第1接続孔を介して前記周辺回路用MISFETの半導体領域に接続されることを特徴とする半導体集積回路装置の製造方法。

**【請求項5】**

請求項4において、

前記下部電極を露出させる工程は、前記周辺回路領域の前記第3絶縁膜が除去されるように行われることを特徴とする半導体集積回路装置の製造方法。

**【請求項6】**

請求項4において、

20

前記第1絶縁膜に、前記メモリセル選択用MISFETの他方の半導体領域に接続されるシリコン膜からなる第2プラグが形成され、

前記第2プラグは前記下部電極に接続されることを特徴とする半導体集積回路装置の製造方法。

**【請求項7】**

請求項4において、

前記ストップ膜は窒化シリコン膜であることを特徴とする半導体集積回路装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

30

本発明は、半導体集積回路装置およびその製造技術に関し、特に、いわゆるCOB(Capacitor Over Bitline)構造を有するDRAM(Dynamic Random Access Memory)、あるいは、そのようなDRAMと論理制御回路または論理演算回路等のロジック回路とが1つの半導体基板に混載された半導体集積回路装置に適用して有効な技術に関するものである。

**【背景技術】**

**【0002】**

DRAMのメモリセルは、一般に、半導体基板の主面上にマトリクス状に配置された複数のワード線と複数のピット線との交点に配置され、1個のメモリセル選択用MISFET(Metal Insulator Semiconductor Field Effect Transistor)とこれに直列に接続された1個の情報蓄積用容量素子(キャパシタ)とで構成されている。メモリセル選択用MISFETは、周囲を素子分離領域で囲まれた活性領域に形成され、主としてゲート酸化膜、ワード線と一体に構成されたゲート電極およびソース、ドレインを構成する一対の半導体領域で構成されている。ピット線は、メモリセル選択用MISFETの上部に配置され、その延在方向に隣接する2個のメモリセル選択用MISFETによって共有されるソース、ドレインの一方と電気的に接続されている。情報蓄積用容量素子は、同じくメモリセル選択用MISFETの上部に配置され、上記ソース、ドレインの他方と電気的に接続されている。

**【0003】**

特開平7-7084号公報(特許文献1)は、ピット線の上部に情報蓄積用容量素子を

40

50

配置するキャパシタ・オーバー・ビットライン( C O B ; Capacitor Over Bitline )構造の D R A M を開示している。この公報に記載された D R A M では、キャパシタの下部電極( 蓄積電極 )が上方に開口を有する円筒形状に加工され、これによってその表面積を増加して、メモリセルの微細化に伴う情報蓄積用容量素子の蓄積電荷量( C s )の減少を補い、半導体記憶装置としての動作信頼度を確保している。また、下部電極に接して容量絶縁膜が形成され、その上部に上部電極( プレート電極 )が形成されている。

#### 【 0 0 0 4 】

このような円筒形状の下部電極を有するキャパシタは、その形状に由来して必然的に立体化される。この立体化のために、キャパシタが形成されるメモリセルアレイ領域と、周辺回路領域等それ以外の領域との間に、キャパシタの高さに相当する段差が発生する。

10

#### 【 0 0 0 5 】

このような段差が存在すれば、キャパシタの形成後に形成される配線層のパターニングの際に露光焦点の合わせが困難になり、微細な配線パターンが得られなくなる。半導体集積回路装置の微細化の進展に伴って単位面積あたりに確保する必要がある蓄積容量値が大きくなり、このためキャパシタ高さがさらに高くなり、他方、配線パターンの微細化によって許容される露光焦点の合わせ余裕の値が益々厳しいものとなる。したがって、前記段差を緩和する手段は、 C O B 構造のメモリセル構造を採用する限り必須の技術課題となる。

#### 【 0 0 0 6 】

前記段差を緩和できる技術として以下のような技術が知られている。たとえば、平成 5 年 10 月 26 日、工業調査会発行、「やさしい U L S I 技術」、p 155 ~ p 164 ( 非特許文献 1 ) に記載されているように、 S O G ( Spin On Glass ) 膜あるいは低融点ガラスの塗布および溶融による塗布法、ガラスフローによる熱処理法、 C V D ( Chemical Vap or Deposition ) の表面反応メカニズムを適用して自己平坦化させる方法等が知られ、たとえば、特開平 7 - 122654 号公報 ( 特許文献 2 ) には、 B P S G ( Boron-doped Phospho-Silicate Glass ) 膜のリフローによる平坦化とスピノングラス膜 ( S O G 膜 ) による平坦化とを組み合わせて段差の低減を図る技術が開示されている。

20

#### 【 0 0 0 7 】

また、たとえば、平成 8 年 5 月 1 日、工業調査会発行、「電子材料」 1996 年 5 月号、 p 22 ~ p 27 ( 非特許文献 2 ) に記載されているように、フォトレジスト犠牲膜、 S O G 膜あるいは自己平坦化 C V D 膜の堆積とエッチバック法とを組み合わせた方法および C M P ( Chemical Mechanical Polishing ) 法が知られている。

30

#### 【 0 0 0 8 】

しかし、 S O G 膜あるいは低融点ガラスの塗布および溶融による塗布法では、微細な凹凸を埋め込む ( 平坦化 ) することはできても、周辺回路領域のように広い面積の凹部を埋め込むことはできず、前記のような段差の緩和には顕著な効果を期待できない。すなわち、キャパシタの高さに起因するメモリセルアレイ領域と周辺回路領域との絶対段差は解消されず、たとえばメモリセルアレイ上に配置される配線をパターニングする際、焦点深度の余裕が十分にとれない関係から、微細な配線パターンを得ることは困難である。

#### 【 0 0 0 9 】

40

また、ガラスフローによる熱処理法 ( たとえば B P S G のリフロー膜 ) 、あるいは B P S G 膜のリフローによる平坦化とスピノングラス膜 ( S O G 膜 ) による平坦化とを組み合わせて段差の低減を図る技術では、 B P S G 膜のリフローの際に高い温度の熱処理が必要となり、今後の高集積化された D R A M においてゲート、プラグあるいはキャパシタの材料としてメタル系材料が用いられることを考慮すれば、そのような高温プロセスを採用することによるメタル系材料の好ましくない反応が生じ、 D R A M の性能を向上できない恐れがある。

#### 【 0 0 1 0 】

また、 C V D の表面反応メカニズムを適用して自己平坦化させる方法、あるいは、フォトレジスト犠牲膜、 S O G 膜、自己平坦化 C V D 膜の堆積とエッチバック法とを組み合わ

50

せた方法では、プロセスが複雑となり、安定な工程の実現という観点から好ましくない。

【0011】

そこで、比較的安定な工程を得ることができ、また、原理的にウェハ全面での平坦性を得ることが可能なC M P法を段差の解消に適用する技術が有望視される。

【特許文献1】特開平7-7084号公報

【特許文献2】特開平7-122654号公報

【非特許文献1】平成5年10月26日、工業調査会発行、「やさしいU L S I技術」、p155～p164

【非特許文献2】平成8年5月1日、工業調査会発行、「電子材料」1996年5月号、p22～p27

10

【発明の開示】

【発明が解決しようとする課題】

【0012】

しかし、C M P法で前記段差を解消した場合には、メモリセルアレイ領域以外の領域にキャパシタと同層に形成される絶縁膜の厚さが、キャパシタ高さと同等あるいはそれ以上となって、相當に厚くなる。微細化されたD R A Mにおいてはキャパシタ高さを高くして蓄積容量を確保する必要上その厚さは1 μmにまでおよぶ場合も生じる。このため、キャパシタ形成工程の前に形成された第1層配線と、完全平坦化が実現された絶縁膜上の配線（第2層配線）とを接続する場合には、キャパシタの段差を反映した厚い絶縁膜に接続孔を開口する必要があり、その接続孔のアスペクト比（接続孔開口径に対する接続孔の深さ）が大きくなってしまう。すなわち、第1層配線と第2層配線とをプラグを用いて接続する場合であっても高いアスペクト比のプラグで接続することとなり、このような高いアスペクト比のプラグを形成するために、歩留りの低下を招く恐れが存在する。

20

【0013】

また、D R A Mと論理制御回路または論理演算回路等のロジック回路とが1つの半導体基板に混載された半導体集積回路装置にあっては、ロジック回路部は、D R A Mの周辺回路と同様に高いアスペクト比のプラグによって第1層配線と第2層配線とが接続されることとなる。このような高いアスペクト比のプラグで配線が接続されれば、その抵抗によって、ロジック回路の高速応答性等の性能が阻害されることとなる。

【0014】

30

なお、特開平9-92794号公報には、段差の低減および蓄積電極の加工工程の簡略化のために、キャパシタを掘込み型とし、キャパシタ形成用の凹部と配線溝とを同時に形成する方法が開示されているが、円筒型の蓄積電極（下部電極）の内外面を利用するキャパシタの形成には不適当であり、また、キャパシタを形成した後に配線（第2層配線）を形成する際には、C M P法を用いることができないという不具合がある。また、前記公報の技術によりキャパシタの下部電極を周辺回路の第2層配線と同時に形成した場合には、その第2層配線の形成工程の後にキャパシタの容量絶縁膜の形成を行うこととなる。キャパシタの蓄積電荷の増大を考慮して酸化タンタル等の酸化物金属で容量絶縁膜を構成した場合には、必然的に高い温度の熱処理工程を実施する必要があり、第2層配線に低抵抗な銅あるいはアルミニウム等の金属材料を用いることは、熱的拡散性及び軟化の観点から採用できない。

40

【0015】

本発明の目的は、C O B構造のメモリセルを有する半導体集積回路装置において、立体化されたキャパシタと同層に形成された厚い絶縁膜を挟んで配置される第1層配線と第2層配線との接続信頼性を向上することにある。

【0016】

また、本発明の目的は、前記第1層配線と第2層配線との接続孔部分の抵抗を低減することにある。

【0017】

また、本発明の目的は、第2層配線以上の配線の配線抵抗を低減することにある。

50

**【0018】**

また、本発明の目的は、第2層配線の形成工程を高い熱処理工程が必要なキャパシタの形成工程以降とし、熱拡散係数の大きな材料であっても第2層配線に用いることが可能な技術を提供することにある。

**【0019】**

また、本発明の目的は、COB構造のメモリセルを有するDRAMと同一の基板に形成される周回路、あるいはロジック回路の高速応答性能を向上することにある。

**【0020】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

10

**【課題を解決するための手段】****【0021】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

**【0022】**

(1) 本発明の半導体集積回路装置は、半導体基板のメモリセルアレイ領域に形成されたメモリセル選択用MISFETと、メモリセルアレイ領域の周辺の周回路領域に形成された周回路用MISFETと、メモリセル選択用MISFETおよび周回路用MISFETを覆う第1層間絶縁膜と、メモリセルアレイ領域の第1層間絶縁膜上に形成されたビット線と、ビット線上に形成され、メモリセル選択用MISFETの一方のソース・ドレイン領域に電気的に接続された下部電極を備えた情報蓄積用容量素子と、情報蓄積用容量素子と同層に形成され、情報蓄積用容量素子の高さに起因するメモリセルアレイ領域と周回路領域との段差を緩和または解消する第1の部分、および情報蓄積用容量素子を覆う第2の部分を含む第2層間絶縁膜とを有する半導体集積回路装置であって、第2層間絶縁膜の表面が平坦化され、かつ、第2層間絶縁膜の表面近傍に配線溝が形成されており、配線溝の内部には、表面と同一面内にその表面を有する配線が形成されているものである。

20

**【0023】**

また、本発明の半導体集積回路装置は、前記した半導体集積回路装置のメモリセルアレイ領域および周回路領域以外に、演算回路その他のロジック回路を構成するロジック回路用MISFETが形成されたロジック回路領域を有し、このロジック回路領域の第2層間絶縁膜についても、その表面が平坦化され、かつ、その表面近傍に配線溝が形成され、配線溝の内部には、表面と同一面内にその表面を有する配線が形成されているものである。

30

**【0024】**

このような半導体集積回路装置によれば、第2層間絶縁膜の表面が平坦化されているため、メモリセルアレイ領域とその他の領域との間に情報蓄積用容量素子の起因する段差が形成されず、このような段差が存在した場合には生ずるであろう露光光の焦点ずれが発生しない。このため、第2層間絶縁膜上に形成される配線等のパターニングを精密に行うことができる。これにより微細な配線等を形成して半導体集積回路装置の高集積化および高性能化に対応することが可能となる。

40

**【0025】**

ただし、このように第2層間絶縁膜の表面を平坦化すれば、周回路領域あるいはロジック回路領域についての第2層間絶縁膜の膜厚が前記段差に相当する寸法だけ厚くなり、何ら対策を施さない従来技術の場合には第2層間絶縁膜上に形成する配線とその下部部材とを接続する接続孔を高いアスペクト比で加工する必要があることは前記したとおりである。

**【0026】**

しかし、本発明では、第2層間絶縁膜の表面を平坦化するとともにその表面近傍に配線溝を形成し、この配線溝に第2層間絶縁膜の表面と同一の平面内にその表面を有する配線

50

が形成されるため、第2層間絶縁膜の下部の部材と、配線底部との距離が短くなり、配線と前記部材とを接続する接続部の長さを短くできる。これにより、接続部を形成する接続孔の長さを短くしてその加工を容易とし、加工不良の発生を抑制して半導体集積回路装置の製造歩留まりと信頼性を向上できる。また、接続部の長さが短くなることから、その接続部の抵抗が低くなり、配線と前記部材との接続抵抗を低減して半導体集積回路装置の高速応答性等の性能を向上できる。

#### 【0027】

また、前記配線はメモリセルアレイ領域には形成されず、周辺回路領域にのみ、または周辺回路領域およびロジック回路領域にのみ形成することができる。これにより、周辺回路領域またはロジック回路領域での配線および接続部の抵抗値を低減して周辺回路およびロジック回路の高速応答性能を向上できる。特にロジック回路部分の高速応答性能の向上は、そのまま演算速度の向上等、半導体集積回路装置の性能向上に直接影響し、重要である。10

#### 【0028】

また、配線の底面は、情報蓄積用容量素子の上面よりも下方に位置するものとすることができます。このように、配線底面を情報蓄積用容量素子の上面よりも下方に位置させることにより、配線底面からその下部に位置する部材に向けて接続する接続部の長さを、より短くすることができる。接続部の長さの短縮は、前記したとおり半導体集積回路装置の歩留まりおよび信頼性の向上、および性能向上に寄与するため、この長さをさらに短くできることは、前記効果をより顕著に発現させることができることを意味する。20

#### 【0029】

また、周辺回路領域、または、周辺回路領域およびロジック回路領域の第1層間絶縁膜上には、ピット線と同一の材料からなる第1層配線が形成され、配線は、第1層配線の上部に形成された第2層配線とすることができます。このように、第1層間絶縁膜上にピット線と同一材料の第1層配線を形成することにより、第1層配線の形成工程をピット線の形成工程と同一にして、工程を簡略化することが可能となる。また、前記配線を第2層配線とし、第2層配線と接続される下部部材を、第1層配線とすることにより、第2層配線と第1層配線との間、すなわち接続部の長さを短くできる。これにより、接続孔の形成工程の容易化による製造歩留まりおよび信頼性の向上、接続部の長さ短縮化による直列抵抗の低減、それに基づく半導体集積回路装置の性能向上をより顕著に図ることができる。30

#### 【0030】

なお、配線（あるいは第2層配線）と接続部とは、配線が配線溝に、接続部が接続孔にそれぞれ形成され、一体として形成されたものとすることができます。すなわち、配線溝の下部に接続孔を形成し、配線または第2層配線は、接続孔の内部に配線または第2層配線と一体に形成された接続部を介して周辺回路用MISFET、ロジック回路用MISFETまたは第1層配線に接続されているものとすることができます。このような配線および接続部は、後に説明するように、いわゆるダマシン法（特に配線と接続部とを一体で形成するデュアルダマシン法）で形成することができる。

#### 【0031】

また、配線およびその接続部または第2層配線およびその接続部は、銅を主導電層とする金属導電体とすることができる、この場合、銅からなる主導電層と配線溝および接続孔との界面には、タンタル膜、ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲスタン膜から選択された何れか1つのまたは複数の薄膜を形成することができる。また、配線または第2層配線の表面をシリコン窒化膜で覆うことができる。40

#### 【0032】

銅を主導電層とすることにより配線および接続部の抵抗値を低減し、半導体集積回路装置の性能を向上できる。特にロジック回路部分での性能向上は、その要求が強く期待されており、技術的効果が大きい。また、タンタル膜、ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲスタン膜から選択された何れか1つのまたは複数の薄膜は、銅に対するプロッキング層として機能するものである。これにより銅の層間絶縁膜等への拡散を50

防止して、半導体集積回路装置の信頼性を向上できる。特に、タンタル膜およびニオブ膜は、タンタルおよびニオブと銅との化学結合が安定に存在し、タンタル／銅界面（ニオブ／銅界面）での銅原子の移動が抑制される。このため、銅の拡散のみならず、エレクトロマイグレーションに対してもその抑制効果が大きく、その結果、耐エレクトロマイグレーションに優れた高い信頼性の半導体集積回路装置を得ることができる。さらに、配線または第2層配線の表面をシリコン窒化膜で覆うことにより、銅の上方への拡散を抑制することができる。

【0033】

また、配線およびその接続部または第2層配線およびその接続部は、アルミニウムを主導電層とする金属導電体とすることができる、この場合、アルミニウムからなる主導電層と配線溝および接続孔との界面には、窒化チタン膜を形成することができる。10

【0034】

アルミニウムを主導電層とすることにより配線および接続部の抵抗値を低減し、半導体集積回路装置の性能を向上できる。特にロジック回路部分での性能向上は、その要求が強く期待されており、技術的効果が大きい。また、窒化チタン膜は後に説明するアルミニウムを高圧力下で接続孔に埋め込む際のウェッティング層として機能させることができる。

【0035】

なお、下部電極は、上方に開孔を有する筒形状を有するものとすることができる。このような上方に開孔を有する筒形状の下部電極は大きな表面積を得ることができることから今後のDRAMの高集積化には有利な形状であるが必然的に立体的な形状となり、そのため、情報蓄積用容量素子に起因する段差も高くなる。よって、本発明を適用した場合の効果が特に顕著になる下部電極の形状である。20

【0036】

また、配線または第2層配線の上層には、さらに、その表面近傍に配線溝を有する上層層間絶縁膜、および、配線溝内に形成されその表面と上層層間絶縁膜の表面とがほぼ同一平面内にある上層配線が形成されてもよい。このように第2層配線以上の第3あるいは第4層配線をも前記した第2層配線（配線）と同様としてその直列抵抗を低減し、半導体集積回路装置の性能を向上できる。

【0037】

（2）本発明の半導体集積回路装置の製造方法は、半導体基板の正面のメモリセルアレイ領域にメモリセル選択用MISFETを、半導体基板の周辺回路領域またはロジック回路領域に周辺回路用MISFETまたはロジック回路用MISFETをそれぞれ形成する工程、メモリセル選択用MISFETおよび周辺回路用MISFETまたはロジック回路用MISFETを覆う第1絶縁膜を形成する工程、メモリセルアレイ領域の第1絶縁膜上にビット線を形成する工程、ビット線を覆う第2絶縁膜を形成する工程、メモリセルアレイ領域の第2絶縁膜上に情報蓄積用容量素子の下部電極、下部電極を覆う容量絶縁膜および上部電極を形成する工程、情報蓄積用容量素子上に第3絶縁膜を形成する工程、を含む半導体集積回路装置の製造方法であって、第3絶縁膜の表面をCMP法で平坦化した後、周辺回路領域またはロジック回路領域の平坦化された第3絶縁膜およびその下層絶縁膜に配線溝および接続孔を形成し、配線溝および接続孔の内部を含む第3絶縁膜上に第1導電層および第2導電層を順次堆積し、第3絶縁膜の表面上の第1および第2導電層をCMP法により除去して、配線溝内に第1および第2導電層からなる配線を、接続孔内に第1および第2導電層からなる接続部を形成する工程、を含むものである。3040

【0038】

このような半導体集積回路装置の製造方法によれば、いわゆるデュアルダマシン法で配線を形成し、前記（1）で記載した半導体集積回路装置を形成できる。

【0039】

また、本製造方法によれば、配線は、情報蓄積用容量素子を形成した後に形成されるため、情報蓄積用容量素子の形成の際に通常行われる高い温度の熱処理により配線が影響を受けることがない。逆にいえば、情報蓄積用容量素子の形成の際に未だ配線は形成されて

いないため、配線の耐熱性を考慮して情報蓄積用容量素子の形成の際の熱工程を制限する必要がない。これにより情報蓄積用容量素子の形成の際には十分に高い温度の熱処理（たとえば700程度）を施して蓄積容量の大きい情報蓄積用容量素子を形成することができ、一方、配線には耐熱性には劣るが高い導電率を有した材料、たとえば銅、アルミニウム等を使用して配線抵抗を低減し、半導体集積回路装置の性能を向上できる。このような製造方法により、融点の低いアルミニウムあるいは拡散速度の速い銅を配線材料に用いることが可能となる。

#### 【0040】

さらに、本製造方法では、配線溝を形成した後に接続孔を形成するため、配線溝の深さに相当する分だけ接続孔の深さが緩和される。このため接続孔の加工工程を容易にして加工不良による半導体集積回路装置の歩留まりの低下を抑制することができる。また、接続孔に形成される接続部の長さが短縮されるため配線とそれが接続部により接続される下部部材との間の直列抵抗を低減して半導体集積回路装置の性能を向上できる。

10

#### 【0041】

なお、第3絶縁膜の平坦化の際には、情報蓄積用容量素子に起因する段差が解消されるが、このような段差を解消するには、第3絶縁膜の堆積前にその段差に相当する絶縁膜をあらかじめ形成する方法がある。すなわち、第3絶縁膜の堆積前に、周辺回路領域またはロジック回路領域に情報蓄積用容量素子と同層に形成される第4絶縁膜を形成し、メモリセルアレイ領域と周辺回路領域またはロジック回路領域との間の情報蓄積用容量素子の高さに起因する段差を緩和または解消することができる。

20

#### 【0042】

この段差の解消方法つまり第4絶縁膜の形成方法としては、第4絶縁膜を、情報蓄積用容量素子の下部電極の形成の際に円筒形状の溝が形成される絶縁膜とする方法とができる。この方法によれば、情報蓄積用容量素子の下部電極を上方に開口を有する筒形状にする場合、第4絶縁膜を別途形成する必要はなく、下部電極を形成する際に必要な第4絶縁膜を段差の緩和にも用いるものであり、工程を簡略化することができる。特に、第3絶縁膜の堆積およびCMP法による研磨の際には、あらかじめ第4絶縁膜で段差の緩和が行われているため、CMP工程による第3絶縁膜の研磨量が多くならず、CMP工程の工程負荷を低減できる。

#### 【0043】

30

また、第3絶縁膜を、情報蓄積用容量素子を覆い、情報蓄積用容量素子の高さに相当する寸法以上の膜厚で堆積されるものとして、段差を解消することもできる。この場合、段差の解消は第3絶縁膜の堆積および第3絶縁膜のCMP法による研磨のみで行う。この場合のCMP法による研磨は、メモリセルアレイ領域上の第3絶縁膜の膜厚が相當に厚いため、CMP法での平坦性を確保することが困難になる場合も生じる。このような場合には、周辺回路領域あるいはロジック回路領域にのみCMP法による研磨の研磨速度調整層（たとえば第3絶縁膜の代表的な材料であるシリコン酸化膜よりも研磨速度の遅いシリコン窒化膜）を堆積することができる。

#### 【0044】

40

また、上記半導体集積回路装置の製造方法において、ビット線の形成と同時に、周辺回路領域またはロジック回路領域の第1絶縁膜上に、ビット線と同一の材料からなる第1層配線を形成し、接続部は、第1層配線に接続されるものとすることができる。このような半導体集積回路装置の製造方法によれば、接続部の長さが短縮化できる。すなわち、接続部が形成される接続孔の深さを低減して、接続孔の形成工程を容易にして加工不良の発生を抑制し、半導体集積回路装置の歩留まりを向上できる。

#### 【0045】

また、第1導電層を、窒化チタン膜とし、第2導電層をアルミニウム膜とすることができる。この場合、アルミニウム膜の堆積後に、半導体基板を高圧力化に保持し、アルミニウム膜を接続孔内に埋め込むことができる。

#### 【0046】

50

あるいは、第1導電層を、タンタル膜、ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜から選択された何れか1つのまたは複数の薄膜とし、第2導電層を銅膜とすることができます。この場合、銅膜は、メッキ法により堆積することができる。メッキ法には電解メッキ法、あるいは無電解メッキ法が例示できる。さらに、第3絶縁膜および配線上にシリコン窒化膜を堆積することができる。

【発明の効果】

【0047】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0048】

(1) C O B 構造のメモリセルを有する半導体集積回路装置において、立体化されたキャパシタと同層に形成された厚い絶縁膜を挟んで配置される第1層配線と第2層配線との接続信頼性を向上できる。10

【0049】

(2) 第1層配線と第2層配線との接続孔部分の抵抗を低減できる。

【0050】

(3) 第2層配線以上の配線の配線抵抗を低減できる。

【0051】

(4) 第2層配線の形成工程を高い熱処理工程が必要なキャパシタの形成工程以降とし、熱拡散係数の大きな材料あるいは熱流動性のある材料であっても第2層配線に用いることが可能となる。20

【0052】

(5) C O B 構造のメモリセルを有するD R A M と同一の基板に形成される周辺回路、あるいはロジック回路の高速応答性能を向上できる。

【0053】

また、上記効果は、特に工程数を増加することなく達成できる。

【発明を実施するための最良の形態】

【0054】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。30

【0055】

(実施の形態1)

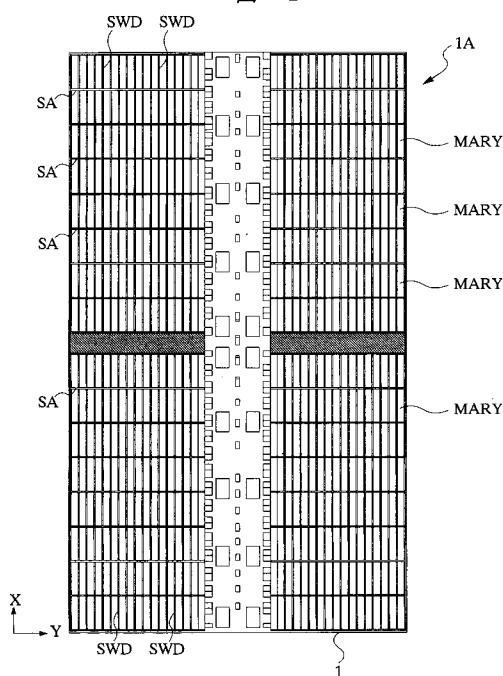

図1は、本発明の一実施の形態であるD R A M を形成した半導体チップ全体の一例を示した平面図である。本実施の形態のD R A M は、256 M b i t の記憶容量を有し、その外形サイズは、たとえば12×5 mm<sup>2</sup> であり、メモリ占有率は58%である。図示のように、単結晶シリコンからなる半導体チップ1 A の正面には、X方向(半導体チップ1 A の長辺方向)およびY方向(半導体チップ1 A の短辺方向)に沿って多数のメモリアレイM A R Y がマトリクス状に配置されている。X方向に沿って互いに隣接するメモリアレイM A R Y の間にはセンスアンプS A が配置され、センスアンプS A に接続されるビット線B L には512個のメモリセルがつながっている。ワード線に階層ワード構造が採用されている場合にはY方向に沿って互いに隣接するメモリアレイM A R Y の間にはサブワードデコーダS W D が配置されている。また、半導体チップ1 A の正面の中央部には、ワードドライバW D 、データ線選択回路などの制御回路や、入出力回路、ボンディングパッドなどが配置されている。40

【0056】

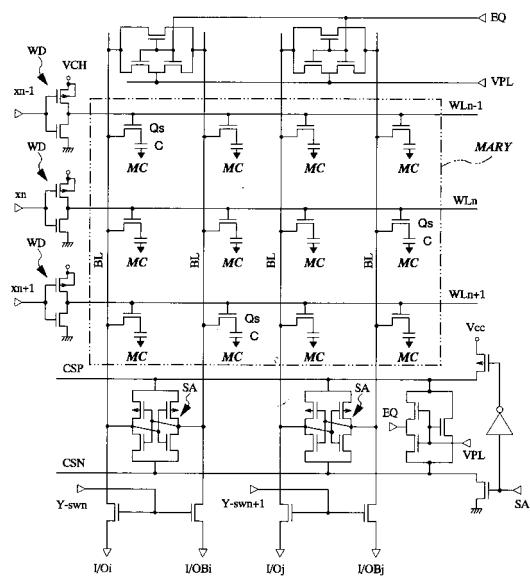

図2は、本実施の形態1のD R A M の等価回路図である。図示のように、このD R A M のメモリアレイ(M A R Y )は、マトリクス状に配置された複数のワード線W L (W L<sub>n-1</sub>、W L<sub>n</sub>、W L<sub>n+1</sub> ...)と複数のビット線B L およびそれらの交点に配置された複数のメモリセル(M C )により構成されている。1ビットの情報を記憶する1個のメモリセル

は、1個のキャパシタCとこれに直列に接続された1個のメモリセル選択用MISFETQsとで構成されている。メモリセル選択用MISFETQsのソース、ドレインの一方は、キャパシタCと電気的に接続され、他方はビット線BLと電気的に接続されている。ワード線WLの一端は、ワードドライバWDに接続され、ビット線BLの一端は、センスアンプSAに接続されている。

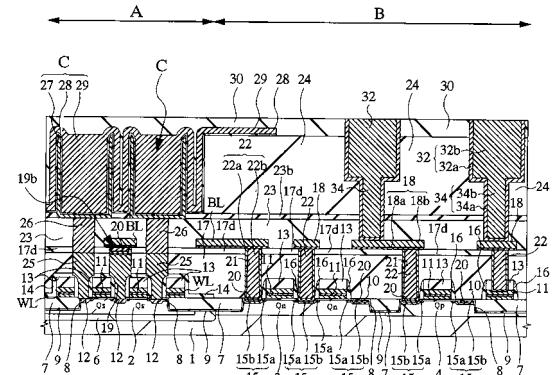

【0057】

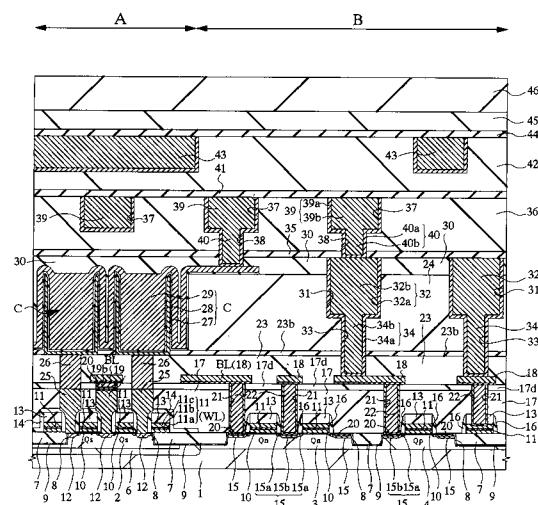

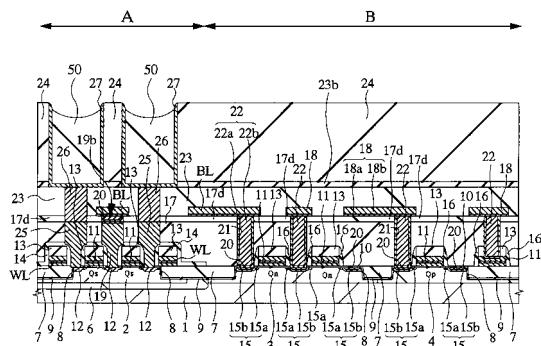

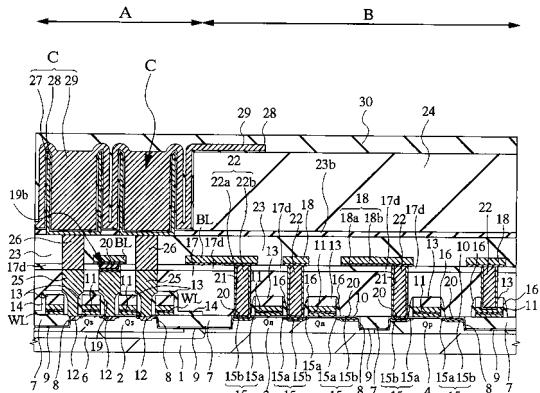

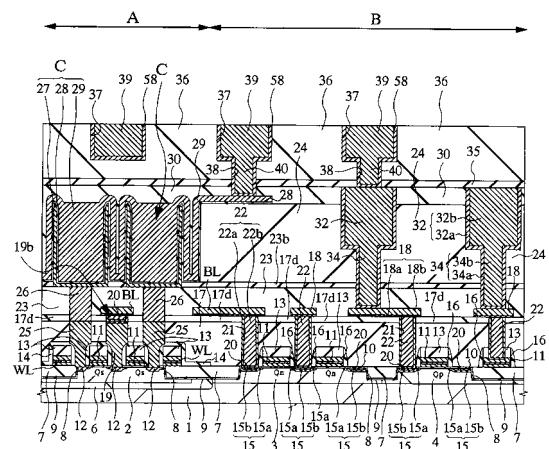

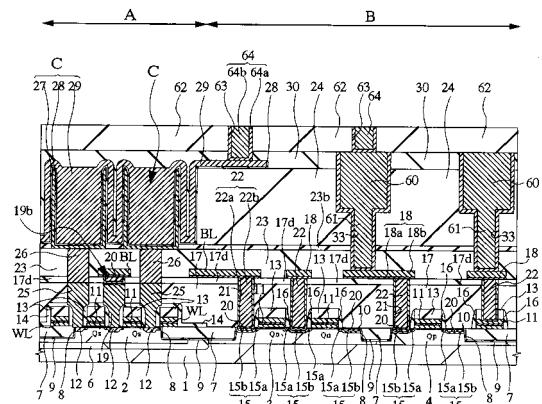

図3は、本実施の形態1のDRAMの要部断面図である。図3において、A領域はメモリアレイMARYの一部を示し、B領域は周辺回路の一部を示す。

【0058】

p形の単結晶シリコンからなる半導体基板1の主面には、A領域のp形ウェル2、B領域のp形ウェル3およびn形ウェル4が形成されている。また、p形ウェル2を囲むようにn形のディープウェル6が形成されている。なお、各ウェルには、しきい値電圧調整層が形成されていてもよい。

【0059】

各ウェルの主面には、分離領域7が形成されている。分離領域7はシリコン酸化膜からなり、半導体基板1の主面に形成された浅溝8に熱酸化されたシリコン酸化膜9を介して形成されている。

【0060】

p形ウェル2の主面にはDRAMのメモリセル選択用MISFETQsが形成されている。また、p形ウェル3およびn形ウェル4の主面には各々nチャネルMISFETQnおよびpチャネルMISFETQpが形成されている。

【0061】

メモリセル選択用MISFETQsは、p形ウェル2の主面上にゲート絶縁膜10を介して形成されたゲート電極11と、ゲート電極11の両側のp形ウェル2の主面に形成された不純物半導体領域12とからなる。ゲート絶縁膜10は、たとえば7~8nmの膜厚を有する熱酸化により形成されたシリコン酸化膜からなる。ゲート電極11は、たとえば膜厚70nmの多結晶シリコン膜11a、膜厚50nmの窒化チタン膜11bおよび膜厚100nmのタンゲステン膜11cの積層膜とすることができます。また、不純物半導体領域12にはn形の不純物、たとえば砒素またはリンが導入されている。

【0062】

メモリセル選択用MISFETQsのゲート電極11の上層にはシリコン窒化膜からなるキャップ絶縁膜13が形成され、さらにその上層をシリコン窒化膜14で覆われる。シリコン窒化膜14は、ゲート電極11の側壁にも形成され、後に説明する接続孔を形成する際の自己整合加工に利用される。なお、メモリセル選択用MISFETQsのゲート電極11は、DRAMのワード線として機能するものであり、分離領域7の上面にはワード線WLが形成されている。

【0063】

一方、nチャネルMISFETQnおよびpチャネルMISFETQpは、各々p形ウェル3およびn形ウェル4の主面上に形成され、ゲート絶縁膜10を介して形成されたゲート電極11と、ゲート電極11の両側の各ウェルの主面に形成された不純物半導体領域15とから構成される。ゲート絶縁膜10およびゲート電極11は前記と同様である。不純物半導体領域15は低濃度不純物領域15aと高濃度不純物領域15bとからなり、いわゆるLDD(Lightly Doped Drain)構造を形成している。不純物半導体領域15に導入される不純物は、MISFETの導電形に応じてn形またはp形の不純物が導入される。

【0064】

nチャネルMISFETQnおよびpチャネルMISFETQpのゲート電極11の上層にはシリコン窒化膜からなるキャップ絶縁膜13が形成され、側面には、たとえばシリコン窒化膜からなるサイドウォールスペーサ16が形成されている。

【0065】

10

20

30

40

50

メモリセル選択用M I S F E T Q s、nチャネルM I S F E T Q nおよびpチャネルM I S F E T Q pは、層間絶縁膜17で覆われている。層間絶縁膜17は、たとえばS O G (Spin On Glass)膜、T E O S (テトラメトキシシラン)を原料ガスとしプラズマC V D法により形成されたシリコン酸化膜(以下T E O S酸化膜という)がC M P (Chemical Mechanical Polishing)法により平坦化されたT E O S酸化膜およびT E O S酸化膜の積層膜とすることができます。

#### 【0066】

層間絶縁膜17上には、さらにT E O S酸化膜17dが形成され、その上面にビット線B Lおよび第1層配線18が形成されている。ビット線B Lおよび第1層配線18は、たとえば窒化チタン膜とタンゲステン膜との積層膜とすることができます。これにより、ビット線B Lおよび第1層配線18を低抵抗化してD R A Mの性能を向上することができます。また、ビット線B Lと第1層配線18とは、後に説明するように同時に形成される。これにより工程を簡略化することができます。

#### 【0067】

ビット線B Lはプラグ19およびプラグ19bを介して一対のメモリセル選択用M I S F E T Q sに共有される不純物半導体領域12に接続される。プラグ19は、たとえばn形の不純物が導入された多結晶シリコン膜とすることができます。プラグ19bは、たとえば窒化チタン膜とタンゲステン膜との積層膜とすることができます。また、プラグ19とプラグ19bとの接続部にはコバルトシリサイド膜20が形成されている。これによりプラグ19とプラグ19bとの間、つまりビット線B Lとプラグ19との間の接続抵抗を低減し、接続信頼性を向上することができます。

#### 【0068】

第1層配線18は、接続孔21内に形成されたプラグ22を介してnチャネルM I S F E T Q nおよびpチャネルM I S F E T Q pの不純物半導体領域15またはゲート電極11に接続される。プラグ22は、プラグ19bと同様にたとえば窒化チタン膜とタンゲステン膜との積層膜とすることができます。また、プラグ22と不純物半導体領域15との接続部にはコバルトシリサイド膜20が形成されている。これによりプラグ22と不純物半導体領域15との間の接続抵抗を低減し、接続信頼性を向上することができます。

#### 【0069】

ビット線B Lおよび第1層配線18は、層間絶縁膜23で覆われている。層間絶縁膜23は、たとえばS O G膜、C M P法により平坦化されたT E O S酸化膜、T E O S酸化膜の積層膜とすることができます。なお、ビット線B Lおよび第1層配線18はシリコン窒化膜からなるキャップ絶縁膜およびサイドウォールスペーサで覆われてもよい。

#### 【0070】

層間絶縁膜23の上層のA領域には情報蓄積用のキャパシタCが形成されている。また、B領域の層間絶縁膜23の上層にはキャパシタCと同層に絶縁膜24が形成されている。絶縁膜24はたとえばシリコン酸化膜とすることができます。キャパシタCと同層に形成することによりキャパシタCの標高に起因するA領域とB領域との間の段差の発生を防止することができる。これによりフォトリソグラフィの焦点深度に余裕を持たせることができ、工程を安定にして微細加工に対応することができる。なお、層間絶縁膜23の上面にはシリコン窒化膜23bが形成されている。シリコン窒化膜23bは後に説明するようにキャパシタCの下部電極27を形成する際のエッティングストップとして機能する薄膜である。

#### 【0071】

キャパシタCは、メモリセル選択用M I S F E T Q sのビット線B Lに接続される不純物半導体領域12とは逆の不純物半導体領域12に接続されるプラグ25に、プラグ26を介して接続される下部電極27と、たとえばシリコン窒化膜および酸化タンタルからなる容量絶縁膜28と、たとえば窒化チタンからなるプレート電極29とから構成される。

#### 【0072】

キャパシタCの上層には、たとえばT E O S酸化膜からなる絶縁膜30が形成されてい

10

20

30

40

50

る。絶縁膜30と絶縁膜24とは、キャパシタCを覆い、これを他の部材から絶縁する層間絶縁膜（第2層間絶縁膜）である。絶縁膜24が前記情報蓄積用容量素子（キャパシタC）の高さに起因する前記メモリセルアレイ領域と前記周辺回路領域との段差を緩和または解消する部分（第1の部分）に相当し、絶縁膜30が情報蓄積用容量素子を覆う部分（第2の部分）に相当する。絶縁膜30の表面はCMP法により平坦化され、半導体基板1の全面において平坦性が確保されている。

【0073】

絶縁膜30および絶縁膜24の表面近傍には、配線溝31が形成され、その配線溝31内には第2層配線32が形成されている。図3に示すとおり、第2層配線32の表面と絶縁膜30の表面とは同一の平面内にあり、また、第2層配線32の底面はキャパシタCの表面（プレート電極29の表面）よりも下部に位置している。第2層配線32は後に説明するようにCMP法で形成される。

【0074】

また、配線溝31の下部には接続孔33が形成され、接続孔33内には接続部34が形成されている。第2層配線32および接続部34は一体として形成されており、第2層配線32は第1導電層32aおよび第2導電層32bから構成され、接続部34は第1導電層34aおよび第2導電層34bから構成される。第1導電層32a、34aは、たとえばタンタル膜からなり、第2導電層32b、34bは、たとえば銅からなる。

【0075】

第2導電層32b、34bは、第2層配線32および接続部34の主導電層として機能するものである。このように銅からなる主導電層を有するため、第2層配線32および接続部34の低抵抗化を図ることができ、半導体集積回路装置、特に周辺回路の応答性を高速化してDRAMの性能を向上することができる。

【0076】

第1導電層32a、34aは、銅の拡散を防止するバリア層として機能するものである。特に本実施の形態ではタンタル膜を用いるため、第1導電層32a、34aと第2導電層32b、34bとの界面でTa-Cuの結合を形成し、銅の拡散またはエレクトロマイグレーションによる移動を有效地に防止することができる。また、Ta-Cuの結合を形成することにより銅膜の接着性を向上することができる。これによりDRAMの信頼性を向上できる。

【0077】

また、本実施の形態では、配線溝31の下部に接続孔33が形成されるため、配線溝31の深さに相当する分だけ接続孔33の深さを浅くできる。ここでは、たとえば配線溝31の深さ、すなわち第2層配線32の膜厚を0.7μmとし、接続孔33の深さ、すなわち接続部34の長さを0.7μmとすることができる。これは、従来技術のように絶縁膜30上に第2層配線を形成する場合と比較して接続孔の深さを1.4μmから0.7μmに短縮することができることを意味する。このように、接続孔33の深さを浅くすることにより、接続孔33の加工工程を容易にし、加工不良の発生を抑制して接続信頼性を向上し、DRAMの製造歩留まりを向上することができる。また、接続孔33の深さを浅くできるため、接続部34の長さも短くでき、接続部34の抵抗を低減して第2層配線32と第1層配線18との間の抵抗を低減することができる。

【0078】

なお、ここでは、第1導電層32a、34aとしてタンタル膜を例示しているが、ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜であってもよく、これらの積層膜であってもよい。

【0079】

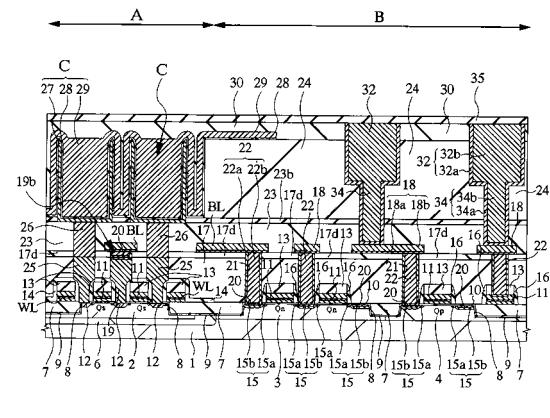

絶縁膜30および第2層配線32の上面にはシリコン窒化膜35が形成されている。このようなシリコン窒化膜35により銅の上方への拡散を防止することができる。

【0080】

シリコン窒化膜35の上層には層間絶縁膜36が形成され、層間絶縁膜36の表面近傍

10

20

30

40

50

には配線溝37が形成されている。配線溝37の底部には第2層配線32またはキャパシタCのプレート電極29に接続される接続孔38が形成されている。配線溝37の内部には第3層配線39が形成され、接続孔38の内部には接続部40が形成されている。層間絶縁膜36および第3層配線39の表面は同一平面内に存在し、後に説明するようにCMP法で形成される。

【0081】

第3層配線39は、第2層配線32と同様に、第1導電層39aおよび第2導電層39bからなり、接続部40は、接続部34と同様に、第1導電層40aおよび第2導電層40bからなる。第1導電層39a、40aは、第1導電層32a、34aと同様に、たとえばタンタル膜とすることができます、また、ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜あるいはこれらの積層膜としてもよい。第2導電層39b、40bは、第2導電層32b、34bと同様にたとえば銅からなる。第3層配線39はメインワード線MWBあるいはワード線WLのシャント配線として用いることができる。

10

【0082】

層間絶縁膜36および第3層配線39の表面にはシリコン窒化膜41が形成されており、シリコン窒化膜により第3層配線39からの銅の拡散を防止する。

【0083】

シリコン窒化膜41の上層には層間絶縁膜42が形成され、その表面近傍には第2層配線32、第3層配線39と同様な構成の第4層配線43が形成されている。第4層配線43は、図示しない接続部を介して第3層配線39に接続される。第4層配線43は、Yセレクト線YSとして用いることができる。

20

【0084】

層間絶縁膜42および第4層配線43上にはシリコン窒化膜44が形成され、さらに絶縁膜45およびパッシベーション膜46が形成されている。シリコン窒化膜44は、第4層配線43からの銅の拡散を防止する。

【0085】

次に、本実施の形態のDRAMの製造方法を図4～図28を用いて工程順に説明する。図4～図28は本発明の一実施の形態のDRAMの製造方法の一例を工程順に示した断面図である。

【0086】

30

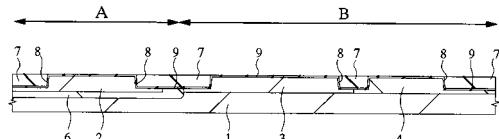

まず、p形の半導体基板1を用意し、この半導体基板1の正面に浅溝8を形成する。その後半導体基板1に熱酸化を施し、シリコン酸化膜9を形成する。さらにシリコン酸化膜を堆積してこれをCMP法により研磨して浅溝8内にのみシリコン酸化膜を残し、分離領域7を形成する。

【0087】

次に、フォトレジストをマスクにして不純物をイオン注入し、p形ウェル2、3、n形ウェル4およびディープウェル6を形成する(図4)。

【0088】

次に、p形ウェル2、3、n形ウェル4が形成された活性領域に熱酸化法によりゲート絶縁膜10を形成し、さらに半導体基板1の全面に不純物がドープされた多結晶シリコン膜、窒化チタン膜、タンゲステン膜およびシリコン窒化膜を順次堆積する。その後、シリコン窒化膜、タンゲステン膜、窒化チタン膜および多結晶シリコン膜をフォトリソグラフィ技術およびエッチング技術を用いてパターニングし、ゲート電極11(ワード線WL)およびキャップ絶縁膜13を形成する。さらにキャップ絶縁膜13およびゲート電極11とフォトレジストをマスクとして不純物をイオン注入し、不純物半導体領域12および低濃度不純物領域15aを形成する(図5)。

40

【0089】

次に、半導体基板1の全面にシリコン窒化膜(図示せず)を堆積し、メモリセルが形成される領域(A領域)にのみフォトレジスト膜47を形成する。その後、そのフォトレジスト膜をマスクとして、前記シリコン窒化膜を異方性エッチングし、A領域の半導体基板

50

1上にのみシリコン窒化膜14を形成すると同時にB領域のゲート電極11の側壁にサイドウォールスペーサ16を形成する。さらに、サイドウォールスペーサ16をマスクにして不純物を自己整合的にイオン注入し、高濃度不純物領域15bを形成する(図6)。

【0090】

次に、フォトレジスト膜47を残したまま半導体基板1の全面にコバルト膜(図示せず)をスパッタ法等で堆積し、フォトレジスト膜47を除去した後に熱処理を行って、コバルト膜と高濃度不純物領域15bとの間で選択的にシリサイド反応を行い、その後、未反応のコバルト膜を選択的にエッティングして除去し、コバルトシリサイド膜20を高濃度不純物領域15b上に形成する。

【0091】

次に、半導体基板1の全面にSOG膜を塗布し、これを400程度の温度でキュアした後、800程度の熱処理を施して安定化する。さらにプラズマCVD法によりTEOS酸化膜を堆積する。この場合のTEOS酸化膜は、半導体基板1の主面上からその表面が1.3μmの高さとなるように堆積することができる。このTEOS酸化膜をCMP法を用いて研磨し、その表面を平坦化する。これによりゲート電極11およびキャップ絶縁膜13に起因する段差が解消される。この結果、この後のフォトリソグラフィ工程のフォーカスマージンを向上することができ、微細な接続孔の開口等が可能となる。表面を洗浄後、CMPにより生じたTEOS酸化膜17d上のスクラッチによる損傷を補修するため、さらにTEOS酸化膜を堆積する。このようにして、SOG膜、CMP法により平坦化されたTEOS酸化膜およびTEOS酸化膜からなる層間絶縁膜17を形成する。

10

【0092】

次に、層間絶縁膜17に接続孔を開口し、プラグインプラを施した後に不純物がドープされた多結晶シリコン膜を堆積し、この多結晶シリコン膜をCMP法により研磨してプラグ19, 25を形成する(図7)。なお、この接続孔は、2段階のエッティングにより開口して半導体基板1の過剰エッティングを防止することができる。

【0093】

次に、TEOS酸化膜17dを形成する。このTEOS酸化膜17dを形成した時点で半導体基板1の主面からの標高は約0.8μmとなる。

【0094】

次に、ビット線BLが接続されるプラグ19が露出するようにTEOS酸化膜17dに開口を形成する。その後、半導体基板1の全面にコバルト膜(図示せず)をスパッタ法等で堆積し、熱処理を行って、コバルト膜とプラグ19との間で選択的にシリサイド反応を行い、その後、未反応のコバルト膜を選択的にエッティングして除去し、コバルトシリサイド膜20をプラグ19上に形成する。

30

【0095】

次に、nチャネルMISFETQnおよびpチャネルMISFETQpの不純物半導体領域15およびゲート電極11が露出するように層間絶縁膜17に接続孔21を形成する(図8)。なおこの段階で、先に説明した高濃度不純物領域15b上のコバルトシリサイド膜20を形成することもできる。

【0096】

次に、半導体基板1の全面、つまり接続孔21の内部を含むTEOS酸化膜17d上に窒化チタン膜22aおよびタンゲステン膜22bをたとえばスパッタ法で堆積し、TEOS酸化膜17d表面の窒化チタン膜22aおよびタンゲステン膜22bをCMP法で研磨して除去する。このようにして窒化チタン膜22aおよびタンゲステン膜22bからなるプラグ22およびプラグ19bを形成する(図9)。なお、窒化チタン膜22aは、チタン膜および窒化チタン膜の積層膜とすることもできる。

40

【0097】

次に、窒化チタン膜18aおよびタンゲステン膜18bを、たとえばスパッタ法により順次堆積し、これをフォトリソグラフィとドライエッティング技術を用いてパターニングし、窒化チタン膜18aおよびタンゲステン膜18bからなるビット線BLおよび第1層配

50

線 18 を形成する(図 10)。このように、本実施の形態では、ピット線 BL と第 1 層配線 18 とを同時に形成するため、工程を簡略化することができる。また、プラグ 22 を形成した後にピット線 BL および第 1 層配線 18 を形成するため、ピット線 BL および第 1 層配線 18 の膜厚を薄くすることができ、この結果、特にピット線 BL 間の線間容量を低減して蓄積電荷の有無の検出感度を向上できる。

#### 【0098】

なお、ピット線 BL および第 1 層配線 18 は、単層のタンゲステン膜により形成することもできる。ピット線 BL および第 1 層配線 18 をタンゲステン膜のみで形成することにより窒化チタン膜との積層膜の場合に比較して同一断面積状態での抵抗値を低減できる。これは、窒化チタンよりもタンゲステンの方が抵抗率が低いことに基づく。また、ピット線 BL および第 1 層配線 18 には、たとえばシリコン窒化膜からなるキャップ絶縁膜およびサイドウォールスペーサを形成することができる。10

#### 【0099】

次に、半導体基板 1 の全面に SOG 膜を塗布し、これを 400 程度の温度でキュアした後、プラズマ CVD 法により TEOS 酸化膜を堆積する。この TEOS 酸化膜の堆積は、その表面が TEOS 酸化膜 17d から 0.8 μm となるように行う。その後、この TEOS 酸化膜を CMP 法を用いて研磨し、SOG 膜および表面が平坦化された層間絶縁膜 23 を形成する。平坦化された層間絶縁膜 23 の表面は、TEOS 酸化膜 17d から 0.6 μm となる。これによりこの後のフォトリソグラフィ工程のフォーカスマージンを向上することができ、微細な接続孔の開口等が可能となる。なお、表面を洗浄後、さらに TEOS 酸化膜を堆積して CMP により形成されたスクラッチを覆ってもよい。20

#### 【0100】

次に、層間絶縁膜 23 に接続孔を開口し、不純物がドープされた多結晶シリコン膜を堆積し、この多結晶シリコン膜を CMP 法により研磨してプラグ 26 を形成する(図 11)。

。

#### 【0101】

次に、半導体基板 1 の全面に 200 nm 膜厚のシリコン窒化膜 23b を形成し、絶縁膜 24 を堆積する(図 12)。絶縁膜 24 の堆積はプラズマ CVD により行うことができ、その膜厚は 1.2 μm とする。

#### 【0102】

次に、キャパシタ C の形成工程を説明する。必要な蓄積容量は約 30 pF である。30

#### 【0103】

キャパシタ C が形成される領域に 0.75 × 0.25 μm の寸法で溝 48 を形成する。溝 48 の形成によりプラグ 26 を露出させる(図 13)。溝 48 の形成にはフォトリソグラフィおよびドライエッチング技術を用いることができる。

#### 【0104】

次に、溝 48 を覆う多結晶シリコン膜 49 を半導体基板 1 の全面に堆積し、さらに半導体基板 1 の全面にシリコン酸化膜 50 を堆積する(図 14)。多結晶シリコン膜 49 にはリンをドープすることができ、その膜厚は 0.03 μm とすることができる。多結晶シリコン膜 49 の膜厚が溝 48 の寸法に対して十分に薄いため、多結晶シリコン膜 49 は溝 48 の内部にもステップカバレッジよく堆積される。シリコン酸化膜 50 は、溝 48 の内部に埋め込まれるように堆積する。溝 48 の内部への埋め込み性を考慮すれば、シリコン酸化膜 50 は SOG 膜あるいは TEOS を用いた CVD 法によるシリコン酸化膜とすることができます。40

#### 【0105】

次に、絶縁膜 24 上のシリコン酸化膜 50 および多結晶シリコン膜 49 を除去して、キャパシタ C の下部電極 27 を形成する(図 15)。シリコン酸化膜 50 および多結晶シリコン膜 49 の除去はエッチバッカ法または CMP 法により行うことができる。また、下部電極 27 の内部には、シリコン酸化膜 50 が残存している。

#### 【0106】

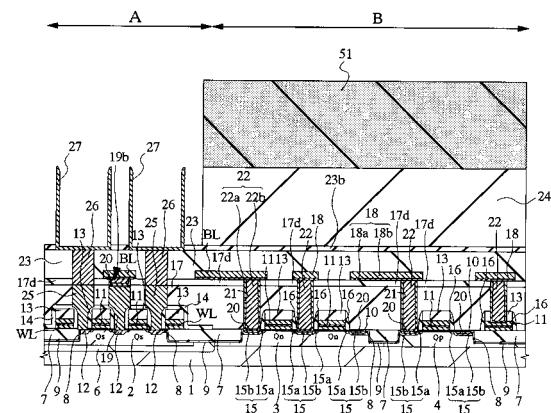

次に、フォトレジスト膜51をマスクとしてウェットエッティングを施し、メモリセルアレイ領域(A領域)の絶縁膜24およびシリコン酸化膜50を除去する(図16)。これにより下部電極27が露出される。

【0107】

なお、シリコン窒化膜23bはウェットエッティング工程でのエッティングストップとして機能する。また、絶縁膜24のエッジ部分は、ウェットエッティングによりエッティングされるため、厳密には図示のように急峻ではないが、簡単のため急峻に(直角に)示している。

【0108】

このように、周辺回路領域(B領域)に絶縁膜24を残すため、キャパシタCが形成された後のメモリセルアレイ領域(A領域)と周辺回路領域(B領域)との間に、キャパシタCの高さ(下部電極27の高さもある)に起因した段差が大きく形成されないため、キャパシタCの形成工程後の工程のフォトリソグラフィを精細に行うことができ、DRAMの高集積化に対応することが容易となる。

【0109】

次に、下部電極27表面を窒化または酸化タンタル膜を堆積する。酸化タンタル膜の堆積は、有機タンタルガスを原料としたCVD法により形成できる。この段階での酸化タンタル膜はアモルファス構造を有するものである。ここで酸化タンタル膜に熱処理を施して結晶化(多結晶化)された酸化タンタル膜( $Ta_2O_5$ )とし、より強固な誘電体として容量絶縁膜28を形成する。この熱処理は700以上(10)の温度で行う必要がある。したがって、本熱処理工程前に形成された部材の耐熱性が問題となるが、本実施の形態では、未だ耐熱性に問題のある第2層配線等が形成されていない。このため、熱処理工程に特に制限を設ける必要はない。このため、誘電率の大きな多結晶酸化タンタル膜を安定に形成でき、キャパシタCの形成面積を増大させることなくキャパシタCの蓄積容量を増加することができる。

【0110】

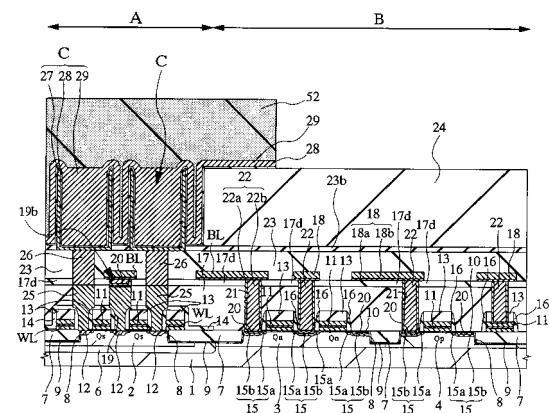

さらに、窒化チタン膜をたとえばCVD法により堆積する。その後、フォトレジスト膜52を用いて窒化チタン膜および多結晶酸化タンタル膜をパターニングし、容量絶縁膜28およびプレート電極29を形成する(図17)。このようにして下部電極27、容量絶縁膜28およびプレート電極29からなるキャパシタCが形成される。

【0111】

次に、TEOS酸化膜53を半導体基板1の全面に堆積する(図18)。TEOS酸化膜53は、プレート電極29を絶縁するためのものであり、その膜厚は、0.3μmとする。このTEOS酸化膜53をCMP法により研磨して平坦化し、絶縁膜30を形成する(図19)。この段階で、絶縁膜30の上面と第1層配線18との距離は、1.4μmである。このように、絶縁膜24でメモリセルアレイ領域(A領域)と周辺回路領域(B領域)との段差をあらかじめ緩和しているため、TEOS酸化膜53を平坦化して絶縁膜30を形成するCMP工程の工程負荷を低減することができる。また、絶縁膜30の表面が平坦化されているため、その後のフォトリソグラフィ工程を精密に行うことができ微細な加工が可能となり、また、後に説明するようにいわゆるダマシン法を用いて配線を形成しても、絶縁膜30の表面に残留金属が生じない。

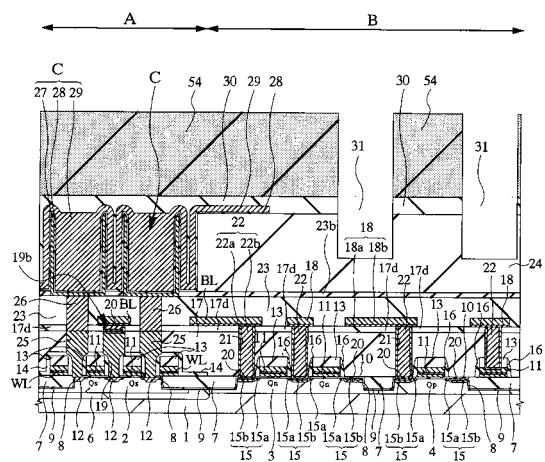

【0112】

次に、フォトレジスト膜54を用いて、絶縁膜30および絶縁膜24をドライエッティングによりエッティングし、配線溝31を形成する(図20)。さらに、フォトレジスト膜54を除去した後、フォトレジスト膜55を形成し、これを用いて絶縁膜24、シリコン窒化膜23bおよび層間絶縁膜23をドライエッティングによりエッティングし、接続孔33を形成する(図21)。このように、配線溝31の底面下に接続孔33を形成するため、接続孔33を加工するドライエッティングでのエッティング深さが浅くなる。このため接続孔33のドライエッティング工程のエッティングアスペクト比を小さくすることができ、エッティング加工を容易にすることができる。この結果、接続孔33のドライエッティング工程での加

10

20

30

40

50

工不良を低減してDRAMの製造歩留まりの向上および信頼性の向上を図ることができる。

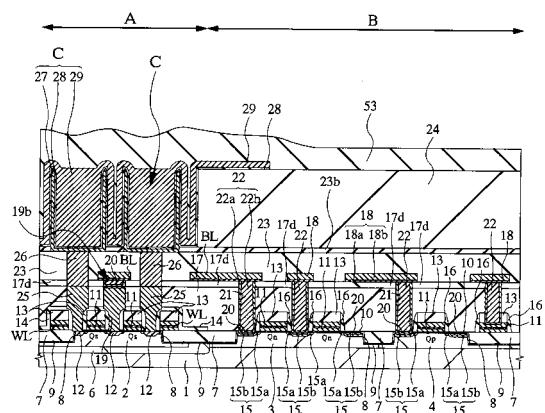

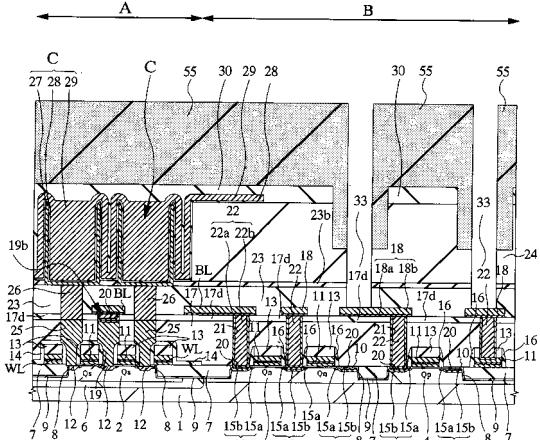

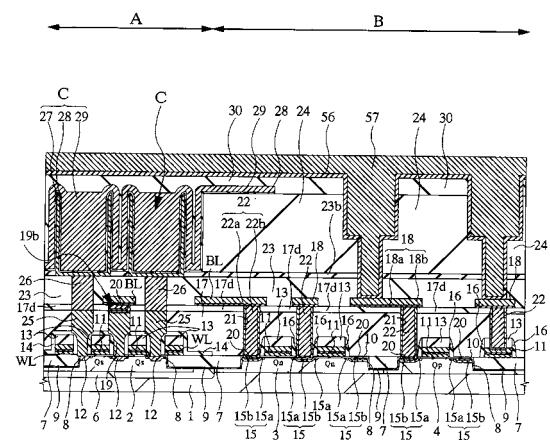

【0113】

次に、配線溝31および接続孔33の内部を含む半導体基板1の全面に、タンタル膜56をスパッタ法またはCVD法を用いて堆積する。さらに、銅膜57をタンタル膜56上に堆積する(図22)。銅膜57の堆積は、電解メッキ法または無電解メッキ法等のメッキ法により行うことができる。メッキ法を用いるため、接続孔33のような微細な空間内にも銅膜57を良好に埋め込むことができる。

【0114】

次に、配線溝31以外の領域の絶縁膜30上の銅膜57およびタンタル膜56を、CMP法を用いて研磨し除去する。このようにして配線溝31内に第2層配線32を、接続孔33内に接続部34を形成する(図23)。タンタル膜56は、第2層配線32の第1導電層32aとなり、接続部34の第1導電層34aとなる。また、銅膜57は、第2層配線32の第2導電層32bとなり、接続部34の第2導電層34bとなる。前記したとおり、第2層配線32と接続部34とは一体に形成される。第1導電層32a、34aが銅のバリア膜として機能し、第2導電層32b、34bが第2層配線32および接続部34の主導電層となることは前記したとおりである。

【0115】

なお、本実施の形態では、第2層配線32の厚さ(配線溝31の深さ)を0.7μmとし、接続部34の長さ(接続孔33の深さ)を、0.7μmとすることができます。また、タンタル膜56の他にニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜であってもよく、これらの積層膜であってもよい。ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜もスパッタ法またはCVD法を用いて堆積できる。

【0116】

次に、絶縁膜30および第2層配線32上にシリコン窒化膜35を堆積する(図24)。シリコン窒化膜35の堆積はプラズマCVD法あるいはスパッタ法で行える。このシリコン窒化膜35により第2層配線32の銅の拡散を抑制できる。

【0117】

次に、シリコン窒化膜35上に層間絶縁膜36を堆積する。層間絶縁膜36としてTEOS酸化膜を堆積することができます。さらに、前記した配線溝31および接続孔33の場合と同様にフォトレジスト膜をマスクとしたドライエッティングにより層間絶縁膜36、シリコン窒化膜35あるいは絶縁膜30をエッティングし、配線溝37および接続孔38を形成する(図25)。

【0118】

次に、前記したタンタル膜56および銅膜57と同様に、配線溝37および接続孔38の内部を含む半導体基板1の全面にタンタル膜58および銅膜59を堆積する(図26)。さらに、層間絶縁膜36上のタンタル膜58および銅膜59をCMP法により研磨して除去し、配線溝37に第3層配線39を、接続孔38に接続部40を形成する(図27)。タンタル膜58は、第3層配線39の第1導電層39aとなり、接続部40の第1導電層40aとなる。また、銅膜59は、第3層配線39の第2導電層39bとなり、接続部40の第2導電層40bとなる。第3層配線39と接続部40とは一体に形成されることは第2層配線32の場合と同様である。第1導電層39a、40aが銅のバリア膜として機能し、第2導電層39b、40bが第3層配線39および接続部40の主導電層となることは前記したとおりである。

【0119】

なお、タンタル膜58の他にニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜であってもよく、これらの積層膜であってもよい。ニオブ膜、窒化タンタル膜、窒化チタン膜または窒化タンゲステン膜もスパッタ法またはCVD法を用いて堆積できる。

【0120】

10

20

30

40

50

次に、層間絶縁膜36および第3層配線39上にシリコン窒化膜41を堆積し、第3層配線39の場合と同様に、層間絶縁膜42、第4層配線43および図示しない接続部を形成後、シリコン窒化膜44を堆積する(図28)。これらの詳細は第3層配線39の場合と同様であるため説明を省略する。

【0121】

最後に、絶縁膜45を半導体基板1の全面に堆積後、MISFETのダメージ回復を図るため、400での水素アニール処理を施し、さらに半導体基板1の全面にパッシベーション膜46を堆積して図3に示すDRAMがほぼ完成する。

【0122】

上記したDRAMおよびその製造方法によれば、絶縁膜30が平坦化され、メモリセルアレイ領域(A領域)と周辺回路領域(B領域)との間の段差が解消されているため、第2層配線32以降の工程を精密に行って、加工精度を向上できるとともに、配線溝31の底面下に接続孔33を形成するため、前記段差解消に起因する絶縁膜30および絶縁膜24の厚さによる接続孔のアスペクト比を小さくすることができる。これにより、接続孔33を確実に開口してDRAMの歩留まりおよび信頼性を向上できる。また、このため、第2層配線32の底面は、キャパシタCの上面よりも低く位置することとなる。

【0123】

また、接続孔33の深さが浅くなるため、接続部34の長さが短くなり、接続部34の抵抗を低減できる。これにより第1層配線18と第2層配線32との間の抵抗を低減してDRAMの周辺回路の高速応答性能等の性能向上を図ることができる。

【0124】

さらに、第2層配線32および接続部34の主導電層(第2導電層32b, 34b)に銅材料を採用して、第2層配線32および接続部34の抵抗をさらに低減し、DRAMの性能をさらに向上できる。

【0125】

また、本実施の形態では、キャパシタCの形成後に第2層配線32および接続部34を形成するため、キャパシタCの容量絶縁膜28の形成工程における熱処理に制限を設ける必要はなく、安定して高い誘電率の容量絶縁膜28を形成し、キャパシタCの蓄積容量値を大きくできる。逆に、第2層配線32および接続部34の材料として耐熱性の高い多結晶シリコン膜やタンゲステン膜を採用する必要はなく、熱拡散しやすい銅を用いることが可能となる。これにより、導電率の高い銅を用いて第2層配線32および接続部34の抵抗を低減し、DRAMの性能を向上できる。

【0126】

なお、本実施の形態の効果を説明するため、特開平9-92794号公報に記載された技術等(従来技術)と比較して説明する。

【0127】

特開平9-92794号公報に記載の技術では第1層配線と第2層配線とを接続するプラグをキャパシタ形成工程前に形成しているため、プラグ形成工程が増える欠点があり、その他に、第2層配線の形成後にキャパシタ形成されるため、銅のような拡散係数の高い材料を第2層配線に用いることができない。仮に銅を第2層配線に用いた場合には、キャパシタ形成工程に700という高い温度の熱処理工程を採用することはできない。しかし、本実施の形態ではこのような不具合はない。

【0128】

また、本実施の形態の構造を採用しないDRAMでは、キャパシタCの形成工程後に第2層配線がメモリセルアレイ上にも形成されるが、プレート電極との絶縁性を確保する必要等から、さらにシリコン酸化膜を0.3μm程度の膜厚で堆積している。このため、第2層配線と第1層配線との間隔は、1.7μmとなる。また、第2層配線は、メモリセルアレイ領域と周辺回路領域との段差を解消する絶縁膜上に形成されるため、第2層配線と第1層配線とを接続する接続孔の深さは1.7μmとなる。仮に0.3μm厚さのシリコン酸化膜を形成しない場合であっても接続孔の深さは1.4μmとなる。したがって、第2層配線と

10

20

30

40

50

第1層配線とを接続するプラグの長さは $1.4 \mu m$ 以上となる。このようなアスペクト比の高いプラグを形成するためには深い接続孔にも埋め込みの可能な窒化チタン膜あるいはブランケットCVD法等によるタンゲステン膜の採用が必要となる。よって、このような技術により形成されたプラグの抵抗は、約5程度となり、また、接続孔が深いため製造歩留りは70%程度に止まる。また、このように高い抵抗値のプラグにより周辺回路の配線を構成するため、周辺回路の動作周波数は、プラグの抵抗で律速され、最大で約125kHzとなる。

#### 【0129】

これに対し、本実施の形態では、前記プラグの相当する接続部34の主導電層の抵抗率の低い銅を用い、また、その長さが $0.7 \mu m$ と短いため、接続部34の抵抗値は1以下となる。また、製造歩留りは、接続孔33の深さが浅いため99%以上を確保することができる。したがって、周辺回路の動作周波数は、接続部34が銅を主導電層とすることに加え第2層配線32も主導電層を銅としているため、最大700kHz以上とすることが可能となる。

#### 【0130】

なお、本実施の形態では、接続部34が第1層配線18に接続される例を説明したが、周辺回路領域(B領域)に第1層配線18およびプラグ22を形成せず、接続部34をnチャネルMISFETQnおよびpチャネルMISFETQpの不純物半導体領域15またはゲート電極11に直接接続させることも可能である。この場合、第2層配線32は、第1層配線として機能する。

#### 【0131】

また、本実施の形態では、絶縁膜24によりキャパシタCに起因する段差を緩和する例を示したが、絶縁膜24を形成せず、キャパシタCの標高以上の膜厚の絶縁膜30を堆積し、この絶縁膜30をCMP法により研磨して平坦化してもよい。この場合、周辺回路領域(B領域)のCMPによるディッシングを防止するため、周辺回路領域(B領域)にたとえばシリコン窒化膜を形成することが望ましい。

#### 【0132】

また、絶縁膜24は、キャパシタCの下部電極27を形成するための溝48を形成した絶縁膜24を用いるのではなく、キャパシタCの形成後に、キャパシタCの標高以上の膜厚の絶縁膜を堆積し、この絶縁膜を周辺回路領域(B領域)を覆うフォトトレジスト膜をマスクとしてエッティングし、周辺回路領域にのみ残すようにして形成されたものであってよい。

#### 【0133】

また、本実施の形態では、第3層配線39、第4層配線43にも銅を主導電層とする配線を適用した例を示したが、下層配線と接続されるプラグを形成した後に、たとえばチタン膜、アルミニウム膜、窒化チタン膜の積層膜をパターニングして第3層配線、第4層配線としてもよい。

#### 【0134】

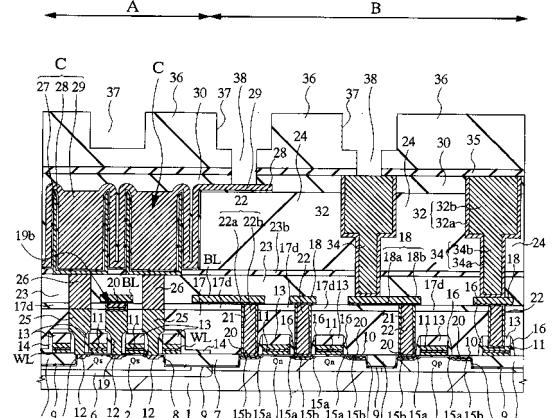

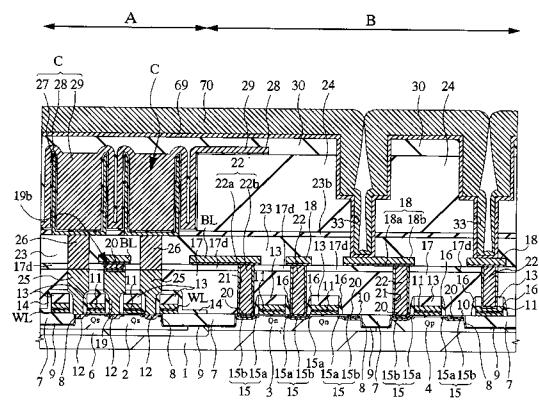

##### (実施の形態2)

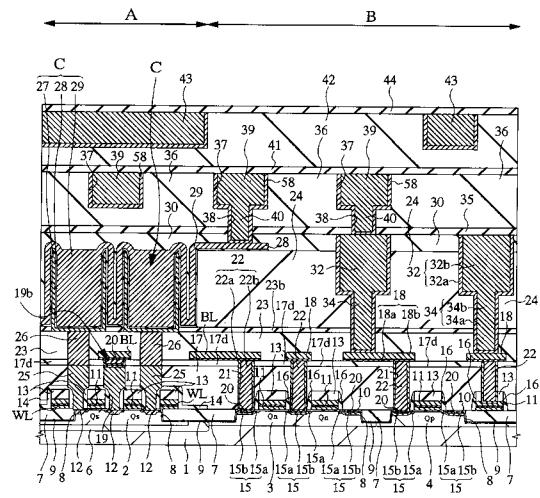

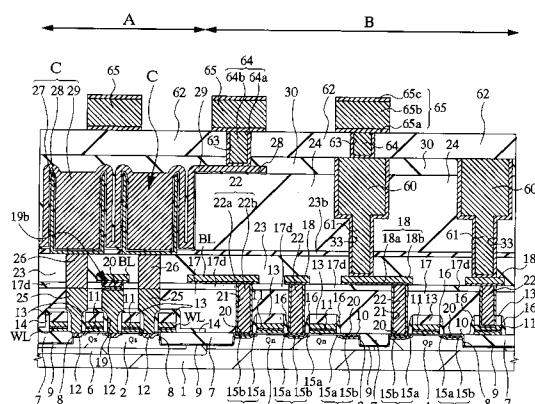

図29は、本発明の他の実施の形態であるDRAMの要部断面図である。本実施の形態のDRAMは実施の形態1のDRAMとその平面配置および回路構成(図1および図2)において同様である。したがって、その部分の説明は省略する。また、本実施の形態のDRAMは、実施の形態1のDRAMと第2層配線以上の構成および製造方法についてのみ相違し、その他の構成および絶縁膜30への配線溝31および接続孔33の形成工程(図21)まで同様である。したがって、その部分の説明についても省略する。

#### 【0135】

本実施の形態のDRAMの第2層配線60は、絶縁膜30および絶縁膜24の表面近傍に形成された配線溝31内に形成されている。図29に示すとおり、第2層配線60の表面と絶縁膜30の表面とは同一の平面内にあり、また、第2層配線60の底面はキャパシタCの表面(プレート電極29の表面)よりも下部に位置している。この点は実施の形態

10

20

30

40

50

1と同様である。

【0136】

また、配線溝31の下部には接続孔33が形成され、接続孔33内には接続部61が形成されている。第2層配線60および接続部61は、実施の形態1と同様、一体として形成されており、第2層配線60は窒化チタン膜からなる第1導電層60aおよびアルミニウム膜からなる第2導電層60bから構成される。接続部61は窒化チタン膜からなる第1導電層61aおよびアルミニウム膜からなる第2導電層61bから構成される。

【0137】

第2導電層60b、61bは、第2層配線60および接続部61の主導電層として機能するものである。このようにアルミニウムからなる主導電層を有するため、第2層配線60および接続部61の低抵抗化を図ることができ、半導体集積回路装置、特に周辺回路の応答性を高速化してDRAMの性能を向上することができる。第1導電層60a、61aは、アルミニウム膜を形成する際のウェッティング層として機能するものである。

【0138】

また、実施の形態1と同様に、配線溝31の下部に接続孔33が形成されるため、配線溝31の深さに相当する分だけ接続孔33の深さを浅くできる。したがって、実施の形態1と同様に、第2層配線60の膜厚を0.7μmとし、接続部61の長さを0.7μmとすることができる。この結果、実施の形態1で説明した加工不良の発生の抑制による接続信頼性の向上、DRAMの製造歩留まりの向上の効果、接続部61の長さの短縮化によるDRAMの性能向上の効果も同様に得ることができる。

【0139】

絶縁膜30および第2層配線60の上面には層間絶縁膜62が形成され、層間絶縁膜62には、接続孔63が形成されている。接続孔63には、窒化チタン膜64aおよびタンゲステン膜64bからなるプラグ64が形成され、第2層配線60またはプレート電極29に接続されている。層間絶縁膜62は、たとえばTEOS酸化膜とすることができます。

【0140】

層間絶縁膜62およびプラグ64上には、窒化チタン膜65a、アルミニウム膜65bおよび窒化チタン膜65cからなる第3層配線65が形成され、第3層配線65は、層間絶縁膜66で覆われている。また、層間絶縁膜66上には、窒化チタン膜67a、アルミニウム膜67bおよび窒化チタン膜67cからなる第4層配線67が形成され、第4層配線67は、絶縁膜68で覆われている。

【0141】

層間絶縁膜66および絶縁膜68は、たとえばバイアスパッタを併用したCVD法で形成されたシリコン酸化膜とすることができます。第3層配線65はメインワード線MWBあるいはワード線WLのシャント配線として用いることができる。第4層配線67は、図示しない接続部を介して第3層配線65に接続される。第4層配線67は、Yセレクト線YSとして用いることができる。絶縁膜68上にはパッシベーション膜46が形成されている。

【0142】

次に、本実施の形態のDRAMの製造方法を図30～図37を用いて工程順に説明する。図30～図37は本発明の他の実施の形態のDRAMの製造方法の一例を工程順に示した断面図である。

【0143】

本実施の形態のDRAMの製造方法は、前記したとおり、実施の形態1の図21の工程までは同様である。

【0144】

配線溝31および接続孔33の内部を含む半導体基板1の全面に、窒化チタン膜69をたとえばCVD法を用いて堆積する。さらに、アルミニウム膜70をたとえばスパッタ法を用いて堆積する(図30)。アルミニウム膜70は、スパッタ法で堆積されるため、図示するとおりステップカバレッジが悪く、ボイド等を有する状態となる。

10

20

30

40

50

## 【0145】

そこで、半導体基板1を3000気圧程度の高圧力下に保持する。このような高圧力下では温度の上昇し、アルミニウム膜70が流動性を持つ状態となって、配線溝31および接続孔33の内部に完全に埋め込まれる(図31)。この際、窒化チタン膜69がアルミニウム膜70のウェッティング層として機能し、アルミニウムの流動性をよくして埋め込み性を向上できる。

## 【0146】

次に、配線溝31以外の領域の絶縁膜30上のアルミニウム膜70および窒化チタン膜69を、CMP法を用いて研磨し除去する。このようにして配線溝31内に窒化チタン膜からなる第1導電層60aおよびアルミニウム膜からなる第2導電層60bから構成される第2層配線60を、接続孔33内に窒化チタン膜からなる第1導電層61aおよびアルミニウム膜からなる第2導電層61bから構成される接続部61を形成する(図32)。このように第2層配線60と接続部61とは一体に形成される。

10

## 【0147】

次に、絶縁膜30および第2層配線60上にTEOS酸化膜を堆積し、層間絶縁膜62を形成する。さらに、フォトレジスト膜をマスクとしたドライエッティングにより層間絶縁膜62および絶縁膜30をエッティングし接続孔63を形成する(図33)。

## 【0148】

次に、接続孔63の内部を含む層間絶縁膜62上に窒化チタン膜71およびタンゲステン72を順次堆積し(図34)、接続孔63以外の層間絶縁膜62上の窒化チタン膜71およびタンゲステン72をCMP法で研磨し除去して窒化チタン膜64aおよびタンゲステン膜64bからなるプラグ64を形成する(図35)。窒化チタン膜64aおよびタンゲステン膜64bはCVD法またはスパッタ法で堆積できる。

20

## 【0149】

次に、窒化チタン膜をCVD法で、アルミニウム膜をスパッタ法で堆積し、窒化チタン膜、アルミニウム膜および窒化チタン膜からなる積層膜を堆積する。その後、フォトリソグラフィとドライエッティング技術を用いて積層膜をパターニングし、窒化チタン膜65a、アルミニウム膜65bおよび窒化チタン膜65cからなる第3層配線65を形成する(図36)。

## 【0150】

30

次に、スパッタを重畳させたCVD法でシリコン酸化膜を堆積し、これによってシリコン酸化膜を第3層配線65に埋め込む。その後このシリコン酸化膜をCMP法を用いて平坦化し、層間絶縁膜66を形成する。さらに、第3層配線65と同様に、図示しないプラグおよび第4層配線67を形成する(図37)。

## 【0151】

最後に、絶縁膜68を半導体基板1の全面に堆積後、MISFETのダメージ回復を図るため、400での水素アニール処理を施し、さらに半導体基板1の全面にパッシバーション膜46を堆積して図29に示すDRAMがほぼ完成する。

## 【0152】

本実施の形態のDRAMおよびその製造方法によれば、実施の形態1で説明した効果と同様の効果を得ることができる。また、本実施の形態では、電気抵抗が低いアルミニウムを用いているため、接続部61の抵抗値は1以下である。また、製造歩留りは、接続孔33が短いため、99%以上である。また、周辺回路の動作周波数は、第2層配線60および接続部61がアルミニウムを用いてあるため、最大500kHz以上である。

40

## 【0153】

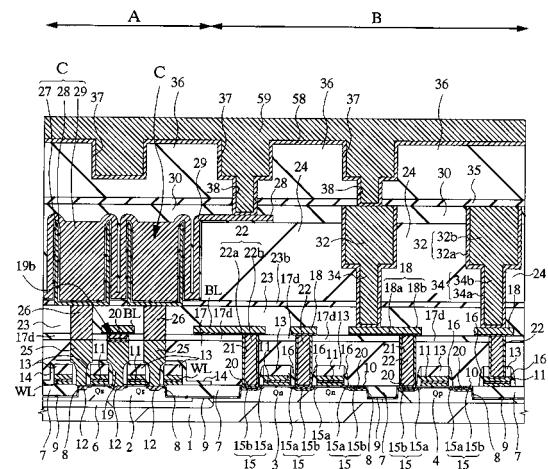

## (実施の形態3)

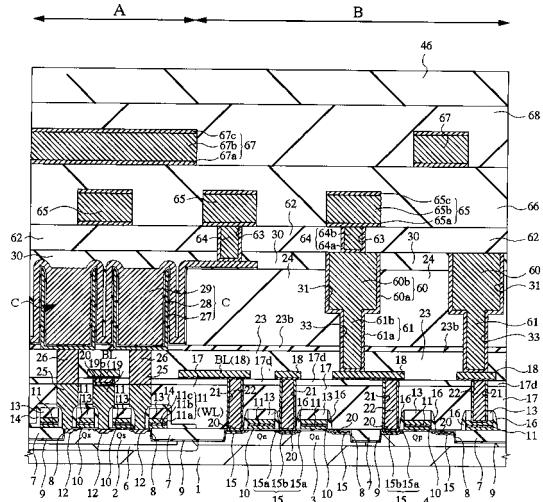

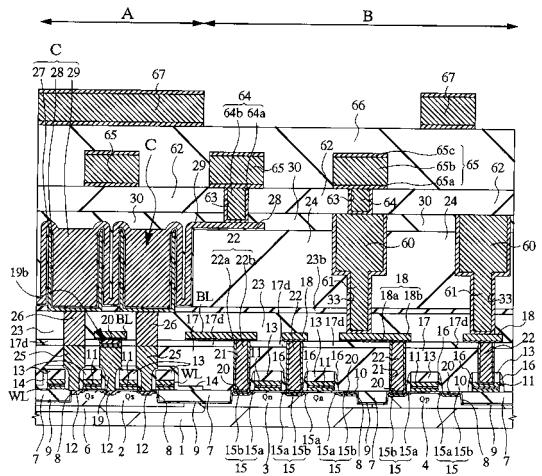

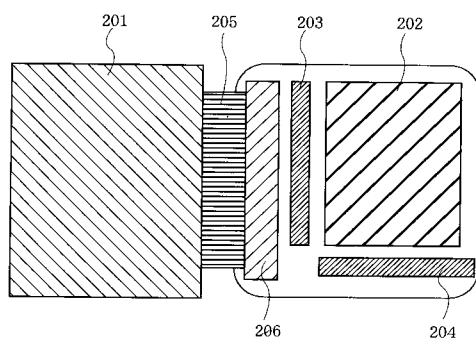

図38は、本発明のさらに他の実施の形態である半導体集積回路装置を形成した半導体チップ全体の一例を示した平面図である。

## 【0154】

本実施の形態の半導体集積回路装置は、DRAMとロジック回路とを单一チップ内に混

50

載させたものであり、ロジック部 201、メモリ部 202 を有する。ロジック部 201 には論理演算等を行う C P U、スタック等が形成され、メモリ部 202 にはデータの記憶素子が形成されている。メモリ部 202 の周辺には第 1 の I/O 部 203、第 2 の I/O 部 204 が配置され、データの入出力を制御する。また、第 1 の I/O 部 203、第 2 の I/O 部 204 を介して入出力されるデータは、デコーダ部 206 を介してバス 205 に伝送され、ロジック部 201 に送られる。

【0155】

本実施の形態の半導体集積回路装置のチップサイズは  $15 \times 8 \text{ mm}^2$  であり、D R A M のメモリ容量は 256 M b i t である。

【0156】

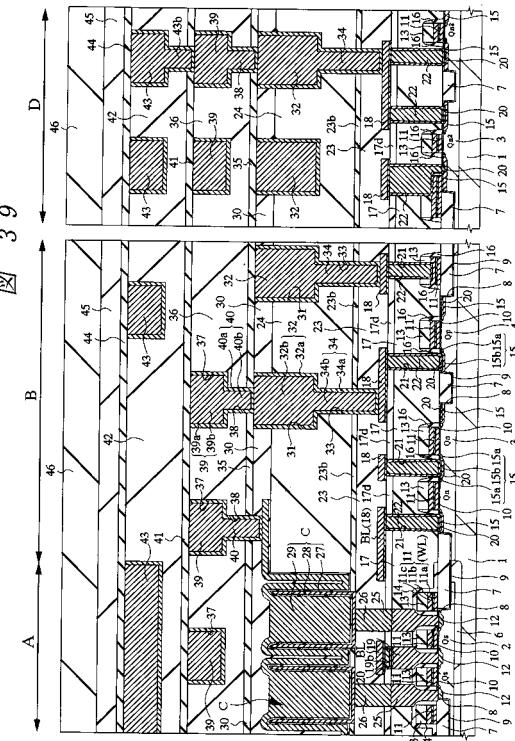

図 39 は、本実施の形態の D R A M の要部断面図である。本実施の形態の D R A M のメモリセルアレイ領域 (A 領域) および周辺回路領域 (B 領域) は、実施の形態 1 とその構成および製造方法において同様である。したがって、その部分の説明を省略する。

【0157】

本実施の形態の半導体集積回路装置は、メモリセルアレイ領域 (A 領域) および周辺回路領域 (B 領域) の他にロジック回路領域 (D 領域) を有する。ロジック回路領域は、メモリセルアレイ領域および周辺回路領域以外の領域であり、たとえばロジック部 201、第 1 の I/O 部 203、第 2 の I/O 部 204、バス 205、等が形成されている。

【0158】

ロジック回路領域 (D 領域) の半導体基板 1 には、周辺回路領域と同様の p 形ウェル 3、分離領域 7 が形成され、その主面上には、周辺回路領域と同様の n チャネル M I S F E T Q n が形成されている。ここでは n チャネル M I S F E T Q n 2 を例示しているが p チャネル M I S F E T であってもよい。また、C M I S F E T 構造を有していてもよい。

【0159】

n チャネル M I S F E T Q n 2 のゲート電極 11、キャップ絶縁膜 13、サイドウォールスペーサ 16、ソース・ドレイン領域を構成する不純物半導体領域 15 は、周辺回路領域と同様である。また、層間絶縁膜 17、T E O S 酸化膜 17 d その上層に形成される第 1 層配線 18、プラグ 22 も周辺回路領域と同様である。さらに、層間絶縁膜 23、シリコン窒化膜 23 b、絶縁膜 24、絶縁膜 30、第 2 層配線 32、接続部 34、シリコン窒化膜 35、41、44、層間絶縁膜 36、42、第 3 層配線 39、接続孔 38、第 4 層配線 43、第 4 層配線の接続部 43 b、絶縁膜 45、パッシベーション膜 46 についても周辺回路領域と同様である。したがって、説明を省略する。第 4 層配線 43 は、メモリ部 202 とロジック部 201 とを接続するバス 205 に適用することができる。

【0160】

本実施の形態の半導体集積回路装置の製造方法は、前記したロジック回路領域の各々の部材に対応する周辺回路領域の各部材の製造方法と同様であり、実施の形態 1 で説明したとおりである。したがって、詳細な説明を省略する。

【0161】

本実施の形態の半導体集積回路装置によれば、前記した実施の形態 1 の効果に加えて、以下の効果を有する。すなわち、図 39 に示したとおり、D R A M の領域 (メモリセルアレイ領域 (A 領域) および周辺回路領域 (B 領域)) とロジック回路領域 (D 領域) とが、同一の第 2 層配線 32、第 3 層配線 39 および第 4 層配線 43 で接続されることとなるが、これらの配線は銅を主導電層とする高速応答性能に優れた配線である。したがって、D R A M の部分とロジック回路の部分とは高速配線で接続され、半導体集積回路装置の動作周波数を大きくして半導体集積回路装置の性能を向上できる。本実施の形態の場合、動作周波数は、最大 700 k H z 以上とすることができます。このような高速応答性能は、D R A M とロジック回路とを別個独立した半導体チップで構成した場合には、それらを接続する配線が長くならざるを得ず、高い動作周波数は得られない。一方、同一チップに D R A M とロジック回路とを混載した場合であっても、抵抗率の高い配線を用いる場合や、抵抗値の高い接続部あるいはプラグで異層間の配線接続を行う場合にもこのような高い動作

10

20

30

40

50

周波数は得難い。すなわち、本実施の形態では、接続部34の抵抗値を低減し、第2層配線32、第3層配線39および第4層配線43に抵抗率の低い銅材料を用い、かつ、DRAMの領域とロジック回路領域で同一の配線を用いることにより、前記した難点を解消し、半導体集積回路装置の性能を著しく高めたものである。

【0162】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0163】

たとえば、上記実施の形態ではシリコンMISFETを例示して説明したが他の半導体材料を用いたMIS型半導体装置にも適用することができる。 10

【産業上の利用可能性】

【0164】

本発明は、半導体集積回路装置およびその製造技術に適用でき、特に、いわゆるCOB (Capacitor Over Bitline) 構造を有するDRAM (Dynamic Random Access Memory)、あるいは、そのようなDRAMと論理制御回路または論理演算回路等のロジック回路とが1つの半導体基板に混載された半導体集積回路装置に適用して有効な技術である。

【図面の簡単な説明】

【0165】

【図1】実施の形態1のDRAMを形成した半導体チップ全体の一例を示した平面図である。 20

【図2】実施の形態1のDRAMの等価回路図である。

【図3】実施の形態1のDRAMの要部断面図である。

【図4】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図5】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図6】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

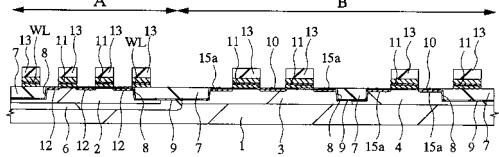

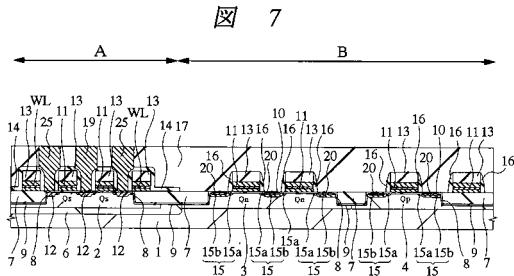

【図7】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

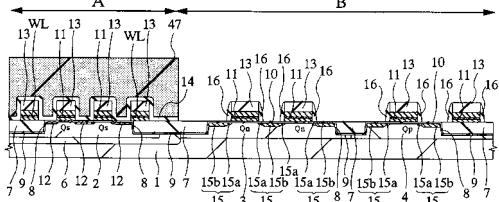

【図8】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図9】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図10】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。 30

【図11】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図12】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図13】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図14】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図15】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図16】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図17】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図18】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図19】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図20】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。 40

【図21】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図22】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図23】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図24】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図25】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図26】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図27】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図28】実施の形態1のDRAMの製造方法の一例を工程順に示した断面図である。

【図29】実施の形態2のDRAMの要部断面図である。

【図30】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。 50

【図31】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図32】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図33】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図34】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図35】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図36】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図37】実施の形態2のDRAMの製造方法の一例を工程順に示した断面図である。

【図38】実施の形態3の半導体集積回路装置を形成した半導体チップ全体の一例を示した平面図である。

【図39】実施の形態3のDRAMの要部断面図である。

10

【符号の説明】

【0166】

1 半導体基板

1A 半導体チップ

2 p形ウェル

3 p形ウェル

4 n形ウェル

6 ディープウェル

7 分離領域

8 浅溝

20

9 シリコン酸化膜

10 ゲート絶縁膜

11 ゲート電極

11a 多結晶シリコン膜

11b 窒化チタン膜

11c タングステン膜

12 不純物半導体領域

13 キャップ絶縁膜

14 シリコン窒化膜

15 不純物半導体領域

30

15a 低濃度不純物領域

15b 高濃度不純物領域

16 サイドウォールスペーサ

17 層間絶縁膜

17d TEOS酸化膜

18 第1層配線

18a 窒化チタン膜

18b タングステン膜

19 プラグ

19b プラグ

40

20 コバルトシリサイド膜

21 接続孔

22 プラグ

22a 窒化チタン膜

22b タングステン膜

23 層間絶縁膜

23b シリコン窒化膜

24 絶縁膜

25 プラグ

26 プラグ

50

|       |           |    |

|-------|-----------|----|

| 2 7   | 下部電極      |    |

| 2 8   | 容量絶縁膜     |    |

| 2 9   | プレート電極    |    |

| 3 0   | 絶縁膜       |    |

| 3 1   | 配線溝       |    |

| 3 2   | 第2層配線     |    |

| 3 2 a | 第1導電層     |    |

| 3 2 b | 第2導電層     |    |

| 3 3   | 接続孔       |    |

| 3 4   | 接続部       | 10 |

| 3 4 a | 第1導電層     |    |

| 3 4 b | 第2導電層     |    |

| 3 5   | シリコン窒化膜   |    |

| 3 6   | 層間絶縁膜     |    |

| 3 7   | 配線溝       |    |

| 3 8   | 接続孔       |    |

| 3 9   | 第3層配線     |    |

| 3 9 a | 第1導電層     |    |

| 3 9 b | 第2導電層     |    |

| 4 0   | 接続部       | 20 |

| 4 0 a | 第1導電層     |    |

| 4 0 b | 第2導電層     |    |

| 4 1   | シリコン窒化膜   |    |

| 4 2   | 層間絶縁膜     |    |

| 4 3   | 第4層配線     |    |

| 4 3 b | 接続部       |    |

| 4 4   | シリコン窒化膜   |    |

| 4 5   | 絶縁膜       |    |

| 4 6   | パッシベーション膜 |    |

| 4 7   | フォトレジスト膜  | 30 |

| 4 8   | 溝         |    |

| 4 9   | 多結晶シリコン膜  |    |

| 5 0   | シリコン酸化膜   |    |

| 5 1   | フォトレジスト膜  |    |

| 5 2   | フォトレジスト膜  |    |

| 5 3   | TEOS酸化膜   |    |

| 5 4   | フォトレジスト膜  |    |

| 5 5   | フォトレジスト膜  |    |

| 5 6   | タンタル膜     |    |

| 5 7   | 銅膜        | 40 |

| 5 8   | タンタル膜     |    |

| 5 9   | 銅膜        |    |

| 6 0   | 第2層配線     |    |

| 6 0 a | 第1導電層     |    |

| 6 0 b | 第2導電層     |    |

| 6 1   | 接続部       |    |

| 6 1 a | 第1導電層     |    |

| 6 1 b | 第2導電層     |    |

| 6 2   | 層間絶縁膜     |    |

| 6 3   | 接続孔       | 50 |

|         |                |    |

|---------|----------------|----|

| 6 4     | プラグ            |    |

| 6 4 a   | 窒化チタン膜         |    |

| 6 4 b   | タンゲステン膜        |    |

| 6 5     | 第3層配線          |    |

| 6 5 a   | 窒化チタン膜         |    |

| 6 5 b   | アルミニウム膜        |    |

| 6 5 c   | 窒化チタン膜         |    |

| 6 6     | 層間絶縁膜          |    |

| 6 7     | 第4層配線          |    |

| 6 7 a   | 窒化チタン膜         | 10 |

| 6 7 b   | アルミニウム膜        |    |

| 6 7 c   | 窒化チタン膜         |    |

| 6 8     | 絶縁膜            |    |

| 6 9     | 窒化チタン膜         |    |

| 7 0     | アルミニウム膜        |    |

| 7 1     | 窒化チタン膜         |    |

| 7 2     | タンゲステン         |    |

| 2 0 1   | ロジック部          |    |

| 2 0 2   | メモリ部           |    |

| 2 0 3   | 第1のI/O部        | 20 |

| 2 0 4   | 第2のI/O部        |    |

| 2 0 5   | バス             |    |

| 2 0 6   | デコーダ部          |    |

| B L     | ビット線           |    |

| C       | キャパシタ          |    |

| M A R Y | メモリアレイ         |    |

| M W B   | メインワード線        |    |

| Q n     | nチャネルMISFET    |    |

| Q n 2   | nチャネルMISFET    |    |

| Q p     | pチャネルMISFET    | 30 |

| Q s     | メモリセル選択用MISFET |    |

| S A     | センスアンプ         |    |

| S W D   | サブワードデコーダ      |    |

| W D     | ワードドライバ        |    |

| W L     | ワード線           |    |

| Y S     | Yセレクト線         |    |

【 図 1 】

図 1

【 図 2 】

图 2

【図3】

图 3

18: 第1層配線 32: 第2層配線

24: 絶縁膜 33: 接続孔

30: 絶縁膜 34: 接続部

31: 配線溝 C: キャバシタ

【 図 4 】

4

〔 図 5 〕

図 5

〔 図 6 〕

図 6

【図7】

【図14】

図 14

【 図 1 5 】

図 15

【図16】

四 16

【 図 17 】

図 17

【 図 1 8 】

図 18

【 図 1 9 】

四 19

【 図 2 0 】

図 20

【 図 2 1 】

図 21

【 図 2 2 】

図 22

【 図 2 3 】

図 23

【 図 2 4 】

図 24

【 図 25 】

図 25

【図26】

图 26

【 図 27 】

図 27

【 図 2 8 】

図 28

【 図 29 】

图 29

【図30】

图 30

### 【 図 3 1 】

四 31

【図32】

图 32

### 【図33】

図 33

### 【図3-4】

图 34

【 図 3 5 】

図 35

【図36】

図 36

【図37】

図 37

【 図 3 8 】

【図39】

图 38

5.

---

フロントページの続き

審査官 北島 健次

(56)参考文献 国際公開第97/019468 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

H01L 21/3205

H01L 21/768

H01L 27/10

H01L 27/108