República Federativa do Brasil

Ministério do Desenvolvimento, Indústria,

Comércio e Serviços

Instituto Nacional da Propriedade Industrial

**(11) BR 112018014012-0 B1**

**(22) Data do Depósito:** 02/12/2016

**(45) Data de Concessão:** 07/11/2023

**(54) Título:** SISTEMAS E MÉTODOS PARA RENDERIZAR MÚLTIPLOS NÍVEIS DE DETALHE E MEMÓRIA LEGÍVEL POR COMPUTADOR

**(51) Int.Cl.:** G06T 11/40; G06T 15/00; G06T 15/50; G06T 17/20; G06T 3/00; (...).

**(52) CPC:** G06T 11/40; G06T 15/005; G06T 15/503; G06T 17/20; G06T 3/0012; (...).

**(30) Prioridade Unionista:** 12/01/2016 US 14/993,760.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** PHI HUNG NGUYEN; NING BI.

**(86) Pedido PCT:** PCT US2016064769 de 02/12/2016

**(87) Publicação PCT:** WO 2017/123341 de 20/07/2017

**(85) Data do Início da Fase Nacional:** 10/07/2018

**(57) Resumo:** Um aparelho eletrônico é descrito. O dispositivo eletrônico inclui um processador. O processador é configurado para renderizar uma primeira zona de uma imagem. O processador também é configurado para renderizar uma segunda zona da imagem. A primeira zona tem um nível tecelado mais elevado de detalhe do que a segunda zona. O processador é adicionalmente configurado para apresentar a primeira zona e a segunda zona em pelo menos uma janela de veículo.

“SISTEMAS E MÉTODOS PARA RENDERIZAR MÚLTIPLOS NÍVEIS DE DETALHE E MEMÓRIA LEGÍVEL POR COMPUTADOR”

CAMPO DE DIVULGAÇÃO

[0001] A presente invenção refere-se genericamente a dispositivos eletrônicos. Mais especificamente, a presente divulgação refere-se a sistemas e métodos para renderizar múltiplos níveis de detalhe.

FUNDAMENTOS

[0002] Alguns dispositivos eletrônicos (por exemplo, smartphones, computadores, televisores, automóveis, sistemas de videogame, reprodutores de mídia, câmeras, telefones celulares, câmeras pessoais, set-top boxes, projetores, displays, etc.) exibem imagens. Por exemplo, um smartphone pode capturar e/ou processar imagens estáticas e/ou de vídeo. Processamento de imagens pode exigir uma quantidade relativamente grande de recursos de tempo, memória e energia. Os recursos exigidos podem variar de acordo com a complexidade do processamento.

[0003] o processamento de grandes quantidades de dados de imagem pode ser particularmente difícil. Por exemplo, grandes quantidades de dados de imagem podem exigir quantidades relativamente grandes de recursos, como a energia, tempo, largura de banda do processador, memória e/ou custos monetários. Como pode ser observado a partir desta discussão, sistemas e métodos que melhoram o processamento de imagem podem ser benéficos.

SUMÁRIO

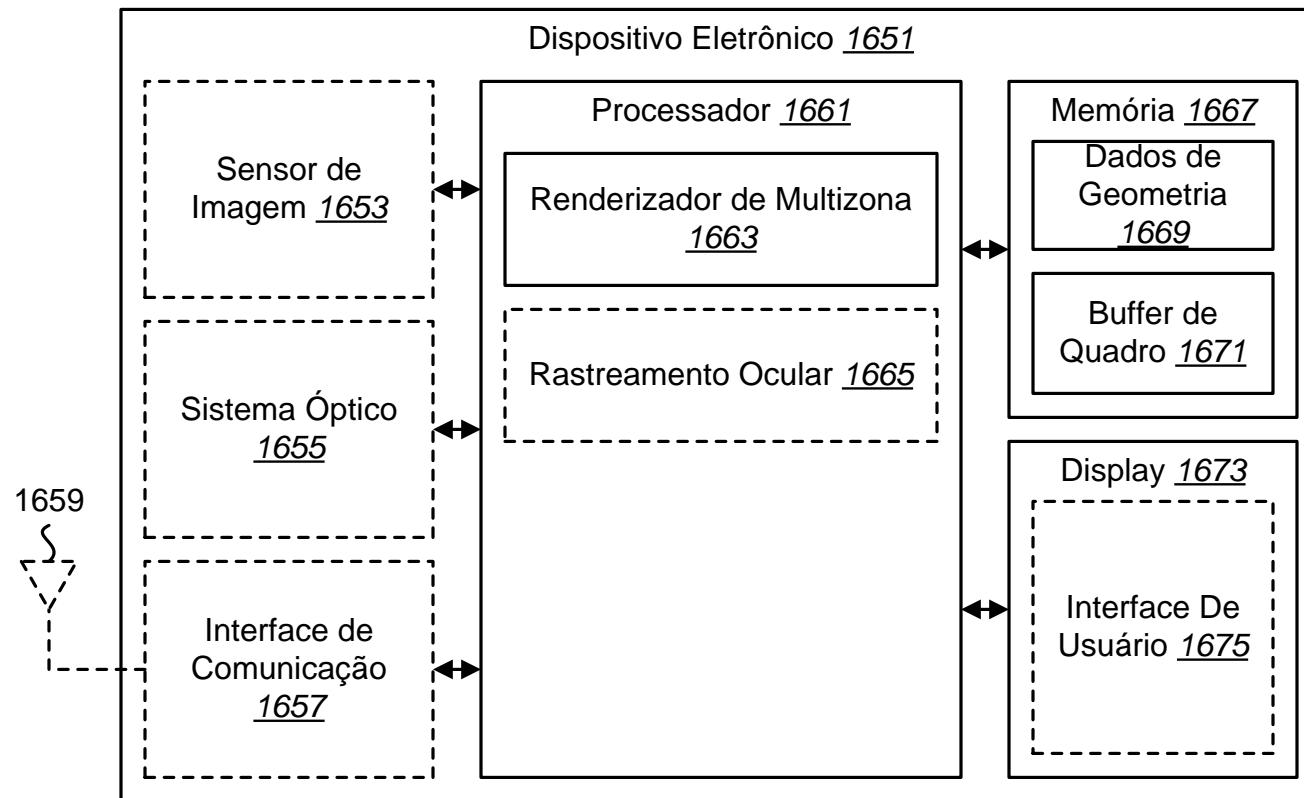

[0004] Um dispositivo eletrônico é descrito. O dispositivo eletrônico inclui um processador configurado para renderizar uma primeira zona de uma imagem. O

processador também é configurado para renderizar uma segunda zona da imagem. A primeira zona tem um nível tecelado mais elevado de detalhe do que a segunda zona. O processador é adicionalmente configurado para apresentar a primeira zona e a segunda zona em pelo menos uma janela de veículo. O dispositivo eletrônico pode ser pelo menos parte de um módulo removível em um veículo.

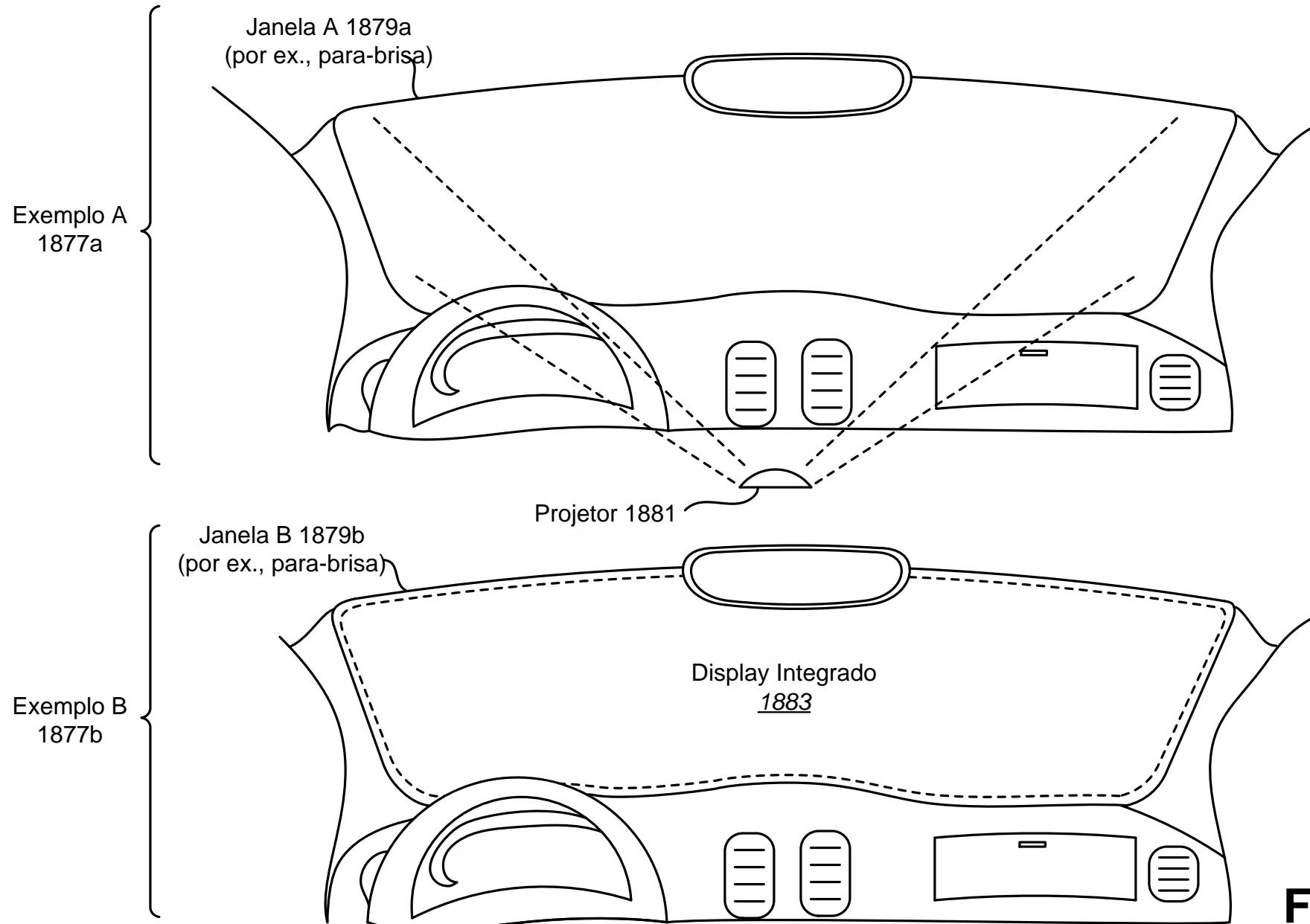

[0005] O dispositivo eletrônico pode incluir pelo menos um display. O processador pode ser configurado para enviar a primeira zona e a segunda zona para o pelo menos um display para apresentar a primeira zona e a segunda zona. O pelo menos um display pode ser um projetor de janela ou de um painel de exibição de janela integrada.

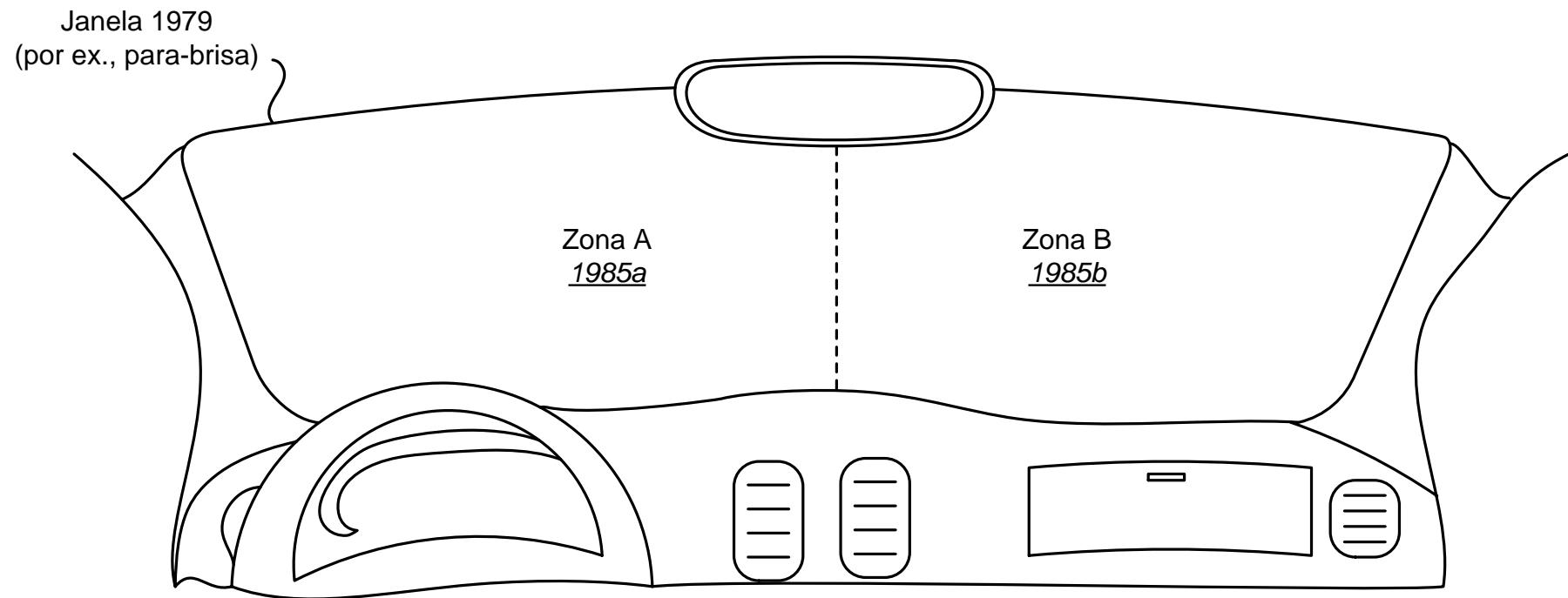

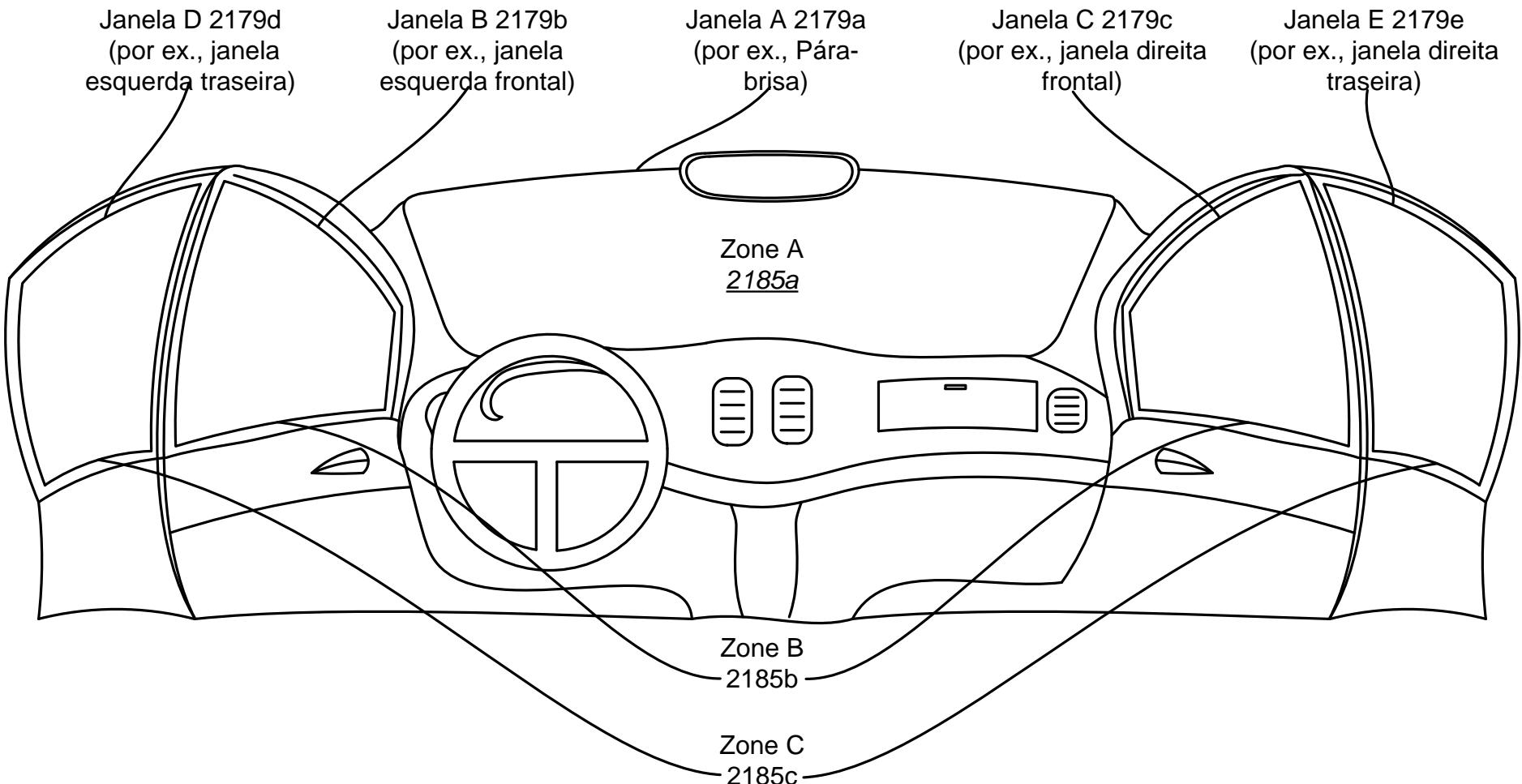

[0006] O processador pode ser configurado para apresentar a primeira zona em uma primeira janela e para apresentar a segunda zona em uma segunda janela. A primeira janela pode ser um para-brisa frontal e a segunda janela pode ser uma outra janela de um veículo.

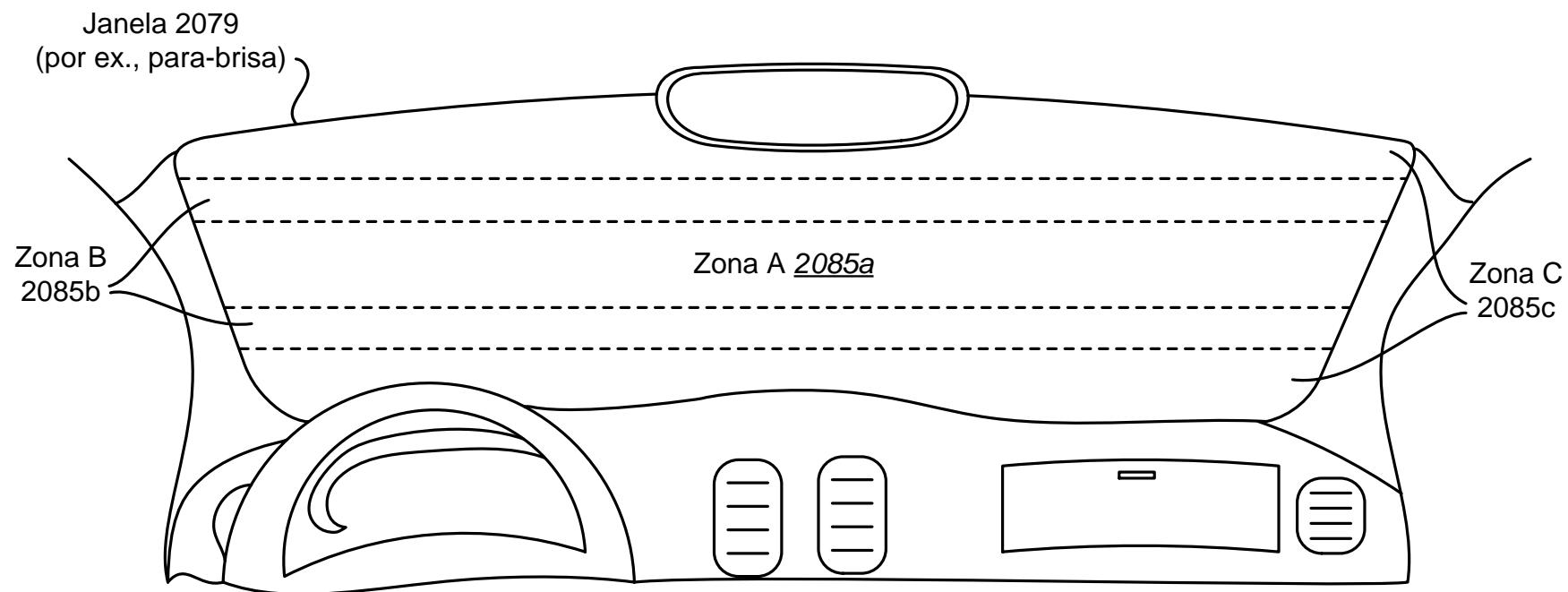

[0007] O processador pode ser configurado para apresentar a primeira zona em uma primeira seção de uma janela e pode ser configurado para apresentar a segunda zona em uma segunda seção da janela. A primeira seção pode ter uma seção lateral de um para-brisa e a segunda seção pode ser uma outra seção lateral do para-brisa. A primeira seção pode ser uma primeira barra horizontal através de um para-brisa e a segunda seção pode ser uma segunda barra horizontal através do para-brisa.

[0008] O processador pode ser configurado para realizar o rastreamento ocular (eye tracking). O processador pode também ser configurado para renderizar a primeira zona

e a segunda zona baseado em um rastreamento ocular. O processador pode ser configurado para executar rastreamento ocular por múltiplos usuários. O processador pode priorizar renderização de zona baseado no rastreamento ocular.

[0009] O processador pode ser configurado para renderizar uma terceira zona. A terceira zona pode ter um nível de detalhe tecelado inferior do que a primeira zona e a segunda zona. O processador pode ser configurado para apresentar a terceira zona na pelo menos uma janela do veículo.

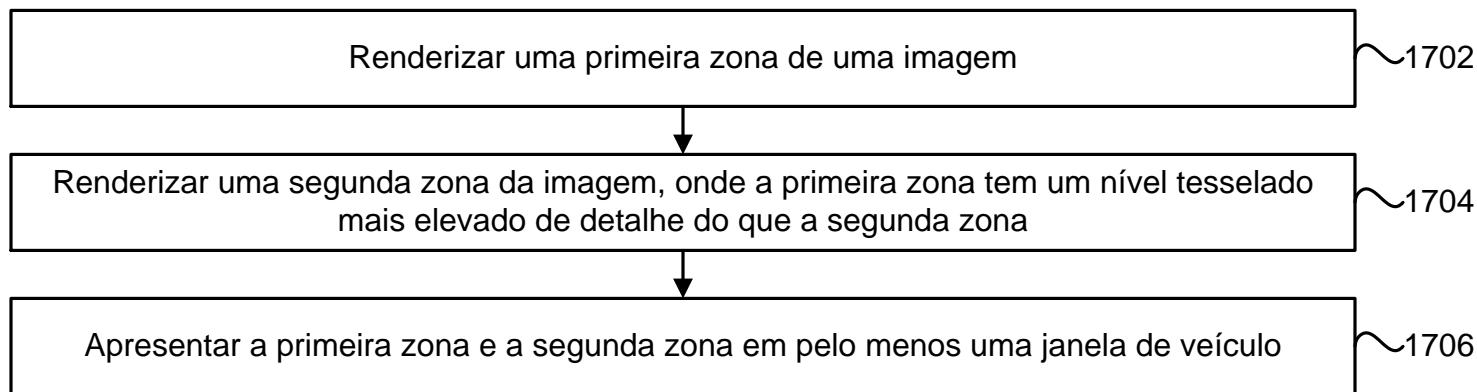

[0010] Um método realizado por um dispositivo eletrônico também é descrito. O método inclui a renderizar uma primeira zona de uma imagem. O método também inclui renderizar uma segunda zona da imagem. A primeira zona tem um nível tecelado mais elevado de detalhe do que a segunda zona. O método inclui ainda apresentar a primeira zona e a segunda zona em pelo menos uma janela de veículo.

[0011] Um produto de programa de computador é também descrito. O produto de programa de computador inclui um meio legível por computador tangível não transitório com instruções. As instruções incluem código para fazer com que um dispositivo eletrônico renderize uma primeira zona de uma imagem. As instruções incluem também código para fazer com que o dispositivo eletrônico renderize uma segunda zona da imagem. A primeira zona tem um nível tecelado mais elevado de detalhe do que a segunda zona. As instruções incluem ainda código para fazer com que o dispositivo eletrônico apresente a primeira zona e a segunda zona em pelo menos uma janela de veículo.

[0012] Um aparelho também é descrito. O aparelho inclui meios para renderizar uma primeira zona de uma imagem. O aparelho também inclui meios para renderizar uma segunda zona da imagem. A primeira zona tem um nível tecelado mais elevado de detalhe do que a segunda zona. O aparelho inclui ainda meios para apresentar a primeira zona e a segunda zona em pelo menos uma janela de veículo.

#### BREVE DESCRIÇÃO DOS DESENHOS

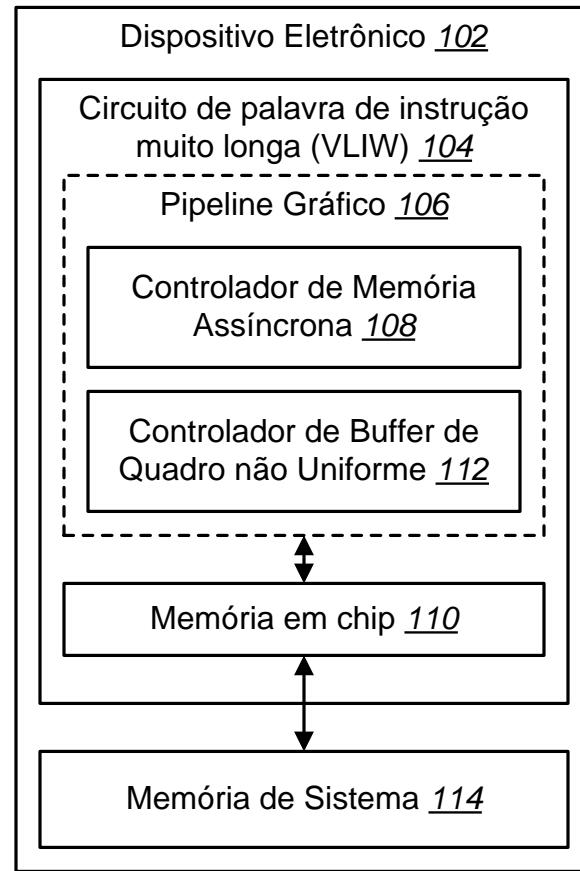

[0013] A Figura 1 é um diagrama de blocos que ilustra uma configuração de um dispositivo eletrônico, em que os sistemas e métodos para renderizar múltiplos níveis de detalhe podem ser implementados;

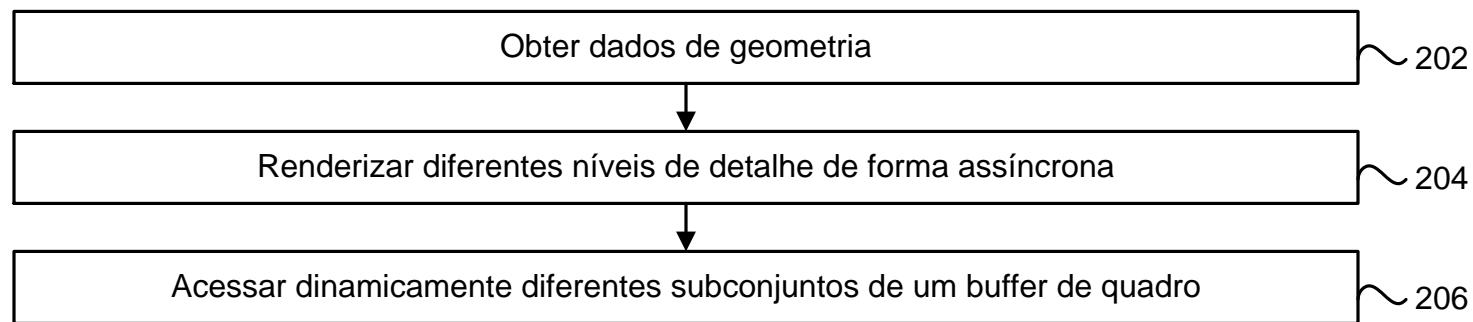

[0014] A Figura 2 é um diagrama de fluxo que ilustra uma configuração de um método para produzir múltiplos níveis de detalhe;

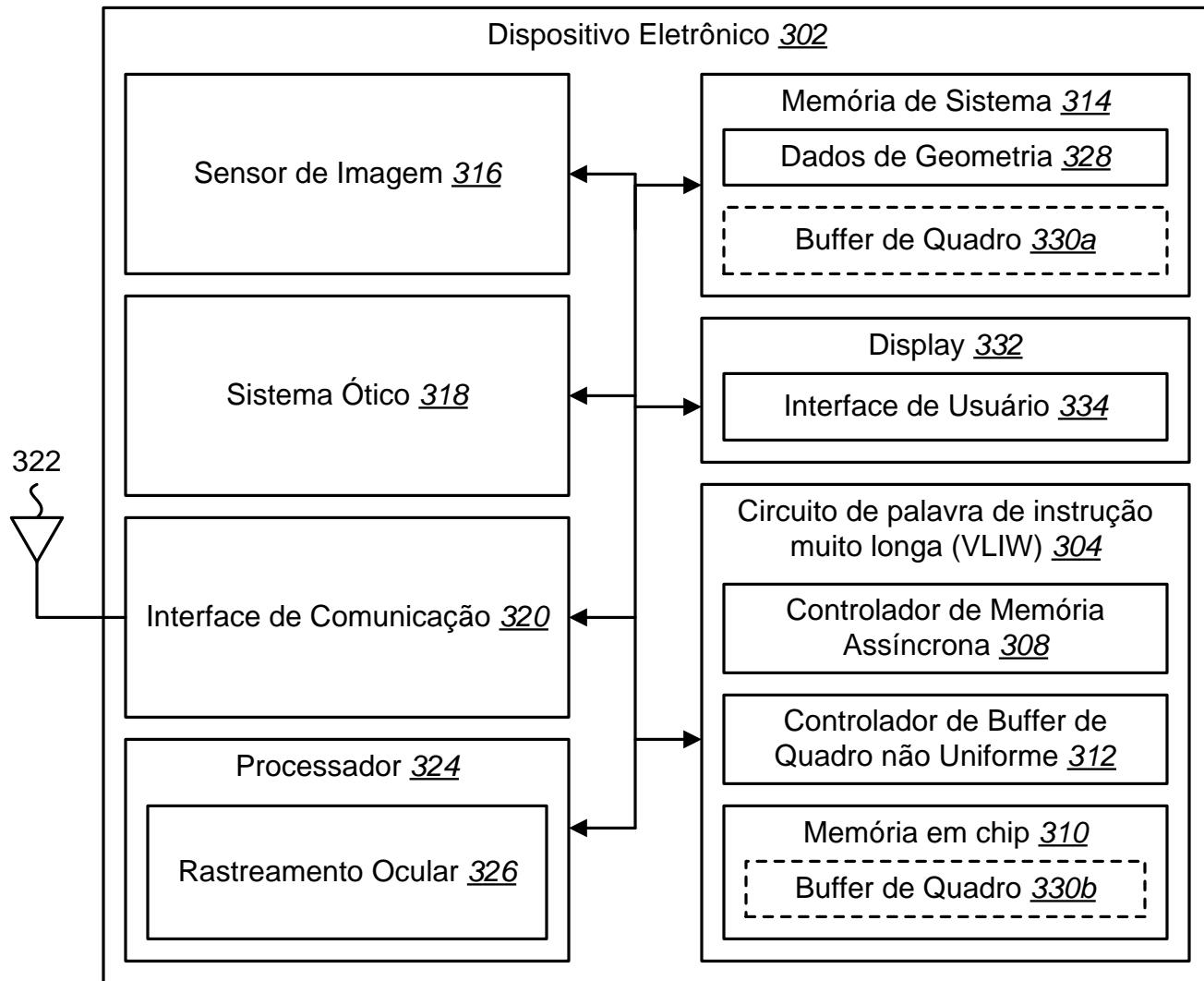

[0015] A Figura 3 é um diagrama de blocos que ilustra uma configuração de um dispositivo eletrônico, em que os sistemas e métodos para renderizar múltiplos níveis de detalhe podem ser implementados;

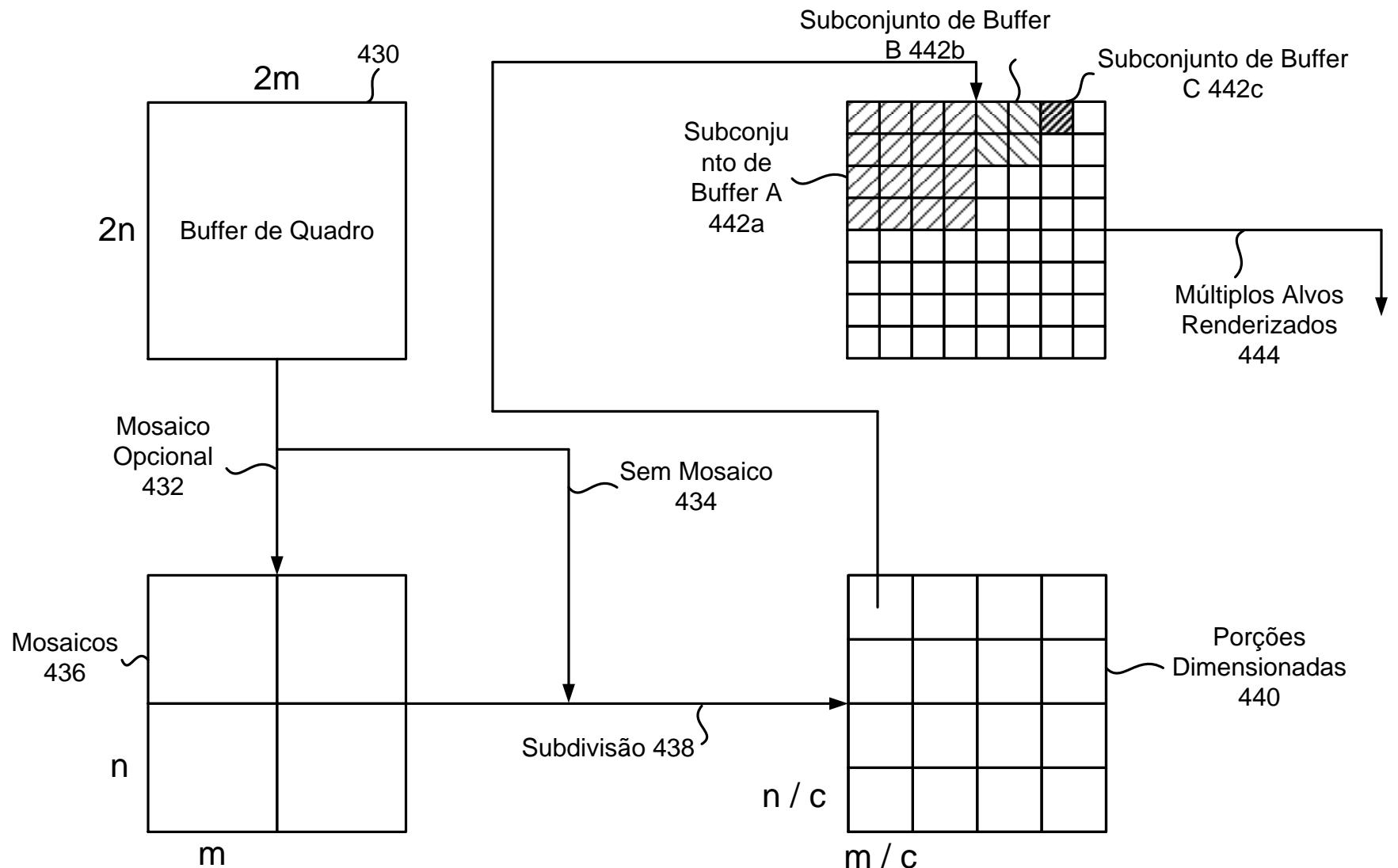

[0016] A Figura 4 é um diagrama que ilustra um exemplo de um buffer (armazenador temporário) de quadro não uniforme;

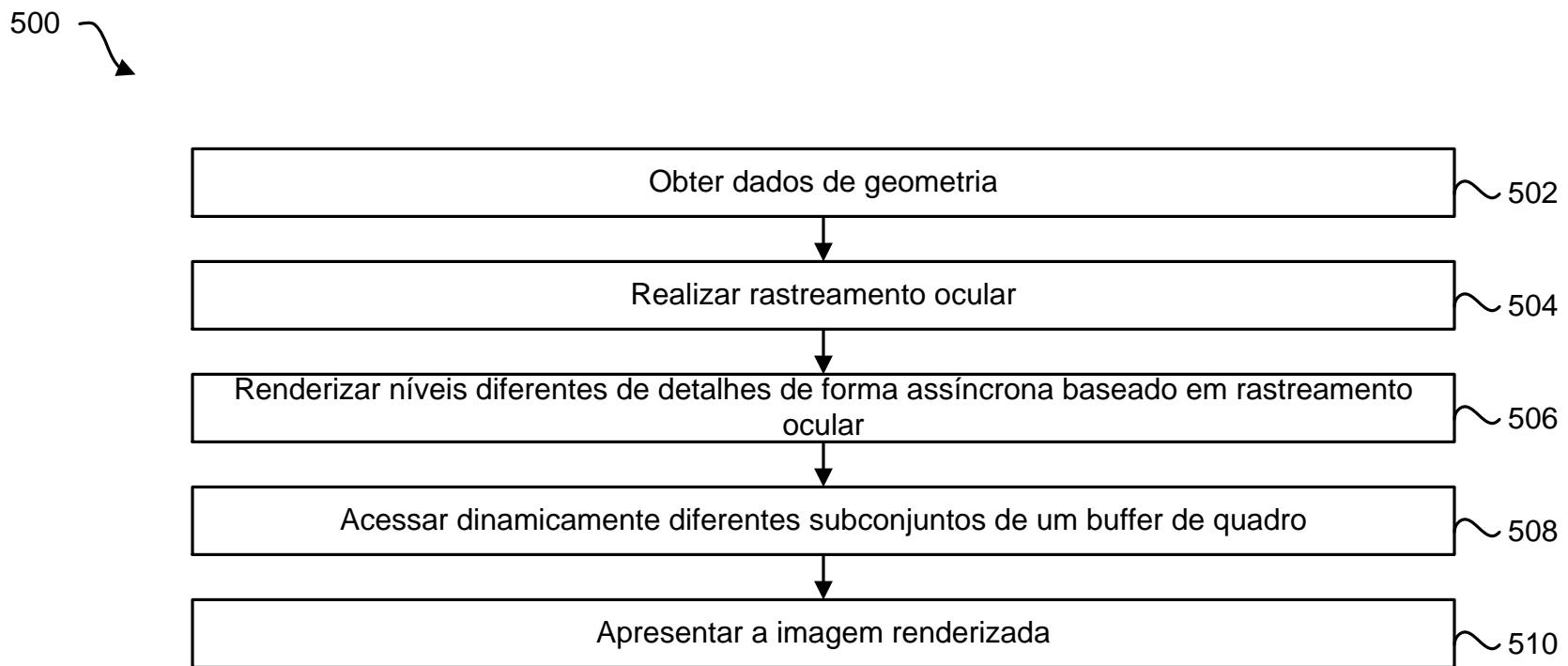

[0017] A Figura 5 é um diagrama de fluxo que ilustra uma configuração mais específica de um método para produzir múltiplos níveis de detalhe;

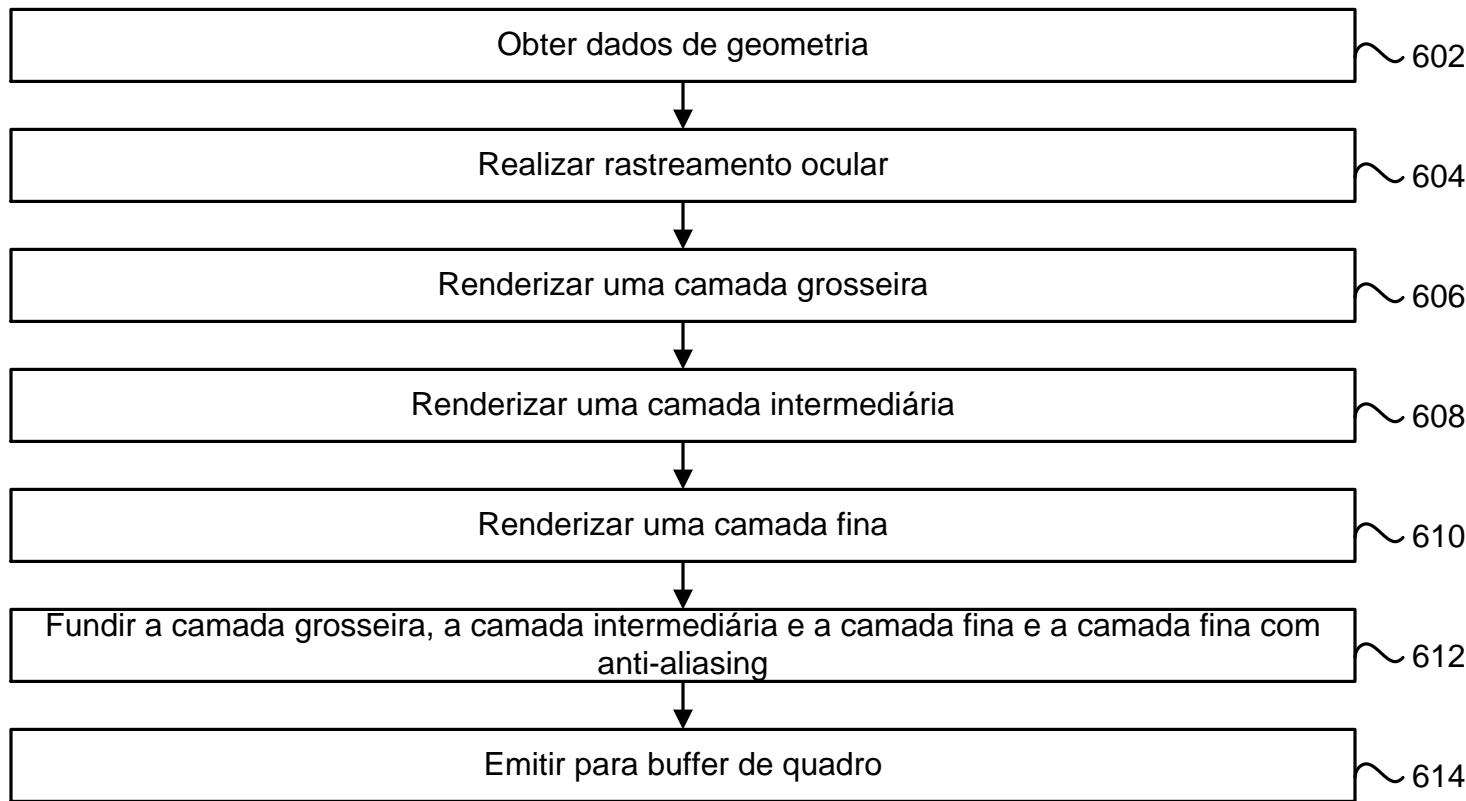

[0018] A Figura 6 é um diagrama de fluxo que ilustra exemplo de um método para renderização foveada;

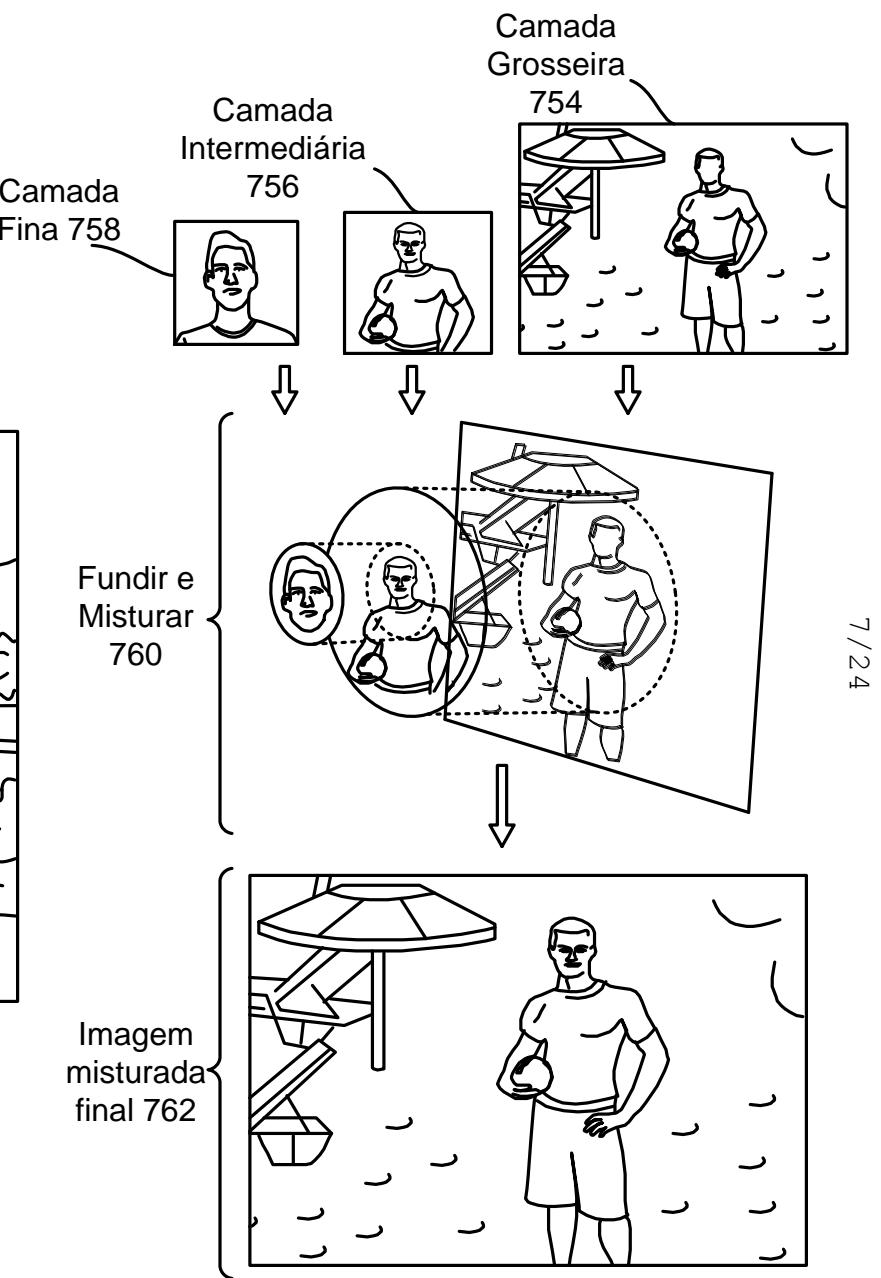

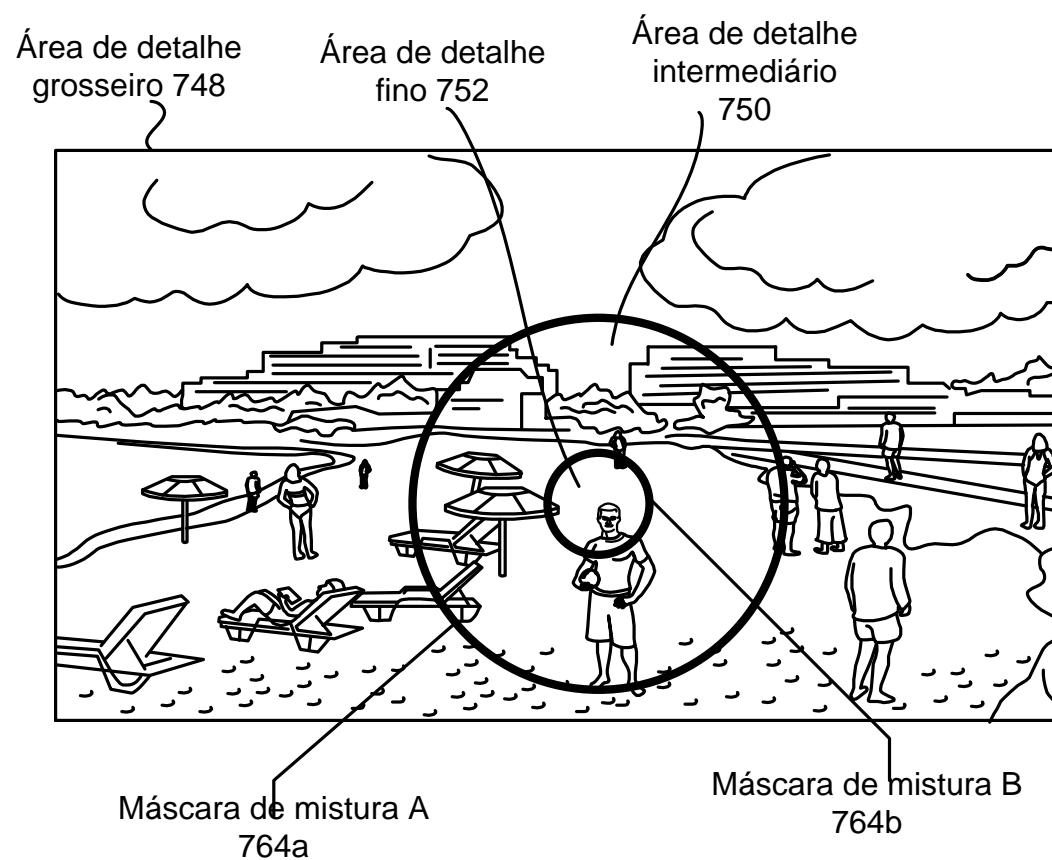

[0019] A Figura 7 ilustra um exemplo de renderização foveada;

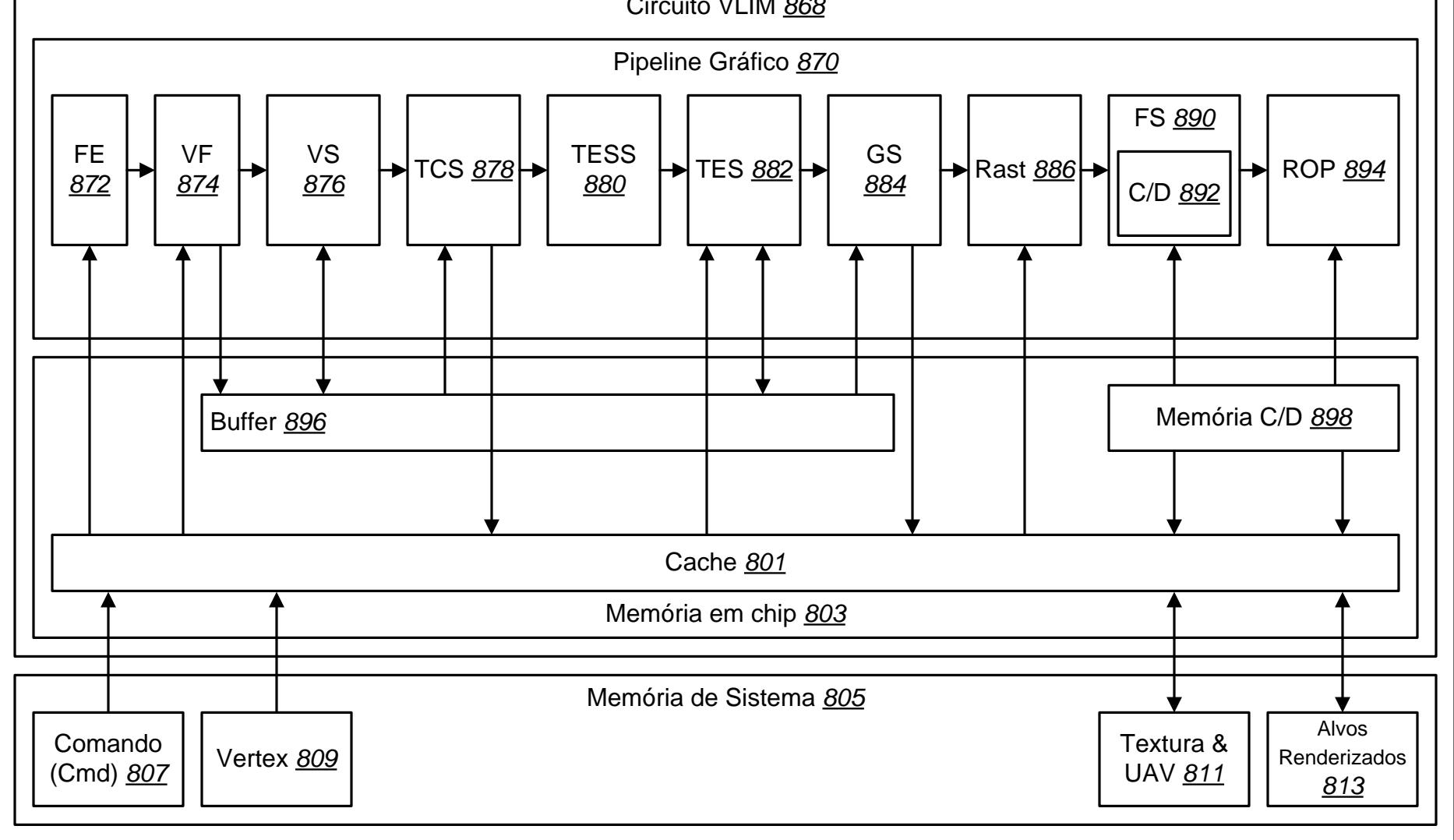

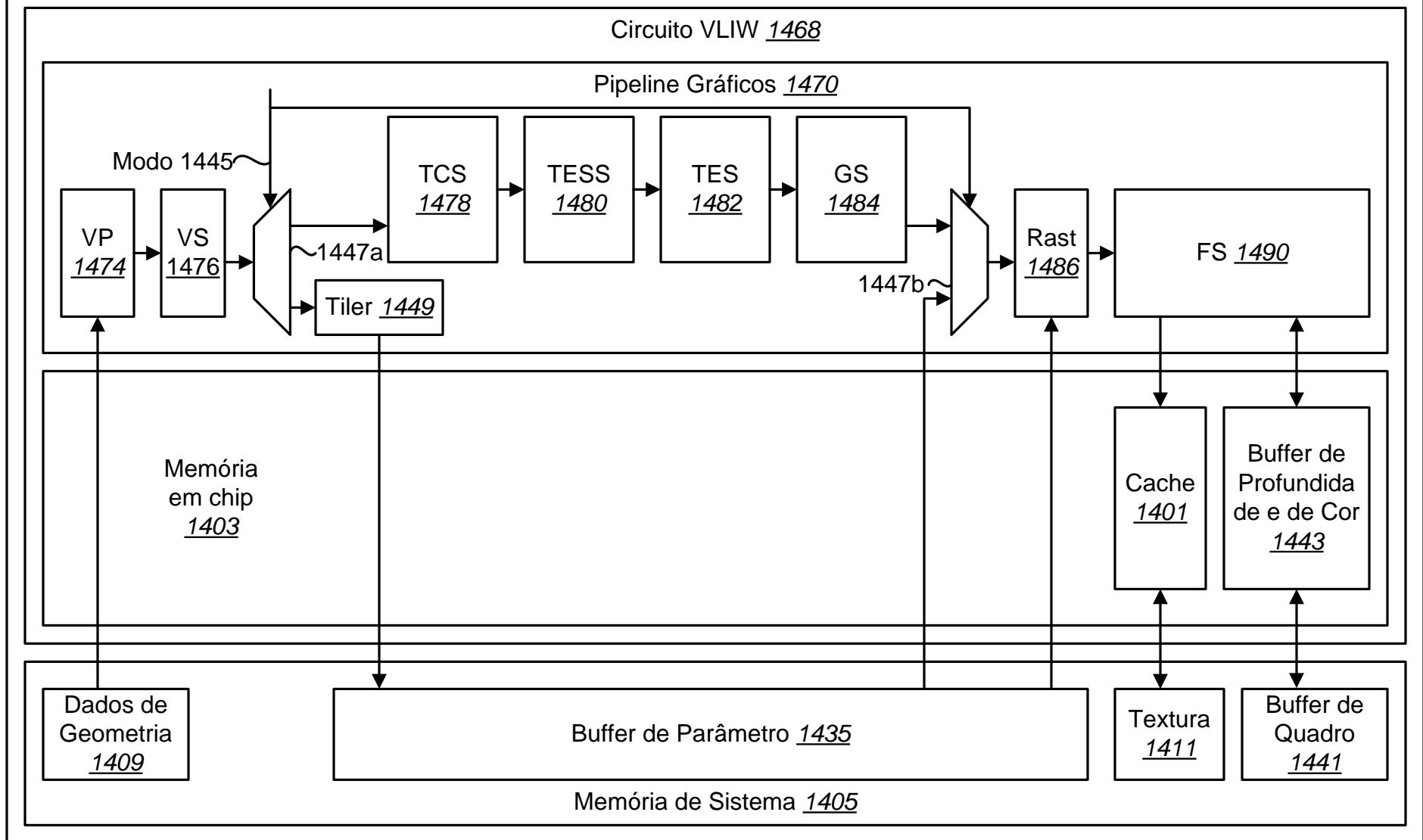

[0020] A Figura 8 é um diagrama de blocos que ilustra um exemplo de um dispositivo eletrônico incluindo um circuito de palavra de instrução muita longa (VLIW);

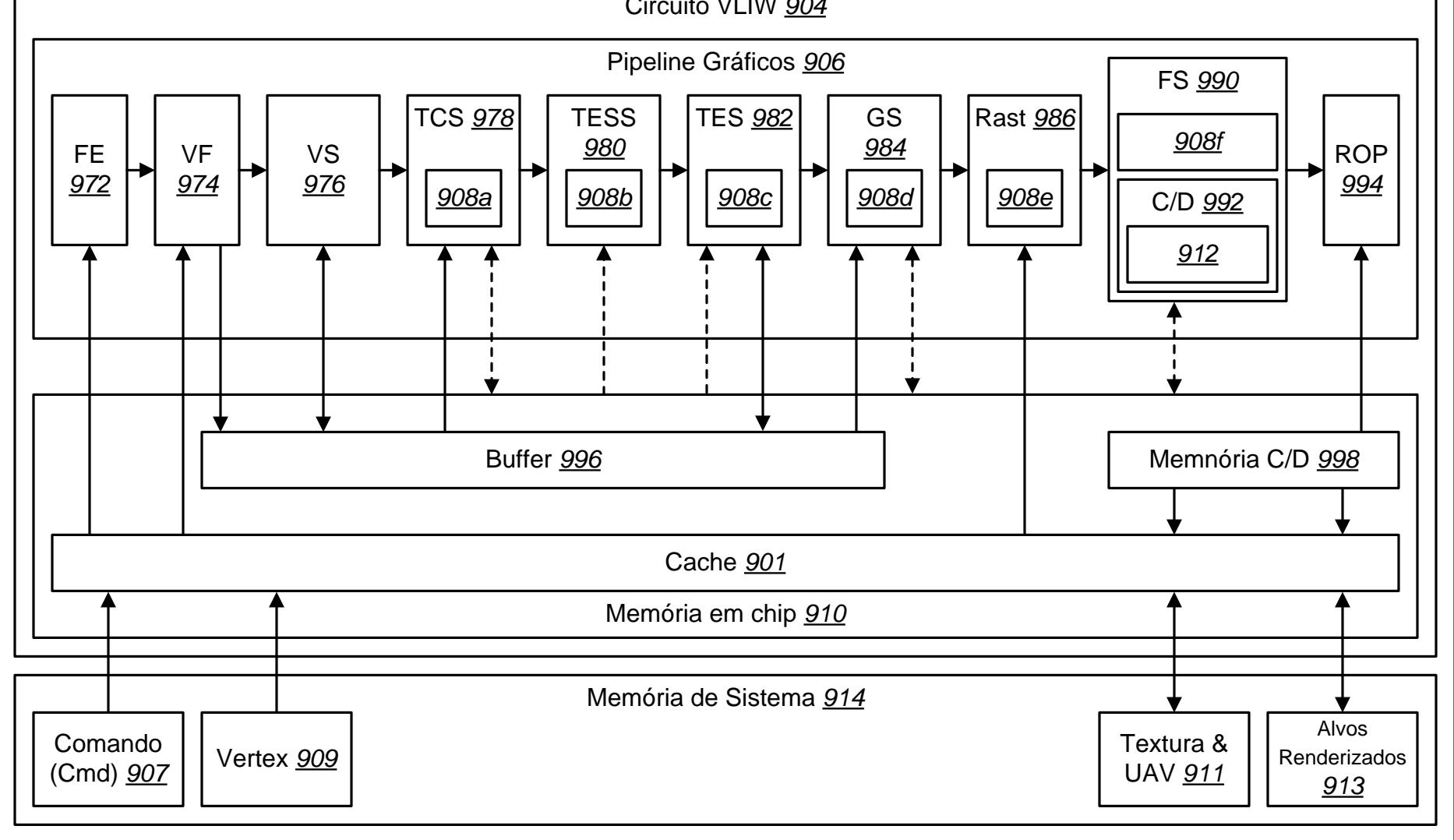

[0021] A Figura 9 é um diagrama de blocos que ilustra um exemplo dos sistemas e processos divulgados aqui implementados na arquitetura descrita em ligação com a Figura 8;

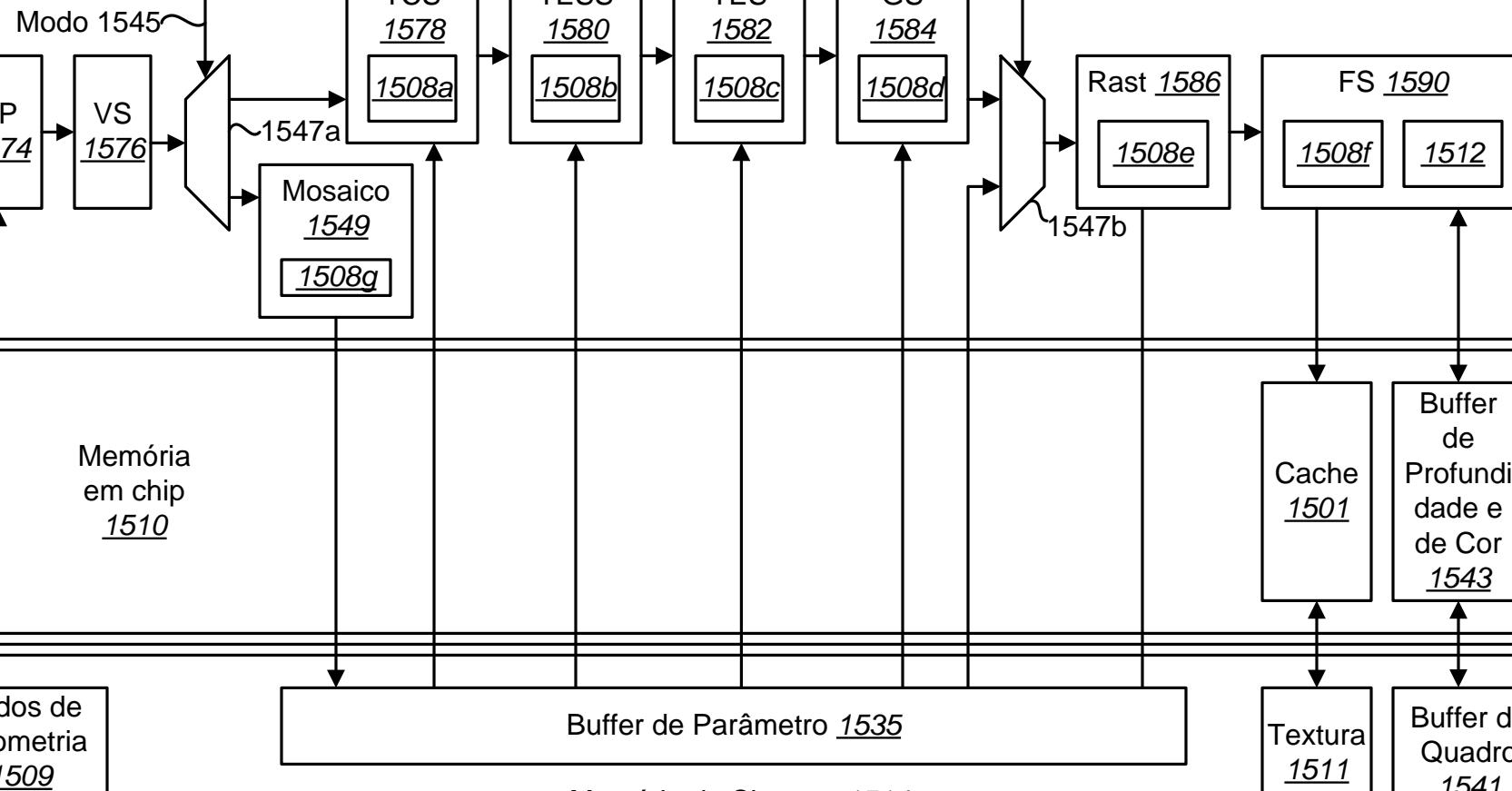

[0022] A Figura 10 é um diagrama de blocos que ilustra um outro exemplo de um dispositivo eletrônico incluindo um circuito de palavra de instrução muita longa (VLIW);

[0023] A Figura 11 é um diagrama de blocos que ilustra um outro exemplo dos sistemas e processos divulgados aqui implementados na arquitetura descrita em ligação com a Figura 10;

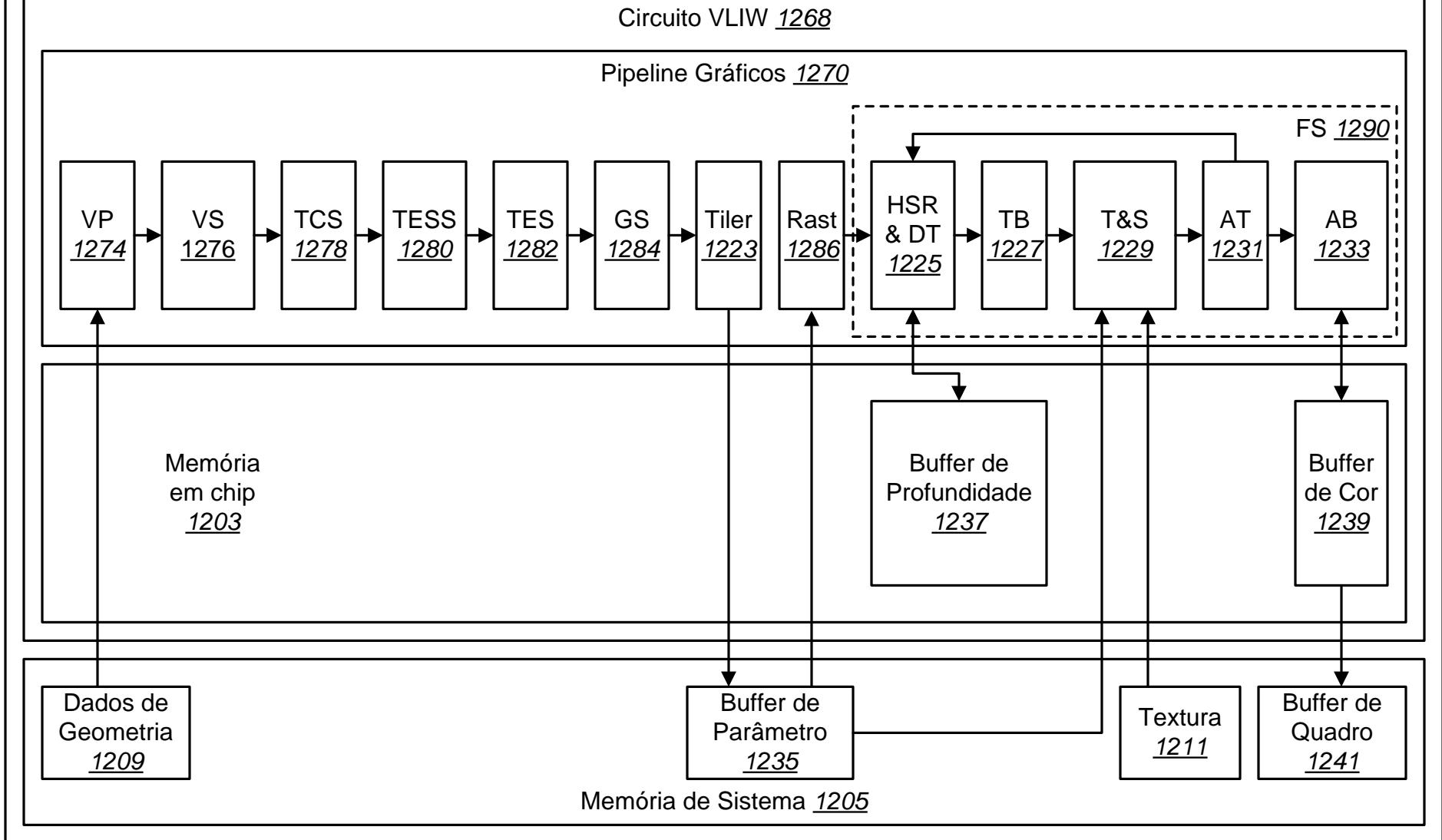

[0024] A Figura 12 é um diagrama de blocos que ilustra um outro exemplo de um dispositivo eletrônico incluindo um circuito de palavra de instrução muita longa (VLIW);

[0025] A Figura 13 é um diagrama de blocos que ilustra um exemplo dos sistemas e processos divulgados aqui implementados na arquitetura descrita em ligação com a Figura 12;

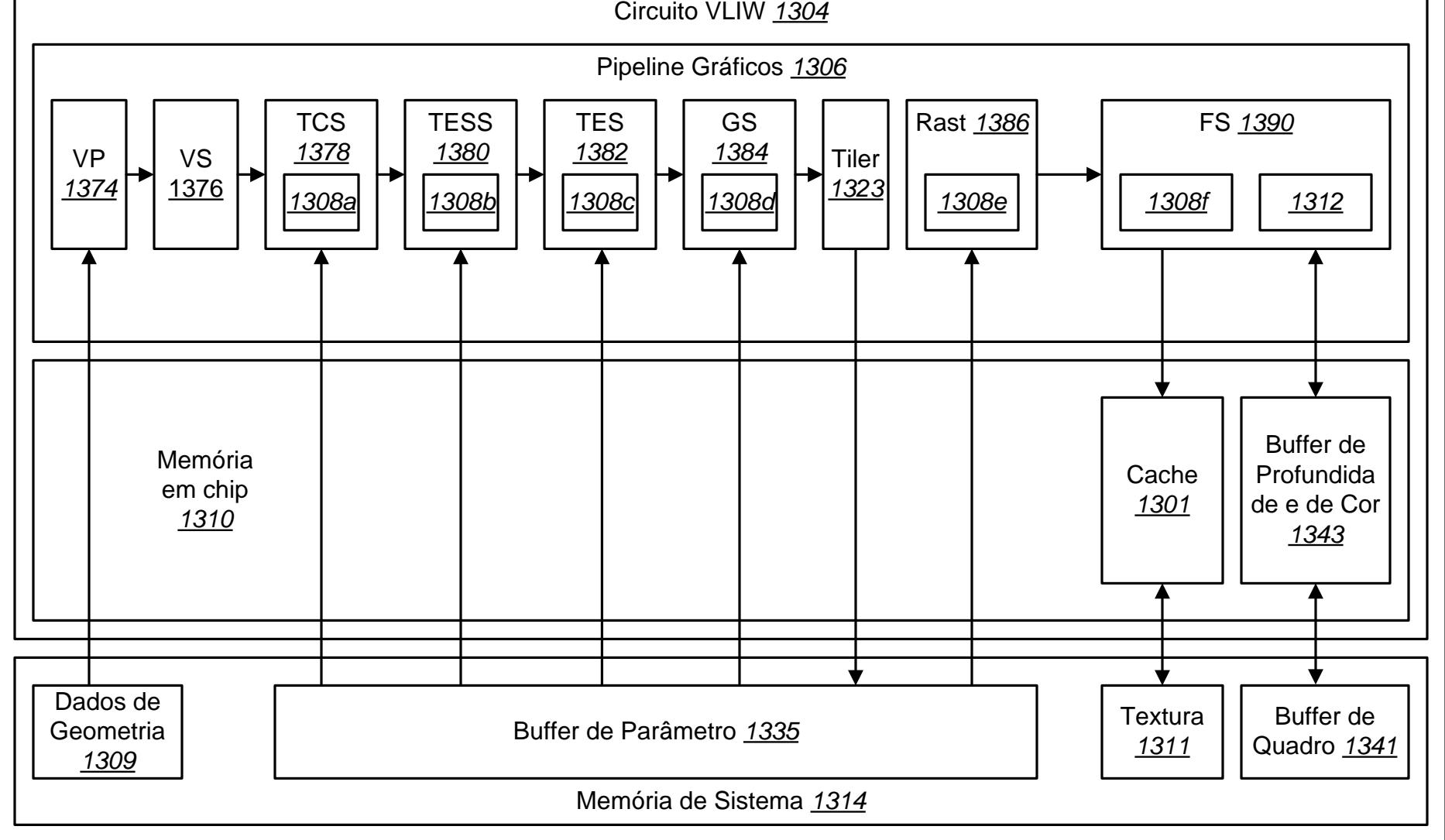

[0026] A Figura 14 é um diagrama de blocos que ilustra um outro exemplo de um dispositivo eletrônico incluindo um circuito de palavra de instrução muita longa (VLIW);

[0027] A Figura 15 é um diagrama de blocos que ilustra um exemplo dos sistemas e processos divulgados aqui

implementados na arquitetura descrita em ligação com a Figura 14;

[0028] A Figura 16 é um diagrama de blocos que ilustra uma configuração de um dispositivo eletrônico, em que os sistemas e métodos para renderizar várias zonas podem ser implementados;

[0029] A Figura 17 é um diagrama de fluxo que ilustra um método para renderizar várias zonas;

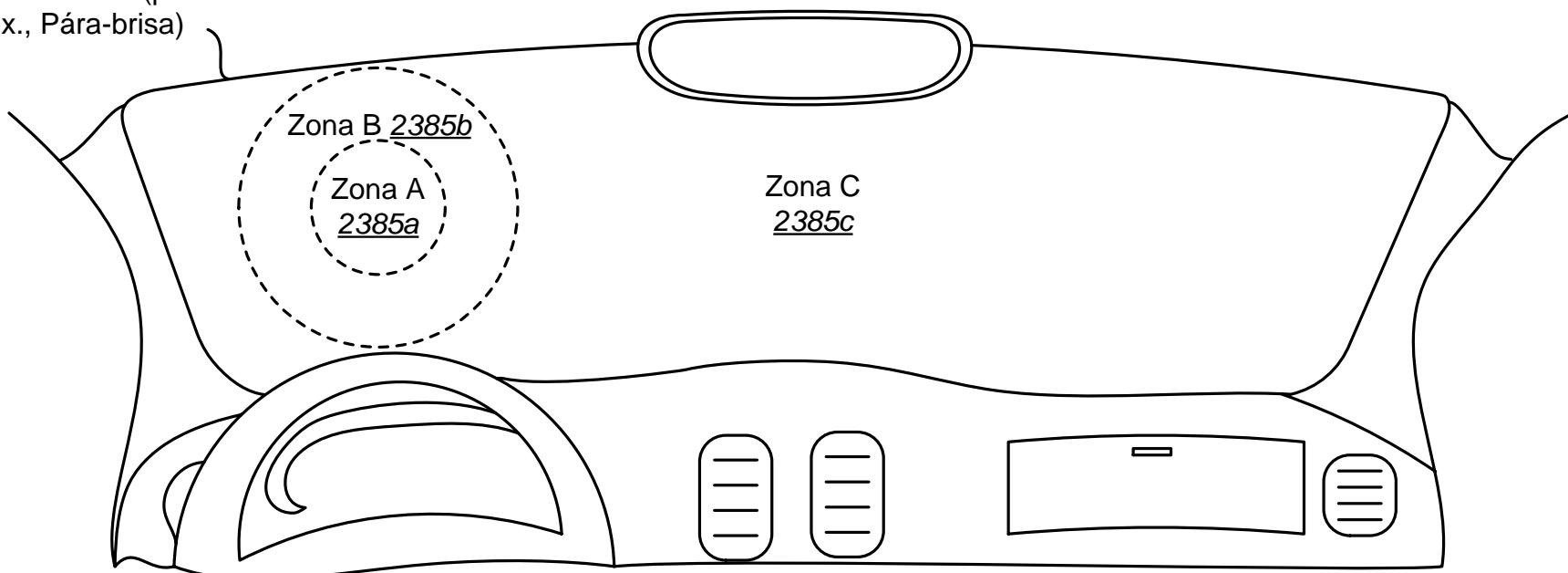

[0030] A Figura 18 é um diagrama que ilustra alguns exemplos de displays de janelas;

[0031] A Figura 19 é um diagrama que ilustra um exemplo de zonas sobre uma janela;

[0032] A Figura 20 é um diagrama que ilustra um outro exemplo de zonas sobre uma janela;

[0033] A Figura 21 é um diagrama que ilustra um outro exemplo de zonas sobre múltiplas janelas;

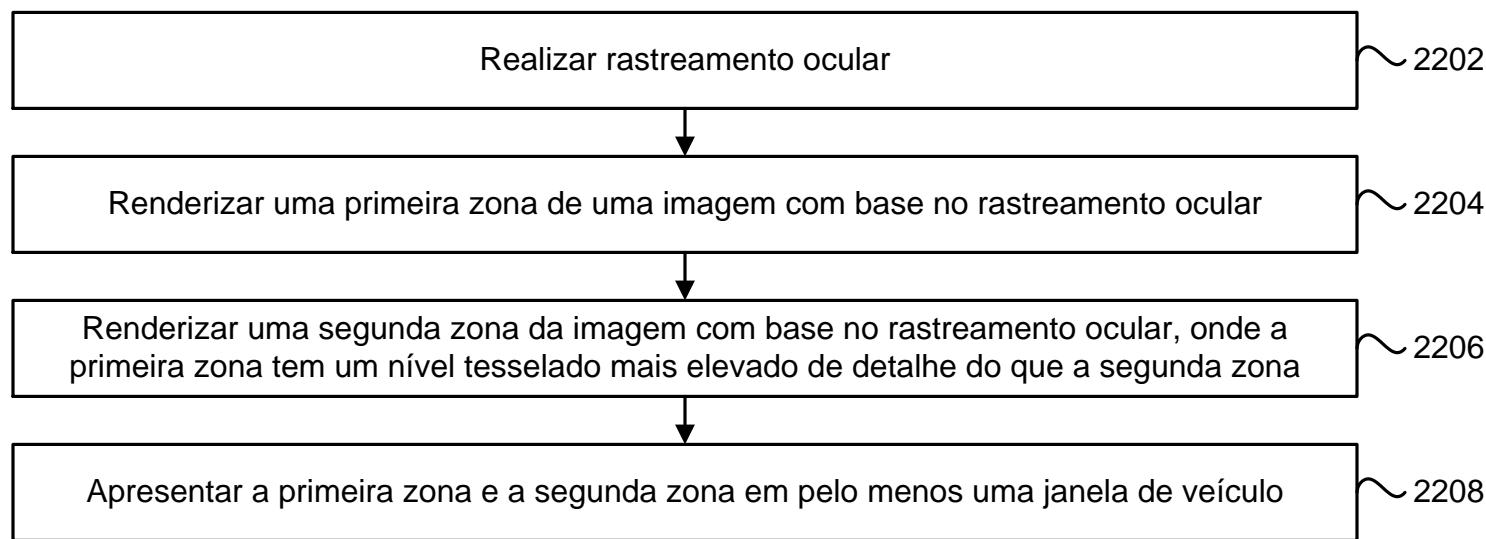

[0034] A Figura 22 é um diagrama de fluxo que ilustra uma configuração mais específica de um método para processamento de múltiplas zonas;

[0035] A Figura 23 é um diagrama que ilustra um outro exemplo de zonas sobre uma janela; e

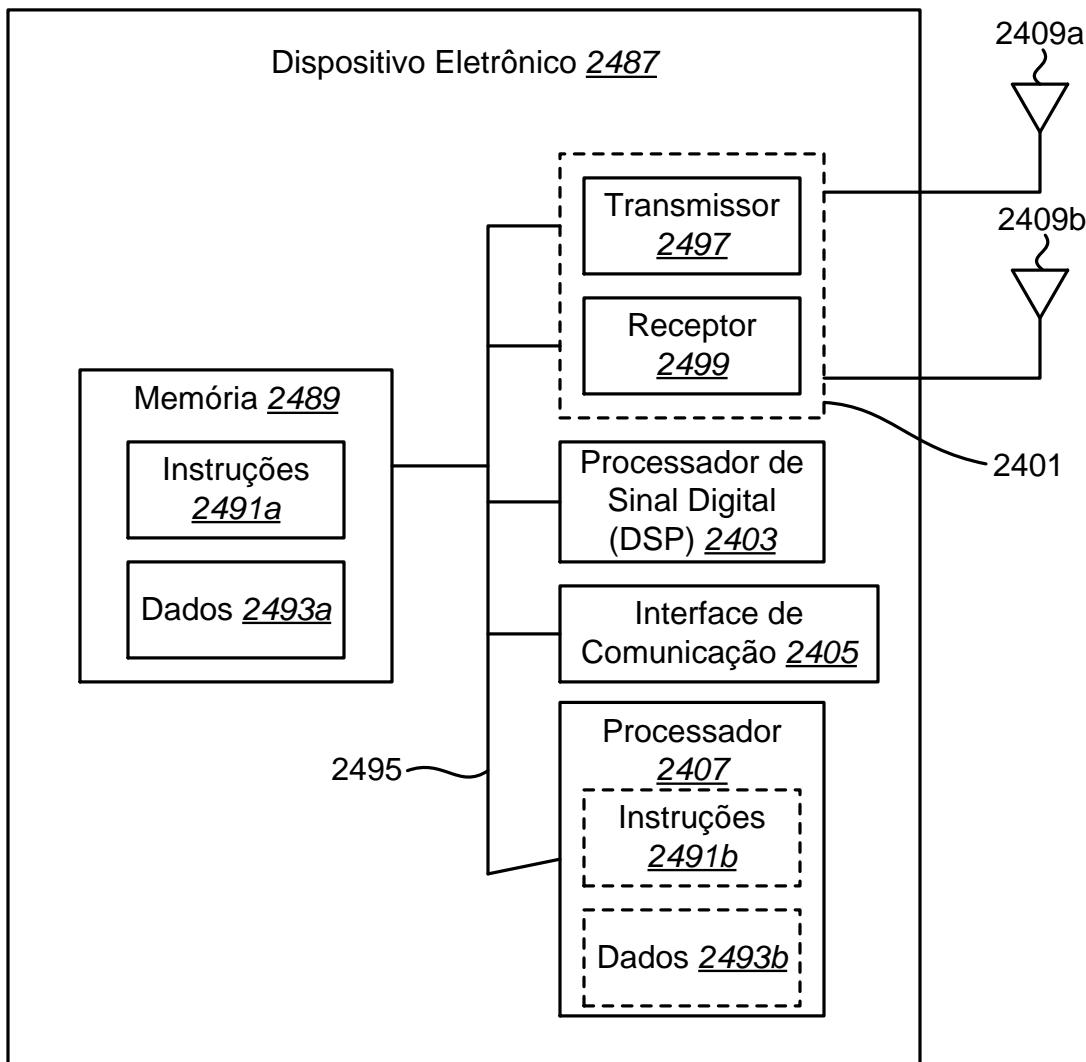

[0036] A Figura 24 ilustra certos componentes que podem ser incluídos dentro de um dispositivo eletrônico.

#### DESCRIÇÃO DETALHADA

[0037] Os sistemas e métodos aqui descritos podem prover abordagens para renderizar múltiplos níveis de detalhe. Por exemplo, múltiplos diferentes níveis de detalhe podem ser renderizados na mesma imagem. Isso pode melhorar a eficiência de renderização e/ou experiência do usuário. Tal como aqui utilizado, o termo "renderizar" e as suas

variações podem significar realizar uma ou mais operações para a produção de dados de imagem. Por exemplo, renderização pode incluir a realização de uma ou mais operações para converter dados geométricos (por exemplo, modelos geométricos, vértices, polígonos, etc.) para os dados de imagem (por exemplo, dados de pixel, pixels, dados de domínio visuais, etc.). Os dados de imagem resultantes de processamento podem ser apresentados em um display, armazenados e/ou transmitidos. Por exemplo, dados de imagem renderizados podem ou não ser apresentados em um display imediatamente. Os dados de imagem renderizada podem ser armazenados (para apresentação posterior em um display, por exemplo), podem ser transmitidos para outro dispositivo (que pode apresentar os dados de imagem renderizada em um display, por exemplo) e/ou podem ser apresentados em um display.

[0038] Ineficiência de renderização pode ser um problema atual. Por exemplo, a realidade virtual (VR) pode incluir a renderização de duas visualizações de uma cena, o que pode renderizar o conteúdo duas vezes mais lento para renderizar. Uma abordagem pode envolver a realização de um rastreamento ocular (que pode ser realizado com precisão e baixo custo), renderizar três passagens geometrias com diferentes níveis de rudeza, realizando o antialiasing e mesclando as três diferentes qualidades de buffer de quadro. No entanto, essa abordagem podem ser ineficientes, uma vez que as várias passagens de geometria podem se sobrepor, resultando em alguns pixels sendo processados repetidamente.

[0039] Em algumas configurações, os sistemas e métodos aqui descritos podem prover abordagens multinível de única passagem de renderização de detalhe (multi-LOD) (por

exemplo, renderização foveada de única passagem). Por exemplo, algumas abordagens podem utilizar um tessellator (por exemplo, máquina de tecelagem), antialiasing multiamostra (MSAA), envio de núcleo dinâmico e/ou um buffer de quadro multirresolução (por exemplo, não uniforme) (por exemplo, objeto de buffer de quadro (FBO)). Em algumas abordagens, pode ser necessária apenas uma passagem de geometria. Esta melhoria pode reduzir o uso de largura de banda de geometria e/ou pode reutilizar MSAA.

[0040] As configurações de alguns dos sistemas e métodos aqui divulgados podem oferecer um ou mais benefícios de desempenho. Por exemplo, hardware pode ser implementado, que inclui um FBO multirresolução e/ou envio de núcleo dinâmico. Isto pode reduzir o consumo de largura de banda. Por exemplo, múltiplas passagens de geometria (por exemplo, três) podem ser colapsadas em uma usando o tessellator (por exemplo, máquina de tecelagem). Antialiasing de hardware de rasterização pode ser reutilizado em algumas configurações. Isto pode permitir melhorias na renderização de conteúdo regular. Adicionalmente ou em alternativa, envio dinâmico de núcleos de fragmento pode reduzir computação. Estas melhorias podem ser particularmente benéficas no contexto da realidade virtual (VR) e/ou realidade aumentada (AR), onde múltiplas visualizações de uma cena podem ser renderizadas de cada vez (para visualizações estereoscópicas, por exemplo). Em algumas configurações, RV e RA podem ser combinadas. Os sistemas e métodos aqui divulgados podem ser benéficos, como a indústria de processamento gráfico buscando por maneiras de prover experiências imersivas.

[0041] Os sistemas e métodos aqui descritos também descrevem abordagens para renderizar múltiplas zonas para apresentação em janelas. Estes sistemas e métodos podem ser particularmente benéficos no contexto de veículos para melhorar a experiência de usuário em aplicações tais como a ajuda de condutor e veículos autônomos (por exemplo, carros de autocondução).

[0042] Várias configurações são agora descritas com referência às Figuras, em que números de referência semelhantes, podem indicar elementos funcionalmente semelhantes. Os sistemas e métodos geralmente como descritos e ilustrados nas figuras aqui podem ser dispostos e concebidos de uma ampla variedade de configurações diferentes. Assim, a seguinte descrição mais detalhada de várias configurações, como representado nas figuras, não se destina a limitar o escopo, tal como reivindicado, mas é meramente representativo dos sistemas e métodos.

[0043] A Figura 1 é um diagrama de blocos que ilustra uma configuração de um dispositivo eletrônico 102 no qual os sistemas e métodos para renderizar múltiplos níveis de detalhe podem ser implementados. Exemplos do dispositivo eletrônico 102 incluem smartphones, computadores (por exemplo, desktops, laptops, etc.), displays head-mounted (por exemplo, fones de ouvido de realidade Virtual (RV), fones de ouvido de realidade aumentada (AR), etc.), dispositivos VR, dispositivos AR, tablets, reprodutores de mídia, televisores, automóveis, veículos, máquinas fotográficas, câmeras de vídeo, câmeras digitais, telefones celulares, câmeras pessoais, câmeras de ação, aeronaves, aviões, veículos aéreos não tripulados (UAVs), equipamentos

de saúde, consoles de jogos, assistentes digitais pessoais (PDAs), set-top boxes, leitores de mídia, etc. O dispositivo eletrônico 102 pode incluir um ou mais componentes ou elementos. Um ou mais dos componentes ou elementos podem ser implementados em hardware (por exemplo, circuitos), firmware e/ou uma combinação de hardware e software (por exemplo, um processador com instruções).

[0044] Em algumas configurações, o dispositivo eletrônico 102 pode incluir um circuito de palavra de instrução muita longa (VLIW) 104 e a memória de sistema 114. O circuito VLIW 104 pode ser um circuito (por exemplo, processador) que implementa paralelismo de nível de instruções. Por exemplo, o circuito VLIW 104 pode executar instruções em paralelo (por exemplo, ao mesmo tempo). O circuito VLIW 104 pode ser acoplado a (por exemplo, em comunicação eletrônica com) a memória de sistema 114. O circuito VLIW 104 pode ser um dispositivo de renderização de imagens. Por exemplo, o circuito VLIW 104 pode converter dados de geometria (por exemplo, dados de geometria de modelo (s) geométrico, bidimensional (2D) ou tridimensional (3D), vértices, polígonos, etc.) em uma ou mais imagens. A imagem (s) resultante pode ser apresentada em um ou mais displays. Por exemplo, a imagem (s) pode ser uma única imagem para produzir uma visualização 2D ou pode ser múltiplas imagens (por exemplo, imagens estereoscópicas) para produzir uma visualização 3D. Por exemplo, o circuito VLIW 104 pode produzir imagens múltiplas (por exemplo, diferentes visualizações) para uma visualização estereoscópica (por exemplo, uma imagem de um olho esquerdo e outro para uma imagem do olho direito). Deve ser notado que o circuito VLIW

104 pode renderizar uma série de imagens (por exemplo, vídeo). O circuito VLIW 104 pode ser implementado em hardware ou em uma combinação de hardware e software. Um exemplo do circuito VLIW 104 é uma unidade de processamento gráfico (GPU).

[0045] Em algumas configurações, o dispositivo eletrônico 102 pode executar uma ou mais das funções, processos, métodos, etapas, etc. descritos em ligação com uma ou mais das Figuras 2-5, 9, 11, 13 e 15-24. Adicionalmente ou em alternativa, o dispositivo eletrônico 102 pode incluir uma ou mais das estruturas descritas em ligação com uma ou mais das Figuras 2-5, 9, 11, 13 e 15-24.

[0046] A memória de sistema 114 pode armazenar instruções e/ou dados. Exemplos de memória de sistema 114 inclui a memória de acesso aleatório (RAM), memória de acesso aleatório dinâmica (DRAM), memória de acesso aleatório dinâmica síncrona (SDRAM), memória de acesso aleatório dinâmica síncrona de taxa de dados dupla (DDR SDRAM), DDR2, DDR3, DDR4, memória de acesso aleatório estática (SRAM), registradores, memória somente de leitura (ROM), memória somente de leitura programável apagável (EPROM), memória somente de leitura programável eletricamente apagável (EEPROM), memória flash NAND, memória flash NOR, etc. O circuito VLIW 104 pode acessar (por exemplo, ler a partir de e/ou gravar em) a memória de sistema 114. A memória de sistema 114 pode ser acessível por outros elementos (se houver) do dispositivo eletrônico 102, tal como um ou mais processadores (por exemplo, unidades de processamento central (CPUs)). A memória de sistema 114 pode ser separada do circuito VLIW 104. Exemplos de instruções e/ou dados que

podem ser armazenados pelo memória de sistema 114 podem incluir instruções, dados de comando, dados geométricos (por exemplo, vértices, polígonos, normais (por exemplo, orientações de objeto), primitivas, metadados, etc.), dados de textura, dados de visualização de acesso não ordenados, parâmetro (s) de renderização (por exemplo, parâmetro de nível de detalhe (s)), etc. Em algumas configurações, o dispositivo eletrônico 102 (por exemplo, o memória de sistema 114) pode incluir um ou mais buffers de quadro. O buffer (s) de quadro pode armazenar temporariamente (por exemplo, armazenar) dados de imagem. Os dados de imagem em buffer podem ser apresentados em um ou mais displays.

[0047] O circuito VLIW 104 pode incluir um ou mais elementos de renderizar imagens. Alguns exemplos dos elementos podem incluir um front end (EF), processador de vértice (VPS, coletor de vértice (VF), shader de vértice (VS), shader de controle de tecelagem (TCS), hull shader (HS), tessellator (por exemplo, máquina de tecelagem) (TESS), shader de avaliação de tecelagem (TES), shader de domínio (DS), shader de geometria (GS), rasterizador (RAST), shader de fragmento (FS), pixel shader (PS), mosaico, unidade de saída de renderização (ROP), clipper (clip) e/ou saída de fluxo (SOL), etc. Em algumas configurações, um ou mais destes elementos podem ser referidos como um pipeline gráfico 106. Deve ser notado que o tessellator pode ser uma máquina de tecelagem de função fixa em alguns configurações. O tessellator (e/ou um ou mais outros elementos de um pipeline gráfico) pode ser implementado em hardware, software ou uma combinação de hardware e software

[0048] O circuito VLIW 104 pode incluir memória em chip 110. A memória em chip 110 pode ser implementada no circuito VLIW 104 para prover acesso à memória rápida. Por exemplo, a memória em chip 110 pode ser acessada de forma mais rápida do que a memória de sistema 114. Exemplos de memória em chip 110 podem incluir memória de acesso aleatório (RAM), memória de acesso aleatório dinâmica (DRAM), memória de acesso aleatório dinâmica síncrona (SDRAM), memória de acesso aleatório dinâmica síncrona de taxa de dados dupla (DDR SDRAM), DDR2, DDR3, DDR4, memória de acesso aleatório estática (SRAM), registradores, memória somente de leitura programável (ROM), memória somente de leitura programável apagável (EPROM), memória somente de leitura programável eletricamente apagável (EEPROM), memória flash NAND, memória flash NOR, etc. Em algumas configurações, a memória em chip 110 pode ser implementada em múltiplos níveis (por exemplo, cache de nível 1 (L1), cache de nível 2 (L2), cache de nível 3 (L3), etc.). Exemplos de dados que podem ser armazenados pela memória em chip 110 podem incluir dados de geometria (por exemplo, os vértices, polígonos, normais, primitivas, metadados, etc.), dados de textura, dados de visualização de acesso não ordenados, um ou mais parâmetros de renderização (por exemplo, parâmetro (s) de nível de detalhe (LOD)), etc. Em algumas configurações, a memória em chip 110 pode incluir um ou mais buffer (s) de quadro (além de ou em alternativa a partir da memória de sistema 114, por exemplo). O buffer (s) de quadro pode armazenar em buffer (por exemplo, armazenar) dados de imagem. Os dados de imagem em buffer podem ser apresentados em um ou mais displays.

[0049] Em algumas configurações, o circuito VLIW 104 pode incluir um controlador de memória assíncrona 108. O controlador de memória assíncrona 108 pode ser implementado em hardware ou em uma combinação de hardware e software. O controlador de memória assíncrona 108 pode ser implementado no circuito VLIW 104, separadamente do circuito VLIW, ou pode ser implementado parcialmente no circuito VLIW 104 e parcialmente separado do circuito VLIW 104. O controlador de memória assíncrona 108 pode ser configurado para acessar a memória (por exemplo, memória em chip 110 e/ou a memória de sistema 114) de forma assíncrona. Em algumas configurações, o controlador de memória assíncrona 108 opera "de forma assíncrona" no sentido de que o controlador de memória assíncrona 108 pode acessar a memória (por exemplo, parâmetro (s) de nível de detalhe (LOD), etc.) fora de sincronização com um conjunto de dados que está a ser processado (por exemplo, tecelado). Por exemplo, o circuito VLIW 104 pode periodicamente processar conjuntos de dados. Processar (por exemplo, tecelar) um único conjunto de dados pode ser referido como uma chamada de desenho. Por exemplo, uma chamada de desenho pode ser uma instrução (por exemplo, uma solicitação de programação, a instrução, etc.) para o circuito VLIW 104 processar (por exemplo, renderizar) um conjunto de dados. Um ou mais parâmetros (por exemplo, parâmetro de LOD, configuração de tecelagem, um ou mais de outros parâmetros, etc.) podem ser associados com e/ou definidos para a chamada de desenho. Por conseguinte, uma chamada de desenho pode estabelecer um LOD a ser renderizado para o conjunto de dados, por exemplo.

[0050] Em abordagens conhecidas, cada conjunto de dados (por exemplo, chamada de desenho) tem um nível fixo de detalhe (LOD). Nestas abordagens, o LOD para um conjunto de dados não pode ser alterado, uma vez que processamento já começou naquele conjunto de dados (por exemplo, não pode mudar durante uma chamada de desenho). Além disso, cada conjunto de dados pode ter apenas um único LOD em abordagens conhecidas.

[0051] De acordo com os sistemas e métodos aqui descritos, o controlador de memória assíncrona 108 pode de forma assíncrona acessar a memória (por exemplo, memória em chip 110 e/ou a memória de sistema 114) para permitir renderizar diferentes níveis de detalhe (por exemplo, zonas diferentes com diferentes níveis de detalhe) dentro de um único conjunto de dados (por exemplo, durante o processamento de uma chamada de desenho). Por exemplo, o controlador de memória assíncrona 108 pode acessar a memória (por exemplo, o parâmetro (s), parâmetro de LOD (s), etc.) após o processamento (por exemplo, tecelagem, shading, etc.) em um conjunto de dados que já começou e antes do processamento do conjunto de dados ser concluído. Isto pode permitir que o circuito VLIW 104 altere LOD durante o processamento de um conjunto de dados para produzir diferentes níveis de detalhe em um conjunto de dados. Cada conjunto de dados pode incluir múltiplos primitivos (por exemplo, pontos, polígonos, etc.). Em algumas configurações, cada conjunto de dados pode (inicialmente) ter um único LOD atribuído. No entanto, o controlador de memória assíncrona 108 pode atribuir um nível de detalhe diferente para um conjunto de dados durante o processamento desse conjunto de dados. Em outras palavras,

o controlador de memória assíncrona 108 pode alterar o LOD para um conjunto de dados (depois do processamento (por exemplo, tecelagem, shading, etc.) sobre aquele conjunto de dados que já começou, mas antes do processamento (por exemplo, tecelagem, shading, etc.) sobre aquele conjunto de dados que foi concluído). Por exemplo, os sistemas e métodos aqui divulgados podem permitir a mudança de LOD em uma base por pixel e/ou per-primitivo (mesmo dentro de um conjunto de dados, por exemplo). Em algumas configurações, os parâmetros (por exemplo, o parâmetro (s), parâmetro de LOD (s), etc.) podem ser atualizados durante o processamento. Por exemplo, um processador (por exemplo, a unidade de processamento central (CPU), processador de sinal digital (DSP), etc.) ou qualquer bloco de hardware dedicado (por exemplo, qualquer hardware que lida com os dados do sensor (por exemplo, dados do sensor de rastreamento ocular, dados de sensor de movimento, etc.)) pode atualizar os parâmetros. O circuito VLTW 104 (por exemplo, GPU) pode ler (por exemplo, pode sempre ler, ler continuamente, periodicamente ler, etc.) a partir de uma seção de memória (por exemplo, memória em chip 110 e/ou memória de sistema 114) que inclui os parâmetros. Por conseguinte, o circuito VLTW 104 (por exemplo, GPU) pode ajustar em conformidade por primitivo em vez de para uma chamada de desenho inteira. Em algumas configurações, o circuito VLIW 104 pode renderizar diferentes níveis de detalhe em uma única chamada de desenho.

[0052] Os sistemas e métodos aqui descritos podem prover um ou mais benefícios. Por exemplo, o controlador de memória assíncrona 108 pode permitir o processamento mais eficiente ao renderizar múltiplos LODs. Em abordagens

conhecidas, múltiplas camadas de sobreposição podem ser renderizadas, em que cada camada tem um LOD diferente. Em seguida, as camadas de sobreposição podem ser misturadas. No entanto, esta abordagem é ineficiente, porque os mesmos dados são renderizados várias vezes. De acordo com os sistemas e métodos aqui divulgados, os diferentes níveis de detalhe podem ser renderizados em uma única passagem. Isto pode evitar a rerenderização dos mesmos dados e/ou pode evitar ter que misturar várias camadas com diferentes níveis de detalhe.

[0053] Adicionalmente ou em alternativa, os sistemas e métodos aqui divulgados podem permitir a mudança de forma assíncrona de LOD. Por exemplo, renderizar uma ou mais zonas de uma imagem pode ser baseado em rastreamento ocular. Por exemplo, o dispositivo eletrônico 102 pode renderizar várias zonas com diferentes níveis de detalhe, em que uma zona com um maior nível de detalhe é renderizada em uma área em que um usuário está olhando. O rastreamento ocular pode detectar quando um usuário muda para olhar para uma parte diferente da imagem. Os sistemas e métodos aqui descritos (por exemplo, o controlador de memória assíncrona 108) podem mudar imediatamente o LOD renderizado baseado em um rastreamento ocular. Por exemplo, o circuito VLIW 104 pode aumentar o nível de detalhe em uma área da imagem que o usuário tiver alterado o olhar para visualizar, mesmo durante o processamento de um conjunto de dados. Isto pode prover uma melhor experiência de usuário. Além disso, os sistemas e métodos aqui descritos (por exemplo, o controlador de memória assíncrona 108) pode reduzir o LOD em uma área da

imagem para a qual o olhar do usuário não é dirigido. Isto pode reduzir o processamento desnecessário.

[0054] O circuito VLIW 104 pode incluir um controlador de buffer de quadro não uniforme 112. O controlador de buffer de quadro não uniforme 112 (por exemplo, FBO de multirresolução) pode ser implementado em hardware ou em uma combinação de hardware e software. O controlador de buffer de quadro não uniforme 112 pode ser implementado no circuito VLIW 104, separadamente do circuito VLIW 104, ou pode ser implementado parcialmente no circuito VLIW 104 e parcialmente separado do circuito VLIW 104. Em algumas configurações, o controlador de buffer de quadro não uniforme 112 pode ser implementado como parte do pipeline gráfico 106. Em alternativa, o controlador de buffer de quadro não uniforme 112 pode ser implementado como parte da memória em chip 110. Em uma outra implementação, o controlador de buffer de quadro não uniforme 112 pode ser implementado no circuito VLIW 104, mas separado do pipeline gráfico 106 e da memória em chip 110.

[0055] O controlador de buffer de quadro não uniforme 112 pode ser configurado para acessar dinamicamente diferentes subconjuntos de um ou mais buffer (s) de quadro. Em algumas configurações, os diferentes subconjuntos de um buffer de quadro podem corresponder a diferentes níveis de detalhe, zonas com diferentes níveis de detalhe e/ou diferentes níveis de mapa de bits. Por exemplo, o controlador de buffer de quadro não uniforme 112 pode ser configurado para operar em diferentes subconjuntos de um buffer de quadro dinamicamente. Deve ser notado que pode haver dois ou mais subconjuntos de buffer de quadro. Em algumas configurações,

diferentes subconjuntos do buffer de quadro não uniforme podem corresponder a diferentes visualizações (por exemplo, uma visualização de olho esquerdo e uma visualização de olho direito para renderização estereoscópica). O buffer de quadro não uniforme pode melhorar a utilização da largura de banda. Com um buffer de quadro não uniforme, por exemplo, a visualização do olho esquerdo e a visualização do olho direito podem ser processadas simultaneamente (por exemplo, ao mesmo tempo) e salvas na memória de sistema 114 em uma passagem. Adicionalmente ou em alternativa, por exemplo, o buffer de quadro não uniforme pode ativar e/ou melhorar a utilização da memória para renderizar múltiplos LODs em uma só passagem.

[0056] Em algumas configurações, o acesso dinamicamente a diferentes subconjuntos do buffer de quadro pode incluir o acesso a pelo menos um pixel de uma primeira zona a uma taxa diferente de pelo menos um pixel de uma segunda zona. A primeira zona e a segunda zona podem corresponder a diferentes níveis de detalhe. Por exemplo, o controlador de buffer de quadro não uniforme 112 pode permitir que pixels de uma zona (com uma LOD superior, por exemplo) sejam processados em uma taxa maior do que pixels de uma outra zona (com um LOD inferior, por exemplo). Esta abordagem pode permitir economias de energia ao diminuir o processamento de uma ou mais zonas (por exemplo, zonas de menor LOD). Note-se que pode haver pixels de duas ou mais zonas que podem ser acessados em duas ou mais taxas diferentes.

[0057] Além disso ou alternativamente, o acesso de forma dinâmica a diferentes subconjuntos do buffer de quadro

pode incluir permitir troca de sub-rotina de shader. Por exemplo, troca de sub-rotina de shader pode ser realizada quando o processamento de um primeiro pixel está em andamento e processo de um segundo pixel é concluído. Por exemplo, um primeiro subconjunto do buffer de quadro pode ser alocado a um ou mais pixels processados com uma primeira sub-rotina de shader, enquanto que um segundo subconjunto do buffer de quadro pode ser alocado para um ou mais pixels processados com uma segunda sub-rotina de shader. Quando o processamento de um ou mais pixels de segunda sub-rotina de shader é concluído, o dispositivo eletrônico 102 pode trocar de sub-rotinas de shader para ocupar o segundo subconjunto do buffer de quadro. Isto pode prover um renderização mais eficiente permitindo que a capacidade do buffer de quadro seja utilizada de forma mais eficiente. Deve ser notado que dois ou mais subconjuntos do buffer de quadro podem ser utilizados para permitir troca de sub-rotina para um ou mais dos subconjuntos.

[0058] O controlador de buffer de quadro não uniforme 112 pode ser configurado para substituir uma primeira amostra processada de um primeiro pixel para uma segunda amostra de um segundo pixel para evitar o processamento da segunda amostra do segundo pixel. O primeiro pixel pode ter um número diferente de amostras do que o segundo pixel. Por exemplo, um primeiro pixel a partir de uma primeira zona pode ter um nível de detalhe maior do que um segundo pixel vizinho de uma segunda zona com um LOD inferior. O controlador de buffer de quadro não uniforme 112 pode substituir a amostra (não processada) do segundo pixel com a amostra (processada) do primeiro pixel. Deste modo, o

controlador de buffer de quadro não uniforme 112 pode reduzir o processamento. Deve ser notado que o controlador de buffer de quadro não uniforme 112 pode substituir uma ou mais amostras (não processadas) de um ou mais pixels com uma ou mais amostras (processadas) de um ou mais outros pixels.

[0059] Em algumas configurações, o dispositivo eletrônico pode incluir 102 e/ou pode ser acoplado a um ou mais (por exemplo, displays, displays head-mounted). O display (s) pode ser configurado para apresentar os diferentes níveis de detalhe.

[0060] Figura 2 é um diagrama de fluxo que ilustra uma configuração de um método 200 para renderizar múltiplos níveis de detalhe. O método 200 pode ser realizado pelo dispositivo eletrônico 102 descrito em ligação com a Figura 1.

[0061] O dispositivo eletrônico 102 pode obter 202 dados de geometria. Por exemplo, o dispositivo eletrônico 102 pode carregar dados de geometria provenientes do armazenamento (por exemplo, armazenamento em disco rígido, armazenamento removível, tal como um disco rígido externo, unidade de disco de vídeo digital (DVD), unidade de Blu-Ray, disco compacto (CD), thumb drive, etc.) para a memória (por exemplo, a memória de sistema 114 e/ou de memória em chip 110). Adicionalmente ou em alternativa, o dispositivo eletrônico 102 pode receber dados de geometria a partir de outro dispositivo. Por exemplo, o dispositivo eletrônico 102 pode receber dados de geometria através de uma interface de comunicação (por exemplo, Ethernet, Institute of Eletrônica and Electronic Engineers (IEEE) interface 802.11, interface de rede celular, etc.) e carregar os dados de geometria na

memória (por exemplo, memória de sistema 114 e/ou memória em chip 110). Exemplos de dados de geometria podem incluir pontos, linhas e/ou polígonos (por exemplo, triângulos), etc.

[0062] O dispositivo eletrônico 102 pode renderizar 204 diferentes níveis de detalhe de forma assíncrona. Isto pode ser conseguido tal como descrito acima em ligação com a Figura 1. Por exemplo, o dispositivo eletrônico 102 pode acessar a memória de forma assíncrona (por exemplo, a memória de sistema 114 e/ou memória em chip 110) para renderizar diferentes níveis de detalhe. Por exemplo, o dispositivo eletrônico 102 pode alterar um LOD para um conjunto de dados durante o processamento (em que o conjunto de dados inicialmente tinha um LOD diferente, por exemplo). Em algumas configurações, renderizar 204 diferentes níveis de detalhe de forma assíncrona pode incluir a realização de tecelagem de LOD dinâmico.

[0063] O dispositivo eletrônico 102 pode acessar dinamicamente 206 diferentes subconjuntos de um buffer de quadro. Isto pode ser conseguido tal como descrito acima em ligação com a Figura 1. Por exemplo, o dispositivo eletrônico 102 pode acessar pelo menos um pixel de uma primeira zona a uma taxa diferente de pelo menos um pixel de uma segunda zona. Adicionalmente ou em alternativa, o dispositivo eletrônico 102 pode permitir troca de sub-rotina de shader, quando o processamento de um primeiro pixel está em andamento e processo de um segundo pixel é concluído. Adicionalmente ou em alternativa, o dispositivo eletrônico 102 pode substituir uma primeira amostra processada de um primeiro

pixel para uma segunda amostra de um segundo pixel para evitar o processamento da segunda amostra do segundo pixel.

[0064] A figura 3 é um diagrama de blocos que ilustra uma configuração de um dispositivo eletrônico 302 no qual os sistemas e métodos para renderizar múltiplos níveis de detalhe podem ser implementados. O dispositivo eletrônico 302 descrito em ligação com a Figura 3 pode ser um exemplo do dispositivo eletrônico 102 descrito em conexão com a Figura 1. Em algumas configurações, um ou mais dos componentes ou elementos do dispositivo eletrônico 302 podem ser semelhantes aos componentes ou elementos correspondentes descritos em ligação com a Figura 1. Um ou mais dos componentes ou elementos podem ser implementados em hardware (por exemplo, circuitos) ou uma combinação de hardware e de software (por exemplo, um processador com instruções).

[0065] Em algumas configurações, o dispositivo eletrônico 302 pode incluir um circuito de palavra de instrução muito longa (VLIW) 304, memória de sistema 314, um ou mais displays 332, um ou mais sensores de imagem 316, um ou mais sistemas ópticos 318, uma ou mais interfaces de comunicação 320, uma ou mais antenas 322 e/ou um ou mais processadores 324. Dois ou mais dos elementos ou componentes descritos em ligação com a Figura 3 podem estar em comunicação eletrônica um com o outro. Por exemplo, o circuito VLIW 304 pode ser acoplado a (por exemplo, em comunicação eletrônica com) a memória de sistema 314. O circuito VLIW 304 pode ser um dispositivo de renderização de imagens, tal como descrito acima em ligação com uma ou mais das Figuras 1 e 2. Em algumas configurações, a imagem (s) resultante pode ser apresentada em um ou mais displays 332.

O circuito VLIW 304 pode ser separado do processador 324, em algumas implementações. Em outras implementações, o circuito VLIW 304 pode ser integrado no processador 324.

[0066] A interface de comunicação 320 pode permitir que o dispositivo eletrônico 302 se comunique com um ou mais outros dispositivos eletrônicos. Por exemplo, a interface de comunicação 320 pode prover uma interface para comunicações com e/ou sem fio. Em algumas configurações, a interface de comunicação 320 pode ser acoplada a uma ou mais antenas 322 para a transmissão e/ou recepção de sinais de radiofrequência (RF). Adicionalmente ou em alternativa, a interface de comunicação 320 pode permitir um ou mais tipos de comunicação fixa (por exemplo, Barramento Universal Serial (USB), Ethernet, Arranjo de Gráficos de Vídeo (VGA), Interface Digital Visual (DVI), Interface Multimídia de Alta Definição (HDMI), Porta de Display, link de Alta Definição móvel (MHL), etc.).

[0067] Em algumas configurações, várias interfaces de comunicações 320 podem ser implementada e/ou utilizadas. Por exemplo, uma interface de comunicação 320 pode ser uma interface de comunicação celular 320 (por exemplo, 3G, Evolução de Longo Prazo (LTE), CDMA, etc.), uma outra interface de comunicação 320 pode ser uma interface Ethernet, uma outra interface de comunicação 320 pode ser uma interface de barramento serial universal (USB), ainda outra interface de comunicação 320 pode ser uma interface de rede de área local sem fio (WLAN) (por exemplo, Interface 802.11 do Institute of Eletrônica and Electronics Engineers (IEEE)) e ainda outra interface de comunicação 320 pode ser uma interface Bluetooth.

[0068] Em algumas configurações, o dispositivo eletrônico 302 pode executar uma ou mais das funções, processos, métodos, etapas, etc., descritos em ligação com uma ou mais das Figuras 1, 3-5, 9, 11, 13 e 15-24. Adicionalmente ou em alternativa, o dispositivo eletrônico 302 pode incluir uma ou mais das estruturas descritas em ligação com uma ou mais das Figuras 1, 3-5, 9, 11, 13 e 15-24.

[0069] A memória de sistema 314 pode armazenar instruções e/ou dados. A memória de sistema 314 descrita em ligação com a Figura 3 pode ser um exemplo do memória de sistema 114 descrito em ligação com a Figura 1. O circuito VLIW 304 pode acessar (por exemplo, ler a partir de e/ou gravar na) a memória de sistema 314. A memória de sistema 314 pode também ser acessível pelo processador (s) 324. A memória de sistema 314 pode armazenar dados de geometria 328. Em algumas configurações, a memória de sistema 314 pode incluir um buffer de quadro 330a. O buffer de quadro 330a pode ser uma parte da memória de sistema 314 para armazenar os dados de imagem. Os dados de imagem armazenados em buffer podem ser apresentados, por um ou mais displays 332, em algumas configurações.

[0070] O circuito VLIW 304 pode incluir um ou mais elementos de renderização de imagens. Alguns exemplos dos elementos pode incluir um front end (EF), processador de vértice (VPs), coletor de vértice (VF), shader de vértice (VS), shader de controle de tecelagem (TCS), hull shader (HS), tessellator (por exemplo, máquina de tecelagem) (TESS), shader de avaliação de tecelagem (TES), shader de domínio (DS), shader de shader (GS), rasterizador (RAST),

shader de fragmento (FS), pixel shader (PS), mosaico, unidade de saída de renderização (ROP), clipper (clip) e/ou saída de fluxo (SOL), etc. Em algumas configurações, um ou mais destes elementos podem ser referidos como um pipeline gráfico.

[0071] O circuito VLIW 304 pode incluir memória 310. A memória em chip 310 descrita em ligação com a Figura 3 pode ser um exemplo da memória em chip 110 descrita em conexão com a Figura 1. Em algumas configurações, a memória em chip 310 pode incluir um buffer de quadro 330b (além de ou em alternativa ao buffer de quadro 330a na memória de sistema 314, por exemplo). O buffer de quadro pode ser uma parte da memória em chip 310 para armazenar dados de imagem. Os dados de imagem armazenados em buffer podem ser apresentados, por um ou mais displays 332, em algumas configurações.

[0072] Em algumas configurações, o circuito VLIW 304 pode incluir um controlador de memória assíncrona 308. O controlador de memória assíncrona 308 pode ser implementado em hardware ou em uma combinação de hardware e software. O controlador de memória assíncrona 308 pode ser implementado no circuito VLIW 304, separadamente do circuito VLIW, ou pode ser implementado parcialmente no circuito VLIW 304 e parcialmente separado do circuito VLIW 304. O controlador de memória assíncrona 308 pode ser configurado para acessar a memória (por exemplo, memória em chip 310 e/ou memória de sistema 314) de forma assíncrona. Deve ser notado que o controlador de memória assíncrona 308 pode utilizar (por exemplo, acesso) a memória em chip 110 e/ou a memória de sistema 114 (por exemplo, um ou ambos). Algumas configurações podem depender de um caso de uso. Por exemplo, se os dados

do sensor (por exemplo, dados de sensor de imagem 316) estão sendo gravados a uma taxa elevada (por exemplo, 1000 hertz (Hz)), em seguida, o cache pode perder tempo, bateria e/ou outros recursos. O controlador de memória assíncrona 308 descrito em ligação com a Figura 3 pode ser um exemplo do controlador de memória assíncrona 108 descrito em conexão com a Figura 1. O controlador de memória assíncrona 308 descrito em ligação com a Figura 3 pode operar como descrito em ligação com o controlador de memória assíncrona 108 descrito em ligação com a Figura 1.

[0073] O circuito VLIW 304 pode incluir um controlador de buffer de quadro não uniforme 312. O controlador de buffer de quadro não uniforme 312 pode ser implementado em hardware ou uma combinação de hardware e software. O controlador de buffer de quadro padrão não uniforme 312 pode ser implementado no circuito VLIW 304, separadamente do circuito VLIW 304, ou pode ser implementado parcialmente no circuito VLIW 304 e parcialmente separado do circuito VLIW 304. Em algumas configurações, o controlador de buffer de quadro não uniforme 312 pode ser implementado como parte do pipeline gráfico. Em alternativa, o controlador de buffer de quadro não uniforme 312 pode ser implementado como parte da memória em chip 310. Em outra implementação, o controlador de buffer de quadro não uniforme 312 pode ser implementado no circuito VLIW 304, mas separado do pipeline gráfico 306 e da memória em chip 310. O controlador de buffer de quadro não uniforme 312 descrito em ligação com a Figura 3 pode ser um exemplo do controlador de buffer de quadro não uniforme 112 descrito em conexão com a Figura 1. O controlador de buffer de quadro não uniforme 312 descrito em

ligação com a Figura 3 pode operar como descrito em ligação com o controlador de buffer de quadro não uniforme 112 descrito em ligação com a Figura 1.

[0074] Em algumas configurações, o dispositivo eletrônico 302 pode realizar renderização de passagem única multi-LOD. Renderização multi-LOD pode incluir renderização de diferentes zonas de uma imagem com diferentes níveis de detalhe. Renderização de passagem única multi-LOD pode incluir renderizar zonas diferentes com diferentes níveis de detalhe (por exemplo, níveis de tecelados de detalhe) em uma única passagem (sem processar repetidamente todo o pixel, por exemplo). Renderização de passagem única foveada pode ser um exemplo de renderização de passagem única multi-LOD, em que diferentes zonas com diferentes níveis de detalhe podem ser baseadas em rastreamento ocular. Por exemplo, uma zona pode ser uma área circular (ou uma região de outra forma) aproximadamente centrada no ponto de uma visualização (por exemplo, imagem) onde o usuário está olhando. Adicionalmente ou em alternativa, renderização de passagem única (por exemplo, renderização de passagem única multi-LOD) pode incluir a realização de uma passagem (por exemplo, passagem de processamento) sobre os dados e/ou textura para ser renderizada, mesmo que ambas uma visualização de olho esquerdo e uma visualização de olho direito precise de ser processada. Por conseguinte, algumas configurações dos sistemas e métodos aqui descritos podem utilizar o máximo dos dados para ambos os pontos de visualização do olho, tanto quanto possível, antes de mover os dados entre a memória de sistema e a memória em chip (por exemplo, a memória da GPU). Em algumas configurações, o controlador de memória

assíncrona 308 e/ou o controlador de buffer de quadro não uniforme 312 pode permitir a realização de uma renderização de única passagem multi-LOD (por exemplo, renderização foveada de passagem única). Por exemplo, o controlador de memória assíncrona 308 pode permitir parâmetro de leitura (s) (por exemplo, o parâmetro nível de detalhe (LOD)) a partir de um bloco de memória volátil (por exemplo, adaptar dinamicamente durante uma chamada de desenho). Por exemplo, o controlador de memória assíncrona 308 pode permitir um ou mais de um shader de controle de tecelagem (TCS), tessellator (TESS), shader de avaliação de tecelagem (TES), shader de geometria (GS), rasterizador e shader de fragmento (FS) para acessar um ou mais parâmetros a partir de um bloco de memória volátil (por exemplo, para se adaptar dinamicamente durante uma chamada de desenho).

[0075] Em algumas configurações, o circuito VLIW 304 pode incluir um rasterizador. O rasterizador pode permitir MSAA para executar mais amostragem dos primitivos, os quais por sua vez podem ativar mais avaliações de shader de fragmento (FS). Além disso, amostragem dos primitivos pode ser realizada para evitar artefatos como jaggies, que são devido a amostras insuficientes sendo processadas e medidas.

[0076] O dispositivo eletrônico 302 pode obter uma ou mais imagens (por exemplo, imagens digitais, quadros de imagens, vídeo, etc.). As uma ou mais imagens podem ser imagens de um ou mais usuários e/ou uma cena (por exemplo, um ou mais objetos e/ou fundo). Por exemplo, o dispositivo eletrônico 302 pode incluir um ou mais sensores de imagem 316 e/ou um ou mais sistemas ópticos 318 (por exemplo,

lentes) que se concentram as imagens de objetos que se encontram dentro do campo de visualização do sistema óptico (s) 318 para o sensor de imagem (s) 316. Em algumas configurações, o sensor (s) de imagem 316 pode captar uma ou mais imagens. O sensor (s) de imagem 316 e/ou sistema óptico (s) 318 pode ser acoplado a e/ou controlado pelo processador 324.

[0077] Adicionalmente ou em alternativa, o dispositivo eletrônico 302 pode solicitar e/ou receber uma ou mais imagens a partir de outro dispositivo (por exemplo, um sensor de imagem externo acoplado ao dispositivo eletrônico 302, um servidor de rede, câmera de tráfego, câmera drop, câmera de automóvel, câmera web, etc.). Em algumas configurações, o dispositivo eletrônico 302 pode solicitar e/ou receber uma ou mais imagens através da interface de comunicação 320. Por exemplo, o dispositivo eletrônico 302 pode ou não incluir uma câmara (por exemplo, um sensor de imagem 316 e/ou sistema óptico 318) e pode receber imagens de um dispositivo remoto.

[0078] Em algumas configurações, os um ou mais sensores de imagem 316 incluídos no dispositivo eletrônico 302 e/ou um ou mais outros sensores de imagem acoplados ao dispositivo eletrônico 302 podem ser orientados para captar uma ou mais imagens de um usuário. Por exemplo, um smartphone pode incluir uma câmara montada na mesma face de um display (por exemplo, display 332). Desta forma, a câmara pode capturar imagens de um usuário enquanto o usuário está olhando para o display. Em um outro exemplo, uma câmara pode ser montada em um console e/ou volante de um veículo para capturar imagens de um usuário (por exemplo, condutor).

[0079] Adicionalmente ou em alternativa, os um ou mais sensores de imagem 316 incluídos no dispositivo eletrônico 302 e/ou um ou mais outros sensores de imagem acoplados ao dispositivo eletrônico 302 podem ser orientados para capturar cenário. Por exemplo, uma ou mais câmeras podem ser montadas na parte de trás de um smartphone. Em um outro exemplo, uma ou mais câmaras podem ser montadas no exterior de um veículo. Em algumas configurações, o dispositivo eletrônico 302 pode utilizar as imagens da paisagem em aplicações de realidade aumentada (AR), aplicações de realidade virtual (VR) e/ou outras aplicações (por exemplo, visualização surround, assistência ao condutor, sistemas de assistência ao condutor avançados (ADAS), etc.).

[0080] Em algumas configurações, a imagem (s) capturada pelo sensor (s) de imagem 316 e/ou recebida através da interface de comunicação (s) 320 pode ser utilizada pelo dispositivo eletrônico 302 para o rastreamento ocular. Por exemplo, o processador 324 pode incluir e/ou implementar um rastreamento ocular 326. O rastreamento ocular 326 pode controlar o olhar (por exemplo, direção do olhar) de um ou mais usuários. Por exemplo, o rastreamento ocular 326 pode localizar o olho (s) de um ou mais usuários na imagem (s) e pode estimar o olhar (por exemplo, direção do olhar) do usuário (es). Por exemplo, o rastreamento ocular 326 pode determinar (por exemplo, estimar) onde um usuário está olhando em um display (por exemplo, display 332 ou um display externo) e/ou quando um usuário está olhando de uma imagem apresentada por um display. Em outras palavras, o rastreamento ocular 326 pode determinar (por exemplo,

estimativa) para onde o olhar de um usuário está direcionado em relação a uma imagem e/ou display.

[0081] Os sistemas e métodos aqui divulgados podem permitir a mudança de forma assíncrona de LOD e/ou renderização de múltiplos níveis de detalhe, em uma única passagem. Em algumas configurações, renderizar uma ou mais zonas de uma imagem pode ser baseado em rastreamento ocular. As zonas da imagem podem ter diferentes níveis de detalhe. Por exemplo, o dispositivo eletrônico 302 pode processar várias zonas com diferentes níveis de detalhe, em que uma zona com um maior nível de detalhe é renderizada em uma área em que um usuário está atualmente olhando. Em algumas configurações, isso pode ser referido como renderização foveada. O rastreamento ocular 326 pode produzir informações de rastreamento ocular. As informações de rastreamento ocular podem indicar para onde o olhar de um usuário está direcionado (por exemplo, olhares dos usuários são direcionados) em relação a um display e/ou imagem. Em algumas configurações, o processador 324 e/ou o circuito VLIW 304 pode determinar um ou mais parâmetros de nível de detalhe com base na informação de rastreamento ocular. O parâmetro (s) de LOD pode indicar um LOD a ser renderizado por uma ou mais zonas de uma imagem. O parâmetro (s) de LOD pode ser armazenado na memória de sistema 314 310 e/ou memória em chip. O parâmetro de LOD (s) pode ser atualizado de forma assíncrona em relação a um conjunto de dados (por exemplo, chamada de desenho) que está sendo processado pelo circuito VLIW 304. O controlador de memória assíncrona 308 pode ler o parâmetro de LOD (s) (a partir da memória de sistema 314 e/ou memória em chip 310) durante o processamento do conjunto

de dados (por exemplo, chamada de desenho). Por exemplo, o controlador de memória assíncrona 308 pode atualizar definições de tecelagem durante o processamento do conjunto de dados (por exemplo, chamada de desenho).

[0082] O rastreamento ocular 326 pode detectar quando um usuário muda a ótica para olhar para uma parte diferente da imagem. Os sistemas e métodos aqui descritos (por exemplo, o controlador de memória assíncrona 308) pode mudar imediatamente o LOD renderizado baseado no rastreamento ocular (por exemplo, a informação de rastreamento ocular e/ou parâmetro (s) de LOD). Por exemplo, o controlador de memória assíncrona 308 pode ler um ou mais parâmetros (por exemplo, parâmetros de LOD), que podem mudar durante o processamento de um conjunto de dados (por exemplo, chamada de desenho). Por exemplo, o circuito VLIW 304 pode aumentar o nível de detalhe em uma área (por exemplo, zona) da imagem que o usuário alterou a ótica para visualizar, mesmo durante o processamento de um conjunto de dados. Adicionalmente ou em alternativa, os sistemas e métodos aqui descritos (por exemplo, o controlador de memória assíncrona 308) pode reduzir o LOD em uma área (por exemplo, zona) da imagem para a qual o olhar do usuário já não é dirigido. Em algumas configurações, a zona pode ser uma área circular (ou a uma região de outro formato) aproximadamente centrada no ponto de visualização (por exemplo, imagem) onde o usuário está olhando. Em outras configurações, uma zona pode ser toda a área de uma imagem que corresponde a uma janela que o usuário está olhando.

[0083] Em algumas configurações, o dispositivo eletrônico 302 pode incluir um aplicativo de câmera e/ou um

display 332. Quando a aplicativo de câmara está em execução, as imagens de objetos que se encontram dentro do campo de visualização do sistema óptico 318 podem ser capturadas pelo sensor de imagem 316. As imagens que estão sendo capturadas pelo sensor de imagem 316 podem ser apresentadas no display 332. Em algumas configurações, tais imagens podem ser apresentadas em sucessão rápida a uma taxa de quadro relativamente elevada de modo que, em qualquer dado momento em tempo, os objetos que se encontram dentro do campo de visualização do sistema óptico 318 são apresentados no display 332.

[0084] Deve ser notado que um ou mais dos elementos ilustrados no dispositivo eletrônico 302 podem ser opcionais. Por exemplo, um ou mais dos elementos ilustrados no dispositivo eletrônico 302 podem ou não ser incluídos e/ou implementados. Adicionalmente ou em alternativa, um ou mais dos elementos ilustrados no processador 324 e/ou circuito VLIW 304 podem ser implementados separadamente a partir do processador 324 e/ou circuito VLIW 304 (por exemplo, em outros circuitos, sobre outro processador, sobre um dispositivo eletrônico separado, etc.). Por exemplo, o sensor de imagem 316, o sistema óptico 318, a interface de comunicação 320, o processador 324, o rastreamento ocular 326 e/ou o display 332 não podem ser implementados no dispositivo eletrônico 302. Em algumas configurações, o dispositivo eletrônico 302 pode receber imagens e/ou informações de rastreamento ocular de outro dispositivo. Adicionalmente ou em alternativa, um ou mais displays podem ser implementados em um ou mais dispositivos separados.

[0085] Em algumas configurações, o dispositivo eletrônico 302 pode apresentar uma interface de usuário 334 no display 332. Por exemplo, a interface de usuário 334 pode permitir que um usuário interaja com o dispositivo eletrônico 302. Em algumas configurações, o display 332 pode ser uma tela de toque que recebe a entrada a partir de toque físico (por um dedo, caneta ou outra ferramenta, por exemplo). Adicionalmente ou em alternativa, o dispositivo eletrônico 302 pode incluir ou ser associado a uma outra interface de entrada. Por exemplo, o dispositivo eletrônico 302 pode incluir uma câmara de frente para um usuário e pode detectar gestos de usuário (por exemplo, gestos de mão, gestos de braço, rastreamento ocular, piscada dos olhos, etc.). Em outro exemplo, o dispositivo eletrônico 302 pode ser acoplado a um mouse e pode detectar um clique do mouse. Deve ser notado que nenhuma entrada do usuário pode ser necessária em algumas configurações.

[0086] Em algumas configurações, o dispositivo eletrônico 302 pode opcionalmente incluir um sensor de movimento (por exemplo, giroscópio (s), acelerômetro (s), etc.). Por exemplo, o sensor de movimento pode detectar movimento e/ou uma orientação (do dispositivo eletrônico 302, por exemplo). Em algumas configurações, a imagem sendo processada pode ser baseada em informações de movimento e/ou orientação. Por exemplo, o dispositivo eletrônico 302 pode ser um display montado na cabeça (por exemplo, um fone de ouvido de realidade virtual (RV), um fone de ouvido de realidade aumentada (AR), etc.), um veículo (por exemplo, automóvel, drone, avião, etc.), um dispositivo móvel (por exemplo, smartphone) ou outro dispositivo que pode utilizar

informações de movimento e/ou orientação para processar uma imagem. Por exemplo, a informação de movimento e/ou orientação pode indicar uma direção de visualização geral em uma cena renderizada. O dispositivo eletrônico 302 pode processar a imagem com base nesta direção de observação, em complemento ou em alternativa, a partir da informação de rastreamento ocular em algumas configurações. O uso de um sensor de movimento pode ilustrar um outro aspecto da operação assíncrona do controlador de memória assíncrona 308. Por exemplo, um sensor de movimento pode prover a informação do movimento e/ou informação de orientação para a memória (por exemplo, memória de sistema 314 e/ou memória em chip 310) a uma taxa particular (por exemplo, 1000 hertz (Hz)), enquanto que o circuito VLIW 304 pode renderizar quadros a uma taxa relativamente mais baixa (por exemplo, 30 quadros por segundo (fps)). O controlador de memória assíncrona 308 pode de forma assíncrona alterar uma ou mais operações de renderização (por exemplo, tecelagem) no meio de renderização de um conjunto de dados com base na informação do movimento e/ou informação de orientação.

[0087] A Figura 4 é um diagrama que ilustra um exemplo de um buffer de quadro não uniforme 430. Neste exemplo, o buffer de quadro 430 tem uma capacidade de  $2n \times 2m$  pixels. Em algumas configurações, o dispositivo eletrônico 302 pode, opcionalmente, ladrilhar 432 o buffer de quadro 430 em mosaicos 436. No exemplo ilustrado na Figura 4, quatro mosaicos 436 de tamanho  $(n, m)$  estão ilustrados. Em algumas modalidades, memória em chip 310 ou uma parte da memória em chip 310 pode ser limitada ao tamanho de um mosaico 436. Deste modo, o dispositivo eletrônico 302 pode

dividir o buffer de quadro 430 em mosaicos 436. Em outras implementações, o memória em chip 310 ou uma parte da memória em chip 310 pode ser grande o suficiente para acomodar todo o buffer de quadro 430 e nenhuma ladrilhagem 434 pode não ser realizada.

[0088] O dispositivo eletrônico 302 pode subdividir o buffer de quadro 438 430 e/ou mosaicos 436 em porções dimensionadas 440. Por exemplo, o buffer de quadro 430 e/ou mosaicos 436 pode ser subdivididos para se encaixarem em várias resoluções e/ou níveis de detalhe. No exemplo ilustrado na Figura 4, as porções dimensionadas 440 são de tamanho (n/c, m/c), em que c é um fator de escala. O fator de escala c pode variar e/ou pode ser selecionado com base na configuração.

[0089] O dispositivo eletrônico 302 (por exemplo, controlador de buffer de quadro não uniforme 312) pode acessar dinamicamente diferentes subconjuntos 442a-c do buffer de quadro 430. No exemplo, ilustrado na Figura 4, o dispositivo eletrônico 302 pode acessar dinamicamente o subconjunto de buffer A 442a, subconjunto de buffer B 442b e 442c subconjunto de buffer C. Deve ser notado que menos ou mais subconjuntos de buffer podem ser utilizados. Deve também notar-se que a totalidade ou apenas uma parte do buffer de quadro 430 pode ser ocupada por subconjuntos de buffer. Por exemplo, as outras porções não hachuradas do buffer de quadro podem ser utilizadas por um ou mais de outros subconjuntos.

[0090] Acesso dinâmico (por exemplo, a leitura e/ou gravação) dos diferentes subconjuntos de buffer de quadro (por exemplo, os subconjuntos de buffer 442a-c) pode permitir uma ou mais abordagens para prover um maior controle

e/ou eficiência em imagens de renderização. Em algumas abordagens, acesso dinâmico de diferentes subconjuntos de buffer de quadro pode permitir renderização de passagem única multi-LOD. Isso ocorre porque renderização de uma zona em um LOD não precisa ser concluída antes de renderização de outra zona em um LOD diferente poder ser iniciada. Nesta abordagem, um ou mais dos subconjuntos de buffer 442a-c podem corresponder a diferentes zonas da imagem. Por exemplo, subconjunto de buffer A 442a pode corresponder a uma zona com um LOD maior, subconjunto de buffer B 442b pode corresponder a uma zona com um LOD médio e subconjunto de buffer C 442c pode corresponder a uma zona com um LOD inferior. Por exemplo, o circuito VLIW 304 pode renderizar uma maior zona de LOD, que pode ser gravado no subconjunto de buffer A 442a, enquanto ao mesmo tempo ou sequencialmente renderiza uma zona de LOD médio, que pode ser gravado no subconjunto de buffer B 442b. Deve ser notado que as zonas de LOD diferentes podem ser processadas em qualquer ordem (por exemplo, a partir do LOD de mais alto para o mais baixo, na ordem inversa ou outra ordem). Adicionalmente ou em alternativa, acesso dinâmico de diferentes subconjuntos de buffer de quadro pode permitir o processamento de diferentes zonas em diferentes taxas (por exemplo, um subconjunto de buffer de quadro maior pode ser alocado para uma zona a ser processada mais rapidamente, enquanto um subconjunto de buffer de quadro menor pode ser alocado para outra zona a ser processada mais devagar).

[0091] Em algumas abordagens, acesso dinâmico de diferentes subconjuntos de buffer de quadro pode permitir processos de shader paralelos (por exemplo, sub-rotinas).

Por exemplo, processos de shader diferentes podem ser executados em paralelo, em que um processo de shader de acessa um subconjunto do buffer de quadro e um outro processo de shader acessa outro subconjunto do buffer de quadro. Adicionalmente ou em alternativa, o acesso dinâmico de diferentes subconjuntos de buffer de quadro pode permitir troca de sub-rotina de shader. Por exemplo, uma primeira sub-rotina de shader pode ser executada a qual acessa subconjunto de buffer A 442a. Enquanto a primeira sub-rotina de shader está em andamento, uma segunda sub-rotina de shader que acessa subconjunto de buffer B 442b pode terminar. A segunda sub-rotina de shader pode ser trocada por outra sub-rotina de shader (que pode acessar o subconjunto de buffer B 442b, por exemplo), enquanto a primeira sub-rotina de shader está em andamento. Isso pode permitir uma maior eficiência na utilização do espaço do buffer de quadro, em vez de ter que esperar que uma sub-rotina de shader seja concluída antes que outra possa ser iniciada.

[0092] Em algumas abordagens, acesso dinâmico de diferentes subconjuntos de buffer de quadro pode permitir a substituição de amostra. Por exemplo, o controlador de buffer de quadro não uniforme 312 pode trocar uma ou mais amostras de um pixel processados para uma ou mais amostras de outro pixel. Em algumas configurações, o circuito VLIW 304 pode executar antialiasing (por exemplo, antialiasing multiamostra (MSAA)). No desempenho antialiasing, pixels diferentes podem ter diferentes números de amostras. Por exemplo, um primeiro pixel (por exemplo, "fino") no subconjunto de buffer A 442a pode ter 4 amostras e pode utilizar shader de maior qualidade, enquanto um próximo

segundo (por exemplo, vizinho) pixel (por exemplo, "grosseiro") no subconjunto de buffer B 442b pode ter uma amostra e usar shader de qualidade inferior. Em vez de executar o processamento (por exemplo, o shader) sobre o segundo pixel, o controlador de buffer de quadro não uniforme 312 pode substituir uma amostra do primeiro pixel por uma amostra do segundo pixel. Isto pode evitar a realização de qualquer um dos processamentos para o segundo pixel. Adicionalmente ou em alternativa, o controlador de buffer de quadro não uniforme 312 pode executar substituição de amostra ao processar mapa de bit. Por exemplo, o controlador de buffer de quadro não uniforme 312 pode substituir uma amostra a partir de um nível mais elevado (em subconjunto de buffer A 442a, por exemplo) para uma amostra a partir de um nível inferior (em subconjunto de buffer B 442b, por exemplo). Isto pode evitar alguns ou processar em um ou mais níveis inferiores.

[0093] O controlador de buffer de quadro não uniforme 312 pode permitir o envio dinâmico de processamento de shader (por exemplo, sub-rotinas, núcleos, etc.), pode permitir a substituição do pixel de amostra e/ou pode prover um buffer de quadro multi-LOD. Tal como ilustrado na Figura 4, o buffer de quadro 430 pode armazenar dados de imagem que podem ser transmitidos como múltiplos alvos renderizados 444.

[0094] Listagem (1) ilustra um exemplo de pseudocódigo que ilustra uma abordagem para a funcionalidade de buffer de quadro não uniforme. Deve ser notado que GLSL é uma abreviação para Linguagem de Shading OpenGL e SSBO é uma abreviação para Shader Storage Buffer Object. Listagem

(1) ilustra a forma como várias zonas com diferentes níveis de detalhe

```

evitar main() { //computar buffer_subset_A usando

GLSL + texturas arbitrárias.

//imageStore()/buffer de cor/SSBO como mecanismo

de gravação.

}

evitar         main_lod_1(samplerTile/imageTile

red_square) {

//computar quadrado verde usando GLSL + texturas

arbitrárias

//e     possivelmente      textura(red_square,

uv)/imageRead()

}

...

evitar main_lod_n(samplerTile last_square) {

//"_lod_<n>()"     seria     acionado     após     a

renderização de nível 0 (buffer_subset_A).

//poderia ser simulado via um triângulo de tela

cheia e alterando porta de visualização.

//"_lod_<i>()" pode quer executar direto [0 a n

- 1] ou reverso [n - 1 a 0].

}

```

Listagem (1)

[0095] A Figura 5 é um diagrama de fluxo que ilustra uma configuração mais específica de um método 500 para renderizar múltiplos níveis de detalhe. O método 500 pode ser realizado pelo dispositivo eletrônico 302 descrito em ligação com a Figura 3.

[0096] O dispositivo eletrônico 302 pode obter 502 dados geométricos (por exemplo, dados de geometria 328). Isto pode ser conseguido como descrito em ligação com uma ou mais das Figuras 1-3. Por exemplo, o dispositivo eletrônico 302 pode carregar dados de geometria do armazenamento para a memória (por exemplo, a memória de sistema 314 e/ou memória em chip 310) e/ou pode receber dados de geometria a partir de outro dispositivo e carregar os dados de geometria para a memória (por exemplo, memória de sistema 314 e/ou memória em chip 310).

[0097] O dispositivo eletrônico 302 pode executar 504 rastreamento ocular. Isto pode ser conseguido como descrito em ligação com a Figura 3. Por exemplo, o dispositivo eletrônico 302 pode obter (por exemplo, capturar e/ou receber) uma ou mais imagens e pode determinar para onde o olhar de um usuário está direcionado (por exemplo, onde um usuário está olhando em uma tela e/ou uma imagem que está sendo apresentada no display) com base em uma ou mais imagens.

[0098] O dispositivo eletrônico 302 pode renderizar 506 diferentes níveis de detalhe de modo assíncrono baseado em um rastreamento ocular. Isto pode ser conseguido tal como descrito acima em ligação com uma ou mais das Figuras 1-3. Por exemplo, o dispositivo eletrônico 302 pode acessar de forma assíncrona a memória (por exemplo, memória de sistema 314 e/ou memória em chip 310) para renderizar diferentes níveis de detalhe com base no rastreamento ocular. Por exemplo, o dispositivo eletrônico 302 pode alterar um LOD para um conjunto de dados durante o processamento (em que o conjunto de dados inicialmente tinha

um LOD diferente, por exemplo) quando a zona para o conjunto de dados muda com base no rastreamento ocular. Em algumas configurações, o dispositivo eletrônico 302 pode aumentar o nível de detalhe para o conjunto de dados quando o olhar do usuário é dirigido para uma área da imagem que corresponde ao conjunto de dados. Adicionalmente ou em alternativa, o dispositivo eletrônico 302 pode diminuir o LOD para o conjunto de dados quando a direção do olhar de um usuário se afasta de uma área da imagem correspondente ao conjunto de dados.

[0099] Em algumas configurações, renderizar 506 diferentes níveis de detalhe de forma assíncrona pode incluir a realização de tecelagem de LOD dinâmico. Por exemplo, a memória (por exemplo, a memória de sistema 314 e/ou memória em chip 310) pode ser atualizada para indicar uma alteração no parâmetro (s) de tecelagem de LOD (por exemplo, um grau de tecelagem). O controlador de memória assíncrona 308 pode acessar o parâmetro de tecelagem de LOD atualizado para alterar a tecelagem de LOD de forma assíncrona.

[00100] O dispositivo eletrônico 302 pode acessar dinamicamente 508 diferentes subconjuntos de um buffer de quadro. Isto pode ser conseguido tal como descrito acima em ligação com uma ou mais das Figuras 1-4. Por exemplo, o dispositivo eletrônico 302 pode acessar pelo menos um pixel de uma primeira zona a uma taxa diferente de pelo menos um pixel de uma segunda zona. Adicionalmente ou em alternativa, o dispositivo eletrônico 302 pode permitir troca de sub-rotina de shader, quando o processamento de um primeiro pixel está em andamento e o processo de um segundo pixel é concluído. Adicionalmente ou em alternativa, o dispositivo

eletrônico 302 pode substituir uma primeira amostra processada de um primeiro pixel para uma segunda amostra de um segundo pixel para evitar o processamento da segunda amostra do segundo pixel.

[00101] O dispositivo eletrônico 302 pode apresentar 510 a imagem renderizada. Por exemplo, o dispositivo eletrônico 302 pode fluir para fora dados de imagem que foi renderizada 506 com diferentes níveis de detalhe de forma assíncrona. Em algumas configurações, os dados de imagem podem ser provados a um display integrado 332. Em outras configurações, os dados de imagem podem ser provados a um display remoto que se encontra em comunicação com o dispositivo eletrônico 302. Por exemplo, o dispositivo eletrônico 302 pode prover os dados de imagem para um display que é acoplado ao dispositivo eletrônico 302 (via VGA, DVI, HDMI, etc.)

[00102] A Figura 6 é um diagrama de fluxo que ilustra um exemplo do método 600 para renderizar foveado. Neste método, os dados de geometria são obtidos 602. Rastreamento ocular também é realizado 604. Uma camada grosseira é processada 606, uma camada média é renderizada 608 e uma camada fina é renderizada 610. Por exemplo, a camada fina pode ser renderizada 610 em uma imagem, onde o olhar de um usuário é direcionado. A camada média pode ser renderizada 608 em uma área maior, que se sobrepõe à área de camada fina. A camada grossa pode ser renderizada 606 em uma área ainda maior (por exemplo, a totalidade da imagem) que inclui a área de camada média e a área de camada fina. Por conseguinte, pode haver uma sobreposição significativa entre as camadas. A camada grossa, a camada média e a camada fina

podem ser fundidas 612 com antialiasing. A imagem resultante pode ser emitida 614 para o buffer de quadro.

[00103] Conforme pode ser observado, o método pode incluir 600 renderizar quantidades significativas de áreas que se sobrepõem. Por exemplo, a área de detalhe fino pode ser renderizada três vezes: uma vez na camada grossa, uma vez na camada média, e uma vez na camada fina. Isto pode ser ineficiente uma vez que executa múltiplas renderizações passando sobre os mesmos pixels.

[00104] A Figura 7 ilustra um exemplo de renderização foveada. Em particular, a Figura 7 ilustra um exemplo de uma cena para renderização foveada. A cena para renderização foveada inclui uma área de detalhe grosso 748, uma área de detalhe médio 750 e uma área de detalhe fino 752. Tal como descrito em conexão com a Figura 6, uma abordagem para renderização foveada inclui renderizar a camada grossa 754, tornando a camada média 756 e renderizar a camada fina 758. Em seguida, a fusão e mistura 760 pode ser realizada sobre a camada grossa 754, camada média 756 e a camada fina 758 para produzir uma imagem misturada final 762. Por exemplo, máscara de mistura A 764a entre a camada média 756 e camada grossa 754 pode ser usada para misturar a camada média 756 e a camada grossa 754. Além disso, máscara de mistura B 764b entre a camada média 756 e a camada fina 758 pode ser usada para misturar a camada média 756 e a camada fina 758. Como pode ser observado, esta abordagem renderiza os mesmos pixels em passagens múltiplas, conduzindo à ineficiência. Deve ser notado que uma ou mais das máscaras de mistura 764a-b podem prover uma mistura ponderada (por exemplo, gradual), em

algumas configurações, em que o peso da mistura aumenta das bordas exteriores das máscaras de mistura para área interior. Deve também ser notado que a camada grosseira 754 e/ou a imagem misturada final 762 estão ilustradas na Figura 7 como subconjuntos de toda a cena para conveniência. No entanto, a camada grosseira 754 e/ou a imagem misturada final 762 pode cobrir toda a cena.

[00105] A figura 8 é um diagrama de blocos que ilustra um exemplo de um dispositivo eletrônico 866 incluindo um circuito de palavra de instrução muito longa (VLIW) 868. Em particular, a Figura 8 ilustra um exemplo de uma arquitetura de processamento gráfico. Um ou mais aspectos da arquitetura descrita em ligação com a Figura 8 podem funcionar semelhantemente aos aspectos da arquitetura Nvidia. Esta arquitetura pode prover renderização de modo imediato (EVIR) com um projeto de largura de banda elevada com o custo de energia e área de matriz. Neste projeto, o cache 801 pode ser utilizado para reduzir a largura de banda (por exemplo, para evitar amostragem repetida, leitura e/ou gravação para a memória de sistema 805). Por exemplo, o cache 801 pode ser suficientemente grande para acomodar os dados durante todo um quadro de imagem. Deve ser notado que uma ou mais dos pipelines gráficos aqui descritos, podem ter um ou mais aspectos semelhantes a pipelines DirectX e/ou OpenGL e/ou interfaces de programação de aplicações (API). Pedido de Patente US Número de Publicação 2014/0347363 descreve alguns aspectos do processamento gráfico que podem ter semelhanças com o pipeline DirectX.

[00106] O dispositivo eletrônico 866 pode incluir um circuito VLIW 868 (por exemplo, GPU) e memória de sistema

805 (por exemplo, DRAM). O circuito VLIW 868 pode incluir um pipeline gráfico 870 e memória em chip 803. O pipeline gráfico 870 pode incluir um ou mais de um front-end (FEC) 872, um coletor de vértice (VF) 874, shader de vértice (VS) 876, shader de controle de tecelagem (TCS) 878, tessellator (TESS) 880 (por exemplo, máquina de tecelagem), shader de avaliação de tecelagem (TES) 882, shader de geometria (GS) 884, rasterizador (RAST) 886, shader de fragmento (FS) 890 e unidade de saída de renderização (ROP) 894. Muitos dos rótulos de elementos foram abreviados por conveniência. A memória em chip 803 pode incluir um buffer 896, memória de composição / decomposição (C/D) 898 e cache 801. Em algumas configurações, o buffer 896 pode ser e/ou incluir um buffer de textura, buffer de quadro e/ou outro bloco de memória em chip 910. A memória de sistema 805 pode incluir dados de comando (Cmd) 807, dados de vértice 809, dados de textura e dados de visualização de acesso desordenado 811 e dados de alvos renderizados 813.

[00107] A fim de renderizar a cena, o dispositivo eletrônico 866 pode carregar dados de comando 807 e dados de vértice 809 da memória de sistema 805 para o cache 801 na memória em chip 803. Os dados de vértice 809 podem indicar um ou mais pontos (por exemplo, os vértices), as linhas e/ou polígonos. Os dados de vértice 809 podem representar uma cena e/ou um ou mais objetos em uma cena.

[00108] A FE 872 pode prover uma interface entre o cache 801 e o pipeline gráfico 870 (por exemplo, VF 874). Por exemplo, o FE 872 pode obter dados a serem desformatados pelo VF 874 e/ou pode controlar o VF 874 em relação aos dados

(por exemplo, dados de vértice) que são recuperados a partir do cache 801.

[00109] O VF 874 pode obter dados de vértice do cache 801 para o pipeline gráfico 870. O VF 874 pode acessar o buffer 896. Por exemplo, o FV pode gravar dados no buffer 896. O VF 874 pode prover os dados de vértice para o VS 876. Adicionalmente ou em alternativa, o VS 876 pode recuperar dados de vértice do buffer 896.

[00110] O VS 876 pode transformar os dados de vértice em um espaço diferente. Por exemplo, o VS 876 pode transformar os dados de vértice a partir do espaço tridimensional (3D) em um espaço bidimensional (2D). O VS 876 pode prover os dados de vértice transformados para o TCS 878 e/ou pode armazenar dados de vértice transformados no buffer 896.