**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                              |                          |

|----------------------------------------------|--------------------------|

| (51) Int. Cl.<br><i>H01L 33/00</i> (2006.01) | (45) 공고일자<br>2006년11월02일 |

|                                              | (11) 등록번호<br>10-0641925  |

|                                              | (24) 등록일자<br>2006년10월26일 |

|                              |                              |

|------------------------------|------------------------------|

| (21) 출원번호<br>10-2000-0005424 | (65) 공개번호<br>10-2000-0076604 |

| (22) 출원일자<br>2000년02월03일     | (43) 공개일자<br>2000년12월26일     |

|                          |             |        |

|--------------------------|-------------|--------|

| (30) 우선권주장<br>09/245,435 | 1999년02월05일 | 미국(US) |

|--------------------------|-------------|--------|

|                                                                              |

|------------------------------------------------------------------------------|

| (73) 특허권자<br>필립스 루미리즈 라이팅 캠파니 엘엘씨<br>미국 캘리포니아주 95131-1008 산호세 웨스트 트림블 로드 370 |

|------------------------------------------------------------------------------|

|                                                   |

|---------------------------------------------------|

| (72) 발명자<br>코만캐리카터<br>미국캘리포니아주95117산호세밸리스퀘어레인3301 |

|---------------------------------------------------|

|                                      |

|--------------------------------------|

| 컨알스코트<br>미국캘리포니아주95134산호세버디그리스서클4226 |

|--------------------------------------|

|                                         |

|-----------------------------------------|

| 키쉬프레드에이2세<br>미국캘리포니아주95138산호세뉴게이트코트5815 |

|-----------------------------------------|

|                                      |

|--------------------------------------|

| 크라메스마이클<br>미국캘리포니아주94041마운틴뷰프론트레인550 |

|--------------------------------------|

|                                        |

|----------------------------------------|

| 너미코아토브이<br>미국로드아일랜드주02906프로비던스사전트애비뉴82 |

|----------------------------------------|

|                                        |

|----------------------------------------|

| 송윤-규<br>미국로드아일랜드주02906프로비던스메드웨이스트리트103 |

|----------------------------------------|

|                        |

|------------------------|

| (74) 대리인<br>김창세<br>장성구 |

|------------------------|

|                                                                    |                             |

|--------------------------------------------------------------------|-----------------------------|

| (56) 선행기술조사문현<br>JP06342958 A<br>JP11026870 A<br>* 심사관에 의하여 인용된 문현 | JP09237936 A<br>US5724376 A |

|--------------------------------------------------------------------|-----------------------------|

심사관 : 이진홍

**(54) 알루미늄 갈륨 인듐 질화물 구조 디바이스 및 그 제조 방법**

**요약**

수직 광학 경로, 예를 들면 고품질 미러를 구비하고 수직 공동 표면 발광 레이저나 공진 공동 발광 또는 검출 장치를 구비하는 발광 디바이스는 웨이퍼 본딩이나 금속 납땜 기술을 사용하여 이루어질 수 있다. 발광 영역은 유전체가 분포된 브래그 반사기(DBR)를 포함하는 하나 또는 두 반사기 스택을 삽입한다. 유전체 DBR은 발광 디바이스에 침착되거나 부착될 수 있다. GaP, GaAs, InP 또는 Si의 호스트 스택은 유전체 DBR 중 하나에 부착된다. 전기 접점은 발광 디바이스에 부가된다.

## 대표도

도 2

## 명세서

### 도면의 간단한 설명

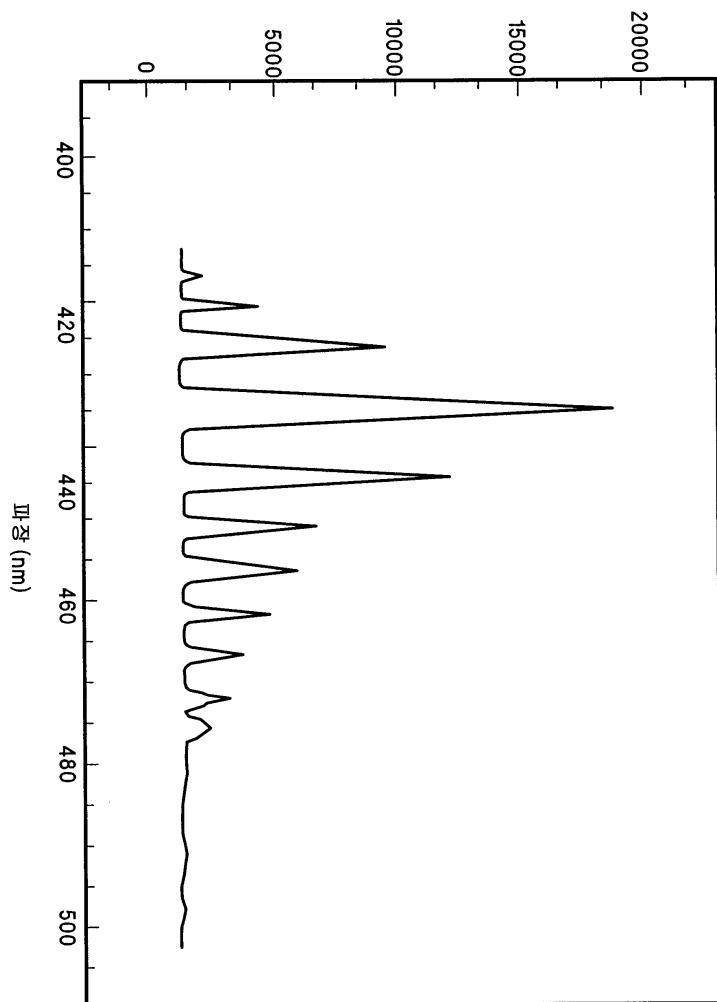

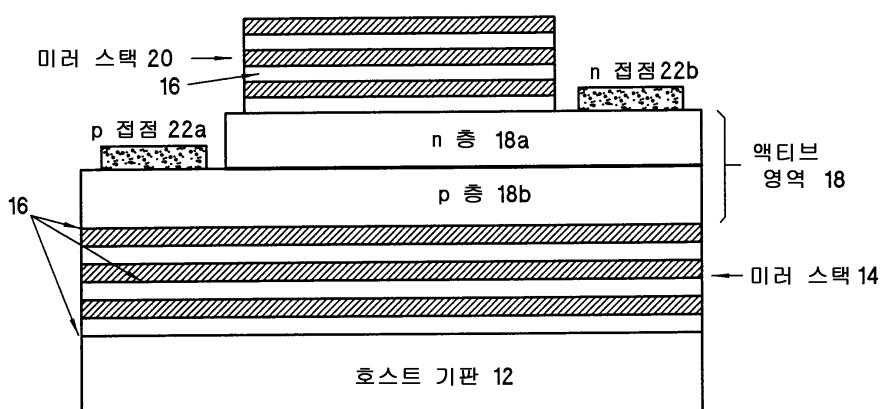

도 1은 AlN/GaN과 Al<sub>.30</sub>Ga<sub>.70</sub>N/GaN DBR에 대한 이론적 반사율 대 과장을 예시한 도면.

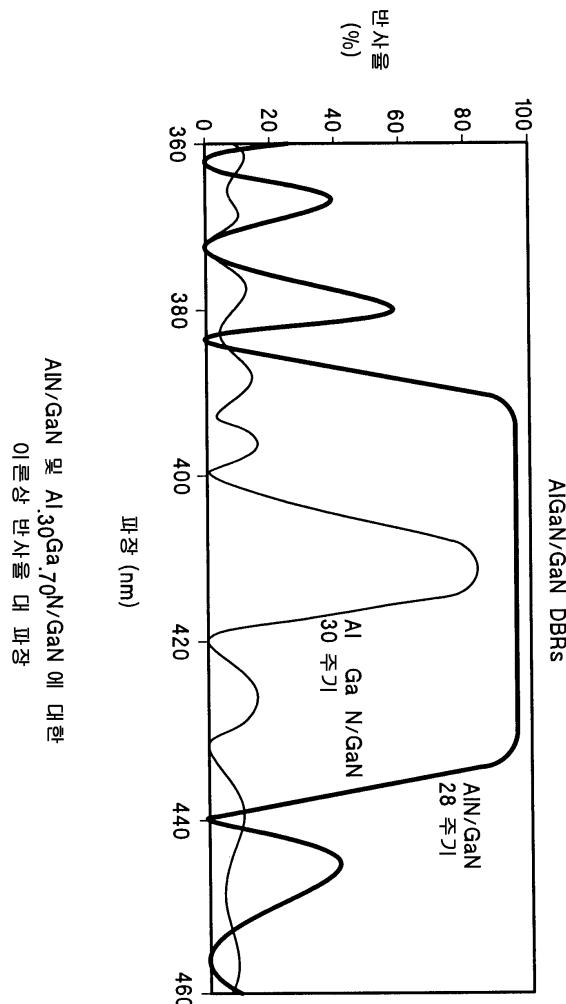

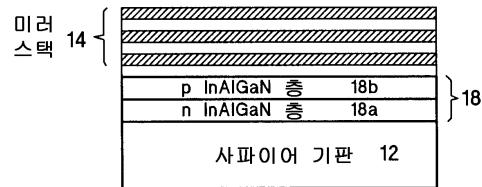

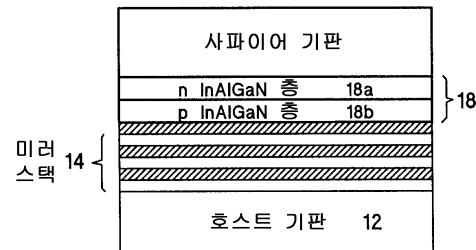

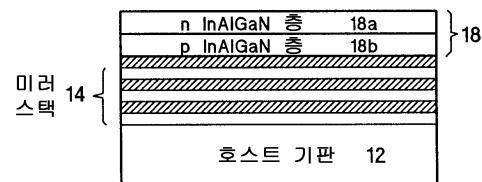

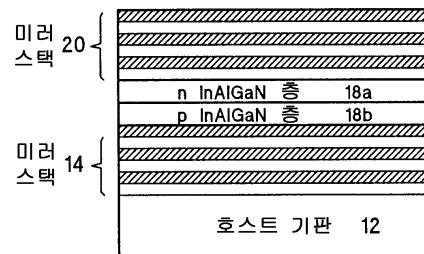

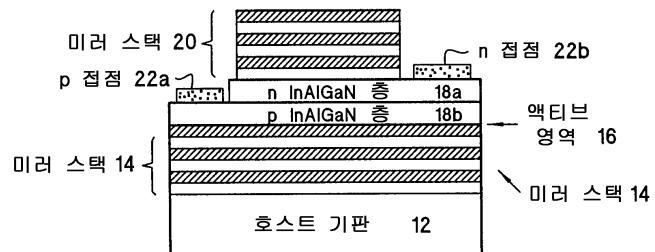

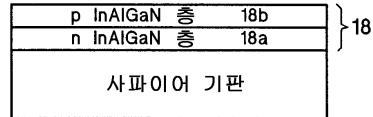

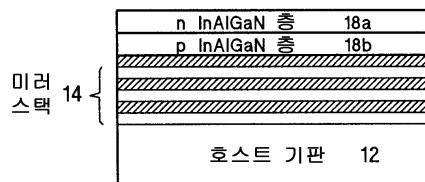

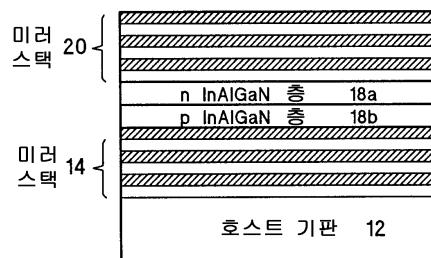

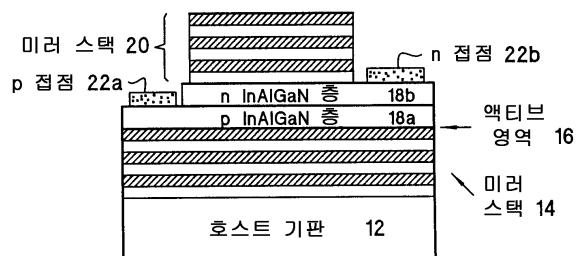

도 2는 본 발명의 바람직한 실시예를 예시하는 도면.

도 3a-f는 본 발명에 대응하는 플로차트를 도시하는 도면.

도 4a-f는 본 발명에 대응하는 대안적 플로차트를 도시하는 도면.

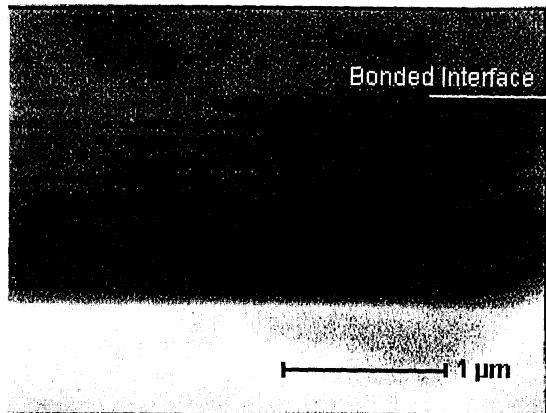

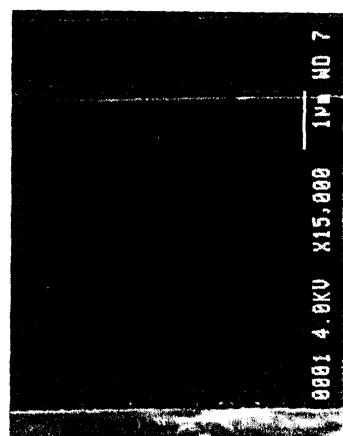

도 5는 GaN/Al<sub>2</sub>O<sub>3</sub> 구조와 GaP 호스트 기판상에 침착된 D-DBR 사이에 직접 웨이퍼 본딩된 인터페이스의 스캐닝 전자 현미경(SEM; scanning electron microscope) 단면 영상을 도시하는 도면.

도 6은 호스트 기판에 금속 본딩되고, 침착된 D-DBR을 가진 액티브 영역의 SEM 단면 – 기판은 제거되었고, 제 2 D-DBR은 제 1 D-DBR과 반대쪽의 Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N 액티브 영역의 측면에 침착됨 – 을 나타낸 도면.

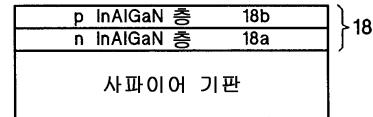

도 7은 도 6에서 설명된 디바이스로부터 400nm-500nm의 발광 스펙트럼을 – 형태상의 피크는 수직 공동 구조를 설명함 – 도시한 도면.

### 도면의 주요 부분에 대한 부호의 설명

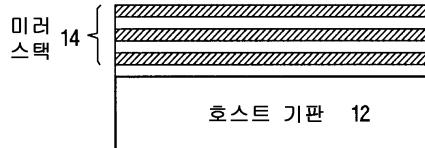

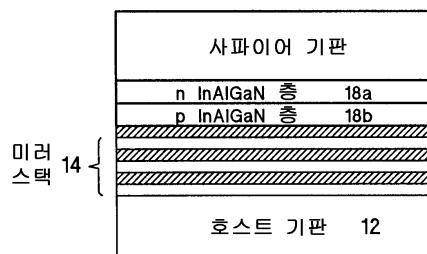

12 : 호스트 기판 14, 20: 미러 스택

16 : 본딩된 인터페이스 18 : 액티브 영역

## 발명의 상세한 설명

### 발명의 목적

### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 미국 DARPA(Defense Advanced Research Projects Agency)가 협정 제 MDA972-96-3-0014에 의거 지불한 정부 지원으로 이루어 졌다. 미 연방 정부는 본 발명의 권리를 소유한다.

본 발명은 발광 분야에 관한 것으로, 구체적으로는, Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N 디바이스의 양측면에 고품질 반사면을 제공하는 것에 관한 것이다.

수직 공동 광전자 구조는 액티브 영역으로 구성되고, 액티브 영역은 도핑되거나, 도핑되지 않거나 또는 p-n 접합을 포함하는 감금층(confining layers) 사이에 삽입된 발광층으로 형성된다. 또한, 그 구조는 발광층에 수직한 방향으로 파브리-페로 공동(Fabry-Perot cavity)을 형성하는 적어도 하나의 반사 미러를 포함한다. GaN/Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N/Al<sub>x</sub>Ga<sub>1-x</sub>N

( $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$ 에서  $x+y+z=1$ 이고,  $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 에서  $x \leq 1$ 이다) 재료 시스템에 수직 공동 광전자 구조를 제조하는 것은 다른 III-V족 재료 시스템과는 별도의 난제를 내포한다.  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조를 높은 광학적 품질로 성장시키는 것은 어렵다. 전류 스프레딩(current spreading)은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  디바이스에 대한 주 관심사이다. p형 재료에서의 측면 전류 스프레딩은 n형 재료에서의 측면 전류 스프레딩보다 30배까지 낮다. 더욱이, 디바이스는 최적한 방열(heat sinking)을 위해 접합부가 하향(junction down)으로 설치되어야 하기 때문에, 열 전도도가 낮은 대부분의 기판에서는 디바이스 설계가 복잡하게 된다.

예를 들면, 수직 공동 표면 발광 레이저(VCSEL; vertical cavity surface emitting laser)와 같은 하나의 수직 공동 광전자 구조는 예를 들면, 99.5%의 반사율과 같은 고품질 미러를 필요로 한다. 고품질 미러를 얻는 한가지 방법은 반도체 성장 기술에 의한 것이다. VCSEL에 적합한 분포 브래그 반사기(DBR; distributed Bragg reflectors)에 필요한 높은 반사율(>99%)에 도달하기 위해서는, 크래킹(cracking) 및 전기 전도도를 포함하는, 반도체  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  DBR의 성장에 대해 심각한 재료 문제가 존재한다. 이들 미러들은 교변하는 인듐 알루미늄 갈륨 질화물 조성물( $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}/\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$ )의 많은 주기/층을 필요로 한다. 유전체 DBR(D-DBR)은, 반도체 DBR과는 대조적으로,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  시스템에 의해 미치는 스펙트럼 범위에서 99% 이상의 반사율로 만들어지기가 비교적 쉽다. 이들 미러는 대체로 증발 또는 스퍼터(sputter) 기술에 의해 침착되지만, 분자 빔 에피택셜(MBE; molecular beam epitaxial)과 금속 유기 화학 증착(MOCVD; metal-organic chemical vapor deposition)이 사용될 수도 있다. 그러나, 성장 기판이 제거되지 않으면, 액티브 영역의 한 측면만이 D-DBR 침착을 위해 액세스될 수 있다.  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역의 양측면상에 D-DBR을 본딩(bonding)하고/본딩하거나 침착할 수 있었다면  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  수직 공동 광전자 구조를 생성하는 것이 상당히 용이해졌을 것이다.

웨이퍼 본딩(wafer bonding)은 두 기본 카테고리 즉, 직접 웨이퍼 본딩과 금속 웨이퍼 본딩으로 나누어질 수 있다. 직접 웨이퍼 본딩에서, 두 웨이퍼는 본딩 인터페이스에서의 질량 수송(mass transport)을 통해 서로 융착된다. 직접 웨이퍼 본딩은 반도체, 산화물 및 유전체 재료를 임의 조합한 것 중에서 실행될 수 있다. 직접 웨이퍼 본딩은 보통 고온(>400°C)에서 단축(uniaxial) 스트레스 하에서 실행된다. 한가지 적합한 직접 웨이퍼 본딩 기술은 키쉬(Kish)등에 의한 미국 특허 제5,502,316에서 기술된다. 금속 웨이퍼 본딩에서는, 금속 층이 두 본딩 기판 사이에 침착되어 두 본딩 기판을 부착시킨다. 응용 물리학회지, 1990년도 56권 2419-2421페이지, 앤블로노비치 등이 기술한 금속 본딩(metallic bonding, disclosed by yablonovitch, et al. in Applied Physics Letters, vol. 56, pp. 2419-2421, 1990)의 한 예로는 디바이스를 기판에 뒤집어 부착하기 위해 마이크로 산업 및 광전자 산업에서 사용되는 기술인 플립 칩 본딩(flip-chip bonding)이 있다. 플립 칩 본딩은 디바이스의 방열을 향상시키는데 사용되기 때문에, 기판을 제거하는 것은 디바이스 구조에 달려있으며, 기준의 금속 본딩 층의 유일한 요건은 금속 본딩 층이 전기 전도성이 있고 기계적으로 강해야 한다는 것이다.

응용 물리학회지 1994년도 64권 12호 1463-1465페이지,"저 임계치, 웨이퍼 융착 장파장 수직 공동 레이저"에서 뉴들리 등(In "Low threshold, wafer fused long wavelength vertical cavity lasers", Applied Physics Letters, Vol. 64, No. 12, 1994, pp 1463-1465, Dudley, et al.)은  $\text{AlAs}/\text{GaAs}$  반도체 DBR을 수직 공동 구조의 한 측면에 직접 웨이퍼 본딩하는 것을 개시하고 있으며, 반면에 IEEE 포토닉스 기술지 1995년 11월 7권 11호의 "1.54  $\mu\text{m}$  수직 공동 레이저의 실온 연속 웨이브 동작"에서 바비 등(in "Room-Temperature Continuous-Wave Operation of 1.54- $\mu\text{m}$  Vertical-Cavity Lasers," IEEE Photonics Technology Letters, Vol. 7, No. 11, November 1995, Babic, et al.)은  $\text{AlAs}/\text{GaAs}$  사이의 높은 굴절률 변화를 이용하기 위하여  $\text{InGaAsP}$  VCSEL의 양측면에 직접 웨이퍼 본딩된 반도체 DBR을 개시하고 있다. 설명되는 바와 같이,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$ 에 D-DBR을 웨이퍼 본딩하는 것은 반도체와 반도체를 웨이퍼 본딩하는 것보다 훨씬 더 복잡하고, 당해 기술에서 이전에 알려져 있지 않았다.

IEEE 포토닉스 기술지, 1994년 12월 5권 12호의 "변형 보상 다중 양자 웨이퍼 사용하여 GaAs 기판에 직접 본딩된 장파장 수직 공동 레이저"에서 추아 등(In "Dielectrically-bonded Long Wavelength Vertical Cavity Laser on GaAs Substrate Using Strain-Compensated Multiple Quantum Wells." IEEE Photonics Technology Letters, Vol.5, No.12, December 1994, Chua et al.)은 스핀 온(spin-on) 유리 층에 의해  $\text{InGaAsP}$  레이저에 부착된  $\text{AlAs}/\text{GaAs}$  반도체 DBR을 개시한다. 스핀 온 유리의 정확한 두께를 제어하기 어렵고 따라서 VCSEL 공동에 필요한 정밀한 층 제어가 이루어지지 못하기 때문에, VCSEL에 있어서 스핀 온 유리(spin on glass)는 액티브 층과 DBR 사이에서의 본딩에 적합한 재료가 아니다. 더욱이, 유리의 특성이 비균질성이기 때문에, 공동에서 산란과 다른 손실을 유발시킨다.

예를 들면, >99%의 VCESEL에 적합한 반사율을 갖는 반도체 DBR 미러의  $\text{Al}_x\text{Ga}_{1-x}\text{N}/\text{GaN}$  페어의 광학적 미러 성장은 어렵다. 도 1을 참조하면, 반사율의 이론적 계산에 따르면, 필요한 높은 반사율을 얻기 위해서는, 높은 지수의 콘트라스트가 필요하며, 높은 지수의 콘트라스트는 낮은 지수의  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  층의 Al 조성물을 증가시키고/증가시키거나, 보다 많은 층

주기를 증가시킴으로써 (재료 특성은 1997년 질화물 반도체 리서치의 MRS 인터넷 저널 2(22), 앰바처(Ambacher) 등에 의해 얻음(material properties taken from Ambacher et al., MRS Internet Journal of Nitride Semiconductor Research, 2(22) 1997)) 제공될 수 있을 뿐이다. 상기 방식 모두 심각한 난제를 발생시킨다. 전류가 DBR 층을 통하여 전도될 것이면, DBR이 전도성인 것이 중요하다. 충분한 전도성을 띠도록,  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  층은 적절히 도핑되어야 한다. Al 조성물이 Si(n형) 도핑에 대해 약 50% 이하로 감소되지 않고 Mg(p형) 도핑에 대해 약 20% 이하로 감소되지 않으면 전기 전도성은 불충분하다. 그러나, 도 1에 도시된 바와 같이, 보다 낮은 Al 조성물 층을 사용하여 충분한 반사율을 얻는데 필요한 층 주기의 수는 전체 두께가 두꺼운  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  재료를 필요로 하고, 그에 따라 (AlN과 GaN 사이의 비교적 큰 격자 부정합(lattice mismatch)으로 인해) 에피택셜 층 크래킹(cracking)의 리스크(risk)를 증가시키고, 조성물의 제어를 감소시킨다. 실제로, 도 1의  $\text{Al}_{.30}\text{Ga}_{.70}\text{N}/\text{GaN}$  스택은 이미  $\sim 2.5\mu\text{m}$  두께이고, VCSEL에 충분할 정도의 반사율을 전혀 갖지 않는다. 따라서, 상기 층 페어를 기반으로 한 높은 반사율의 DBR은  $2.5\mu\text{m}$  보다 훨씬 더 큰 전체 두께를 필요로 하며, AlN과 GaN 성장 조건과 재료 특성간에 부정합이 존재할 경우에는, 신뢰할 수 있게 성장하는 것이 어려울 것이다. 층이 도핑되지 않을 경우 크래킹이 큰 문제점은 아닐지라도, 높은 반사율의 DBR을 성장시키는데 있어서 조성물의 제어와 AlN/GaN 성장 온도는 여전히 큰 난제이다. 따라서, DBR이 전류를 전도시킬 필요가 없는 응용에서 조차도,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  재료 시스템에서 반사율이  $>99\%$ 인 반도체 미러 스택은 논증되지 않았다. 이러한 이유로 유전체 기반 DBR 미러가 바람직하다.

### 발명이 이루고자 하는 기술적 과제

예를 들면, 유전체 분포 브래그 반사기(D-DBR; dielectirc distributed Bragg reflector) 또는 복합 D-DBR/반도체 DBR과 같은 하나 이상의 미러 스택이  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역과 호스트 기판 사이에 삽입된다. 웨이퍼 본드 인터페이스는 호스트 기판과 액티브 영역 사이의 임의 위치에 배치된다. 선택적 중간 본딩 층은 웨이퍼 본드 인터페이스에 인접하여 웨이퍼 본드 인터페이스에서의 변형과 열 계수 부정합을 조절한다. 선택적 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 인접하게 배치된다. 호스트 기판이나 중간 본딩 층은 컴플라이언스(compliance)를 위해 선택된다.

상술한 발명의 한 실시예는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 인접하여 배치된 웨이퍼 본드 인터페이스를 갖는 디바이스로 구성되며,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역은 예를 들면,  $\text{Al}_2\text{O}_3$ 와 같은 희생 기판 위에 제조된다. 호스트 기판에 부착된 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 직접 웨이퍼 본딩된다. 다음, 희생 기판이 제거된다. 선택적 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역의 상단에 부착된다. 부착 기술은 본딩, 침착 및 성장을 포함한다. 전기 접점은 n형 층과 p형 층에 부가된다.

호스트 기판에 인접 배치된 웨이퍼 본드 인터페이스를 갖는 대안적 실시예의 경우, 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역의 상단에 부착된다. 직접 웨이퍼 본딩이 사용되면, 적절한 기계적 특성을 갖도록 선택된 호스트 기판은 미러 스택에 웨이퍼 본딩된다. 대안적으로, 금속 본딩은 미러 스택에 호스트 기판을 본딩하는데 사용될 수 있다. 희생 기판이 제거된다. 선택적 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역의 상부에 부착된다. 전기 접점은 n형 층과 p형 층에 부가된다. 원하는 특성을 얻도록 직접 웨이퍼 본딩하는 경우에 호스트 기판의 선택은 중요하다. 추가의 실시예는 DBR 내에 웨이퍼 본드 인터페이스를 배치하는 것을 포함한다.

### 발명의 구성 및 작용

유전체 분포 브래그 반사기(D-DBR)는 저손실 유전체의 적층 페어로 구성되고, 페어 재료 중 하나는 낮은 굴절률을 가지며, 다른 하나는 높은 굴절률을 갖는다. 몇 가지 가능한 유전체 DBR 미러는 티타늄 산화물( $\text{TiO}_2$ ), 지르코늄 산화물( $\text{ZrO}_2$ ), 탄탈륨 산화물( $\text{Ta}_2\text{O}_5$ ) 또는 하프늄 산화물( $\text{HfO}_2$ )과 실리콘 이산화물( $\text{SiO}_2$ )의 페어를 이룬 층을 기반으로 하며, 예를 들면,  $>99.5\%$ 의 청색 수직 공동 표면 발광 레이저(VCSEL; vertical cavity surface emitting laser)에 필요한 높은 반사율이나, 예를 들면  $\sim 60\%$  또는 그 이상의 공진 공동 발광 디바이스(RCLED; resonant cavity light emitting device)를 얻는데 필요한 높은 반사율을 얻을 수 있다.  $\text{SiO}_2/\text{HfO}_2$  적층 페어는 350nm-500nm의 파장 범위에서 99%를 초과하는 반사율을 갖는 미러 스택을 생성하는데 사용될 수 있기 때문에 특히 중요하다.  $\text{SiO}_2$ 와  $\text{HfO}_2$ 의 교번층으로 만들어진 D-DBR은 최고 1050°C까지 기계적으로 안정되어, 후속 처리에 융통성을 제공하는 것으로 알려져 있다.

바람직한 실시예는 도 2에 도시된다. 도 2에서, 예를 들면, 높은 반사율의 DBR과 같은 제 1 미러 스택(14)은 적절한 기판에 부착된다. 미러 스택(14)은 다음의 재료 즉, 유전체, 반도체 및 금속 중 하나 이상의 재료로 구성된다. 제 1 미러 스택(14)은 희생 기판상에 성장한  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역(18)내의 상부 p층(18b)에 웨이퍼 본딩된다.  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  수직 공동

광전자 구조(18)는 원하는 파장에서 높은 이득을 얻도록 설계되었다. 웨이퍼 본딩된 인터페이스(16)는 매우 낮은 산란(scattering)을 가진 우수한 광학 품질로 이루어져야 한다. 웨이퍼 본딩된 인터페이스(16)는 선택적 중간 본딩 층(도시되지 않음)을 포함할 수 있다. 예를 들면, D-DBR(도 2에 도시됨)과 같은 선택적 제 2 미러 스택(20)은 제 1 미러 스택(14)의 마주보는 측면상의  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  수직 공동 광전자 구조(18)에 부착된다. 선택적 제 2 미러 스택(20)과  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역(18)의 n형 층(18a) 및 p형 층(18b)은 저항성 접촉을 위한 영역을 제공하도록 패턴화되고 예칭될 수 있다. VCSEL의 경우, 미러는 >99%의 매우 높은 반사율을 가져야 한다. RCLED의 경우, 미러의 반사율 요건은 완화된다(>60%).

대안적 방법은 미러 스택(14)이  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부착되는 것이다. 웨이퍼 본드 인터페이스(16)는 미러 스택(14)과 호스트 기판(12) 사이에 있다. 이러한 구조는 선택적 제 2 미러 스택(20)을 가질 수도 있다. 처음 두 가지 중 어느 하나와 관련하여 사용될 또 다른 방법은 미러 스택 중 하나 또는 둘 모두의 중간에 직접 웨이퍼 본드를 갖는 것이다. 웨이퍼 본딩된 인터페이스(16)의 여러 가지 가능한 위치가 도 2에 도시된다.

전류 및 광학적 감금(current and optical confinement)을 개선하여 레이저 발생 임계치를 감소시키거나 디바이스 효율을 개선하도록 예칭되고/되거나 산화될 수 있는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  층을 삽입함으로써 n형 액티브 영역 재료 또는 p형 액티브 영역 재료에서 전류 제한이 이루어질 수 있다. 상기 층을 결합하는 것은 D-DBR 및/또는 도핑되지 않은 반도체 DBR이 사용될 때 중요한데, 이는 전류가 이들을 통해 전도되지 않기 때문이다. 공동은 적절히 낮은 순방향 전압을 얻도록 접촉 층의 필요로 하는 두께에 따라 단일 공동이나 다중 공동이 될 수 있다. 상기 구조에 관한 많은 변형이 가능하다. p형 재료와 n형 재료가 교환되는 유사한 구조가 생성될 수 있다.

도 4a-4f는 본 발명의 실시예에 대응하는 플로차트를 도시한 것이다. 도 4a에서,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역은, 예를 들면,  $\text{Al}_2\text{O}_3$ 와 같은 희생 기판상에 제조된다. 도 4b에서, 제 1 미러 스택은 호스트 기판에 부착된다. 부착 기술은 본딩, 침착 및 성장을 포함한다. 도 4c에서, 제 1 미러 스택은 웨이퍼 본딩을 통하여  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부착된다. VCSEL의 경우, 낮은 광학 손실을 갖는것이 중요하기 때문에 직접 웨이퍼 본딩이 사용되어야 한다. 도 4d에서, 희생 기판이 제거된다. 도 4e에서, 선택적 제 2 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역의 상단에 부착된다. 도 4f에서, 전기적 접점이 선택적 제 2 미러 스택이나  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부가된다. 디바이스 영역을 정의하고 접촉 층을 노출시키도록 패턴화하는 것은 처리 플로우에서 실행될 수도 있다.

도 3a-3f는 다른 처리 플로차트를 도시한 것이다. 도 3a에서,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역은 희생 기판 위에 성장된다. 도 3b에서, 제 1 미러 스택은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부착된다. 도 3c에서, 호스트 기판은 직접 웨이퍼 본딩 또는 금속 본딩을 통하여 제 1 미러 스택에 부착된다. 웨이퍼 본드가 광학 공동의 외부에 있기 때문에, 웨이퍼 본드로 인한 손실은 덜 중요하다. 도 3d에서, 희생 기판이 제거된다. 도 3e에서, 선택적 제 2 미러 스택이  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부착된다. 도 3f에서, 전기 접점이 선택적 제 2 미러 스택이나  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 부가된다. 디바이스 영역을 정의하고 접촉 층을 노출시키도록 패턴화하는 것은 처리 플로우에서 실행될 수도 있다.

직접 웨이퍼 본딩에 적합한 호스트 기판의 선택은 중요하며, 다음의 여러 가지 특성 즉, 질량 수송, 캠플라이언스, 스트레스/변형 완화에 의해 영향을 받는다. 호스트 기판은 갈륨 인화물(GaP), 갈륨 비소(GaAs), 인듐 인화물(InP) 또는 실리콘(Si)을 포함하는 그룹으로부터 선택될 수 있다. Si의 경우, 기판의 바람직한 두께는 1000Å과 50 $\mu\text{m}$  사이이다.

질량 수송은 직접 웨이퍼 본딩에서 중요한 역할을 담당한다. 표준 III-V족과 III-V족 직접 웨이퍼 본딩이나, III-V족과 유전체 본딩에서, 하나 이상의 표면은 층의 품질을 보존하기에 충분할 정도의 저온에서 질량 수송을 나타낸다. 대조적으로,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$ 과 대부분의 유전체 재료는 In을 다량 함유한  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 층의 무결성을 유지하는 것과 일치하는 온도에서 (<1000°C) 질량 수송을 나타내지 못한다. 하나 또는 두 본딩 재료의 질량 수송이 결여되면 웨이퍼 부착을 방해한다. 이에 대한 모델로는 두 재료가 본딩 온도에서 질량 수송을 나타낼 때 두 재료의 본드가 인터페이스에 걸쳐서 가장 강한 본드로 재배열될 수 있는 것이 있다. 단지 한 재료만이 질량 수송을 나타낼 경우, 이러한 한 재료만의 본드는 다른 재료의 표면 본드와 정렬될 수 있다. 이러한 상황에서는 높은 기계적 강도의 웨이퍼 본드를 형성하는 것이 어렵다.

캠플라이언스는 변형과 스트레스를 조절하기 위해 원자 스케일이나 거시적인 스케일로 형상을 변경시키는 재료의 기능이다. 본 발명의 목적을 위하여, 캠플라이언스는 본딩 온도보다 낮은 용융점을 갖는 재료에 의해서나, 재료가 본딩 온도보다 낮은 연성/부서지기 쉬운 변이를 갖거나, 기판이 ~50 $\mu\text{m}$ 보다 얕을 때 성취되도록 정의된다.

GaP, GaAs 및 InP의 기판을 위한 표준 III-V족 웨이퍼 본딩은, 두 기판이 캠플라이언스를 갖게 되는 대개 400°C-1000°C의 온도에서 실행된다. 하나 이상의 본딩 재료의 캠플라이언스는, 재료가 초소형 스케일이나 거시적인 스케일에서 고유의 표면 거칠기를 갖고/갖거나 평탄성이 약하기 때문에 웨이퍼 본딩에 필수적이다. 1000°C의 온도, 및 N<sub>2</sub> 환경에서 20분 동안 어닐링된 Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N 구조는 약 20%의 PL 강도의 약화를 초래한다. 따라서, 본딩 온도를 1000°C 이하로 유지시키는 것이 바람직하다. Al<sub>2</sub>O<sub>3</sub> 기판상에서 성장한 GaN 기반 재료는 1000°C 이하의 본딩 온도에서 캠플라이언스를 갖지 못한다. 큰 밴드 갭 반도체용의 높은 반사율의 D-DBR을 제조하는데 사용되는 유전체 재료는 대체로 1000°C 이하에서 캠플라이언스를 갖지 못한다. 따라서, 본딩/지지 기판 및/또는 중간 본딩은 이 온도에서 캠플라이언스를 갖는 것이 중요하다.

용융점은 재료의 캠플라이언스를 결정하는 한 가지 특성이다. 예를 들면, 다음의 재료 즉, GaAs(Tm=1510K), GaP (Tm=1750K) 및 InP(Tm=1330K)의 경우, 캠플라이언스의 상대적 순서는 InP, GaAs, GaP로써, InP가 가장 큰 캠플라이언스를 가짐을 알 수 있다. 재료는 대개 용융점 이하에서 연성/부서지기 쉬운 변이를 겪는다. 고온에서의 이들 재료의 캠플라이언스는 구성 요소중 하나의 흡수 제거와 평형을 이루어야 한다. InP가 1000°C에서 캠플라이언스를 갖는다 할지라도, 인의 흡수 제거 때문에 그 재료는 그 온도에서 심각하게 분해된다. 그러한 재료와의 본딩은, 본딩 동안 대기압에서의 흡수 제거 온도의 약 2배보다 낮은 온도로 제한되어야 한다. 따라서, 재료의 선택은 필요로 하는 캠플라이언스 및 본딩 온도와 모두 양립해야 한다.

매우 얇은 기판이 캠플라이언스를 가질 수 있다. 예를 들면, <50μm의 얇은 실리콘은, 기판이 얇을 경우, 큰 곡률 반경에서 조차, 스트레스가 적기 때문에 캠플라이언스를 갖게 된다. 상기 기술은, 예를 들면, 실리콘 또는 Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N과 같은 높은 분열 경도(11270 N/mm<sup>2</sup>)를 갖는 재료에 대해 잘 작용한다. 그러나, 예를 들면, GaAs와 같이 낮은 분열 경도(2500 N/mm<sup>2</sup>)를 갖는 재료는 처리할 때 쉽게 분열될 수 있다. 두께가 >50μm인 실리콘의 경우, 작은 곡률 반경조차도 재료에서 높은 스트레스를 일으켜서 재료가 분열되게 한다. 기판 후보 가능성성이 있는 다른 재료에서도 마찬가지이다.

스트레스와 변형 완화는 Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N와 대부분의 다른 적합한 지지 기판 재료 사이의 열 팽창 계수 부정합뿐만 아니라 Al<sub>2</sub>O<sub>3</sub>에 성장한 GaN에서의 높은 부정합 변형에 의해 악화된다. 웨이퍼 본딩되는 다른 반도체 재료와는 대조적으로, Al<sub>x</sub>Ga<sub>y</sub>In<sub>z</sub>N과 다른 반도체 재료간의 CTE 부정합은 더 크며, 스트레스는 부르자이트(wuzite) 재료의 a 및 c 평면을 따르는 서로 다른 CTE 부정합에 의해 더욱 악화된다. 상이한 기판(GaAs CTE=5.8, GaP CTE=6.8, InP=4.5x10<sup>-6</sup>)에 본딩되는 GaN(CTE=5.59, a 평면/3.17x10<sup>-6</sup>, c 평면/°C) 웨이퍼에서의 스트레스는 호스트 기판의 TCE 부정합이 두 GaN 평면을 밀접하게 정합시켜야 하기 때문에 국부적인 스트레스 완화를 필요로 한다. 이러한 스트레스는 캠플라이언스 재료, 또는 본딩 온도에 있어서 본딩 인터페이스에서 연성이거나 액체 상태인 중간 본딩 층에서 조정되거나, 또는 예를 들면, 하나 이상의 본딩된 인터페이스의 패턴화와 같은 국부적 변형 완화를 제공함으로써 조정될 수 있다. 중간 본딩 층은 할로겐화물(예를 들면, CaF<sub>2</sub>), ZnO, 인듐(In), 주석(Sn), 크롬(Cr), 금(Au) 니켈(Ni), 구리(Cu) 및 II-VI족 재료를 함유한 합금 및 유전체를 포함하는 그룹으로부터 선택된다.

전류 스프레딩은 GaN 기판 디바이스에 대한 다른 주요 관심사이다. p형 재료에 있어서의 측면 전류 스프레딩은 n형 재료에서의 측면 전류 스프레딩보다 ~30x 적다. 액티브 층의 양측면에 높은 반사율의 미러를 형성하는 것은 양호한 공동을 위해 필요한 반면, D-DBR의 절연 특성으로 인해 측면 p 층 전류 스프레딩의 문제점은 악화된다. p 층에서의 전류 스프레딩을 개선하는 한 가지 방법은 전도성 투명 반도체와 유전체 스택의 복합 DBR을 만드는 것이다. 스택의 반도체 부분은, p 층에 두께를 더함으로써 전류 스프레딩을 향상시키고, 유전체 스택은 전체 미러 반사율이 99% 이상이 되도록 낮은 반도체 반사율을 향상시킨다. 이와 동일한 절차가 n형 미러에 적용될 수 있지만, 그것은 n형 층의 높은 전도율 때문에 덜 중요하다.

전류 제한 층을 부가하면 전류만을 공동으로 지향시킴으로서 전류 스프레딩을 더욱 향상시킬 것이며, VCSEL에 필수적이다. 이는 복합 반도체/유전체 DBR을 가지고 또는 복합 반도체/유전체 DBR 없이 수직 공동 광전자 구조에 적용될 수 있고, 복합 미러의 반도체 부분에 결합될 수 있다. 전류 제한 층이 감금층의 p 층과 n 층 모두에 포함될 수 있지만, 낮은 전도율로 인해 p 감금층에서 가장 효과적이다.

액티브 영역의 양면에 D-DBR이 부착될 경우 지지 기판이 필요한데, 이는 원래의 호스트 기판이 제거되어야 하기 때문이다. 대개 성장 기판으로 사용되는 사파이어 기판을 제거하는 여러 가지 방법이 있다. 아래에 개요가 설명된 방법은 사파이어 외의 다른 재료일 수도 있는 성장 기판을 제거하는데 사용될 수 있는 기술의 서브셋일 뿐이다.

레이저 용융에 있어서, 옹 등과 켈리 등(Wong, et al. and Kelley, et al.)이 개시한 기술에서는, 사파이어 기판에 대해 투과되지만 기판에 인접한 반도체 층에 대해서는 투과되지 않은 파장을 갖는 레이저가 구조체의 후방(사파이어 측면)을 조사한다. 레이저 에너지는 인접 반도체 층을 침투할 수 없다. 레이저 에너지가 충분할 경우, 사파이어 기판에 인접한 반도체 층은 분해되는 온도까지 가열된다. GaN이 사파이어 기판에 인접한 층인 경우, 인터페이스에 있는 층은 Ga와 N으로 분해되어, 인터페이스의 이면에 Ga를 남긴다. Ga 금속은 용융되고, 사파이어 기판은 나머지 층 구조로부터 제거된다. 사파이어 기판에 인접한 층의 분해는 레이저 에너지, 파장, 재료 분해 온도 및 재료의 흡수성에 좌우된다. 사파이어 기판은, 상술한 기술에 의해 제거되어 D-DBR이 액티브 영역의 다른 측면에 부착될 수 있게 한다. 그러나, VCSEL 인터페이스가 손실이 최소로(<0.5%) 되고 매우 평탄하여 공동 공진 특성이 최대화되도록 하는 것이 중요하다. 이 레이저 용융 기술은, VCSEL에 필요한 레이저 인터페이스의 평탄성이 결여되게 하는 많은 설계 변수를 갖는다. 그 외에, VCSEL은 매우 엄격한 두께적 제한을 받는다. 상술한 문제들을 모두 완화시키기 위해 레이저 용융을 사용할 수 있는 여러 방식이 있다.

희생 성장 기판에 인접한 층은, 그 층의 두께가 레이저에 의해 완전히 분해되도록 하는 경우 희생 층인 것으로 정의된다. 논문{옹(Wong) 등}에 공개된 결과에서 나타낸 바로는, 완전히 분해되는 층의 두께가 약 500Å이지만 이 값은 레이저 에너지, 레이저 파장, 재료 분해 온도 및 기판 인접 층의 흡수성에 좌우된다. 희생 층에 인접한 층(기판과 반대쪽) 즉, 사파이어 층은 희생 층의 레이저 파장에서 보다 높은 분해 온도나 보다 낮은 흡수성을 갖도록 선택된다. 정지 층은 레이저 에너지에 의해 크게 영향 받지는 않을 것인데, 그 이유는 보다 높은 분해 온도나 낮은 흡수성을 갖기 때문이다. 이 구조에서, 희생 층은 레이저에 의해 분해되어, 보다 높은 분해 온도 또는 보다 낮은 흡수성을 갖는 정지 층에 금 경사의 인터페이스를 남긴다. 정지 층은 다른 에너지 및 파장을 갖는 레이저를 사용하여 후속적으로 예칭되거나, 산화 및 예칭되거나, 분해될 수 있다.

바람직한 층 조합은  $\text{GaN}/\text{Al}_x\text{Ga}_{1-x}\text{N}$ ,  $\text{InGaN}/\text{Al}_x\text{Ga}_{1-x}\text{N}$ , 및  $\text{InGaN}/\text{GaN}$ 이다.  $\text{GaN}/\text{Al}_x\text{Ga}_{1-x}\text{N}$  조합의 경우, GaN 희생 층은 레이저로 분해될 것이지만,  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  정지 층은 영향을 받지 않을 것이다.  $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 은 평탄한  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  인터페이스상에서 정지하도록 선택적 습식 화학 예칭을 사용하여 예칭 제거될 수 있다. 대안적으로, 상술한 GaN 층이 완전히 분해되지 않으면, 잔류 GaN이 예칭 제거될 수 있다. 두꺼운 버퍼 층이 GaN 성장의 시작에서 필요하고 VCSEL 층 인터페이스가 두께 조절되고 매우 평탄할 필요가 있기 때문에, 이 기술은 특히 유익하다.

특정 층이나 공동의 두께는 하나 이상의 희생 층 및 정지 층을 사용하여 재단(tailor)될 수 있다. 레이저 용융 및 선택적 습식 화학 예칭에 의해, 원하는 두께에 이를 때까지 층 페어는 분해되고 순차적으로 예칭될 수 있다. 바람직한 층 조합은  $\text{GaN}/\text{Al}_x\text{Ga}_{1-x}\text{N}$ 이고, 여기서 GaN은 희생 층이며,  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  정지 층은 선택적으로 습식 화학 예칭될 수 있다.

성장 기판을 제거하는 다른 대안적 방법이 있다. 한가지 방법은 습식 화학 예칭을 사용하여 선택적으로 예칭될 수 있는 AlN을 사용하는 것이다. AlN은 희생 층으로써 사용될 수 있는데, 여기서,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  층은, 구조의 아래 부분을 잘라내도록 AlN 선택 예칭을 사용하여 호스트 기판으로부터 제거될 수 있다. 대안적으로, AlN 층은 상승된 온도에서 습식 산화 처리를 사용하여 산화될 수 있다. AlN 산화물은 예를 들면, HF와 같은 예칭액을 사용하여 예칭 제거될 수 있다. 다른 방식에서는, 예를 들면, 광 이온(light ion)을 재료에 주입하는 것과 같이, 기판을 박리시킬 수 있다. 이에 따라, 소정 깊이에 결함이 생길 수 있다. 기판이 가열되면, 재료는 전위(dislocation)를 통하여 선택적으로 분열되고, 기판은 액티브 층으로부터 분리된다. 화학 예칭액을 통하여 ZnO나 다른 유전체 버퍼 층의 아래를 절단하는 것은  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  층으로부터 기판을 제거하는데 사용될 수도 있다. 이 기술은 2-D 또는 3-D 성장 기술(예를 들면, ELOG에 사용되는  $\text{SiO}_2$ 나 다른 유전체)에 응용될 수 있으며, 여기서,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  층은 기판에 걸쳐서 연속적으로 존재하거나 패턴화된 영역에만 존재할 수 있다.

사파이어 기판상에 성장한  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 유전체 DBR을 침착하였다. DBR/ $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역 구조를 호스트 기판에 웨이퍼 본딩하였다. 경우 1에서, DBR/ $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역 구조를 GaP 호스트 기판에 직접 웨이퍼 본딩하였다(도 3 참조). 경우 2에서, DBR/ $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역 구조를 중간  $\text{CaF}_2$  층을 통하여 GaP 호스트 기판에 웨이퍼 본딩하였다(도 3, 도 3에는 중간층이 도시되지 않음). 경우 3에서, D-DBR을 호스트 기판(GaP)상에 침착하였고,  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역에 직접 웨이퍼 본딩하였다(도 4). 경우 1과 3에서, 본딩된 면적은, 중간 층이 사용되지 않았기 때문에 경우 2보다 훨씬 더 작다. 도 5는, 경우 1의 구조에 대해 본딩된 인터페이스의 스캐닝 전자 현미경(SEM; scanning electron microscope) 단면 이미지를 도시한다. 인터페이스는 평탄한데, 이 배율에서는 공백을 볼 수 없다. 경우 4에서, DBR/ $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  액티브 영역 구조를 CrAuNiCu 합금으로 구성된 금속 중간 층을 통하여 호스트 기판에 본딩하였다. 도 6은 경우 4의 SEM 단면을 도시하는데, 사파이어 기판은 제거되었고, 제 2 D-DBR은 제 1 D-DBR의 반대쪽의  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$

액티브 영역의 측면에 침착되었다. 모든 디바이스의 경우 D-DBR 스택은  $\text{SiO}_2/\text{HfO}_2$ 였고, 사파이어 기판은 레이저 용융 기술을 사용하여 제거되었다. 도 7은 도 6에 설명된 디바이스로부터 400nm-500nm의 발광 스펙트럼을 도시한다. 형태상의 피크는 수직 공동 구조의 특성이다.

### 발명의 효과

이상에서 설명된 바와 같이, 본 발명에 의거하여  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  디바이스의 양면에 고품질 반사면이 제공된다.

### (57) 청구의 범위

#### 청구항 1.

기판과,

n형 층, p형 층 및 액티브 층을 포함하고 상기 기판에 근접 배치된  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물과,

상기 기판과 상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물의 밑면 사이에 삽입된 제 1 미리 스택과,

상기 기판과 상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 중 선택된 하나와 상기 제 1 미리 스택 사이에 삽입되고 본딩 온도를 갖는 웨이퍼 본딩된 인터페이스와,

p 접점과 n 접점 - 상기 p 접점은 상기 p형 층에 전기 접속되고, 상기 n 접점은 상기 n형 층에 전기 접속됨 - 을 포함하는 디바이스.

#### 청구항 2.

제 1 항에 있어서,

상기 웨이퍼 본딩된 인터페이스에 인접한 적어도 하나의 중간 본딩 층을 더 포함하되,

상기 중간 본딩 층과 상기 기판 중 하나는 컴플라이언스를 갖도록 선택되는 디바이스.

#### 청구항 3.

제 2 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물은 수직 공동 광전자 구조물인 디바이스.

#### 청구항 4.

제 3 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물은 상기 p형 층내에 전류 제한 층을 더 포함하는 디바이스.

#### 청구항 5.

제 2 항에 있어서,

상기 기판은 캠플라이언스를 가지며, 갈륨 인화물(GaP), 갈륨 비소(GaAs), 인듐 인화물(InP) 및 실리콘(Si)을 포함하는 그룹으로부터 선택되는 디바이스.

### 청구항 6.

제 2 항에 있어서,

상기 중간 본딩 층은 캠플라이언스를 가지며, 할로겐화물, ZnO, 인듐, 주석, 크롬(Cr), 금, 니켈, 구리, II-VI 재료를 함유하는 합금 및 유전체를 포함하는 그룹으로부터 선택되는 디바이스.

### 청구항 7.

제 2 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물의 상측면에 인접 배치된 제 2 미러 스택을 더 포함하는 디바이스.

### 청구항 8.

제 7 항에 있어서,

상기 제 1 및 제 2 미러 스택중 적어도 하나의 스택은 유전체 분포 브래그 반사기와 복합 분포 브래그 반사기를 포함하는 그룹으로부터 선택되는 디바이스.

### 청구항 9.

제 1 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물에 인접 배치된 제 2 미러 스택을 더 포함하는 디바이스.

### 청구항 10.

제 9 항에 있어서,

상기 제 1 및 제 2 미러 스택중 적어도 하나의 스택은 유전체 분포 브래그 반사기와 복합 분포 브래그 반사기를 포함하는 그룹으로부터 선택되는 디바이스.

### 청구항 11.

제 1 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물은 상기 p형 층 내에 전류 제한 층을 더 포함하는 디바이스.

### 청구항 12.

제 1 항에 있어서,

상기 기판은 캠플라이언스를 가지며, 갈륨 인화물(GaP), 갈륨 비소(GaAs), 인듐 인화물(InP) 및 실리콘(Si)을 포함하는 그룹으로부터 선택되는 디바이스.

### 청구항 13.

제 1 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물은 수직 공동 광전자 구조물인 디바이스.

### 청구항 14.

$\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물을 제조하는 방법에 있어서,

호스트 기판을 제 1 미러 스택에 부착하는 단계와,

희생 성장 기판상에 상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물을 제조하는 단계와,

웨이퍼 본드 인터페이스를 생성하는 단계와,

상기 희생 성장 기판을 제거하는 단계와,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물에 전기 접점을 침착하는 단계

를 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 15.

제 14 항에 있어서,

상기 희생 성장 기판을 제거하는 단계는 레이저 용융 단계를 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 16.

제 14 항에 있어서,

상기 웨이퍼 본드 인터페이스에서 중간 본딩 층을 부착하는 단계를 더 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 17.

제 16 항에 있어서,

상기 호스트 기판과 상기 중간 본딩 층 중 하나는 캠플라이언스를 갖도록 선택되는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 18.

제 14 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물의 상부에 제 2 미러 스택을 부착하는 단계를 더 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 19.

$\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법에 있어서,

희생 성장 기판에  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물을 형성하는 단계와,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물의 상부에 제 1 미러 스택을 부착하는 단계와,

웨이퍼 본드 인터페이스를 생성하기 위해 상기 제 1 미러 스택에 호스트 기판을 웨이퍼 본딩하는 단계와,

상기 희생 성장 기판을 제거하는 단계와,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물에 전기 접점을 침착하는 단계

를 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 20.

제 19 항에 있어서,

상기 희생 성장 기판을 제거하는 단계는 레이저 용융 단계를 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 21.

제 19 항에 있어서,

상기 웨이퍼 본드 인터페이스에서 중간 본딩 층을 부착하는 단계를 더 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 22.

제 19 항에 있어서,

상기 호스트 기판과 상기 중간 본딩 층 중 하나는 캠플라이언스를 갖도록 선택되는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

### 청구항 23.

제 19 항에 있어서,

상기  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물의 상부에 제 2 미러 스택을 부착하는 단계를 더 포함하는  $\text{Al}_x\text{Ga}_y\text{In}_z\text{N}$  구조물 제조 방법.

도면

도면1

$\text{AlN}/\text{GaN}$  및  $\text{Al}_{0.30}\text{Ga}_{0.70}\text{N}/\text{GaN}$ 에 대한

이론상 반사를 대비

도면2

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면5

도면6

도면7