(12)

## Patentschrift

(21) Aktenzeichen: 10 2012 207 222.5

(22) Anmelddatum: 30.04.2012

(43) Offenlegungstag: 08.11.2012

(45) Veröffentlichungstag

der Patenterteilung: 25.05.2016

(51) Int Cl.: H03K 17/16 (2006.01)

H03K 17/12 (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

2011-102779 02.05.2011 JP

2012-054269 12.03.2012 JP

(62) Teilung in:

10 2012 025 769.4

(73) Patentinhaber:

Mitsubishi Electric Corporation, Tokio/Tokyo, JP

(74) Vertreter:

Prüfer & Partner mbB Patentanwälte

Rechtsanwalt, 81479 München, DE

(72) Erfinder:

Hussein, Khalid Hassan, Tokyo, JP; Kumagai, Toshiyuki, Fukuoka, JP; Saito, Shoji, Tokyo, JP

(56) Ermittelter Stand der Technik:

JP 2000-092 820 A

JP H05-291 913 A

JP H06-209 565 A

JP H06-209 566 A

JP 2009-135 626 A

(54) Bezeichnung: **Leistungshalbleitervorrichtung mit einer Mehrzahl parallel geschalteter Schaltelemente**

(57) Hauptanspruch: Leistungshalbleitervorrichtung (208) mit:

einem ersten und einem zweiten Leistungshalbleiterelement (Q1, Q2), die parallel zueinander geschaltet sind, und einer Treibersteuereinheit (108) zum Ein- und Ausschalten des ersten und des zweiten Leistungshalbleiterelements (Q1, Q2) als Reaktion auf einen Einschaltbefehl und einen Ausschaltbefehl, die wiederholt von außen empfangen werden,

wobei die Treibersteuereinheit (108) in der Lage ist, umzuschalten zwischen einem Fall, in dem als Reaktion auf den Einschaltbefehl das erste und das zweite Leistungshalbleiterelement (Q1, Q2) gleichzeitig eingeschaltet werden, und einem Fall, in dem als Reaktion auf den Einschaltbefehl zunächst das erste oder das zweite Leistungshalbleiterelement (Q1, Q2) eingeschaltet wird und danach das andere Leistungshalbleiterelement eingeschaltet wird, und die Treibersteuereinheit (108) in der Lage ist, als Reaktion auf den Ausschaltbefehl zunächst das erste oder das zweite Leistungshalbleiterelement (Q1, Q2) auszuschalten und danach das andere Leistungshalbleiterelement auszuschalten,

dadurch gekennzeichnet, dass

die Leistungshalbleitervorrichtung (208) weiter einen Stromerfassungsabschnitt (99) enthält zum Erfassen eines Stroms, der zumindest durch das erste oder das zweite Leistungshalbleiterelement (Q1, Q2) fließt, oder einer Sum-

me der Ströme, die durch beide Leistungshalbleiterelemente fließen,

die Treibersteuereinheit (108) in der Lage ist, einen Bestimmungsvorgang durchzuführen zum Bestimmen, ob ein durch den Stromerfassungsabschnitt (99) gewonnener Stromerfassungswert kleiner gleich einem ersten Schwellenwert ( $I_{th1}$ ) ist, wenn das erste und das zweite Leistungshalbleiterelement (Q1, Q2) als Reaktion auf den Einschaltbefehl eingeschaltet sind, ...

**Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Leistungshalbleitervorrichtung, die in Leistungs-umwandlungseinrichtungen oder ähnlichem verwendet wird.

**[0002]** Ein Leistungshalbleiterelement wie z. B. ein Leistungs-MOSFET (Metal Oxide Semiconductor Field Effect Transistor, Metall-Oxid-Halbleiter-Feldefekttransistor) oder ein IGBT (Insulated Gate Bipolar Transistor, Bipolartransistor mit isoliertem Gate) wird verwendet zum Steuern einer Leistungseinrichtung wie z. B. eines Motorantriebsstromrichters, einer unterbrechungsfreien Leistungsversorgung und einer Frequenzumwandlungsvorrichtung. Da eine Nennspannung und ein Nennstrom einer solchen Leistungseinrichtung immer größer werden, muss ein Leistungshalbleiterelement auch auf eine höhere Spannungsfestigkeit und einen höheren Strom angepasst werden.

**[0003]** Ein Verfahren zum Parallelschalten einer Mehrzahl von Leistungshalbleiterelementen ist bekannt als Verfahren zum Erhöhen einer Menge des Stroms, die von dem Leistungshalbleiterelement gesteuert wird (s. z. B. JP 2000-92820 A).

**[0004]** In so einem Fall wie in dem oben genannten Dokument, in dem eine Mehrzahl von Leistungshalbleiterelementen parallel geschaltet sind, werden diese Elemente normalerweise gleichzeitig unter Verwendung des selben Treibersignals geschaltet. Wenn die Anzahl paralleler Halbleiterelemente größer wird oder eine Schaltfrequenz erhöht wird, steigt daher der Schaltverlust (Einschaltverlust und Ausschaltverlust).

**[0005]** Es ist beispielsweise ein Verfahren, wie es in JP 05-291913 A beschrieben ist, bekannt als Verfahren zum Verringern des Ausschaltverlustes von parallel geschalteten Leistungshalbleiterelementen. Gemäß dem in diesem Dokument beschriebenen Verfahren werden ein erster IGBT, der eine niedrige Sättigungsspannung und eine lange Abfallzeit aufweist, und ein zweiter IGBT, der eine hohe Sättigungsspannung und eine kurze Abfallzeit aufweist, parallel geschaltet, und ein Eingangswiderstand wird in ein Gate des zweiten IGBT eingesetzt. Wenn der erste und zweite IGBT durch ein gemeinsames Treibersignal betrieben werden, liegt ein Abschaltpunkt des zweiten IGBT später als ein Abschaltpunkt des ersten IGBT, und daher kann ein Ausschaltbetrieb basierend auf einer kurzen Abfallzeit des zweiten IGBT durchgeführt werden.

**[0006]** Eine ähnliche Technik ist in JP 06-209565 A und JP 06-209566 A beschrieben, auch wenn diese nicht darauf abzielen, den Schaltverlust zu verringern. Beide Dokumente offenbaren Schaltglieder,

die in Reihe geschaltet sind, wobei jedes aus einem Haupthalbleiterelement und einem dazu parallel geschalteten Erfassungshalbleiterelement gebildet ist. Insbesondere sind gemäß der in JP 06-209565 A beschriebenen Technik ein Gate des Hauptleiterelements und eine Gatetreiberschaltung miteinander verbunden, wobei eine Ausschaltverzögerungsschaltung dazwischen eingefügt ist, und ein Gate des Erfassungshalbleiterelements und die Gatetreiberschaltung sind miteinander verbunden, wobei eine Einschaltverzögerungsschaltung dazwischen eingefügt ist. Gemäß der in JP 06-209566 A beschriebenen Technik sind ein Gate des Erfassungshalbleiterelements und eine Gatetreiberschaltung miteinander verbunden, wobei eine Ausschaltverzögerungsschaltung dazwischen eingefügt ist, und ein Gate des Haupthalbleiterelements und die Gatetreiberschaltung sind miteinander verbunden, wobei eine Einschaltverzögerungsschaltung dazwischen eingefügt ist.

**[0007]** Die oben genannte JP 05-291913 A zieht eine Verringerung des Schaltverlusts in Erwägung, richtet ihr Augenmerk jedoch nur auf die Verringerung des Ausschaltverlusts und betrachtet nicht den Einschaltverlust. Da das in diesem Dokument beschriebene Verfahren das zueinander parallel Schalten des ersten IGBT mit einer niedrigen Sättigungsspannung und einer langen Abfallzeit und des zweiten IGBT mit einer hohen Sättigungsspannung und einer kurzen Abfallzeit enthält, ist es nicht auf einen Fall anwendbar, in dem Leistungshalbleiterelemente mit denselben Eigenschaften parallel geschaltet sind.

**[0008]** JP 2009-135626 A beschreibt eine Treibervorrichtung zum Treiben zweier parallel geschalteter Halbleiterschaltelemente. Zum Ausgleich der Temperatur zwischen den Halbleiterschaltelementen wird ein verzögertes Treibersignal erzeugt, bei dem der Einschaltzeitpunkt und dem Ausschaltzeitpunkt verzögert sind. Dem Halbleiterschaltelement mit der niedrigeren Temperatur wird das verzögerte Treibersignal zugeführt, während dem Halbleiterschaltelement mit der höheren Temperatur das nicht verzögerte Treibersignal zugeführt wird. In anderen Ausführungsformen ist bei dem verzögerten Treibersignal entweder nur der Einschaltzeitpunkt oder nur der Ausschaltzeitpunkt verzögert.

**[0009]** Die Aufgabe der vorliegenden Erfindung besteht darin, den Schaltverlust in einem Fall, in dem eine Mehrzahl von Leistungshalbleiterelementen parallel geschaltet sind, verglichen mit einem herkömmlichen Beispiel zu verringern.

**[0010]** Die Aufgabe wird gelöst durch eine Leistungshalbleitervorrichtung gemäß Anspruch 1. Weiterbildungen der Erfindung sind jeweils in den Unteransprüchen angegeben.

**[0011]** Gemäß der vorliegenden Erfindung ist es möglich, als Reaktion auf den Einschaltbefehl umzuschalten zwischen einem Fall, in dem das erste und das zweite Leistungshalbleiterelement gleichzeitig eingeschaltet werden, und einem Fall, in dem sie mit einem unterschiedlichen Zeitablauf eingeschaltet werden, und als Reaktion auf den Ausschaltbefehl werden das erste und das zweite Leistungshalbleiterelement mit einem unterschiedlichen Zeitablauf ausgeschaltet. Daher liegt ein Hauptvorteil der vorliegenden Erfindung in der Fähigkeit, verglichen mit einem herkömmlichen Beispiel einen Schaltverlust zu verringern.

**[0012]** Weitere Merkmale und Zweckmäßigkeiten der Erfindung ergeben sich aus der Beschreibung von Ausführungsbeispielen anhand der beigefügten Zeichnungen.

**[0013]** **Fig. 1** ist ein Diagramm eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer ersten Ausführungsform.

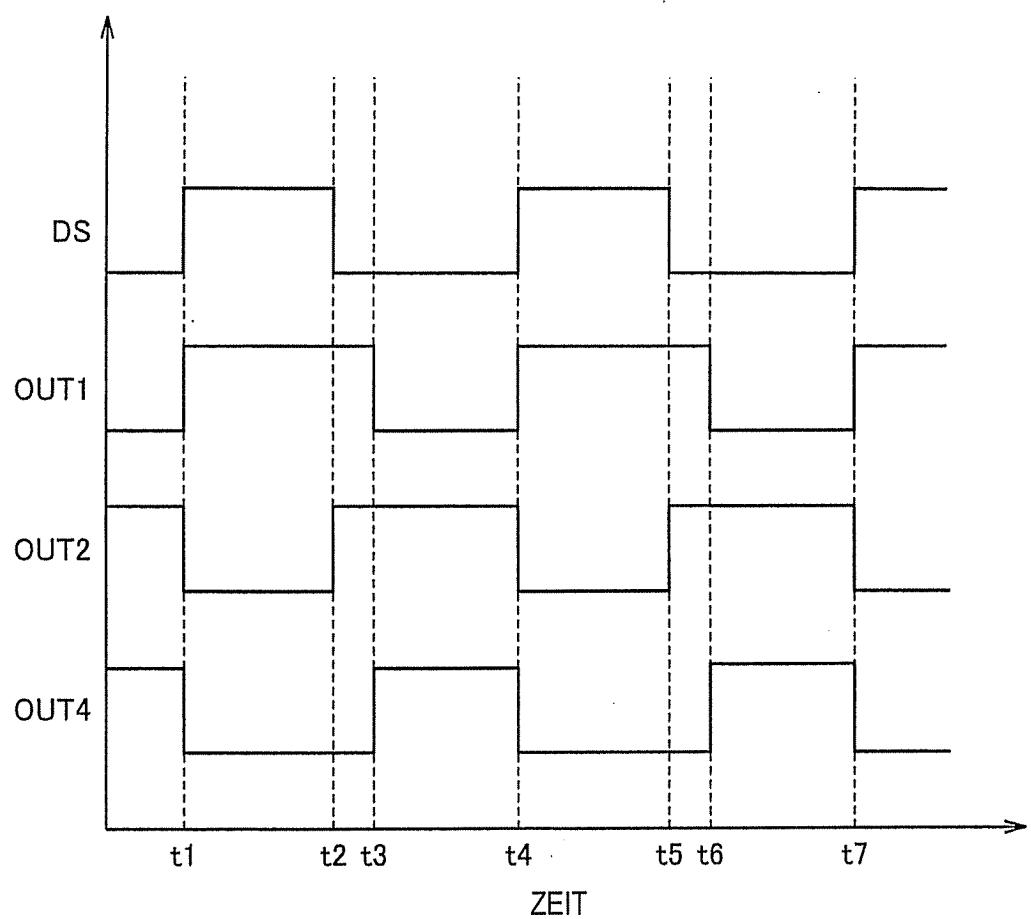

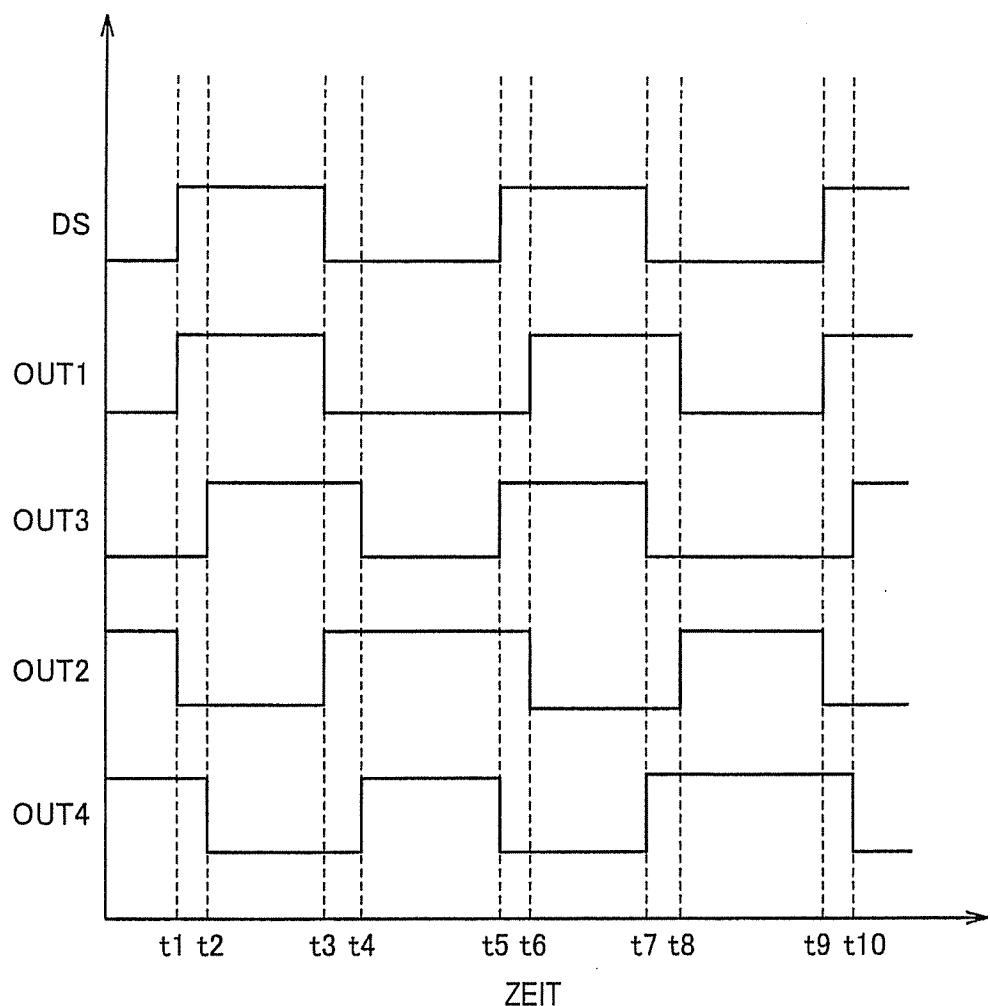

**[0014]** **Fig. 2A** ist ein Zeitverlaufsdigramm, das eine Beziehung zwischen einem Treibersignal und den Gatespannungen der Leistungshalbleiterelemente in einem Fall zeigt, in dem die Größe eines Gesamtstroms relativ klein ist.

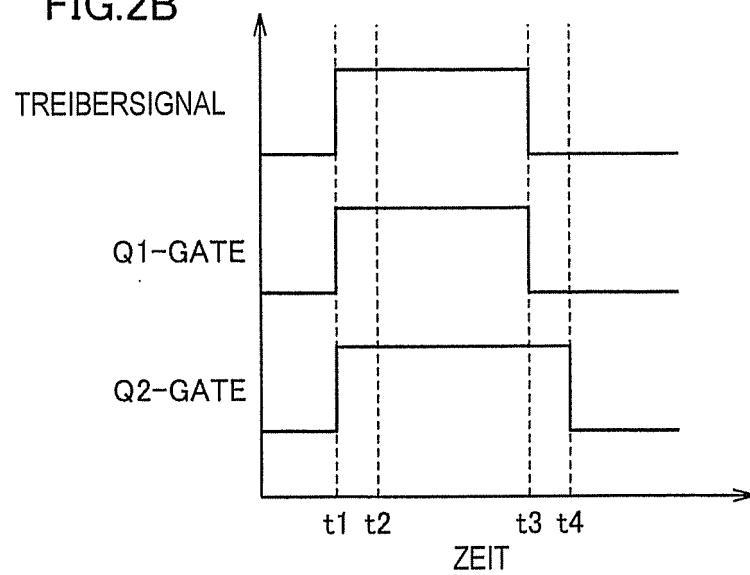

**[0015]** **Fig. 2B** ist ein Zeitverlaufsdigramm, das eine Beziehung zwischen einem Treibersignal und den Gatespannungen der Leistungshalbleiterelemente in einem Fall zeigt, in dem die Größe eines Gesamtstroms mittelgroß ist.

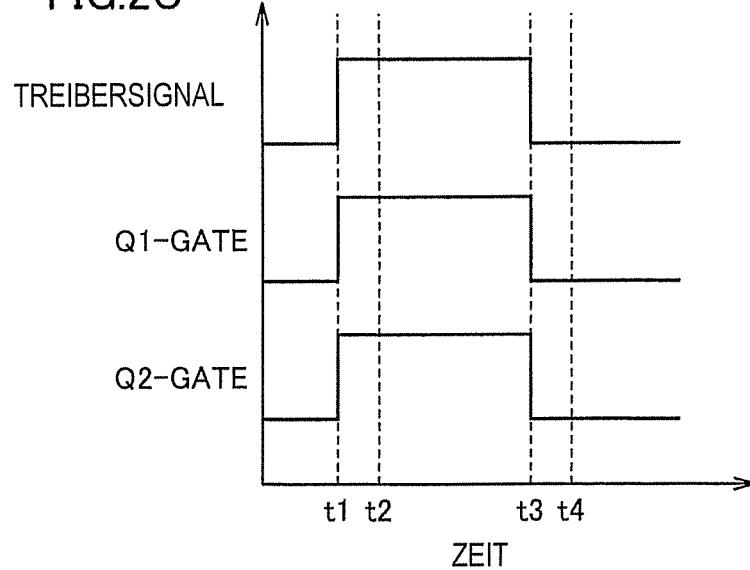

**[0016]** **Fig. 2C** ist ein Zeitverlaufsdigramm, das eine Beziehung zwischen einem Treibersignal und den Gatespannungen der Leistungshalbleiterelemente in einem Fall zeigt, in dem die Größe eines Gesamtstroms relativ groß ist.

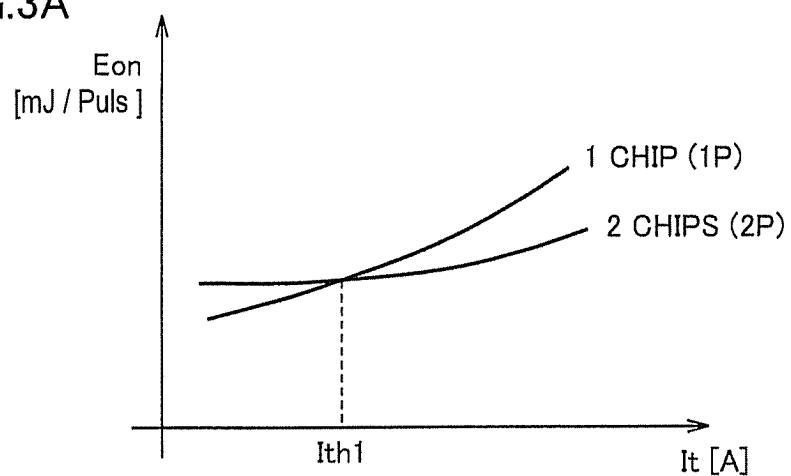

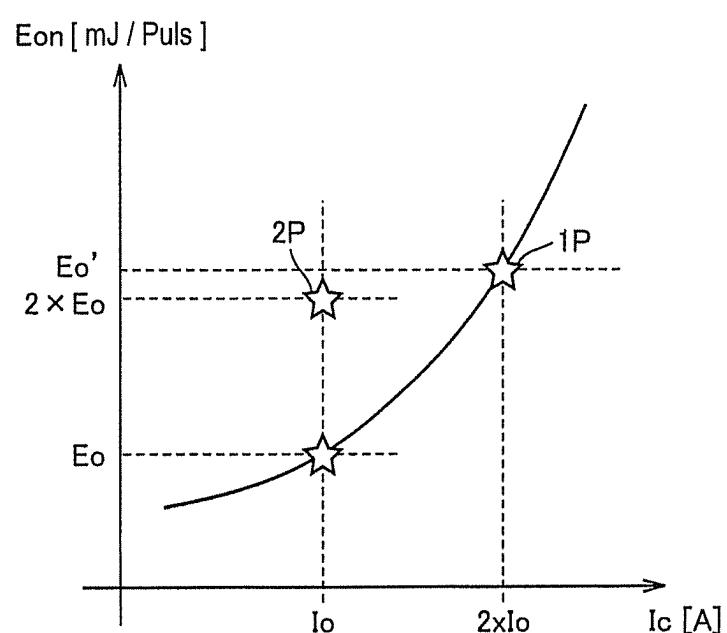

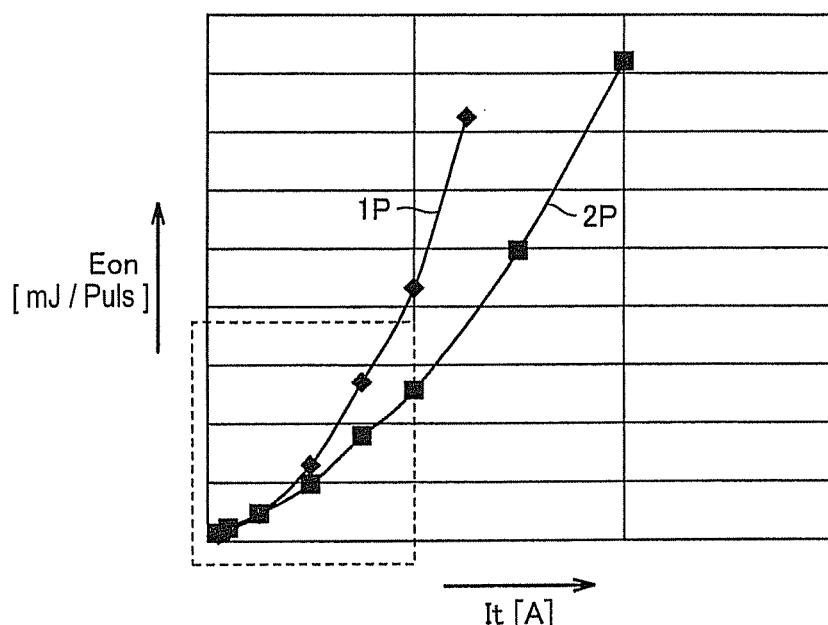

**[0017]** **Fig. 3A** ist ein Diagramm, das eine Beziehung zwischen der Größe eines Gesamtstroms, der durch die IGBTs im eingeschalteten Zustand fließt, und der Größe eines Einschaltverlusts zeigt.

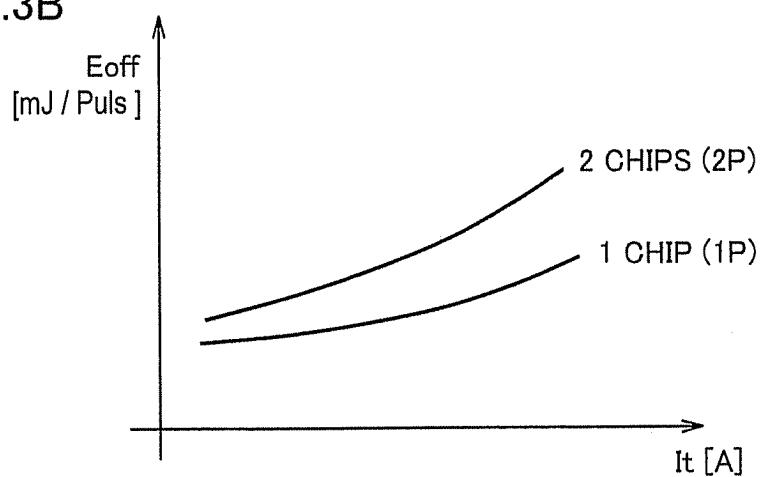

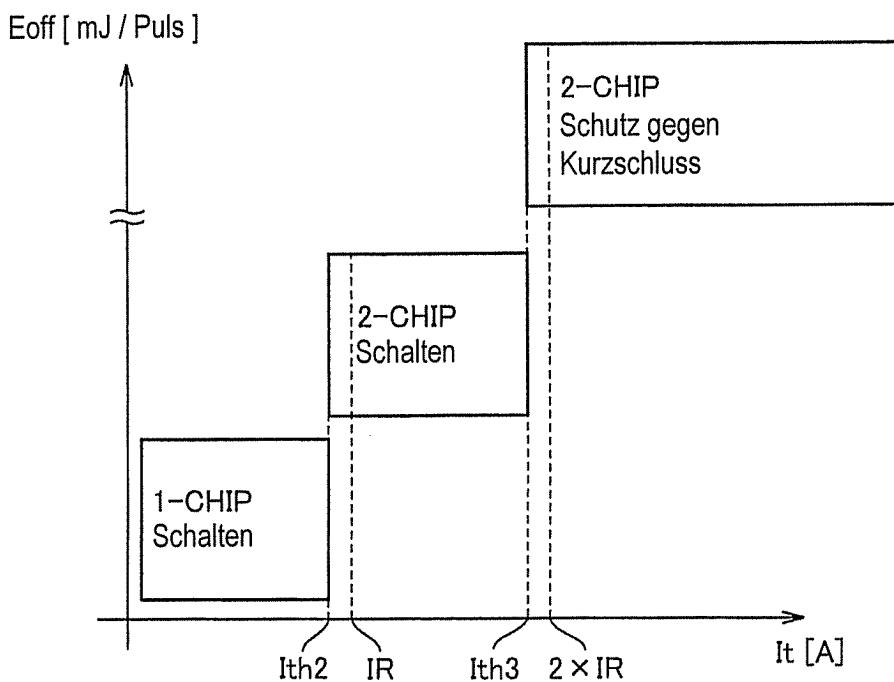

**[0018]** **Fig. 3B** ist ein Diagramm, das eine Beziehung zwischen der Größe eines Gesamtstroms, der durch die IGBTs im eingeschalteten Zustand fließt, und der Größe eines Ausschaltverlusts zeigt.

**[0019]** **Fig. 4** ist ein Diagramm zum Darstellen des Konzepts der Zeitablaufsteuerung, wenn die IGBTs ausgeschaltet werden.

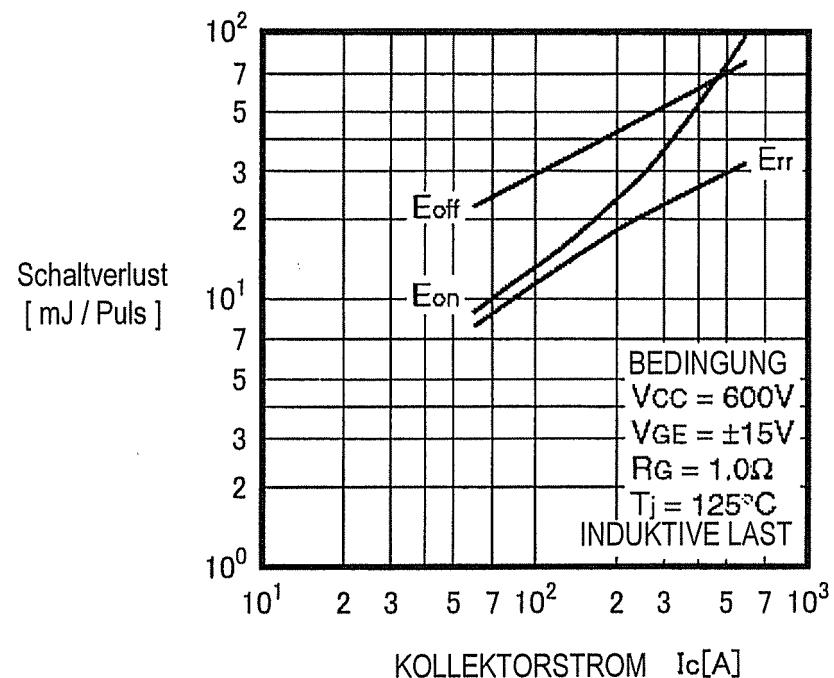

**[0020]** **Fig. 5** ist ein Diagramm, das eine Beziehung zwischen einem Schaltverlust und einem Kollektorstrom des IGBT zeigt.

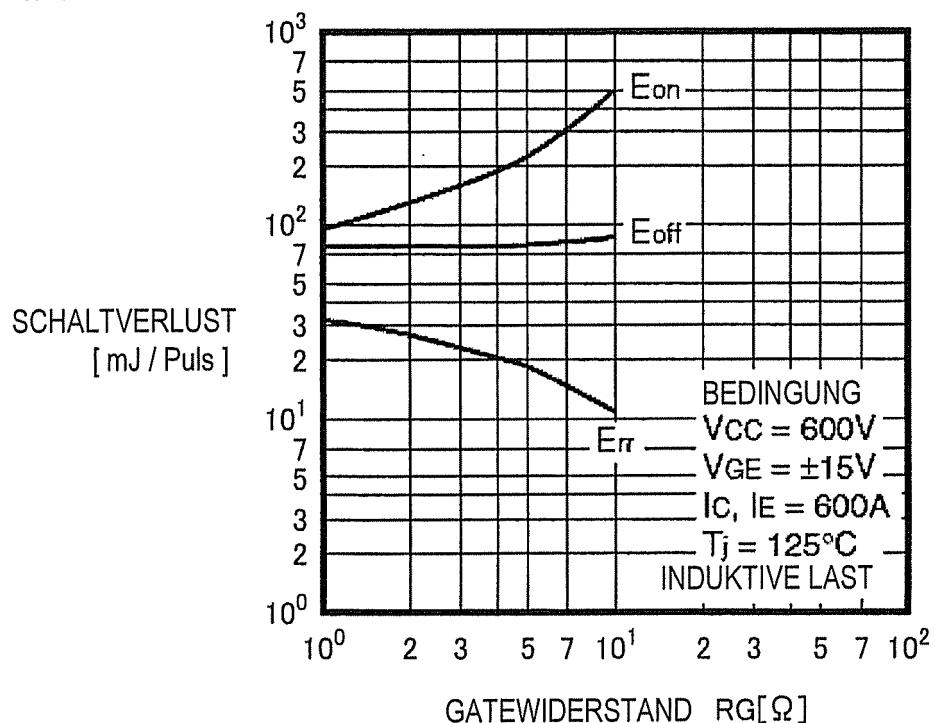

**[0021]** **Fig. 6** ist ein Diagramm, das eine Beziehung zwischen einem Schaltverlust und einem Gatewiderstand des IGBT zeigt.

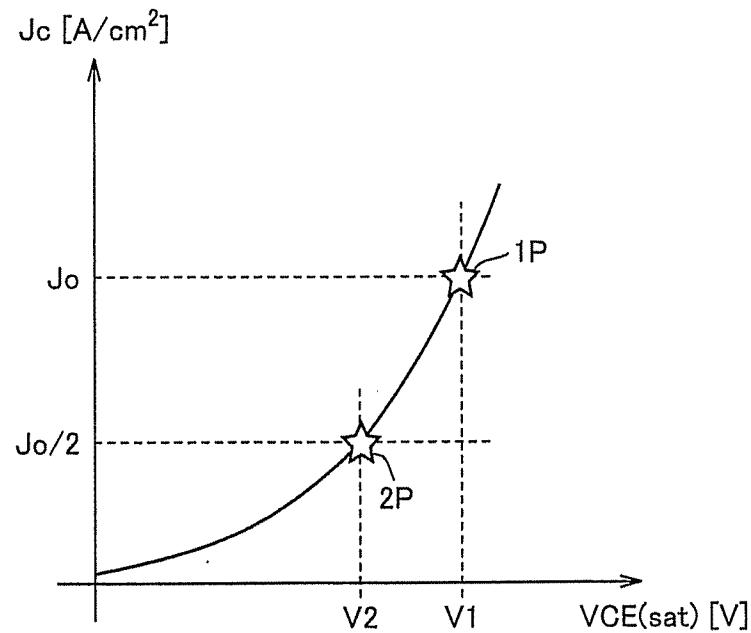

**[0022]** **Fig. 7** ist ein Diagramm, das eine Beziehung zwischen einer Kollektorstromdichte und einer Sättigungsspannung zeigt.

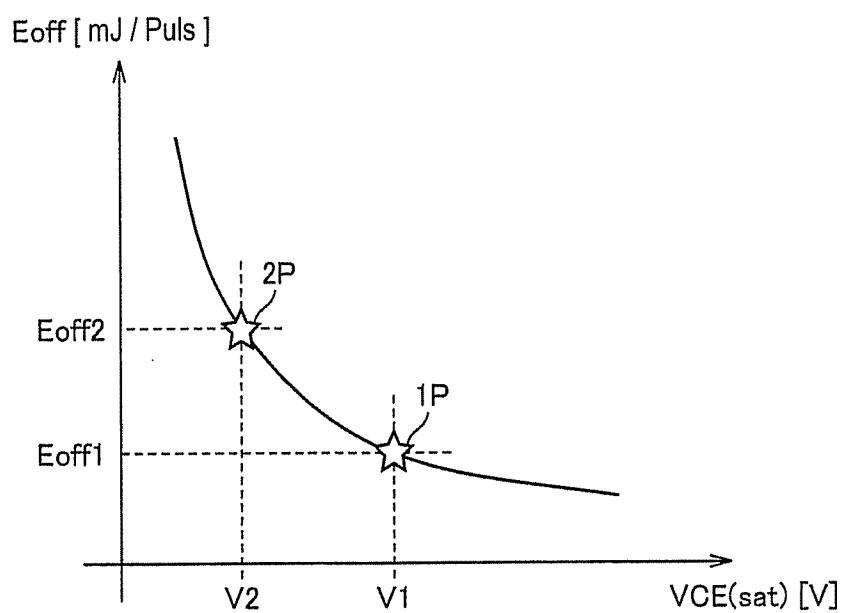

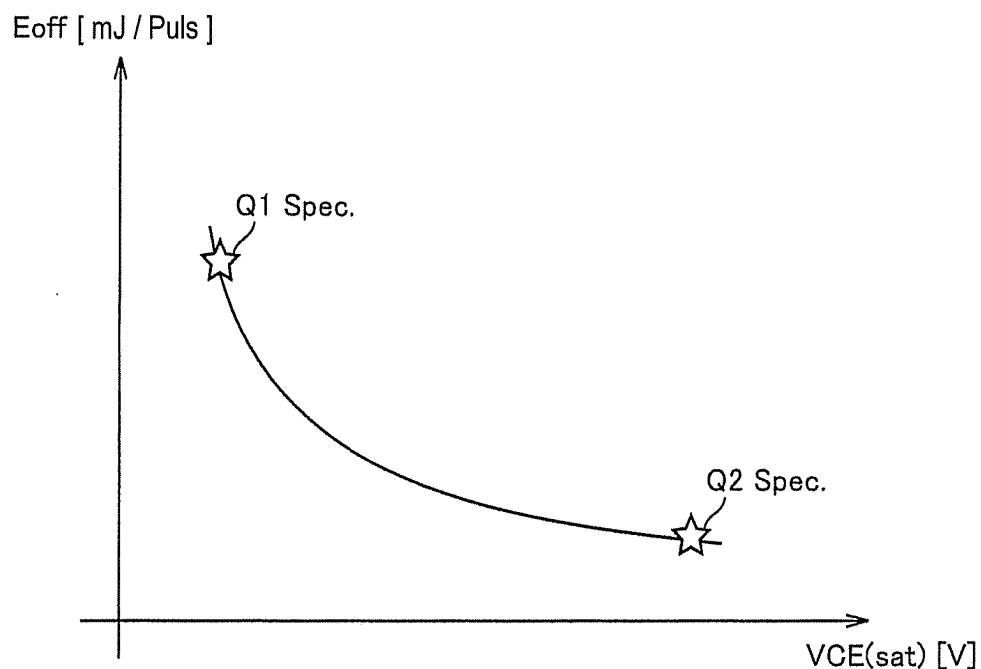

**[0023]** **Fig. 8** ist ein Diagramm, das eine Beziehung zwischen einem Ausschaltverlust und einer Sättigungsspannung zeigt.

**[0024]** **Fig. 9** ist ein Diagramm, das eine Beziehung zwischen einem Kollektorstrom und einem Einschaltverlust zeigt.

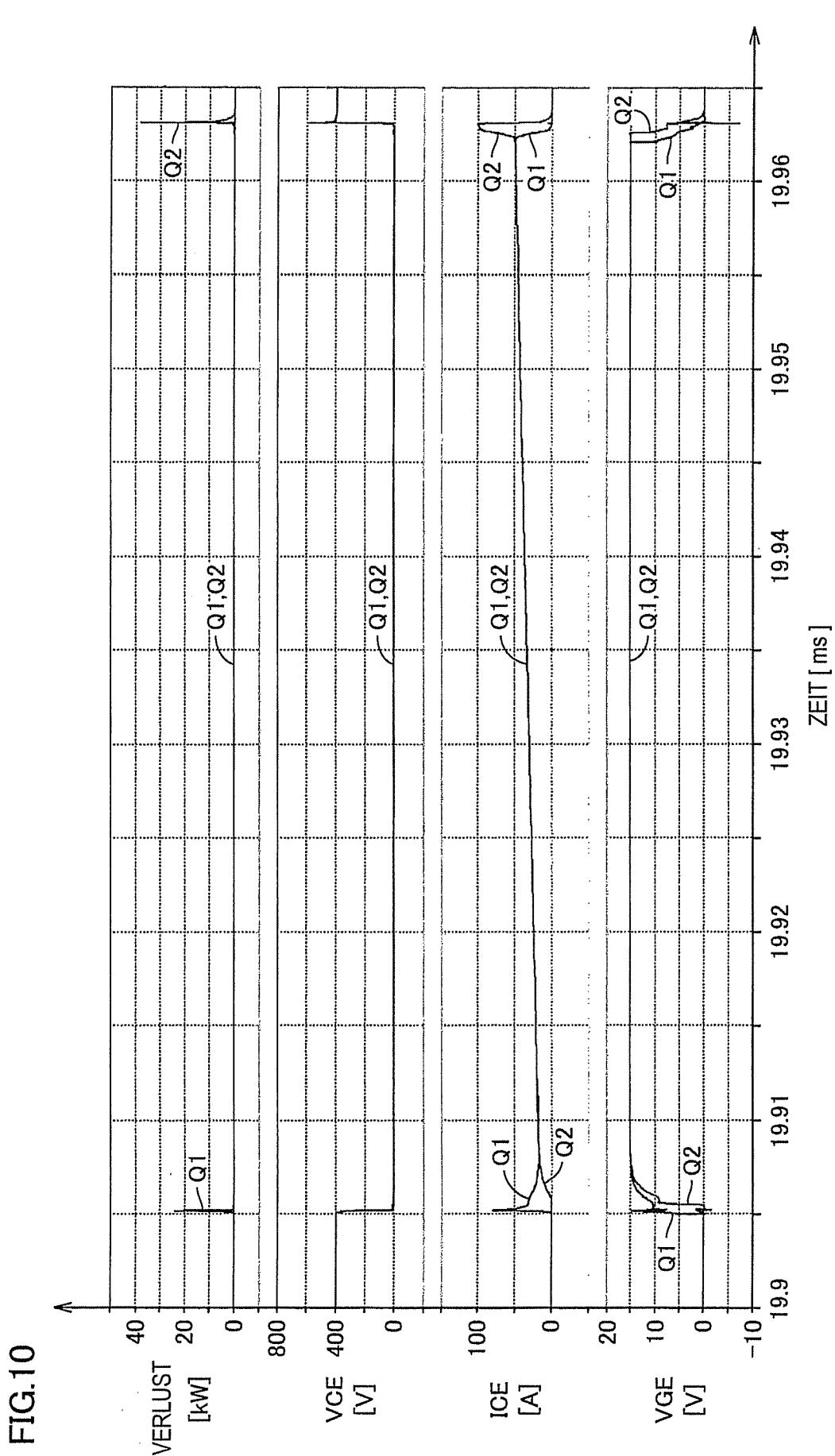

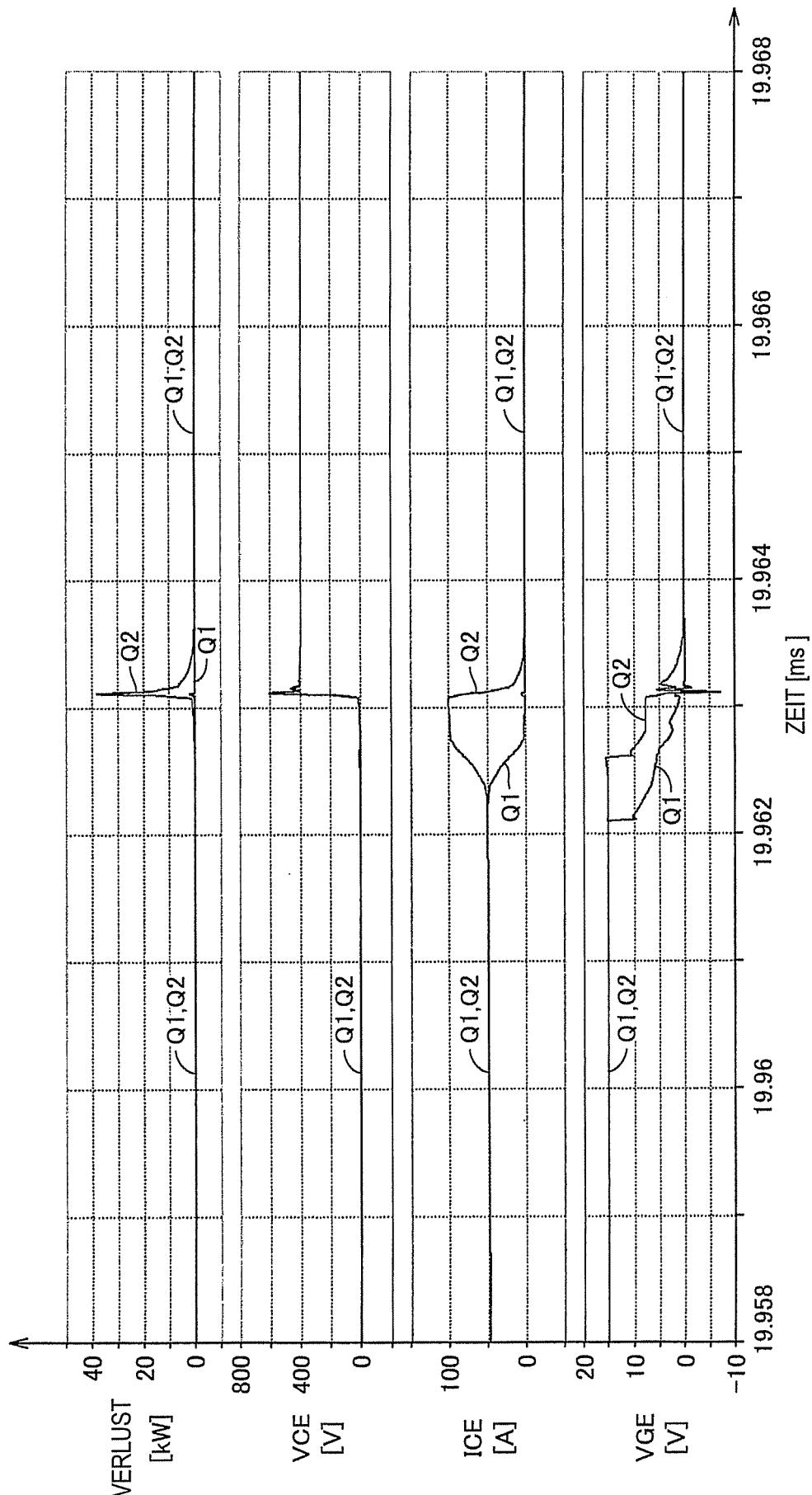

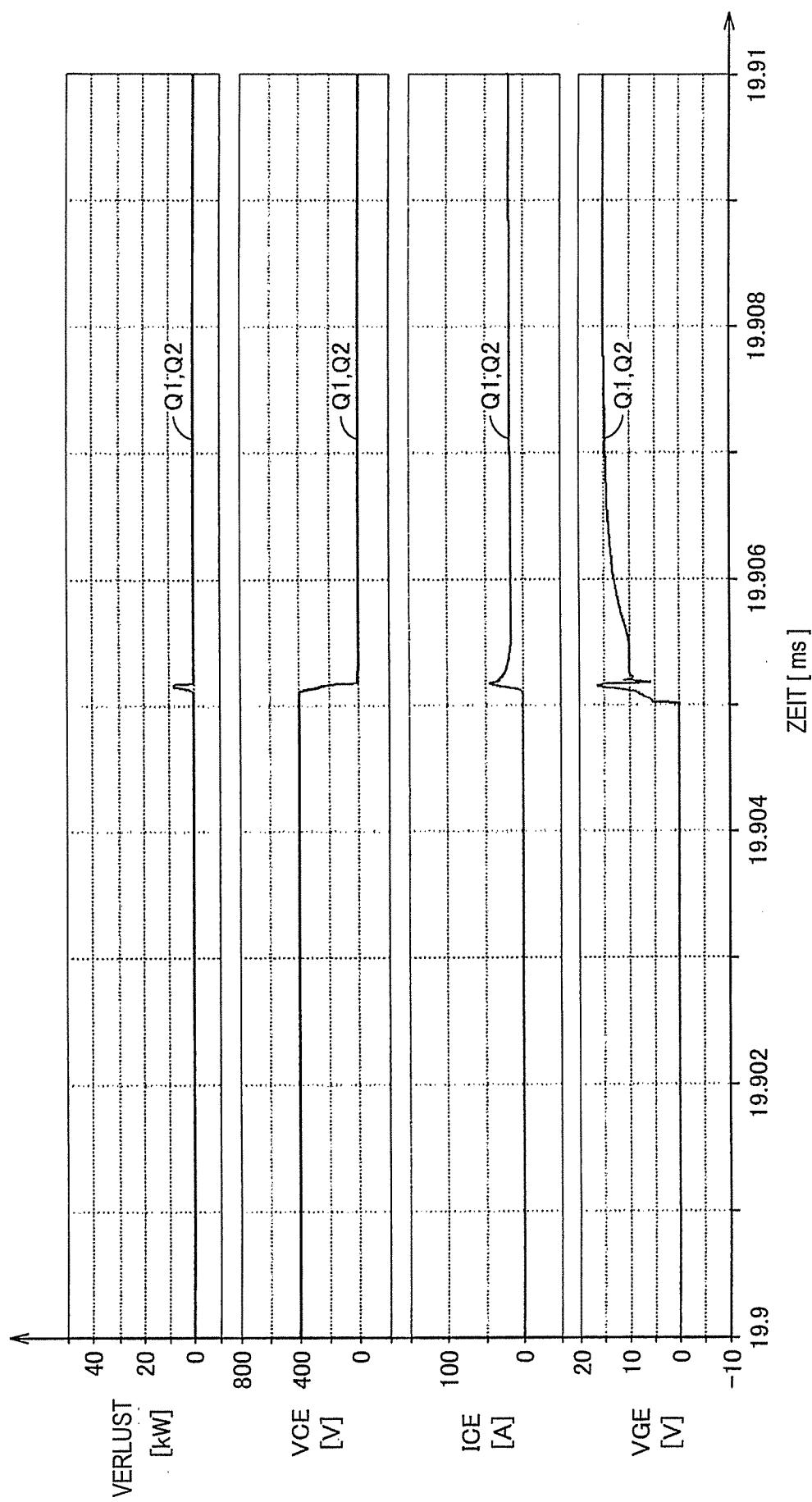

**[0025]** **Fig. 10** ist ein Diagramm, das ein Simulationsergebnis zeigt, wenn parallel geschaltete IGBTs nacheinander geschaltet werden.

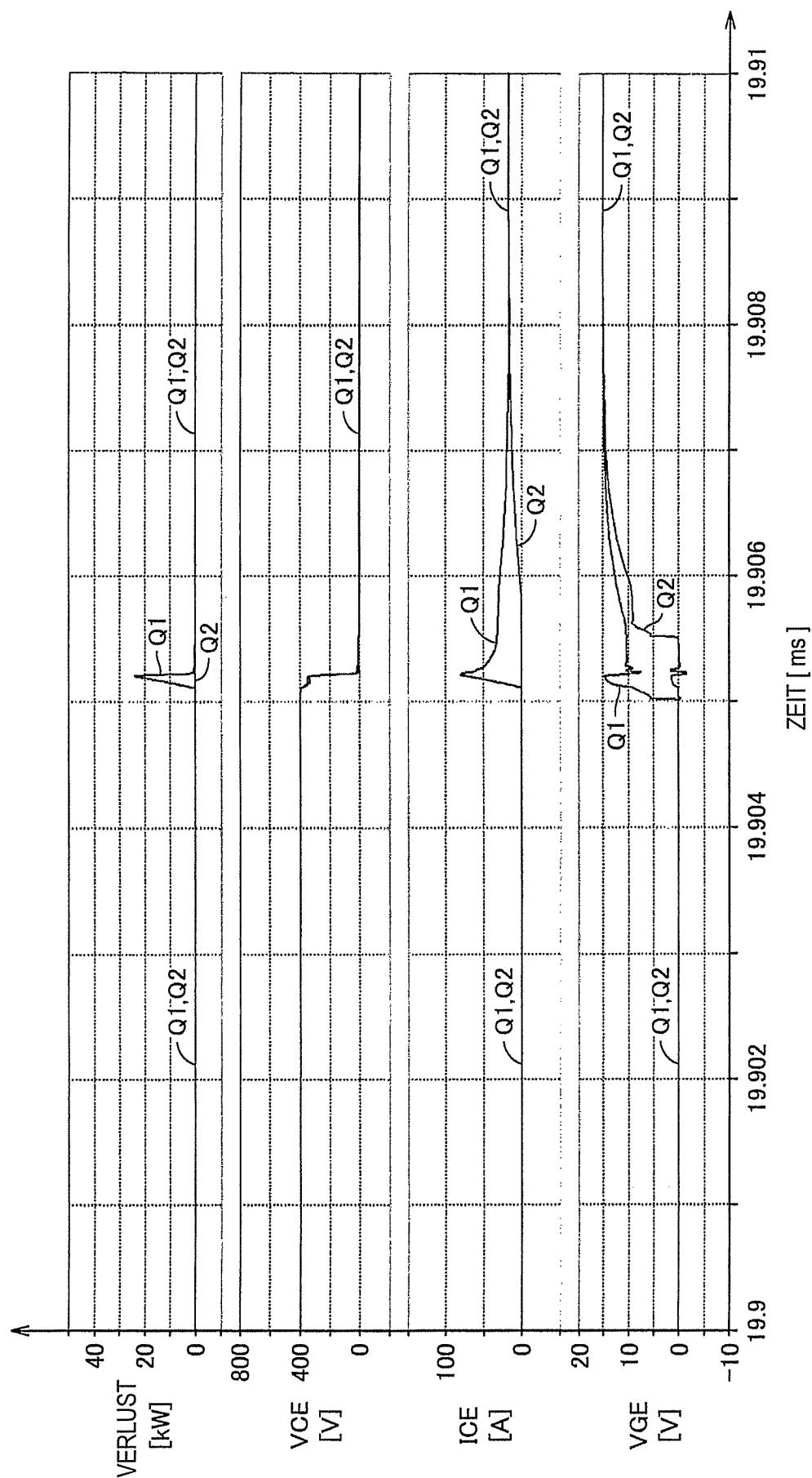

**[0026]** **Fig. 11** ist eine vergrößerte Ansicht von **Fig. 10** zur Zeit des Einschaltens.

**[0027]** **Fig. 12** ist eine vergrößerte Ansicht von **Fig. 10** zur Zeit des Ausschaltens.

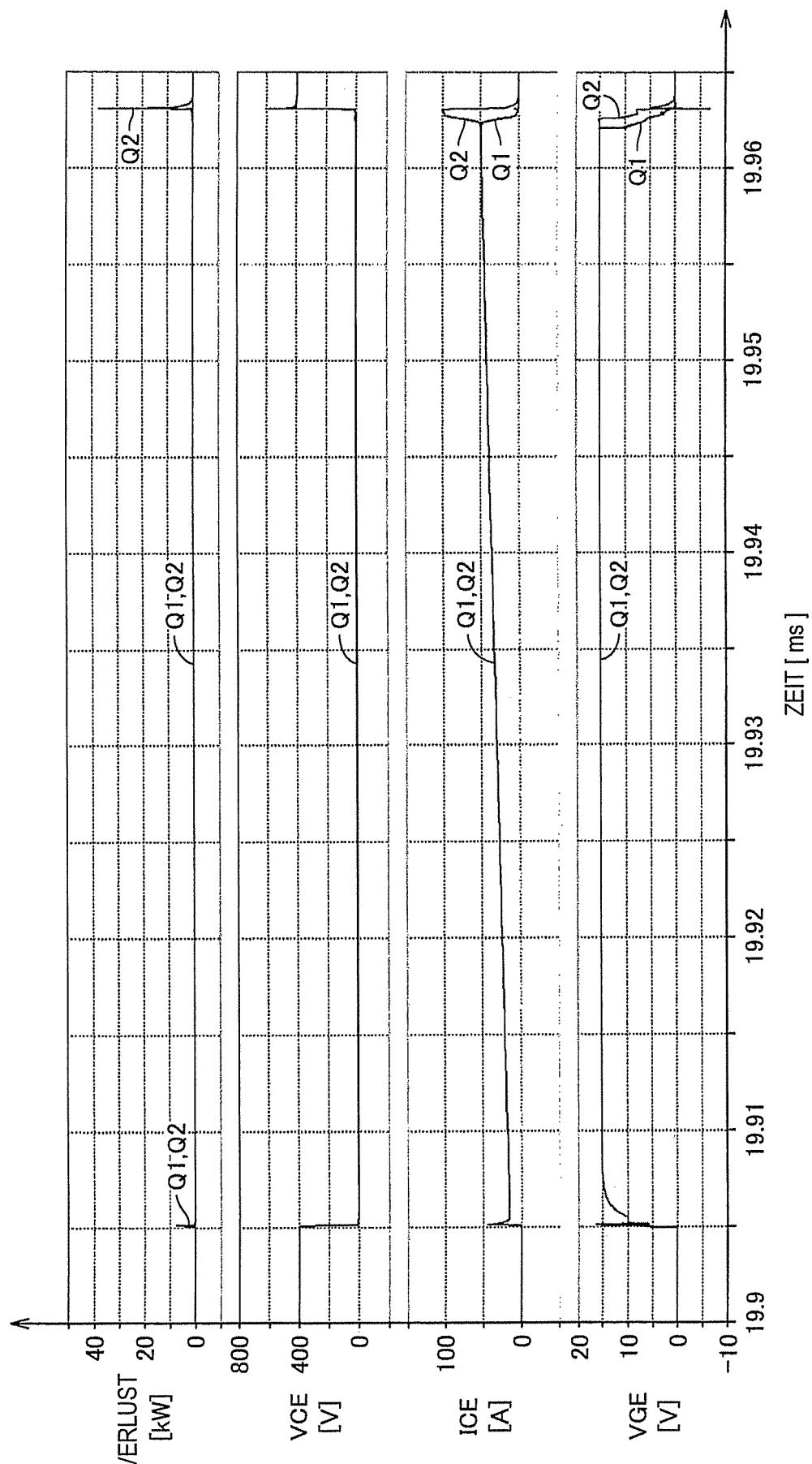

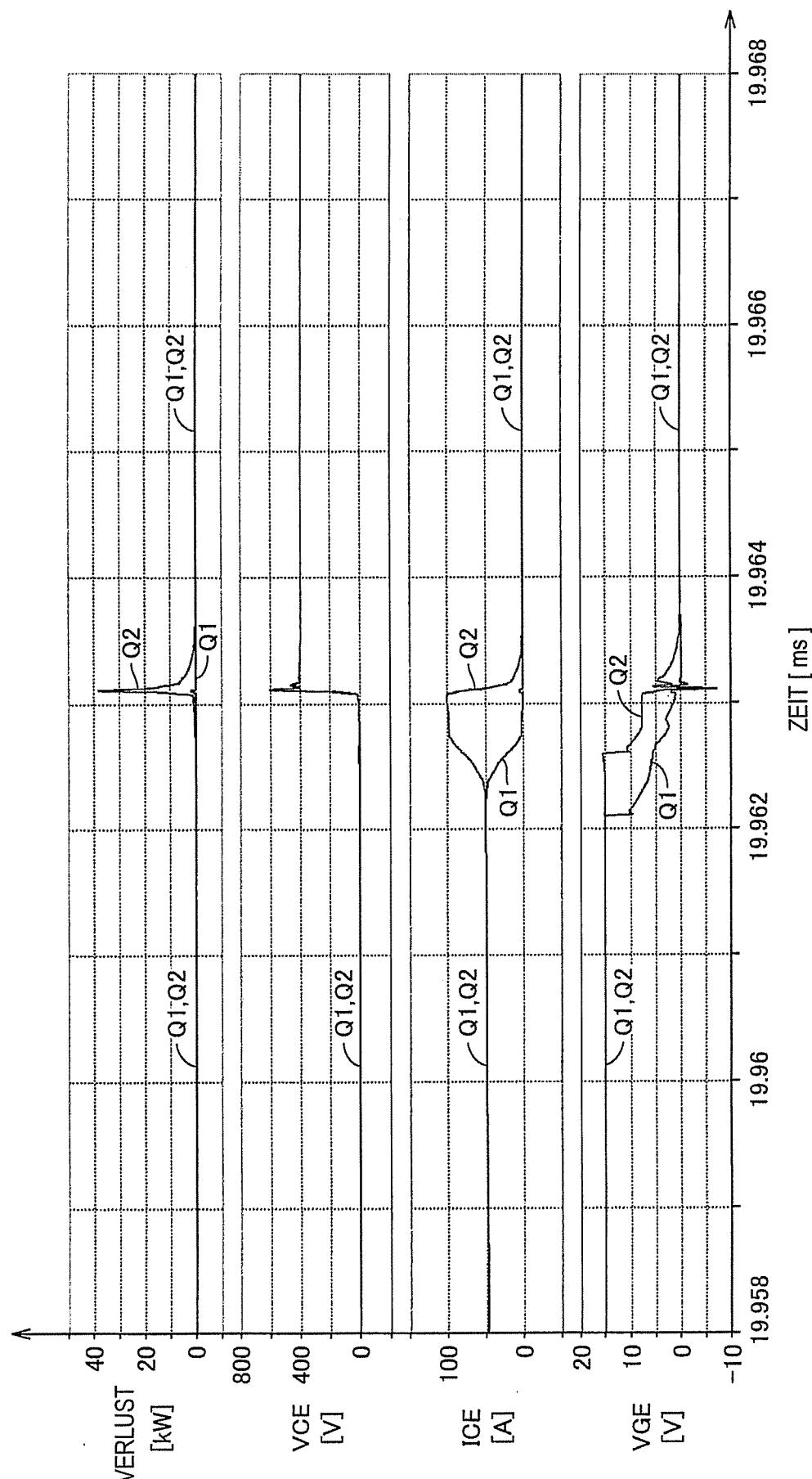

**[0028]** **Fig. 13** ist ein Diagramm, das ein Simulationsergebnis zeigt, wenn das Einschalten der parallel geschalteten IGBTs gleichzeitig durchgeführt wird und das Ausschalten nacheinander durchgeführt wird.

**[0029]** **Fig. 14** ist eine vergrößerte Ansicht von **Fig. 13** zur Zeit des Einschaltens.

**[0030]** **Fig. 15** ist eine vergrößerte Ansicht von **Fig. 13** zur Zeit des Ausschaltens.

**[0031]** **Fig. 16A** ist ein Diagramm, das eine Beziehung zwischen einem Gesamtstrom, der durch die parallel geschalteten IGBTs fließt, und einem Einschaltverlust zeigt.

**[0032]** **Fig. 16B** ist eine vergrößerte Ansicht eines Abschnitts in einem Rahmen, der in **Fig. 16A** durch eine gestrichelte Linie gezeigt ist.

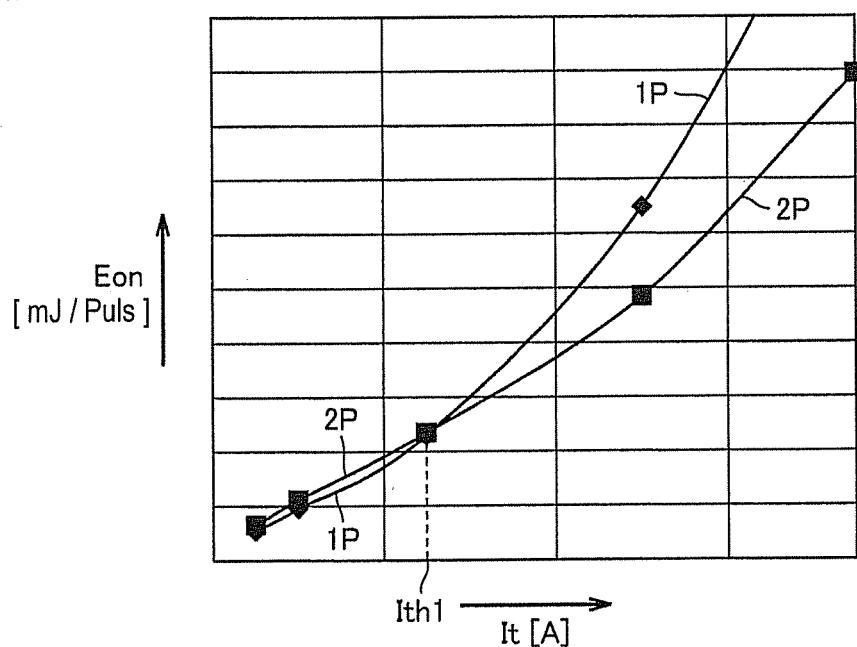

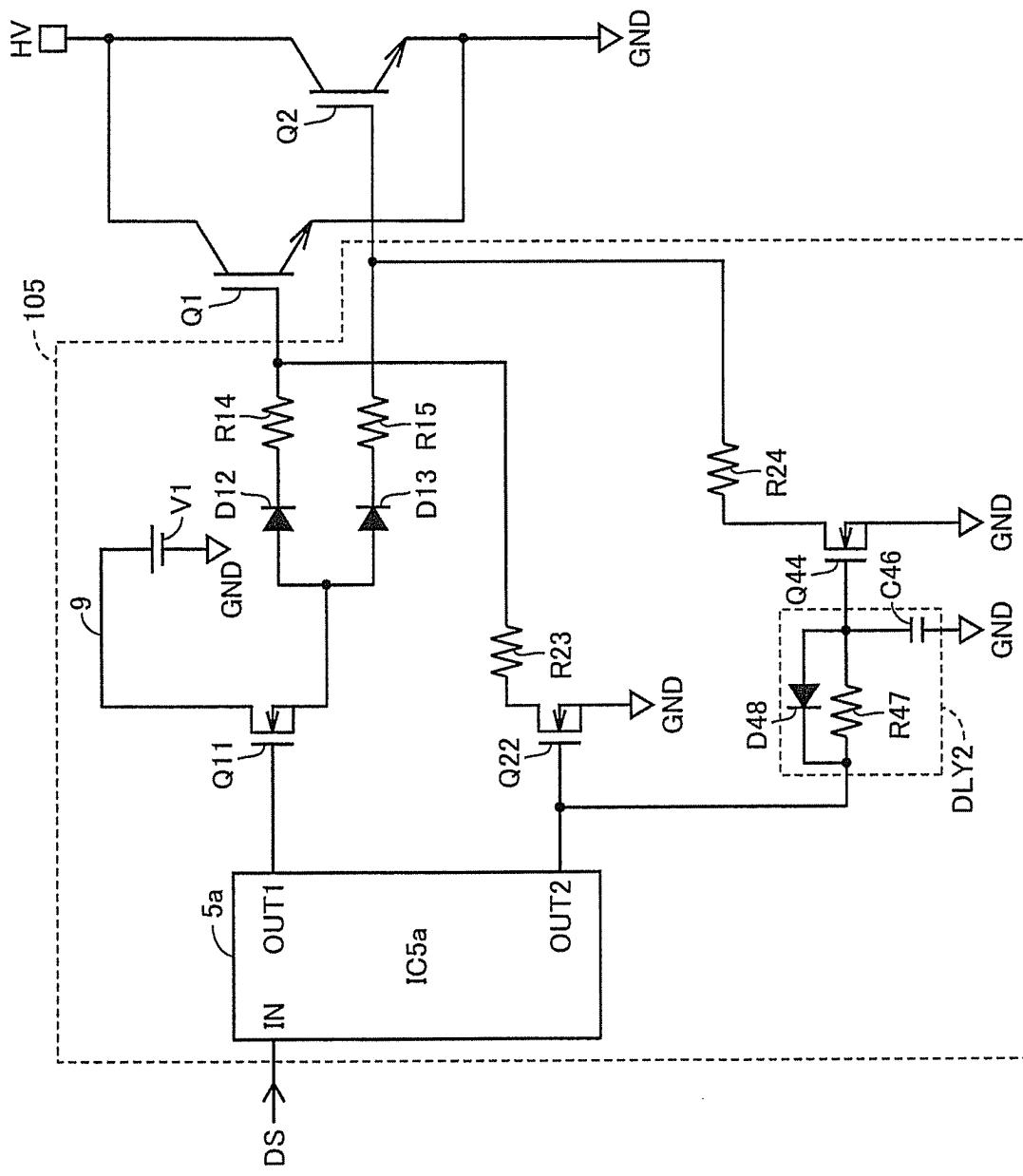

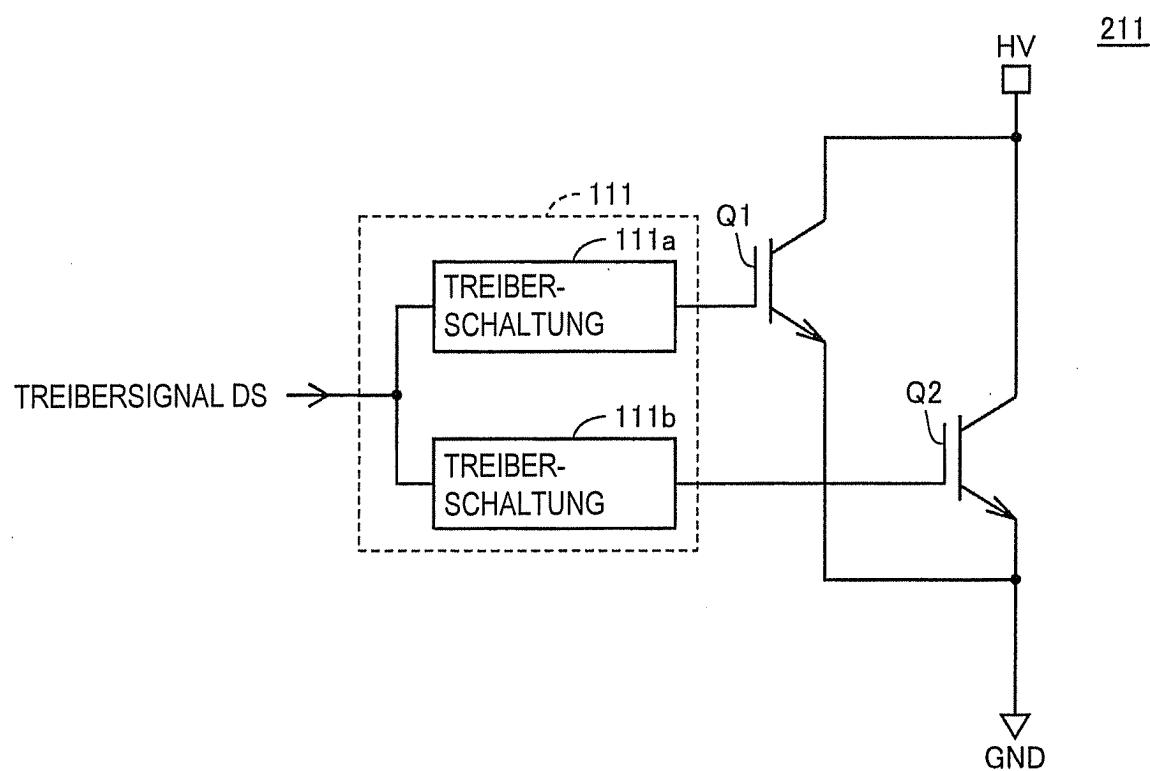

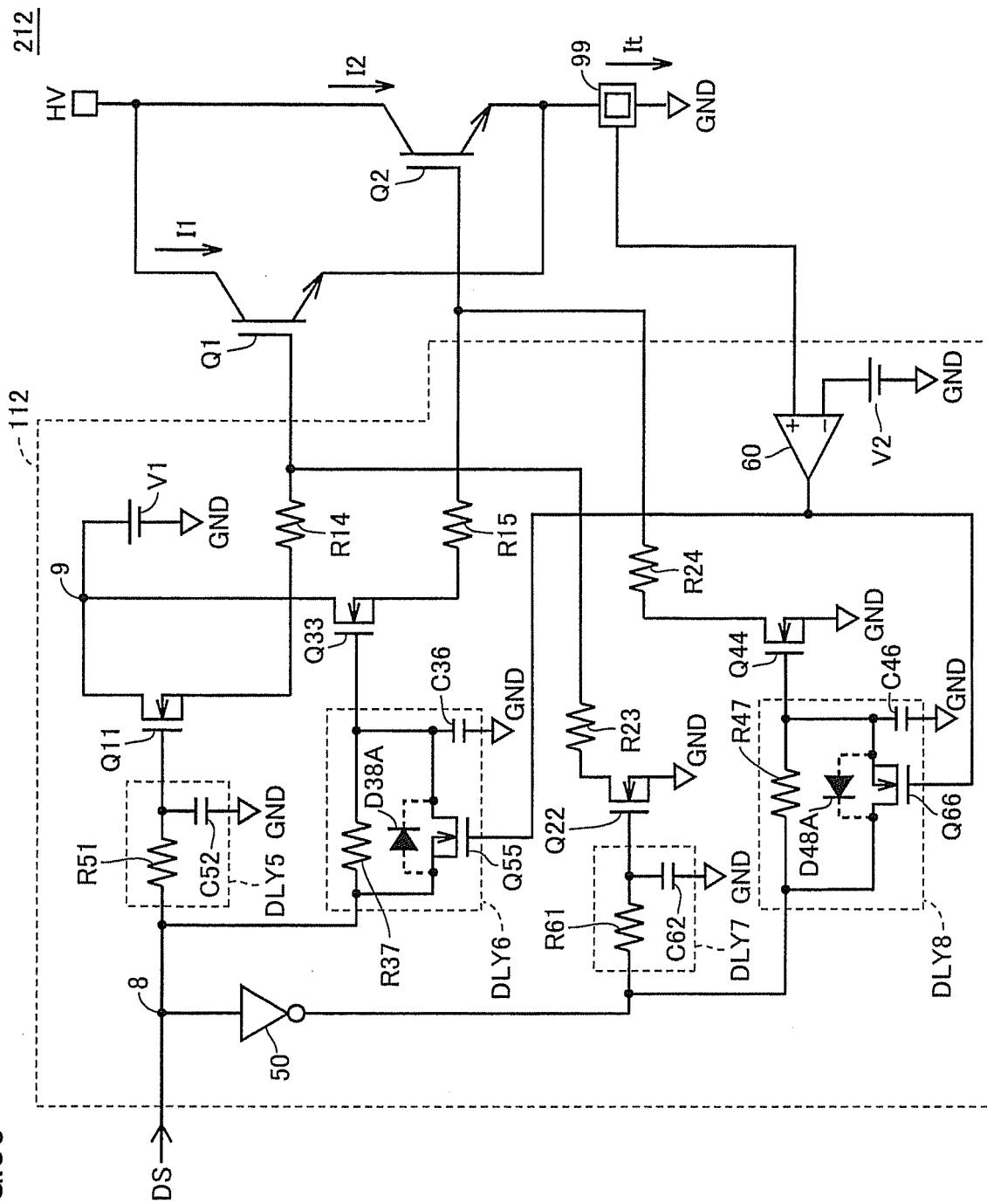

**[0033]** **Fig. 17** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer zweiten Ausführungsform.

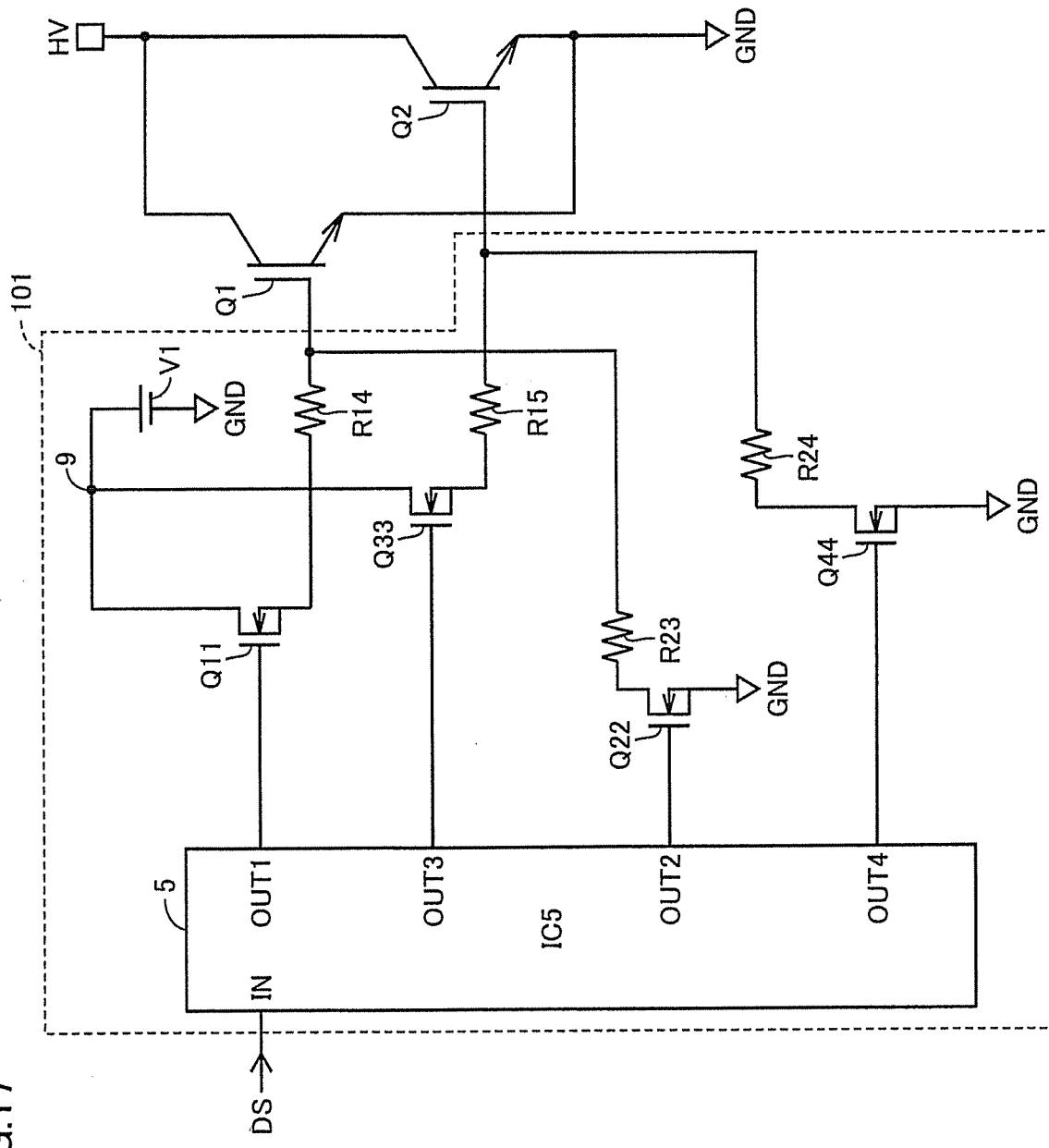

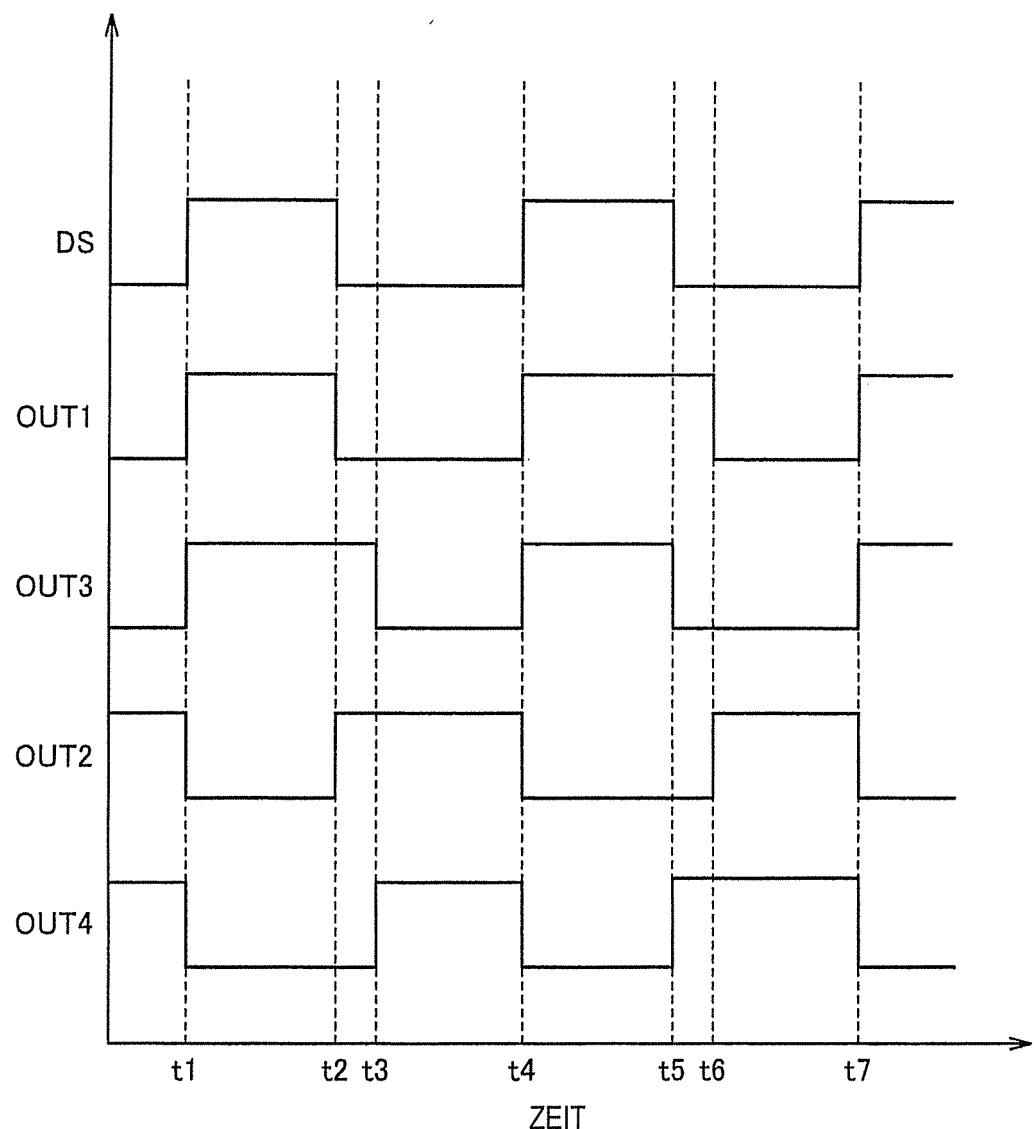

**[0034]** **Fig. 18** ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdigramm eines Steuersignals zeigt, das von einer in **Fig. 17** gezeigten integrierten Schaltung ausgegeben wird.

**[0035]** **Fig. 19** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer dritten Ausführungsform.

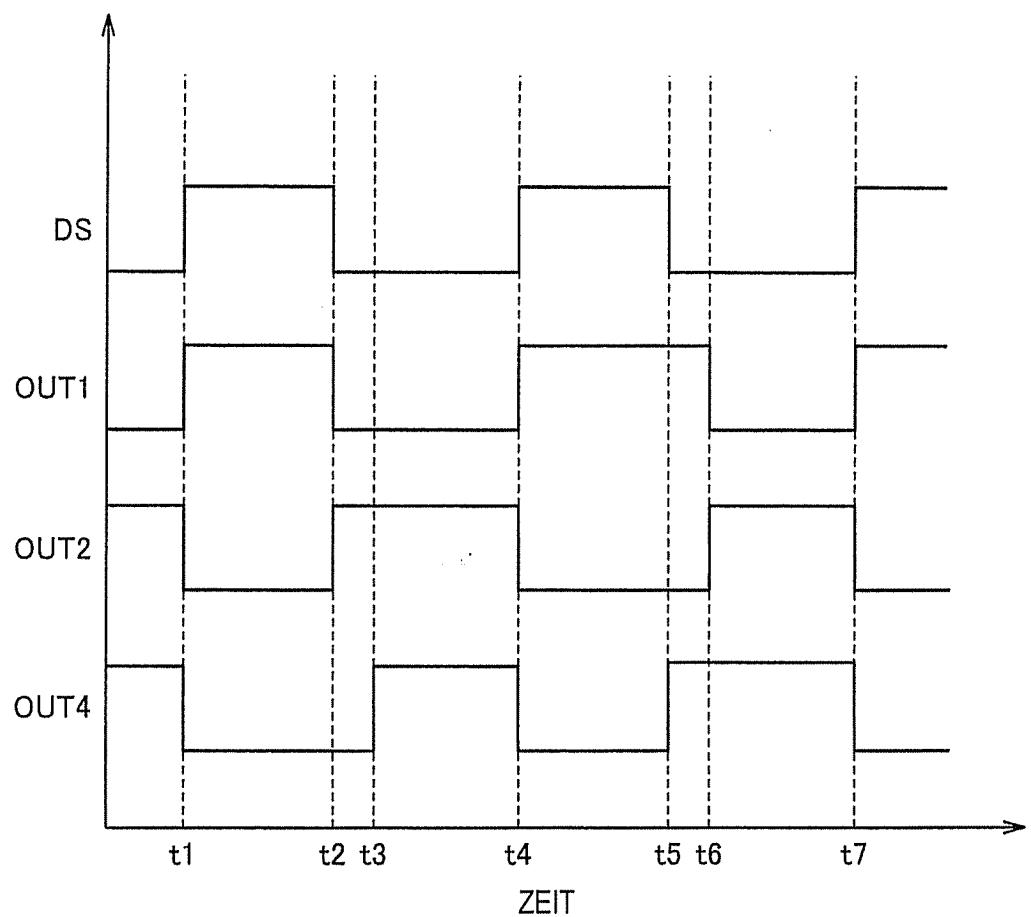

**[0036]** **Fig.** 20 ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von einer in **Fig.** 19 gezeigten integrierten Schaltung ausgegeben wird.

**[0037]** **Fig.** 21 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer vierten Ausführungsform.

**[0038]** **Fig.** 22 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer fünften Ausführungsform.

**[0039]** **Fig.** 23 ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von einer in **Fig.** 22 gezeigten integrierten Schaltung ausgegeben wird.

**[0040]** **Fig.** 24 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer sechsten Ausführungsform.

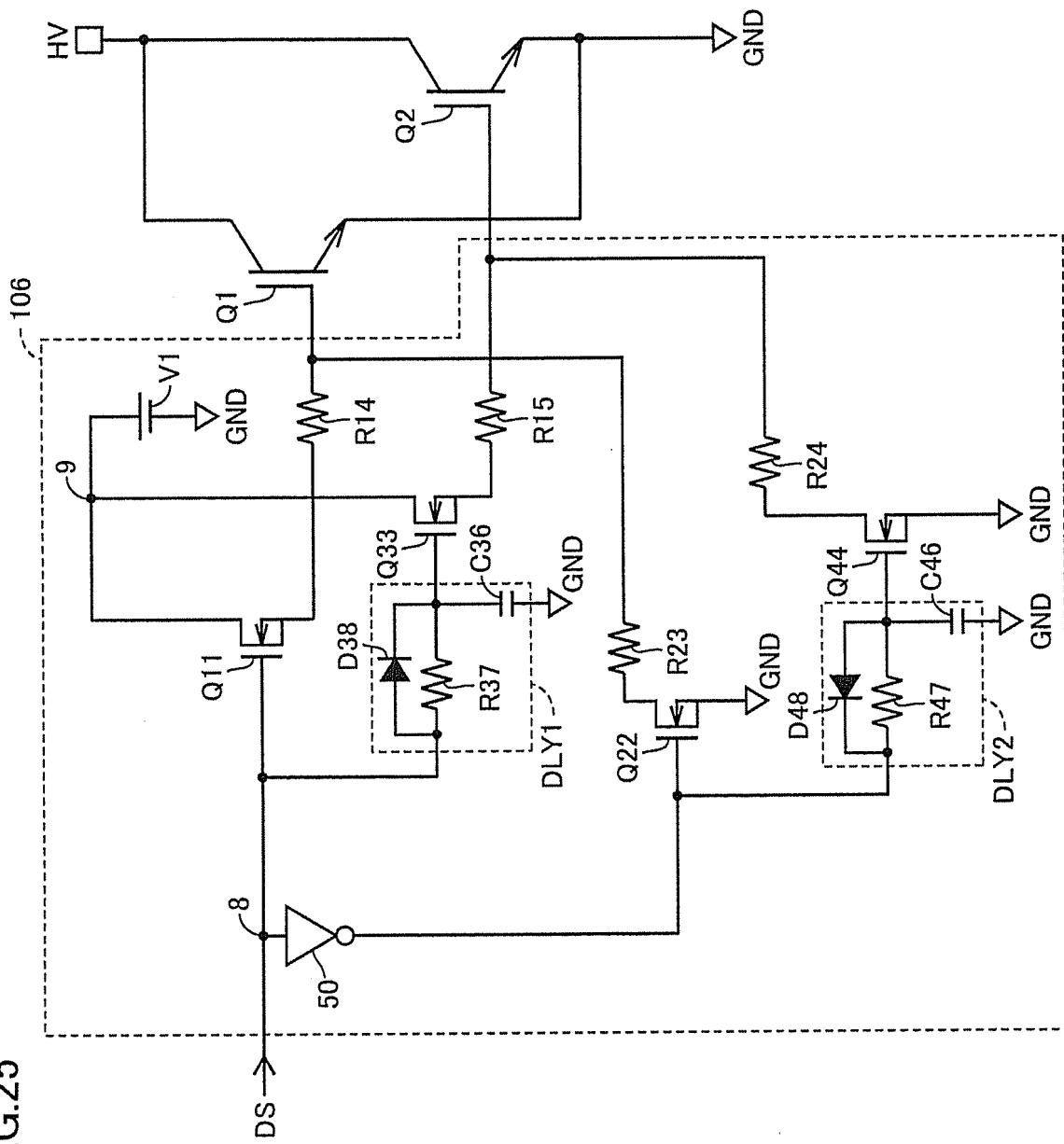

**[0041]** **Fig.** 25 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer siebten Ausführungsform.

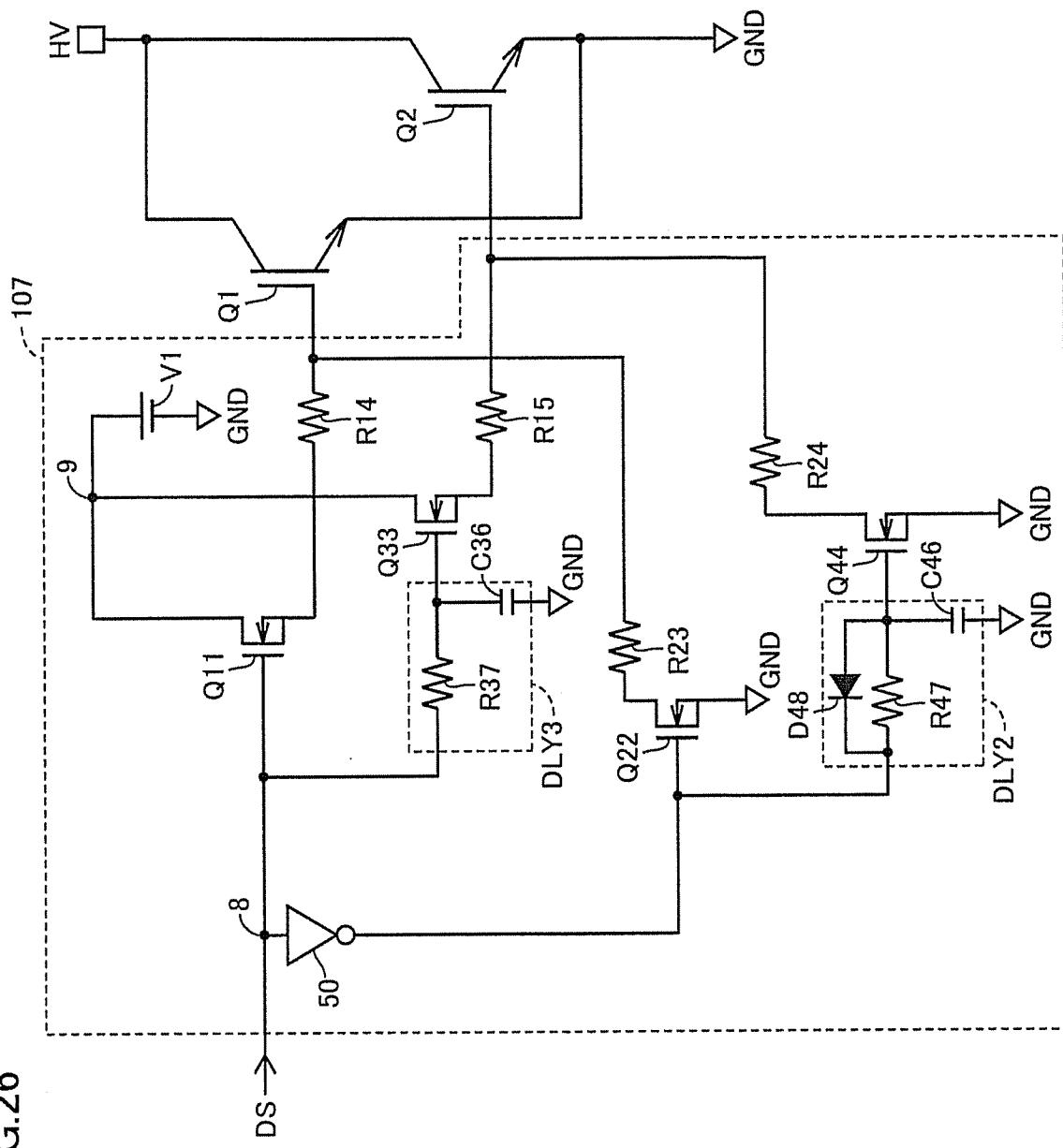

**[0042]** **Fig.** 26 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer achtten Ausführungsform.

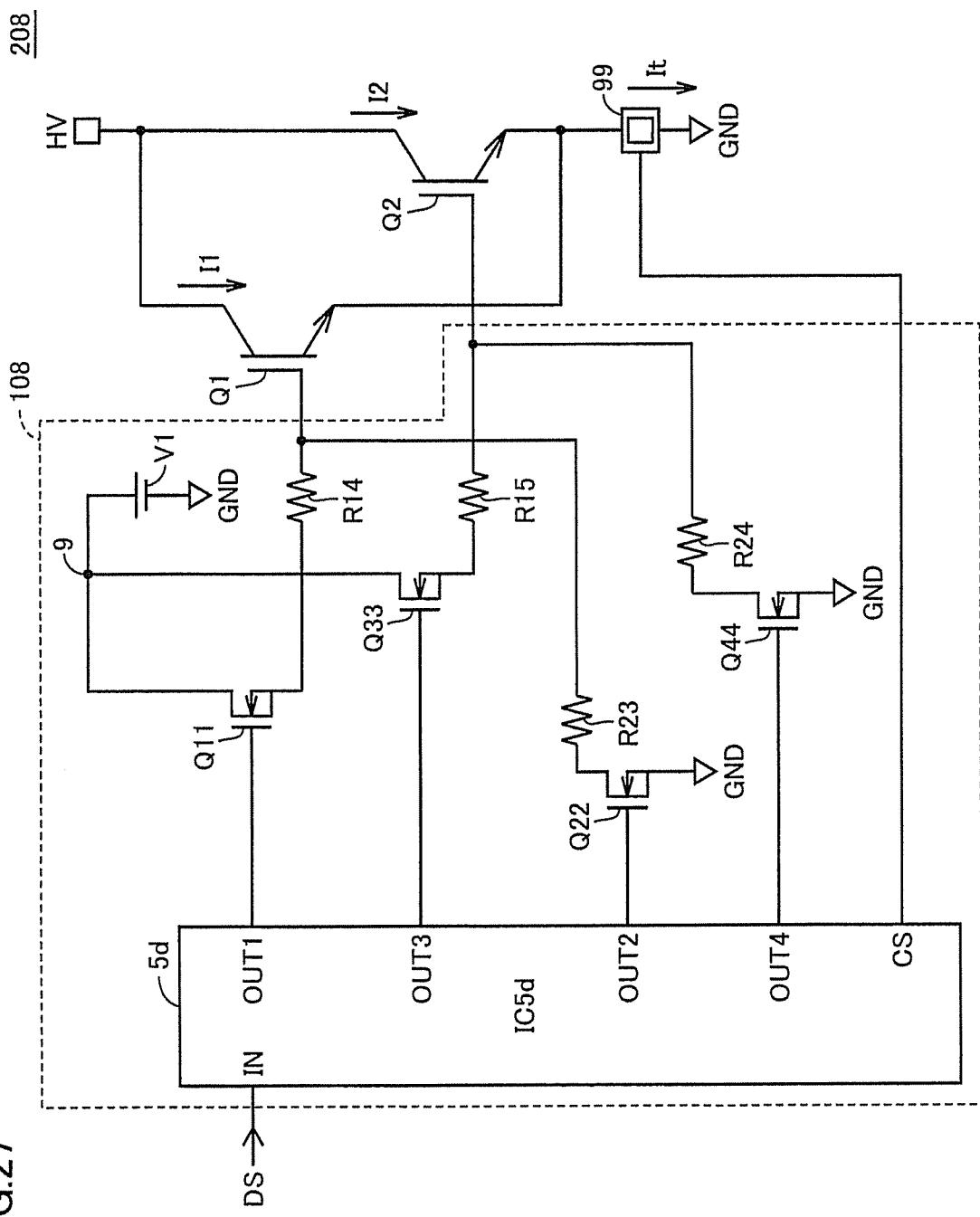

**[0043]** **Fig.** 27 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer neunten Ausführungsform.

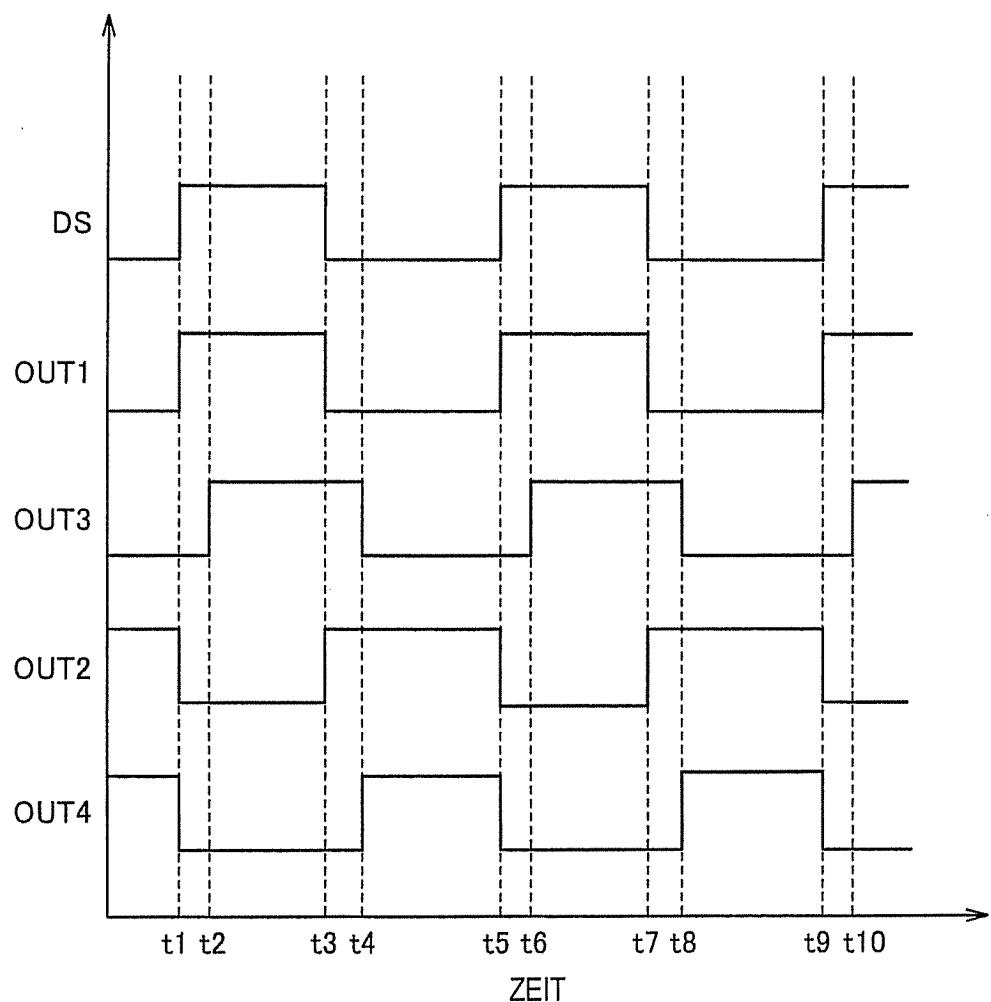

**[0044]** **Fig.** 28 ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von einer in **Fig.** 27 gezeigten integrierten Schaltung ausgegeben wird.

**[0045]** **Fig.** 29 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer zehnten Ausführungsform.

**[0046]** **Fig.** 30 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer elften Ausführungsform.

**[0047]** **Fig.** 31 ist ein Diagramm zum Darstellen von Spezifikationen von IGBTs, die in einer Leistungshalbleitervorrichtung gemäß einer zwölften Ausführungsform enthalten sind.

**[0048]** **Fig.** 32 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer Abwandlung einer dreizehnten Ausführungsform.

**[0049]** **Fig.** 33 ist ein Diagramm, das für eine vierzehnte Ausführungsform eine Abwandlung des Steuers des Schaltens der IGBTs durch Triebsteuer-einheiten in den Leistungshalbleitervorrichtung ge-

mäß der zweiten, neunten und zehnten Ausführungs-form zeigt.

**[0050]** **Fig.** 34 ist ein Diagramm, das für eine fünfzehnte Ausführungsform eine Abwandlung des Steuers des Schaltens der IGBTs durch Triebsteuer-einheiten in den Leistungshalbleitervorrichtung ge-mäß der fünften und elften Ausführungsform zeigt.

**[0051]** **Fig.** 35 ist ein Diagramm, das für eine sechzehnte Ausführungsform eine weitere Abwandlung des Steuers des Schaltens der IGBTs durch Triebsteuer-einheiten in den Leistungshalbleitervorrichtung gemäß der zweiten, neunten und zehnten Aus-führungsform zeigt.

**[0052]** **Fig.** 36 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer neunzehnten Ausführungsform.

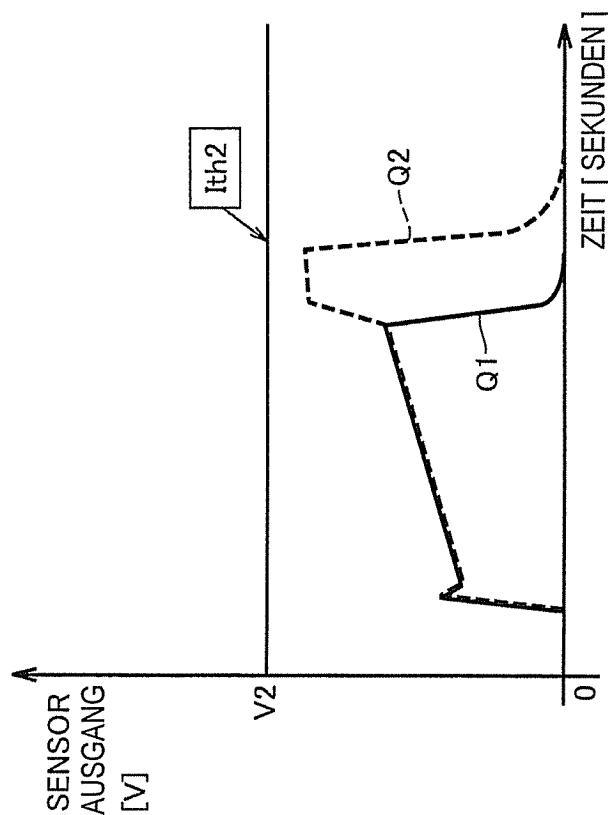

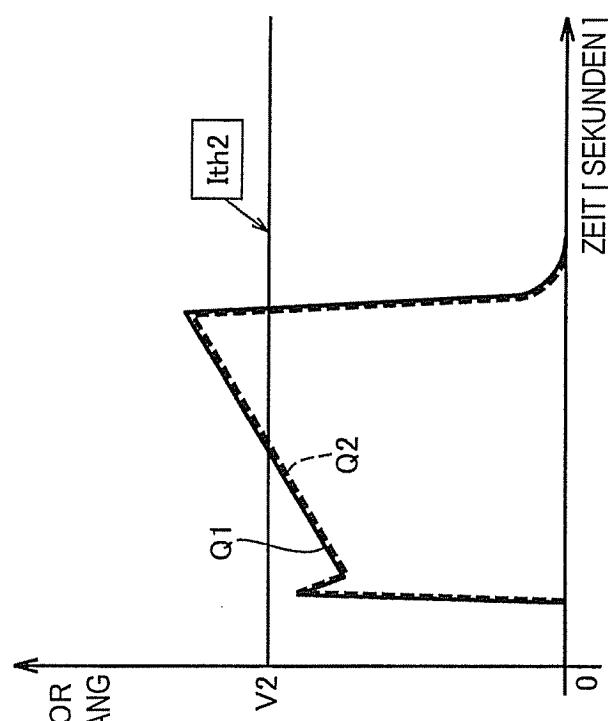

**[0053]** **Fig.** 37A ist ein Diagramm, das ein Beispiel für einen Signalverlauf zeigt, der von einem in **Fig.** 36 gezeigten Stromerfassungssensor ausgegeben wird, wenn eine Ausgabe des Stromerfassungssensors nicht eine Referenzspannung überschreitet, die ei-nem Schwellenwert entspricht.

**[0054]** **Fig.** 37B ist ein Diagramm, das ein Beispiel für einen Signalverlauf zeigt, der von einem in **Fig.** 36 gezeigten Stromerfassungssensor ausgegeben wird, wenn eine Ausgabe des Stromerfassungssensors die Referenzspannung überschreitet, die dem Schwellenwert entspricht.

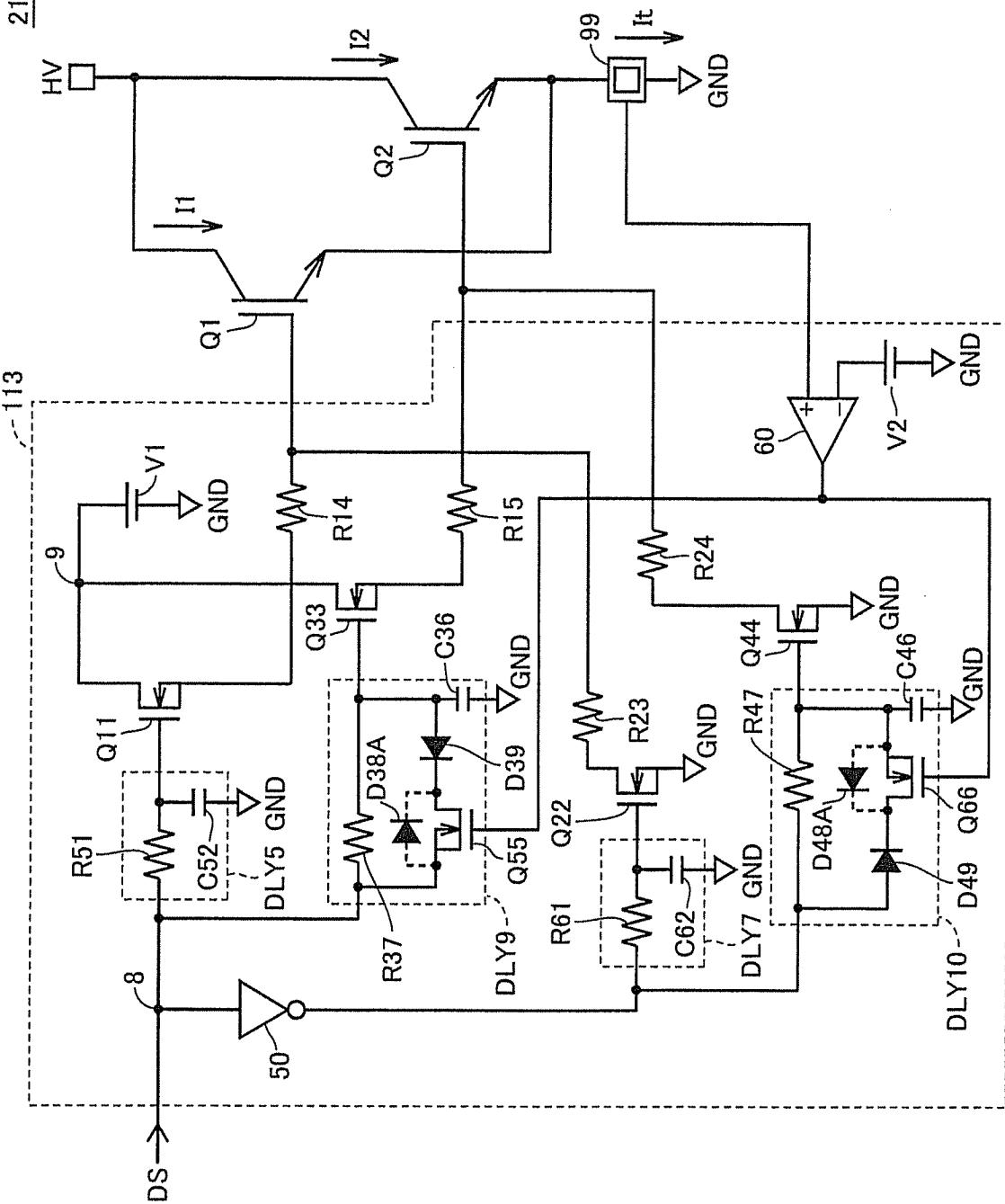

**[0055]** **Fig.** 38 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer zwan-zigsten Ausführungsform.

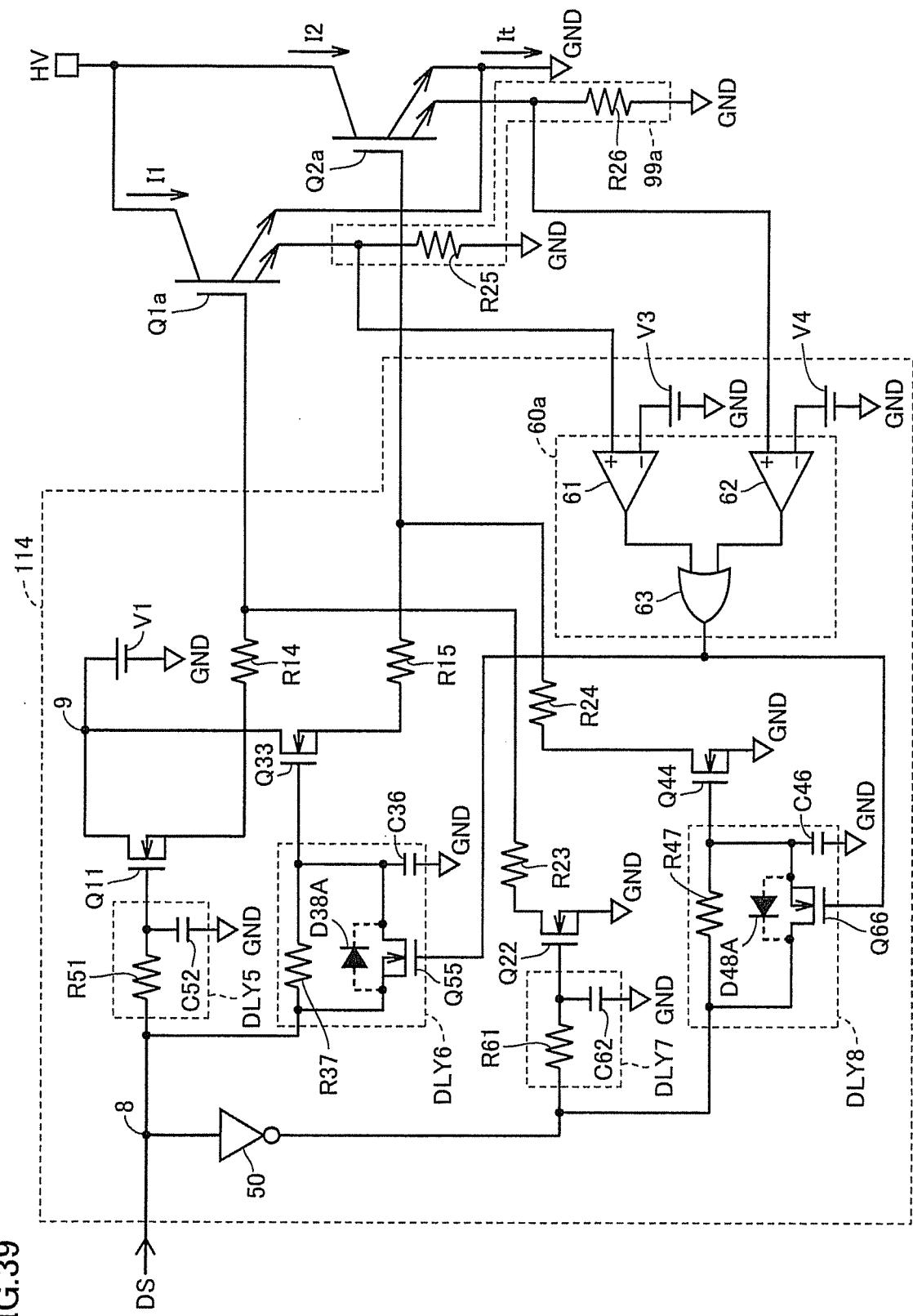

**[0056]** **Fig.** 39 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer einund-zwanzigsten Ausführungsform.

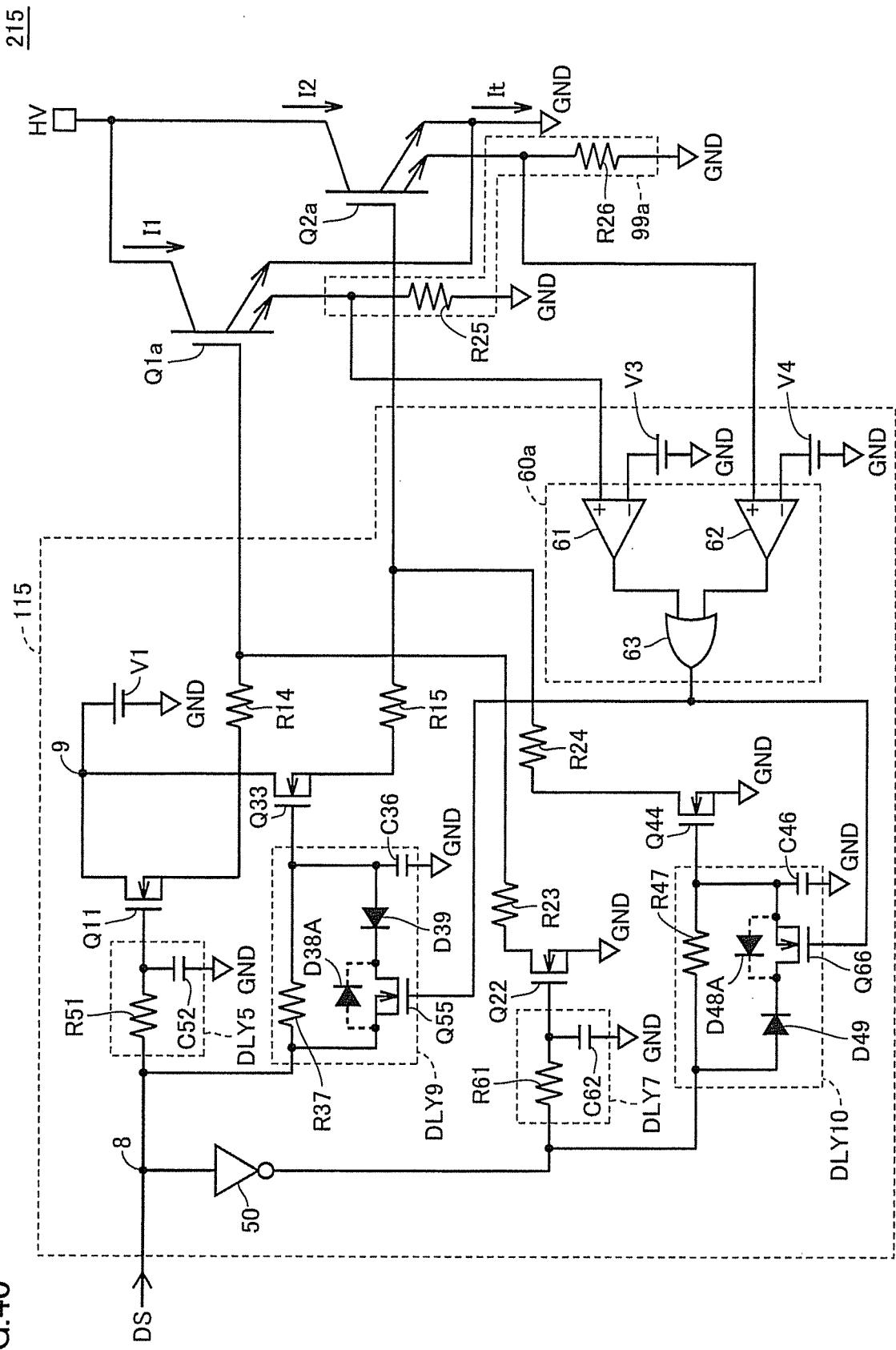

**[0057]** **Fig.** 40 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer zweiund-zwanzigsten Ausführungsform.

**[0058]** Mit Bezug auf die Zeichnungen werden im folgenden Ausführungsformen von Leistungshal-bleitervorrichtungen im Detail beschrieben. Davon sind die in der ersten bis achtten Ausführungsform beschriebenen Leistungshalbleitervorrichtungen kei-ne Leistungshalbleitervorrichtungen gemäß der vor-liegenden Erfindung, weil ihnen der beanspruchte Stromfassungsabschnitt fehlt. Sie beschreiben je-doch bereits Merkmale der erfindungsgemäßen Aus-führungsformen und dienen daher als Erläuterungs-beispiele zum besseren Verständnis der vorliegen-den Erfindung.

**[0059]** Es sei angemerkt, dass dieselben oder einander entsprechende Elemente durch dieselben Bezeichnungen gekennzeichnet sind und ihre Beschreibung nicht wiederholt wird.

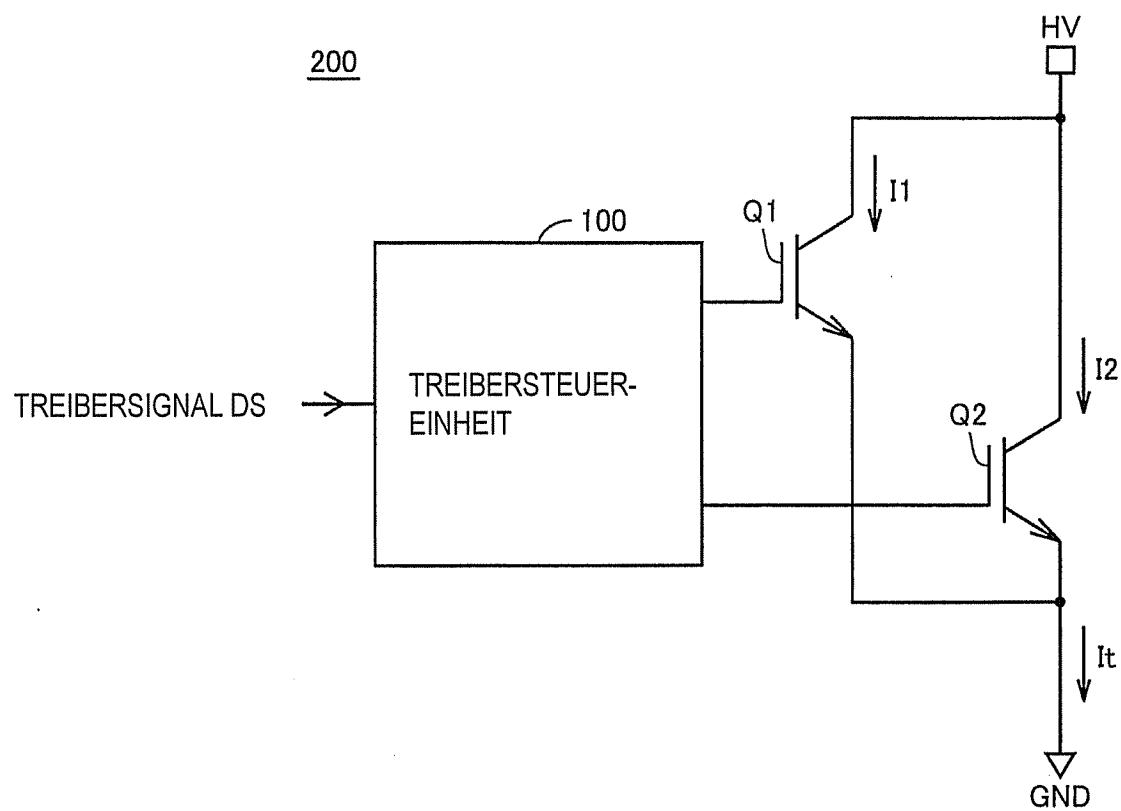

**[0060]** **Fig. 1** ist ein Diagramm eines Aufbaus einer Leistungshalbleitervorrichtung gemäß einer ersten Ausführungsform. Mit Bezug auf **Fig. 1** enthält die Leistungshalbleitervorrichtung **200** die Leistungshalbleiterelemente Q1 und Q2, die parallel zueinander zwischen einen Hochspannungsknoten HV und einen Masseknoten GND geschaltet sind, und eine Treibersteuereinheit **100**. Auch wenn in **Fig. 1** als Beispiel ein IGBT als Leistungshalbleiterelement Q1, Q2 dargestellt ist, können auch andere Halbleiterelemente wie z. B. ein Leistungs-MOSFET oder ein Bipolartransistor verwendet werden. Die Leistungshalbleiterelemente Q1, Q2 werden im folgenden jeweils auch als IGBTs Q1, Q2 bezeichnet. Der Hochspannungsknoten HV, mit dem die Kollektoren der IGBTs Q1, Q2 jeweils verbunden sind, ist mit der zu steuernden elektrischen Einrichtung verbunden, und eine hohe Spannung liegt an ihm an.

**[0061]** Die Treibersteuerschaltung **100** schaltet die IGBTs Q1, Q2 in Übereinstimmung mit einem Logikpegel eines von außen empfangenen Treibersignals DS ein oder aus. In dieser Ausführungsform wird angenommen, dass die Treibersteuereinheit **100** die Leistungshalbleiterelemente Q1, Q2 einschaltet, wenn sie das Treibersignal DS auf einem hohen Pegel (H-Pegel) empfängt, und dass sie die Leistungshalbleiterelemente Q1, Q2 ausschaltet, wenn sie das Treibersignal DS auf einem niedrigen Pegel (L-Pegel) empfängt. Das Treibersignal DS auf H-Pegel wird auch als Einschaltbefehl bezeichnet, während das Treibersignal DS auf L-Pegel auch als Ausschaltbefehl bezeichnet wird. Der Einschaltbefehl und der Ausschaltbefehl werden der Treibersteuereinheit **100** abwechselnd und wiederholt zugeführt. Ein bestimmtes Aufbaubeispiel der Treibersteuereinheit **100** wird in der zweiten und den folgenden Ausführungsformen beschrieben.

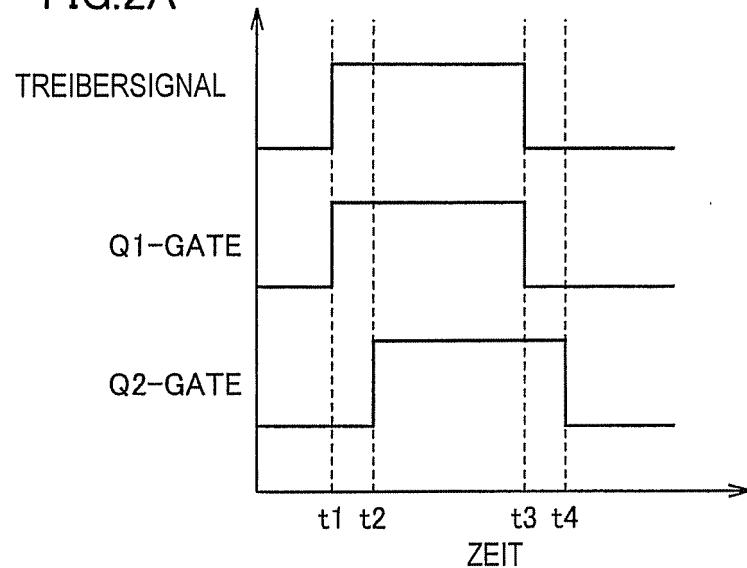

**[0062]** **Fig. 2A–Fig. 2C** sind Zeitverlaufsdigramme, die eine Beziehung zwischen dem Treibersignal DS und den Gatespannungen der Leistungshalbleiterelemente Q1, Q2 zeigen. Mit Bezug auf **Fig. 1** und **Fig. 2A–Fig. 2C** kann die Treibersteuereinheit **100**, wenn sie den Einschaltbefehl empfängt und die IGBTs Q1, Q2 einschaltet, zwischen einem Fall, in dem die IGBTs Q1, Q2 gleichzeitig eingeschaltet werden, und einem Fall, in dem einer der IGBTs Q1, Q2 (beispielsweise IGBT Q1) zuerst eingeschaltet wird und dann der andere IGBT eingeschaltet wird, umschalten. Wenn die Treibersteuereinheit **100** den Ausschaltbefehl erhält und die IGBTs Q1, Q2 ausschaltet, kann sie außerdem zwischen einem Fall, in dem die IGBTs Q1, Q2 gleichzeitig ausgeschaltet werden, und einem Fall, in dem einer der IGBTs Q1,

Q2 (beispielsweise der IGBT Q1) zuerst ausgeschaltet wird und danach der andere IGBT ausgeschaltet wird, umschalten. Ob die IGBTs Q1, Q2 gleichzeitig geschaltet werden sollen oder ob sie unabhängig voneinander zu unterschiedlichen Zeiten geschaltet werden sollen, kann bestimmt werden basierend auf der Größe der Hauptströme I1, I2 oder des Gesamtstroms It, der eine Kombination der Hauptströme I1 und I2 ist, die jeweils durch die IGBTs Q1, Q2 fließen, wenn die IGBTs Q1, Q2 als Reaktion auf den Einschaltbefehl eingeschaltet (leitend) sind. Insbesondere ist in der ersten Ausführungsform der Gesamtstrom It, der durch die Halbleiterleistungselemente Q1, Q2 fließt, basierend auf seiner Größe in drei Bereiche eingeteilt.

**[0063]** **Fig. 2A** zeigt einen Fall, in dem die Größe des Gesamtstroms It relativ klein ist. Wenn das Treibersignal S zum Zeitpunkt t1 vom L-Pegel zum H-Pegel wechselt, schaltet die Treibersteuereinheit **100** den IGBT Q1 ein, indem sie eine Spannung auf H-Pegel an das Gate des IGBT Q1 anlegt. Zu einem nachfolgenden Zeitpunkt t2 schaltet die Treibersteuereinheit **100** den IGBT Q2 ein durch Anlegen einer Spannung auf H-Pegel an das Gate des IGBT Q2. Wenn das Treibersignal DS zum Zeitpunkt t3 vom H-Pegel zum L-Pegel wechselt, schaltet die Treibersteuereinheit **100** den IGBT Q1 aus durch Anlegen einer Spannung auf L-Pegel an das Gate des IGBT Q1. Zu einem nachfolgenden Zeitpunkt t4 schaltet die Treibersteuereinheit **100** den IGBT Q2 aus durch Anlegen einer Spannung auf L-Pegel an das Gate des IGBT Q2. Daher wird beim Einschalten ein Schaltverlust (Einschaltverlust Eon) hauptsächlich in dem IGBT Q1 bewirkt, der zuerst eingeschaltet wird, während beim Ausschalten ein Schaltverlust (Ausschaltverlust Eoff) hauptsächlich in dem IGBT Q2 bewirkt wird, der nachfolgend ausgeschaltet wird.

**[0064]** **Fig. 2B** zeigt einen Fall, in dem die Größe des Gesamtstroms It mittelgroß ist. Wenn das Treibersignal DS zum Zeitpunkt t1 vom L-Pegel zum H-Pegel wechselt, schaltet die Treibersteuereinheit **100** hierbei die IGBTs Q1, Q2 gleichzeitig ein durch Anlegen einer Spannung auf H-Pegel an die Gates beider IGBTs Q1, Q2. Wenn das Treibersignal DS zum Zeitpunkt t3 vom H-Pegel zum L-Pegel wechselt, schaltet die Treibersteuereinheit **100** den IGBT Q1 aus durch Anlegen einer Spannung auf L-Pegel an das Gate des IGBT Q1. Zum nachfolgenden Zeitpunkt t4 schaltet die Treibersteuereinheit **100** den IGBT Q2 aus durch Anlegen einer Spannung auf L-Pegel an das Gate des IGBT Q2. Daher wird beim Einschalten ein Schaltverlust (Einschaltverlust Eon) in beiden IGBTs Q1, Q2 bewirkt. Beim Ausschalten wird ein Schaltverlust (Ausschaltverlust Eoff) hauptsächlich in dem IGBT Q2 bewirkt, der nachfolgend ausgeschaltet wird.

**[0065]** **Fig. 2C** zeigt einen Fall, in dem die Größe des Gesamtstroms  $I_t$  relativ groß ist. Wenn das Treibersignal DS in diesem Fall zum Zeitpunkt  $t_1$  vom L-Pegel zum H-Pegel wechselt, schaltet die Steuereinheit **100** die IGBTs Q1, Q2 gleichzeitig an durch Anlegen einer Spannung auf H-Pegel an die Gates beider IGBTs Q1, Q2. Wenn das Treibersignal DS zum Zeitpunkt  $t_3$  vom H-Pegel zum L-Pegel wechselt, schaltet die Treibersteuereinheit **100** die IGBTs Q1, Q2 gleichzeitig aus durch Anlegen einer Spannung auf L-Pegel an die Gates beider IGBTs Q1, Q2. Daher wird sowohl beim Einschalten als auch beim Ausschalten ein Schaltverlust in beiden IGBTs Q1, Q2 bewirkt.

**[0066]** Auch wenn in der obigen Beschreibung beim aufeinanderfolgenden Schalten der IGBTs Q1, Q2 zu unterschiedlichen Zeitpunkten der IGBT Q1 früher ein- oder ausgeschaltet wird als der IGBT Q2, kann ein beliebiger von ihnen zuerst geschaltet werden, wenn die IGBTs Q1, Q2 identische Eigenschaften haben.

**[0067]** Es werden nun die Gründe beschrieben, warum das Schalten der IGBTs Q1, Q2 mit dem obigen Verfahren gesteuert wird.

**[0068]** **Fig. 3A** ist ein Diagramm, das eine Beziehung zwischen der Größe des Gesamtstroms  $I_t$ , der durch die IGBTs Q1, Q2 im eingeschalteten Zustand fließt, und der Größe eines Einschaltverlusts  $E_{on}$  zeigt. **Fig. 3B** ist ein Diagramm, das eine Beziehung zwischen der Größe eines Gesamtstroms, der durch die IGBTs im eingeschalteten Zustand fließt, und der Größe eines Ausschaltverlusts  $E_{off}$  zeigt. In **Fig. 3A** und **Fig. 3B** sind der Einschaltverlust  $E_{on}$  und der Ausschaltverlust  $E_{off}$  als elektrische Leistung in  $mJ$  angegeben, die pro Puls des Treibersignals DS verbraucht wird. Ein Fall, in dem die IGBTs Q1, Q2 jeweils alleine mit unterschiedlichem Zeitablauf geschaltet werden, ist als "1 CHIP" (1P) bezeichnet, während ein Fall, in dem die IGBTs Q1, Q2 gleichzeitig geschaltet werden als "2 CHIP" (2P) bezeichnet ist.

**[0069]** Mit Bezug auf **Fig. 3A** führt das Einschalten der IGBTs Q1, Q2 alleine mit unterschiedlichem Zeitablauf, wenn der Gesamtstrom  $I_t$ , der durch die IGBTs Q1, Q2 fließt, kleiner als ein bestimmter Schwellenwert  $I_{th1}$  ist, zu einem geringeren Einschaltverlust  $E_{on}$  als in einem Fall, in dem die IGBTs Q1, Q2 gleichzeitig eingeschaltet werden. In einem Fall, in dem der Gesamtstrom größer als der Schwellenwert  $I_{th1}$  ist, führt das gleichzeitige Einschalten der IGBTs Q1, Q2 zu einem geringeren Einschaltverlust  $E_{on}$  als in einem Fall, in dem die IGBTs Q1, Q2 jeweils alleine eingeschaltet werden. Wenn der Gesamtstrom kleiner gleich dem Schwellenwert  $I_{th1}$  ist, schaltet die Treibersteuereinheit **100** in **Fig. 1** deshalb zuerst den IGBT Q1 an, und anschließend schaltet sie den IGBT Q2 an, wie es in **Fig. 2A** gezeigt ist.

Wenn der Gesamtstrom  $I_t$  größer als der Schwellenwert  $I_{th1}$  ist, schaltet die Treibersteuereinheit **100** die IGBTs Q1, Q2 gleichzeitig an, wie es in **Fig. 2B** gezeigt ist. Somit kann der Einschaltverlust  $E_{on}$  verglichen mit dem herkömmlichen Beispiel verringert werden.

**[0070]** Mit Bezug auf **Fig. 3B** führt im Fall des Ausschaltverlusts  $E_{off}$  das gleichzeitige Ausschalten der IGBT Q1, Q2 mit unterschiedlichen Zeitabläufen unabhängig von der Größe des Gesamtstroms  $I_t$ , der durch die IGBTs Q1, Q2 im leitenden Zustand fließt, zu einem kleineren Ausschaltverlust als in einem Fall, in dem sie gleichzeitig eingeschaltet werden. Wie in **Fig. 2A** und **Fig. 2B** gezeigt, schaltet die Treibersteuereinheit **100** in **Fig. 1** daher zuerst den IGBT Q1 ein, und anschließend schaltet sie den IGBT Q2 ein. Somit kann der Ausschaltverlust  $E_{off}$  verglichen mit einem Fall, in dem die IGBTs Q1, Q2 gleichzeitig eingeschaltet werden, verringert werden.

**[0071]** Es sei angemerkt, dass in einem Fall, in dem die IGBTs Q1, Q2 jeweils alleine ausgeschaltet werden, der Gesamtstrom  $I_t$ , der durch die IGBTs Q1, Q2 fließt, wenn er den Maximalwert pro Element überschreitet, ein Element zerstören kann, das nachfolgend ausgeschaltet wird. Um den Durchbruch eines Elements zu verhindern, werden die IGBTs Q1, Q2 dann, wenn der Gesamtstrom  $I_t$  nahe dem Maximalwert pro Element ist, gleichzeitig ausgeschaltet, wie es in **Fig. 2C** gezeigt ist.

**[0072]** **Fig. 4** ist ein Diagramm zum Darstellen eines Konzepts der Zeitablaufsteuerung beim Ausschalten der IGBTs Q1, Q2.

**[0073]** In Bezug auf **Fig. 4** wird der genannte Maximalwert eines Hauptstroms pro Element der IGBTs Q1, Q2 als  $IR$  angenommen. Ein Schwellenwert  $I_{th2}$  wird auf einen Wert eingestellt, der geringfügig kleiner ist als der angegebene Maximalwert  $IR$ , und ein Schwellenwert  $I_{th3}$  wird auf einen Wert gesetzt, der geringfügig kleiner ist als das Zweifache des angegebenen Maximalwerts  $IR$  ( $2 \times IR$ ). Wenn der Gesamtstrom  $I_t$ , der durch die IGBTs Q1, Q2 im leitenden Zustand fließt, kleiner ist als der Schwellenwert  $I_{th2}$ , steuert die Treibersteuereinheit **100** in **Fig. 1** die IGBTs Q1, Q2 so, dass jeder von ihnen als Reaktion auf den Ausschaltbefehl aufeinanderfolgend ausgeschaltet wird. Wenn der Gesamtstrom  $I_t$  größer gleich dem Schwellenwert  $I_{th2}$  und kleiner gleich dem Schwellenwert  $I_{th3}$  ist, steuert die Treibersteuereinheit **100** die IGBTs Q1, Q2 so, dass sie als Reaktion auf den Ausschaltbefehl gleichzeitig ausgeschaltet werden. Auch wenn verglichen mit einem Fall, in dem ein Element nachträglich ausgeschaltet wird, der Ausschaltverlust  $E_{off}$  ansteigt, wird eine solche Schaltsteuerung durchgeführt zum Schutz gegen das Kurzschließen eines IGBT. Wenn der Gesamtstrom größer gleich dem Schwellenwert  $I_{th3}$  ist, wird ein

Schutz gegen Kurzschluss bereitgestellt zum Steuern der IGBTs Q1, Q2 so, dass sie beide unabhängig von einem Logikpegel des Treibersignals DS ausgeschaltet werden.

**[0074]** Es werden nun die Gründe beschrieben, warum die in **Fig. 3A** und **Fig. 3B** gezeigten Schalteigenschaften erzielt werden.

**[0075]** **Fig. 5** ist ein Diagramm, das eine Beziehung zwischen einem Schaltverlust und einem Kollektorstrom des IGBT zeigt. **Fig. 5** zeigt in Abhängigkeit von dem Kollektorstrom  $I_c$  einen Einschaltverlust  $E_{on}$ , einen Ausschaltverlust  $E_{off}$  und einen Schaltverlust  $E_{err}$  bei einem Rückwärtserholungsvorgang. **Fig. 6** ist ein Diagramm, das eine Beziehung zwischen einem Schaltverlust und einem Gatewiderstand des IGBT zeigt. **Fig. 6** zeigt in Abhängigkeit von einem Gatewiderstand  $R_G$  einen Einschaltverlust  $E_{on}$ , einen Ausschaltverlust  $E_{off}$ , und einen Schaltverlust  $E_{err}$  in einem Rückwärtserholungsvorgang. Die in **Fig. 5** und **Fig. 6** gezeigten Kennlinien sind Datenblätter eines IGBT-Moduls (Modellnummer CM600HX-24A von Mitsubishi Electric Corporation) entnommen.

**[0076]** Mit Bezug auf **Fig. 5** wird der Ausschaltverlust  $E_{off}$  als Potenzfunktion des Kollektorstroms  $I_c$  ausgedrückt. Das bedeutet, dass der Ausschaltverlust  $E_{off}$  in dem in **Fig. 5** gezeigten doppeltlogarithmischen Diagramm proportional zu dem Kollektorstrom  $I_c$  ist. Wenn ein Exponent mit dem Symbol " $^a$ ", bezeichnet wird, kann der Ausschaltverlust  $E_{off}$  unter Verwendung von Konstanten  $a, b$  wie folgt ausgedrückt werden:

$$E_{off} = a \times I_c^b \quad (1)$$

**[0077]** Wenn ein Strom, der durch jeden der IGBTs Q1, Q2 in **Fig. 1** fließt, als  $I_0$  [in A] bezeichnet wird, wird der Ausschaltverlust  $E_{off\_1P}$ , wenn die Elemente einzeln ausgeschaltet werden, wie folgt ausgedrückt:

$$E_{off\_1P} = a \times (2 \times I_0)^b \quad (2)$$

**[0078]** Der Ausschaltverlust  $E_{off\_2P}$ , wenn zwei Elemente gleichzeitig ausgeschaltet werden, wird wie folgt ausgedrückt:

$$E_{off\_2P} = 2 \times a \times I_0^b \quad (3)$$

**[0079]** Ein Verhältnis zwischen den obigen Gleichungen (2) und (3) wird wie folgt ausgedrückt:

$$E_{off\_1P}/E_{off\_2P} = 2^{b-1} \quad (4)$$

**[0080]** Wenn  $b < 1$ , ist die unten gezeigte Beziehung erfüllt:

$$E_{off\_1P} < E_{off\_2P} \quad (5)$$

**[0081]** Die Beziehung  $b < 1$  bedeutet, dass eine Steigung des Graphen in **Fig. 5** kleiner 1 ist, und diese Beziehung  $b < 1$  ist normalerweise erfüllt.

**[0082]** Unter Verwendung eines spezifischen Zahlenwerts wird eine Verifizierung durchgeführt. Es sei angenommen, dass ein Hauptstrom von 200 A pro Element durch die in **Fig. 1** gezeigten IGBTs Q1, Q2 fließt, d. h.  $I_1 = I_2 = 200$  A. Der Gesamtstrom  $I_t$  ist dann 400 A. In Bezug auf **Fig. 5** ist der Ausschaltverlust, wenn der Kollektorstrom 200 A beträgt, etwa 41 mJ/Puls, und wenn der Kollektorstrom 400 A beträgt, ist der Ausschaltverlust  $E_{off}$  etwa 62 mJ/Puls. Daher beträgt der Ausschalterlust  $E_{off}$ , wenn zwei Elemente gleichzeitig ausgeschaltet werden, 82 mJ/Puls insgesamt, während der Ausschaltverlust  $E_{off}$ , wenn die Elemente einzeln ausgeschaltet werden, 62 mJ/Puls beträgt, weil der Verlust in einem Element erzeugt wird, das nachträglich ausgeschaltet wird. Somit führt das einzelne Ausschalten der Elemente zu einem geringeren Ausschaltverlust  $E_{off}$ .

**[0083]** Hinsichtlich des Ausschaltverlusts  $E_{off}$  sei angemerkt, dass der Ausschaltverlust  $E_{off}$  wie in **Fig. 6** gezeigt kaum von dem Gatewiderstand  $R_G$  abhängt, und es ist zu sehen, dass die Eigenschaften des Ausschaltverlusts  $E_{off}$  im Wesentlichen durch die Elementeigenschaften eines IGBT bestimmt sind. Die obigen Ergebnisse können qualitativ wie folgt betrachtet werden. **Fig. 7** ist ein Diagramm, das eine Beziehung zwischen einer Kollektorstromdichte  $J_c$  und einer Sättigungsspannung  $V_{CE(sat)}$  zeigt. Mit Bezug auf **Fig. 7** sei angemerkt, dass IGBTs Q1, Q2 mit identischen Eigenschaften und identischer Größe parallel geschaltet sind. Beim einzelnen Ausschalten eines Chips (1P) ist eine Querschnittsfläche eines Abschnitts, durch die ein Hauptstrom fließt, halb so groß wie in einem Fall, in dem zwei Chips gleichzeitig ausgeschaltet werden (2P), und daher ist die Kollektorstromdichte  $J_c$  für einen Chip doppelt so groß. Wenn die Kollektorstromdichte  $J_c$  steigt, steigt die Sättigungsspannung  $V_{CE(sat)}$ .

**[0084]** **Fig. 8** ist ein Diagramm, das eine Beziehung zwischen einem Ausschaltverlust  $E_{off}$  und der Sättigungsspannung  $V_{CE(sat)}$  zeigt. Mit Bezug auf **Fig. 8** genügen bei einem Bipolarelement der Ausschaltverlust  $E_{off}$  und die Sättigungsspannung  $V_{CE(sat)}$  einer Abwägungsbeziehung. Daher ist beim einzelnen Ausschalten der Chips (1P) der Ausschaltverlust  $E_{off}$  kleiner als beim gleichzeitigen Ausschalten der zwei Chips (2P). Natürlich ist der Dauerverlust, wenn die IGBTs Q1, Q2 als Reaktion auf den Einschaltbefehl leitend sind, sowohl beim aufeinanderfolgenden Ausschalten (1P) als auch beim gleichzeitigen Ausschalten (2P) derselbe.

**[0085]** Mit Bezug wieder auf **Fig. 5** kann der Einschaltverlust Eon im Wesentlichen als Exponentialfunktion des Kollektorstroms  $I_C$  ausgedrückt werden. In dem in **Fig. 5** gezeigten doppeltlogarithmischen Diagramm erfüllen der Einschaltverlust Eon und der Kollektorstrom  $I_C$  keine direkt proportionale Beziehung. Daher kann der Einschaltverlust unter Verwendung von Konstanten  $a, b$  wie folgt dargestellt werden:

$$Eon = a \times \exp(I_C \times b) \quad (6)$$

**[0086]** In der obigen Gleichung (6) stellt "exp(...)" eine Exponentialfunktion dar.

**[0087]** Unter der Bezeichnung eines Stroms, der durch jeden der IGBTs Q1, Q2 in **Fig. 1** fließt, als  $I_o$  [a] wird der Einschaltverlust  $Eon\_1P$ , wenn die Elemente einzeln eingeschaltet werden, wie folgt dargestellt:

$$Eon\_1P = a \times \exp(2 \times I_o \times b) \quad (7)$$

**[0088]** Der Einschaltverlust  $Eon\_2P$ , wenn zwei Elemente gleichzeitig eingeschaltet werden, wird wie folgt dargestellt:

$$Eon\_2P = 2 \times a \times \exp(I_o \times b) \quad (8)$$

**[0089]** Ein Verhältnis zwischen den Gleichungen (7) und (8) wird wie folgt dargestellt:

$$Eon\_1P/Eon\_2P = \exp(I_o \times b)/2 \quad (9)$$

**[0090]** Deshalb ist in einem Bereich eines relativ niedrigen Stroms, wo die Beziehung  $I_o < b \times \ln(2)$  erfüllt, wobei in einen natürlichen Logarithmus darstellt, die folgende Beziehung erfüllt:

$$Eon\_1P < Eon\_2P \quad (10)$$

**[0091]** In einem Bereich eines relativ großen Stroms, in dem die Beziehung  $I_o > b \times \ln(2)$  erfüllt ist, ist die folgende Beziehung erfüllt:

$$Eon\_1P > Eon\_2P \quad (11)$$

**[0092]** **Fig. 9** ist ein Diagramm, das eine Beziehung zwischen dem Kollektorstrom  $I_C$  und dem Einschaltverlust Eon des IGBT zeigt. Mit Bezug auf **Fig. 9** sei angenommen, dass ein Kollektorstrom  $I_o$  durch jeden der parallel geschalteten IGBTs Q1, Q2 im eingeschalteten Zustand fließt, und der Einschaltverlust Eon, der dem Kollektorstrom  $I_o$  entspricht, wird als  $Eo$  in  $\text{mJ}/\text{Puls}$  bezeichnet. Daher ist der Einschaltverlust Eon beim gleichzeitigen Einschalten von zwei Elementen  $2 \times Eo$  (ein Punkt 2P in **Fig. 9**). Beim aufeinanderfolgenden einzelnen Einschalten der Elemente fließt zunächst durch ein Element, das zuerst eingeschaltet wird, ein Strom von  $2 \times I_o$ , und daher ist der

Einschaltverlust Eon in diesem Fall  $Eo'$  (ein Punkt 1P in **Fig. 9**).

**[0093]** Da der Einschaltverlust Eon exponentiell mit dem Ansteigen des Kollektorstroms  $I_C$  ansteigt, ist der Verlust  $Eo'$  größer als  $2 \times Eo$ , wenn der Strom  $I_o$  relativ groß ist, wie es in **Fig. 9** gezeigt ist. Deshalb führt ein gleichzeitiges Einschalten von zwei Elementen zu einem niedrigeren Verlust. Wenn dagegen  $I_o$  relativ klein ist, ist der Verlust  $Eo'$  kleiner als  $2 \times Eo$ . Daher führt ein aufeinanderfolgendes einzelnes Einschalten der Elemente zu einem niedrigeren Verlust.

**[0094]** Es sei angemerkt, dass es nicht nur der Kollektorstrom  $I_C$  ist, der für den Einschaltverlust Eon relevant ist. Wie in **Fig. 6** gezeigt, weist der Einschaltverlust Eon eine exponentielle Beziehung mit dem Gatewiderstand  $RG$  auf. Wenn der Gatewiderstand  $RG$  ansteigt, steigt nämlich der Einschaltverlust Eon exponentiell an. Außerdem sind eine Kapazität eines IGBT (eine Eingangskapazität, eine Spiegelkapazität) und Eigenschaften einer Freilaufdiode ebenso relevant für den Einschaltverlust.

**[0095]** **Fig. 10–Fig. 15** und **Fig. 16A** und **Fig. 16B** zeigen Simulationsergebnisse in Verbindung mit parallel geschalteten IGBTs. Bei den in **Fig. 10–Fig. 15** gezeigten Signalverlaufsdigrammen sind Signalverläufe eines Verlusts in  $\text{kW}$ , eine Kollektor-Emitter-Spannung  $VCE$  in  $\text{V}$ , ein Kollektor-Emitter-Strom  $ICE$  in  $\text{A}$  und eine Gate-Emitter-Spannung  $VGE$  in  $\text{V}$  für jeden der IGBTs Q1, Q2 in dieser Reihenfolge von oben nach unten dargestellt. Der Verlust ist ein Produkt aus der Kollektor-Emitter-Spannung  $VCE$  und dem Kollektor-Emitter-Strom  $ICE$ .

**[0096]** **Fig. 10** ist ein Diagramm, das Simulationsergebnisse zeigt, wenn parallel geschaltete IGBTs nacheinander geschaltet werden. **Fig. 11** ist eine vergrößerte Ansicht von **Fig. 10** zur Zeit des Einschaltens, und **Fig. 12** ist eine vergrößerte Ansicht von **Fig. 10** zur Zeit des Ausschaltens. Bei der in **Fig. 10–Fig. 12** gezeigten Simulation wurde beim Einschalten zuerst der IGBT Q1 eingeschaltet, und der IGBT Q2 wurde 0,5 Mikrosekunden danach eingeschaltet. Beim Ausschalten wurde zunächst der IGBT Q1 ausgeschaltet, und der IGBT Q2 wurde 0,5 Mikrosekunden danach ausgeschaltet. Es ist zu sehen, dass der Einschaltverlust von dem zuerst eingeschalteten IGBT Q1 getragen wird und dass der Ausschaltverlust  $Eoff$  von dem später ausgeschalteten IGBT Q2 getragen wird.

**[0097]** **Fig. 13** ist ein Diagramm, das ein Simulationsergebnis zeigt, wenn das Einschalten der parallel geschalteten IGBTs gleichzeitig durchgeführt wird und das Ausschalten nacheinander durchgeführt wird. **Fig. 14** ist eine vergrößerte Ansicht von **Fig. 13** zur Zeit des Einschaltens. **Fig. 15** ist eine vergrößerte Ansicht von **Fig. 13** zur Zeit des Ausschaltens.

Bei der in **Fig. 13–Fig. 15** gezeigten Simulation wurden beim Einschalten die IGBTs Q1, Q2 gleichzeitig eingeschaltet. Beim Ausschalten wurde der IGBT Q1 zuerst ausgeschaltet, und der IGBT Q2 wurde 0,5 Mikrosekunden danach ausgeschaltet. Es ist ersichtlich, dass der Einschaltverlust  $E_{on}$  von beiden IGBTs Q1, Q2 getragen wird und dass der Ausschaltverlust  $E_{off}$  von dem später ausgeschalteten IGBT Q2 getragen wird.

**[0098]** **Fig. 16** ist ein Diagramm, das eine Beziehung zwischen dem Gesamtstrom  $I_t$ , der durch die parallel geschalteten IGBTs Q1, Q2 fließt, und dem Einschaltverlust  $E_{on}$  zeigt. **Fig. 16B** ist eine vergrößerte Ansicht eines Abschnitts in einem Rahmen, der in **Fig. 16A** durch eine gestrichelte Linie gezeigt ist. Wie in **Fig. 16B** gezeigt, ist in einem Bereich, in dem der Strom kleiner als der Schwellenwert  $I_{th1}$  ist, ein Fall, in dem die Elemente nacheinander einzeln eingeschaltet werden (1P) einen kleineren Einschaltverlust  $E_{on}$  als in einem Fall, in dem die beiden Elemente gleichzeitig eingeschaltet werden (2P). In einem Bereich, in dem ein Strom größer als der Schwellenwert  $I_{th1}$  ist, ist der Einschaltverlust  $E_{on}$  in dem Fall, in dem zwei Elemente gleichzeitig eingeschaltet werden (2P) kleiner als in dem Fall, in dem die Elemente einzeln nacheinander eingeschaltet werden (1P).

**[0099]** **Fig. 17** ist ein Diagramm, das einen Aufbau einer Leistungshalbleitervorrichtung **201** gemäß einer zweiten Ausführungsform zeigt. Die zweite Ausführungsform zeigt ein Beispiel für einen spezifischen Aufbau der in **Fig. 1** gezeigten Treibersteuerseinheit **100**. Eine in **Fig. 17** gezeigte Treibersteuerseinheit **101** enthält eine integrierte Steuerschaltung **5** (IC, integrated circuit), eine Treiberversorgungsspannung  $V_1$ , Widerstandselemente R14, R15, R23 und R24 sowie n-MOS-Transistoren Q11, Q22, Q33, Q44 (MOS = metal oxide semiconductor, Metall-Oxid-Halbleiter) zum Treiben der IGBTs Q1, Q2.

**[0100]** Die integrierte Schaltung **5** enthält einen Eingangsanschluss IN, der das Treibersignal DS empfängt, und Ausgangsanschlüsse OUT1, OUT2, OUT3 und OUT4 zum Ausgeben von Steuersignalen entsprechend dem Treibersignal DS jeweils an die Gates der Transistoren Q11, Q22, Q33, Q44.

**[0101]** Die Drains der Transistoren Q11, Q33 sind mit einem Leistungsversorgungsknoten **9** verbunden, dem von der Treiberleistungsversorgung  $V_1$  eine Treiberspannung zugeführt wird. Die Sourcen der Transistoren Q22, Q44 sind mit einem Masseknoten GND verbunden.

**[0102]** Die einen Enden der Widerstandselemente R14, R23 sind mit dem Gate des IGBT Q1 verbunden, und die einen Enden der Widerstandselemente R15, R24 sind mit dem Gate des IGBT Q2 verbunden. Das andere Ende des Widerstandselementes R14 ist

mit der Source des Transistors Q11 verbunden, und das andere Ende des Widerstandselementes R15 ist mit der Source des Transistors Q33 verbunden. Das andere Ende des Widerstandselementes R23 ist mit dem Drain des Transistors Q22 verbunden, und das andere Ende des Widerstandselementes R24 ist mit dem Drain des Transistors Q44 verbunden.

**[0103]** **Fig. 18** ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von der in **Fig. 17** gezeigten integrierten Schaltung **5** ausgegeben wird.

**[0104]** Mit Bezug auf **Fig. 17** und **Fig. 18** schaltet die integrierte Schaltung **5** als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel zum Zeitpunkt  $t_1$  die von den Ausgangsanschlüssen OUT1, OUT3 ausgegebenen Steuersignale auf H-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf L-Pegel. Somit werden die Transistoren Q11 und Q33 eingeschaltet, und die Transistoren Q22, Q44 werden ausgeschaltet. Dementsprechend werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet.

**[0105]** Zum Zeitpunkt  $t_2$  schaltet die integrierte Schaltung **5** als Reaktion auf einen Wechsel des Treibersignals DS auf L-Pegel das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT2 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q11 ausgeschaltet, und der Transistor Q22 wird eingeschaltet. Dementsprechend wird der IGBT Q1 ausgeschaltet.

**[0106]** Zu einem Zeitpunkt  $t_3$ , der um eine vorbestimmte Zeitspanne später als der Zeitpunkt  $t_2$  liegt, schaltet die integrierte Schaltung **5** das von dem Ausgangsanschluss OUT3 ausgegebene Steuersignal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT4 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q33 ausgeschaltet, und der Transistor Q44 wird eingeschaltet. Dementsprechend wird der IGBT Q2 später ausgeschaltet als der IGBT Q1.

**[0107]** Danach wird ein ähnlicher Betrieb wiederholt. Ein Betrieb der integrierten Schaltung **5** zu den Zeitpunkten  $t_4$ ,  $t_7$  ist nämlich derselbe wie der Betrieb zum Zeitpunkt  $t_1$ , und der Betrieb der integrierten Schaltung **5** zu den Zeitpunkten  $t_5$ ,  $t_6$  ist jeweils derselbe wie der Betrieb zu den Zeitpunkten  $t_2$ ,  $t_3$ .

**[0108]** Der Betrieb der oben beschriebenen integrierten Schaltung **5** kann einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig. 2B** gezeigte, der in der ersten Ausführungsform beschrieben ist.

**[0109]** Die integrierte Schaltung **5** kann die Transistoren Q11, Q22, Q33 und Q44 auch mit von den in

**Fig. 18** gezeigten Zeitabläufen verschiedenen Zeitabläufen einschalten. Zum Verwirklichen eines Steuerbetriebs, der derselbe ist wie der in **Fig. 2A** gezeigte, der in der ersten Ausführungsform beschrieben ist, sollte die folgende Schaltsteuerung durchgeführt werden: Als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel schaltet die integrierte Schaltung 5 das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf H-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2 und OUT4 ausgegebenen Signale auf L-Pegel. Die integrierte Schaltung 5 schaltet das von dem Ausgangsanschluss OUT3 ausgegebene Steuersignal um eine vorbestimmte Zeitspanne später auf H-Pegel, als der Wechsel des Treibersignals DS auf H-Pegel. Außerdem schaltet die integrierte Schaltung 5 als Reaktion auf einen Wechsel des Treibersignals DS auf L-Pegel den von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT2 ausgegebene Signal auf H-Pegel. Die integrierte Schaltung 5 schaltet das von dem Ausgangsanschluss OUT3 ausgegebene Steuersignal, um eine vorbestimmte Zeitspanne später auf L-Pegel als der Wechsel des Treibersignals DS auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT4 ausgegebene Steuersignal auf H-Pegel. Als Folge der obigen Steuerung werden die IGBTs Q1, Q2 in dieser Reihenfolge eingeschaltet und in dieser Reihenfolge ausgeschaltet.

**[0110]** Um einen Steuerbetrieb zu verwirklichen, der derselbe ist wie in **Fig. 2C** gezeigte, der in der ersten Ausführungsform beschrieben ist, sollte die folgende Schaltsteuerung ausgeführt werden: Als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel schaltet die integrierte Schaltung 5 die von den Ausgangsanschlüssen OUT1 und OUT3 ausgegebenen Steuersignale auf H-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf L-Pegel. Außerdem schaltet die integrierte Schaltung 5, wenn das Treibersignal DS auf L-Pegel wechselt, die von den Ausgangsanschlüssen OUT1, OUT3 ausgegebenen Steuersignale auf L-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf H-Pegel. Als Ergebnis der obigen Steuerung werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet und gleichzeitig ausgeschaltet.

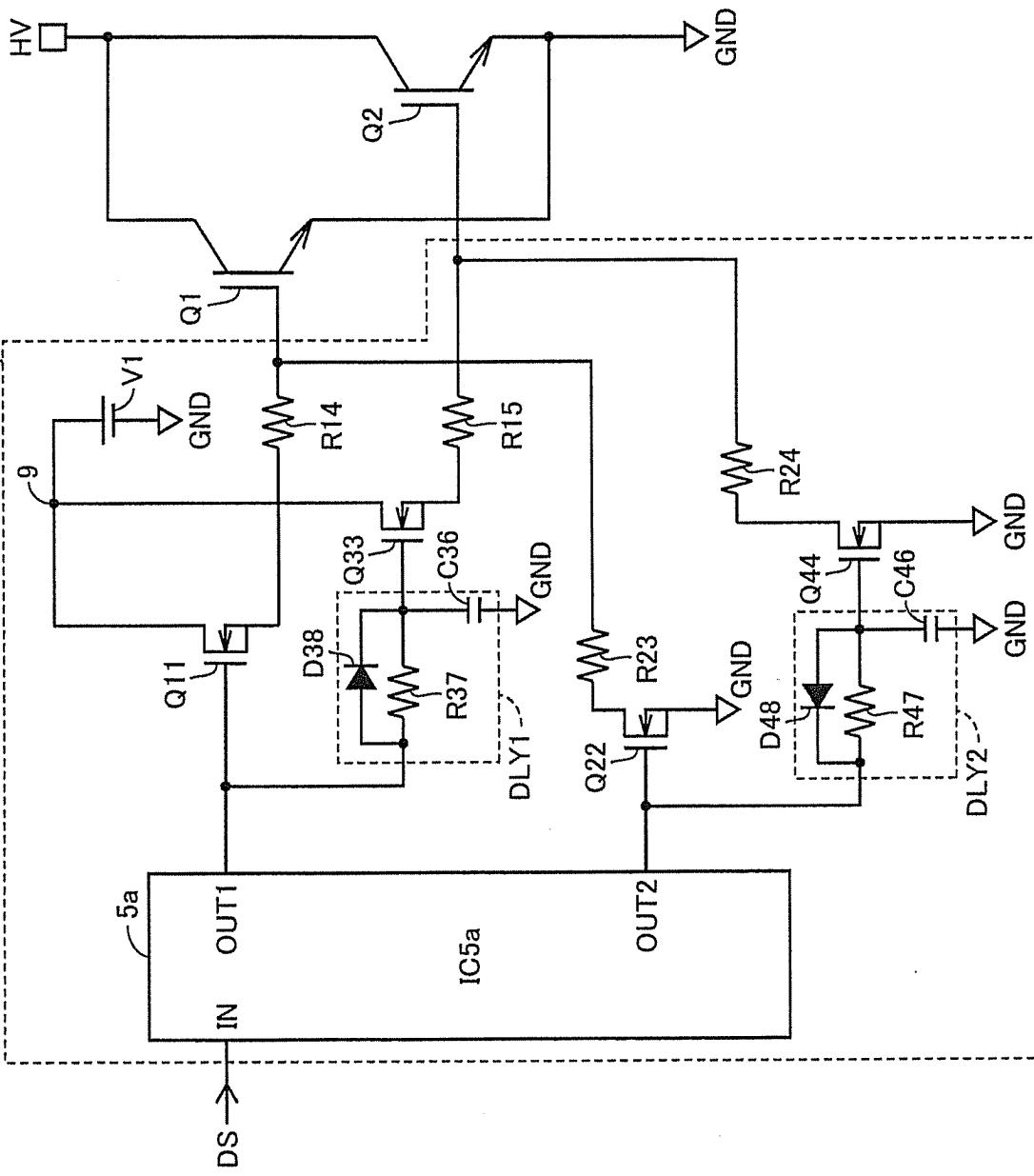

**[0111]** **Fig. 19** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung 202 gemäß einer dritten Ausführungsform. Die dritte Ausführungsform zeigt ein Beispiel für einen spezifischen Aufbau der in **Fig. 1** gezeigten Treibersteuereinheit 100. Eine in **Fig. 19** gezeigte Treibersteuereinheit 102 enthält eine integrierte Steuerschaltung 5a, eine Treiberleistungsversorgung V1, Widerstandselemente R14, R15, R23, R24, n-MOS-Transistoren Q11, Q22, Q33, Q44 zum Treiben der IGBTs Q1, Q2 und Verzögerungsschaltungen DLY1, DLY2.

**[0112]** Die integrierte Schaltung 5a enthält einen Eingangsanschluss IN, der das Treibersignal DS empfängt, einen Ausgangsanschluss OUT1 zum Ausgeben eines Steuersignals entsprechend dem Treibersignal DS an das Gate des Transistors Q11 und an die Verzögerungsschaltung DLY1, und einen Ausgangsanschluss OUT2 zum Ausgeben eines Steuersignals entsprechend dem Treibersignal DS an das Gate des Transistors Q22 und an die Verzögerungsschaltung DLY2.

**[0113]** Die Drains der Transistoren Q11, Q33 sind mit einem Leistungsversorgungsknoten 9 verbunden, dem von der Treiberleistungsversorgung V1 eine Treiberspannung zugeführt wird. Die Sourcen der Transistoren Q22, Q44 sind mit einem Masseknoten GND verbunden.

**[0114]** Die einen Enden der Widerstandselemente R14, R23 sind mit dem Gate des IGBT Q1 verbunden, und die einen Enden der Widerstandselemente R15, R24 sind mit dem Gate des IGBT Q2 verbunden. Das andere Ende des Widerstandselement R14 ist mit der Source des Transistors Q11 verbunden, und das andere Ende des Widerstandselement R15 ist mit der Source des Transistors Q33 verbunden. Das andere Ende des Widerstandselement R23 ist mit dem Drain des Transistors Q22 verbunden, und das andere Ende des Widerstandselement R24 ist mit dem Drain des Transistors Q44 verbunden.

**[0115]** Die Verzögerungsschaltung DLY1 enthält ein Widerstandselement C37, einen Kondensator C36 und eine Diode D38. Das Widerstandselement R37 ist zwischen den Ausgangsanschluss OUT1 der integrierten Schaltung 5a und das Gate des Transistors Q33 geschaltet. Der Kondensator C36 ist zwischen das Gate des Transistors Q33 und den Masseknoten GND geschaltet. Die Anode der Diode D38 ist mit dem Ausgangsanschluss OUT1 der integrierten Schaltung 5a verbunden, und ihre Kathode ist mit dem Gate des Transistors Q33 verbunden. Die Verzögerungsschaltung DLY1 verzögert eine abfallende Flanke eines von dem Ausgangsanschluss OUT1 der integrierten Schaltung 5a ausgegebenen Steuersignals, d. h. eine Flanke, die dem Ausschalten des Transistors Q33 entspricht.

**[0116]** Die Verzögerungsschaltung DLY2 enthält ein Widerstandselement R47, einen Kondensator C46 und eine Diode D48. Das Widerstandselement R47 ist zwischen den Ausgangsanschluss OUT2 der integrierten Schaltung 5a und das Gate des Transistors Q44 geschaltet. Der Kondensator C46 ist zwischen das Gate des Transistors Q44 und den Masseknoten GND geschaltet. Die Kathode der Diode D48 ist mit dem Ausgangsanschluss OUT2 der integrierten Schaltung 5a verbunden, und ihre Anode ist mit dem Gate des Transistors Q44 verbunden. Die Verzögerungsschaltung DLY2 verzögert eine ansteigen-

de Flanke eines von dem Ausgangsanschluss OUT2 der integrierten Schaltung **5a** ausgegebenen Steuersignals, d. h. eine Flanke, die dem Einschalten des Transistors Q44 entspricht.

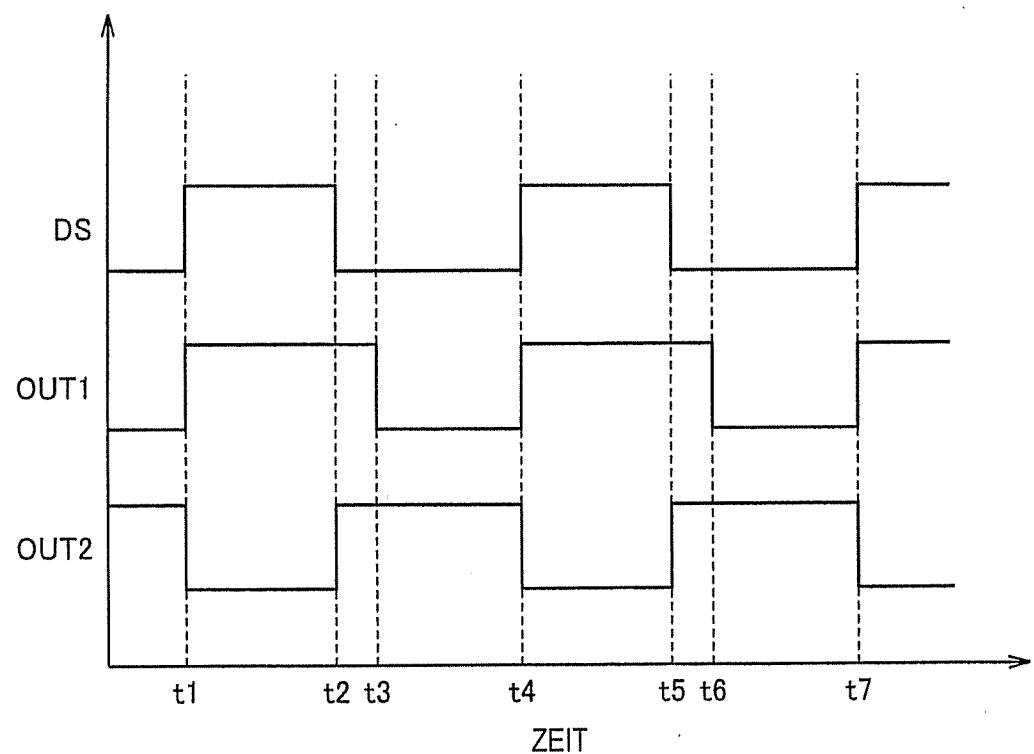

**[0117]** **Fig.** 20 ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von der in **Fig.** 19 gezeigten integrierten Schaltung **5a** ausgegeben wird.

**[0118]** Mit Bezug auf **Fig.** 19 und **Fig.** 20 schaltet die integrierte Schaltung **5a** zum Zeitpunkt t1 als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel ein von dem Ausgangsanschluss OUT1 ausgegebenes Steuersignal auf H-Pegel, und sie schaltet ein von dem Ausgabeanschluss OUT2 ausgegebenes Steuersignal auf L-Pegel. Somit werden die Transistoren Q11, Q33 eingeschaltet, und die Transistoren Q22, Q44 werden ausgeschaltet. Dementsprechend werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet.

**[0119]** Zum Zeitpunkt t2 schaltet die integrierte Schaltung **5a** als Reaktion auf einen Wechsel des Treibersignals DS auf L-Pegel das von dem Ausgabeanschluss OUT2 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q22 eingeschaltet, und der Transistor Q44 wird mit einer Verzögerung um eine Verzögerungszeitspanne eingeschaltet, die durch die Verzögerungsschaltung DLY2 bestimmt wird.

**[0120]** Wenn dabei eine Ausgangsspannung der Treiberleistungsversorgung V1 als v1 bezeichnet wird, die Widerstandswerte der Widerstandselemente R14, R23 jeweils als r14, r23 und eine Schwellenspannung des IGBT Q1 als Vq1, sind v1, r14, r23 und Vq1 normalerweise so eingestellt, dass sie die folgende Beziehung erfüllen:

$$Vq1 > V1 \cdot r23 / (r14 + r23) \quad (12)$$

**[0121]** Die Schwellenspannung des IGBT Q1 ist also höher als eine Spannung, die durch Teilen der Ausgangsspannung der Treiberleistungsversorgung V1 durch die Widerstandselemente R14, R23 gewonnen wird. Demzufolge wird zum Zeitpunkt t2 der IGBT Q1 ausgeschaltet.

**[0122]** Zum Zeitpunkt t3, der um eine vorbestimmte Zeitspanne später liegt als der Zeitpunkt t2, schaltet die integrierte Schaltung **5a** das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf L-Pegel. Somit wird der Transistor Q11 ausgeschaltet, und der Transistor Q33 wird mit einer Verzögerung um eine Verzögerungszeitspanne ausgeschaltet, die durch die Verzögerungsschaltung DLY1 bestimmt ist. Demzufolge wird der IGBT Q2 ausgeschaltet.

**[0123]** Danach wird ein ähnlicher Betrieb wiederholt. Ein Betrieb der integrierten Schaltung **5a** zu den Zeitpunkten t4 und t7 ist nämlich derselbe wie der Betrieb zum Zeitpunkt t1, und der Betrieb der integrierten Schaltung **5a** zu den Zeitpunkten t5, t6 ist jeweils derselbe wie der Betrieb zu den Zeitpunkten t2, t3.

**[0124]** Der Betrieb der obigen integrierten Schaltung **5a** kann einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig.** 2B gezeigte, der in der ersten Ausführungsform beschrieben ist.

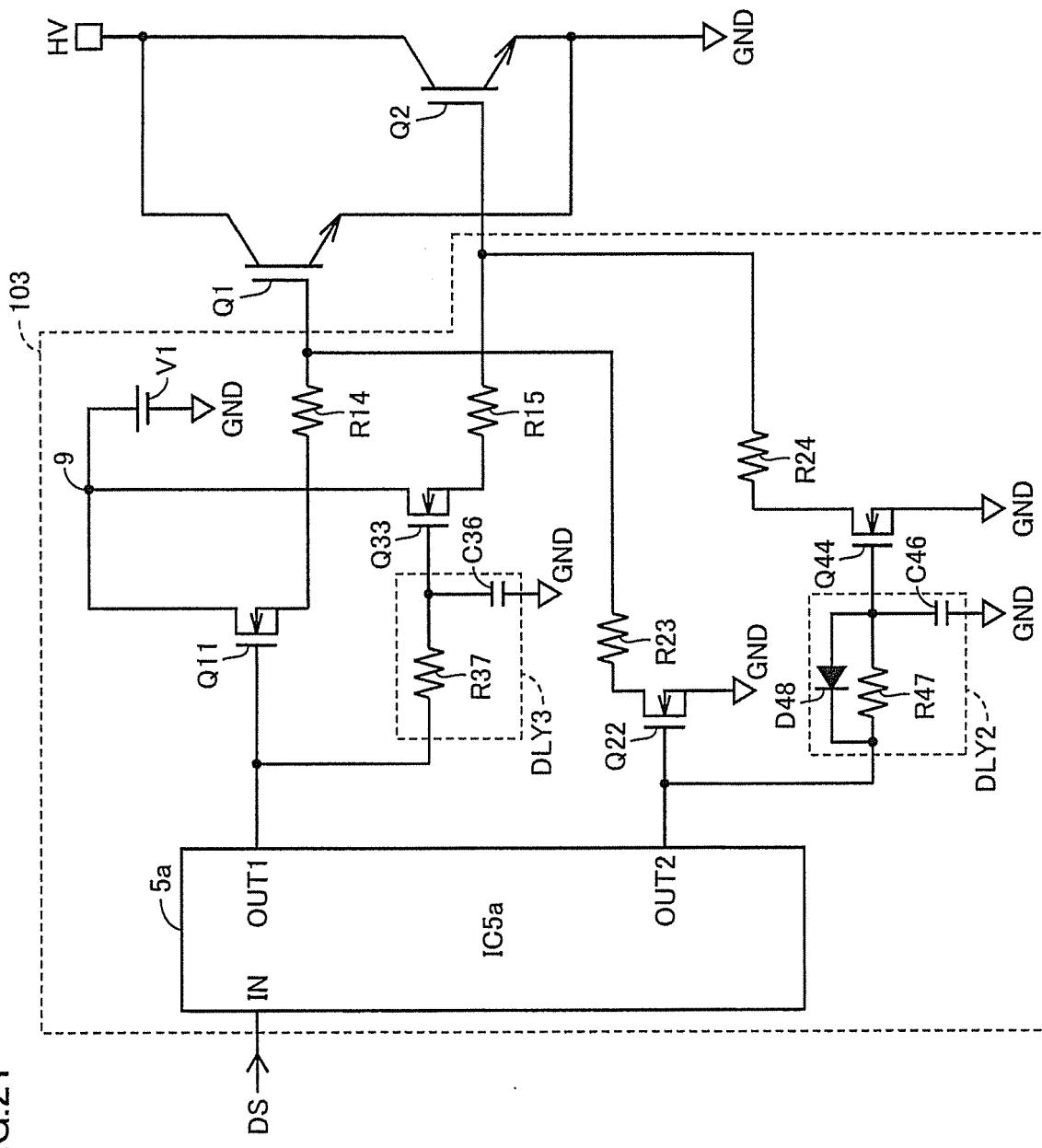

**[0125]** **Fig.** 21 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **203** gemäß einer vierten Ausführungsform. Eine Verzögerungsschaltung DLY3, die in einer in **Fig.** 21 gezeigten Treibersteuereinheit **103** enthalten ist, unterscheidet sich von der in **Fig.** 19 gezeigten Verzögerungsschaltung DLY1 darin, dass sie keine Diode D38 enthält. Daher liefert die in **Fig.** 21 gezeigte Verzögerungsschaltung DLY3 ein Signal, das durch Verzögerung sowohl der ansteigenden Flanke als auch der abfallenden Flanke eines von dem Ausgangsanschluss OUT1 der integrierten Schaltung **5a** ausgegebenen Steuersignals gewonnen wird, an das Gate des Transistors Q33. Da **Fig.** 21 ansonsten dieselbe ist wie **Fig.** 19, sind die gleichen oder einander entsprechende Komponenten durch dieselben Bezeichnungen gekennzeichnet, und ihre Beschreibung wird nicht wiederholt. Der Zeitablauf der von den Ausgangsanschlüssen OUT1, OUT2 der integrierten Schaltung **5a** ausgegebenen Steuersignale ist ebenfalls derselbe wie in **Fig.** 20.

**[0126]** Wenn das von dem Ausgangsanschluss OUT1 der integrierten Schaltung **5a** ausgegebene Steuersignal bei der in **Fig.** 21 gezeigten Treibersteuereinheit **103** auf H-Pegel geschaltet wird (Zeitpunkte t1, t4, t7 in **Fig.** 20), wird der Transistor Q33 mit einer Verzögerung um eine Verzögerungszeitspanne, die durch die Verzögerungsschaltung DLY3 bestimmt ist, eingeschaltet. Demzufolge wird, wenn das Treibersignal DS auf H-Pegel wechselt, der IGBT Q2 später eingeschaltet als das Einschalten des IGBT Q1. Das Ausschalten des IGBT Q2 später als das Ausschalten des IGBT Q1 zum Zeitpunkt t2, t5 ist daselbe wie in der dritten Ausführungsform. Daher kann die in **Fig.** 21 gezeigte Leistungshalbleitervorrichtung **203** einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig.** 2A gezeigte, der in der ersten Ausführungsform beschrieben ist.

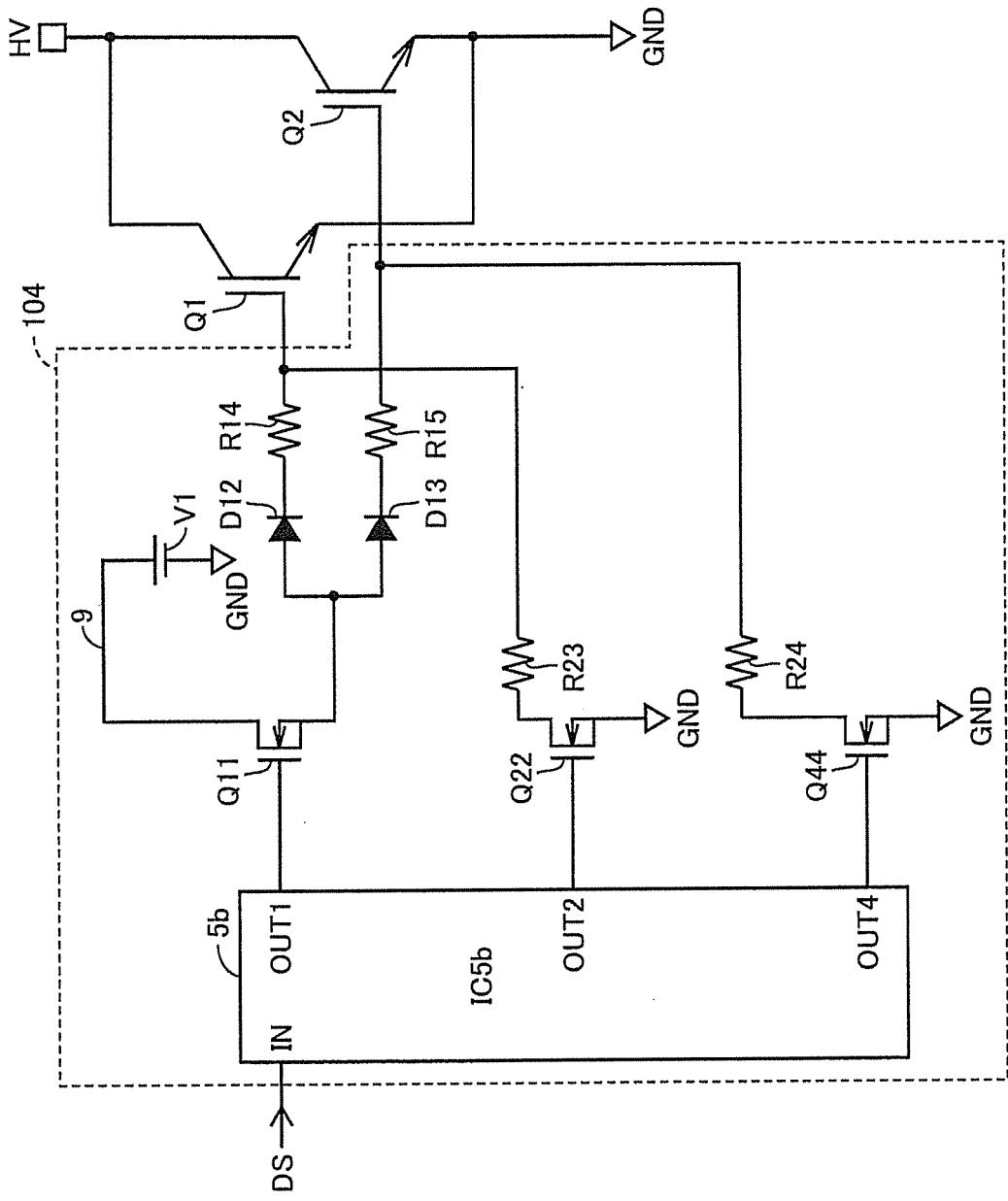

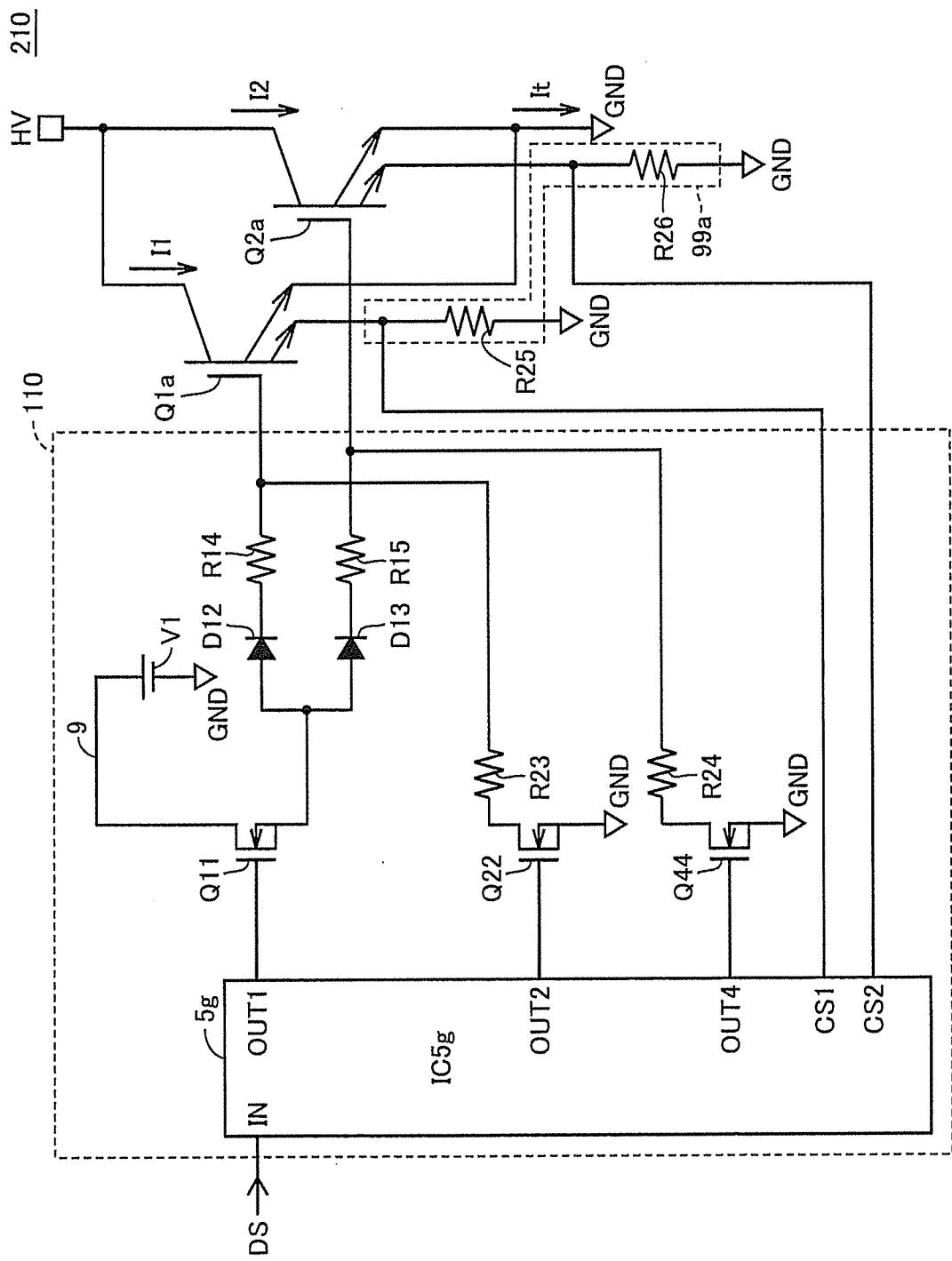

**[0127]** **Fig.** 22 ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **204** gemäß einer fünften Ausführungsform. Die fünfte Ausführungsform zeigt ein Beispiel für einen bestimmten Aufbau der in **Fig.** 1 gezeigten Treibersteuereinheit **100**. Eine in **Fig.** 22 gezeigte Treibersteuereinheit **104** enthält eine integrierte Steuerschaltung **5b**, eine Treiberleistungsversorgung V1, Widerstandselemente R14,

R15, R23, R24, n-MOS-Transistoren Q11, Q22, Q44 zum Treiben der IGBTs Q1, Q2 und Dioden D12, D13.

**[0128]** Die integrierte Schaltung **5b** enthält einen Eingangsanschluss IN, der das Trebersignal DS empfängt, und Ausgangsanschlüsse OUT1, OUT2 und OUT4 zum Ausgeben von Steuersignalen entsprechend dem Trebersignal DS jeweils an das Gate des Transistors Q11, Q22 bzw. Q44.

**[0129]** Der Drain des Transistors Q11 ist mit dem Leistungsversorgungsknoten **9** verbunden, dem von der Treiberleistungsversorgung V1 eine Treiberspannung zugeführt wird. Die Sourcen der Transistoren Q22, Q44 sind mit dem Masseknoten GND verbunden.

**[0130]** Die einen Enden der Widerstandselemente R14, R23 sind mit dem Gate des IGBT Q1 verbunden, und die einen Enden der Widerstandselemente R15, R24 sind mit dem Gate des IGBT Q2 verbunden. Das andere Ende des Widerstandselement R14 ist mit der Kathode der Diode D12 verbunden, und das andere Ende des Widerstandselement R15 ist mit der Kathode der Diode D13 verbunden. Das andere Ende des Widerstandselement R23 ist mit dem Drain des Transistors Q22 verbunden, und das andere Ende des Widerstandselement R24 ist mit dem Drain des Transistors Q44 verbunden. Die Anoden der Dioden D12, D13 sind jeweils mit der Source des Transistors Q11 verbunden. Die Dioden D12, D13 werden leitend gemacht, wenn der Transistor Q11 eingeschaltet wird.

**[0131]** **Fig. 23** ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von der in **Fig. 22** gezeigten integrierten Schaltung **5b** ausgegeben wird.

**[0132]** Mit Bezug auf **Fig. 22** und **Fig. 23** schaltet die integrierte Schaltung **5b** zum Zeitpunkt t1 als Reaktion auf einen Wechsel des Trebersignals DS auf H-Pegel ein von dem Ausgangsanschluss OUT1 ausgegebenes Steuersignal auf H-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf L-Pegel. Somit wird der Transistor Q11 eingeschaltet, und die Transistoren Q22, Q44 werden ausgeschaltet. Demzufolge werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet.

**[0133]** Zum Zeitpunkt t2 schaltet die integrierte Schaltung als Reaktion auf einen Wechsel des Trebersignals DS auf L-Pegel das von dem Ausgangsanschluss OUT2 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q22 eingeschaltet. Wenn dabei eine Ausgangsspannung der Treiberleistungsversorgung V1 als v1 bezeichnet wird, die Widerstandswerte der Widerstandselemente R14, R23 jeweils als r14, r23 und eine Schwellenspannung des IGBT Q1 als Vq1, sind v1, r14, r23 und Vq1 norma-

lerweise so eingestellt, dass sie die in der oben beschriebenen Gleichung (12) angegebene Beziehung erfüllen. Die Schwellenspannung des IGBT Q1 ist also größer als eine Spannung, die durch Teilen der von der Treiberleistungsversorgung V1 ausgegebenen Spannung durch die Widerstandselemente R14, R23 gewonnen wird. Demzufolge wird der IGBT Q1 zum Zeitpunkt t2 ausgeschaltet.

**[0134]** Zu einem Zeitpunkt t3, der um eine vorbestimmte Zeitspanne später als der Zeitpunkt t2 liegt, schaltet die integrierte Schaltung **5b** das von dem Ausgangsanschluss OUT1 ausgegebene Signal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT4 ausgegebene Signal auf H-Pegel. Somit wird der Transistor Q11 ausgeschaltet, und der Transistor Q44 wird eingeschaltet. Demzufolge wird der IGBT Q2 ausgeschaltet.

**[0135]** Danach wird ein ähnlicher Betrieb wiederholt. Ein Betrieb der integrierten Schaltung **5b** zu den Zeitpunkten t4, t7 ist nämlich derselbe wie der Betrieb zum Zeitpunkt t1, und der Betrieb der integrierten Schaltung **5b** zu den Zeitpunkten t5, t6 ist jeweils derselbe wie der Betrieb zu den Zeitpunkten t2, t3.

**[0136]** Der Betrieb der oben beschriebenen integrierten Schaltung **5b** kann einen Steuervorgang verwirklichen, der derselbe ist wie der in **Fig. 23** gezeigte, der in der ersten Ausführungsform beschrieben ist. Anders als oben dargestellt, können die IGBTs Q1, Q2 jedoch auch gleichzeitig ausgeschaltet werden, wenn zum Zeitpunkt t2, t5 das von dem Ausgangsanschluss OUT1 der integrierten Schaltung **5b** ausgegebene Steuersignal auf L-Pegel geschaltet wird und die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf H-Pegel geschaltet werden. Es kann also auch ein Steuerbetrieb verwirklicht werden, wie er in **Fig. 2C** in Verbindung mit der ersten Ausführungsform gezeigt ist.

**[0137]** **Fig. 24** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **205** gemäß einer sechsten Ausführungsform. Die sechste Ausführungsform zeigt ein Beispiel für einen spezifischen Aufbau der in **Fig. 1** gezeigten Treibersteuereinheit **100**. Eine in **Fig. 24** gezeigte Treibersteuereinheit **105** enthält eine integrierte Steuerschaltung **5a**, eine Treiberleistungsversorgung V1, Widerstandselemente R14, R15, R23, R24, n-MOS-Transistoren Q11, Q22, Q44 zum Treiben der IGBTs Q1, Q2, Dioden D12, D13 und eine Verzögerungsschaltung DLY2.

**[0138]** Die integrierte Schaltung **5a** enthält einen Eingangsanschluss IN, der das Trebersignal DS empfängt, einen Ausgangsanschluss OUT1 zum Ausgeben eines Steuersignals entsprechend dem Trebersignal DS an das Gate des Transistors Q11, und einen Ausgangsanschluss OUT2 zum Ausgeben eines Steuersignals entsprechend dem Trebersignal

DS an das Gate des Transistors Q22 und an die Verzögerungsschaltung DLY2.

**[0139]** Der Drain des Transistors Q11 ist mit dem Leistungsversorgungsknoten **9** verbunden, dem von der Treiberleistungsversorgung V1 eine Treiberspannung zugeführt wird. Die Sourcen der Transistoren Q22, Q44 sind mit dem Masseknoten GND verbunden.

**[0140]** Die einen Enden der Widerstandselemente R14, R23 sind mit dem Gate des IGBT Q1 verbunden, und die einen Enden der Widerstandselemente R15, R24 sind mit dem Gate des IGBT Q2 verbunden. Das andere Ende des Widerstandselement R14 ist mit der Kathode der Diode D12 verbunden, und das andere Ende des Widerstandselement R15 ist mit der Kathode der Diode D13 verbunden. Das andere Ende des Widerstandselement R23 ist mit dem Drain des Transistors Q22 verbunden, und das andere Ende des Widerstandselement R24 ist mit dem Drain des Transistors Q44 verbunden. Die Anoden der Dioden D12, D13 sind mit der Source des Transistors Q11 verbunden. Die Dioden D12, D13 werden leitend gemacht, wenn der Transistor Q11 eingeschaltet wird.

**[0141]** Die Verzögerungsschaltung DLY2 enthält ein Widerstandselement R47, einen Kondensator C46 und eine Diode D48. Das Widerstandselement R47 ist zwischen den Ausgangsanschluss OUT2 der integrierten Schaltung **5a** und das Gate des Transistors Q44 geschaltet. Der Kondensator C46 ist zwischen das Gate des Transistors Q44 und den Masseknoten GND geschaltet. Die Kathode der Diode D48 ist mit dem Ausgangsanschluss OUT2 der integrierten Schaltung **5a** verbunden, und ihre Anode ist mit dem Gate des Transistors Q44 verbunden. Die Verzögerungsschaltung DLY2 verzögert eine ansteigende Flanke eines von dem Ausgangsanschluss OUT2 der integrierten Schaltung **5a** ausgegebenen Steuersignals, d. h. eine Flanke, die dem Einschalten des Transistors Q44 entspricht.

**[0142]** Ein Betrieb der integrierten Schaltung **5a** ist derselbe, wie er mit Bezug auf **Fig. 20** in Verbindung mit der dritten Ausführungsform beschrieben ist. Mit Bezug auf **Fig. 20** und **Fig. 24** wird im Folgenden ein Betrieb der Leistungshalbleitervorrichtung **205** beschrieben.

**[0143]** Zu dem in **Fig. 20** gezeigten Zeitpunkt t1 schaltet die integrierte Schaltung **5a** als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf H-Pegel, und sie schaltet das von dem Ausgabeanschluss OUT2 ausgegebene Steuersignal auf L-Pegel. Somit wird der Transistor Q11 eingeschaltet, und die Transistoren Q22, Q44 werden ausgeschaltet. Demzufolge werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet.

**[0144]** Zum Zeitpunkt t2 schaltet die integrierte Schaltung **5a** als Reaktion auf einen Wechsel des Treibersignals DS auf L-Pegel das von dem Ausgabeanschluss OUT2 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q22 eingeschaltet, und der Transistor Q44 wird mit einer Verzögerung um eine Verzögerungszeitspanne eingeschaltet, die durch die Verzögerungsschaltung DLY2 bestimmt ist. Wenn dabei eine Ausgangsspannung der Treiberleistungsversorgung V1 als v1 bezeichnet wird, die Widerstandswerte der Widerstandselemente R14, R23 jeweils als r14, r23 und eine Schwellenspannung des IGBT Q1 als Vq1, sind v1, r14, r23 und Vq1 normalerweise so eingestellt, dass sie die in der oben beschriebenen Gleichung (12) angegebene Beziehung erfüllen. Die Schwellenspannung des IGBT Q1 ist also größer als eine Spannung, die durch Teilen der Ausgangsspannung der Treiberleistungsversorgung V1 durch die Widerstandselemente R14, R23 gewonnen wird. Demzufolge wird der IGBT Q1 zum Zeitpunkt t2 ausgeschaltet.

**[0145]** Zum Zeitpunkt t3, der um eine vorbestimmte Zeitspanne später liegt als der Zeitpunkt t2, schaltet die integrierte Schaltung **5a** das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf L-Pegel. Somit wird der Transistor Q11 ausgeschaltet, und der Transistor Q44 wird mit einer Verzögerung um eine Verzögerungszeitspanne ausgeschaltet, die durch die Verzögerungsschaltung DLY2 bestimmt ist. Demzufolge wird der IGBT Q2 ausgeschaltet.

**[0146]** Danach wird ein ähnlicher Betrieb wiederholt. Ein Betrieb der integrierten Schaltung **5a** zu den Zeitpunkten t4, t7 ist nämlich derselbe wie der Betrieb zum Zeitpunkt t1, und ein Betrieb der integrierten Schaltung **5a** zu den Zeitpunkten t5, t6 ist jeweils derselbe wie ein Betrieb zu den Zeitpunkten t2, t3.

**[0147]** Der Betrieb der oben beschriebenen integrierten Schaltung **5a** kann einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig. 23** gezeigte, der in der ersten Ausführungsform beschrieben ist.

**[0148]** **Fig. 25** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **206** gemäß einer siebten Ausführungsform. Die siebte Ausführungsform zeigt ein Beispiel für einen spezifischen Aufbau der in **Fig. 1** gezeigten Treibersteuereinheit **100**. Eine in **Fig. 25** gezeigte Treibersteuereinheit **106** enthält einen Eingangsknoten **8**, dem das Treibersignal DS zugeführt wird, einen Inverter **50**, eine Treiberleistungsversorgung V1, Widerstandselemente R14, R15, R23, R24, n-MOS-Transistoren Q11, Q22, Q33, Q34 zum Treiben der IGBTs Q1, Q2 und Verzögerungsschaltungen DLY1, DLY2.

**[0149]** Die Drains der Transistoren Q11, Q33 sind mit dem Leistungsversorgungsknoten **9** verbunden, dem von der Treiberleistungsversorgung V1 eine

Treiberspannung zugeführt wird. Das Gate des Transistors Q11 ist mit dem Eingangsknoten **8** verbunden, und das Gate des Transistors Q22 ist mit einem Ausgangsknoten des Inverters **50** verbunden. Die Sourcen der Transistoren Q22, Q24 sind mit Masse verbunden.

**[0150]** Die einen Enden der Widerstandselemente R14, R23 sind mit dem Gate des IGBT Q1 verbunden, und die einen Enden der Widerstandselemente R15, R24 sind mit dem Gate des IGBT Q2 verbunden. Das andere Ende des Widerstandselement R14 ist mit der Source des Transistors Q11 verbunden, und das andere Ende des Widerstandselement R15 ist mit der Source des Transistors Q33 verbunden. Das andere Ende des Widerstandselement R23 ist mit dem Drain des Transistors Q22 verbunden, und das andere Ende des Widerstandselement R24 ist mit dem Drain des Transistors Q44 verbunden.

**[0151]** Die Verzögerungsschaltung DLY1 enthält ein Widerstandselement R37, einen Kondensator C36 und eine Diode D38. Das Widerstandselement R37 ist zwischen den Eingangsknoten **8** und das Gate des Transistors Q33 geschaltet. Der Kondensator C36 ist zwischen das Gate des Transistors Q33 und den Masseknoten geschaltet. Die Anode der Diode D38 ist mit dem Eingangsknoten **8** verbunden, und ihre Kathode ist mit dem Gate des Transistors Q33 verbunden. Die Verzögerungsschaltung DLY1 verzögert eine abfallende Flanke des Treibersignals DS, d. h. eine Flanke, die dem Ausschalten des Transistors Q33 entspricht.

**[0152]** Die Verzögerungsschaltung DLY2 enthält ein Widerstandselement R47, einen Kondensator C46, und eine Diode D48. Das Widerstandselement R47 ist zwischen den Ausgangsknoten des Inverters **50** und das Gate des Transistors Q44 geschaltet. Der Kondensator C46 ist zwischen das Gate des Transistors Q44 und den Masseknoten GND geschaltet. Die Kathode der Diode D48 ist mit dem Ausgangsknoten des Inverters **50** verbunden, und ihre Anode ist mit dem Gate des Transistors Q44 verbunden. Die Verzögerungsschaltung DLY2 verzögert eine ansteigende Flanke eines von dem Inverter **50** ausgegebenen Signals, d. h. eine Flanke, die dem Einschalten des Transistors Q44 entspricht.

**[0153]** Es wird nun ein Betrieb der Leistungshalbleitervorrichtung der in **Fig. 25** gezeigten Leistungshalbleitervorrichtung **206** beschrieben. Wenn das Treibersignal DS auf H-Pegel wechselt, werden die Transistoren Q11, Q33 eingeschaltet. Da dabei ein Ausgang des Inverters **50** auf L-Pegel geschaltet wird, werden die Transistoren Q22, Q44 ausgeschaltet. Demzufolge werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet.

**[0154]** Wenn das Treibersignal DS auf L-Pegel wechselt, wird der Transistor Q11 ausgeschaltet, und der Transistor Q33 wird mit einer Verzögerung um eine Verzögerungszeitspanne ausgeschaltet, die durch die Verzögerungsschaltung DLY1 bestimmt ist. Da dabei die Ausgabe des Inverters **50** auf H-Pegel geschaltet wird, wird der Transistor Q22 eingeschaltet, und der Transistor Q44 wird mit einer Verzögerung um eine Verzögerungszeitspanne eingeschaltet, die durch die Verzögerungsschaltung DLY2 bestimmt ist. Demzufolge wird der IGBT Q1 zuerst ausgeschaltet, und der IGBT Q2 wird später ausgeschaltet.

**[0155]** Wie oben beschrieben kann ein Steuervorgang verwirklicht werden, der derselbe ist wie der in **Fig. 2B** gezeigte, der in der ersten Ausführungsform beschrieben ist.

**[0156]** **Fig. 26** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **207** gemäß einer achten Ausführungsform. Die in einer in **Fig. 26** gezeigten Treibersteuereinheit **107** bereitgestellte Verzögerungsschaltung DLY3 unterscheidet sich von der in **Fig. 25** gezeigten Verzögerungsschaltung DLY1 darin, dass sie nicht die Diode D38 enthält. Daher liefert die in **Fig. 26** gezeigte Verzögerungsschaltung DLY3 ein Signal, das durch Verzögern sowohl der ansteigenden Flanke als auch der abfallenden Flanke des Treibersignals DS gewonnen wird, an das Gate des Transistors Q33. Da **Fig. 26** ansonsten dieselbe ist wie **Fig. 25**, sind dieselben oder einander entsprechende Komponenten durch dieselben Bezugssymbole gekennzeichnet, und ihre Beschreibung wird nicht wiederholt.

**[0157]** Wenn bei der in **Fig. 26** gezeigten Treibersteuereinheit **107** das Treibersignal DS auf H-Pegel wechselt, wird der Transistor Q33 mit einer Verzögerung um eine Verzögerungszeitspanne eingeschaltet, die durch die Verzögerungsschaltung DLY3 bestimmt wird. Demzufolge wird, wenn das Treibersignal DS auf H-Pegel wechselt, der IGBT Q2 später eingeschaltet als das Einschalten des IGBT Q1. Das Ausschalten des IGBT Q2 später als das Ausschalten des IGBT Q1 ist dasselbe wie bei der siebten Ausführungsform. Somit kann die in **Fig. 26** gezeigte Leistungshalbleitervorrichtung **207** einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig. 2A** gezeigte, der in der ersten Ausführungsform beschrieben ist.

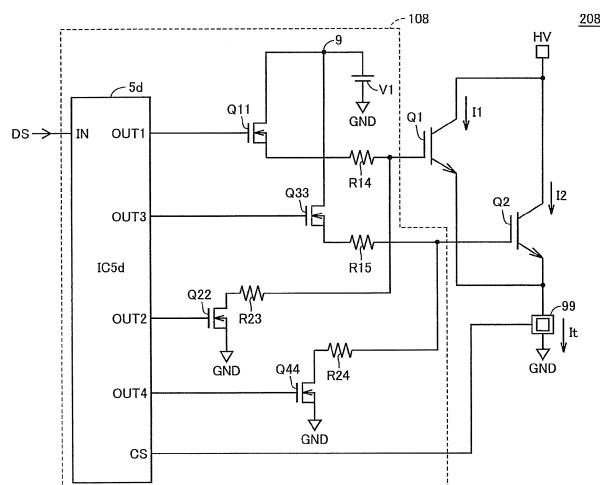

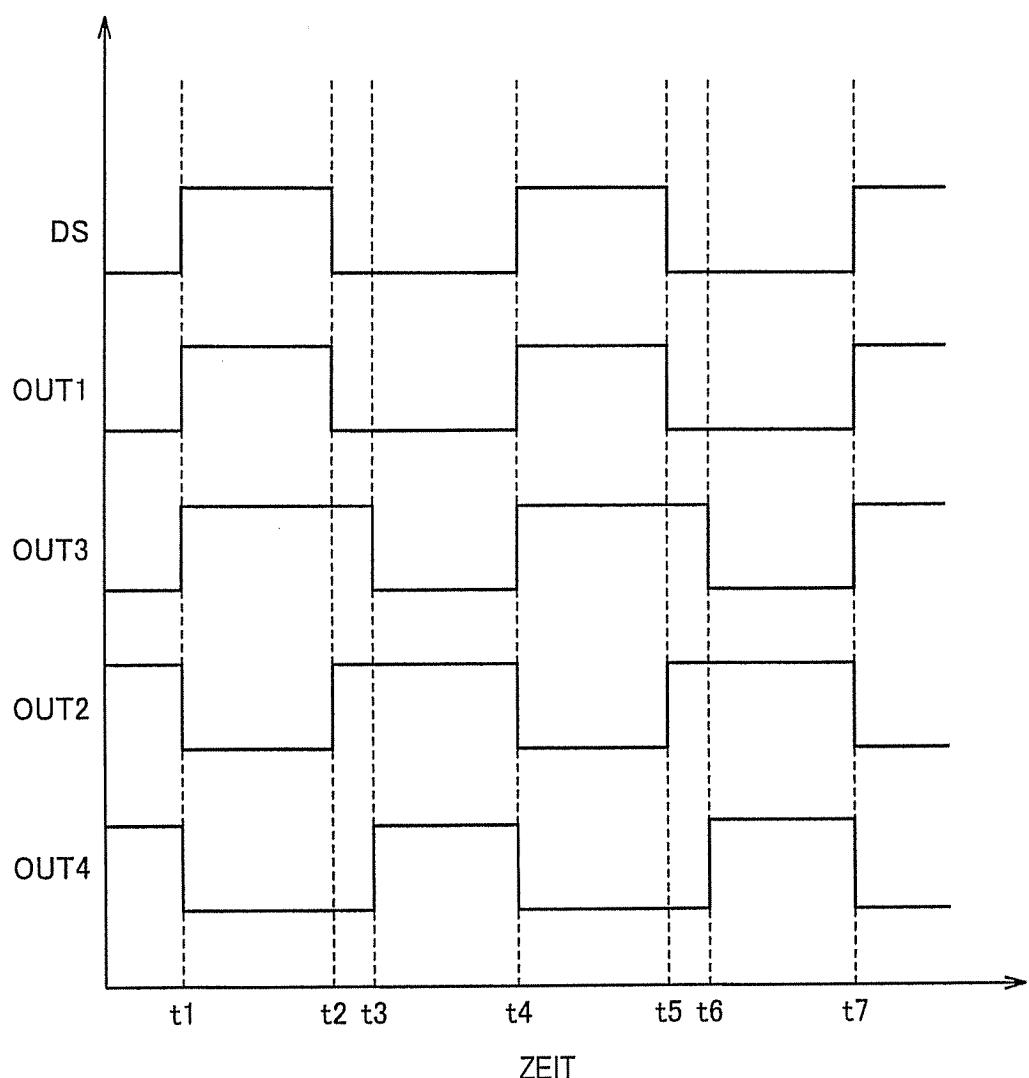

**[0158]** **Fig. 27** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **208** gemäß einer neunten Ausführungsform. Die in **Fig. 27** gezeigte Leistungshalbleitervorrichtung **208** unterscheidet sich von der in **Fig. 17** gezeigten Leistungshalbleitervorrichtung **201** darin, dass sie weiter einen Stromfassungssensor **99** zum Erfassen eines Gesamtstroms  $I_t$  enthält, der durch die IGBTs Q1, Q2 fließt.

Beispielsweise wird ein Stromwandler als Stromerfassungssensor **99** verwendet.

**[0159]** Eine in der in **Fig. 27** gezeigten Leistungshalbleitervorrichtung **208** verwendete integrierte Schaltung **5d** unterscheidet sich von der in der in **Fig. 17** gezeigten Leistungshalbleitervorrichtung **201** bereitgestellten integrierten Schaltung **5** darin, dass sie weiter einen Anschluss CS zum Empfangen eines Detektionssignals von dem Stromerfassungssensor enthält. Da der in **Fig. 27** gezeigte Aufbau ansonsten derselbe ist wie derjenige der in **Fig. 17** gezeigten Leistungshalbleitervorrichtung **201**, sind dieselben oder einander entsprechende Komponenten durch dieselben Bezugszeichen gekennzeichnet, und ihre Beschreibung wird nicht wiederholt.

**[0160]** Die integrierte Schaltung **5d** bestimmt auf der Grundlage eines Erfassungswerts von dem Stromerfassungssensor **99** in welchem Bereich der durch die Schwellenwerte  $I_{th1}$ ,  $I_{th2}$  unterteilten Bereiche, die mit Bezug auf **Fig. 3A** und **Fig. 4** beschrieben sind, der Gesamtstrom  $I_t$  liegt. Die integrierte Schaltung **5d** wählt dann einen optimalen Schaltzeitablauf basierend auf einem Ergebnis dieser Bestimmung während einer Zeitspanne, bis die nächste Bestimmung auf der Grundlage eines Erfassungswerts von dem Stromerfassungssensor **99** durchgeführt wird. Wenn beispielsweise der Gesamtstrom  $I_t$  kleiner als der in **Fig. 3A** gezeigte Schwellenwert  $I_{th1}$  ist, steuert die integrierte Schaltung **5d** die Transistoren Q11, Q22, Q33, Q44 mit einem wie in der unten beschriebenen **Fig. 28** gezeigten Zeitablauf ein und aus.

**[0161]** **Fig. 28** ist ein Diagramm, das ein Beispiel für ein Zeitverlaufsdiagramm eines Steuersignals zeigt, das von der in **Fig. 27** gezeigten integrierten Schaltung **5d** ausgegeben wird. Mit Bezug auf **Fig. 27** und **Fig. 28** schaltet die integrierte Schaltung **5d** zum Zeitpunkt  $T_a$  als Reaktion auf einen Wechsel des Treibersignals DS auf H-Pegel ein von dem Ausgangsanschluss OUT1 ausgegebenes Steuersignal auf H-Pegel, und sie schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf L-Pegel. Somit wird der Transistor Q11 eingeschaltet, und die Transistoren Q22, Q44 werden ausgeschaltet.

**[0162]** Dementsprechend wird der IGBT Q1 eingeschaltet. Zum Zeitpunkt  $t_2$ , der um eine vorbestimmte Zeitspanne später liegt als der Zeitpunkt  $t_1$ , schaltet die integrierte Schaltung **5d** das von dem Ausgangsanschluss OUT3 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q33 eingeschaltet, und demzufolge wird der IGBT Q2 später eingeschaltet als der IGBT Q1.

**[0163]** Zum Zeitpunkt  $t_3$  schaltet die integrierte Schaltung **5d** als Reaktion auf einen Wechsel des

Treibersignals DS auf L-Pegel das von dem Ausgangsanschluss OUT1 ausgegebene Steuersignal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT2 ausgegebene Steuersignal auf H-Pegel. Somit wird der Transistor Q11 ausgeschaltet, und der Transistor Q22 wird eingeschaltet. Demzufolge wird der IGBT Q1 ausgeschaltet.

**[0164]** Zum Zeitpunkt  $t_4$ , der um eine vorbestimmte Zeitspanne später liegt als der Zeitpunkt  $t_3$ , schaltet die integrierte Schaltung **5d** das von dem Ausgangsanschluss OUT3 ausgegebene Signal auf L-Pegel, und sie schaltet das von dem Ausgangsanschluss OUT4 ausgegebene Signal auf H-Pegel. Somit wird der Transistor Q33 ausgeschaltet, und der Transistor Q44 wird eingeschaltet. Demzufolge wird der IGBT Q2 später ausgeschaltet als der IGBT Q1.

**[0165]** Danach wird ein ähnlicher Betrieb wiederholt. Ein Betrieb der integrierten Schaltung **5d** zu den Zeitpunkten  $t_5$ – $t_8$  ist nämlich derselbe wie der Betrieb zu den Zeitpunkten  $t_1$ – $t_4$ , und ein Betrieb der integrierten Schaltung **5d** zu den Zeitpunkten  $t_9$  und  $t_{10}$  ist derselbe wie der Betrieb zu den Zeitpunkten  $t_1$ ,  $t_2$ .

**[0166]** Der oben beschriebene Betrieb der integrierten Schaltung **5d** kann einen Steuerbetrieb verwirklichen, der derselbe ist wie der in **Fig. 2A** gezeigte, der in der ersten Ausführungsform beschrieben ist.

**[0167]** Wenn der Gesamtstrom  $I_t$  größer gleich dem in **Fig. 3A** gezeigten Schwellenwert  $I_{th1}$  und kleiner als der in **Fig. 4** gezeigte Schwellenwert  $I_{th2}$  ist, werden die Transistoren Q11, Q22, Q33 und Q44 mit demselben Zeitablauf ein und aus gesteuert wie mit dem in dem Zeitverlaufsdiagramm in **Fig. 18** gezeigten der in der zweiten Ausführungsform beschrieben ist. Somit kann wie in dem Fall von **Fig. 18** ein Steuerbetrieb verwirklicht werden, der derselbe ist wie der in **Fig. 2B** gezeigte, der in der ersten Ausführungsform beschrieben ist.

**[0168]** In einem Fall, in dem der Gesamtstrom größer gleich dem in **Fig. 4** gezeigten Schwellenwert  $I_{th2}$  ist, schaltet die integrierte Schaltung **5d**, wenn das Treibersignal DS auf H-Pegel wechselt, die von den Ausgangsanschlüssen OUT1, OUT3 ausgegebenen Steuersignale auf H-Pegel, und sie schaltet die von den Steueranschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf L-Pegel. Somit werden die IGBTs Q1, Q2 gleichzeitig eingeschaltet. Außerdem schaltet die integrierte Schaltung **5d**, wenn das Treibersignal DS auf L-Pegel wechselt, die von den Ausgangsanschlüssen OUT1, OUT3 ausgegebenen Steuersignale auf L-Pegel, und die schaltet die von den Ausgangsanschlüssen OUT2, OUT4 ausgegebenen Steuersignale auf H-Pegel. Somit werden die IGBTs Q1, Q2 gleichzeitig ausgeschaltet. Wie oben beschrieben, kann derselbe Steuerbetrieb verwirk-

licht werden wie der in **Fig. 2C** gezeigte, der in der ersten Ausführungsform beschrieben ist.

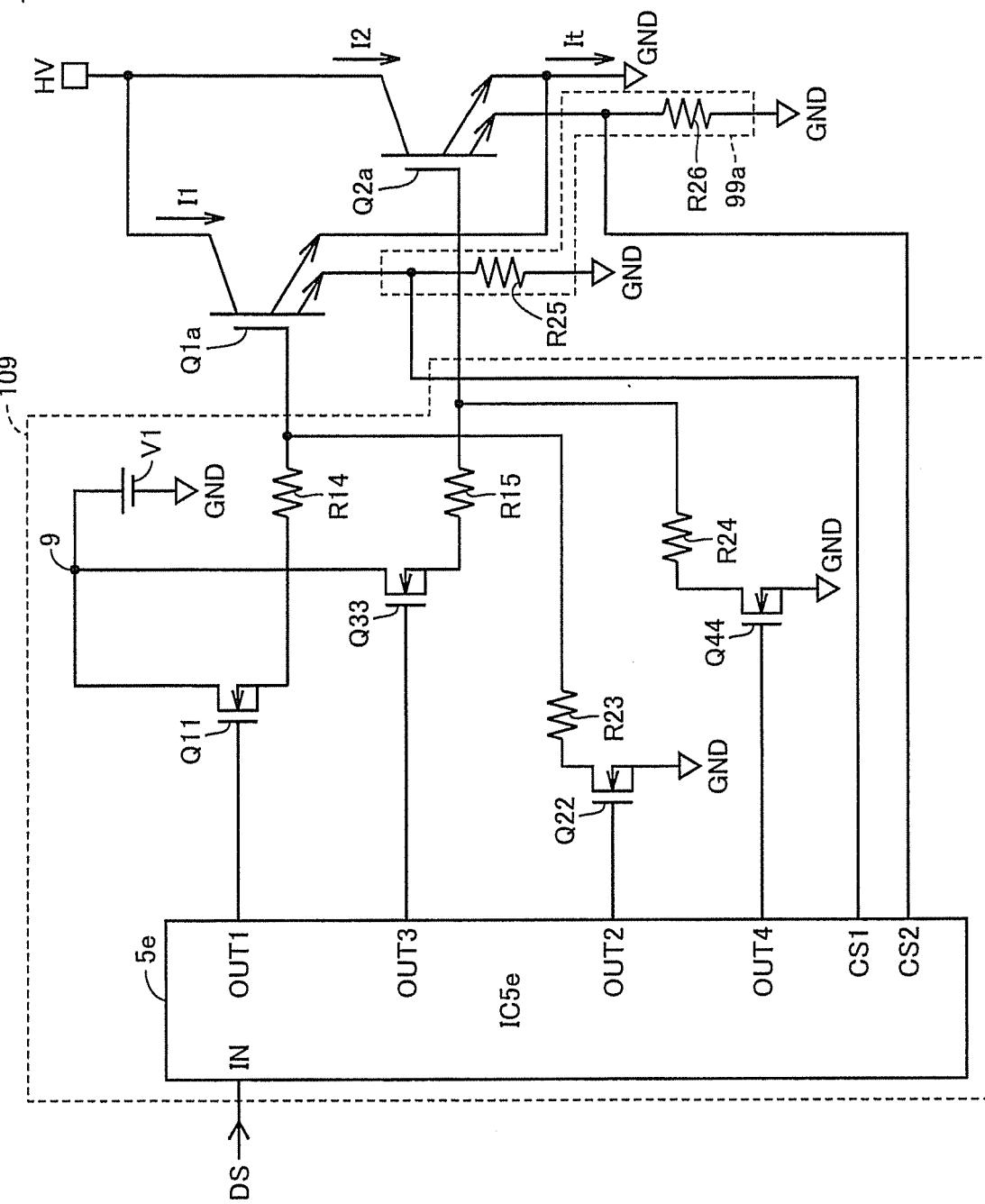

**[0169]** **Fig. 29** ist ein Schaltbild eines Aufbaus einer Leistungshalbleitervorrichtung **209** gemäß einer zehnten Ausführungsform. Die in **Fig. 29** gezeigte Leistungshalbleitervorrichtung **209** ist eine Abwandlung der in **Fig. 27** gezeigten Leistungshalbleitervorrichtung **208**. Die Leistungshalbleitervorrichtung **209** unterscheidet sich nämlich von der Leistungshalbleitervorrichtung **208** darin, dass sie anstelle der in **Fig. 27** gezeigten IGBTs Q1, Q2 die IGBTs Q1a, Q2a mit Fühlanschluss enthält. Ein Teil des Hauptstroms, der durch einen Emitteranschluss eines IGBT fließt, fließt abgeleitet über einen Fühlanschluss. Außerdem unterscheidet sich die Leistungshalbleitervorrichtung **209** von der Leistungshalbleitervorrichtung **208** darin, dass sie anstelle des in **Fig. 27** gezeigten Stromerfassungssensors **99** Messwiderstände (Shuntwiderstände) R25, R26 enthält. Der Messwiderstand R25 ist zwischen den Fühlanschluss des IGBT Q1a und den Masseknoten GND geschaltet, und der Messwiderstand R26 ist zwischen den Fühlanschluss des IGBT Q2a und den Masseknoten GND geschaltet. Wie der in **Fig. 27** gezeigte Stromerfassungssensor **99** wirken die Messwiderstände R25, R26 als ein Stromerfassungssensor **99a** zum Überwachen der Hauptströme I1, I2, die jeweils durch die IGBTs Q1a, Q2a fließen.

**[0170]** Eine in einer **Fig. 29** gezeigten Treibersteuereinheit **109** bereitgestellte integrierte Schaltung **5e** unterscheidet sich von der in **Fig. 27** gezeigten integrierten Schaltung **5d** darin, dass sie anstelle des in **Fig. 27** gezeigten Erfassungsanschlusses CS Erfassungsanschlüsse CS1, CS2 enthält zum Erfassen der Spannungen, die jeweils an den Messwiderständen R25, R26 anliegen. Die integrierte Schaltung **5e** steuert die Transistoren Q11, Q22, Q33, Q44 basierend auf der Größe der über die Messwiderstände R25, R26 überwachten Ströme I1, I2 in einem optimalen Zeitablauf ein und aus.