(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5205173号

(P5205173)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl.

H01L 25/065 (2006.01)

F 1

H01L 25/08

Z

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

請求項の数 11 (全 28 頁)

(21) 出願番号

特願2008-205038 (P2008-205038)

(22) 出願日

平成20年8月8日(2008.8.8)

(65) 公開番号

特開2010-40955 (P2010-40955A)

(43) 公開日

平成22年2月18日(2010.2.18)

審査請求日

平成23年7月6日(2011.7.6)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 黒田 宏

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 田代 吉成

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のボンディングリードが形成された表面、及び前記表面と反対側の裏面を有する基板と、

複数の第1パッドが形成された第1主面、及び前記第1主面とは反対側の第1裏面を有し、平面視において前記基板の前記複数のボンディングリードの内側に位置するように、前記基板の前記表面上に搭載された第1半導体チップと、

複数の第2パッドが形成され、かつ前記第1半導体チップの外形寸法よりも小さい第2主面、及び前記第2主面とは反対側の第2裏面を有し、平面視において前記第1半導体チップの前記複数の第1パッドの内側に位置し、前記第2裏面が前記第1半導体チップと対向するように、前記第1半導体チップ上に搭載された第2半導体チップと、

前記第1半導体チップの前記複数の第1パッドと前記基板の前記複数のボンディングリードのうちの複数の第1ボンディングリードとをそれぞれ電気的に接続する複数の第1接続手段と、

前記第2半導体チップの前記複数の第2パッドと前記基板の前記複数のボンディングリードのうちの複数の第2ボンディングリードとをそれぞれ電気的に接続する複数の第2接続手段と、

前記第1半導体チップ、前記第2半導体チップ及び前記複数の第2接続手段を封止する封止体と、

前記基板の前記裏面に設けられた複数の外部端子と、

10

20

を含み、

前記第2半導体チップは、前記第2半導体チップの端部と前記第1半導体チップの端部との距離が前記第1半導体チップの端部と前記基板の前記ボンディングリードとの距離よりも長くなるように、前記第1半導体チップの前記第1主面上に搭載され、

前記第2接続手段は、ワイヤであり、

前記第2ボンディングリード上における前記ワイヤと前記基板の前記表面との成す角度は、前記第2半導体チップの前記第2パッド上における前記ワイヤと前記第2半導体チップの前記第2主面との成す角度より大きいことを特徴とする半導体装置。

#### 【請求項2】

請求項1記載の半導体装置において、

10

前記基板の前記表面の平面形状は、一対の第1辺と、前記第1辺と交差する一対の第2辺を有する四角形であり、

前記複数の第2ボンディングリードは、前記基板の前記第1辺に沿って形成され、

前記第2半導体チップの前記第2主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第3辺と、前記第3辺と交差する一対の第4辺を有する四角形であり、

前記複数の第2パッドは、前記第2半導体チップの前記第3辺に沿って形成されていることを特徴とする半導体装置。

#### 【請求項3】

請求項2記載の半導体装置において、

20

前記複数の第2ボンディングリードは、さらに前記第2辺に沿って形成され、

前記複数の第2パッドは、さらに前記第4辺に沿って形成され、

前記基板の前記第2辺に沿って形成された前記第2ボンディングリード上における前記ワイヤと前記基板の前記表面との成す角度は、前記第2半導体チップの前記第4辺に沿って形成された前記第2パッド上における前記ワイヤと前記第2半導体チップの前記第2主面との成す角度より小さいことを特徴とする半導体装置。

#### 【請求項4】

請求項3記載の半導体装置において、前記第1半導体チップの前記第1主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第5辺と、前記第5辺と交差する一対の第6辺を有する四角形であり、

前記第1半導体チップの前記第5辺と前記基板の前記第1辺に沿って形成された前記第2ボンディングリードとの距離(M1)は、前記第1半導体チップの前記第6辺と前記基板の前記第2辺に沿って形成された前記第2ボンディングリードとの距離(M2)よりも短いことを特徴とする半導体装置。

30

#### 【請求項5】

請求項4記載の半導体装置において、前記第2半導体チップの厚さは、前記第1半導体チップの厚さよりも厚いことを特徴とする半導体装置。

#### 【請求項6】

(a) 複数のボンディングリードが形成された表面、及び前記表面と反対側の裏面を有する基板を準備する工程；

(b) 複数の第1パッドが形成された第1主面、及び前記第1主面とは反対側の第1裏面を有する第1半導体チップを、平面視において前記基板の前記複数のボンディングリードの内側に位置するように、前記基板の前記表面上に搭載する工程；

(c) 複数の第2パッドが形成され、かつ前記第1半導体チップの外形寸法よりも小さい第2主面、及び前記第2主面とは反対側の第2裏面を有する第2半導体チップを、平面視において前記第1半導体チップの前記複数の第1パッドの内側に位置し、前記第2裏面が前記第1半導体チップと対向するように、前記第1半導体チップ上に搭載する工程；

(d) 前記第1半導体チップの前記複数の第1パッドと前記基板の前記複数のボンディングリードのうちの複数の第1ボンディングリードとを、複数の第1接続手段を介してそれぞれ電気的に接続する工程；

(e) 前記第2半導体チップの前記複数の第2パッドと前記基板の前記複数のボンディ

40

50

ングリードのうちの複数の第2ボンディンググリードとを、複数の第2接続手段を介してそれぞれ電気的に接続する工程；

(f) 前記第1半導体チップ、前記第2半導体チップ及び前記複数の第2接続手段を樹脂で封止する工程；

(g) 前記基板の前記裏面に複数の外部端子を形成する工程；

を含み、

前記第2半導体チップは、前記第2半導体チップの端部と前記第1半導体チップの端部との距離が前記第1半導体チップの端部と前記基板の前記ボンディンググリードとの距離よりも長くなるように、前記第1半導体チップの前記第1主面上に搭載され、

前記第2接続手段は、ワイヤであり、

10

前記(e)工程では、前記基板の前記第2ボンディンググリードに前記ワイヤの一端部を接続した後、前記ワイヤの一端部とは反対側の他端部を前記第2半導体チップの前記第2パッドに接続することを特徴とする半導体装置の製造方法。

#### 【請求項7】

請求項6記載の半導体装置の製造方法において、前記基板の前記表面の平面形状は、一対の第1辺と、前記第1辺と交差する一対の第2辺を有する四角形であり、

前記複数の第2ボンディンググリードは、前記基板の前記第1辺に沿って形成され、

前記第2半導体チップの前記第2主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第3辺と、前記第3辺と交差する一対の第4辺を有する四角形であり、

前記複数の第2パッドは、前記第2半導体チップの前記第3辺に沿って形成されていることを特徴とする半導体装置の製造方法。

20

#### 【請求項8】

請求項7記載の半導体装置の製造方法において、前記(f)工程では、前記基板の前記第1辺側から前記樹脂を供給することを特徴とする半導体装置の製造方法。

#### 【請求項9】

請求項8記載の半導体装置の製造方法において、

前記複数の第2ボンディンググリードは、さらに前記第2辺に沿って形成され、

前記複数の第2パッドは、さらに前記第4辺に沿って形成され、

前記基板の前記第2辺に沿って形成された前記第2ボンディンググリードと前記第2半導体チップの前記第4辺に沿って形成された前記第2パッドとを電気的に接続する前記ワイヤは、前記第2半導体チップの前記第2パッドに前記ワイヤの一端部を接続した後、前記ワイヤの前記一端部とは反対側の前記他端部を前記基板の前記第2ボンディンググリードに接続することを特徴とする半導体装置の製造方法。

30

#### 【請求項10】

請求項9記載の半導体装置の製造方法において、前記第1半導体チップの前記第1主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第5辺と、前記第5辺と交差する一対の第6辺を有する四角形であり、

前記第1半導体チップの前記第5辺と前記基板の前記第1辺に沿って形成された前記第2ボンディンググリードとの距離(M1)は、前記第1半導体チップの前記第6辺と前記基板の前記第2辺に沿って形成された前記第2ボンディンググリードとの距離(M2)よりも短いことを特徴とする半導体装置の製造方法。

40

#### 【請求項11】

請求項10記載の半導体装置の製造方法において、前記第2半導体チップの厚さは前記第1半導体チップの厚さより厚いことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置及びその製造技術に関し、特に、積層された複数の半導体チップを有するマルチチップモジュールに関する。

#### 【背景技術】

50

**【0002】**

チップ積層型の半導体装置において、パッケージ基板のアドレス端子に対応したボンディングリードに接続されるボンディングパッドとデータ端子に対応したボンディングリードに接続されるボンディングパッドとが4つの辺のうちの2つの辺に振り分けて配置された半導体チップとメモリチップとを積層する技術がある（例えば、特許文献1参照）。

【特許文献1】特開2004-71838号公報

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

近年、半導体装置の高集積化に伴い、複数の半導体チップを1つの半導体装置（パッケージ）に混載する傾向にある。また、半導体装置の小型化の要求もあり、この要求に対応するために、前記特許文献1に示すように、基板（配線基板）上に複数の半導体チップを積層することが有効とされている。10

**【0004】**

今回、本願発明者は、基板上に複数の半導体チップが積層され、かつ複数のワイヤを介して半導体チップのパッドと基板の電極が電気的に接続される構成の半導体装置について検討した。

**【0005】**

そして、チップ積層型の半導体装置において更なる小型化が進んだ際、上段側の半導体チップのパッドに接続されたワイヤが、下段の半導体チップの端部に接触する問題を発見した。この問題について本願発明者が検討した結果、以下のことがわかった。20

**【0006】**

まず、半導体装置の小型化が進むと、基板の外形寸法が小さくなる。

**【0007】**

そのため、下段側の半導体チップの端部と基板の表面の周縁部に形成されたボンディングリードとの距離が短くなる。

**【0008】**

一方、半導体チップの高機能化に伴い、半導体チップの外形寸法もシルリンクする傾向にある。そのため、複数の半導体チップのそれぞれの外形寸法に、極端な差が生じてきている。30

**【0009】**

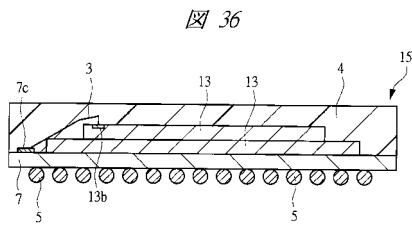

今回、本願発明者が検討した半導体チップは、上段側の半導体チップの外形寸法が下段側の半導体チップの外形寸法に比べ小さい場合である。このような状態で、上段側の半導体チップのパッドにワイヤの一端部を形成してから、このパッドに対応する基板のボンディングリードにワイヤの他端部を接続する、所謂、正ボンディング方式を適用した場合、図36の比較例の半導体装置15に示すように、ワイヤ3の一部が下段側の半導体チップ13の端部（角部）と接触することがわかった。

**【0010】**

なお、前記特許文献1では、半導体装置の外形寸法がシルリンクされた場合に生じる問題（ワイヤがチップに接触する問題）の具体的な対応策については、記載が無い。40

**【0011】**

本発明の目的は、半導体装置における半導体チップとのワイヤショートを防止することができる技術を提供することにある。

**【0012】**

また、本発明の他の目的は、半導体装置の小型化を図ることができる技術を提供することにある。

**【0013】**

また、本発明の他の目的は、半導体装置の低コスト化を図ることができる技術を提供することにある。

**【0014】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0016】

すなわち、本発明は、複数のボンディングリードが形成された基板と、基板の複数のボンディングリードの内側に位置するように基板の表面上に搭載された第1半導体チップと、第1半導体チップの複数の第1パッドの内側に位置するように第1半導体チップ上に搭載された第2半導体チップとを含むものである。さらに、本発明は、第1半導体チップの複数の第1パッドと基板の複数のボンディングリードとを電気的に接続する複数の第1接続手段と、第2半導体チップの複数の第2パッドと基板の複数のボンディングリードとを電気的に接続する複数の第2接続手段と、第1半導体チップ、第2半導体チップ、複数の第1接続手段及び第2接続手段を封止する封止体と、基板の裏面に設けられた複数の外部端子とを含むものである。さらに、本発明は、第2半導体チップの端部と第1半導体チップの端部との距離が第1半導体チップの端部と基板のボンディングリードとの距離よりも長くなるように、第2半導体チップが第1半導体チップの第1主面上に搭載され、第2接続手段はワイヤであり、第2ボンディングリード上におけるワイヤと基板の表面との成す角度は、第2半導体チップの第2パッド上におけるワイヤと第2半導体チップの第2主面との成す角度より大きいものである。10

【0017】

また、本発明は、(a)複数のボンディングリードが形成された基板を準備する工程；(b)複数の第1パッドが形成された第1半導体チップを、基板の複数のボンディングリードの内側に位置するように基板の表面上に搭載する工程；(c)第1半導体チップの外形寸法よりも小さい第2主面を有する第2半導体チップを、第1半導体チップの複数の第1パッドの内側に位置するように第1半導体チップ上に搭載する工程；を含むものである。さらに、本発明は、(d)第1半導体チップの複数の第1パッドと基板の複数のボンディングリードとを複数の第1接続手段を介してそれぞれ電気的に接続する工程；(e)第2半導体チップの複数の第2パッドと基板の複数のボンディングリードとを複数の第2接続手段を介してそれぞれ電気的に接続する工程；を含むものである。さらに、本発明は、(f)第1半導体チップ、第2半導体チップ、複数の第1接続手段及び複数の第2接続手段を樹脂で封止する工程；(g)基板の裏面に複数の外部端子を形成する工程；を含み、第2半導体チップは、第2半導体チップの端部と第1半導体チップの端部との距離が第1半導体チップの端部と基板のボンディングリードとの距離よりも長くなるように第1半導体チップの第1主面上に搭載されているものである。さらに、本発明は、第2接続手段はワイヤであり、前記(e)工程では、基板のボンディングリードにワイヤの一端部を接続した後、ワイヤの一端部とは反対側の他端部を第2半導体チップの第2パッドに接続するものである。30

【発明の効果】

【0018】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0019】

上段側の第2半導体チップの端部と下段側の第1半導体チップの端部との距離が第1半導体チップの端部と基板のボンディングリードとの距離よりも長くなるように、第2半導体チップが第1半導体チップ上に搭載され、かつ第2半導体チップと接続する複数の第2ワイヤが逆ボンディング方式により形成されていることで、下段側の第1半導体チップの端部と第2ワイヤの間にクリアランスを大きく設けることができる。これにより、下段側の半導体チップとワイヤのショートを防止することができる。40

50

**【発明を実施するための最良の形態】****【0020】**

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

**【0021】**

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

**【0022】**

10

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

**【0023】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

**【0024】****(実施の形態1)**

20

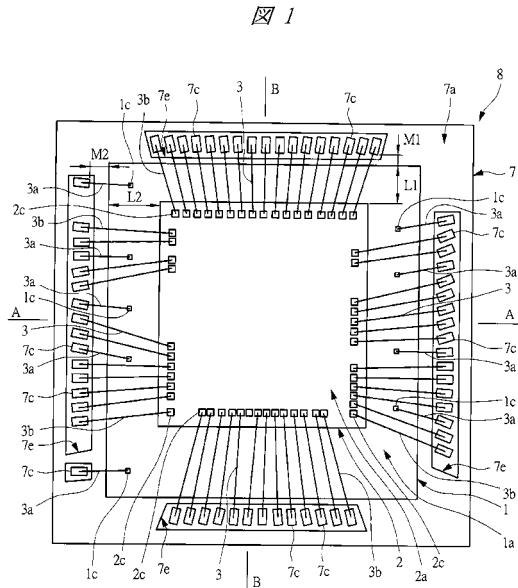

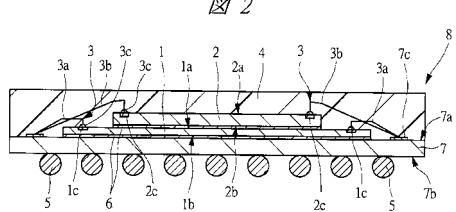

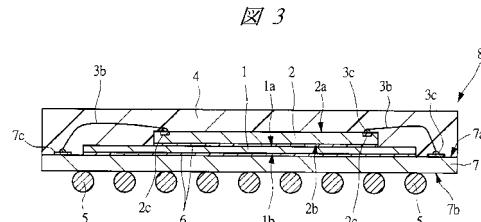

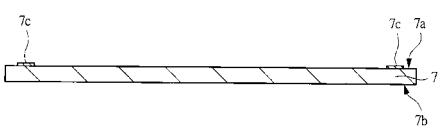

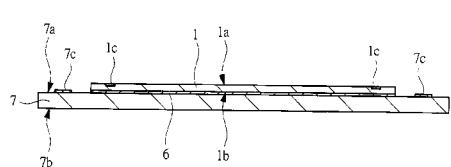

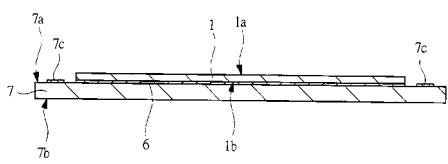

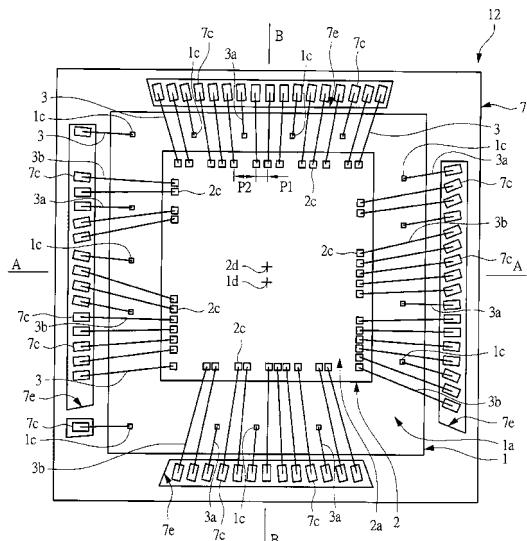

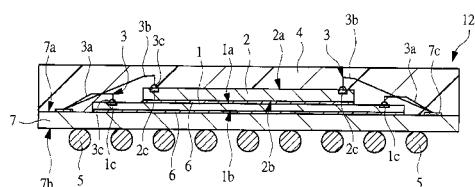

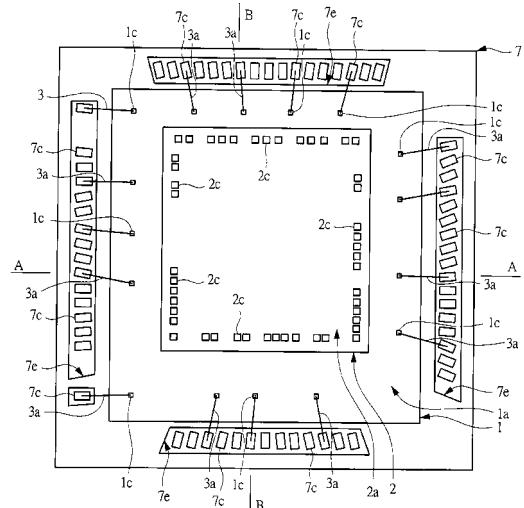

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1のA-A線に沿って切断した構造の一例を示す断面図、図3は図1のB-B線に沿って切断した構造の一例を示す断面図である。

**【0025】**

図1～図3に示す本実施の形態1の半導体装置は、配線を有した基板である配線基板7上に複数の半導体チップが積層された（積み重ねられた）半導体パッケージであり、本実施の形態1では、前記半導体装置の一例として、配線基板7上に2つの半導体チップが積層されたマルチチップモジュール8を取り上げて説明する。

**【0026】**

30

マルチチップモジュール8において、積層される一方の半導体チップは、例えば、RF-I C（Integrated Circuit）であり、他方の半導体チップは、Secure I Cである。この場合、それぞれの半導体チップを制御する信号は、マルチチップモジュール8と電気的に接続される外部機器から発信される。

**【0027】**

マルチチップモジュール8の詳細構成について説明すると、配線基板7は、表面（正面）、チップ搭載面）7aと、表面7aと反対側の裏面7bを有している。表面7aと裏面7bのそれぞれの平面形状は、一対の辺（第1辺）と、この辺（第1辺）と交差する一対の辺（第2辺）を有する四角形から成り、表面7aの各辺に沿って（周縁部に）複数のボンディングリード（電極）7cが形成されている。また、複数のボンディングリード7cは、積層される一方の半導体チップ（下段側の半導体チップ1）と電気的に接続される第1ボンディングリードと、他方の半導体チップ（上段側の半導体チップ2）と電気的に接続される第2ボンディングリードとを有している。

40

**【0028】**

また、配線基板7の表面7a上には、配線基板7の複数のボンディングリード7cの内側に位置するように第1半導体チップ1が接着剤6を介してフェイスアップ実装されている。尚、この接着剤6は、フィルム状の接着材である。また、フェイスアップ実装とは、半導体チップ（第1半導体チップ1）の裏面（第1裏面1b）が配線基板7の表面7aと対向するように、半導体チップを配線基板7上に搭載することである。

**【0029】**

なお、図1に示すように、下段チップ（1段目チップ）である第1半導体チップ1の平

50

面形状は、一対の辺（第5辺）と、この辺（第5辺）と交差する一対の辺（第6辺）とを有する四角形から成り、第5辺は配線基板7の第1辺と並んでおり、第6辺は配線基板7の第2辺と並んでいる。そして、四角形の第1主面1aには、一対の辺（第6辺）のそれぞれに沿ってのみ複数の第1パッド（第1電極パッド）1cが形成されている。また、本実施の形態1のマルチチップモジュール8では、この辺（第6辺）と交差する一対の辺（第5辺）側には第1パッド1cは形成されていない。

#### 【0030】

また、第1半導体チップ1上には第2半導体チップ2が接着剤6を介して積層されている。尚、この接着剤6は、フィルム状の接着材である。また、第1半導体チップ1の第1主面1a上に、複数の第1パッド1cの内側に位置するように、第1半導体チップ1の外形寸法よりも小さい第2主面2aを有した第2半導体チップ2が接着剤6を介してフェイスアップ実装されている。すなわち、上段側の半導体チップ（第2半導体チップ2）の裏面（第2裏面2b）が下段側の半導体チップ（第1半導体チップ1）の主面（第1主面1a）と対向するように、下段の半導体チップ上に搭載されている。10

#### 【0031】

なお、上段チップ（2段目チップ）である第2半導体チップ2の平面形状は、一対の辺（第3辺）と、この辺（第3辺）と交差する一対の辺（第4辺）とを有する四角形から成り、第3辺は配線基板7の第1辺と並んでおり、第4辺は配線基板7の第2辺と並んでいる。そして、四角形の第2主面2aには、各辺（第3辺及び第4辺）に沿って複数の第2パッド（第2電極パッド）2cが周縁部に形成されている。20

#### 【0032】

また、第1半導体チップ1の複数の第1パッド1cとこれらに対応する配線基板7の複数のボンディングリード（第1ボンディングリード）7cとがそれぞれ複数の第1接続手段（第1ワイヤ）3aによって電気的に接続されており、さらに第2半導体チップ2の複数の第2パッド2cとこれらに対応する配線基板7の複数のボンディングリード（第2ボンディングリード）7cとがそれぞれ複数の第2接続手段（第2ワイヤ）3bによって電気的に接続されている。尚、本実施の形態1における第1及び第2接続手段のそれぞれはワイヤであり、例えば金（Au）から成る。

#### 【0033】

また、図2及び図3に示すように配線基板7の表面7a上には、第1半導体チップ1、第2半導体チップ2、複数の第1接続手段3a及び複数の第2接続手段3bを封止する封止体4が形成されている。この封止体4は、図27に示すモールドレジン（樹脂）10から成るものである。また、図2に示すように、第1パッド1c及び第2パッド2c上には、金バンプ3cが形成されている。これは、ワイヤボンディング工程において、ワイヤの一端部を放電させることで形成されたボール状の金バンプ3cであり、ワイヤとパッド（第1パッド1c、第2パッド2c）との接続性を向上させるためである。また、図3に示すように、後に説明する逆ボンディング方式を適用する場合は、配線基板7のボンディングリード7c上だけでなく、半導体チップのパッド上にも金バンプ3cを形成している。この理由については、後ほど説明する。30

#### 【0034】

また、配線基板7の裏面7bには、マルチチップモジュール8の複数の外部端子である半田ボール5が格子状に配置されて設けられている。40

#### 【0035】

なお、図1に示すように本実施の形態1のマルチチップモジュール8では、第2半導体チップ2は、第2半導体チップ2の端部（端面、側面）と第1半導体チップ1の端部（端面、側面）との距離（L1, L2）が第1半導体チップ1の端部（端面、側面）と配線基板7のボンディングリード7cの端部との距離（M1, M2）よりもそれ長くなるように、第1半導体チップ1の第1主面1a上に搭載されている（L1 > M1, L2 > M2）。尚、本実施の形態におけるL1の距離は約0.5mm、L2の距離は約0.6mm、M1の距離は約0.1mm、M2の距離は約0.3mmであり、L1及びL2のそれぞれ50

は、何れもM1及びM2の距離よりも長い。また、図1に示すように、下段チップ(1段目チップ)の半導体チップ1の平面形状は長方形である。そのため、第1半導体チップ1の第5辺と配線基板7の第1辺に沿って形成されたボンディングリード7cの端部との距離(M1)は、第1半導体チップ1の第6辺と配線基板7の第2辺に沿って形成されたボンディングリード7cの端部との距離(M2)よりも短い。

#### 【0036】

すなわち、マルチチップモジュール8は、その小型化によって配線基板7の外形寸法が小さいものであり、その結果、下段側の第1半導体チップ1の端部とその外側に配置された配線基板7のボンディングリード7cとの距離が短く設定されたものであり、さらに、上段側の第2半導体チップ2の外形寸法が下段側の第1半導体チップ1の外形寸法に比べて小さい構造のものである。10

#### 【0037】

このような構造のマルチチップモジュール8において、第2半導体チップ2の複数の第2パッド2cとこれらに対応する配線基板7の複数のボンディングリード7cとを電気的に接続する複数の第2接続手段(ワイヤ)3bが、部分的に逆ボンディング方式によって形成されている。ここで、逆ボンディング方式とは、配線基板のボンディングリードにワイヤの一端部を接続した後、ワイヤの一端部とは反対側の他端部を半導体チップのパッドに接続することである。

#### 【0038】

すなわち、マルチチップモジュール8の組み立てのワイヤボンディング工程において、上段側の第2半導体チップ2の複数の第2パッド2cと、これらに対応する配線基板7の複数のボンディングリード7cをワイヤボンディングする際に、まず、配線基板7のボンディングリード7cに第2ワイヤ3bの一端部を接続し、その後、第2ワイヤ3bの一端部とは反対側の他端部を第2半導体チップ2の第2パッド2cに接続するものである。このとき、半導体チップ(第2半導体チップ2)のパッド(第2パッド2c)上には、金(Au)から成るバンプ3cが形成されている。これにより、ワイヤとパッドとの接続性を向上することができる。また、ワイヤの一部が半導体チップの正面と接触するのを抑制できる。

#### 【0039】

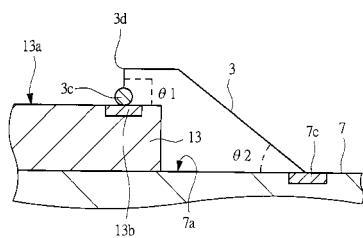

ここで、図28と図29を用いて、正ボンディングを行った時と逆ボンディングを行った時のそれぞれのワイヤ形状の特徴について説明する。図28は正ボンディングを行った後のワイヤ3の形状の一例を示すものであり、一方、図29は逆ボンディングを行った後のワイヤ3の形状の一例を示すものである。30

#### 【0040】

図28に示すように、正ボンディングでは1st側が半導体チップ13のパッド13bであり、2nd側が配線基板7のボンディングリード7cとなる。その際、まず、ワイヤ3の一端部を半導体チップ13のパッド13bに接続し、接続後、ワイヤ3を略直上に引き上げ、所定の高さでワイヤ3を略水平に引き出した後、2nd側として配線基板7のボンディングリード7cに向けてワイヤ3を斜めに打ち降ろしてボンディングリード7cにワイヤ3の他端部を接続する。したがって、正ボンディングでは、半導体チップ13のパッド13b上におけるワイヤ3と半導体チップ13の正面13aとの成す角度(1)は、略直角であり、配線基板7のボンディングリード7c上におけるワイヤ3と配線基板7の表面7aとの成す角度(2)より大きくなる(1 > 2)。40

#### 【0041】

一方、図29に示す逆ボンディングでは、1st側が配線基板7のボンディングリード7cであり、2nd側が半導体チップ13のパッド13bとなる。その際、まず、ワイヤ3の一端部を配線基板7のボンディングリード7cに接続し、接続後、ワイヤ3を略直上に引き上げ、所定の高さでワイヤ3を略水平に引き出した後、2nd側として半導体チップ13のパッド13bに向けてワイヤ3を引き出してパッド13b上の金バンプ3cにワイヤ3の他端部を接続する。したがって、逆ボンディングでは、配線基板7のボンディン50

グリード 7 c 上におけるワイヤ 3 と配線基板 7 の表面 7 aとの成す角度( 4 )は、略直角(急峻な角度)であり、半導体チップ 1 3 のパッド 1 3 b 上におけるワイヤ 3 と半導体チップ 1 3 の正面 1 3 a との成す角度( 3 )より大きくなる( 4 > 3 )。

#### 【 0 0 4 2 】

また、別の言い方をすると、正ボンディング(図 2 8 )と逆ボンディング(図 2 9 )のそれぞれの 1 s t 側において、 1 s t ボンド点から最も近いワイヤ 3 の折り曲げ点 3 d までの距離は、正ボンディングよりも逆ボンディングの方が長い。

#### 【 0 0 4 3 】

以上のように本実施の形態 1 のマルチチップモジュール 8 では、図 3 に示すように、配線基板 7 のボンディンググリード 7 c からワイヤ 3 を略直上(急峻)に引き上げる逆ボンディングを採用することで、下段側の第 1 半導体チップ 1 の端部とその外側に配置された配線基板 7 のボンディンググリード 7 c との距離が短く設定された構造であっても、ワイヤボンディングを行うことが可能になる。10

#### 【 0 0 4 4 】

すなわち、本実施の形態 1 の図 1 及び図 3 に示すように、第 2 半導体チップ 2 (上段)の端部と第 1 半導体チップ 1 (下段)の端部との距離( L 1 , L 2 )が第 1 半導体チップ 1 の端部と配線基板 7 のボンディンググリード 7 c との距離( M 1 , M 2 )よりも長い構造では、上段側の半導体チップ(第 2 半導体チップ 2 )のパッド(第 2 パッド 2 c )と配線基板 7 のボンディンググリード(第 2 ボンディンググリード) 7 c とを電気的に接続するワイヤを、逆ボンディング方式により形成することが好ましい。20

#### 【 0 0 4 5 】

この結果、下段側の第 1 半導体チップ 1 の端部と第 2 ワイヤ 3 b との間にクリアランスを大きく設けることができ、下段側の第 1 半導体チップ 1 とワイヤ 3 のショートを防止することができる。

#### 【 0 0 4 6 】

また、配線基板 7 のボンディンググリード 7 c に対して第 2 ワイヤ 3 b を逆ボンディングすることで、下段の第 1 半導体チップ 1 と配線基板 7 の端部との隙間が狭くても上段の第 2 半導体チップ 2 とボンディンググリード 7 c を第 2 ワイヤ 3 b で接続することができ、したがって、配線基板 7 の小型化を図ることができる。その結果、マルチチップモジュール 8 の小型化を図ることができる。30

#### 【 0 0 4 7 】

なお、本実施の形態 1 のマルチチップモジュール 8 では、図 1 ~ 図 3 に示すように、第 2 半導体チップ 2 の第 2 パッド 2 c と配線基板 7 のボンディンググリード 7 c とを接続する複数の第 2 ワイヤ 3 b において、逆ボンディングと正ボンディングの両者が適用されている。

#### 【 0 0 4 8 】

すなわち、複数の第 2 ワイヤ 3 b は、複数の第 2 ワイヤ 3 b それぞれのボンディンググリード 7 c 上における第 2 ワイヤ 3 b と配線基板 7 の表面 7 a との成す角度が、複数の第 2 ワイヤ 3 b それぞれの第 2 半導体チップ 2 の第 2 パッド 2 c 上における第 2 ワイヤ 3 b と第 2 半導体チップ 2 の第 2 主面 2 a との成す角度より大きいワイヤ(第 2 逆ボンディングワイヤ)と、複数の第 2 ワイヤ 3 b それぞれのボンディンググリード 7 c 上における第 2 ワイヤ 3 b と配線基板 7 の表面 7 a との成す角度が、複数の第 2 ワイヤ 3 b それぞれの第 2 半導体チップ 2 の第 2 パッド 2 c 上における第 2 ワイヤ 3 b と第 2 半導体チップ 2 の第 2 主面 2 a との成す角度より小さいワイヤ(第 2 正ボンディングワイヤ) 3 とを含んでいる。40

#### 【 0 0 4 9 】

一方、配線基板 7 の表面 7 a に形成されたボンディンググリード(第 1 ボンディンググリード、第 2 ボンディンググリード)は、各辺(第 1 辺、第 2 辺)に沿って形成されているが、逆ボンディング方式により形成されたワイヤ(第 1 逆ボンディングワイヤ、第 2 逆ボンディングワイヤ)と接続されるボンディンググリードは配線基板 7 の第 1 辺に沿って形成され50

、正ポンディング方式により形成されたワイヤ（第1正ポンディングワイヤ、第2正ポンディングワイヤ）と接続されるボンディングリードは配線基板7の第2辺に沿って形成されている。

#### 【0050】

つまり、本実施の形態1のマルチチップモジュール8では、対向する1組の2辺に対応して逆ポンディングまたは正ポンディングが使い分けされている。例えば、図1に示すマルチチップモジュール8では、その上下方向（B-B断面の方向）の対向する2辺（第1辺）に、図3に示すように逆ポンディングが適用されており、一方、左右方向（A-A断面の方向）の対向する2辺（第2辺）に、図2に示すように正ポンディングが適用されている。

10

#### 【0051】

これは、上記したように、第2半導体チップ2の端部と第1半導体チップ1の端部との距離が第1半導体チップ1の端部と配線基板7のボンディングリード7cの端部との距離よりも大きい場合には、逆ポンディング方式を適用することが好ましいが、逆ポンディング方式により形成されたワイヤ（第1逆ポンディングワイヤ、第2逆ポンディングワイヤ）は、正ポンディング方式により形成されたワイヤ（第1正ポンディングワイヤ、第2正ポンディングワイヤ）よりも、強度が低い。そのため、後の封止体を形成する工程において、樹脂の充填圧力により、逆ポンディング方式により形成されたワイヤは流されやすい。

20

#### 【0052】

そこで、本実施の形態では、第2半導体チップ2の第2パッド2cと接続されるワイヤは、全て逆ポンディング方式により形成せずに、第2半導体チップ2の第4辺に沿って形成された第2パッド2cと配線基板7の第2辺に沿って形成されたボンディングリード（第2ボンディングリード）7cは、正ポンディング方式により形成されたワイヤを介して電気的に接続している。

30

#### 【0053】

これは、下段の半導体チップ（第1半導体チップ1）の平面形状が長方形であるために、第1半導体チップ1の長辺側の端部（第6辺）と配線基板7の第2辺に沿って形成されたボンディングリードの端部との距離（M2）が、第1半導体チップ1の短辺側の端部（第5辺）と配線基板7の第1辺に沿って形成されたボンディングリードの端部との距離（M1）よりも大きく、正ポンディング方式を適用したとしても、第1半導体チップ1とワイヤ（第2正ポンディングワイヤ）との接触が起き難いためである。

#### 【0054】

また、下段の第1半導体チップ1の第1パッド1cと配線基板7のボンディングリード7cとを接続する複数の第1ワイヤ3aでは、複数の第1ワイヤ3aそれぞれのボンディングリード7c上における第1ワイヤ3aと配線基板7の表面7aとの成す角度が、複数の第1ワイヤ3aそれぞれの第1半導体チップ1の第1パッド1c上における第1ワイヤ3aと第1半導体チップ1の第1主面1aとの成す角度より小さくなっている。

#### 【0055】

すなわち、本実施の形態では、複数の第1ワイヤ3aが全て正ポンディングによってワイヤボンディングされている。その際、正ポンディングが行われるため、第1半導体チップ1の端部とボンディングリード7cとの距離が長い方（M2）の配線基板7の辺側のみにおいて第1ワイヤ3aが形成されている。つまり、図1に示す構造の左右方向（A-A断面の方向）の対向する2辺側のみにおいて、図2に示すように第1ワイヤ3aにより正ポンディングが行われている。

40

#### 【0056】

これにより、本実施の形態1のマルチチップモジュール8に形成された複数の第1ワイヤ3aは、全て正ポンディングを採用した接続となっている。

#### 【0057】

また、マルチチップモジュール8では、図2及び図3に示すように第2半導体チップ2

50

の厚さは第1半導体チップ1の厚さより厚くなっている。すなわち、上段の第2半導体チップ2は、その厚さが下段の第1半導体チップ1よりも厚い。例えば、第2半導体チップ2の厚さが140μmであり、一方、第1半導体チップ1の厚さが90μmである。

#### 【0058】

このように上段に下段よりも厚い第2半導体チップ2を搭載することで、正ボンディングが行われている辺側のワイヤショート(第2ワイヤ3bと下段の第1半導体チップ1のワイヤショート)の発生を防止することができる。すなわち、正ボンディングが行われている辺側では、逆ボンディングが行われている辺側に比べて第2ワイヤ3bと下段の第1半導体チップ1との間に所定のクリアランスは確保されているが、マルチチップモジュール8の小型化やチップシーリングにより大きなクリアランスは確保困難となっているため、上段の第2半導体チップ2を厚くして高い位置から第2ワイヤ3bを打ち降ろすことで、第2ワイヤ3bと下段の第1半導体チップ1とのクリアランスを確保している。

10

#### 【0059】

なお、より高い位置から第2ワイヤ3bを打ち降ろすという意味では、上段の第2半導体チップ2のチップ厚は厚くせずに第2ワイヤ3bの立ち上がり部分を高くすることも考えられるが、第2ワイヤ3bの立ち上がり部分を高くすると、樹脂モールド時のワイヤ流れの影響を受け易くなるため、第2ワイヤ3bの立ち上がり部分を高くすることは好ましくない。したがって、本実施の形態1のマルチチップモジュール8では、上段の第2半導体チップ2の厚さを下段の第1半導体チップ1の厚さより厚くしている。

#### 【0060】

20

また、マルチチップモジュール8では、配線基板7の四角形の表面7aの各辺の周縁部に沿って配置された複数のボンディングリード7cは、一列で配置されている。これは、下段の第1半導体チップ1の端部と配線基板7の端部との距離が短いため、ボンディングリード7cを複数列で配置することはスペース的に困難であり、したがって、複数のボンディングリード7cが一列に並んで配置されている。

#### 【0061】

また、マルチチップモジュール8では、第1半導体チップ1及び第2半導体チップ2が接着剤6によってダイボンディングされている。すなわち、第1半導体チップ1及び第2半導体チップ2のダイボンド材として、接着剤6が用いられている。これは、特に、下段の第1半導体チップ1の端部とボンディングリード7cとが近くに配置されているため、ダイボンド材としてペースト材を用いた際の第1半導体チップ1からのはみ出しによるペースト材の流れ出しを無くすためであり、したがって、ダイボンド材として接着剤6を用いることで、ダイボンド材の流れ出しによるボンディングリード7cへの付着を防ぐことができる。

30

#### 【0062】

なお、このことは、上段の第2半導体チップ2からのダイボンド材の流れ出しによる第1半導体チップ1の第1パッド1cへのダイボンド材の付着についても同様の効果を得ることができる。

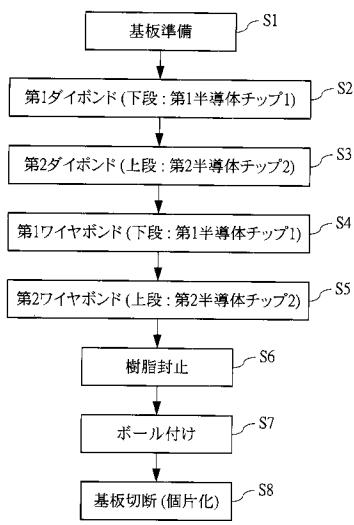

#### 【0063】

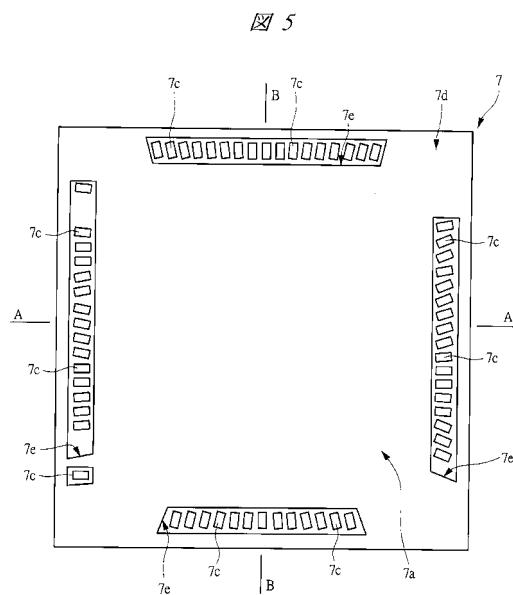

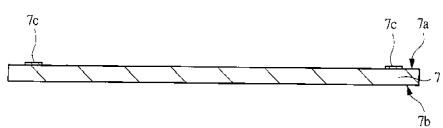

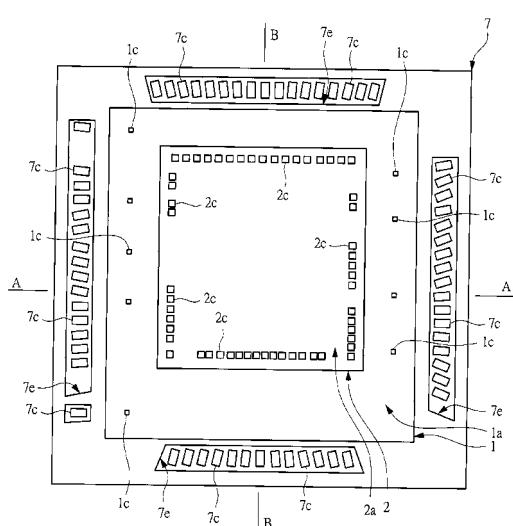

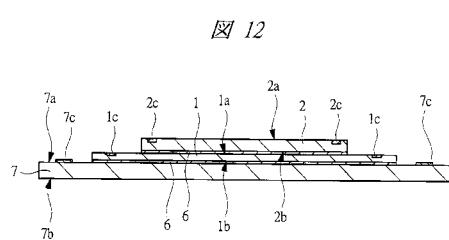

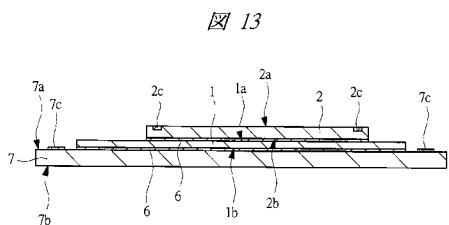

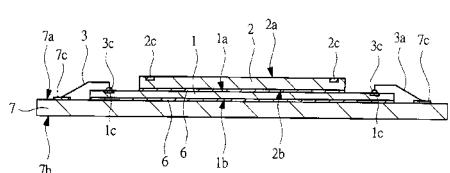

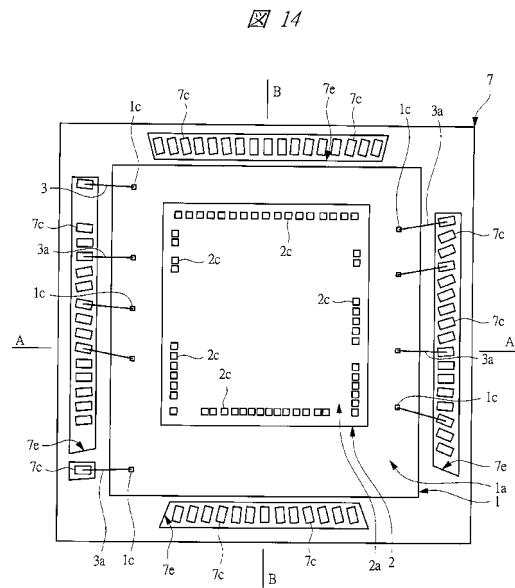

次に、本実施の形態1の半導体装置(マルチチップモジュール8)の組み立て手順を、図4に示すプロセスフロー図に沿って説明する。図4は図1の半導体装置の製造方法の一例を示すプロセスフロー図、図5は図1の半導体装置に組み込まれる配線基板の構造の一例を示す平面図、図6は図5のA-A線に沿って切断した構造の一例を示す断面図、図7は図5のB-B線に沿って切断した構造の一例を示す断面図である。また、図8は図4に示す製造方法の第1ダイボンドにおける下段チップのダイボンディング状態の一例を示す平面図、図9は図8のA-A線に沿って切断した構造の一例を示す断面図、図10は図8のB-B線に沿って切断した構造の一例を示す断面図である。また、図11は図4に示す製造方法の第2ダイボンドにおける上段チップのダイボンディング状態の一例を示す平面図、図12は図11のA-A線に沿って切断した構造の一例を示す断面図、図13は図11のB-B線に沿って切断した構造の一例を示す断面図である。また、図14は図4に示す

40

50

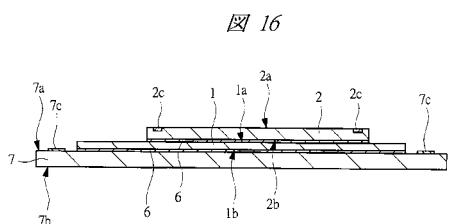

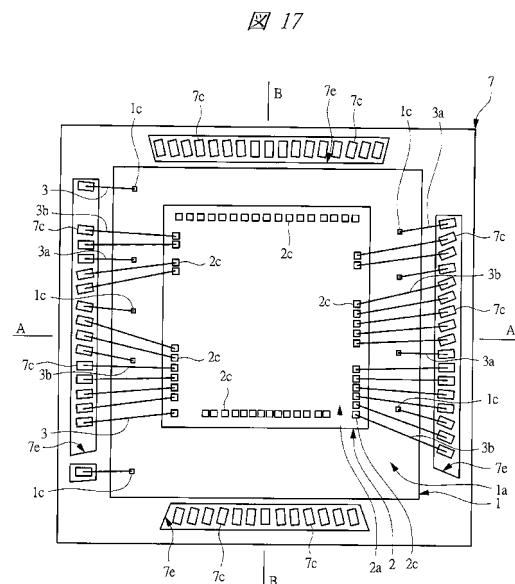

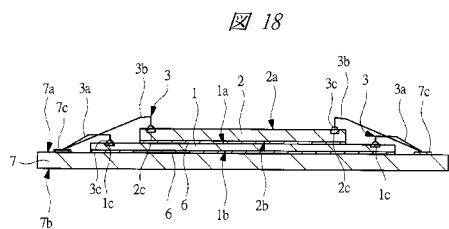

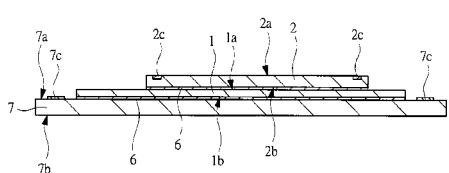

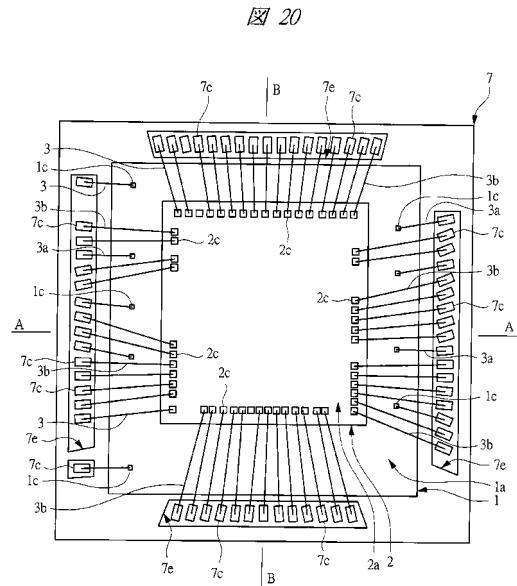

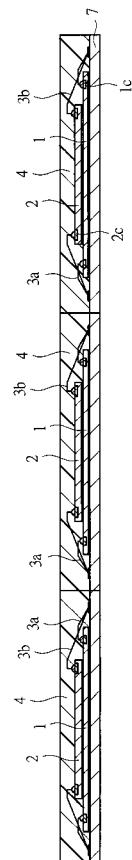

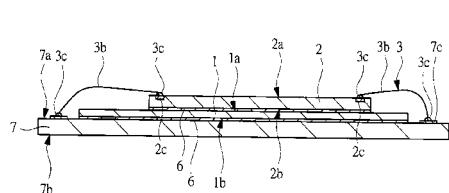

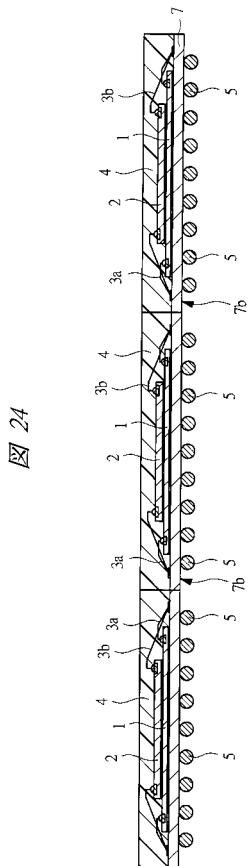

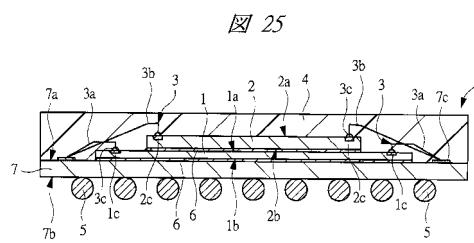

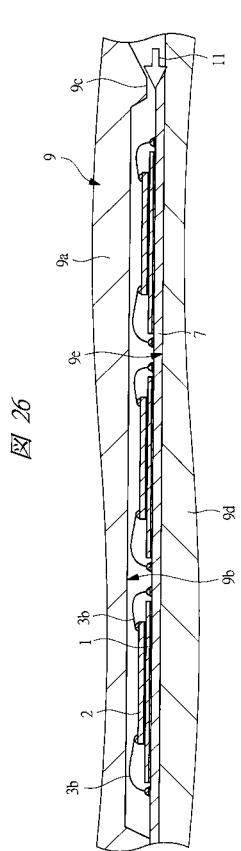

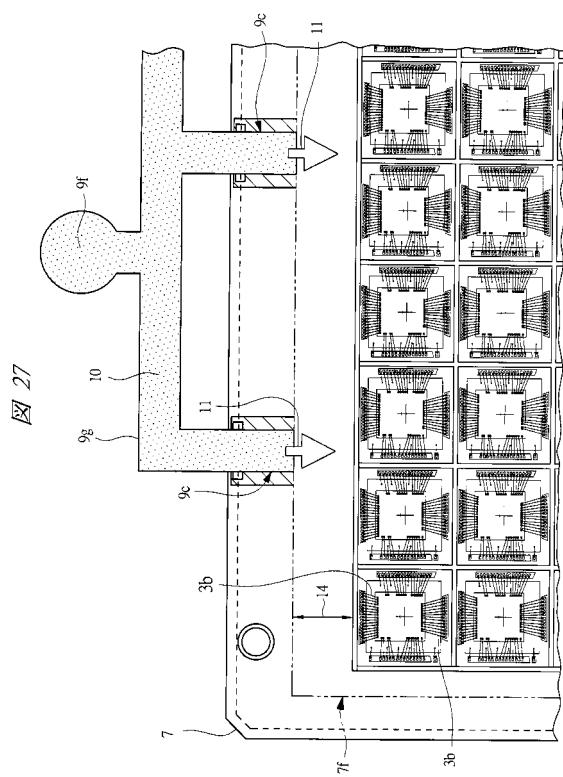

す製造方法の第1ワイヤボンドにおける下段チップのワイヤボンディング状態の一例を示す平面図、図15は図14のA-A線に沿って切断した構造の一例を示す断面図、図16は図14のB-B線に沿って切断した構造の一例を示す断面図である。また、図17は図4に示す製造方法の第2ワイヤボンドにおける上段チップの正ボンディングのワイヤボンディング状態の一例を示す平面図、図18は図17のA-A線に沿って切断した構造の一例を示す断面図、図19は図17のB-B線に沿って切断した構造の一例を示す断面図である。また、図20は図4に示す製造方法の第2ワイヤボンドにおける上段チップの逆ボンディングのワイヤボンディング状態の一例を示す平面図、図21は図20のA-A線に沿って切断した構造の一例を示す断面図、図22は図20のB-B線に沿って切断した構造の一例を示す断面図である。また、図23は図4に示す製造方法における樹脂封止後の構造の一例を示す断面図、図24は図4に示す製造方法におけるボール付け後の構造の一例を示す断面図、図25は図4に示す製造方法における基板切断後の構造の一例を示す断面図、図26は図4に示す製造方法の樹脂封止工程における樹脂充填方向の一例を示す部分断面図、図27は図26の樹脂充填方向の一例を示す部分平面図である。

10

#### 【0064】

まず、図示しない半導体ウェハにバックグラウンドを施して半導体ウェハを薄型化し、その後、ウェハ裏面にダイボンド材である接着剤6を貼り付ける。その後、半導体ウェハをダイシングして個々のチップを取得する。

#### 【0065】

その後、図4のステップS1に示す基板準備を行う。ここでは、図5、図6及び図7に示す配線基板7を準備する。すなわち、複数のボンディングリード7cが周縁部に形成された表面7a、及び表面7aと反対側の裏面7bを有する配線基板7を準備する。なお、複数のボンディングリード7cは、四角形の表面7aの周縁部に、各辺に沿って一列に並んで形成されており、したがって、各辺のボンディングリード7c列によって略四角形が形成されている。配線基板7の表面7aは、絶縁膜であるソルダレジスト膜7dによって覆われているが、各ボンディングリード7cは、ソルダレジスト膜7dの開口部7eに露出している。

20

#### 【0066】

その後、ステップS2に示す第1ダイボンドを行う。すなわち、図8、図9及び図10に示すように、下段の第1半導体チップ1のダイボンディングを行う。ここでは、複数の第1パッド1cが形成された第1主面1aを有する第1半導体チップ1を、配線基板7の略四角形に配置された複数のボンディングリード7cの内側に位置するように、配線基板7の表面7a上に搭載する。その際、図9に示すように第1半導体チップ1の裏面1bには予め接着剤6が貼り付けられており、配線基板7の表面7a上に第1半導体チップ1を配置した後、熱圧着によって第1半導体チップ1の裏面1bと配線基板7の表面7aとを接合する。なお、第1半導体チップ1の第1主面1aには、図1に示すように、その1組の対向する2辺の周縁部それぞれに、それぞれの辺に沿って複数の第1パッド1cが形成されている。

30

#### 【0067】

第1半導体チップ1の搭載により、図1中の配線基板7の上下方向(B-B断面の方向)の辺側における第1半導体チップ1の端部とボンディングリード7cとの距離(M1)は、図1中の配線基板7の左右方向(A-A断面の方向)の辺側における第1半導体チップ1の端部とボンディングリード7cとの距離(M2)より短くなっている(M1 < M2)。

40

#### 【0068】

その後、ステップS3に示す第2ダイボンドを行う。すなわち、図11、図12及び図13に示すように、上段の第2半導体チップ2のダイボンディングを行う。ここでは、複数の第2パッド2cが形成され、かつ第1半導体チップ1の第1主面1aの外形寸法よりも小さい第2主面2aを有する第2半導体チップ2を、第1半導体チップ1の第1主面1aの対向する1組の辺それぞれに沿って設けられた複数の第1パッド1cの内側(間)に

50

位置するように、第1半導体チップ1上に搭載する。このとき、第2半導体チップ2の正面（第2正面）2aにおける中心部を、第1半導体チップ1の正面（第1正面）1aにおける中心部からも第1半導体チップ1の一対の辺（第5辺）のうち、一方の辺側にずらして搭載している。これは、第2半導体チップ2の第2正面2aに形成（特に第4辺に沿って形成）された第2パッド2cの形成箇所が、配線基板7のボンディングリード（第2ボンディングリード）7cの形成箇所と一致していないためである。そのため、第2半導体チップ2の中心部をずらして積層しない場合、第1半導体チップ1の第6辺に沿って形成された第1パッド1cと配線基板7の第2辺に沿って形成された第1ボンディングリード7cとを電気的に接続するワイヤ（第1正ボンディングワイヤ）3と、第2半導体チップ2の第4辺に沿って形成された第2パッド2cと配線基板7の第2辺に沿って形成された第2ボンディングリード7cとを電気的に接続するワイヤ（第2正ボンディングワイヤ）3とが平面的に重なる部分が生じる。そして、後の封止体を形成する工程において、樹脂の充填圧力により流されたワイヤ同士が接触する恐れがある。そこで、本実施の形態では、第2半導体チップ2の正面（第2正面）2aにおける中心部を、第1半導体チップ1の正面（第1正面）1aにおける中心部から第1半導体チップ1の一対の辺（第5辺）のうち、一方の辺側にずらして搭載している。これにより、第2半導体チップ2と配線基板7と電気的に接続されるワイヤ3が、第1半導体チップ1と配線基板7とを電気的に接続するワイヤ3と、平面的に重ならなくなり、樹脂封止体を形成する工程において、ワイヤ同士が接触するのを抑制できる。また、図12に示すように第2半導体チップ2の裏面2bにも予め接着剤6が貼り付けられており、第1半導体チップ1の第1正面1a上に第2半導体チップ2を配置した後、熱圧着によって第2半導体チップ2の裏面2bと第1半導体チップ1の第1正面1aとを接合する。なお、第1半導体チップ1の第1正面1aには、対向する1組の2つの辺の周縁部それぞれに、それぞれの辺に沿って複数の第1パッド1cが形成されている。

10

#### 【0069】

第2半導体チップ2の搭載により、図1に示すように第2半導体チップ2の端部と第1半導体チップ1の端部との距離（L1, L2）が、第1半導体チップ1の端部と配線基板7のボンディングリード7cとの距離（M1, M2）よりもそれぞれ長くなっている（L1 > M1, L2 > M2）。

#### 【0070】

その後、ステップS4に示す第1ワイヤボンドを行う。すなわち、図14、図15及び図16に示すように、下段の第1半導体チップ1のワイヤボンディングを行う。ここでは、第1半導体チップ1の複数の第1パッド1cとこれらに対応する配線基板7の複数のボンディングリード7cとを、複数の第1ワイヤ3aを介してそれぞれ電気的に接続する。その際、まず、ワイヤ3の一端部を第1半導体チップ1の第1パッド1cに接続し、その後、ワイヤ3の他端部を配線基板7のボンディングリード7cに接続する正ボンディングを行う。つまり、本実施の形態1のマルチチップモジュール8では、下段の第1半導体チップ1については、対向する一方向（A-A断面の方向）の2辺のみに複数の第1パッド1cが設けられているため、この方向に対して、正ボンディングのみによってワイヤボンディングを行って第1パッド1cとボンディングリード7cとを接続する。

30

#### 【0071】

その後、ステップS5に示す第2ワイヤボンドを行う。すなわち、図17～図22に示すように、上段の第2半導体チップ2のワイヤボンディングを行う。ここでは、第2半導体チップ2の複数の第2パッド2cとこれらに対応する配線基板7の複数のボンディングリード7cとを、複数の第2ワイヤ3bを介してそれぞれ電気的に接続する。その際、第2半導体チップ2においては、第2パッド2cが第2正面2aの4辺に沿って周縁部に形成されており、各辺ごとに正ボンディングと逆ボンディングとを使い分けてボンディングする。

40

#### 【0072】

そこで、第2半導体チップ2においては、下段の第1半導体チップ1で正ボンディング

10

20

30

40

50

を行った対向する 2 辺と同じ側の対向する 2 辺に対しては、同様に正ボンディングを行い、これらの 2 辺と交差する方向の対向する 2 辺に対しては逆ボンディングを行う。

#### 【 0 0 7 3 】

したがって、図 17、図 18 及び図 19 に示すように、まず、第 1 半導体チップ 1 で正ボンディングを行った 2 辺と同じ側の 2 辺に対して正ボンディングを行い、その後、図 20、図 21 及び図 22 に示すように、これらの 2 辺と交差する方向の対向する 2 辺に対して逆ボンディングを行う。その際、正ボンディングでは、まず、ワイヤ 3 の一端部を第 2 半導体チップ 2 の第 2 パッド 2c に接続し、その後、ワイヤ 3 の他端部を配線基板 7 のボンディングリード 7c に接続する。一方、逆ボンディングでは、まず、ワイヤ 3 の一端部を配線基板 7 のボンディングリード 7c に接続し、その後、ワイヤ 3 の他端部を第 2 半導体チップ 2 の第 2 パッド 2c に接続する。10

#### 【 0 0 7 4 】

なお、図 22 に示すように、逆ボンディングでワイヤ 3 の他端部が接続される第 2 半導体チップ 2 の第 2 パッド 2c については、逆ボンディング前にその第 2 パッド 2c 上にスタッドバンプと呼ばれる金バンプ 3c を予め接続しておき、逆ボンディングの際にはワイヤ 3 の他端部をこの金バンプ 3c に接続する。

#### 【 0 0 7 5 】

その際、金バンプ 3c の接続については、ステップ S5 の第 2 ワイヤボンド工程の最初の段階で、逆ボンディングが行われる全ての第 2 パッド 2c に対して予めまとめて形成してもよいし、もしくは逆ボンディングが行われる個々の第 2 パッド 2c に対して、それぞれの第 2 パッド 2c に対する一連の逆ボンディング動作の中で形成してもよい。20

#### 【 0 0 7 6 】

第 2 ワイヤボンド終了後、ステップ S6 に示す樹脂封止を行う。すなわち、トランスファモールドによって図 23 に示す封止体 4 を形成し、配線基板 7 上の第 1 半導体チップ 1、第 2 半導体チップ 2、複数の第 1 ワイヤ 3a 及び複数の第 2 ワイヤ 3b をモールドレジン（樹脂）10 から成る封止体 4 で封止する。

#### 【 0 0 7 7 】

なお、図 36 に示す比較例の半導体装置 15 のように、上段側の半導体チップ 13 の外形寸法が下段側の半導体チップ 13 の外形寸法に比べ小さく、かつ下段側の半導体チップ 13 の端部と配線基板 7 のボンディングリード 7c との距離が近く、さらに上段側の半導体チップ 13 のパッド 13b とボンディングリード 7c の距離が長い場合、チップとのワイヤショートが発生し易い。30

#### 【 0 0 7 8 】

このワイヤショートの対策として、単に、全てのワイヤ 3 を逆ボンディングにすることが考えられる。

#### 【 0 0 7 9 】

しかしながら、図 29 に示すように、逆ボンディング方式により形成されるワイヤと半導体チップとの間隔（隙間）は、図 28 に示すように、正ボンディング方式により形成されるワイヤと半導体チップの端部との間隔（隙間）よりも大きくなる。これにより、逆ボンディング方式でワイヤを形成した場合、この隙間に流れ込む樹脂の量が多くなり、ワイヤ流れが正ボンディング方式で形成したワイヤよりも生じ易いことを本願発明者は見出した。40

#### 【 0 0 8 0 】

そこで、本実施の形態 1 のマルチチップモジュール 8 では、単に、全てのワイヤ 3 を逆ボンディングにするのではなく、図 1～図 3 に示すように逆ボンディングと正ボンディングの両者を採用するとともに、マルチチップモジュール 8 の組み立ての樹脂封止工程におけるモールド時のモールドレジン 10 を供給する方向（充填方向）を考慮している。

#### 【 0 0 8 1 】

すなわち、図 26 及び図 27 に示すように、図 4 のステップ S6 の樹脂封止工程において、複数の第 2 ワイヤ 3b のうち、一端部を配線基板 7 のボンディングリード 7c に接続50

した後、他端部を第2半導体チップ2の第2パッド2cに接続するワイヤボンディングが行われるボンディングリード7c列に対応した配線基板7の辺側からモールド金型9のキャビティ9b内にモールドレジン(樹脂)10を充填する。つまり、配線基板7の4つの辺のうち、逆ボンディングが行われるボンディングリード7c列に対応した配線基板7の辺(一対の第1辺のうちの一方の辺)側からキャビティ9b内にモールドレジン10を充填する。

#### 【0082】

したがって、モールド金型9において、逆ボンディングが行われるボンディングリード7c列に対応した配線基板7の辺側に複数のゲート9cが設けられた構造となっており、これにより、レジン充填時には、図26及び図27に示す充填方向11にモールドレジン10を注入することができる。すなわち、モールド金型9を、逆ボンディングが行われるボンディングリード7c列に対応した配線基板7の辺側に複数のゲート9cが設けられた構造とすることで、複数の第2ワイヤ3bのうち、図27に示す逆ボンディングが行われた第2ワイヤ3bのワイヤリング方向14(図1に示すB-B断面と同方向)に沿ってモールドレジン10を図26のキャビティ9b内に注入することができる。

#### 【0083】

なお、モールド金型9は、封止体4を形成する凹部であるキャビティ9bを有した上型9aと、配線基板7を配置する金型面9eを有した下型9dと、モールドレジン10のキャビティ9bへの注入口を備えたゲート9cと、ゲート9cに連通してモールドレジン10を案内する流路であるランナ9gと、モールドレジン10をランナ9gに送り出すポート9fとを有している。

#### 【0084】

図26及び図27では、多数個取り用の配線基板7に対して樹脂モールドを行う場合を示している。つまり、図26に示すキャビティ9b内に配線基板7を配置した状態で、図27に示す配線基板7のモールドエリア7fに対して、逆ボンディングが行われたボンディングリード7c列に対応した配線基板7の辺側に設けられた複数のゲート9cから、逆ボンディングが行われた第2ワイヤ3bのワイヤリング方向14に沿うような充填方向11となるようにモールドレジン10を注入している。

#### 【0085】

このように逆ボンディングが行われるボンディングリード7c列に対応した配線基板7の辺側からモールドレジン10を充填することで、第2ワイヤ3bと下段の第1半導体チップ1のワイヤショートを低減することができるとともに、樹脂モールド時の逆ボンディングが行われた第2ワイヤ3bへのレジン抵抗を減らすことができるため、逆ボンディングが行われた第2ワイヤ3bのワイヤ流れを低減することができる。

#### 【0086】

レジン充填完了後、モールドレジン10を硬化させることで、図23に示す一括した封止体4を形成することができる。

#### 【0087】

次に、樹脂封止工程後、図4のステップS7に示すボール付けを行う。すなわち、図24に示すように、配線基板7の裏面7bに複数の外部端子である半田ボール5を形成する。

#### 【0088】

その後、ステップS8に示す基板切断(個片化)を行う。すなわち、図25に示すように、配線基板7と封止体4を切断して個片化を行い、マルチチップモジュール8の組み立て完了となる。

#### 【0089】

本実施の形態1のマルチチップモジュール8の組み立てにおいても、第2半導体チップ2(上段)の端部と第1半導体チップ1(下段)の端部との距離が第1半導体チップ1の端部と配線基板7のボンディングリード7cとの距離よりも長い場合に、第2半導体チップ2と接続する複数の第2ワイヤ3bを逆ボンディング方式とすることで、第1半導体チ

10

20

30

40

50

ツプ 1 の外側の狭い領域において第 2 ワイヤ 3 b を急峻に立ち上がらせることができる。

**【 0 0 9 0 】**

これにより、下段側の第 1 半導体チップ 1 の端部と第 2 ワイヤ 3 b との間にクリアランスを大きく設けることができ、下段側の第 1 半導体チップ 1 とワイヤ 3 のショートを防止することができる。

**【 0 0 9 1 】**

( 実施の形態 2 )

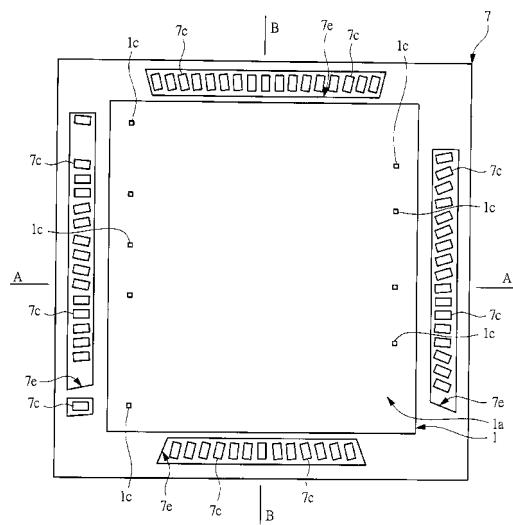

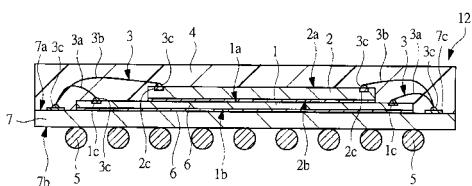

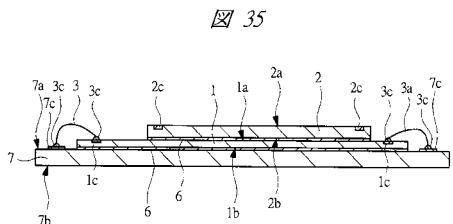

図 3 0 は本発明の実施の形態 2 の半導体装置の構造の一例を封止体を透過して示す平面図、図 3 1 は図 3 0 の A - A 線に沿って切断した構造の一例を示す断面図、図 3 2 は図 3 0 の B - B 線に沿って切断した構造の一例を示す断面図である。また、図 3 3 は図 3 0 に示す半導体装置の製造方法の第 1 ワイヤボンドにおける下段チップのワイヤボンディング状態の一例を示す平面図、図 3 4 は図 3 3 の A - A 線に沿って切断した構造の一例を示す断面図、図 3 5 は図 3 3 の B - B 線に沿って切断した構造の一例を示す断面図である。

10

**【 0 0 9 2 】**

本実施の形態 2 の半導体装置は、実施の形態 1 のマルチチップモジュール 8 と同様に、第 1 半導体チップ 1 と、主面 2 a が第 1 半導体チップ 1 より小さな第 2 半導体チップ 2 とが積層されたマルチチップモジュール 1 2 であり、正ボンディングと逆ボンディングの両者が採用されたものである。

**【 0 0 9 3 】**

図 1 に示す実施の形態 1 のマルチチップモジュール 8 では、第 1 半導体チップ 1 と接続される複数の第 1 ワイヤ 3 a が 1 つの方向 ( A - A 断面の方向 ) のみに沿って形成されているのに対して、本実施の形態 2 のマルチチップモジュール 1 2 では、第 1 半導体チップ 1 と接続される複数の第 1 ワイヤ 3 a が交差する 2 つの方向 ( A - A 断面の方向と B - B 断面の方向 ) に沿って形成されている。

20

**【 0 0 9 4 】**

すなわち、下段の第 1 半導体チップ 1 においてその主面 1 a に形成された複数の電極である第 1 パッド 1 c が、主面 1 a の 4 辺のそれぞれの各周縁部に沿って設けられており、これらの第 1 パッド 1 c と、第 1 半導体チップ 1 の 4 辺それぞれに対応して設けられた配線基板 7 の複数のボンディングリード 7 c とが第 1 ワイヤ 3 a によって電気的に接続されている。つまり、下段の第 1 半導体チップ 1 と配線基板 7 のボンディングリード 7 c とを接続する複数の第 1 ワイヤ 3 a が、第 1 半導体チップ 1 の 4 辺それぞれに複数本形成されている。

30

**【 0 0 9 5 】**

その際、マルチチップモジュール 1 2 では、第 1 半導体チップ 1 の 4 辺それぞれに形成された第 1 ワイヤ 3 a のうち、図 3 0 の B - B 断面の方向に沿って形成された複数の第 1 ワイヤ 3 a が、図 3 2 に示すように逆ボンディングによって形成され、一方、図 3 0 の A - A 断面の方向に沿って形成された複数の第 1 ワイヤ 3 a が、図 3 1 に示すように正ボンディングによって形成されており、逆ボンディングと正ボンディングが各辺に対応して混在している。

**【 0 0 9 6 】**

言い換えると、複数の第 1 ワイヤ 3 a は、複数の第 1 ワイヤ 3 a それぞれのボンディングリード 7 c 上における第 1 ワイヤ 3 a と配線基板 7 の表面 7 a との成す角度 ( 2 ) が、複数の第 1 ワイヤ 3 a それぞれの第 1 半導体チップ 1 の第 1 パッド 1 c 上における第 1 ワイヤ 3 a と第 1 半導体チップ 1 の第 1 主面 1 a との成す角度 ( 1 ) より小さいワイヤ 3 ( 図 2 8 に示す正ボンディング ) を含んでいる。加えて、複数の第 1 ワイヤ 3 a それぞれのボンディングリード 7 c 上における第 1 ワイヤ 3 a と配線基板 7 の表面 7 a との成す角度 ( 4 ) が、複数の第 1 ワイヤ 3 a それぞれの第 1 半導体チップ 1 の第 1 パッド 1 c 上における第 1 ワイヤ 3 a と第 1 半導体チップ 1 の第 1 主面 1 a との成す角度 ( 3 ) より大きいワイヤ 3 ( 図 2 9 に示す逆ボンディング ) とを含んでおり、正ボンディングと逆ボンディングの両者を含んでいる。

40

50

**【 0 0 9 7 】**

なお、上段の第2半導体チップ2と接続する複数の第2ワイヤ3bは、実施の形態1のマルチチップモジュール8と同様である。すなわち、第2ワイヤ3bについては、図30の上下方向（B-B断面の方向）の第2半導体チップ2の対向する2辺には、図32に示すように逆ボンディングが適用されており、一方、図30の左右方向（A-A断面の方向）の第2半導体チップ2の対向する2辺には、図31に示すように正ボンディングが適用されている。

**【 0 0 9 8 】**

したがって、本実施の形態2のマルチチップモジュール12においては、第1半導体チップ1及び第2半導体チップ2の両者とも、図30の上下方向（B-B断面の方向）の対向する2辺には、図32に示すように逆ボンディングが適用されており、一方、図30の左右方向（A-A断面の方向）の対向する2辺には、図31に示すように正ボンディングが適用されている。10

**【 0 0 9 9 】**

このようにマルチチップモジュール12では、4辺それぞれにおいて上段側の第2ワイヤ3bと下段側の第1ワイヤ3aとが形成されている。

**【 0 1 0 0 】**

ところが、マルチチップモジュール12においては、マルチチップモジュール8と同様に、配線基板7の四角形の表面7aの各辺の周縁部に沿って配置された複数のボンディングリード7cは、一列で配置されている。これは、下段の第1半導体チップ1の端部と配線基板7の端部との距離が短いため、ボンディングリード7cを複数列で配置することはスペース的に困難であり、その結果、複数のボンディングリード7cを一列に配置せざるを得ない状況となっているためである。20

**【 0 1 0 1 】**

したがって、マルチチップモジュール12では、上段側の複数の第2ワイヤ3bのそれと下段側の複数の第1ワイヤ3aのそれとを平面的に重ならないように形成する必要がある。

**【 0 1 0 2 】**

そこで本実施の形態2のマルチチップモジュール12には、上段側の複数の第2ワイヤ3bと下段側の複数の第1ワイヤ3aとが重ならないような手段が施されている。まず、図30に示すように、上段側の第2半導体チップ2の複数の第2パッド2cが、異なる複数種類のピッチで配置されている。30

**【 0 1 0 3 】**

すなわち、第2半導体チップ2の複数の第2パッド2cのピッチが、例えば、第1ピッチ（P1）と第1ピッチよりは広い第2ピッチ（P2）等のように複数種類設定されており、広い第2ピッチ（P2）の間に第1ワイヤ3aを配置しており、これによって、上段側の複数の第2ワイヤ3bと下段側の複数の第1ワイヤ3aとを平面的に重ならないようにすることができます。

**【 0 1 0 4 】**

さらに、図30に示すように上段側の第2半導体チップ2は、この第2半導体チップ2の中心2dが第1半導体チップ1の中心1dとは異なった位置に偏心するように配置されている。すなわち、下段の第1半導体チップ1の中心1dと上段の第2半導体チップ2の中心2dとがずれて（偏心して）配置されており、これにより、上段側の複数の第2ワイヤ3bと下段側の複数の第1ワイヤ3aとを平面的に重ならないようにすることができます。40

**【 0 1 0 5 】**

なお、上段側の複数の第2ワイヤ3bと下段側の複数の第1ワイヤ3aとが重ならないような手段（第2パッド2cのピッチを変える、あるいは第2半導体チップ2を偏心させて搭載する）については、実施の形態1のマルチチップモジュール8に適用しても良いことは言うまでもない。50

**【0106】**

本実施の形態2のマルチチップモジュール12のその他の構造と他の効果については、実施の形態1のマルチチップモジュール8のものと同様であるため、その重複説明は省略する。

**【0107】**

次に、本実施の形態2のマルチチップモジュール12の組み立てについて説明する。マルチチップモジュール12の組み立ては、実施の形態1のマルチチップモジュール8の組み立てと略同じであるが、実施の形態1と異なる点は、図4に示すプロセスフローのステップS4の第1ワイヤボンド工程において、第1ワイヤ3aの正ボンディングと逆ボンディングを行うことである。

10

**【0108】**

すなわち、ステップS4の第1ワイヤボンド工程において、まず、下段の第1半導体チップ1に対して図34に示すように正ボンディングを行い、正ボンディング終了後、図35に示すように逆ボンディングを行う。これにより、図33に示すように下段の第1半導体チップ1に対するワイヤボンディングが完了となる。その後、ステップS5の第2ワイヤボンド工程を、同様に、正ボンディング、逆ボンディングの順番で行う。

**【0109】**

ただし、本実施の形態2のマルチチップモジュール12のように、辺ごとに正ボンディングと逆ボンディングが明確に分類されている場合には、先に上下段の正ボンディングを全て行い、その後、上下段の逆ボンディングを行うようにしてもよい。

20

**【0110】**

本実施の形態2のマルチチップモジュール12の組み立てのその他の工程については、実施の形態1のマルチチップモジュール8のものと同様であるため、その重複説明は省略する。

**【0111】**

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

**【0112】**

例えば、前記実施の形態では、半導体装置として、RF-ICとSecure ICを有したマルチチップモジュール8, 12の場合を一例として取り上げて説明したが、前記半導体装置は、マイコンチップとメモリチップを搭載したSIP(System In Package)等であってもよい。

30

**【0113】**

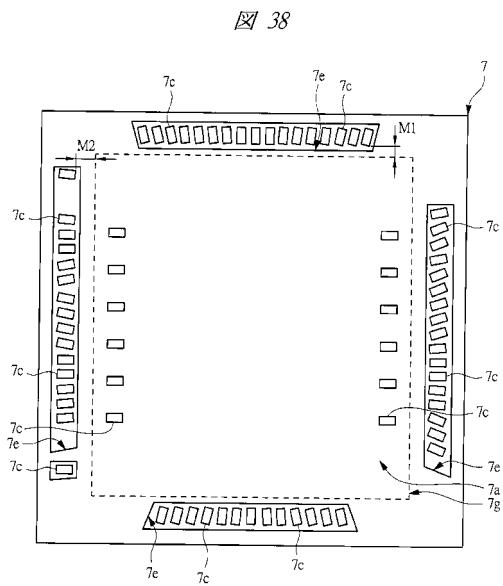

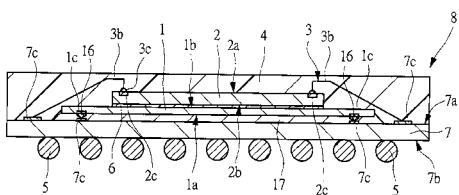

また、前記実施の形態では、第1半導体チップ1の第1裏面1bが配線基板7の表面7aと対向するように、第1半導体チップ1を配線基板7上に搭載し、接続手段であるワイヤを介して、第1半導体チップ1と配線基板7とを電気的に接続することについて説明したが、これに限定されるものではない。例えば、図37に示すように、第1半導体チップ1の第1パッド1c上に突起電極(金パンプ)16を形成しておき、第1半導体チップ1の第1正面1aが配線基板7の表面7aと対向するように、この突起電極16を介して第1半導体チップ1を配線基板7上に搭載してもよい。第1半導体チップ1と配線基板7の間にはアンダーフィル樹脂17が充填されている。この場合、配線基板7の表面7aには、図38に示すように、第1半導体チップ1が搭載されるチップ搭載領域7g内に、第1パッド1cと同じピッチでボンディングリード7cが形成されているものを使用する。これにより、ワイヤを介して第1半導体チップ1と配線基板7を電気的に接続する構造に比べ、半導体装置の高速化が可能である。

40

**【産業上の利用可能性】****【0114】**

本発明は、複数の半導体チップを有する電子装置に好適である。

**【図面の簡単な説明】**

50

## 【0115】

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図2】図1のA-A線に沿って切断した構造の一例を示す断面図である。

【図3】図1のB-B線に沿って切断した構造の一例を示す断面図である。

【図4】図1の半導体装置の製造方法の一例を示すプロセスフロー図である。

【図5】図1の半導体装置に組み込まれる配線基板の構造の一例を示す平面図である。

【図6】図5のA-A線に沿って切断した構造の一例を示す断面図である。

【図7】図5のB-B線に沿って切断した構造の一例を示す断面図である。

【図8】図4に示す製造方法の第1ダイボンドにおける下段チップのダイボンディング状態の一例を示す平面図である。 10

【図9】図8のA-A線に沿って切断した構造の一例を示す断面図である。

【図10】図8のB-B線に沿って切断した構造の一例を示す断面図である。

【図11】図4に示す製造方法の第2ダイボンドにおける上段チップのダイボンディング状態の一例を示す平面図である。 20

【図12】図11のA-A線に沿って切断した構造の一例を示す断面図である。

【図13】図11のB-B線に沿って切断した構造の一例を示す断面図である。

【図14】図4に示す製造方法の第1ワイヤボンドにおける下段チップのワイヤボンディング状態の一例を示す平面図である。 25

【図15】図14のA-A線に沿って切断した構造の一例を示す断面図である。

【図16】図14のB-B線に沿って切断した構造の一例を示す断面図である。

【図17】図4に示す製造方法の第2ワイヤボンドにおける上段チップの正ボンディングのワイヤボンディング状態の一例を示す平面図である。 30

【図18】図17のA-A線に沿って切断した構造の一例を示す断面図である。

【図19】図17のB-B線に沿って切断した構造の一例を示す断面図である。

【図20】図4に示す製造方法の第2ワイヤボンドにおける上段チップの逆ボンディングのワイヤボンディング状態の一例を示す平面図である。 35

【図21】図20のA-A線に沿って切断した構造の一例を示す断面図である。

【図22】図20のB-B線に沿って切断した構造の一例を示す断面図である。

【図23】図4に示す製造方法における樹脂封止後の構造の一例を示す断面図である。 40

【図24】図4に示す製造方法におけるボール付け後の構造の一例を示す断面図である。

【図25】図4に示す製造方法における基板切断後の構造の一例を示す断面図である。

【図26】図4に示す製造方法の樹脂封止工程における樹脂充填方向の一例を示す部分断面図である。 45

【図27】図26の樹脂充填方向の一例を示す部分平面図である。

【図28】本発明の実施の形態の半導体装置の製造方法における正ボンディングの一例を示す部分断面図である。

【図29】本発明の実施の形態の半導体装置の製造方法における逆ボンディングの一例を示す部分断面図である。 50

【図30】本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図31】図30のA-A線に沿って切断した構造の一例を示す断面図である。

【図32】図30のB-B線に沿って切断した構造の一例を示す断面図である。

【図33】図30に示す半導体装置の製造方法の第1ワイヤボンドにおける下段チップのワイヤボンディング状態の一例を示す平面図である。 55

【図34】図33のA-A線に沿って切断した構造の一例を示す断面図である。

【図35】図33のB-B線に沿って切断した構造の一例を示す断面図である。

【図36】比較例の半導体装置の構造を示す断面図である。

【図37】本発明の変形例の半導体装置の断面図である。

【図38】本発明の変形例の半導体装置における配線基板の平面図である。 60

## 【符号の説明】

## 【0116】

- |      |                    |    |

|------|--------------------|----|

| 1    | 第1半導体チップ           |    |

| 1 a  | 第1正面               |    |

| 1 b  | 裏面                 |    |

| 1 c  | 第1パッド(第1電極パッド)     |    |

| 1 d  | 中心                 |    |

| 2    | 第2半導体チップ           | 10 |

| 2 a  | 第2正面               |    |

| 2 b  | 裏面                 |    |

| 2 c  | 第2パッド(第2電極パッド)     |    |

| 2 d  | 中心                 |    |

| 3    | ワイヤ                |    |

| 3 a  | 第1ワイヤ              |    |

| 3 b  | 第2ワイヤ              |    |

| 3 c  | 金パンプ               |    |

| 3 d  | 折り曲げ点              |    |

| 4    | 封止体                |    |

| 5    | 半田ボール(外部端子)        | 20 |

| 6    | 接着剤                |    |

| 7    | 配線基板(基板)           |    |

| 7 a  | 表面(正面)             |    |

| 7 b  | 裏面                 |    |

| 7 c  | ボンディングリード          |    |

| 7 d  | ソルダレジスト膜           |    |

| 7 e  | 開口部                |    |

| 7 f  | モールドエリア            |    |

| 7 g  | チップ搭載領域            |    |

| 8    | マルチチップモジュール(半導体装置) |    |

| 9    | モールド金型             | 30 |

| 9 a  | 上型                 |    |

| 9 b  | キャビティ              |    |

| 9 c  | ゲート                |    |

| 9 d  | 下型                 |    |

| 9 e  | 金型面                |    |

| 9 f  | ポット                |    |

| 9 g  | ランナ                |    |

| 10   | モールドレジン(樹脂)        |    |

| 11   | 充填方向               |    |

| 12   | マルチチップモジュール(半導体装置) | 40 |

| 13   | 半導体チップ             |    |

| 13 a | 正面                 |    |

| 13 b | パッド                |    |

| 14   | ワイヤリング方向           |    |

| 15   | 半導体装置              |    |

| 16   | 突起電極               |    |

| 17   | アンダーフィル樹脂          |    |

【図1】

【図2】

【図3】

1: 第1半導体チップ

1a: 第1正面

2: 第2半導体チップ

2a: 第2正面

2c: 第2パッド(第2電極パッド)

3: 第2ワイヤ

3a: 第2ワイヤ

4: 封止体

5: 半田ボール(外部端子)

7: 配線基板(基板)

7a: 表面(正面)

7b: 裏面

7c: ボンディンググリード

8: マルチチップモジュール

(半導体装置)

【図4】

図4

【図5】

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【 図 1 2 】

【図13】

【図15】

【図16】

【図14】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【図25】

【図26】

【図27】

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

【図33】

図33

【図34】

【図36】

【図35】

【図38】

図37

---

フロントページの続き

(56)参考文献 特開2008-78367(JP,A)

特開2008-159786(JP,A)

特開2000-307057(JP,A)

特開2007-184385(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18