(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5802005号

(P5802005)

(45) 発行日 平成27年10月28日(2015.10.28)

(24) 登録日 平成27年9月4日(2015.9.4)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 21/8242 | (2006.01) | HO1L | 27/10 | 321  |

| HO1L 27/108  | (2006.01) | HO1L | 29/78 | 371  |

| HO1L 21/336  | (2006.01) | HO1L | 27/10 | 481  |

| HO1L 29/788  | (2006.01) | HO1L | 27/10 | 434  |

| HO1L 29/792  | (2006.01) | HO1L | 27/08 | 102E |

請求項の数 8 (全 63 頁) 最終頁に続く

(21) 出願番号 特願2010-236650 (P2010-236650)

(22) 出願日 平成22年10月21日 (2010.10.21)

(65) 公開番号 特開2011-171702 (P2011-171702A)

(43) 公開日 平成23年9月1日 (2011.9.1)

審査請求日 平成25年10月18日 (2013.10.18)

(31) 優先権主張番号 特願2009-249330 (P2009-249330)

(32) 優先日 平成21年10月29日 (2009.10.29)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2010-12619 (P2010-12619)

(32) 優先日 平成22年1月22日 (2010.1.22)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 小山 満

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第8の配線と、

第1のトランジスタと、

第2のトランジスタと、

容量素子と、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

10

20

続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を有し、

前記第2のトランジスタは、第2のチャネル形成領域を有し、

前記第1のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のトランジスタの単位チャネル幅あたりのオフ電流は、温度が25、ソースとドレイン間の電圧が3.1Vである環境下において、10zA/μm以下であることを特徴とする半導体装置。

### 【請求項2】

第1乃至第8の配線と、

第1のトランジスタと、

第2のトランジスタと、

容量素子と、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を含む第1の半導体層を有し、

前記第2のトランジスタは、第2のチャネル形成領域を含む第2の半導体層を有し、

前記第1のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のチャネル形成領域は、c軸が前記第2の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

10

20

30

40

50

前記第2のトランジスタの単位チャネル幅あたりのオフ電流は、温度が25、ソースとドレイン間の電圧が3.1Vである環境下において、10zA/μm以下であることを特徴とする半導体装置。

【請求項3】

第1乃至第8の配線と、

第1のトランジスタと、

第2のトランジスタと、

容量素子と、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を有し、

前記第2のトランジスタは、第2のチャネル形成領域を有し、

前記第1のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のトランジスタの単位チャネル幅あたりのオフ電流は、温度が85、ソースとドレイン間の電圧が3.1Vである環境下において、100zA/μm以下であることを特徴とする半導体装置。

【請求項4】

第1乃至第8の配線と、

第1のトランジスタと、

第2のトランジスタと、

容量素子と、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

40

50

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

10

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を含む第1の半導体層を有し、

前記第2のトランジスタは、第2のチャネル形成領域を含む第2の半導体層を有し、

前記第1のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

20

前記第2のチャネル形成領域は、c軸が前記第2の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

前記第2のトランジスタの単位チャネル幅あたりのオフ電流は、温度が85、ソースとドレイン間の電圧が3.1Vである環境下において、100zA/μm以下であることを特徴とする半導体装置。

#### 【請求項5】

第1乃至第10の配線と、

第1のトランジスタ、第2のトランジスタ、及び第1の容量素子を有する第1のメモリセルと、

第4のトランジスタ、第5のトランジスタ、及び第2の容量素子を有する第2のメモリセルと、

30

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記第1の容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

40

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第5のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第2の容量素子の一方の電極は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第5のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

50

前記第5のトランジスタのゲートは、前記第9の配線と電気的に接続されており、

前記第2の容量素子の他方の電極は、前記第10の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

10

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を有し、

前記第2のトランジスタは、第2のチャネル形成領域を有し、

前記第4のトランジスタは、第4のチャネル形成領域を有し、

前記第5のトランジスタは、第5のチャネル形成領域を有し、

前記第1のチャネル形成領域及び前記第4のチャネル形成領域は、シリコンを有し、

20

前記第2のチャネル形成領域及び前記第5のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のトランジスタ及び前記第5のトランジスタの各々において、単位チャネル幅あたりのオフ電流は、温度が25、ソースとドレイン間の電圧が3.1Vである環境下において、10zA/μm以下であることを特徴とする半導体装置。

#### 【請求項6】

第1乃至第10の配線と、

第1のトランジスタ、第2のトランジスタ、及び第1の容量素子を有する第1のメモリセルと、

第4のトランジスタ、第5のトランジスタ、及び第2の容量素子を有する第2のメモリセルと、

30

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記第1の容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

40

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第5のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第2の容量素子の一方の電極は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第5のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

50

前記第5のトランジスタのゲートは、前記第9の配線と電気的に接続されており、

前記第2の容量素子の他方の電極は、前記第10の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

10

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を含む第1の半導体層を有し、

前記第2のトランジスタは、第2のチャネル形成領域を含む第2の半導体層を有し、

前記第4のトランジスタは、第4のチャネル形成領域を含む第3の半導体層を有し、

前記第5のトランジスタは、第5のチャネル形成領域を含む第5の半導体層を有し、

前記第1のチャネル形成領域及び前記第4のチャネル形成領域は、シリコンを有し、

20

前記第2のチャネル形成領域及び前記第5のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のチャネル形成領域は、c軸が前記第2の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

前記第5のチャネル形成領域は、c軸が前記第5の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

前記第2のトランジスタ及び前記第5のトランジスタの各々において、単位チャネル幅あたりのオフ電流は、温度が25、ソースとドレイン間の電圧が3.1Vである環境下において、10zA/μm以下であることを特徴とする半導体装置。

【請求項7】

30

第1乃至第10の配線と、

第1のトランジスタ、第2のトランジスタ、及び第1の容量素子を有する第1のメモリセルと、

第4のトランジスタ、第5のトランジスタ、及び第2の容量素子を有する第2のメモリセルと、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

40

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記第1の容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第5のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続されており、

50

前記第2の容量素子の一方の電極は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第5のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第5のトランジスタのゲートは、前記第9の配線と電気的に接続されており、

前記第2の容量素子の他方の電極は、前記第10の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第6の配線と電気的に接続されており、

前記第3のトランジスタのゲートは、前記第7の配線と電気的に接続されており、

前記センスアンプの第2の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を有し、

前記第2のトランジスタは、第2のチャネル形成領域を有し、

前記第4のトランジスタは、第4のチャネル形成領域を有し、

前記第5のトランジスタは、第5のチャネル形成領域を有し、

前記第1のチャネル形成領域及び前記第4のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域及び前記第5のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のトランジスタ及び前記第5のトランジスタの各々において、単位チャネル幅あたりのオフ電流は、温度が85°C、ソースとドレイン間の電圧が3.1Vである環境下において、100zA/μm以下であることを特徴とする半導体装置。

#### 【請求項8】

第1乃至第10の配線と、

第1のトランジスタ、第2のトランジスタ、及び第1の容量素子を有する第1のメモリセルと、

第4のトランジスタ、第5のトランジスタ、及び第2の容量素子を有する第2のメモリセルと、

第3のトランジスタ及びセンスアンプを有する回路と、を有し、

前記第2のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第1の容量素子の一方の電極は、前記第1のトランジスタのゲートと電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の配線と電気的に接続されており、

前記第1の容量素子の他方の電極は、前記第5の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第5のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続されており、

10

20

30

40

50

前記第2の容量素子の一方の電極は、前記第4のトランジスタのゲートと電気的に接続されており、

前記第5のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続されており、

前記第5のトランジスタのゲートは、前記第9の配線と電気的に接続されており、

前記第2の容量素子の他方の電極は、前記第10の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続されており、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続されており、

前記センスアンプの第1の入力端子は、前記第2の配線と電気的に接続されており、

前記センスアンプの第3の入力端子は、前記第8の配線と電気的に接続されており、

前記第7の配線は、バイアス電位を供給することができる機能を有し、

前記第8の配線は、参照電位を供給することができる機能を有し、

前記第1のトランジスタは、第1のチャネル形成領域を含む第1の半導体層を有し、

前記第2のトランジスタは、第2のチャネル形成領域を含む第2の半導体層を有し、

前記第4のトランジスタは、第4のチャネル形成領域を含む第3の半導体層を有し、

前記第5のトランジスタは、第5のチャネル形成領域を含む第5の半導体層を有し、

前記第1のチャネル形成領域及び前記第4のチャネル形成領域は、シリコンを有し、

前記第2のチャネル形成領域及び前記第5のチャネル形成領域は、高純度化され、真性化または実質的に真性化されたIn-Ga-Zn-O系の酸化物半導体を有し、

前記第2のチャネル形成領域は、c軸が前記第2の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

前記第5のチャネル形成領域は、c軸が前記第5の半導体層の表面に垂直な方向になるように配向した結晶領域を有し、

前記第2のトランジスタ及び前記第5のトランジスタの各々において、単位チャネル幅あたりのオフ電流は、温度が85、ソースとドレイン間の電圧が3.1Vである環境下において、100zA/μm以下であることを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

開示する発明は、半導体素子を利用した半導体装置およびその作製方法に関するものである。

##### 【背景技術】

##### 【0002】

半導体素子を利用した記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性記憶装置と、電力の供給がなくなっても記憶内容は保持される不揮発性記憶装置とに大別される。

##### 【0003】

揮発性記憶装置の代表的な例としては、DRAM(Dynamic Random Access Memory)がある。DRAMは、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶する。

##### 【0004】

上述の原理から、DRAMでは、情報を読み出すとキャパシタの電荷は失われることになるため、データの読み込みの度に、再度の書き込み動作が必要となる。また、記憶素子を

構成するトランジスタにはリーク電流が存在し、トランジスタが選択されていない状況でも電荷が流出、または流入するため、データの保持期間が短い。このため、所定の周期で再度の書き込み動作（リフレッシュ動作）が必要であり、消費電力を十分に低減することは困難である。また、電力の供給がなくなると記憶内容が失われるため、長期間の記憶の保持には、磁性材料や光学材料を利用した別の記憶装置が必要となる。

#### 【0005】

揮発性記憶装置の別の例としては S R A M ( S t a t i c R a n d o m A c c e s s M e m o r y ) がある。S R A M は、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においては D R A M より有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりの単価が高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、D R A M と変わることろはない。10

#### 【0006】

不揮発性記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル形成領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く（半永久的）、揮発性記憶装置で必要なリフレッシュ動作が不要であるという利点を有している（例えば、特許文献 1 参照）。

#### 【0007】

しかし、書き込みの際に生じるトンネル電流によって記憶素子を構成するゲート絶縁層が劣化するため、書き込みを何度も繰り返すことで、記憶素子が機能しなくなるという問題が生じる。この問題を回避するために、例えば、各記憶素子の書き込み回数を均一化する手法が採られるが、これを実現するためには、複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。つまり、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きである。20

#### 【0008】

また、フローティングゲートに電荷を注入し、または、その電荷を除去するためには、高い電圧が必要である。さらに、電荷の注入、または除去のためには比較的長い時間を要し、書き込み、消去の高速化が容易ではないという問題もある。

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

#### 【特許文献 1】特開昭 57 - 105889 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

上述の問題に鑑み、開示する発明の一態様では、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的のとする。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様は、酸化物半導体を用いて形成されるトランジスタと、それ以外の材料を用いて形成されるトランジスタとの積層構造に係る半導体装置である。例えば、次のような構成を採用することができる。

#### 【0012】

本発明の一態様は、第 1 の配線（ソース線）と、第 2 の配線（ビット線）と、第 3 の配線（第 1 信号線）と、第 4 の配線（第 2 信号線）と、第 1 のゲート電極、第 1 のソース電極、および第 1 のドレイン電極を有する第 1 のトランジスタと、第 2 のゲート電極、第 2 のソース電極、および第 2 のドレイン電極を有する第 2 のトランジスタと、を有し、第 1 のトランジスタは、半導体材料を含む基板に設けられ、第 2 のトランジスタは酸化物半導体

40

50

層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線（ソース線）と、第1のソース電極とは、電気的に接続され、第2の配線（ビット線）と、第1のドレイン電極とは、電気的に接続され、第3の配線（第1信号線）と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線（第2信号線）と、第2のゲート電極とは、電気的に接続された半導体装置である。

【0013】

上記において、第1のトランジスタは、半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する。10

【0014】

また、上記において、第2のトランジスタは、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する。

【0015】

また、上記において、半導体材料を含む基板としては、単結晶半導体基板またはSOI基板を採用するのが好適である。特に、半導体材料はシリコンとするのが好適である。

【0016】

また、上記において、酸化物半導体層は、In-Ga-Zn-O系の酸化物半導体材料を含むことが好適である。特に、酸化物半導体層は、In<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub>の結晶を含むことが好適である。さらに、酸化物半導体層の水素濃度は5×10<sup>19</sup>atoms/cm<sup>3</sup>以下とすることが好適である。また、第2のトランジスタのオフ電流は1×10<sup>-13</sup>A以下とすることが好適である。また、第2のトランジスタのオフ電流は1×10<sup>-20</sup>A以下とするとより好適である。20

【0017】

また、上記において、第2のトランジスタは、第1のトランジスタと重畳する領域に設けられた構成とすることができます。

【0018】

なお、本明細書において「上」や「下」という用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。また、「上」「下」という用語は説明の便宜のために用いる表現に過ぎず、特に言及する場合を除き、その上下を入れ替えたものも含む。30

【0019】

また、本明細書において「電極」や「配線」という用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」という用語は、複数の「電極」や「配線」が一体となって形成されている場合などをも含む。40

【0020】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

【0021】

なお、本明細書において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

【0022】

10

20

30

40

50

例えば、「何らかの電気的作用を有するもの」には、電極や配線はもちろんのこと、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【0023】

また、一般に「SOI基板」は絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板をも含む概念として用いる。つまり、「SOI基板」が有する半導体層は、シリコン半導体層に限定されない。また、「SOI基板」における基板は、シリコンウェハなどの半導体基板に限らず、ガラス基板や石英基板、サファイア基板、金属基板などの非半導体基板をも含む。つまり、絶縁表面を有する導体基板や絶縁体基板上に半導体材料からなる層を有するものも、広く「SOI基板」に含まれる。さらに、本明細書において、「半導体基板」は、半導体材料のみからなる基板を指すに留まらず、半導体材料を含む基板全般を示すものとする。つまり、本明細書においては「SOI基板」も広く「半導体基板」に含まれる。

10

【発明の効果】

【0024】

本発明の一態様では、下部に酸化物半導体以外の材料を用いたトランジスタを有し、上部に酸化物半導体を用いたトランジスタを有する半導体装置が提供される。

【0025】

酸化物半導体を用いたトランジスタはオフ電流が極めて小さいため、これを用いることにより極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

20

【0026】

また、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。さらに、トランジスタのオン状態、オフ状態の切り替えによって、情報の書き込みが行われるため、高速動作も容易に実現しうる。また、トランジスタに入力する電位を制御することで情報の書き換えが可能であるため、情報を消去するための動作が不要であるというメリットもある。

30

【0027】

また、酸化物半導体以外の材料を用いたトランジスタは、酸化物半導体を用いたトランジスタと比較して、さらなる高速動作が可能なため、これを用いることにより、記憶内容の読み出しを高速に行うことが可能である。

【0028】

このように、酸化物半導体以外の材料を用いたトランジスタと、酸化物半導体を用いたトランジスタとを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。

【図面の簡単な説明】

【0029】

40

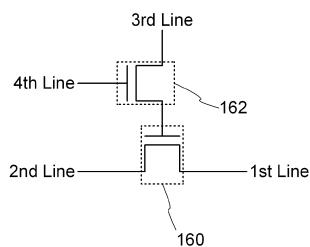

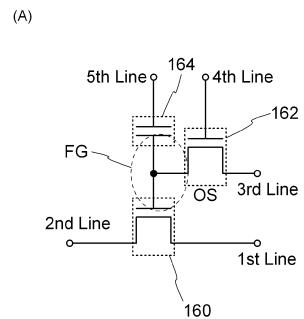

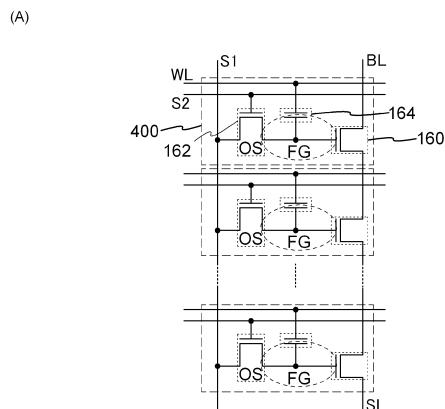

【図1】半導体装置を説明するための回路図

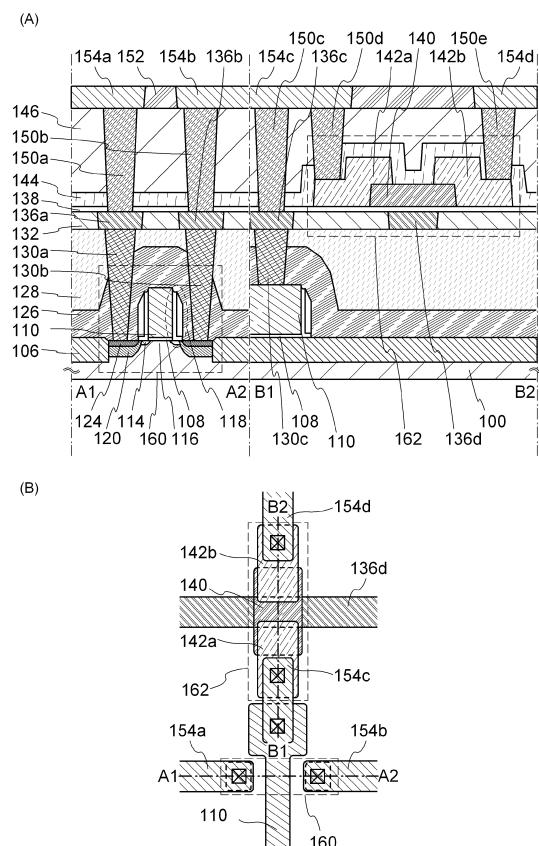

【図2】半導体装置を説明するための断面図および平面図

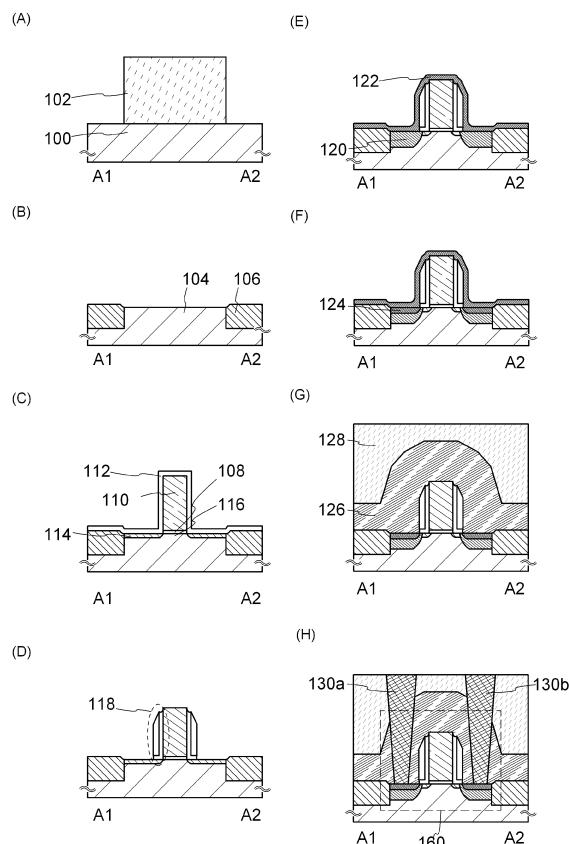

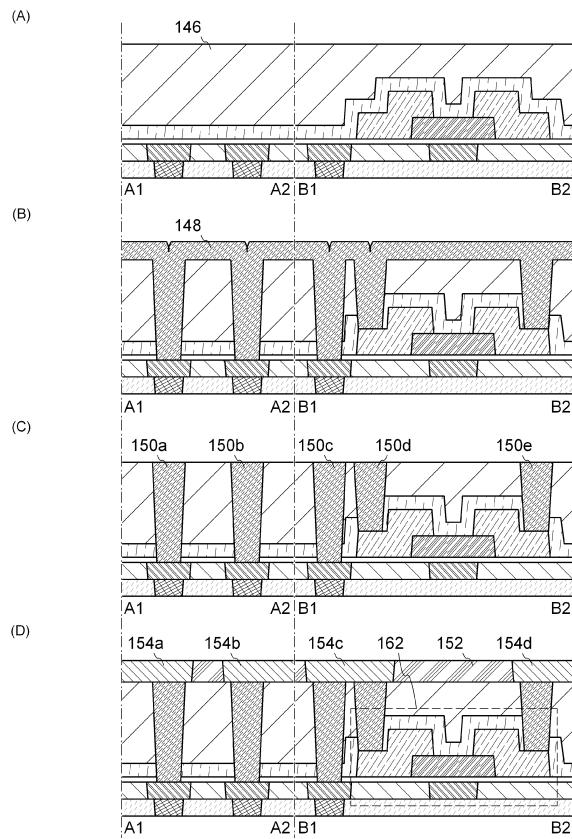

【図3】半導体装置の作製工程を説明するための断面図

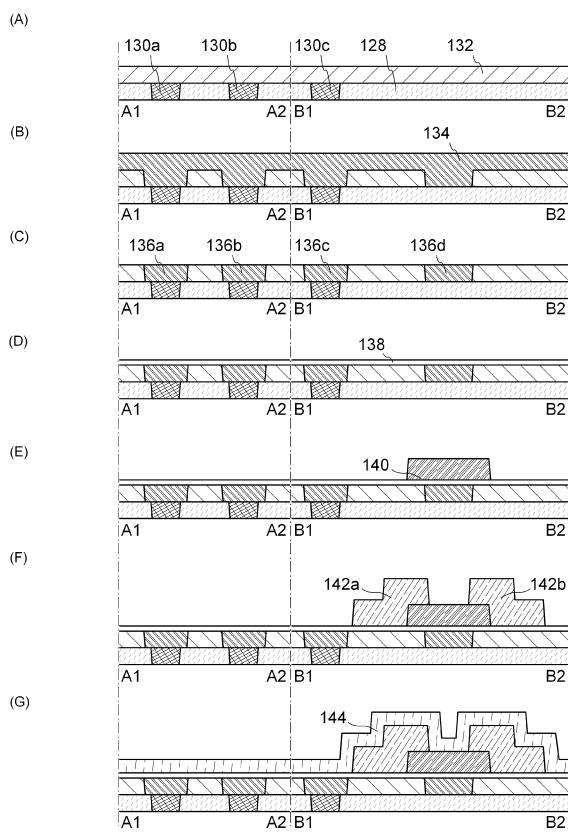

【図4】半導体装置の作製工程を説明するための断面図

【図5】半導体装置の作製工程を説明するための断面図

【図6】半導体装置を説明するための断面図

【図7】半導体装置を説明するための断面図

【図8】半導体装置を説明するための断面図

【図9】半導体装置を説明するための断面図

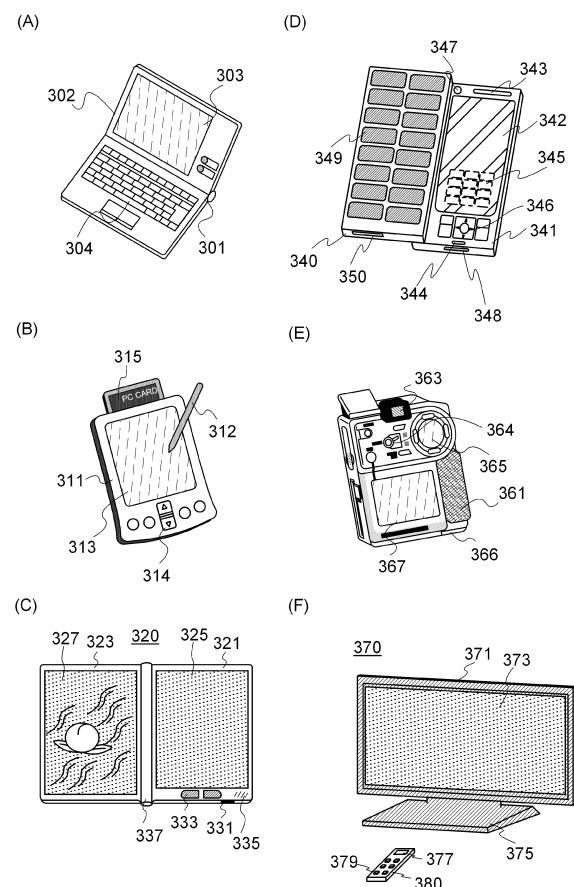

【図10】半導体装置を用いた電子機器を説明するための図

50

- 【図11】酸化物半導体を用いた逆スタガー型のトランジスタの縦断面図

【図12】図11のA-A'断面におけるエネルギー・バンド図（模式図）

【図13】(A)ゲート(GE1)に正の電位(+V<sub>G</sub>)が与えられた状態を示し、(B)ゲート(GE1)に負の電位(-V<sub>G</sub>)が与えられた状態を示す図

【図14】真空準位と金属の仕事関数(Φ<sub>M</sub>)、酸化物半導体の電子親和力(Φ)の関係を示す図

【図15】半導体装置を説明するための回路図

【図16】半導体装置を説明するための回路図

【図17】半導体装置を説明するための回路図

【図18】半導体装置を説明するための回路図

【図19】半導体装置を説明するための回路図

【図20】電位の関係を示すタイミングチャート

【図21】半導体装置を説明するための回路図

【図22】半導体装置を説明するための断面図および平面図

【図23】半導体装置を説明するための断面図

【図24】半導体装置を説明するための断面図

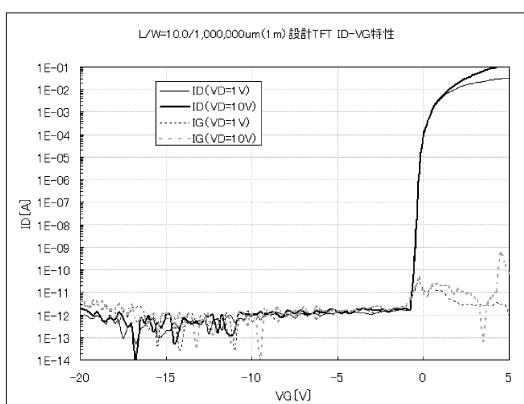

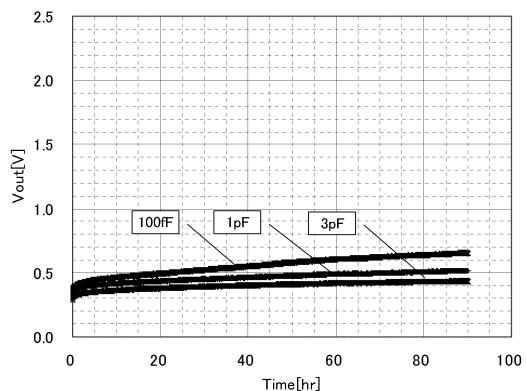

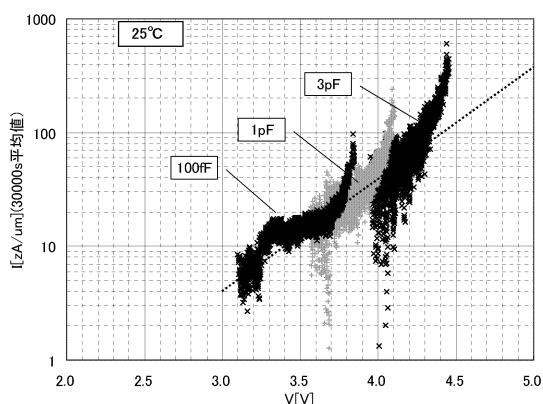

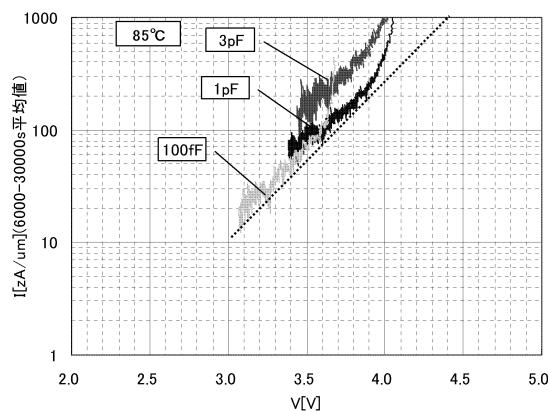

【図25】酸化物半導体を用いたトランジスタの特性を示す図

【図26】酸化物半導体を用いたトランジスタの特性評価用回路図

【図27】酸化物半導体を用いたトランジスタの特性評価用タイミングチャート

【図28】酸化物半導体を用いたトランジスタの特性を示す図

【図29】酸化物半導体を用いたトランジスタの特性を示す図

【図30】酸化物半導体を用いたトランジスタの特性を示す図

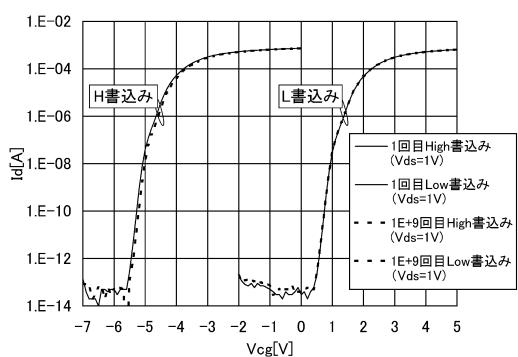

【図31】メモリウィンドウ幅の調査結果を示す図

【発明を実施するための形態】

【0030】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0031】

なお、図面において示す各構成の、位置、大きさ、範囲などは、理解を容易にするため、実際の位置、大きさ、範囲などを表していない場合がある。よって、必ずしも、図面に開示された位置、大きさ、範囲などに限定されない。

【0032】

なお、本明細書における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0033】

(実施の形態1)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成および作製方法について、図1乃至図9を参照して説明する。

【0034】

<半導体装置の回路構成>

図1には、半導体装置の回路構成の一例を示す。当該半導体装置は、酸化物半導体以外の材料（例えばシリコン）を用いたトランジスタ160と酸化物半導体を用いたトランジスタ162によって構成される。なお、以下において、図1に示す半導体装置をメモリセルと呼ぶ場合がある。

【0035】

ここで、トランジスタ160のゲート電極と、トランジスタ162のソース電極またはドレイン電極の一方とは、電気的に接続されている。また、第1の配線(1st Line:ソース線SLとも呼ぶ)とトランジスタ160のソース電極とは、電気的に接続され、

10

20

30

40

50

第2の配線(2nd Line: ビット線BLとも呼ぶ)とトランジスタ160のドレイン電極とは、電気的に接続されている。そして、第3の配線(3rd Line: 第1信号線S1とも呼ぶ)とトランジスタ162のソース電極またはドレイン電極の他方とは、電気的に接続され、第4の配線(4th Line: 第2信号線S2とも呼ぶ)と、トランジスタ162のゲート電極とは、電気的に接続されている。

【0036】

酸化物半導体以外の材料を用いたトランジスタ160は、酸化物半導体を用いたトランジスタと比較して、さらなる高速動作が可能なため、これを用いることにより、記憶内容の読み出しなどを高速に行なうことが可能である。また、酸化物半導体を用いたトランジスタ162は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、トランジスタ160のゲート電極の電位を極めて長時間にわたって保持することが可能である。また、酸化物半導体を用いたトランジスタ162では、短チャネル効果が現れにくいというメリットもある。

10

【0037】

ゲート電極の電位を保持することができるという特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0038】

はじめに、情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位として、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極に与えられる(書き込み)。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位として、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極の電位が保持される(保持)。

20

【0039】

トランジスタ162のオフ電流は極めて小さいから、トランジスタ160のゲート電極の電位は長時間にわたって保持される。例えば、トランジスタ160のゲート電極の電位がトランジスタ160をオン状態とする電位であれば、トランジスタ160のオン状態が長時間にわたって保持されることになる。また、トランジスタ160のゲート電極の電位がトランジスタ160をオフ状態とする電位であれば、トランジスタ160のオフ状態が長時間にわたって保持される。

30

【0040】

次に、情報の読み出しについて説明する。上述のように、トランジスタ160のオン状態またはオフ状態が保持された状態において、第1の配線に所定の電位(低電位)が与えられると、トランジスタ160のオン状態またはオフ状態に応じて、第2の配線の電位は異なる値をとる。例えば、トランジスタ160がオン状態の場合には、第1の配線の電位の影響を受けて、第2の配線の電位が低下することになる。逆に、トランジスタ160がオフ状態の場合には、第2の配線の電位は変化しない。

【0041】

このように、情報が保持された状態において、第2の配線の電位を所定の電位と比較することで、情報を読み出すことができる。

40

【0042】

次に、情報の書き換えについて説明する。情報の書き換えは、上記情報の書き込みおよび保持と同様に行われる。つまり、第4の配線の電位を、トランジスタ162がオン状態となる電位として、トランジスタ162をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、トランジスタ160のゲート電極に与えられる。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位として、トランジスタ162をオフ状態とすることにより、新たな情報が保持された状態となる。

【0043】

このように、開示する発明に係る半導体装置は、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされ

50

る消去動作が不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、半導体装置の高速動作が実現される。

【0044】

酸化物半導体を用いた書き込み用トランジスタ162のオフ電流は極めて小さく、トランジスタ160のゲート電極の電位は長時間にわたって保持される。このため、例えば、従来のDRAMで必要とされたリフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低く（例えば、一ヶ月～一年に一回程度）することが可能である。このように、開示する発明の半導体装置は、実質的な不揮発性記憶装置としての特徴を備えている。

【0045】

また、開示する発明の半導体装置は従来のDRAMとは異なり、読み出しによって情報が失われることがないため、読み出しの度に再び情報を書き込む必要もない。このように、DRAMと比較して情報の書き込みの頻度を著しく低減することができるため、消費電力を十分に抑制することが可能である。

【0046】

また、開示する発明の半導体装置は、半導体装置への再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる消去動作が不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、半導体装置の高速動作が実現される。また、従来のフローティングゲート型トランジスタで書き込みや消去の際に必要とされた高い電圧を必要としないため、半導体装置の消費電力をさらに低減することができる。

【0047】

また、開示する発明に係る半導体装置は、書き込み用トランジスタと読み出し用トランジスタと、を少なくとも含んでいればよく、1メモリセルあたり6つのトランジスタを必要とするSRAMなどと比較して、メモリセルあたりの面積を十分に小さくすることが可能である。このため、半導体装置を高密度に配置することができる。

【0048】

また、従来のフローティングゲート型トランジスタでは、書き込み時にゲート絶縁膜（トンネル絶縁膜）中を電荷が移動するために、当該ゲート絶縁膜（トンネル絶縁膜）の劣化が不可避であった。しかしながら、本発明の一態様に係るメモリセルにおいては、書き込み用トランジスタのスイッチング動作により情報の書き込みがなされるため、従来問題とされていたゲート絶縁膜の劣化を解消することができる。これは、原理的な書き込み回数の制限が存在せず、書き換え耐性が極めて高いことを意味するものである。例えば、 $1 \times 10^9$ 回（10億回）以上の書き込み後であっても、電流-電圧特性に劣化が見られない。

【0049】

なお、酸化物半導体を用いた書き込み用トランジスタ162の電界効果移動度は、オン状態において、 $3 \text{ cm}^2 / \text{V s}$ 以上 $250 \text{ cm}^2 / \text{V s}$ 以下、好ましくは $5 \text{ cm}^2 / \text{V s}$ 以上 $200 \text{ cm}^2 / \text{V s}$ 以下、より好ましくは $10 \text{ cm}^2 / \text{V s}$ 以上 $150 \text{ cm}^2 / \text{V s}$ 以下とする。また、酸化物半導体を用いたトランジスタは、サブスレッショルドスイング値（S値）が $0.1 \text{ V} / \text{dec}$ 以下となるようにする。このようなトランジスタを用いることにより、情報の書き込みに要する時間を十分に短くすることができる。

【0050】

また、酸化物半導体を用いた書き込み用トランジスタ162のチャネル長Lは $10 \text{ nm}$ 以上 $400 \text{ nm}$ 以下とするのが好ましい。このようなチャネルサイズとすることで、トランジスタの動作の高速化、低消費電力化、高集積化など、様々な効果を得ることができる。

【0051】

なお、読み出し用トランジスタ160には、結晶性のシリコンを用いたトランジスタを適用するのが好ましい。特に、読み出し動作の高速化の観点からは、単結晶シリコンを用いたnチャネル型のトランジスタを用いるのがよい。このような単結晶シリコントランジス

10

20

30

40

50

タは、例えば、バルクシリコン（いわゆるシリコンウェハ）を用いて形成することができる。

【0052】

なお、上記説明は、n型トランジスタ（nチャネル型トランジスタ）を用いる場合についてのものであるが、n型トランジスタに代えて、p型トランジスタを用いることができるのにはいうまでもない。

【0053】

＜半導体装置の平面構成および断面構成＞

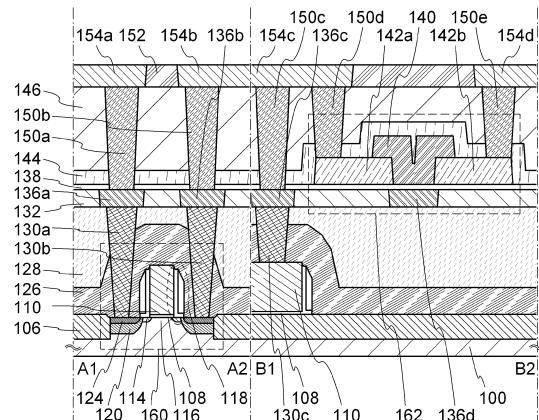

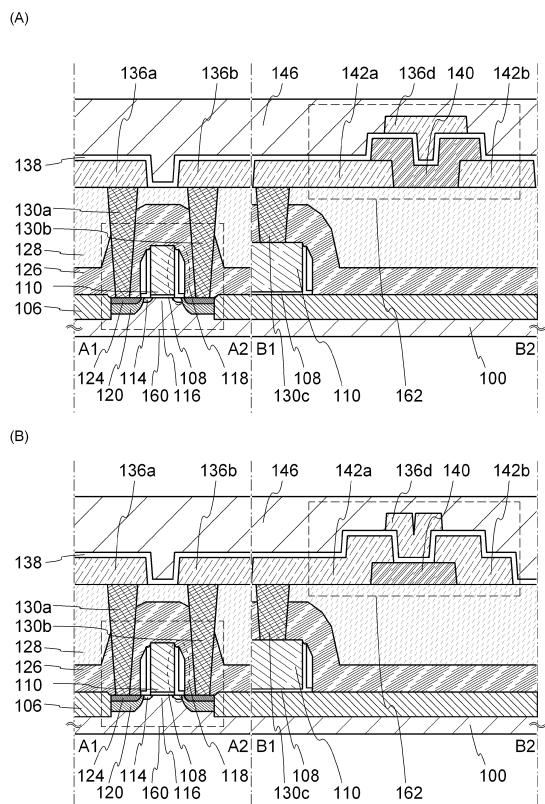

図2は、上記半導体装置の構成の一例である。図2(A)には、半導体装置の断面を、図2(B)には、半導体装置の平面を、それぞれ示す。ここで、図2(A)は、図2(B)の線A1-A2および線B1-B2における断面に相当する。図2(A)および図2(B)に示される半導体装置は、下部に酸化物半導体以外の材料を用いたトランジスタ160を有し、上部に酸化物半導体を用いたトランジスタ162を有するものである。なお、トランジスタ160およびトランジスタ162は、いずれもn型トランジスタとして説明するが、p型トランジスタを採用しても良い。特に、トランジスタ160は、p型とすることが容易である。

【0054】

トランジスタ160は、半導体材料を含む基板100に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設けられた不純物領域114および高濃度不純物領域120（これらをあわせて単に不純物領域とも呼ぶ）と、チャネル形成領域116上に設けられたゲート絶縁層108と、ゲート絶縁層108上に設けられたゲート電極110と、不純物領域114と電気的に接続するソース電極またはドレイン電極130a、ソース電極またはドレイン電極130bを有する。

【0055】

ここで、ゲート電極110の側面にはサイドウォール絶縁層118が設けられている。また、基板100の、断面図に示すように、サイドウォール絶縁層118と重ならない領域には、高濃度不純物領域120を有し、高濃度不純物領域120上には金属化合物領域124が存在する。また、基板100上にはトランジスタ160を囲むように素子分離絶縁層106が設けられており、トランジスタ160を覆うように、層間絶縁層126および層間絶縁層128が設けられている。ソース電極またはドレイン電極130a、ソース電極またはドレイン電極130bは、層間絶縁層126および層間絶縁層128に形成された開口を通じて、金属化合物領域124と電気的に接続されている。つまり、ソース電極またはドレイン電極130a、ソース電極またはドレイン電極130bは、金属化合物領域124を介して高濃度不純物領域120および不純物領域114と電気的に接続されている。また、ゲート電極110には、ソース電極またはドレイン電極130aやソース電極またはドレイン電極130bと同様に設けられた電極130cが電気的に接続されている。

【0056】

トランジスタ162は、層間絶縁層128上に設けられたゲート電極136dと、ゲート電極136d上に設けられたゲート絶縁層138と、ゲート絶縁層138上に設けられた酸化物半導体層140と、酸化物半導体層140上に設けられ、酸化物半導体層140と電気的に接続されているソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bと、を有する。

【0057】

ここで、ゲート電極136dは、層間絶縁層128上に形成された絶縁層132に、埋め込まれるように設けられている。また、ゲート電極136dと同様に、ソース電極またはドレイン電極130aに接して電極136aが、ソース電極またはドレイン電極130bに接して電極136bが、電極130cに接して電極136cが、それぞれ形成されている。

【0058】

10

20

30

40

50

また、トランジスタ 162 の上には、酸化物半導体層 140 の一部と接するように、保護絶縁層 144 が設けられており、保護絶縁層 144 上には層間絶縁層 146 が設けられている。ここで、保護絶縁層 144 および層間絶縁層 146 には、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b にまで達する開口が設けられており、当該開口を通じて、電極 150d、電極 150e が、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b に接して形成されている。また、電極 150d、電極 150e と同様に、ゲート絶縁層 138、保護絶縁層 144、層間絶縁層 146 に設けられた開口を通じて、電極 136a、電極 136b、電極 136c に接する電極 150a、電極 150b、電極 150c が形成されている。

## 【0059】

ここで、酸化物半導体層 140 は水素などの不純物が十分に除去され、高純度化されているものであることが望ましい。具体的には、酸化物半導体層 140 の水素濃度は  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、望ましくは  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、より望ましくは  $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下とする。これにより、一般的なシリコンウェハ（リンやボロンなどの不純物元素が微量に添加されたシリコンウェハ）におけるキャリア濃度（ $1 \times 10^{14}$  / cm<sup>3</sup> 程度）と比較して、十分に小さいキャリア濃度の値（例えば、 $1 \times 10^{12}$  / cm<sup>3</sup> 未満、あるいは、 $1.45 \times 10^{10}$  / cm<sup>3</sup> 未満）となる。このように、水素濃度が十分に低減されて高純度化され、真性化（i型化）または実質的に真性化（i型化）された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ 162 を得ることができる。例えば、トランジスタ 162 の室温（25）

20 でのオフ電流（ここでは、単位チャネル幅（1 μm）あたりの値）は、10 zA / μm（1 zA（ゼプトアンペア）は  $1 \times 10^{-21}$  A）以下、望ましくは、1 zA / μm 以下となる。また、85 では、100 zA / μm（ $1 \times 10^{-19}$  A / μm）以下、好ましくは 10 zA / μm（ $1 \times 10^{-20}$  A / μm）以下となる。このように、水素濃度が十分に低減され、真性化または実質的に真性化された酸化物半導体層 140 を適用し、トランジスタ 162 のオフ電流を低減することにより、新たな構成の半導体装置を実現することができる。なお、上述の酸化物半導体層 140 中の水素濃度は、二次イオン質量分析法（SIMS: Secondary Ion Mass Spectroscopy）で測定したものである。

## 【0060】

また、層間絶縁層 146 上には絶縁層 152 が設けられており、当該絶縁層 152 に埋め込まれるように、電極 154a、電極 154b、電極 154c、電極 154d が設けられている。ここで、電極 154a は電極 150a と接しており、電極 154b は電極 150b と接しており、電極 154c は電極 150c および電極 150d と接しており、電極 154d は電極 150e と接している。

## 【0061】

つまり、図 2 に示される半導体装置では、トランジスタ 160 のゲート電極 110 と、トランジスタ 162 のソース電極またはドレイン電極 142a とが、電極 130c、電極 136c、電極 150c、電極 154c および電極 150d を介して電気的に接続されている。

## 【0062】

## &lt;半導体装置の作製方法&gt;

次に、上記半導体装置の作製方法の一例について説明する。以下では、はじめに下部のトランジスタ 160 の作製方法について図 3 を参照して説明し、その後、上部のトランジスタ 162 の作製方法について図 4 および図 5 を参照して説明する。

## 【0063】

## &lt;下部のトランジスタの作製方法&gt;

まず、半導体材料を含む基板 100 を用意する（図 3（A）参照）。半導体材料を含む基板 100 としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI 基板などを適用することができます

10

20

30

40

50

る。ここでは、半導体材料を含む基板 100 として、単結晶シリコン基板を用いる場合の一例について示すものとする。

#### 【0064】

基板 100 上には、素子分離絶縁層を形成するためのマスクとなる保護層 102 を形成する(図 3 (A) 参照)。保護層 102 としては、例えば、酸化シリコンや窒化シリコン、窒化酸化シリコンなどを材料とする絶縁層を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n 型の導電性を付与する不純物元素や p 型の導電性を付与する不純物元素を基板 100 に添加してもよい。半導体がシリコンの場合、n 型の導電性を付与する不純物としては、例えば、リンや砒素などを用いることができる。また、p 型の導電性を付与する不純物としては、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。10

#### 【0065】

次に、上記の保護層 102 をマスクとしてエッチングを行い、保護層 102 に覆われていない領域(露出している領域)の基板 100 の一部を除去する。これにより分離された半導体領域 104 が形成される(図 3 (B) 参照)。当該エッチングには、ドライエッチングを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液については被エッチング材料に応じて適宜選択することができる。

#### 【0066】

次に、半導体領域 104 を覆うように絶縁層を形成し、半導体領域 104 に重畠する領域の絶縁層を選択的に除去することで、素子分離絶縁層 106 を形成する(図 3 (B) 参照)。当該絶縁層は、酸化シリコンや窒化シリコン、窒化酸化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。なお、半導体領域 104 の形成後、または、素子分離絶縁層 106 の形成後には、上記保護層 102 を除去する。20

#### 【0067】

次に、半導体領域 104 上に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

#### 【0068】

絶縁層は後のゲート絶縁層となるものであり、CVD 法やスパッタリング法等を用いて得られる酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等を含む膜の単層構造または積層構造とすると良い。他に、高密度プラズマ処理や熱酸化処理によって、半導体領域 104 の表面を酸化、窒化させることにより、上記絶縁層を形成してもよい。高密度プラズマ処理は、例えば、He、Ar、Kr、Xe などの希ガスと、酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスを用いて行うことができる。また、絶縁層の厚さは特に限定されないが、例えば、1 nm 以上 100 nm 以下とすることができる。30

#### 【0069】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タンゲステン等の金属材料を用いて形成することができる。また、導電材料を含む多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD 法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。40

#### 【0070】

その後、絶縁層および導電材料を含む層を選択的にエッチングして、ゲート絶縁層 108 、ゲート電極 110 を形成する(図 3 (C) 参照)。

#### 【0071】

次に、ゲート電極 110 を覆う絶縁層 112 を形成する(図 3 (C) 参照)。そして、半導体領域 104 にリン(P) やヒ素(As)などを添加して、基板 100 との浅い接合深さの不純物領域 114 を形成する(図 3 (C) 参照)。なお、ここでは n 型トランジスタ50

を形成するためにリンやヒ素を添加しているが、p型トランジスタを形成する場合には、硼素（B）やアルミニウム（Al）などの不純物元素を添加すればよい。なお、不純物領域114の形成により、半導体領域104のゲート絶縁層108下部には、チャネル形成領域116が形成される（図3（C）参照）。ここで、添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。また、ここでは、絶縁層112を形成した後に不純物領域114を形成する工程を採用しているが、不純物領域114を形成した後に絶縁層112を形成する工程としても良い。

#### 【0072】

次に、サイドウォール絶縁層118を形成する（図3（D）参照）。サイドウォール絶縁層118は、絶縁層112を覆うように絶縁層を形成した後に、当該絶縁層に異方性の高いエッチング処理を適用することで、自己整合的に形成することができる。また、この際に、絶縁層112を部分的にエッチングして、ゲート電極110の上面と、不純物領域114の上面を露出させると良い。

10

#### 【0073】

次に、ゲート電極110、不純物領域114、サイドウォール絶縁層118等を覆うように、絶縁層を形成する。そして、当該絶縁層が不純物領域114と接する領域に、リン（P）やヒ素（As）などを添加して、高濃度不純物領域120を形成する（図3（E）参照）。その後、上記絶縁層を除去し、ゲート電極110、サイドウォール絶縁層118、高濃度不純物領域120等を覆うように金属層122を形成する（図3（E）参照）。当該金属層122は、真空蒸着法やスパッタリング法、スピンドルコート法などの各種成膜方法を用いて形成することができる。金属層122は、半導体領域104を構成する半導体材料と反応して低抵抗な金属化合物となる金属材料を用いて形成することができる。このような金属材料としては、例えば、チタン、タンタル、タンクスチル、ニッケル、コバルト、白金等がある。

20

#### 【0074】

次に、熱処理を施して、上記金属層122と半導体材料とを反応させる。これにより、高濃度不純物領域120に接する金属化合物領域124が形成される（図3（F）参照）。なお、ゲート電極110として多結晶シリコンなどを用いる場合には、ゲート電極110の金属層122と接触する部分にも、金属化合物領域が形成されることになる。

30

#### 【0075】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理が実現できる方法を用いることが望ましい。なお、上記の金属化合物領域は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。当該金属化合物領域を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属化合物領域124を形成した後には、金属層122は除去する。

#### 【0076】

次に、上述の工程により形成された各構成を覆うように、層間絶縁層126、層間絶縁層128を形成する（図3（G）参照）。層間絶縁層126や層間絶縁層128は、酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等の無機絶縁材料を含む材料を用いて形成することができる。また、ポリイミド、アクリル樹脂等の有機絶縁材料を用いて形成することも可能である。なお、ここでは、層間絶縁層126と層間絶縁層128の二層構造としているが、層間絶縁層の構成はこれに限定されない。層間絶縁層128の形成後には、その表面を、CMPやエッチング処理などによって平坦化しておくことが望ましい。

40

#### 【0077】

その後、上記層間絶縁層126、128に、金属化合物領域124にまで達する開口を形成し、当該開口に、ソース電極またはドレイン電極130a、ソース電極またはドレイン

50

電極 130b を形成する（図 3（H）参照）。ソース電極またはドレイン電極 130a やソース電極またはドレイン電極 130b は、例えば、開口を含む領域に PVD 法や CVD 法などを用いて導電層を形成した後、エッティング処理や CMP といった方法を用いて、上記導電層の一部を除去することにより形成することができる。

#### 【0078】

なお、上記導電層の一部を除去してソース電極またはドレイン電極 130a やソース電極またはドレイン電極 130b を形成する際には、その表面が平坦になるように加工することが望ましい。例えば、開口を含む領域にチタン膜や窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する場合には、その後の CMP によって、不要なタンゲステン膜、チタン膜、窒化チタン膜などを除去すると共に、その表面の平坦性を向上させることができる。このように、ソース電極またはドレイン電極 130a、ソース電極またはドレイン電極 130b を含む表面を平坦化することにより、後の工程において、良好な電極、配線、絶縁層、半導体層などを形成することが可能となる。

10

#### 【0079】

なお、ここでは、金属化合物領域 124 と接触するソース電極またはドレイン電極 130a やソース電極またはドレイン電極 130b のみを示しているが、この工程において、ゲート電極 110 と接触する電極（例えば、図 2 における電極 130c）などをあわせて形成することができる。ソース電極またはドレイン電極 130a、ソース電極またはドレイン電極 130b として用いることができる材料について特に限定はなく、各種導電材料を用いることができる。例えば、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウムなどの導電性材料を用いることができる。

20

#### 【0080】

以上により、半導体材料を含む基板 100 を用いたトランジスタ 160 が形成される。なお、上記工程の後には、さらに電極や配線、絶縁層などを形成しても良い。配線の構造として、層間絶縁層および導電層の積層構造である多層配線構造を採用することにより、高度に集積化した半導体装置を提供することができる。

#### 【0081】

##### <上部のトランジスタの作製方法>

次に、図 4 および図 5 を用いて、層間絶縁層 128 上にトランジスタ 162 を作製する工程について説明する。なお、図 4 および図 5 は、層間絶縁層 128 上の各種電極や、トランジスタ 162 などの作製工程を示すものであるから、トランジスタ 162 の下部に存在するトランジスタ 160 等については省略している。

30

#### 【0082】

まず、層間絶縁層 128、ソース電極またはドレイン電極 130a、ソース電極またはドレイン電極 130b、電極 130c 上に絶縁層 132 を形成する（図 4（A）参照）。絶縁層 132 は PVD 法や CVD 法などを用いて形成することができる。また、酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等の無機絶縁材料を含む材料を用いて形成することができる。

#### 【0083】

次に、絶縁層 132 に対し、ソース電極またはドレイン電極 130a、ソース電極またはドレイン電極 130b、および、電極 130c にまで達する開口を形成する。この際、後にゲート電極 136d が形成される領域にも併せて開口を形成する。そして、上記開口に埋め込むように、導電層 134 を形成する（図 4（B）参照）。上記開口はマスクを用いたエッティングなどの方法で形成することができる。当該マスクは、フォトマスクを用いた露光などの方法によって形成することができる。エッティングとしては、ウェットエッティング、ドライエッティングのいずれを用いても良いが、微細加工の観点からは、ドライエッティングを用いることが好適である。導電層 134 の形成は、PVD 法や CVD 法などの成膜法を用いて行うことができる。導電層 134 の形成に用いることができる材料としては、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウムなどの導電性材料や、これらの合金、化合物（例えば窒化物）などが挙げられる。

40

50

げられる。

【0084】

より具体的には、例えば、開口を含む領域にPVD法によりチタン膜を薄く形成し、CVD法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、下部電極（ここではソース電極またはドレイン電極130a、ソース電極またはドレイン電極130b、電極130cなど）の表面の酸化膜を還元し、下部電極との接触抵抗を低減させる機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや、窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

10

【0085】

導電層134を形成した後には、エッチング処理やCMPといった方法を用いて導電層134の一部を除去し、絶縁層132を露出させて、電極136a、電極136b、電極136c、ゲート電極136dを形成する（図4（C）参照）。なお、上記導電層134の一部を除去して電極136a、電極136b、電極136c、ゲート電極136dを形成する際には、表面が平坦になるように加工することが望ましい。このように、絶縁層132、電極136a、電極136b、電極136c、ゲート電極136dの表面を平坦化することにより、後の工程において、良好な電極、配線、絶縁層、半導体層などを形成することが可能となる。

【0086】

次に、絶縁層132、電極136a、電極136b、電極136c、ゲート電極136dを覆うように、ゲート絶縁層138を形成する（図4（D）参照）。ゲート絶縁層138は、CVD法やスパッタリング法等を用いて形成することができる。また、ゲート絶縁層138は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどを含むように形成するのが好適である。なお、ゲート絶縁層138は、単層構造としても良いし、積層構造としても良い。例えば、原料ガスとして、シラン（SiH<sub>4</sub>）、酸素、窒素を用いたプラズマCVD法により、酸化窒化珪素でなるゲート絶縁層138を形成することができる。ゲート絶縁層138の厚さは特に限定されないが、例えば、10nm以上500nm以下とすることができます。積層構造の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層と、第1のゲート絶縁層上の膜厚5nm以上300nm以下の第2のゲート絶縁層の積層とすると好適である。

20

【0087】

なお、不純物を除去することによりi型化または実質的にi型化された酸化物半導体（高純度化された酸化物半導体）は、界面準位や界面電荷に対して極めて敏感であるため、このような酸化物半導体を酸化物半導体層に用いる場合には、ゲート絶縁層との界面は重要である。つまり、高純度化された酸化物半導体層に接するゲート絶縁層138には、高品質化が要求されることになる。

30

【0088】

例えば、μ波（2.45GHz）を用いた高密度プラズマCVD法は、緻密で絶縁耐圧の高い高品質なゲート絶縁層138を形成できる点で好適である。高純度化された酸化物半導体層と高品質ゲート絶縁層とが接することにより、界面準位を低減して界面特性を良好なものとすることができますからである。

40

【0089】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、高純度化された酸化物半導体層を用いる場合であっても、スパッタリング法やプラズマCVD法など他の方法を適用することができる。また、形成後の熱処理によって、膜質や酸化物半導体層との界面特性が改質される絶縁層を適用しても良い。いずれにしても、ゲート絶縁層138としての膜質が良好であると共に、酸化物半導体層との界面準位密度を低減し、良好な界面を形成できるものを形成すれば良い。

【0090】

50

不純物が酸化物半導体に含まれている場合、強い電界や高い温度などのストレスにより、不純物と酸化物半導体の主成分との結合が切断され、生成された未結合手はしきい値電圧( $V_{th}$ )のシフトを誘発する。

【0091】

酸化物半導体の不純物、特に水素や水などの不純物を極力除去し、かつ、上記のようにゲート絶縁層との界面特性を良好にすることにより、強電界や高温などのストレスに対しても安定なトランジスタを得ることが可能である。

【0092】

次いで、ゲート絶縁層138上に、酸化物半導体層を形成し、マスクを用いたエッティングなどの方法によって当該酸化物半導体層を加工して、島状の酸化物半導体層140を形成する(図4(E)参照)。

10

【0093】

酸化物半導体層としては、In-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体層、特に非晶質酸化物半導体層を用いるのが好適である。本実施の形態では、酸化物半導体層としてIn-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いて、非晶質の酸化物半導体層をスパッタ法により形成することとする。なお、非晶質の酸化物半導体層中にシリコンを添加することで、その結晶化を抑制することができるから、例えば、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて酸化物半導体層を形成しても良い。

20

【0094】

酸化物半導体層をスパッタリング法で作製するためのターゲットとしては、例えば、酸化亜鉛を主成分とする酸化物半導体成膜用ターゲットを用いることができる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1[mol比])などを用いることもできる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲットとして、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol比]、またはIn<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:4[mol比]の組成比を有するターゲットなどを用いても良い。酸化物半導体成膜用ターゲットの充填率は90%以上100%以下、好ましくは95%以上(例えば99.9%)である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、緻密な酸化物半導体層が形成される。

30

【0095】

酸化物半導体層の形成雰囲気は、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気、または、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である。具体的には、例えば、水素、水、水酸基を有する化合物、または水素化物などの不純物の濃度が数ppm程度(望ましくは数ppb程度)にまで除去された高純度ガスを用いるのが好適である。

【0096】

酸化物半導体層の形成の際には、減圧状態に保持された処理室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら酸化物半導体層を形成することにより、酸化物半導体層に含まれる不純物濃度を低減することができる。また、スパッタリングによる酸化物半導体層の損傷が軽減される。そして、処理室内の残留水分を除去しつつ水素および水が除去されたスパッタガスを導入し、金属酸化物をターゲットとして酸化物半導体層を形成する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることができる。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、炭素原子を含む化合物に加え、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で形成した酸化物半

40

50

導体層に含まれる不純物の濃度を低減できる。

【0097】

形成条件としては、例えば、基板とターゲットの間との距離が100mm、圧力が0.6Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素流量比率100%)雰囲気、といった条件を適用することができる。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も小さくなるため、好ましい。酸化物半導体層の厚さは、2nm以上200nm以下、好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚さは異なるから、その厚さは用いる材料に応じて適宜選択すればよい。

【0098】

なお、酸化物半導体層をスパッタ法により形成する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層138の表面に付着しているゴミを除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおいては、スパッタターゲットにイオンを衝突させるところ、逆に、処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、基板付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素雰囲気、ヘリウム雰囲気、酸素雰囲気などを用いても良い。

【0099】

上記酸化物半導体層のエッチングには、ドライエッチング、ウェットエッチングのいずれを用いても良い。もちろん、両方を組み合わせて用いることもできる。所望の形状にエッチングできるよう、材料に合わせてエッチング条件(エッチングガスやエッチング液、エッチング時間、温度等)を適宜設定する。

【0100】

ドライエッチングに用いるエッチングガスには、例えば、塩素を含むガス(塩素系ガス、例えば塩素(Cl<sub>2</sub>)、塩化硼素(BCl<sub>3</sub>)、塩化珪素(SiCl<sub>4</sub>)、四塩化炭素(CC<sub>1</sub><sub>4</sub>)など)などがある。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF<sub>4</sub>)、弗化硫黄(SF<sub>6</sub>)、弗化窒素(NF<sub>3</sub>)、トリフルオロメタン(CHF<sub>3</sub>)など)、臭化水素(HBr)、酸素(O<sub>2</sub>)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いても良い。

【0101】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)は適宜設定する。

【0102】

ウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO 07N(関東化学社製)などを用いてもよい。

【0103】

次いで、酸化物半導体層に第1の熱処理を行うことが望ましい。この第1の熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の熱処理の温度は、300以上750以下、好ましくは400以上基板の歪み点未満とする。例えば、抵抗発熱体などを用いた電気炉に基板を導入し、酸化物半導体層140に対して窒素雰囲気下450において1時間の熱処理を行う。この間、酸化物半導体層140は、大気に触れないようにし、水や水素の再混入が行われないようにする。

【0104】

なお、熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置であっても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid

10

20

30

40

50

Thermal Anneal) 装置等のRTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。気体としては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性ガスが用いられる。

#### 【0105】

例えば、第1の熱処理として、650～700の高温に加熱した不活性ガス中に基板を投入し、数分間加熱した後、当該不活性ガス中から基板を取り出すGRTA処理を行ってもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、短時間の熱処理であるため、基板の歪み点を超える温度条件であっても適用が可能となる。

10

#### 【0106】

なお、第1の熱処理は、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気で行なうことが望ましい。例えば、熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

#### 【0107】

第1の熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶または多結晶となる場合もある。例えば、結晶化率が90%以上、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場合もある。

20

#### 【0108】

また、非晶質の酸化物半導体(例えば、酸化物半導体層の表面)に微結晶(粒径1nm以上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる場合もある。

#### 【0109】

また、非晶質の領域中に微結晶を配列させることで、酸化物半導体層の電気的特性を変化させることも可能である。例えば、In-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いて酸化物半導体層を形成する場合には、電気的異方性を有するIn<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub>の結晶粒が配向した微結晶部を形成することで、酸化物半導体層の電気的特性を変化させることができる。

30

#### 【0110】

より具体的には、例えば、In<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub>のc軸が酸化物半導体層の表面に垂直な方向をとるように配向させることで、酸化物半導体層の表面に平行な方向の導電性を向上させ、酸化物半導体層の表面に垂直な方向の絶縁性を向上させることができる。また、このような微結晶部は、酸化物半導体層中への水や水素などの不純物の侵入を抑制する機能を有する。

40

#### 【0111】

なお、上述の微結晶部を有する酸化物半導体層は、GRTA処理による酸化物半導体層の加熱によって形成することができる。また、Znの含有量がInまたはGaの含有量より小さいスパッタターゲットを用いることで、より好適に形成することができる。

#### 【0112】

酸化物半導体層140に対する第1の熱処理は、島状の酸化物半導体層140に加工する前の酸化物半導体層に行なうこともできる。その場合には、第1の熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行うことになる。

#### 【0113】

なお、上記第1の熱処理は、酸化物半導体層140に対する脱水化、脱水素化の効果があ

50

るから、脱水化処理、脱水素化処理などと呼ぶこともできる。このような脱水化処理、脱水素化処理は、酸化物半導体層の形成後、酸化物半導体層 140 上にソース電極またはドレイン電極を積層させた後、ソース電極またはドレイン電極上に保護絶縁層を形成した後、などのタイミングにおいて行うことが可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

#### 【0114】

次に、酸化物半導体層 140 に接するように、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b を形成する（図 4 (F) 参照）。ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b は、酸化物半導体層 140 を覆うように導電層を形成した後、当該導電層を選択的にエッチングすることにより形成することができる。

10

#### 【0115】

導電層は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチルから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムから選択されたいずれか一または複数の材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タンクスチル、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み合わせた材料を用いてもよい。導電層は、単層構造であっても良いし、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された 2 層構造、チタン膜とアルミニウム膜とチタン膜とが積層された 3 層構造などが挙げられる。

20

#### 【0116】

ここで、エッチングに用いるマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光を用いるのが好適である。

#### 【0117】

トランジスタのチャネル長 (L) は、ソース電極またはドレイン電極 142a の下端部と、ソース電極またはドレイン電極 142b の下端部との間隔によって決定される。なお、チャネル長 (L) が 25 nm 未満において露光を行う場合には、数 nm ~ 数 10 nm と極めて波長が短い超紫外線 (Extreme Ultraviolet) を用いてマスク形成の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長 (L) を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化できる。さらにオフ電流値が極めて小さいため、消費電力が大きくならずく済む。

30

#### 【0118】

なお、導電層のエッチングの際には、酸化物半導体層 140 が除去されないように、それぞれの材料およびエッチング条件を適宜調節する。なお、材料およびエッチング条件によつては、当該工程において、酸化物半導体層 140 の一部がエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。

#### 【0119】

40

また、酸化物半導体層 140 とソース電極またはドレイン電極 142a の間や、酸化物半導体層 140 とソース電極またはドレイン電極 142b の間には、酸化物導電層を形成してもよい。酸化物導電層と、ソース電極またはドレイン電極 142a やソース電極またはドレイン電極 142b を形成するための金属層は、連続して形成すること（連続成膜）が可能である。酸化物導電層はソース領域またはドレイン領域として機能しうる。このような酸化物導電層を設けることで、ソース領域またはドレイン領域の低抵抗化を図ることができため、トランジスタの高速動作が実現される。

#### 【0120】

また、上記マスクの使用数や工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによってレジストマスクを形成し、これを用いてエッチング工

50

程を行ってもよい。多階調マスクを用いて形成したレジストマスクは、複数の厚みを有する形状（階段状）となり、アッシングによりさらに形状を変形させることができるために、異なるパターンに加工する複数のエッチング工程に用いることができる。つまり、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって、露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が図れる。

#### 【0121】

なお、上述の工程の後には、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行うのが好ましい。当該プラズマ処理によって、露出している酸化物半導体層の表面に付着した水などが除去される。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

10

#### 【0122】

次に、大気に触れさせることなく、酸化物半導体層140の一部に接する保護絶縁層144を形成する（図4（G）参照）。

#### 【0123】

保護絶縁層144は、スパッタ法など、保護絶縁層144に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。また、その厚さは、1nm以上とする。保護絶縁層144に用いることができる材料としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などがある。また、その構造は、単層構造としても良いし、積層構造としても良い。保護絶縁層144を形成する際の基板温度は、室温以上300以下とするのが好ましく、雰囲気は、希ガス（代表的にはアルゴン）雰囲気、酸素雰囲気、または希ガス（代表的にはアルゴン）と酸素の混合雰囲気とするのが好適である。

20

#### 【0124】

保護絶縁層144に水素が含まれると、その水素の酸化物半導体層への侵入や、水素による酸化物半導体層中の酸素の引き抜き、などが生じ、酸化物半導体層のバックチャネル側が低抵抗化してしまい、寄生チャネルが形成されるおそれがある。よって、保護絶縁層144はできるだけ水素を含まないように、形成方法においては水素を用いないことが重要である。

#### 【0125】

また、処理室内の残留水分を除去しつつ保護絶縁層144を形成することが好ましい。酸化物半導体層140および保護絶縁層144に水素、水酸基または水が含まれないようにするためである。

30

#### 【0126】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水（H<sub>2</sub>O）など水素原子を含む化合物等が除去されているため、当該成膜室で形成した保護絶縁層144に含まれる不純物の濃度を低減できる。

40

#### 【0127】

保護絶縁層144を形成する際に用いるスパッタガスとしては、水素、水、水酸基を含む化合物、または水素化物などの不純物の濃度が数ppm程度（望ましくは数ppb程度）にまで除去された高純度ガスを用いることが好ましい。

#### 【0128】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の熱処理（好ましくは200以上400以下、例えば250以上350以下）を行うのが望ましい。例えば、窒素雰囲気下で250、1時間の第2の熱処理を行う。第2の熱処理を行うと、トランジスタの電気的特性のばらつきを低減することができる。

#### 【0129】

また、大気中、100以上200以下、1時間以上30時間以下の熱処理を行っても

50

よい。この熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この熱処理を、保護絶縁層の形成前に、減圧下で行ってもよい。減圧下で熱処理を行うと、加熱時間を短縮することができる。なお、当該減圧下での熱処理は、上記第2の熱処理に代えて行っても良いし、第2の熱処理の前後などに行っても良い。

#### 【0130】

次に、保護絶縁層144上に、層間絶縁層146を形成する(図5(A)参照)。層間絶縁層146はPVD法やCVD法などを用いて形成することができる。また、酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等の無機絶縁材料を含む材料を用いて形成することができる。層間絶縁層146の形成後には、その表面を、CMPやエッチングなどの方法によって平坦化しておくことが望ましい。

10

#### 【0131】

次に、層間絶縁層146、保護絶縁層144、およびゲート絶縁層138に対し、電極136a、電極136b、電極136c、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bにまで達する開口を形成し、当該開口に埋め込むように導電層148を形成する(図5(B)参照)。上記開口はマスクを用いたエッチングなどの方法で形成することができる。当該マスクは、フォトマスクを用いた露光などの方法によって形成することができる。エッチングとしてはウェットエッチング、ドライエッチングのいずれを用いても良いが、微細加工の観点からは、ドライエッチングを用いることが好適である。導電層148の形成は、PVD法やCVD法などの成膜法を用いて行うことができる。導電層148の形成に用いることができる材料としては、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウムなどの導電性材料や、これらの合金、化合物(例えば窒化物)などが挙げられる。

20

#### 【0132】

具体的には、例えば、開口を含む領域にPVD法によりチタン膜を薄く形成し、CVD法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタングステン膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、下部電極(ここでは、電極136a、電極136b、電極136c、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142b)の表面に生じる酸化膜を還元し、下部電極との接触抵抗を低減させる機能を有する。また、その後の形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや、窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

30

#### 【0133】

導電層148を形成した後には、エッチングやCMPといった方法を用いて導電層148の一部を除去し、層間絶縁層146を露出させて、電極150a、電極150b、電極150c、電極150d、電極150eを形成する(図5(C)参照)。なお、上記導電層148の一部を除去して電極150a、電極150b、電極150c、電極150d、電極150eを形成する際には、表面が平坦になるように加工することが望ましい。このように、層間絶縁層146、電極150a、電極150b、電極150c、電極150d、電極150eの表面を平坦化することにより、後の工程において、良好な電極、配線、絶縁層などを形成することが可能となる。

40

#### 【0134】

さらに、絶縁層152を形成し、絶縁層152に、電極150a、電極150b、電極150c、電極150d、電極150eにまで達する開口を形成し、当該開口に埋め込むように導電層を形成した後、エッチングやCMPなどの方法を用いて導電層の一部を除去し、絶縁層152を露出させて、電極154a、電極154b、電極154c、電極154dを形成する(図5(D)参照)。当該工程は、電極150a等を形成する場合と同様であるから、詳細は省略する。

50

## 【0135】

上述のような方法でトランジスタ162を作製した場合、酸化物半導体層140の水素濃度は $5 \times 10^{-9}$  atoms/cm<sup>3</sup>以下となり、また、トランジスタ162のオフ電流は100zA/μm以下となる。このような、水素濃度が十分に低減されて高純度化された酸化物半導体層140を適用することで、優れた特性のトランジスタ162を得ることができる。また、下部に酸化物半導体以外の材料を用いたトランジスタ160を有し、上部に酸化物半導体を用いたトランジスタ162を有する優れた特性の半導体装置を作製することができる。

## 【0136】

なお、酸化物半導体との比較対象たり得る半導体材料としては、炭化珪素（例えば、4H-SiC）がある。酸化物半導体と4H-SiCはいくつかの共通点を有している。キャリア密度はその一例である。常温での酸化物半導体の真性キャリアは $10^{17}$ /cm<sup>3</sup>程度と見積もられるが、これは、4H-SiCにおける $6.7 \times 10^{11}$ /cm<sup>3</sup>と同様、極めて低い値である。シリコンの真性キャリア密度（ $1.4 \times 10^{10}$ /cm<sup>3</sup>程度）と比較すれば、その程度が並はずれていることが良く理解できる。

## 【0137】

また、酸化物半導体のエネルギー-bandギャップは3.0~3.5eVであり、4H-SiCのエネルギー-bandギャップは3.26eVであるから、ワイドギャップ半導体という点においても、酸化物半導体と炭化珪素とは共通している。

## 【0138】

一方で、酸化物半導体と炭化珪素との間には極めて大きな相違点が存在する。それは、プロセス温度である。炭化珪素は一般に1500~2000の熱処理を必要とするから、他の半導体材料を用いた半導体素子との積層構造は困難である。このような高い温度では、半導体基板や半導体素子などが破壊されてしまうためである。他方、酸化物半導体は、300~500（ガラス転移温度以下、最大でも700程度）の熱処理で作製することが可能であり、他の半導体材料を用いて集積回路を形成した上で、酸化物半導体による半導体素子を形成することが可能となる。

## 【0139】

また、炭化珪素の場合と異なり、ガラス基板など、耐熱性の低い基板を用いることが可能であるという利点を有する。さらに、高温での熱処理が不要という点で、炭化珪素と比較してエネルギーコストを十分に低くすることができるという利点を有する。

## 【0140】

なお、酸化物半導体において、物性研究は多くなされているが、エネルギーギャップ中の局在準位そのものを十分に減らすという思想を含まない。開示する発明の一態様では、局在準位の原因たり得る水や水素を酸化物半導体中より除去することで、高純度化した酸化物半導体を作製する。これは、エネルギーギャップ中の局在準位そのものを十分に減らすという思想に立脚するものである。そして、これによって極めて優れた工業製品の製造を可能とするものである。

## 【0141】

さらに、酸素欠乏により発生する金属の未結合手に対して酸素を供給し、酸素欠陥による局在準位を減少させることにより、いっそう高純度化された（i型の）酸化物半導体とすることも可能である。たとえば、チャネル形成領域に接して酸素過剰の酸化膜を形成し、当該酸化膜から酸素を供給して、酸素欠陥による局在準位を減少させることができる。

## 【0142】

酸化物半導体の欠陥は、過剰な水素による伝導帯下の浅い準位や、酸素の不足による深い準位、などに起因するものとされている。これらの欠陥を無くすために、水素を徹底的に除去し、酸素を十分に供給する。

## 【0143】

酸化物半導体を用いたトランジスタの電導機構

10

20

30

40

50

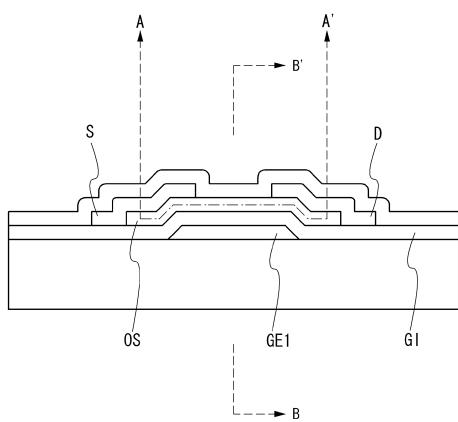

次に、酸化物半導体を用いたトランジスタの電導機構につき、図11乃至図14を用いて説明する。なお、以下の説明では、理解の容易にするため理想的な状況を仮定している。

【0144】

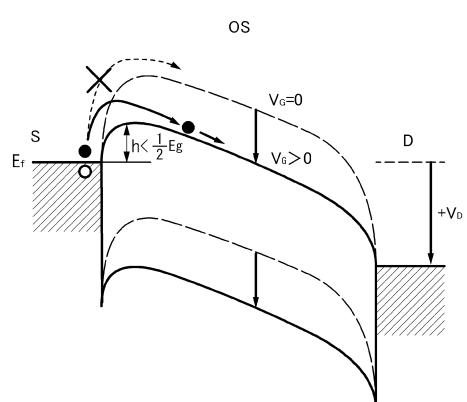

図11は、酸化物半導体を用いた逆スタガー型のトランジスタの断面図である。ゲート電極層(GE1)上にゲート絶縁層(GI)を介して酸化物半導体層(OS)が設けられ、その上にソース電極(S)及びドレイン電極(D)が設けられている。

【0145】

図12(A)、図12(B)には、図11のA-A'上におけるエネルギー・バンド構造の模式図を示す。図12(A)は、ゲート電極層に電圧が印加されず( $V_G = 0$ )、かつ、ドレイン電極、ソース電極のいずれにも電圧を印加しない、または、同じ電圧が印加される場合である( $V_S = V_D = 0$ 、または $V_S = V_D$ )。図12(B)は、ドレイン電極に正の電圧( $V_D > 0$ )を印加した上で、破線はゲート電極層に電圧を印加しない場合( $V_G = 0$ )、実線はゲート電極層に正の電圧( $V_G > 0$ )を印加した場合を示す。ゲート電極層に電圧を印加しない場合は高いポテンシャル障壁のためにソース電極から酸化物半導体側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲート電極層に正の電圧を印加するとポテンシャル障壁が低下し、電流を流すオン状態を示す。

【0146】

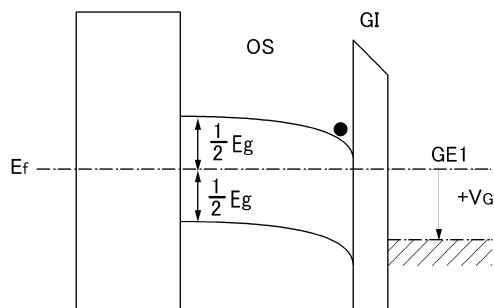

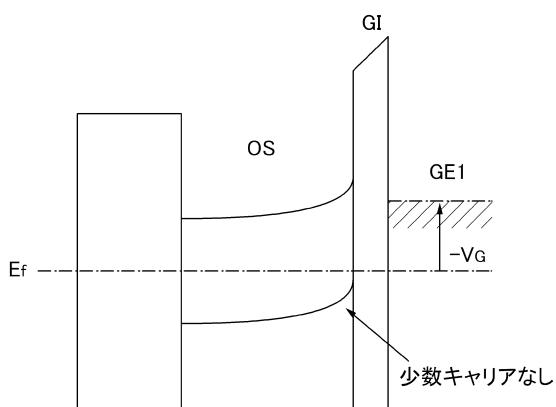

図13(A)、図13(B)には、図11のB-B'の断面におけるエネルギー・バンド図(模式図)を示す。図13(A)は、ゲート電極層(GE1)に正の電位( $V_G > 0$ )が与えられた状態であり、ソース電極とドレイン電極との間にキャリア(電子)が流れるオン状態を示している。また、図13(B)は、ゲート電極層(GE1)に負の電位( $V_G < 0$ )が印加された状態であり、オフ状態(少数キャリアは流れない状態)である場合を示す。

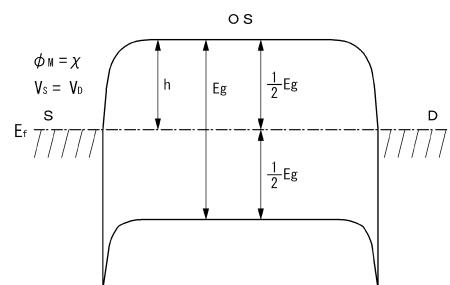

【0147】

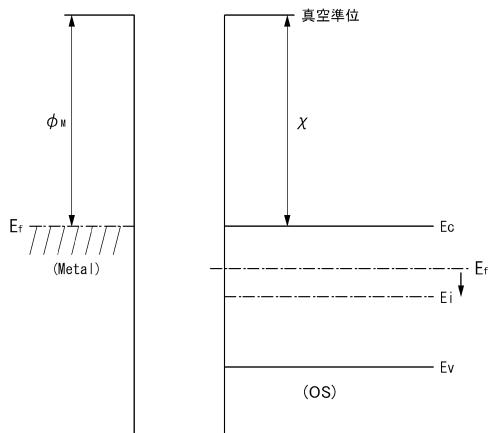

図14は、真空準位と金属の仕事関数( $\phi_M$ )、酸化物半導体の電子親和力( $\phi$ )の関係を示す。

【0148】

金属は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体はn型であり、そのフェルミ準位( $E_f$ )は、バンドギャップ中央に位置する真性フェルミ準位( $E_i$ )から離れて、伝導帯寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなり、n型化する要因の一つであることが知られている。また、酸素欠損もn型化する一つの要因であることが知られている。

【0149】

これに対して開示する発明の一態様に係る酸化物半導体は、n型化の要因である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の元素(不純物元素)が極力含まれないように高純度化し、かつ、酸素欠損を除去することにより真性(i型)とし、または真性に近づけた酸化物半導体である。すなわち、不純物元素を添加してi型化するのではなく、水素や水等の不純物や酸素欠損を極力除去することにより、高純度化されたi型(真性半導体)またはそれに近づけることを特徴としている。これにより、フェルミ準位( $E_f$ )は真性フェルミ準位( $E_i$ )と同程度とすることができます。

【0150】

酸化物半導体のバンドギャップ( $E_g$ )は3.15eVで、電子親和力( $\phi$ )は4.3eVと言われている。ソース電極やドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力( $\phi$ )とほぼ等しい。この場合、金属-酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

【0151】

金属の仕事関数( $\phi_M$ )と酸化物半導体の電子親和力( $\phi$ )が等しい場合、両者が接触すると図12(A)で示すようなエネルギー・バンド図(模式図)が得られる。

【0152】

図12(B)において黒丸(●)は電子を示す。ドレイン電極に正の電位が与えられると

10

20

30

40

50

、電子はバリア (  $h$  ) をこえて酸化物半導体に注入され、ドレイン電極に向かって流れる。バリア (  $h$  ) の高さは、ゲート電圧 (  $V_G$  ) に依存して変化するが、正のドレイン電圧がドレイン電極に印加される場合には、電圧印加のない図 12 ( A ) のバリアの高さ、すなわちバンドギャップ (  $E_g$  ) の  $1/2$  、より低くなる。

【 0153 】

このとき電子は、図 13 ( A ) で示すように、ゲート絶縁層と高純度化された酸化物半導体との界面付近 ( 酸化物半導体のエネルギー的に安定な最低部 ) を移動する。

【 0154 】

また、図 13 ( B ) に示すように、ゲート電極 ( G E 1 ) に負の電位が与えられると、少數キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

【 0155 】

例えば、室温 ( 25 ) におけるオフ電流が、 $10 z A / \mu m$  ( $1 \times 10^{-20} A / \mu m$ ) 以下、あるいは  $1 z A / \mu m$  ( $1 \times 10^{-21} A / \mu m$ ) 以下であり、このため、サブスレッショルドスイング値 ( S 値 ) が  $0.1 V / dec.$  のトランジスタが得られる。

【 0156 】

このように、酸化物半導体の主成分以外の不純物が極力含まれないように酸化物半導体を高純度化させることにより、トランジスタの動作を良好なものとすることができます。

【 0157 】

< 变形例 >

図 6 乃至図 9 には、半導体装置の構成の変形例を示す。なお、以下では、変形例として、トランジスタ 162 の構成が上記とは異なるものについて説明する。つまり、トランジスタ 160 の構成は上記と同様である。

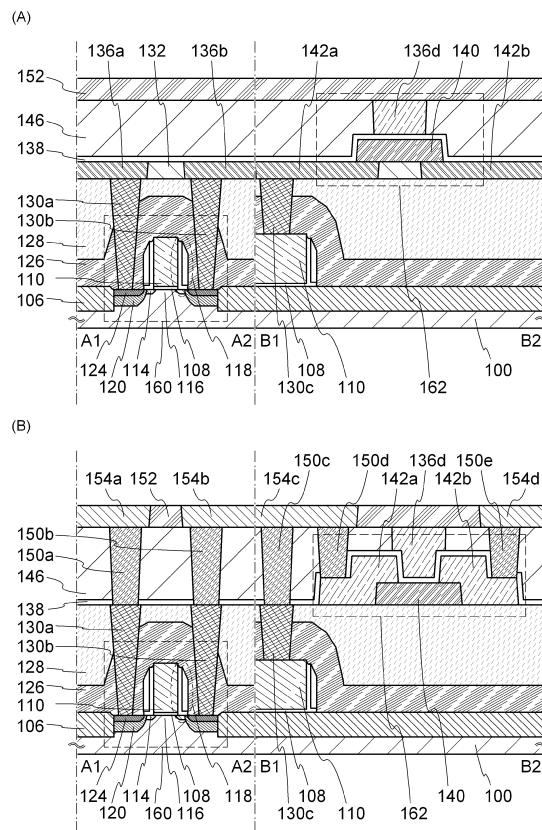

【 0158 】

図 6 には、酸化物半導体層 140 の下にゲート電極 136d を有し、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b が、酸化物半導体層 140 の下側表面において酸化物半導体層 140 と接する構成のトランジスタ 162 を有する例を示す。なお、平面の構造は、断面に対応して適宜変更すればよいかから、ここでは、断面についてのみ示すこととする。

【 0159 】

図 6 に示す構成と図 2 に示す構成の大きな相違点として、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b と、酸化物半導体層 140 との接続の位置がある。つまり、図 2 に示す構成では、酸化物半導体層 140 の上側表面において、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b と接するのに対して、図 6 に示す構成では、酸化物半導体層 140 の下側表面において、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b と接する。そして、この接触の相違に起因して、その他の電極、絶縁層などの配置が異なるものとなっている。各構成要素の詳細は、図 2 と同様である。

【 0160 】

具体的には、層間絶縁層 128 上に設けられたゲート電極 136d と、ゲート電極 136d 上に設けられたゲート絶縁層 138 と、ゲート絶縁層 138 上に設けられた、ソース電極またはドレイン電極 142a 、ソース電極またはドレイン電極 142b と、ソース電極またはドレイン電極 142a 、ソース電極またはドレイン電極 142b の上側表面に接する酸化物半導体層 140 と、を有する。

【 0161 】

ここで、ゲート電極 136d は、層間絶縁層 128 上に形成された絶縁層 132 に、埋め込まれるように設けられている。また、ゲート電極 136d と同様に、ソース電極またはドレイン電極 130a に接して電極 136a が、ソース電極またはドレイン電極 130b に接して電極 136b が、電極 130c に接して電極 136c が、それぞれ形成されている。

10

20

30

40

50

## 【0162】

また、トランジスタ162の上には、酸化物半導体層140の一部と接するように、保護絶縁層144が設けられており、保護絶縁層144上には層間絶縁層146が設けられている。ここで、保護絶縁層144および層間絶縁層146には、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bにまで達する開口が設けられており、当該開口を通じて、電極150d、電極150eが、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bに接して形成されている。また、電極150d、電極150eと同様に、ゲート絶縁層138、保護絶縁層144、層間絶縁層146に設けられた開口を通じて、電極136a、電極136b、電極136cに接する電極150a、電極150b、電極150cが形成されている。

10

## 【0163】

また、層間絶縁層146上には絶縁層152が設けられており、当該絶縁層152に埋め込まれるように、電極154a、電極154b、電極154c、電極154dが設けられている。ここで、電極154aは電極150aと接しており、電極154bは電極150bと接しており、電極154cは電極150cおよび電極150dと接しており、電極154dは電極150eと接している。

## 【0164】

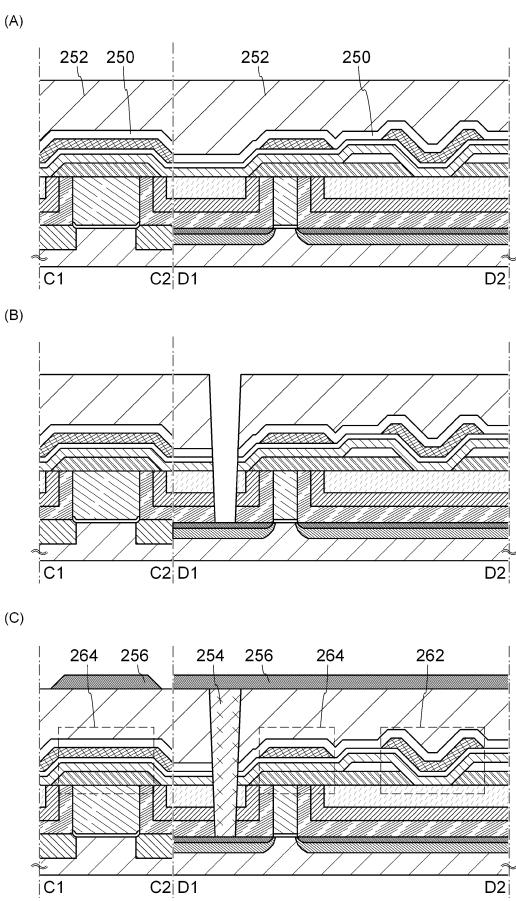

図7は、酸化物半導体層140の上にゲート電極136dを有する構成の例である。ここで、図7(A)は、ソース電極またはドレイン電極142aや、ソース電極またはドレイン電極142bが、酸化物半導体層140の下側表面において酸化物半導体層140と接する構成の例であり、図7(B)は、ソース電極またはドレイン電極142aや、ソース電極またはドレイン電極142bが、酸化物半導体層140の上側表面において酸化物半導体層140と接する構成の例である。

20

## 【0165】

図2や図6に示す構成と図7に示す構成の大きな相違点は、酸化物半導体層140の上にゲート電極136dを有する点である。また、図7(A)に示す構成と図7(B)に示す構成の大きな相違点は、ソース電極またはドレイン電極142aや、ソース電極またはドレイン電極142bが、酸化物半導体層140の下側表面または上側表面のいずれにおいて接触するか、という点である。そして、これらの相違に起因して、その他の電極、絶縁層などの配置が異なるものとなっている。各構成要素の詳細は、図2などと同様である。

30

## 【0166】

具体的には、図7(A)では、層間絶縁層128上に設けられたソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bと、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bの上側表面に接する酸化物半導体層140と、酸化物半導体層140上に設けられたゲート絶縁層138と、ゲート絶縁層138上の酸化物半導体層140と重畳する領域のゲート電極136dと、を有する。

## 【0167】

また、図7(B)では、層間絶縁層128上に設けられた酸化物半導体層140と、酸化物半導体層140の上側表面に接するように設けられたソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bと、酸化物半導体層140、ソース電極またはドレイン電極142a、および、ソース電極またはドレイン電極142b上に設けられたゲート絶縁層138と、ゲート絶縁層138上の酸化物半導体層140と重畳する領域のゲート電極136dと、を有する。

40

## 【0168】

なお、図7に示す構成では、図2に示す構成などと比較して、構成要素が省略できる場合がある（例えば、電極150aや、電極154aなど）。この場合、作製工程の簡略化という副次的な効果も得られる。もちろん、図2などに示す構成においても、必須ではない構成要素を省略できることはいうまでもない。

## 【0169】

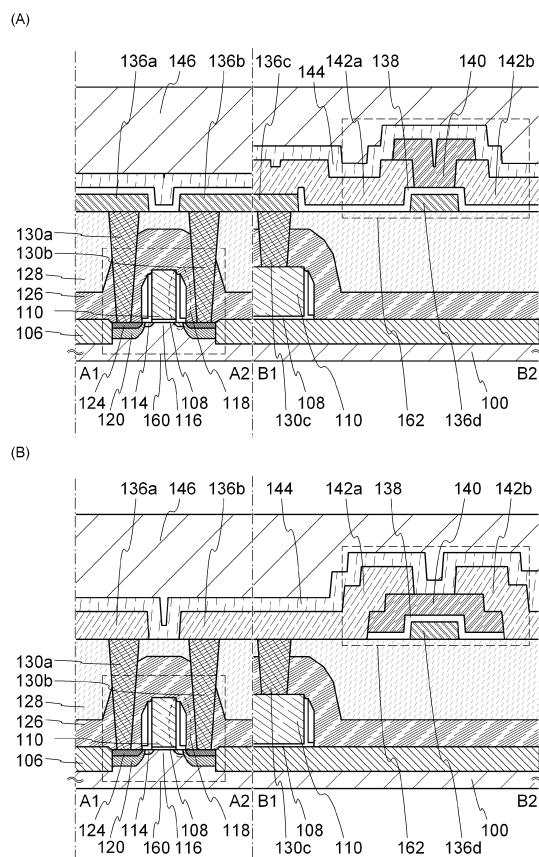

図8は、素子のサイズが比較的大きい場合であって、酸化物半導体層140の下にゲート

50

電極 136d を有する構成の例である。この場合、表面の平坦性やカバレッジに対する要求は比較的緩やかなものであるから、配線や電極などを絶縁層中に埋め込むように形成する必要はない。例えば、導電層の形成後にパターニングを行うことで、ゲート電極 136dなどを形成することが可能である。なお、ここでは図示しないが、トランジスタ 160についても、同様に作製することが可能である。

【0170】

図 8 (A) に示す構成と図 8 (B) に示す構成の大きな相違点は、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b が、酸化物半導体層 140 の下側表面または上側表面のいずれにおいて接触するか、という点である。そして、これらの相違に起因して、他の電極、絶縁層などの配置が異なるものとなっている。各構成要素の詳細は、図 2 などと同様である。

10

【0171】

具体的には、図 8 (A) では、層間絶縁層 128 上に設けられたゲート電極 136d と、ゲート電極 136d 上に設けられたゲート絶縁層 138 と、ゲート絶縁層 138 上に設けられた、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b と、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b の上側表面に接する酸化物半導体層 140 と、を有する。

【0172】

また、図 8 (B) では、層間絶縁層 128 上に設けられたゲート電極 136d と、ゲート電極 136d 上に設けられたゲート絶縁層 138 と、ゲート絶縁層 138 上のゲート電極 136d と重畳する領域に設けられた酸化物半導体層 140 と、酸化物半導体層 140 の上側表面に接するように設けられたソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b と、を有する。

20

【0173】

なお、図 8 に示す構成においても、図 2 に示す構成などと比較して、構成要素が省略できる場合がある。この場合も、作製工程の簡略化という効果が得られる。

【0174】

図 9 は、素子のサイズが比較的大きい場合であって、酸化物半導体層 140 の上にゲート電極 136d を有する構成の例である。この場合にも、表面の平坦性やカバレッジに対する要求は比較的緩やかなものであるから、配線や電極などを絶縁層中に埋め込むように形成する必要はない。例えば、導電層の形成後にパターニングを行うことで、ゲート電極 136dなどを形成することが可能である。なお、ここでは図示しないが、トランジスタ 160についても、同様に作製することが可能である。

30

【0175】

図 9 (A) に示す構成と図 9 (B) に示す構成の大きな相違点は、ソース電極またはドレイン電極 142a や、ソース電極またはドレイン電極 142b が、酸化物半導体層 140 の下側表面または上側表面のいずれにおいて接触するか、という点である。そして、これらの相違に起因して、他の電極、絶縁層などの配置が異なるものとなっている。各構成要素の詳細は、図 2 などと同様である。

【0176】

40

具体的には、図 9 (A) では、層間絶縁層 128 上に設けられたソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b と、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b の上側表面に接する酸化物半導体層 140 と、ソース電極またはドレイン電極 142a、ソース電極またはドレイン電極 142b、酸化物半導体層 140 上に設けられたゲート絶縁層 138 と、ゲート絶縁層 138 上の酸化物半導体層 140 と重畳する領域に設けられたゲート電極 136d と、を有する。

【0177】

また、図 9 (B) では、層間絶縁層 128 上に設けられた酸化物半導体層 140 と、酸化物半導体層 140 の上側表面に接するように設けられたソース電極またはドレイン電極 1

50

42a、ソース電極またはドレイン電極142bと、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142b、酸化物半導体層140上に設けられたゲート絶縁層138と、ゲート絶縁層138上の酸化物半導体層140と重畠する領域に設けられたゲート電極136dと、を有する。

【0178】

なお、図9に示す構成においても、図2に示す構成などと比較して、構成要素が省略できる場合がある。この場合も、作製工程の簡略化という効果が得られる。

【0179】

以上に示したように、開示する発明の一態様によって、新たな構成の半導体装置が実現される。本実施の形態では、トランジスタ160とトランジスタ162を積層して形成する例について説明したが、半導体装置の構成はこれに限られるものではない。また、本実施の形態では、トランジスタ160とトランジスタ162のチャネル長方向が互いに垂直となる例を説明したが、トランジスタ160とトランジスタ162の位置関係などはこれに限られるものではない。さらに、トランジスタ160とトランジスタ162とを重畠して設けても良い。

10

【0180】

また、本実施の形態では理解の簡単のため、最小記憶単位(1ビット)の半導体装置について説明したが、半導体装置の構成はこれに限られるものではない。複数の半導体装置を適当に接続して、より高度な半導体装置を構成することもできる。例えば、上記半導体装置を複数用いて、NAND型やNOR型の半導体装置を構成することが可能である。配線の構成も図1に限定されず、適宜変更することができる。

20

【0181】

本実施の形態に係る半導体装置は、トランジスタ162の低オフ電流特性により、極めて長時間にわたり情報を保持することが可能である。つまり、DRAMなどで必要とされるリフレッシュ動作が不要であり、消費電力を抑制することができる。また、実質的な不揮発性の半導体装置として用いることが可能である。

【0182】

また、トランジスタ162のスイッチング動作によって情報の書き込みなどを行うため、高い電圧を必要とせず、素子の劣化の問題もない。さらに、トランジスタのオン、オフによって、情報の書き込みや消去が行われるため、高速動作も容易に実現しうる。また、トランジスタに入力する電位を制御することで直接情報を書き換えることが可能であるため、情報を消去するための動作が不要であるというメリットもある。

30

【0183】

また、酸化物半導体以外の材料を用いたトランジスタは、酸化物半導体を用いたトランジスタと比較して、さらなる高速動作が可能なため、これを用いることにより、記憶内容の読み出しを高速に行うことが可能である。

【0184】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0185】

40

(実施の形態2)

本実施の形態では、開示する発明の別の一態様に係る半導体装置の構成および作製方法について、図15を参照して説明する。

【0186】

図15(A)には、半導体装置の回路構成の一例を示す。図1との相違は、容量素子164の有無である。すなわち、図15(A)において、トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ160のゲート電極と、は電気的に接続されている。また、第1の配線(1st Line:ソース線BLとも呼ぶ)とトランジスタ160のソース電極とは、電気的に接続され、第2の配線(2nd Line:ビット線BLとも呼ぶ)とトランジスタ160のドレイン電極とは

50

、電気的に接続されている。また、第3の配線(3rd Line:第1の信号線S1とも呼ぶ)とトランジスタ162のソース電極またはドレイン電極の他方とは、電気的に接続され、第4の配線(4th Line:第2の信号線S2とも呼ぶ)と、トランジスタ162のゲート電極とは、電気的に接続されている。そして、第5の配線(5th Line:ワード線WLとも呼ぶ)と、容量素子164の電極の他方は電気的に接続されている。なお、図15においては、酸化物半導体を用いたトランジスタであることを示すために、OSの符号を併せて付している。

#### 【0187】

ここで、トランジスタ162には、上述の酸化物半導体を用いたトランジスタが適用される。酸化物半導体を用いたトランジスタは、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、トランジスタ160のゲート電極の電位を極めて長時間にわたって保持することが可能である。そして、容量素子164を有することにより、トランジスタ160のゲート電極に与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易になる。

10

#### 【0188】

なお、トランジスタ160については特に限定されない。情報の読み出し速度を向上させるという観点からは、例えば、単結晶シリコンを用いたトランジスタなど、スイッチング速度の高いトランジスタを適用するのが好適である。

#### 【0189】

図15(A)に示す半導体装置では、トランジスタ160のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

20

#### 【0190】

はじめに、情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極、および容量素子164に与えられる。すなわち、トランジスタ160のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位を与える電荷(以下、低電位を与える電荷を電荷Q<sub>L</sub>、高電位を与える電荷を電荷Q<sub>H</sub>という)のいずれかがトランジスタ160のゲート電極に与えられるものとする。なお、異なる三つまたはそれ以上の電位を与える電荷を適用して、記憶容量を向上させても良い。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極に与えられた電荷が保持される(保持)。

30

#### 【0191】

トランジスタ162のオフ電流は極めて小さいから、トランジスタ160のゲート電極の電荷は長時間にわたって保持される。

#### 【0192】

次に、情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ160のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ160をnチャネル型とすると、トランジスタ160のゲート電極にQ<sub>H</sub>が与えられている場合の見かけのしきい値V<sub>th\_H</sub>は、トランジスタ160のゲート電極にQ<sub>L</sub>が与えられている場合の見かけのしきい値V<sub>th\_L</sub>より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ160を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をV<sub>th\_H</sub>とV<sub>th\_L</sub>の中間の電位V<sub>0</sub>とすることにより、トランジスタ160のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいて、Q<sub>H</sub>が与えられていた場合には、第5の配線の電位がV<sub>0</sub>(>V<sub>th\_H</sub>)となれば、トランジスタ160は「オン状態」となる。Q<sub>L</sub>が与えられていた場合には、第5の配線の電位がV<sub>0</sub>(<V<sub>th\_L</sub>)となっても、トランジスタ160は「オフ状態」のままである。このため、第2の配線の電位を見ること

40

50

で、保持されている情報を読み出すことができる。

【0193】

なお、メモリセルをアレイ状に配置して用いる場合には、所望のメモリセルの情報のみを読み出せることが必要になる。このように、所定のメモリセルの情報を読み出し、それ以外のメモリセルの情報を読み出さない場合には、読み出しの対象ではないメモリセルの第5の配線に対して、ゲート電極の状態にかかわらずトランジスタ160が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を与える。または、ゲート電極の状態にかかわらずトランジスタ160が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線に与えればよい。

【0194】

次に、情報の書き換えについて説明する。情報の書き換えは、上記情報の書き込みおよび保持と同様に行われる。つまり、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位（新たな情報に係る電位）が、トランジスタ160のゲート電極および容量素子164に与えられる。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極は、新たな情報に係る電荷が与えられた状態となる。

【0195】

このように、開示する発明に係る半導体装置は、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる高電圧を用いてのフローティングゲートからの電荷の引き抜きが不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、半導体装置の高速動作が実現される。

【0196】

なお、トランジスタ162のソース電極またはドレイン電極は、トランジスタ160のゲート電極と電気的に接続されることにより、不揮発性メモリ素子として用いられるフローティングゲート型トランジスタのフローティングゲートと同等の作用を奏する。このため、図中、トランジスタ162のソース電極またはドレイン電極とトランジスタ160のゲート電極が電気的に接続される部位をフローティングゲート部FGと呼ぶ場合がある。トランジスタ162がオフの場合、当該フローティングゲート部FGは絶縁体中に埋設されたと見ることができ、フローティングゲート部FGには電荷が保持される。酸化物半導体を用いたトランジスタ162のオフ電流は、シリコン半導体などで形成されるトランジスタの10万分の1以下であるため、トランジスタ162のリークによる、フローティングゲート部FGに蓄積される電荷の消失を無視することが可能である。つまり、酸化物半導体を用いたトランジスタ162により、電力の供給が無くても情報の保持が可能な不揮発性の記憶装置を実現することが可能である。

【0197】

例えば、トランジスタ162の室温（25）でのオフ電流が10zA（1zA（ゼットアンペア）は $1 \times 10^{-21} A$ ）以下であり、容量素子164の容量値が10fF程度である場合には、少なくとも $10^4$ 秒以上のデータ保持が可能である。なお、当該保持時間が、トランジスタ特性や容量値によって変動することはいうまでもない。

【0198】

また、この場合、従来のフローティングゲート型トランジスタにおいて指摘されているゲート絶縁膜（トンネル絶縁膜）の劣化という問題が存在しない。つまり、従来問題とされていた、電子をフローティングゲートに注入する際のゲート絶縁膜の劣化を解消することができる。これは、原理的な書き込み回数の制限が存在しないことを意味するものである。また、従来のフローティングゲート型トランジスタにおいて書き込みや消去の際に必要であった高電圧も不要である。

【0199】

図15(A)に示す半導体装置は、当該半導体装置を構成するトランジスタなどの要素が

10

20

30

40

50

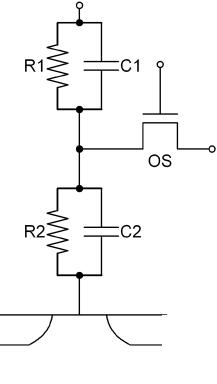

抵抗および容量を含むものとして、図15(B)のように考えることが可能である。つまり、図15(B)では、トランジスタ160および容量素子164が、それぞれ、抵抗および容量を含んで構成されると考えていることになる。R1およびC1は、それぞれ、容量素子164の抵抗値および容量値であり、抵抗値R1は、容量素子164を構成する絶縁層による抵抗値に相当する。また、R2およびC2は、それぞれ、トランジスタ160の抵抗値および容量値であり、抵抗値R2はトランジスタ160がオン状態の時のゲート絶縁層による抵抗値に相当し、容量値C2はいわゆるゲート容量(ゲート電極と、ソース電極またはドレイン電極との間に形成される容量、及び、ゲート電極とチャネル形成領域との間に形成される容量)の容量値に相当する。

## 【0200】

10

トランジスタ162がオフ状態にある場合のソース電極とドレイン電極の間の抵抗値(実効抵抗とも呼ぶ)をROSとすると、トランジスタ162のゲートリークが十分に小さい条件において、R1およびR2が、R1 ROS、R2 ROSを満たす場合には、電荷の保持期間(情報の保持期間ということもできる)は、主としてトランジスタ162のオフ電流によって決定されることになる。

## 【0201】

逆に、当該条件を満たさない場合には、トランジスタ162のオフ電流が十分に小さくとも、保持期間を十分に確保することが困難になる。トランジスタ162のオフ電流以外のリーク電流(例えば、ソース電極とゲート電極の間に生じるリーク電流等)が大きいためである。このことから、本実施の形態において開示する半導体装置は、上述の関係を満たすものであることが望ましいといえる。

20

## 【0202】

一方で、C1とC2は、C1 C2の関係を満たすことが望ましい。C1を大きくすることで、第5の配線によってフローティングゲート部FGの電位を制御する際(例えば、読み出しの際)に、第5の配線の電位の変動を低く抑えることができるためである。

## 【0203】

上述の関係を満たすことで、より好適な半導体装置を実現することが可能である。なお、R1およびR2は、トランジスタ160のゲート絶縁層や容量素子164の絶縁層によって制御される。C1およびC2についても同様である。よって、ゲート絶縁層の材料や厚さなどを適宜設定し、上述の関係を満たすようにすることが望ましい。

30

## 【0204】

本実施の形態で示す半導体装置においては、フローティングゲート部FGが、フラッシュメモリ等のフローティングゲート型のトランジスタのフローティングゲートと同等の作用をするが、本実施の形態のフローティングゲート部FGは、フラッシュメモリ等のフローティングゲートと本質的に異なる特徴を有する。フラッシュメモリでは、コントロールゲートに印加される電圧が高いため、その電位の影響が、隣接するセルのフローティングゲートにおよぶことを防ぐために、セルとセルとの間隔をある程度保つ必要が生じる。このことは、半導体装置の高集積化を阻害する要因の一つである。そして、当該要因は、高電界をかけてトンネル電流を発生させるというフラッシュメモリの根本的な原理に起因するものである。

40

## 【0205】

また、フラッシュメモリの上記原理によって、絶縁膜の劣化が進行し、書き換え回数の限界(10<sup>4</sup> ~ 10<sup>5</sup>回程度)という別の問題も生じる。

## 【0206】

開示する発明に係る半導体装置は、酸化物半導体を用いたトランジスタのスイッチングによって動作し、上述のようなトンネル電流による電荷注入の原理を用いない。すなわち、フラッシュメモリのような、電荷を注入するための高電界が不要である。これにより、隣接セルに対する、コントロールゲートによる高電界の影響を考慮する必要がないため、高集積化が容易になる。

## 【0207】

50

また、トンネル電流による電荷の注入を用いないため、メモリセルの劣化の原因が存在しない。つまり、フラッシュメモリと比較して高い耐久性および信頼性を有することになる。

【0208】

また、高電界が不要であり、大型の周辺回路（昇圧回路など）が不要である点も、フラッシュメモリに対するアドバンテージである。

【0209】

なお、C1を構成する絶縁層の比誘電率  $r_1$  と、C2を構成する絶縁層の比誘電率  $r_2$  とを異なる場合には、C1の面積  $S_1$  と、C2の面積  $S_2$  とが、 $2 \cdot S_2 = S_1$  ( 望ましくは  $S_2 = S_1$  ) を満たしつつ、C1 = C2を実現することが容易である。具体的には、例えば、C1においては、酸化ハフニウムなどのh i g h - k 材料でなる膜、または酸化ハフニウムなどのh i g h - k 材料でなる膜と酸化物半導体でなる膜との積層構造を採用して  $r_1$  を10以上、好ましくは15以上とし、C2においては、酸化シリコンを採用して、 $r_2 = 3 \sim 4$  とすることができる。このような構成を併せて用いることで、開示する発明に係る半導体装置の高集積化が可能である。

【0210】

なお、上記説明は、n型トランジスタ（nチャネル型トランジスタ）を用いる場合についてのものであるが、n型トランジスタに代えて、p型トランジスタを用いることができるのはいうまでもない。

【0211】

以上示したように、開示する発明の一態様の半導体装置は、オフ状態でのソースとドレイン間のリーク電流（オフ電流）が少ない書き込み用トランジスタ、当該書き込み用トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有している。

【0212】

書き込み用トランジスタのオフ電流は、室温（例えば、25°C）で  $100 \text{ zA}$  ( $1 \times 10^{-19} \text{ A}$ ) 以下、好ましくは  $10 \text{ zA}$  ( $1 \times 10^{-20} \text{ A}$ ) 以下、さらに好ましくは、 $1 \text{ zA}$  ( $1 \times 10^{-21} \text{ A}$ ) 以下である。通常のシリコン半導体では、上述のように低いオフ電流を得ることは困難であるが、酸化物半導体を適切な条件で加工して得られたトランジスタにおいては達成しうる。このため、書き込み用トランジスタとして、酸化物半導体を含むトランジスタを用いることが好ましい。

【0213】

さらに酸化物半導体を用いたトランジスタはサブスレッショルドスイッチング値（S値）が小さいため、比較的移動度が低くてもスイッチング速度を十分大きくすることが可能である。よって、当該トランジスタを書き込み用トランジスタとして用いることで、フローティングゲート部FGに与えられる書き込みパルスの立ち上がりを極めて急峻にことができる。また、オフ電流が小さいため、フローティングゲート部FGに保持させる電荷量を少なくすることが可能である。つまり、酸化物半導体を用いたトランジスタを書き込み用トランジスタとして用いることで、情報の書き換えを高速に行うことができる。

【0214】

読み出し用トランジスタとしては、読み出しの速度を高くするために、高速で動作するトランジスタを用いるのが望ましい。例えば、読み出し用トランジスタとしてスイッチング速度が1ナノ秒以下のトランジスタを用いるのが好ましい。

【0215】

メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたフローティングゲート部FGに電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、フローティングゲート部FGに所定量の電荷を保持させることで行う。ここで、書き込み用トランジスタのオフ電流は極めて小さいため、フローティングゲート部FGに供給

10

20

30

40

50

された電荷は長時間にわたって保持される。オフ電流が例えば実質的に 0 であれば、従来の D R A M で必要とされたリフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低く（例えば、一ヶ月乃至一年に一度程度）することが可能となり、半導体装置の消費電力を十分に低減することができる。

【 0 2 1 6 】

また、メモリセルへの再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる消去動作が不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、半導体装置の高速動作が実現される。また、従来のフローティングゲート型トランジスタで書き込みや消去の際に必要とされた高い電圧を必要としないため、半導体装置の消費電力をさらに低減することができる。本実施の形態に係るメモリセルに印加される電圧（メモリセルの各端子に同時に印加される電位の最大のものと最小のものの差）の最大値は、2段階（1ビット）の情報を書き込む場合、一つのメモリセルにおいて、5 V 以下、あるいは 3 V 以下にすることができる。

10

【 0 2 1 7 】

開示する発明に係る半導体装置に配置されるメモリセルは、書き込み用トランジスタと、読み出し用トランジスタと、を少なくとも含んでいればよいため、例えば、1メモリセルあたり 6 つのトランジスタを必要とする S R A M と比較して、メモリセルあたりの面積を十分に小さくすることが可能である。つまり、半導体装置においてメモリセルを高密度に配置することができる。

20

【 0 2 1 8 】

また、従来のフローティングゲート型トランジスタでは、書き込み時にゲート絶縁膜（トンネル絶縁膜）中を電荷が移動するために、当該ゲート絶縁膜（トンネル絶縁膜）の劣化が不可避であった。しかしながら、本発明の一態様に係るメモリセルにおいては、書き込み用トランジスタのスイッチング動作により情報の書き込みがなされるため、ゲート絶縁膜の劣化の問題がない。これは、原理的な書き込み回数の制限が存在せず、書き換え耐性が極めて高いことを意味するものである。例えば、本発明の一態様に係るメモリセルは、 $1 \times 10^9$  回（10億回）以上の書き込み後であっても、電流 - 電圧特性に劣化が見られない。

30

【 0 2 1 9 】

さらに、メモリセルの書き込み用トランジスタとして酸化物半導体を用いたトランジスタを用いる場合、酸化物半導体は一般にエネルギーギャップが大きく（例えば、In - Ga - Zn - O 系の場合  $3.0 \sim 3.5$  eV）熱励起キャリアが極めて少ないこともあり、例えば、150 もの高温環境下でもメモリセルの電流 - 電圧特性に劣化が見られない。

【 0 2 2 0 】

上述のような優れた特性を有するトランジスタをメモリセルの書き込み用トランジスタとして適用することで、従来にない特徴を有する半導体装置を提供することができる。

【 0 2 2 1 】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

40

【 0 2 2 2 】

（実施の形態 3 ）

本実施の形態では、開示する発明の一態様に係る半導体装置の応用例について、図 16 乃至図 21 を用いて説明する。

【 0 2 2 3 】

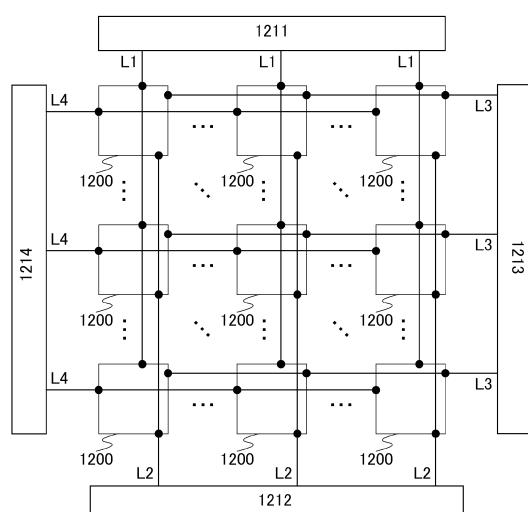

図 16 には、本実施の形態にかかる半導体装置の概略を示す。

【 0 2 2 4 】

図 16 は、図 1 または図 15 (A) に示す半導体装置（以下、メモリセル 1200 とも記載する。）を複数用いて形成される半導体装置の回路図の例である。

【 0 2 2 5 】

50

図16に示す半導体装置は、複数のメモリセル1200がマトリクス状に配置されたメモリセルアレイと、第1の駆動回路1211と、第2の駆動回路1212と、第3の駆動回路1213と、第4の駆動回路1214と、第1の駆動回路1211と電気的に接続された、複数の配線L1と、第2の駆動回路1212と電気的に接続された、複数の配線L2と、第3の駆動回路1213と電気的に接続された、複数の配線L3と、第4の駆動回路1214と電気的に接続された、複数の配線L4と、を有する。

【0226】

図16に示すように、各メモリセル1200には、配線L1、配線L2、配線L3および配線L4が電気的に接続される。これにより、各メモリセル1200を第1の駆動回路1211、第2の駆動回路1212、第3の駆動回路1213および第4の駆動回路1214を用いて、メモリセルの動作を制御することができる。また、各メモリセル1200をマトリクス状に配置し、各配線L1、L2、L3、L4を行方向または列方向の格子状に設けることにより、半導体装置の書き込み動作および読み出し動作を、メモリセル1200の行ごとまたは列ごとに行うこともできる。

【0227】

なお、図16に示すメモリセル1200は、第1の駆動回路1211乃至第4の駆動回路1214からそれ一本ずつ配線が電気的に接続されているが、開示する発明はこれに限定されない。いずれか一、または複数の駆動回路から複数本の配線がメモリセル1200に電気的に接続されても良い。また、いずれか一、または複数のメモリセル1200に、いずれか一、または複数の駆動回路の配線が電気的に接続されないような構成としても良い。

【0228】

また、図16に示す半導体装置では、第1の駆動回路1211、第2の駆動回路1212、第3の駆動回路1213、第4の駆動回路1214は、それぞれ独立に設けているが、開示する発明はこれに限定されない。いずれか一、または複数の機能を有する駆動回路を用いても良い。なお、駆動回路は、十分な動作速度を確保するために、単結晶系の半導体材料を用いて形成されることが望ましい。例えば、バルクシリコン（いわゆるシリコンウェハ）を用いたものにすると良い。

【0229】

次に、より具体的な構成例について説明する。

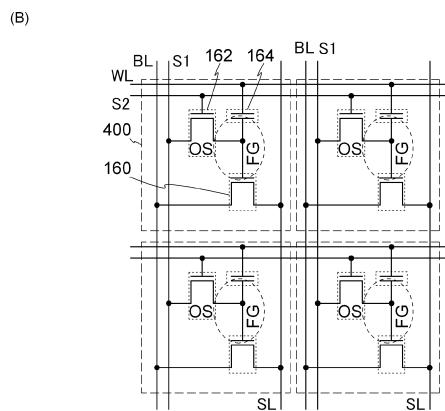

【0230】

図17(A)および図17(B)は、図15(A)に示す半導体装置（以下、メモリセル400とも記載する。）を複数用いて形成される半導体装置の回路図の例である。図17(A)は、メモリセル400が直列に接続された、いわゆるNAND型の半導体装置の回路図であり、図17(B)は、メモリセル400が並列に接続された、いわゆるNOR型の半導体装置の回路図である。

【0231】

図17(A)に示す半導体装置は、ソース線SL、ビット線BL、第1信号線S1、複数本の第2信号線S2、複数本のワード線WL、複数のメモリセル400を有する。図17(A)では、ソース線SLおよびビット線BLを1本ずつ有する構成となっているが、これに限られることなく、ソース線SLおよびビット線BLを複数本有する構成としてもよい。

【0232】

各メモリセル400において、トランジスタ160のゲート電極と、トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続されている。また、第1信号線S1とトランジスタ162のソース電極またはドレイン電極の他方とは、電気的に接続され、第2信号線S2と、トランジスタ162のゲート電極とは、電気的に接続されている。そして、ワード線WLと、容量素子164の電極の他方は電気的に接続されている。

【0233】

10

20

30

40

50

また、メモリセル400が有するトランジスタ160のソース電極は、隣接するメモリセル400のトランジスタ160のドレイン電極と電気的に接続され、メモリセル400が有するトランジスタ160のドレイン電極は、隣接するメモリセル400のトランジスタ160のソース電極と電気的に接続される。ただし、直列に接続された複数のメモリセルのうち、一方の端に設けられたメモリセル400が有するトランジスタ160のドレイン電極は、ビット線BLと電気的に接続される。また、直列に接続された複数のメモリセルのうち、他方の端に設けられたメモリセル400が有するトランジスタ160のソース電極は、ソース線SLと電気的に接続される。

【0234】

図17(A)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は次のように行われる。書き込みを行う行の第2の信号線S2にトランジスタ162がオン状態となる電位を与え、書き込みを行う行のトランジスタ162をオン状態にする。これにより、指定した行のトランジスタ160のゲート電極に第1の信号線S1の電位が与えられ、当該ゲート電極に所定の電荷が与えられる。このようにして、指定した行のメモリセルにデータを書き込むことができる。

10

【0235】

また、読み出し動作は次のように行われる。まず、読み出しを行う行以外のワード線WLに、トランジスタ160のゲート電極に与えられた電荷によらず、トランジスタ160がオン状態となるような電位を与え、読み出しを行う行以外のトランジスタ160をオン状態とする。それから、読み出しを行う行のワード線WLに、トランジスタ160のゲート電極が有する電荷によって、トランジスタ160のオン状態またはオフ状態が選択されるような電位(読み出し電位)を与える。そして、ソース線SLに定電位を与え、ビット線BLに接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL-ビット線BL間の複数のトランジスタ160は、読み出しを行う行を除いてオン状態となっているため、ソース線SL-ビット線BL間のコンダクタンスは、読み出しを行う行のトランジスタ160の状態(オン状態またはオフ状態)によって決定される。読み出しを行う行のトランジスタ160のゲート電極が有する電荷によって、トランジスタのコンダクタンスは異なるから、それに応じて、ビット線BLの電位は異なる値をとることになる。ビット線BLの電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

20

【0236】

図17(B)に示す半導体装置は、ソース線SL、ビット線BL、第1信号線S1、第2信号線S2、およびワード線WLをそれぞれ複数本有し、複数のメモリセル400を有する。各トランジスタ160のゲート電極と、トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続されている。また、ソース線SLとトランジスタ160のソース電極とは、電気的に接続され、ビット線BLとトランジスタ160のドレイン電極とは、電気的に接続されている。また、第1信号線S1とトランジスタ162のソース電極またはドレイン電極の他方とは、電気的に接続され、第2信号線S2と、トランジスタ162のゲート電極とは、電気的に接続されている。そして、ワード線WLと、容量素子164の電極の他方は電気的に接続されている。

30

【0237】

図17(B)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は、上述の図17(A)に示す半導体装置と同様の方法で行われる。読み出し動作は次のように行われる。まず、読み出しを行う行以外のワード線WLに、トランジスタ160のゲート電極に与えられた電荷によらず、トランジスタ160がオフ状態となるような電位を与え、読み出しを行う行以外のトランジスタ160をオフ状態とする。それから、読み出しを行う行のワード線WLに、トランジスタ160のゲート電極が有する電荷によって、トランジスタ160のオン状態またはオフ状態が選択されるような電位(読み出し電位)を与える。そして、ソース線SLに定電位を与え、ビット線BLに接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL-ビット

40

50

線 B L 間のコンダクタンスは、読み出しを行う行のトランジスタ 160 の状態（オン状態またはオフ状態）によって決定される。つまり、読み出しを行う行のトランジスタ 160 のゲート電極が有する電荷によって、ビット線 B L の電位は異なる値をとることになる。ビット線 B L の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0238】

なお、上記においては、各メモリセル 400 に保持させる情報量を 1 ビットとしたが、本実施の形態に示す記憶装置の構成はこれに限られない。トランジスタ 160 のゲート電極に与える電位を 3 以上用意して、各メモリセル 400 が保持する情報量を増加させても良い。例えば、トランジスタ 160 のゲート電極にあたえる電位を 4 種類とする場合には、各メモリセルに 2 ビットの情報を保持させることができる。10

【0239】

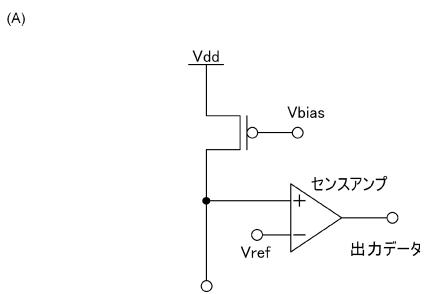

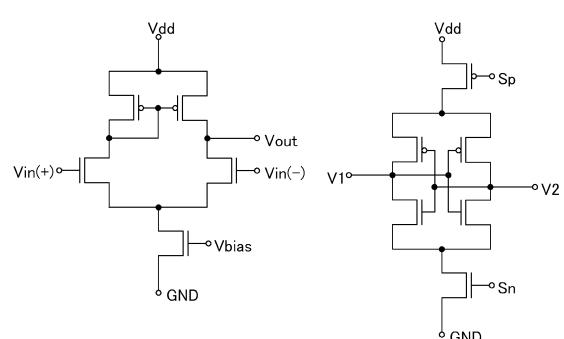

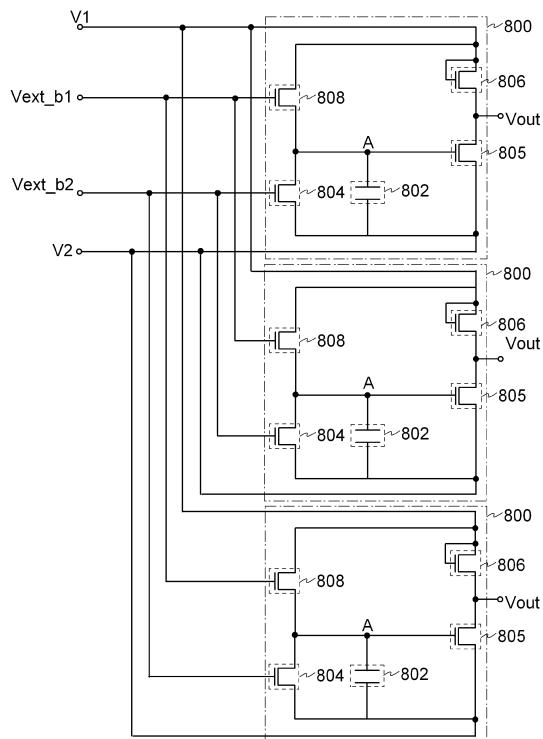

次に、図 17 に示す半導体装置などに用いることができる読み出し回路の一例について図 18 を用いて説明する。

【0240】

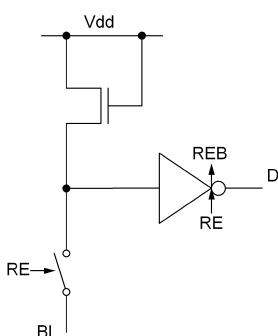

図 18 (A) には、読み出し回路の概略を示す。当該読み出し回路は、トランジスタとセンスアンプ回路を有する。

【0241】

読み出し時には、端子 A は読み出しを行うメモリセルが接続されたビット線 B L に接続される。また、トランジスタのゲート電極にはバイアス電位 V bias が印加され、端子 A の電位が制御される。20

【0242】

メモリセル 400 は、格納されるデータに応じて、異なる抵抗値を示す。具体的には、選択したメモリセル 400 のトランジスタ 160 がオン状態の場合には低抵抗状態となり、選択したメモリセル 400 のトランジスタ 160 がオフ状態の場合には高抵抗状態となる。

【0243】

メモリセルが高抵抗状態の場合、端子 A の電位が参照電位 V ref より高くなり、センスアンプは端子 A の電位に対応する電位を出力する。一方、メモリセルが低抵抗状態の場合、端子 A の電位が参照電位 V ref より低くなり、センスアンプ回路は端子 A の電位に対応する電位を出力する。30

【0244】

このように、読み出し回路を用いることで、メモリセルからデータを読み出すことができる。なお、本実施の形態の読み出し回路は一例である。他の回路を用いても良い。また、読み出し回路は、プリチャージ回路を有しても良い。参照電位 V ref の代わりに参照用のビット線 B L が接続される構成としても良い。

【0245】

図 18 (B) に、センスアンプ回路の一例である差動型センスアンプを示す。差動型センスアンプは、入力端子 V in (+) と V in (-) と出力端子 V out を有し、V in (+) と V in (-) の電位の差を増幅する。V in (+) の電位が V in (-) の電位よりも高ければ V out は、High 信号を出力し、V in (+) の電位が V in (-) よりも低ければ V out は、Low 信号を出力する。当該差動型センスアンプを読み出し回路に用いる場合、V in (+) と V in (-) の一方は端子 A と接続し、V in (+) と V in (-) の他方には参照電位 V ref を与える。40

【0246】

図 18 (C) に、センスアンプ回路の一例であるラッチ型センスアンプを示す。ラッチ型センスアンプは、入出力端子 V 1 および V 2 と、制御用信号 S p、S n の入力端子を有する。まず、信号 S p を High、信号 S n を Low として、電源電位 (V dd) を遮断する。そして、比較を行う電位 V 1 in と V 2 in を V 1 と V 2 にそれぞれ与える。その後、信号 S p を Low、信号 S n を High として、電源電位 (V dd) を供給すると、比50

較を行う電位  $V_{1in}$  と  $V_{2in}$  が  $V_{1in} > V_{2in}$  の関係にあれば、 $V_1$  の出力は  $HIGH$ 、 $V_2$  の出力は  $LOW$  となり、 $V_{1in} < V_{2in}$  の関係にあれば、 $V_1$  の出力は  $LOW$ 、 $V_2$  の出力は  $HIGH$  となる。このような関係を利用して、 $V_{1in}$  と  $V_{2in}$  の差を増幅することができる。当該ラッチ型センスアンプを読み出し回路に用いる場合、 $V_1$  と  $V_2$  の一方は、スイッチを介して端子 A および出力端子と接続し、 $V_1$  と  $V_2$  の他方には参照電位  $Vref$  を与える。

【0247】

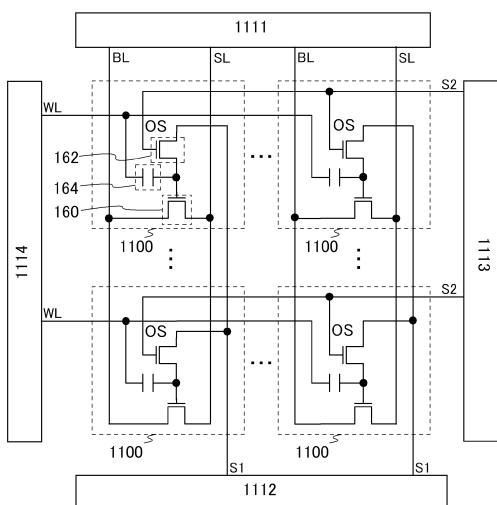

図19は、図15(A)に示す半導体装置を複数用いて形成される半導体装置の回路図の例である。図19に示す半導体装置は、 $m \times n$  ビットの記憶容量を有している。

【0248】

図19に係る半導体装置は、 $m$  本のワード線  $WL$ 、及び  $m$  本の第2の信号線  $S2$  と、 $n$  本のビット線  $BL$ 、 $n$  本のソース線  $SL$ 、及び  $n$  本の第1の信号線  $S1$  と、複数のメモリセル  $1100$  が縦  $m$  個(行) × 横  $n$  個(列)( $m, n$  は自然数)のマトリクス状に配置されたメモリセルアレイと、第1の駆動回路  $1111$ 、第2の駆動回路  $1112$ 、第3の駆動回路  $1113$ 、第4の駆動回路  $1114$ 、といった周辺回路によって構成されている。ここで、メモリセル  $1100$  としては、先の実施の形態において説明した構成(例えば、図15(A)に示される構成)が適用される。

【0249】

つまり、各メモリセル  $1100$  は、第1のトランジスタ  $160$ 、第2のトランジスタ  $162$ 、容量素子  $164$  をそれぞれ有している。第1のトランジスタ  $160$  のゲート電極と、第2のトランジスタ  $162$  のソース電極またはドレイン電極の一方と、容量素子  $164$  の電極の一方とは、接続され、ソース線  $SL$  と、第1のトランジスタ  $160$  のソース電極とは、接続され、ビット線  $BL$  と、第1のトランジスタ  $160$  のドレイン電極とは、接続され、第1の信号線  $S1$  と、第2のトランジスタ  $162$  のソース電極またはドレイン電極の他方とは、接続され、第2の信号線  $S2$  と、第2のトランジスタ  $162$  のゲート電極とは、接続され、ワード線  $WL$  と、容量素子  $164$  の電極の他方とは、接続されている。

【0250】

また、メモリセル  $1100$  は、ソース線  $SL$  とビット線  $BL$  との間に、並列に接続されている。例えば、 $i$  行  $j$  列のメモリセル  $1100$  ( $i, j$ ) ( $i$  は 1 以上  $m$  以下の整数、 $j$  は 1 以上  $n$  以下の整数) は、ソース線  $SL$  ( $j$ )、ビット線  $BL$  ( $j$ )、第1の信号線  $S1$  ( $j$ )、ワード線  $WL$  ( $i$ )、第2の信号線  $S2$  ( $i$ )、にそれぞれ接続されている。

【0251】

ソース線  $SL$  及びビット線  $BL$  は、第1の駆動回路  $1111$  と接続されており、第1の信号線  $S1$  は、第2の駆動回路  $1112$  と接続されており、第2の信号線  $S2$  は、第3の駆動回路  $1113$  と接続されており、ワード線  $WL$  は、第4の駆動回路  $1114$  と接続されている。なお、ここでは、第1の駆動回路  $1111$ 、第2の駆動回路  $1112$ 、第3の駆動回路  $1113$ 、第4の駆動回路  $1114$  は、それぞれ独立に設けているが、開示する発明はこれに限定されない。いずれか一、または複数の機能を有するデコーダを用いても良い。

【0252】

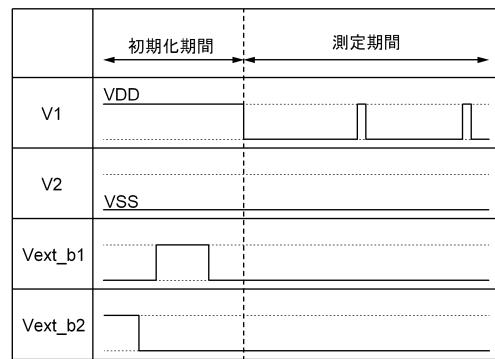

次に、図20に示すタイミングチャートを用いて、図19に示す半導体装置の書き込み動作および読み出し動作について説明する。

【0253】

ここでは、簡単のため、2行 × 2列の半導体装置の動作について説明することとするが、開示する発明はこれに限定されない。

【0254】

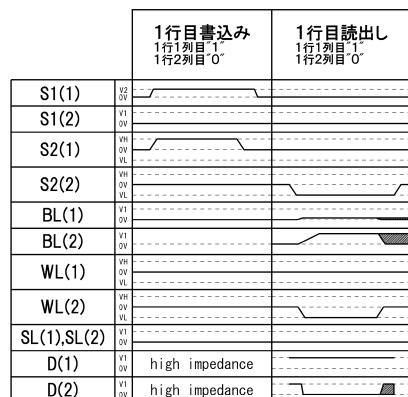

図20は、図19に示す半導体装置の動作を説明するための図である。図20において、 $S1(1)$  および  $S1(2)$  は、それぞれ第1の信号線  $S1$  の電位、 $S2(1)$  および  $S2(2)$  は、それぞれ第2の信号線  $S2$  の電位、 $BL(1)$  および  $BL(2)$  は、それぞれビット線  $BL$  の電位、 $WL(1)$  および  $WL(2)$  は、ワード線  $WL$  の電位、 $SL(1)$

10

20

30

40

50

) および S L ( 2 ) は、それぞれソース線 S L の電位に相当する。

【 0 2 5 5 】

まず、1行目のメモリセル ( 1 , 1 ) 、およびメモリセル ( 1 , 2 ) への書き込み、1行目のメモリセル ( 1 , 1 ) 、およびメモリセル ( 1 , 2 ) からの読み出しを行う場合について説明する。なお、以下では、メモリセル ( 1 , 1 ) へ書き込むデータを " 1 " とし、メモリセル ( 1 , 2 ) へ書き込むデータを " 0 " とする場合について説明する。

【 0 2 5 6 】

はじめに、書き込みについて説明する。1行目書き込み期間において、1行目の第2の信号線 S 2 ( 1 ) に電位 V H を与え、1行目の第2のトランジスタ 1 6 2 をオン状態とする。また、2行目の第2の信号線 S 2 ( 2 ) に 0 V を与え、2行目の第2のトランジスタ 1 6 2 をオフ状態とする。

10

【 0 2 5 7 】

次に、1列目の第1の信号線 S 1 ( 1 ) に電位 V 2 、2列目の第1の信号線 S 1 ( 2 ) に電位 0 V を与える。

【 0 2 5 8 】

その結果、メモリセル ( 1 , 1 ) のフローティングゲート部 F G には電位 V 2 が、メモリセル ( 1 , 2 ) のフローティングゲート部 F G には 0 V が与えられる。ここでは、電位 V 2 は第1のトランジスタ 1 6 0 のしきい値電圧より高い電位とする。そして、1行目の第2の信号線 S 2 ( 1 ) の電位を 0 V として、1行目の第2のトランジスタ 1 6 2 をオフ状態とすることで、書き込みを終了する。

20

【 0 2 5 9 】

なお、ワード線 W L ( 1 ) 、 W L ( 2 ) は 0 V としておく。また、1列目の第1の信号線 S 1 ( 1 ) の電位を変化させる前に1行目の第2の信号線 S 2 ( 1 ) を 0 V とする。書き込み後の、ワード線 W L に接続される端子を制御ゲート電極、第1のトランジスタ 1 6 0 のソース電極をソース電極、第2のトランジスタ 1 6 2 のドレイン電極をドレイン電極、とそれぞれ見なした記憶素子のしきい値は、データ " 0 " では V w 0 、データ " 1 " では V w 1 となる。ここで、メモリセルのしきい値とは、第1のトランジスタ 1 6 0 のソース電極とドレイン電極の間の抵抗が変化する、ワード線 W L に接続される端子の電圧をいうものとする。なお、 V w 0 > 0 > V w 1 とする。

【 0 2 6 0 】

30

次に、読み出しについて説明する。1行目の読み出し期間において、1行目のワード線 W L ( 1 ) に 0 V を与え、2行目のワード線 W L ( 2 ) には電位 V L を与える。電位 V L はしきい値 V w 1 より低い電位とする。W L ( 1 ) を 0 V とすると、1行目において、データ " 0 " が保持されているメモリセル ( 1 , 2 ) の第1のトランジスタ 1 6 0 はオフ状態、データ " 1 " が保持されているメモリセル ( 1 , 1 ) の第1のトランジスタ 1 6 0 はオン状態となる。W L ( 2 ) を電位 V L とすると、2行目において、データ " 0 " 、 " 1 " のいずれが保持されているメモリセルであっても、第1のトランジスタ 1 6 0 はオフ状態となる。

【 0 2 6 1 】

次に、1列目のソース線 S L ( 1 ) 、2列目のソース線 S L ( 2 ) に電位 0 V を与える。

40

【 0 2 6 2 】

その結果、ビット線 B L ( 1 ) - ソース線 S L ( 1 ) 間はメモリセル ( 1 , 1 ) の第1のトランジスタがオン状態であるため低抵抗となり、ビット線 B L ( 2 ) - ソース線 S L ( 2 ) 間はメモリセル ( 1 , 2 ) の第1のトランジスタ 1 6 0 がオフ状態であるため、高抵抗となる。ビット線 B L ( 1 ) 、ビット線 B L ( 2 ) に接続される読み出し回路は、ビット線の抵抗の違いから、データを読み出すことができる。

【 0 2 6 3 】

また、第2の信号線 S 2 ( 1 ) には 0 V を、第2の信号線 S 2 ( 2 ) には電位 V L を与え、第2のトランジスタ 1 6 2 を全てオフ状態としておく。1行目のフローティングゲート部 F G の電位は 0 V または V 2 であるから、第2の信号線 S 2 ( 1 ) を 0 V とすることで

50

1行目の第2のトランジスタ162を全てオフ状態とすることができます。一方、2行目のフローティングゲート部FGの電位は、ワード線WL(2)に電位VLが与えられると、書き込み直後の電位より低い電位となってしまう。これにより、第2のトランジスタ162がオン状態となることを防止するために、第2の信号線S2(2)をワード線WL(2)と同じ低電位とする。以上により、第2のトランジスタ162を全てオフ状態とすることができます。

#### 【0264】

次に、読み出し回路として、図21に示す回路を用いる場合の出力電位について説明する。ビット線BL(1)-ソース線SL(1)間は低抵抗であるため、クロックドインバータには低電位が入力され、出力D(1)はHighとなる。ビット線BL(2)-ソース線SL(2)間は高抵抗であるため、クロックドインバータには高電位が入力され、出力D(2)はLowとなる。

10

#### 【0265】

動作電圧は、例えば、VDD=2V、V2=1.5V、VH=2V、VL=-2Vとすることができる。

#### 【0266】

以上、本実施の形態において示すように、メモリセルを複数設けることで、半導体装置の記憶容量を増加させることができる。なお、メモリセルの数や配置、配線の数や配置、駆動回路の数や配置、などは適宜設計することができるから、上述の構成に限定されるものではない。

20

#### 【0267】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0268】

##### (実施の形態4)

本実施の形態では、実施の形態1および実施の形態2とは異なる、開示する発明の一態様に係る半導体装置の構成およびその作製方法について、図22乃至図24を参照して説明する。なお、本実施の形態において説明するトランジスタ260は、先の実施の形態における回路図中のトランジスタ160として、トランジスタ262は、先の実施の形態における回路図中のトランジスタ162として、容量素子264は、先の実施の形態における回路図中の容量素子164として用いることが可能である。

30

#### 【0269】

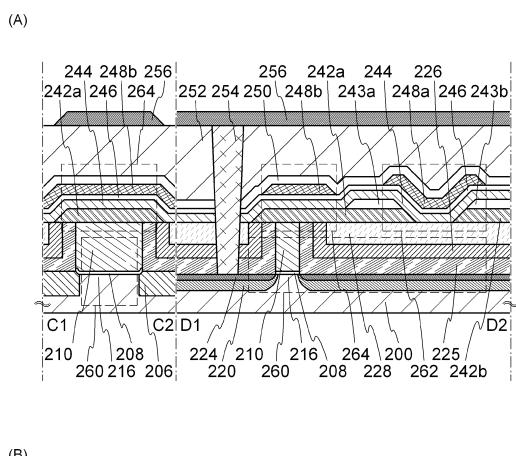

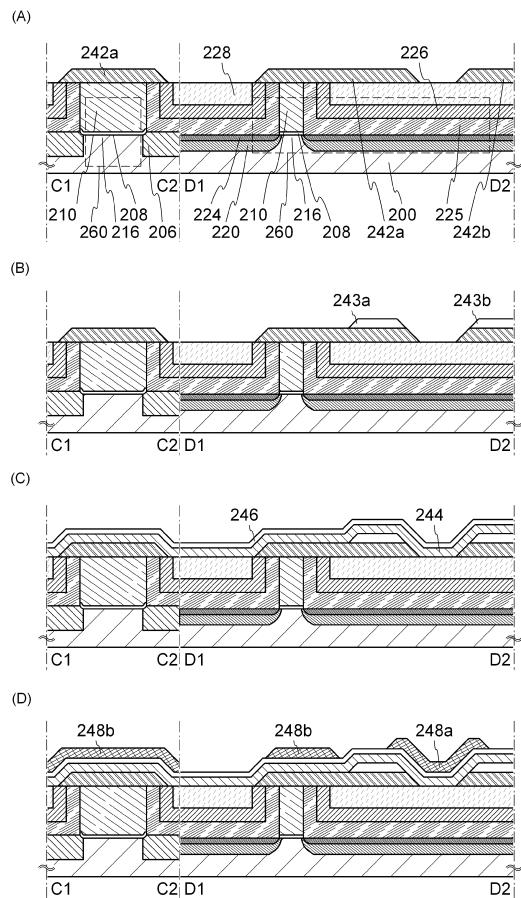

##### 半導体装置の断面構成および平面構成

図22は、上記半導体装置の構成の一例である。図22(A)には、半導体装置の断面を、図22(B)には、半導体装置の平面を、それぞれ示す。ここで、図22(A)は、図22(B)のC1-C2およびD1-D2における断面に相当する。図22(B)の平面図においては、煩雑になることを避けるため、ソース電極またはドレイン電極254や、配線256など、構成要素の一部を省略している。図22(A)および図22(B)に示される半導体装置は、下部に酸化物半導体以外の半導体材料を用いたトランジスタ260を有し、上部に酸化物半導体を用いたトランジスタ262を有するものである。酸化物半導体以外の半導体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

40

#### 【0270】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるるのはいうまでもない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体をトランジスタ262に用いる点にあるから、半導体装置の具体的な構成をここで示すものに限定する必要はない。

#### 【0271】

図22に示される半導体装置は、トランジスタ262および容量素子264が、トランジ

50

スタ 260 と重畳するように設けられている。図 22 (B) に示すような、平面レイアウトを採用することにより、高集積化が可能である。例えば、最小加工寸法を F として、メモリセルの占める面積を  $15 F^2 \sim 25 F^2$  とすることが可能である。

#### 【0272】

図 22 に示される半導体装置と、先の実施の形態に示される半導体装置の相違の一は、トランジスタ 260 におけるサイドウォール絶縁層の有無である。つまり、図 22 に示される半導体装置は、サイドウォール絶縁層を有しない。また、サイドウォール絶縁層を形成しないことにより、不純物領域 114 ( 例えば、図 2 参照 ) が形成されていない。このように、サイドウォール絶縁層を設けない場合は、サイドウォール絶縁層を設ける場合と比較して集積化が容易である。また、サイドウォール絶縁層を設ける場合と比較して、作製工程を簡略化することが可能である。 10

#### 【0273】

図 22 に示される半導体装置と、先の実施の形態に示される半導体装置の相違の他の一は、トランジスタ 260 における層間絶縁層である。つまり、図 22 に示される半導体装置では、水素を含む層間絶縁層 225 がトランジスタ 260 の金属化合物領域 224 と接する。水素を含む層間絶縁層 225 を金属化合物領域 224 と接するように設けることで、トランジスタ 260 に対して水素を供給しトランジスタ 260 の特性を向上させることができ。 20 このような層間絶縁層 225 としては、例えば、プラズマ CVD 法により形成された水素を含む窒化シリコン層などがある。さらに、層間絶縁層 226 として、水素濃度が低い絶縁層を適用することで、トランジスタ 262 の特性を悪化させるおそれがある水素の、トランジスタ 262 への混入を防ぐことが可能である。このような層間絶縁層 226 としては、例えば、水素の非存在下でのスパッタ法により形成された窒化シリコン層などがある。このような構成を採用することにより、トランジスタ 260 とトランジスタ 262 の特性を十分に高めることができ。なお、図 22 において、基板 200 は実施の形態 1 の基板 100 に、素子分離絶縁層 206 は実施の形態 1 の素子分離絶縁層 106 に、ゲート絶縁層 208 は実施の形態 1 のゲート絶縁層 108 に、ゲート電極 210 は実施の形態 1 のゲート電極 110 に、チャネル形成領域 216 は実施の形態 1 のチャネル形成領域 116 に、高濃度不純物領域 220 は実施の形態 1 の高濃度不純物領域 120 に、金属化合物領域 224 は実施の形態 1 の金属化合物領域 124 に、それぞれ対応する。 30

#### 【0274】

図 22 に示される半導体装置と、先の実施の形態に示される半導体装置の相違の他の一は、トランジスタ 262 において、絶縁層 243a および絶縁層 243b が酸化物半導体層 244 とソース電極またはドレイン電極 242a の間、および酸化物半導体層 244 とソース電極またはドレイン電極 242b の間に設けられている点である。このように、絶縁層 243a および絶縁層 243b を設けることにより、ゲート電極 248a と、ソース電極またはドレイン電極 242a ( または、ゲート電極 248a と、ソース電極またはドレイン電極 242b ) が形成するいわゆるゲート容量を低減し、トランジスタ 262 の動作速度を向上させることができる。 40

#### 【0275】

なお、実施の形態 1 と同様、下部のトランジスタ 260 と上部のトランジスタ 262 は、ゲート電極 210 上にソース電極またはドレイン電極 242a が直接形成されることで電気的に接続されている。このような構成とすることで、電極や配線を別途設ける場合と比較して、集積度が向上する。また、作製工程が簡略化される。

#### 【0276】

なお、本実施の形態では、上述の相違点を一体に有する構成を示しているが、当該相違点のいずれか一のみを有する構成を採用しても良い。

#### 【0277】

##### 半導体装置の作製方法

次に、上記半導体装置の作製方法の一例について説明する。以下では、下部のトランジス 50