(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6319151号

(P6319151)

(45) 発行日 平成30年5月9日(2018.5.9)

(24) 登録日 平成30年4月13日(2018.4.13)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 29/78  | (2006.01) | HO 1 L | 29/78 | 6 5 7 A |

| HO 1 L 29/12  | (2006.01) | HO 1 L | 29/78 | 6 5 2 T |

| HO 1 L 29/861 | (2006.01) | HO 1 L | 29/78 | 6 5 3 A |

| HO 1 L 29/868 | (2006.01) | HO 1 L | 29/78 | 6 5 2 N |

| HO 1 L 21/329 | (2006.01) | HO 1 L | 29/78 | 6 5 2 G |

請求項の数 15 (全 22 頁) 最終頁に続く

|           |                               |           |                                        |

|-----------|-------------------------------|-----------|----------------------------------------|

| (21) 出願番号 | 特願2015-59436 (P2015-59436)    | (73) 特許権者 | 000241463<br>豊田合成株式会社<br>愛知県清須市春日長畑1番地 |

| (22) 出願日  | 平成27年3月23日(2015.3.23)         | (74) 代理人  | 110000028<br>特許業務法人明成国際特許事務所           |

| (65) 公開番号 | 特開2016-181534 (P2016-181534A) | (72) 発明者  | 丹羽 隆樹<br>愛知県清須市春日長畑1番地 豊田合成株式会社内       |

| (43) 公開日  | 平成28年10月13日(2016.10.13)       | (72) 発明者  | 小寄 正芳<br>愛知県清須市春日長畑1番地 豊田合成株式会社内       |

| 審査請求日     | 平成29年4月19日(2017.4.19)         | (72) 発明者  | 藤井 隆弘<br>愛知県清須市春日長畑1番地 豊田合成株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置および半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1窒化物半導体層と、前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、前記第1導電型の第4窒化物半導体層と、がこの順に積層された積層体と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する第1の電極と、を有し、

前記第3窒化物半導体層と、前記第4窒化物半導体層とを貫通し、前記第2窒化物半導体層に達するトレンチが形成され、

前記トレンチに絶縁膜を介して設けられたゲート電極を備える、

10

縦型MOSトランジスタと、

前記第1の電極と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する前記第2導電型のオーミック電極と、を有する、

保護素子と、を備える、半導体装置であって、

前記第1導電型の不純物濃度は、前記第1窒化物半導体層に比べて前記第2窒化物半導体層のほうが低く、

前記第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、

前記積層体の積層方向から見たときに、前記凸部の上面は、前記第2導電型のオーミック電極と少なくとも一部が重なる位置に配されており、

20

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記積層方向から見たときに、前記第4窒化物半導体層は、前記凸部の上面と重ならない位置に配されている、半導体装置。

【請求項3】

請求項1または請求項2に記載の半導体装置であって、さらに、

前記積層方向から見たときに、前記凸部に対して、前記トレンチが配されている側とは反対側に、前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達する段差部が形成されており、

前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みは、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚み以下である、半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、

前記段差部の底面と前記凸部との距離は、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置。

【請求項5】

請求項1から請求項4までのいずれか一項に記載の半導体装置であって、さらに、

前記第4窒化物半導体層の面であって、前記第3窒化物半導体層と接する面とは反対側の面と接する前記第1導電型のオーミック電極を備える、半導体装置。

【請求項6】

請求項3又は請求項4に従属する請求項5に記載の半導体装置であって、さらに、

前記第1導電型のオーミック電極と前記第2導電型のオーミック電極とを電気的に接続する第1配線を備え、

前記第1配線は、絶縁膜を介して前記段差部の側面を覆っている、半導体装置。

【請求項7】

請求項1から請求項6までのいずれか一項に記載の半導体装置であって、

前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されている、半導体装置。

【請求項8】

請求項1から請求項7までのいずれか一項に記載の半導体装置であって、

前記第1窒化物半導体層は、窒化ガリウムにより形成されている、半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記第1窒化物半導体層は、窒化ガリウム基板である、半導体装置。

【請求項10】

請求項9に記載の半導体装置であって、

前記凸部の側面は、前記凸部の上面に対して傾斜している、半導体装置。

【請求項11】

請求項1から請求項9までのいずれか一項に記載の半導体装置であって、

前記凸部の側面は、a面またはm面で構成され、前記凸部の上面は、c面で構成されている、半導体装置。

【請求項12】

半導体装置の製造方法であって、

第1導電型の第1窒化物半導体層の面に突出する凸部を形成する工程と、

前記第1窒化物半導体層の面であって、前記凸部を備える面上に、前記第1窒化物半導体層よりも不純物濃度が小さい前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、をこの順に積層する工程と、

前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達するトレンチを形成す

10

20

30

40

50

る工程と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、第1の電極を形成する工程と、

積層方向において、前記凸部の上面と少なくとも一部が重なる位置であって、前記第3窒化物半導体層の面であり、前記第2窒化物半導体層と接する面とは反対側の面に、前記第2導電型のオーミック電極を形成する工程と、

前記トレンチに絶縁膜を介してゲート電極を形成する工程と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、前記第1導電型の第4窒化物半導体層を形成する工程と、

前記第4窒化物半導体層にソース電極を形成する工程と、

を有し、

前記第4窒化物半導体層は、前記積層方向において、前記凸部の上面と重ならない位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、

前記第1窒化物半導体層から前記第4窒化物半導体層までの窒化物半導体層と前記ゲート電極と前記第1の電極と前記ソース電極とから形成される縦型MOSトランジスタと、前記第1窒化物半導体層から前記第3窒化物半導体層までの窒化物半導体層と前記第1電極と前記第2導電型のオーミック電極から形成されるPN接合ダイオードである保護素子と、を備える半導体装置の製造方法。

### 【請求項13】

請求項12に記載の半導体装置の製造方法であって、さらに、

前記凸部の上面と前記トレンチの底面との距離が、前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置の製造方法。

### 【請求項14】

請求項12または請求項13に記載の半導体装置の製造方法であって、

前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されている、半導体装置の製造方法。

### 【請求項15】

請求項12から請求項14までのいずれか一項に記載の半導体装置の製造方法であって

、前記第1窒化物半導体層は、窒化ガリウム基板である、半導体装置の製造方法。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

#### 【背景技術】

#### 【0002】

半導体装置の耐圧性向上を目的として、縦型MOSFETに保護素子としてのPN接合ダイオードを併設する技術が知られている。この場合、PN接合ダイオードを保護素子として機能させるため、縦型MOSFETのN<sup>-</sup>ドリフト層よりも薄いN<sup>-</sup>層を有するPN接合ダイオードを形成することが好ましい。特許文献1には、保護ダイオードを形成する電極間に挟まれたN<sup>-</sup>層を薄くするため、N<sup>-</sup>層の一部を除去した後、除去した部分にP型層を再成長により形成する技術が開示されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【特許文献1】特表2005-520322号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

10

20

30

40

50

## 【0004】

しかし、半導体として窒化物半導体を用いる場合、特許文献1に記載の技術においては、再成長界面に意図しないN型キャリアが発生することにより、PN接合ダイオードの耐圧が低下するという課題を発明者らが見出した。そのほか、従来の半導体装置においては、その小型化や、省資源化、製造の容易化、製造の精確さ、作業性の向上等が望まれていた。

## 【課題を解決するための手段】

## 【0005】

本発明は、上記の課題の少なくとも一部を解決するためになされたものであり、以下の形態として実現することができる。

本発明の第1の形態は、

第1導電型の第1窒化物半導体層と、前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、前記第1導電型の第4窒化物半導体層と、がこの順に積層された積層体と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する第1の電極と、を有し、

前記第3窒化物半導体層と、前記第4窒化物半導体層とを貫通し、前記第2窒化物半導体層に達するトレンチが形成され、

前記トレンチに絶縁膜を介して設けられたゲート電極を備える、

縦型MOSトランジスタと、

前記第1の電極と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する前記第2導電型のオーミック電極と、を有する、

保護素子と、を備える、半導体装置であって、

前記第1導電型の不純物濃度は、前記第1窒化物半導体層に比べて前記第2窒化物半導体層のほうが低く、

前記第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、

前記積層体の積層方向から見たときに、前記凸部の上面は、前記第2導電型のオーミック電極と少なくとも一部が重なる位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置である。

本発明の第2の形態は、

半導体装置の製造方法であって、

第1導電型の第1窒化物半導体層の面に突出する凸部を形成する工程と、

前記第1窒化物半導体層の面であって、前記凸部を備える面に、前記第1窒化物半導体層よりも不純物濃度が小さい前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、をこの順に積層する工程と、

前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達するトレンチを形成する工程と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、第1の電極を形成する工程と、

積層方向において、前記凸部の上面と少なくとも一部が重なる位置であって、前記第3窒化物半導体層の面であり、前記第2窒化物半導体層と接する面とは反対側の面に、前記第2導電型のオーミック電極を形成する工程と、

前記トレンチに絶縁膜を介してゲート電極を形成する工程と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、前記第1導電型の第4窒化物半導体層を形成する工程と、

前記第4窒化物半導体層にソース電極を形成する工程と、

を有し、

10

20

30

40

50

前記第4窒化物半導体層は、前記積層方向において、前記凸部の上面と重ならない位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、

前記第1窒化物半導体層から前記第4窒化物半導体層までの窒化物半導体層と前記ゲート電極と前記第1の電極と前記ソース電極とから形成される縦型MOSトランジスタと、前記第1窒化物半導体層から前記第3窒化物半導体層までの窒化物半導体層と前記第1電極と前記第2導電型のオーミック電極から形成されるPN接合ダイオードである保護素子と、を備える半導体装置の製造方法である。また、本発明は以下の形態として実現することもできる。

10

【0006】

(1) 本発明の一形態によれば、半導体装置が提供される。この半導体装置は、第1導電型の第1窒化物半導体層と、前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、前記第1導電型の第4窒化物半導体層と、がこの順に積層された積層体と、前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する第1の電極と、を有し、前記第3窒化物半導体層と、前記第4窒化物半導体層とを貫通し、前記第2窒化物半導体層に達するトレンチが形成された、縦型MOSトランジスタと、前記第1の電極と、前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する前記第2導電型のオーミック電極と、を有する、保護素子と、を備える、半導体装置であって；前記第1導電型の不純物濃度は、前記第1窒化物半導体層に比べて前記第2窒化物半導体層のほうが低く、前記第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、前記積層体の積層方向から見たときに、前記凸部の上面は、前記第2導電型のオーミック電極と少なくとも一部が重なる位置に配されており、前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい。この形態の半導体装置によれば、第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、トレンチの底面における第2窒化物半導体層の厚みは、凸部の上面における第2窒化物半導体層の厚みよりも大きいため、保護素子の耐圧の低下を抑制できる。

20

【0007】

(2) 上記形態の半導体装置において、前記積層方向から見たときに、前記第4窒化物半導体層は、前記凸部の上面と重ならない位置に配されていてよい。この形態の半導体装置によれば、第4窒化物半導体層から凸部へ電流が流れる前に、保護素子に電流が流れることにより、保護素子の耐圧の低下を抑制できる。

30

【0008】

(3) 上記形態の半導体装置において、さらに、前記積層方向から見たときに、前記凸部に対して、前記トレンチが配されている側とは反対側に、前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達する段差部が形成されており、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みは、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚み以下としてもよい。この形態の半導体装置によれば、段差部と第1の電極との間に電流が流れる前に、保護素子に電流が流れることにより、半導体装置の耐圧破壊を抑制できる。

40

【0009】

(4) 上記形態の半導体装置において、前記段差部の底面と前記凸部との距離は、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚みよりも大きくてよい。この形態の半導体装置によれば、第1の電極から凸部を介して段差部に電流が流れる前に、保護素子に電流が流れることにより、半導体装置の耐圧破壊を抑制できる。

【0010】

(5) 上記形態の半導体装置において、さらに、前記第4窒化物半導体層の面であって、前記第3窒化物半導体層と接する面とは反対側の面と接する前記第1導電型のオーミック

50

電極を備えててもよい。この形態の半導体装置によれば、第1導電型のオーミック電極が形成されているため、縦型MOSトランジスタのオン抵抗を下げることができる。

【0011】

(6) 上記形態の半導体装置において、さらに、前記第1導電型のオーミック電極と前記第2導電型のオーミック電極とを電気的に接続する第1配線を備え、前記第1配線は、絶縁膜を介して前記段差部の側面を覆っていてもよい。この形態の半導体装置によれば、第1配線を備えることにより、段差部側面で電界が集中することを抑制でき、その結果、半導体装置の耐圧破壊を抑制できる。

【0012】

(7) 上記形態の半導体装置において、前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されてもよい。この形態の半導体装置によれば、保護素子の耐圧の低下を抑制できる。 10

【0013】

(8) 上記形態の半導体装置において、前記第1窒化物半導体層は、窒化ガリウムにより形成されてもよい。この形態の半導体装置によれば、保護素子の耐圧の低下を抑制できる。

【0014】

(9) 上記形態の半導体装置において、前記第1窒化物半導体層は、窒化ガリウム基板であってもよい。この形態の半導体装置によれば、保護素子の耐圧の低下を抑制できる。

【0015】

(10) 上記形態の半導体装置において、前記凸部の側面は、前記凸部の上面に対して傾斜してもよい。この形態の半導体装置によれば、保護素子の耐圧の低下を抑制できる。 20

【0016】

(11) 上記形態の半導体装置において、前記凸部の側面は、a面またはm面で構成され、前記凸部の上面は、c面で構成されてもよい。この形態の半導体装置によれば、保護素子の耐圧の低下を抑制できる。

【0017】

(12) 本発明の一形態によれば、半導体装置の製造方法が提供される。この半導体装置の製造方法は、第1導電型の第1窒化物半導体層の面に突出する凸部を形成する工程と、前記第1窒化物半導体層の面であって、前記凸部を備える面に、前記第1窒化物半導体層よりも不純物濃度が小さい前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、をこの順に積層する工程と、前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達するトレンチを形成する工程と、前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、第1の電極を形成する工程と、積層方向において、前記凸部の上面と少なくとも一部が重なる位置であって、前記第3窒化物半導体層の面であり、前記第2窒化物半導体層と接する面とは反対側の面に、前記第2導電型のオーミック電極を形成する工程と、を有し；前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい。この形態の半導体装置の製造方法によれば、第1電極と第2導電型のオーミック電極から形成される保護素子の耐圧の低下を抑制できる。 30

【0018】

(13) 上記形態の半導体装置の製造方法において、さらに、前記凸部の上面と前記トレンチの底面との距離が、前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みよりも大きくてよい。この形態の半導体装置の製造方法によれば、縦型MOSトランジスタのドレイン電流は、トレンチ側方とトレンチ下方の第1窒化物半導体層との間を流れるので、縦型MOSトランジスタの耐圧は、凸部により低下することはない。これにより、保護素子よりも縦型MOSトランジスタの耐圧が下がることは無いので、縦型MOSトランジスタが耐圧破壊することを抑制できる。 40

## 【0019】

(14) 上記形態の半導体装置の製造方法において、前記第3窒化物半導体層の面であつて、前記第2窒化物半導体層と接する面とは反対側の面に、前記第1導電型の第4窒化物半導体層を形成する工程を、備え、前記第4窒化物半導体層は、前記積層方向において、前記凸部の上面と重ならない位置に配されていてもよい。この形態の半導体装置の製造方法によれば、縦型MOSトランジスタのドレイン電流は、第4窒化物半導体層と、トレンチ下方の第1窒化物半導体層との間を流れるので、縦型MOSトランジスタの耐圧が凸部により低下することはない。保護素子よりも縦型MOSトランジスタの耐圧が下がることは無いので、縦型MOSトランジスタが耐圧破壊することを抑制できる。

## 【0020】

10

(15) 上記形態の半導体装置の製造方法において、前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されていてもよい。この形態の半導体装置の製造方法によれば、第1電極と第2導電型のオーミック電極から形成される保護素子の耐圧の低下を抑制できる。

## 【0021】

(16) 上記形態の半導体装置の製造方法において、前記第1窒化物半導体層は、窒化ガリウム基板であつてもよい。この形態の半導体装置の製造方法によれば、第1電極と第2導電型のオーミック電極から形成される保護素子の耐圧の低下を抑制できる。

## 【0022】

20

上述した本発明の各形態の有する複数の構成要素はすべてが必須のものではなく、上述の課題の一部又は全部を解決するため、あるいは、本明細書に記載された効果の一部又は全部を達成するために、適宜、前記複数の構成要素の一部の構成要素について、その変更、削除、新たな他の構成要素との差し替え、限定内容の一部削除を行うことが可能である。また、上述の課題の一部又は全部を解決するため、あるいは、本明細書に記載された効果の一部又は全部を達成するために、上述した本発明の一形態に含まれる技術的特徴の一部又は全部を上述した本発明の他の形態に含まれる技術的特徴の一部又は全部と組み合わせて、本発明の独立した一形態とすることも可能である。

## 【0023】

本発明は、半導体装置およびその製造方法以外の種々の形態で実現することも可能である。例えば、本願発明は、上記形態の半導体装置が組み込まれた電気機器、上記形態の半導体装置を製造する製造装置などの形態で実現することができる。

30

## 【発明の効果】

## 【0024】

この形態の半導体装置によれば、第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、トレンチの底面における第2窒化物半導体層の厚みは、凸部の上面における第2窒化物半導体層の厚みよりも大きいため、保護素子の耐圧の低下を抑制できる。また、この形態の半導体装置の製造方法によれば、第1電極と第2導電型のオーミック電極から形成される保護素子の耐圧の低下を抑制できる。

## 【図面の簡単な説明】

## 【0025】

40

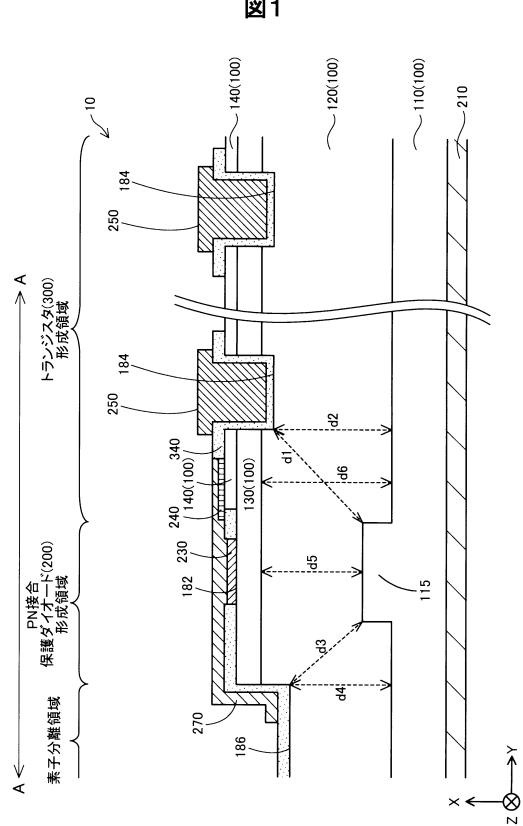

【図1】第1実施形態における半導体装置10の構成を模式的に示す断面図。

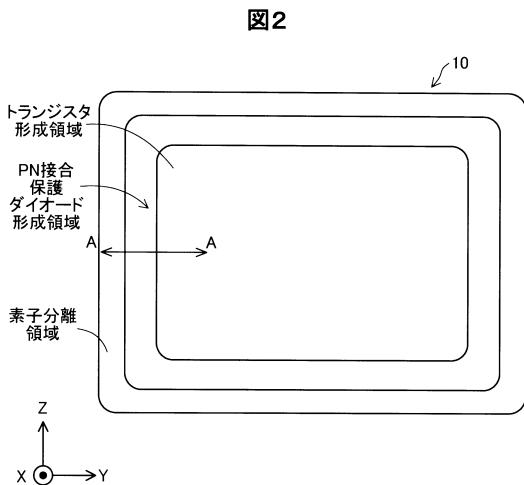

【図2】半導体装置10を+X軸方向から見た外観図。

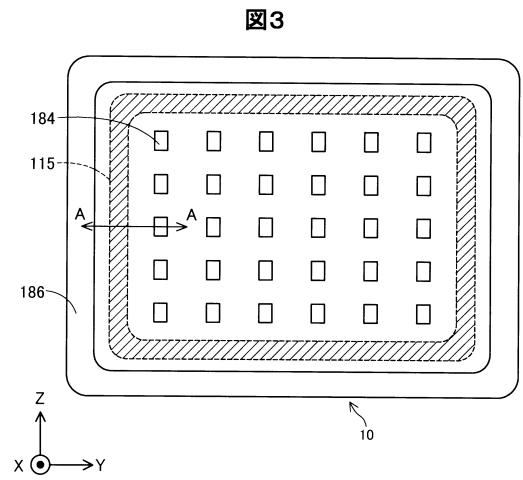

【図3】N型半導体層120とP型半導体層130との界面を+X軸方向から見た概略図。

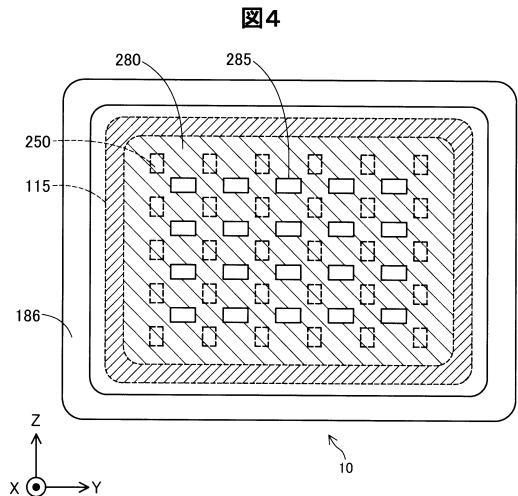

【図4】半導体装置10に備えられた複数の電極250同士を配線280により電気的に接続した状態において、半導体装置10を+X軸方向から見た外観図。

【図5】本実施形態の半導体装置10から得られる効果を説明する図。

【図6】T C A D (Technology CAD) シミュレータにより計算した半導体装置10の電流密度分布を示す図。

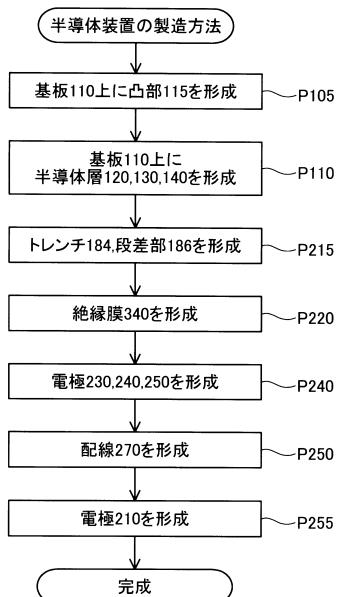

【図7】半導体装置10の製造方法を示す工程図。

50

【図8】工程P105における半導体装置10の中間製品を示す断面図。

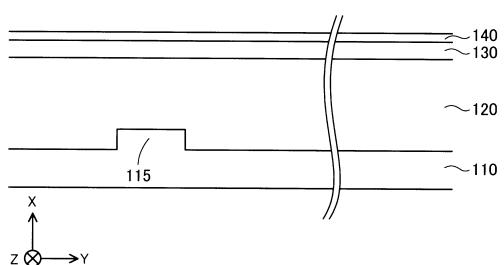

【図9】基板110上に半導体層(120, 130, 140)を形成させた半導体装置10の中間製品を示す断面図。

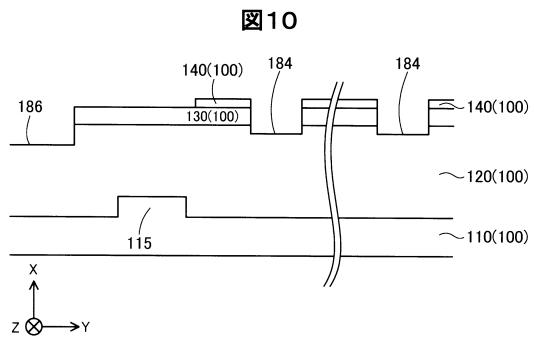

【図10】トレンチ184と段差部186とを形成させた半導体装置10の中間製品を示す断面図。

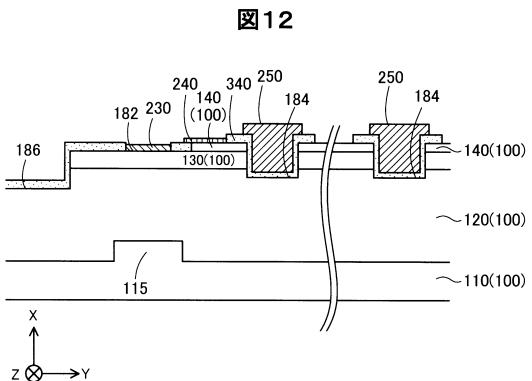

【図11】絶縁膜340を形成させた半導体装置10の中間製品を示す断面図。

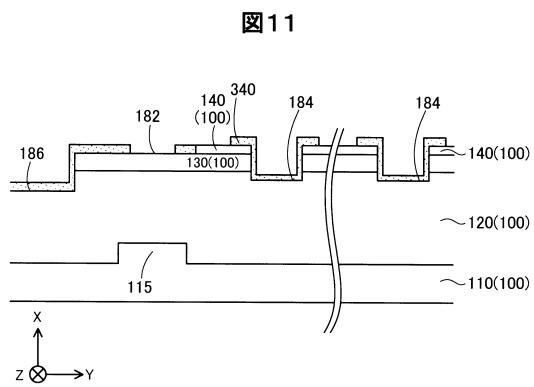

【図12】電極230、240、250を形成させた半導体装置10の中間製品を示す断面図。

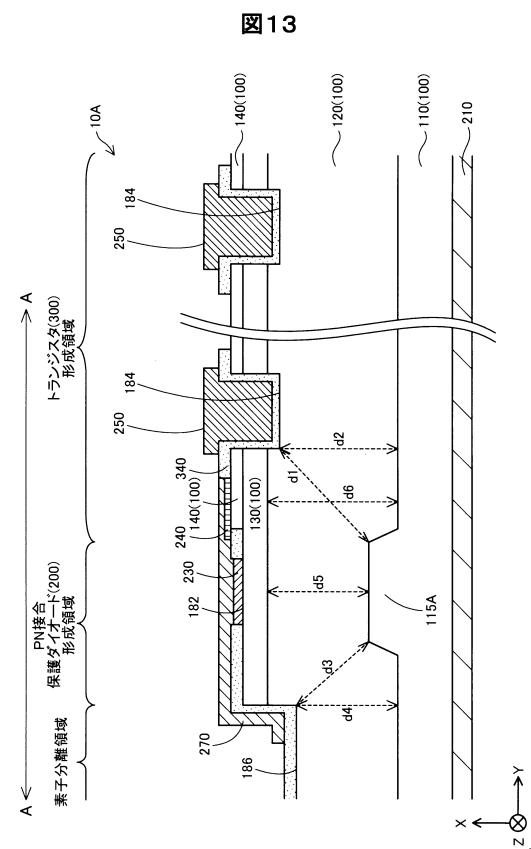

【図13】第2実施形態における半導体装置10Aの構成を模式的に示す図。

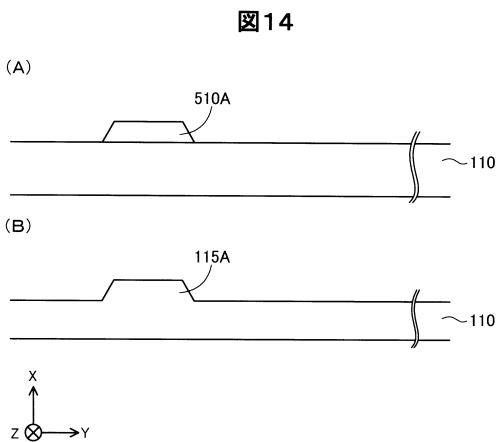

【図14】凸部115Aを形成する工程を説明する図。

10

【図15】再成長により凸部115Bを形成する工程を説明する図。

【図16】積層方向(X軸方向)において、N型半導体層140Cは、凸部115の上面の一部と重なる位置に配されている半導体装置10Cの構成を模式的に示す断面図。

【図17】凸部115Dが段差部186の下方においても配置されている半導体装置の構成を模式的に示す断面図。

【発明を実施するための形態】

【0026】

A. 第1実施形態：

A1. 半導体装置10の構成：

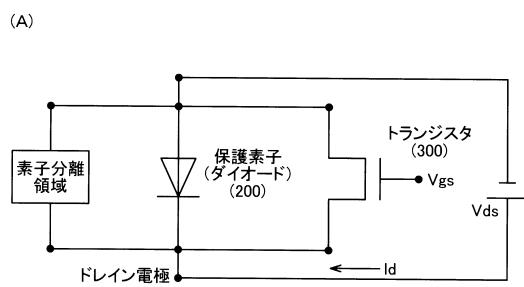

図1は、第1実施形態における半導体装置10の構成を模式的に示す断面図である。半導体装置10は、縦型MOS(Metal-Oxide-Semiconductor)トランジスタ300と保護素子200とを備える。縦型MOSトランジスタ300は、窒化物半導体を用いて形成されたGaN系の半導体装置である。本実施形態では、縦型MOSトランジスタ300は、トレンチゲート型MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)であり、例えば、電力制御に用いられ、パワーデバイスとも呼ばれる。保護素子200は、PN接合ダイオードである。本実施形態においては、窒化物半導体として窒化ガリウム(GaN)を用いる。

20

【0027】

半導体装置10は、基板110と、N型半導体層120と、P型半導体層130と、N型半導体層140と、電極210, 230, 240, 250と、配線270と、絶縁膜340とを備える。半導体装置10は、NPN型の半導体装置であり、N型半導体層120とP型半導体層130とN型半導体層140とが順に積層された構造を有する。

30

【0028】

なお、「基板110」は、「半導体層110」や「第1導電型の第1窒化物半導体層110」とも呼び、「N型半導体層120」は、「第1導電型の第2窒化物半導体層120」とも呼び、「P型半導体層130」は、「第2導電型の第3窒化物半導体層130」とも呼び、「N型半導体層140」は、「第1導電型の第4窒化物半導体層140」とも呼ぶ。また、「半導体基板110と、N型半導体層120と、P型半導体層130と、N型半導体層140と、がこの順に積層された構造体」を、「積層体100」とも呼ぶ。

【0029】

40

半導体装置10のN型半導体層120、P型半導体層130、およびN型半導体層140は、有機金属気相成長法(MOCVD: Metal Organic Chemical Vapor Deposition)による結晶成長によって形成された半導体層である。

【0030】

図1には、相互に直交するXYZ軸が図示されている。図1のXYZ軸のうち、X軸は、基板110に対してN型半導体層120が積層する積層方向に沿った軸である。X軸に沿ったX軸方向のうち、+X軸方向は、基板110からN型半導体層120に向かう方向であり、-X軸方向は、+X軸方向に対向する方向である。図1のXYZ軸のうち、Y軸およびZ軸は、X軸に直交すると共に相互に直交する軸である。Y軸に沿ったY軸方向のうち、+Y軸方向は、図1の紙面左から紙面右に向かう方向であり、-Y軸方向は、+Y

50

軸方向に対向する方向である。Z軸に沿ったZ軸方向のうち、+Z軸方向は、図1の紙面手前から紙面奥に向かう方向であり、-Z軸方向は、+Z軸方向に対向する方向である。

【0031】

半導体装置10の基板110は、Y軸およびZ軸によって規定される面方向に沿って広がるN型の半導体層であり、本実施形態においては、N<sup>+</sup>型の半導体層である。基板110は、主に、ガリウム(Ga)を含む窒化物半導体により形成されている。本実施形態において、基板110は、窒化ガリウム(GaN)から主に形成される。基板110は、ゲルマニウム(Ge)、酸素(O)、ケイ素(Si)などのN型不純物をドナーとして含有する。N型の不純物濃度は、基板110に比べてN型半導体層120のほうが低い。なお、窒化ガリウム(GaN)から主に形成されるとは、モル分率において、窒化ガリウム(GaN)を90%以上含有することを示す。

10

【0032】

基板110は、N型半導体層120へ突出する凸部115を備える。凸部115の側面(Y軸方向側の面)は、a面またはm面で構成され、凸部115の上面(+X軸方向側の面)はc面で構成されている。凸部115を備えることにより得られる効果は、後に詳述する。なお、基板110の代わりに、N<sup>+</sup>型半導体層を設け、電極210とN<sup>+</sup>型半導体層との間に基板を設けてもよい。

【0033】

半導体装置10のN型半導体層120は、基板110の+X軸方向側に積層され、Y軸およびZ軸によって規定される面方向に沿って広がる半導体層である。N型半導体層120は、主に、ガリウム(Ga)を含む窒化物半導体により形成されている。本実施形態において、N型半導体層120は、主に、窒化ガリウム(GaN)から形成されている。N型半導体層120は、ケイ素(Si)をドナーとして含有する。N型半導体層120は、「n<sup>-</sup>-GaN」とも呼ばれる。

20

【0034】

半導体装置10のP型半導体層130は、N型半導体層120の+X軸方向側に積層され、Y軸およびZ軸によって規定される面方向に沿って広がる半導体層である。P型半導体層130は、主に、ガリウム(Ga)を含む窒化物半導体により形成されている。本実施形態において、P型半導体層130は、主に、窒化ガリウム(GaN)から形成されている。P型半導体層130は、マグネシウム(Mg)をP型不純物として含有する。P型半導体層130の不純物濃度は、N型半導体層120の不純物濃度よりも高い。P型半導体層130は、「p-GaN」とも呼ばれる。

30

【0035】

半導体装置10のN型半導体層140は、P型半導体層130の+X軸方向側に積層され、Y軸およびZ軸によって規定される面方向に沿って広がる半導体層である。N型半導体層140は、窒化ガリウム(GaN)から主に形成されている。N型半導体層140は、ケイ素(Si)をN型不純物として含有する。N型半導体層140の不純物濃度は、N型半導体層120の不純物濃度よりも高い。N型半導体層140は、「n<sup>+</sup>-GaN」とも呼ばれる。基板110、N型半導体層120、P型半導体層130、N型半導体層140は、ガリウムを含む窒化物半導体により形成されている。

40

【0036】

半導体装置10の凹部182は、+X軸方向側からP型半導体層130が露出した部位である。凹部182は、リセス(recess)とも呼ばれる。

【0037】

半導体装置10のトレンチ184は、ドライエッチングによって形成されている。トレンチ184は、N型半導体層140の+X軸方向側から、P型半導体層130と、N型半導体層140とを貫通し、N型半導体層120まで達する部位である。本実施形態では、トレンチ184は、凹部182の+Y軸方向側に位置する。

【0038】

トレンチ184の表面には、積層体100の+X軸方向側に至るまで、絶縁膜340が

50

形成されている。本実施形態では、絶縁膜340は、二酸化ケイ素(SiO<sub>2</sub>)から形成されている。なお、二酸化ケイ素(SiO<sub>2</sub>)に代えて、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、酸化ジルコニウム(ZrO<sub>2</sub>)、酸化タンタル(Ta<sub>2</sub>O<sub>3</sub>)を用いてもよい。

#### 【0039】

半導体装置10の段差部186は、ドライエッチングによって形成されている。段差部186は、P型半導体層130を貫通し、N型半導体層120に達する部位である。段差部186は、半導体素子を分離するために設けられた素子分離領域である。積層体100の積層方向(X軸方向)から見たときに、凸部115に対してトレンチ184が配されている側とは反対側に形成されている。つまり、段差部186は、トレンチ184の-Y軸方向側に位置する。

10

#### 【0040】

半導体装置10の電極210は、基板110の面であって、N型半導体層120と接する面とは反対側の面と接するドレイン電極である。つまり、電極210は、基板110の-X軸方向側に形成されている。電極210は、N型オーミック電極である。本実施形態では、電極210は、チタン(Ti)から形成される層にアルミニウム(Al)から形成される層を積層した後に焼成することによって形成される。なお、「電極210」は、「第1の電極210」とも呼ぶ。

#### 【0041】

半導体装置10の電極230は、凹部182の内側に露出されたP型半導体層130に形成されたボディ電極である。電極230は、P型半導体層130の面であって、N型半導体層120と接する面とは反対側の面と接するP型オーミック電極である。「電極230」は、「第2導電型のオーミック電極230」とも呼ぶ。本実施形態では、電極230は、パラジウム(Pd)から形成される層を積層した後に焼成することによって形成される。

20

#### 【0042】

半導体装置10の電極240は、凹部182とトレンチ184との間ににおけるN型半導体層140の上(+X軸方向側)に形成されたソース電極である。つまり、電極240は、N型半導体層140の面であって、P型半導体層130と接する面とは反対側の面と接するN型オーミック電極である。本実施形態では、電極240は、チタン(Ti)から形成される層にアルミニウム(Al)から形成される層を積層した後に焼成することによって形成される。電極240は、オーミック電極であるため、縦型MOSトランジスタ300のON抵抗を下げることができる。

30

#### 【0043】

半導体装置10の電極250は、トレンチ184における絶縁膜340上に形成されたゲート電極である。本実施形態では、電極250は、アルミニウム(Al)から形成される。なお、アルミニウム(Al)に代えて、アルミニウムシリコン(AlSi)、アルミニウムシリコン銅(AlSiCu)を用いてもよい。

#### 【0044】

半導体装置10の配線270は、電極230と電極240とを電気的に接続する配線である。「配線270」は、「第1配線270」とも呼び、アルミニウム(Al)から形成される。なお、アルミニウム(Al)に代えて、アルミニウムシリコン(AlSi)、アルミニウムシリコン銅(AlSiCu)を用いてもよい。配線270は、絶縁膜340を介して段差部186の側面(Y軸方向側の面)を覆っている。配線270により、段差部186の側面において電界が集中することを抑制でき、その結果、半導体装置10の耐圧破壊を抑制できる。

40

#### 【0045】

縦型MOSトランジスタ300は、積層体100と、ドレイン電極である電極210と、ゲート電極である電極250と、ソース電極である電極240と、により形成されている。保護素子200は、積層体100と、電極230と、電極210とにより形成されている。保護素子200は、縦型MOSトランジスタ300が耐圧破壊することから保護す

50

るために設けられたPN接合ダイオードである。ここで、「耐圧破壊」とは、一度耐圧以上の電圧が印加されると縦型MOSトランジスタ内部が破壊され、元の電流・電圧特性が得られなくなる状態を示す。

【0046】

図2は、半導体装置10を+X軸方向から見た外観図である。図2におけるA-A断面が、図1におけるA-A断面に相当する。半導体装置10は、-Y軸方向側から順に、(i)半導体素子を分離するために用いる素子分離領域と、(ii)保護素子200が形成された領域であるPN接合保護ダイオード形成領域と、(iii)縦型MOSトランジスタ300が形成されたトランジスタ形成領域とを備える。

【0047】

図3は、N型半導体層120とP型半導体層130との界面を+X軸方向から見た概略図である。図2と同様に、図3におけるA-A断面が、図1におけるA-A断面に相当する。凸部115は、段差部186の内周に位置していることがわかる。また、凸部115の内周には、複数のトレンチ184が配されていることが分かる。

【0048】

図4は、半導体装置10に備えられた複数の電極250同士を、配線280により電気的に接続した状態において、半導体装置10を+X軸方向から見た外観図である。なお、図4では、理解を容易とするため、凸部115の位置を斜線および破線で示している。配線280は、隣接する電極250同士を直線で結ぶように配されている。配線280の下に電極250が形成されているが、配線280により電極250の表面が覆われているため、図4では、電極250の位置を破線で示している。配線280の一部は、開口部285が形成されている。開口部285は、電極240に接続された配線(不図示)を引き出すための領域である。本実施形態において、配線280は、アルミニウム(A1)により形成されている。なお、アルミニウム(A1)に代えて、アルミニウムシリコン(A1Si)、アルミニウムシリコン銅(A1SiCu)を用いてもよい。

【0049】

図1に示すように、凸部115の上面は、積層体100の積層方向(X軸方向)から見たときに、電極230の少なくとも一部が重なる位置に配されている。また、トレンチ184の底面(-X軸方向側の面)が接する部分におけるN型半導体層120の厚みd2は、凸部115の上面(+X軸方向側の面)が接する部分におけるN型半導体層120の厚みd5よりも大きい。このため、縦型MOSトランジスタ300に保護素子200の耐圧よりも高いドレイン電圧が印加された場合、電流は、電極250から電極210へ流れるよりも、電極230から電極210へ多く流れる。そして、保護素子200により、電極230と電極210との間の電圧が、保護素子200の耐圧値となる。その結果、電極240と電極210との電圧についても、保護素子200の耐圧値となり、縦型MOSトランジスタ300が耐圧破壊することを防ぐことができる。このようにすることにより、保護素子200は、縦型MOSトランジスタ300を保護することができる。

【0050】

次に、本実施形態の作用効果について説明する。保護素子200は縦型MOSトランジスタ300よりも耐圧を低く、かつ、耐圧破壊しないように設計する必要がある。このため、保護素子200の厚みd5を、縦型MOSトランジスタ300の厚みd2よりも小さくする必要がある。厚みd5を厚みd2よりも小さくする方法として、N型半導体層120の+X軸方向側の一部を除去した後、除去した部分にP型半導体層を再成長する方法が考えられる。しかし、この方法を用いた場合、再成長界面に意図しないN型キャリアが発生することにより、PN接合ダイオードの耐圧が低下することが発明者らの検討の結果、明らかとなった。一方、本実施形態の半導体装置10によれば、凸部115を形成することにより厚みd5を厚みd2よりも小さくしている。凸部115を備える基板110上にN型半導体層120が形成されているため、基板110とN型半導体層120との界面に意図しないN型キャリアが発生したとしても、N型層(110, 120)の間にN型キャリアが形成されるため、保護素子200の耐圧の低下を抑制できる。なお、厚みd5を厚

み  $d_2$  よりも小さくする方法として、P型のイオン注入を用いる方法も考えられる。しかし、半導体として窒化物半導体を用いる場合、P型のイオン注入を行うことは困難である。これに対して、本実施形態では、凸部115を形成するため、P型のイオン注入を行うことなく厚み  $d_5$  を厚み  $d_2$  よりも小さくすることができる。

#### 【0051】

また、積層方向(X軸方向)から見たときに、N型半導体層140は、凸部115の上面と重ならない位置に配されている。このため、縦型MOSトランジスタのドレイン電流は、N型半導体層140と、トレンチ下方の基板110との間を流れるので、縦型MOSトランジスタ300の耐圧が凸部115により低下することはない。保護素子200よりも縦型MOSトランジスタ300の耐圧が下がることは無いので、縦型MOSトランジスタ300の耐圧破壊を抑制することができる。10

#### 【0052】

凸部115の上面が接する部分におけるN型半導体層120の厚み  $d_5$  は、段差部186の底面(-X軸方向側の面)が接する部分における厚み  $d_4$  以下である。このため、段差部186と電極210との間に電流が流れる前に、保護素子200に電流が流れる。この結果、半導体装置10の耐圧破壊を抑制できる。

#### 【0053】

段差部186の底面と凸部115との距離  $d_3$  は、段差部186の底面(-X軸方向側の面)が接する部分における厚み  $d_4$  より大きい。このため、段差部186と電極210との間に段差部186を介して電流が流れる前に、保護素子200に電流が流れる。この結果、半導体装置10の耐圧破壊を抑制できる。20

#### 【0054】

凸部115の上面とトレンチ184の底面との距離  $d_1$  は、トレンチ184の底面が接する部分におけるN型半導体層120の厚み  $d_2$  よりも大きい。このため、保護素子200の耐圧以上の電圧が電極210と配線270との間に印加された場合、電極210から凸部115を介してトレンチ184へ電流が流れる前に、保護素子200に電流が流れる。この結果、半導体装置10の耐圧破壊を抑制できる。

#### 【0055】

図5は、本実施形態の半導体装置10から得られる効果を説明する図である。図5(A)は、本実施形態の等価回路を示す。本実施形態において、保護素子200と縦型MOSトランジスタ300と素子分離領域とが、並列に接続されている。縦型MOSトランジスタ300のドレイン電極(電極210)・ソース電極(電極240)間電圧を電圧  $V_{ds}$  とし、ゲート電極(電極250)・ソース電極(電極240)間電圧を電圧  $V_{gs}$  とし、ドレイン電流を電流  $I_d$  とする。30

#### 【0056】

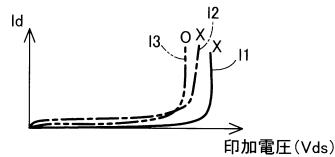

図5(B)は、電流・電圧特性を示す。一点鎖線12は、保護素子200や素子分離領域を備えず、縦型MOSトランジスタ300のみの場合において、ドレイン電極・ソース電極間に電圧  $V_{ds}$  を印加したときの電流  $I_d$  を示す。ゲート電極・ソース電極間電圧  $V_{gs}$  は0Vである。縦型MOSトランジスタ300のみの場合、一点鎖線12におけるXで示す点において、半導体装置の耐圧破壊が起こる。耐圧破壊は、不可逆反応であり、一度起こってしまうと、リーケ電流が大幅に増加し、元の素子特性には戻らず、素子特性は劣化する。40

#### 【0057】

実線11は、素子分離領域のみの場合に、電圧  $V_{ds}$  を印加したときの電流  $I_d$  を示す。実線11におけるXで示す点において、半導体装置の耐圧破壊が起こる。

#### 【0058】

二点鎖線13は、保護素子200のみの場合に、電圧  $V_{ds}$  を印加したときの電流  $I_d$  を示す。二点鎖線13におけるOで示す点において、アバランシェ崩壊により電流が急増するため、これ以上の電圧が印加されることが抑制される。つまり、二点鎖線13で示す結果から、保護素子200が、定電圧ダイオードとして機能することが分かる。ここで、50

保護素子 200 の P N 接合界面は、均一で平坦な面により形成されるため、 P N 接合界面に均等な電界が印加される。この結果、アバランシェ崩壊による P N 接合界面へのダメージが入りにくく、半導体装置の耐圧破壊が起きない。つまり、保護素子 200 の場合、二点鎖線 13 における O で示す点における電圧  $V_{ds}$  が印加されたとしても、不可逆反応は起きない。なお、O で示す点における電圧  $V_{ds}$  よりも低い電圧を印加する場合、二点鎖線 13 に沿った値の電流が流れ、リーク電流は重畠されない。なお、本実施形態の保護素子 200 の接合は、ショットキー接合ではなく、P N 接合である。この理由としては、ショットキー接合に高電圧が印加された場合に金属と半導体との界面が破壊される結果、リーク電流が増加するという不可逆反応が起こる虞があることを挙げることができる。

## 【0059】

10

図 5 (C) は、本実施形態の半導体装置 10 全体に電圧  $V_{ds}$  を印加したときの電流  $I_d$  を示す。なお、図 5 (A) に示すとおり、保護素子 200 と縦型 MOS トランジスタ 300 と素子分離領域とは並列に接続されている。

## 【0060】

図 5 (C) における破線 14 で示されるとおり、半導体装置 10 は保護素子 200 を備えるため、電圧  $V_{ds}$  は、保護素子 200 の特性によって決定される電圧以上になることはない。つまり、素子分離領域に係る電圧及び縦型 MOS トランジスタ 300 のドレイン電極・ソース電極間電圧は、素子分離領域や縦型 MOS トランジスタ 300 の耐圧破壊が起きる電圧よりも小さい電圧が印加されるのみである。例えば、本実施形態の半導体装置 10 の外部から半導体装置 10 へ、素子分離領域や縦型 MOS トランジスタ 300 の耐圧破壊が起きるほどの高い電圧が印加されたとする。このような場合においても、半導体装置 10 は保護素子 200 を備えるため、素子分離領域や縦型 MOS トランジスタ 300 に係る電圧は、保護素子 200 がアバランシェ崩壊する電圧まで抑制される。このため、半導体装置 10 の耐圧破壊を抑制できる。

20

## 【0061】

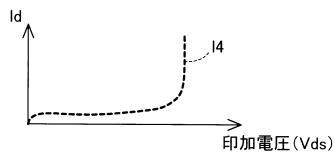

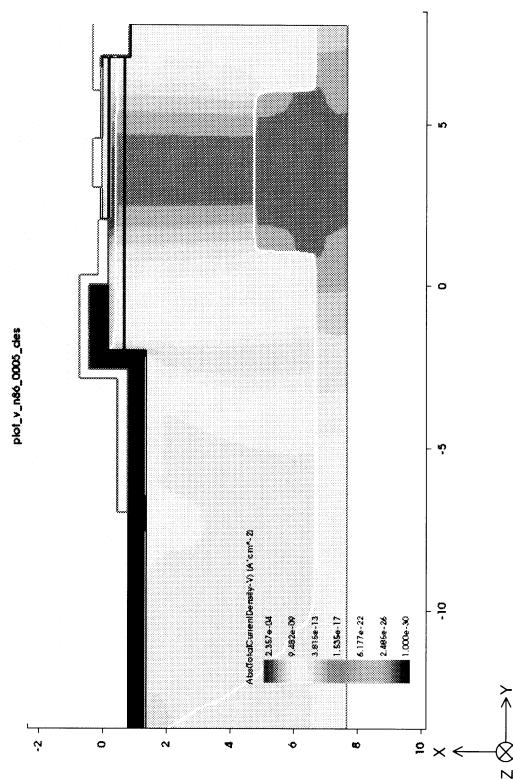

図 6 は、T C A D (Technology CAD) シミュレータにより計算した半導体装置 10 の電流密度分布を示す図である。図面右上方には、ゲートトレンチの左半分が表示されている。図 6 の電流密度分布は、ドレイン電極 (電極 210) ・ソース電極 (電極 240) 間電圧  $V_{ds}$  を 1200V とし、ゲート電極 (電極 250) ・ソース電極 (電極 240) 間電圧  $V_{gs}$  を 0V としたときの分布を示す。凸部 115 の積層方向 (X 軸方向) の厚みは 2  $\mu m$  とし、凸部 115 の幅方向 (Y 軸方向) の厚みは 5  $\mu m$  とした。凸部 115 を除く N 型半導体層 120 の厚み  $d_6$  (図 1 参照) は 6  $\mu m$  とした。段差部 186 の底面が接する部分における厚み  $d_4$  は 5  $\mu m$  とした。

30

## 【0062】

図 6 に示されるとおり、電圧  $V_{ds}$  を 1200V とした場合、凸部 115 の上面から上方 (+ X 軸方向) に向かってインパクトイオン化により電流が流れることが分かる (色の濃い部分)。また、図 6 に示されるとおり、縦型 MOS トランジスタ 300 および素子分離領域において電流密度が低く、インパクトイオン化による電流が流れていないことが分かる (色の薄い部分)。この結果から、半導体装置 10 の耐圧破壊が抑制されていることが分かる。

40

## 【0063】

## A 2 . 半導体装置 10 の製造方法 :

図 7 は、半導体装置 10 の製造方法を示す工程図である。まず、工程 P105 において、基板 110 の面に突出する凸部 115 を形成する。

## 【0064】

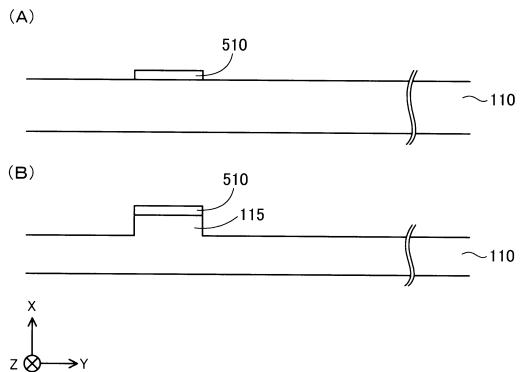

図 8 は、工程 P105 における半導体装置 10 の中間製品を示す断面図である。本実施形態において、工程 P105 では、まず、製造者は、基板 110 の上にプラズマ C V D (Chemical Vapor Deposition) 装置により二酸化ケイ素 ( $SiO_2$ ) の絶縁膜を形成する。次に、製造者は、リソグラフィ法によりパターニングしたレジストをマスクとしてバッファードフッ酸 (BHF : Buffered Hydrogen Fluoride) に浸漬することにより、絶縁膜

50

をエッティングする。その後、製造者は、半導体装置 10 の中間製品を剥離液に浸漬することによりレジストパターンを除去する。図 8 (A) は、基板 110 の上に絶縁膜 510 が形成された半導体装置 10 の中間製品を示す。

【0065】

次に、製造者は、誘導結合方式 (ICP: Inductively Coupled Plasma) を採用したドライエッティング装置により、基板 110 を約  $2 \mu\text{m}$  ドライエッティングする。図 8 (B) は、ドライエッティングを行った後の半導体装置 10 の中間製品を示す。最後に、製造者は、絶縁膜をバッファードフッ酸に浸漬することにより、絶縁膜を除去する。このようにすることにより、基板 110 の面に突出する凸部 115 が形成される。

【0066】

次に、工程 P110 (図 7) において、基板 110 の上に、N型半導体層 120 と、P型半導体層 130 と、N型半導体層 140 と、をこの順に積層する。本実施形態では、製造者は、基板 110 を MOCVD 炉内に導入し、N型半導体層 120 の成長する温度 (例えば、1050) まで加熱する。MOCVD 炉内は、キャリアガスとしての水素 (H) 及びV族元素としてのアンモニア ( $\text{NH}_3$ ) 雰囲気とする。その後、製造者は、III族原料としてトリメチルガリウム (TMGa) とN型不純物としてシラン ( $\text{SiH}_4$ ) を炉内に導入し、ドナー濃度  $1 \times 10^{16} \text{ cm}^{-3}$  程度のN型半導体層 120 を約  $6 \mu\text{m}$  成長させる。ドナー濃度は、 $1 \times 10^{15} \text{ cm}^{-3}$  から  $1 \times 10^{16} \text{ cm}^{-3}$  が好ましく、N型半導体層 120 の厚みは、 $5 \mu\text{m}$  から  $20 \mu\text{m}$  が好ましい。

【0067】

次に、製造者は、III族原料としてトリメチルガリウム (TMGa) とP型不純物としてビス (シクロ pentadienyl) マグネシウム (Cp2Mg: bis (cyclopentadienyl) magnesium) を炉内に導入し、マグネシウム (Mg) 濃度  $4 \times 10^{18} \text{ cm}^{-3}$  程度のP型半導体層 130 を約  $0.7 \mu\text{m}$  成長させる。マグネシウム (Mg) 濃度は、 $1 \times 10^{18} \text{ cm}^{-3}$  以上が好ましく、P型半導体層 130 の厚みは、 $0.5 \mu\text{m}$  から  $2 \mu\text{m}$  が好ましい。

【0068】

次に、本実施形態では、製造者は、III族原料としてトリメチルガリウム (TMGa) とN型不純物としてシラン ( $\text{SiH}_4$ ) を炉内に導入し、ドナー濃度  $1 \times 10^{18} \text{ cm}^{-3}$  程度のN型半導体層 140 を約  $0.2 \mu\text{m}$  成長させる。

【0069】

図 9 は、上記工程 P110 により、基板 110 上に半導体層 (120, 130, 140) を形成させた半導体装置 10 の中間製品を示す断面図である。ここで、再成長界面は、基板 110 と N型半導体層 120 との界面となる。N型半導体層 120 と P型半導体層 130 との界面 (PN接合界面) が再成長界面とする場合、保護素子 200 の耐圧が低下する虞があるが、半導体装置 10 の再成長界面は N型の基板 110 と N型半導体層 120 との界面 (N/N界面) であるため、保護素子 200 の耐圧の低下を抑制できる。

【0070】

工程 P110 の後、工程 P215 (図 7) において、半導体装置 10 の中間製品にトレンチ 184 と段差部 186 とを形成する。製造者は、まずマスクとなる絶縁膜を積層した後、フォトレジストにてパターニングを行なう。その後、エッティングを行なうことにより、製造者は、トレンチ 184 と段差部 186 とを形成する。

【0071】

図 10 は、トレンチ 184 と段差部 186 とを形成させた半導体装置 10 の中間製品を示す断面図である。本実施形態において、エッティングとして、ドライエッティングを採用する。なお、ドライエッティングの後に、エッティングによるダメージ層を除去するため、ウェットエッティングを行なってもよい。

【0072】

次に、工程 P220 (図 7) において、絶縁膜 340 を形成する。製造者は、まずマスクとなる絶縁膜を積層した後、フォトレジストにてパターニングを行なう。

10

20

30

40

50

## 【0073】

図11は、絶縁膜340を形成させた半導体装置10の中間製品を示す断面図である。工程P220によって、絶縁膜340が形成後、パターニングしたレジストをマスクとしてドライエッティングにより一部の絶縁膜340が除去されることにより、凹部182についても形成される。

## 【0074】

工程P240(図7)において、製造者は、リフトオフ法を用いて電極230、240、250を形成する。

## 【0075】

図12は、電極230、240、250を形成させた半導体装置10の中間製品を示す断面図である。

10

## 【0076】

その後、工程P250(図7)において、製造者は、電極230と電極240とを電気的に接続する配線270を形成する。最後に、製造者は、半導体装置10の中間製品の-X側に電極210を形成する(工程P255)。これらの工程を経て、図1に示す半導体装置10が完成する。

## 【0077】

## B. 第2実施形態：

図13は、第2実施形態における半導体装置10Aの構成を模式的に示す図である。半導体装置10Aは、半導体装置10と比較して、凸部の形状が異なるが、それ以外は同じである。半導体装置10Aの凸部115Aの側面(Y軸方向側の面)は、凸部115Aの上面(+X軸方向側の面)に対して傾斜している。本実施形態において、半導体装置10Aの凸部115Aの側面(Y軸方向側の面)は、テーパー形状である。半導体装置10Aの製造方法は、半導体装置10の製造方法と比較して、凸部115Aを形成する工程(工程P105)において異なるが、それ以外は同じである。

20

## 【0078】

図14は、凸部115Aを形成する工程を説明する図である。まず、製造者は、上面に対して側面が傾斜している形状の絶縁膜510Aを形成する。図14(A)は、基板110の上に絶縁膜510Aが形成された半導体装置10Aの中間製品を示す。その後、製造者は、異方性ドライエッティング法によって半導体基板110をエッティングすることにより、凸部115Aを形成する。図14(B)は、凸部115Aが形成された半導体装置10Aの中間製品を示す。凸部の側面を凸部の上面に対して傾斜された形状としても、保護素子の耐圧の低下を抑制する効果が得られる。

30

## 【0079】

## C. 変形例：

この発明は上記の実施形態に限られるものではなく、その要旨を逸脱しない範囲において種々の形態において実施することが可能であり、例えば次のような変形も可能である。

## 【0080】

## C1. 変形例1：

本実施形態において、凸部115はエッティングにより形成したが、本発明はこれに限られない。凸部115の形成方法を、再成長を用いる方法としてもよい。

40

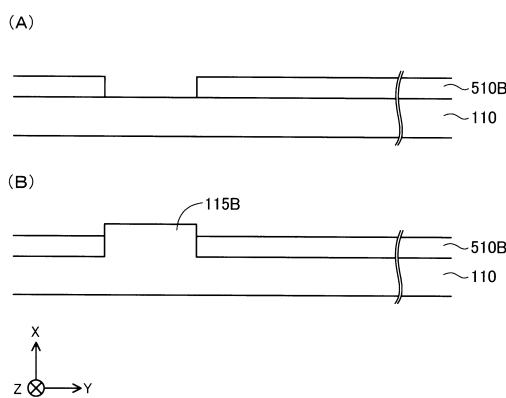

## 【0081】

図15は、再成長により凸部115Bを形成する工程を説明する図である。まず、製造者は、凸部115Bを形成する部分の基板110が露出するように絶縁膜510Bを形成する。図15(A)は、絶縁膜510Bを形成させた半導体装置の中間製品を示す断面図である。次に、製造者は、MOCVD法によって半導体層110を再成長させる。図15(B)は、半導体層110を再成長させた半導体装置の中間製品を示す断面図である。最後に、製造者は、絶縁膜510Bを除去することにより、凸部115Bが形成される。

## 【0082】

## C2. 変形例2：

50

本実施形態において、積層体 100 の積層方向 (X 軸方向) において、N 型半導体層 140 は、凸部 115 の上面と重ならない位置に配されている。しかし、本発明はこれに限らない。

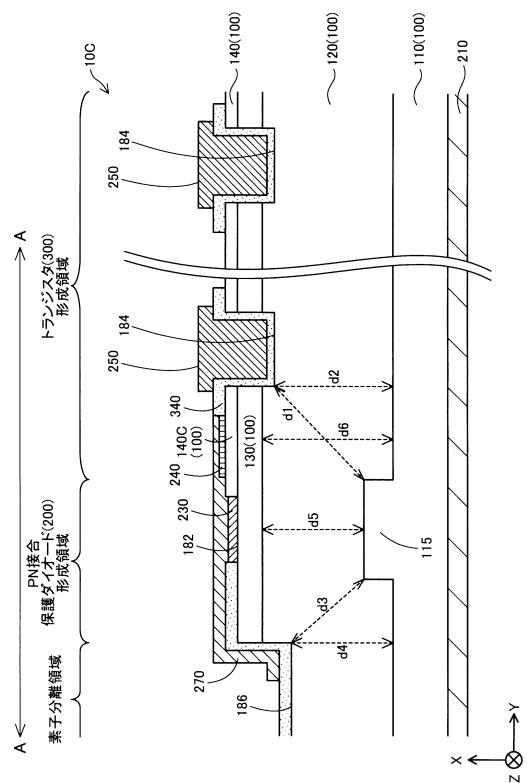

【0083】

図 16 は、積層方向 (X 軸方向) において、N 型半導体層 140C は、凸部 115 の上面の一部と重なる位置に配されている半導体装置 10C の構成を模式的に示す断面図である。N 型半導体層 140C は、凸部 115 の上面の少なくとも一部と重なる位置に配されているてもよい。

【0084】

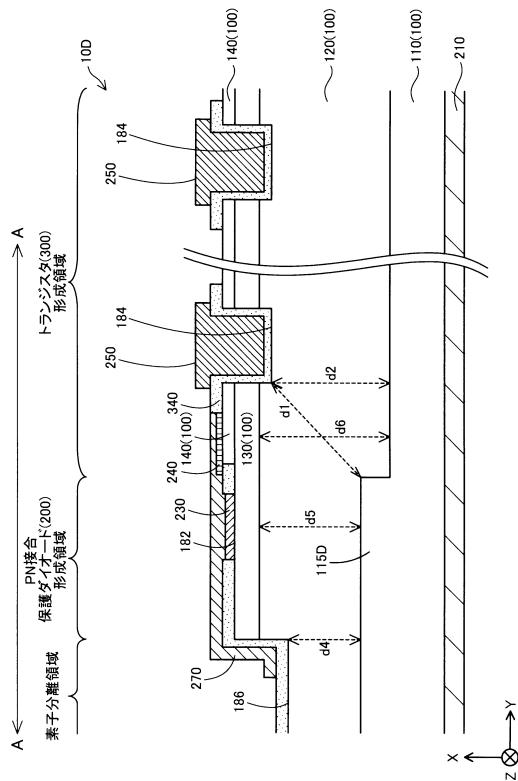

C3. 変形例 3 :

本実施形態において、凸部 115D は、段差部 186 の下方 (-X 軸方向側) には配置されていない。しかし、本発明はこれに限らない。

【0085】

図 17 は、凸部 115D が段差部 186 の下方においても配置されている半導体装置の構成を模式的に示す断面図である。凸部 115D は、段差部 186 の下方に配置されてもよい。この形態によれば、本実施形態の製造方法と比較して、凸部 115D の形成が容易となる。

【0086】

C4. 変形例 4 :

本実施形態において、基板と N 型半導体層との少なくとも一方に含まれるドナーとして、ケイ素 (Si) を用いているが、本発明はこれに限られない。ドナーとして、ゲルマニウム (Ge) や、酸素 (O) を用いてもよい。

【0087】

C5. 変形例 5 :

本実施形態において、P 型半導体層に含まれるアクセプタとして、マグネシウム (Mg) を用いているが、本発明はこれに限られない。アクセプタとして、亜鉛 (Zn) や、炭素 (C) を用いてもよい。

【0088】

C6. 変形例 6 :

本実施形態において、電極 230 は、パラジウム (Pd) から形成される。しかし、本発明はこれに限られない。電極 230 は、他の材料により形成されていてもよく、複数層の構成であってもよい。例えば、電極 230 は、ニッケル (Ni)、白金 (Pt)、コバルト (Co) 等の導電性材料の少なくとも 1 つを含む電極であってもよく、ニッケル (Ni) / パラジウム (Pd) 構成や、白金 (Pt) / パラジウム (Pd) 構成 (パラジウムが半導体基板側) のような 2 層構成であってもよい。

【0089】

C7. 変形例 7 :

本実施形態において、ゲート電極である電極 250 は、アルミニウム (Al) から形成される。しかし、本発明はこれに限られない。電極 250 は、ポリシリコンを用いてもよい。また、電極 250 は、他の材料により形成されていてもよく、複数層の構成であってもよい。例えば、電極 250 は、金 (Au) / ニッケル (Ni) 構成や、アルミニウム (Al) / チタン (Ti) 構成、アルミニウム (Al) / 窒化チタン (TiN) 構成 (それぞれ、ニッケル、チタン、窒化チタンがゲート絶縁膜側) のような 2 層構成であってもよいし、窒化チタン (TiN) / アルミニウム (Al) / 窒化チタン (TiN) 構成のような 3 層構成であってもよい。

【0090】

本発明は、上述の実施形態や変形例に限られるものではなく、その趣旨を逸脱しない範囲において種々の構成で実現することができる。例えば、発明の概要の欄に記載した各形態中の技術的特徴に対応する実施形態、変形例中の技術的特徴は、上述の課題の一部又は全部を解決するために、あるいは、上述の効果の一部又は全部を達成するために、適宜、

10

20

30

40

50

差し替えや、組み合わせを行うことが可能である。また、その技術的特徴が本明細書中に必須なものとして説明されていなければ、適宜、削除することが可能である。

【符号の説明】

【0091】

|         |              |    |

|---------|--------------|----|

| 1 0     | …半導体装置       |    |

| 1 0 A   | …半導体装置       |    |

| 1 0 C   | …半導体装置       |    |

| 1 0 0   | …積層体         |    |

| 1 1 0   | …基板          |    |

| 1 1 5   | …凸部          | 10 |

| 1 1 5 A | …凸部          |    |

| 1 1 5 B | …凸部          |    |

| 1 1 5 D | …凸部          |    |

| 1 2 0   | …N型半導体層      |    |

| 1 3 0   | …P型半導体層      |    |

| 1 4 0   | …N型半導体層      |    |

| 1 4 0 C | …N型半導体層      |    |

| 1 8 2   | …凹部          |    |

| 1 8 4   | …トレンチ        |    |

| 1 8 6   | …段差部         | 20 |

| 2 0 0   | …保護素子        |    |

| 2 1 0   | …電極          |    |

| 2 3 0   | …電極          |    |

| 2 4 0   | …電極          |    |

| 2 5 0   | …電極          |    |

| 2 7 0   | …配線          |    |

| 2 8 0   | …配線          |    |

| 2 8 5   | …開口部         |    |

| 3 0 0   | …縦型MOSトランジスタ |    |

| 3 4 0   | …絶縁膜         | 30 |

| 5 1 0   | …絶縁膜         |    |

| 5 1 0 A | …絶縁膜         |    |

| 5 1 0 B | …絶縁膜         |    |

| I d     | …電流          |    |

| V d s   | …電圧          |    |

| V g s   | …電圧          |    |

| d 1     | …距離          |    |

| d 3     | …距離          |    |

| l 1     | …実線          |    |

| l 2     | …一点鎖線        | 40 |

| l 3     | …二点鎖線        |    |

| l 4     | …破線          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

図5

(B)

(C)

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

图 15

## 【図16】

図16

### 【図17】

図17

---

フロントページの続き

| (51)Int.Cl. |                  | F I     |       |         |

|-------------|------------------|---------|-------|---------|

| H 0 1 L     | 27/06 (2006.01)  | H 0 1 L | 29/91 | D       |

| H 0 1 L     | 21/822 (2006.01) | H 0 1 L | 29/91 | B       |

| H 0 1 L     | 27/04 (2006.01)  | H 0 1 L | 29/91 | F       |

|             |                  | H 0 1 L | 27/06 | 3 1 1 B |

|             |                  | H 0 1 L | 27/04 | H       |

(72)発明者 岡 徹

愛知県清須市春日長畑1番地 豊田合成株式会社内

(72)発明者 上野 幸久

愛知県清須市春日長畑1番地 豊田合成株式会社内

審査官 早川 朋一

(56)参考文献 特開2014-192191 (JP, A)

特表2005-520322 (JP, A)

特開平10-321877 (JP, A)

特開2010-114248 (JP, A)

特開平02-005482 (JP, A)

特開2014-209540 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 7 / 0 4

H 0 1 L 2 7 / 0 6 - 2 7 / 0 7