(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6375960号

(P6375960)

(45) 発行日 平成30年8月22日(2018.8.22)

(24) 登録日 平成30年8月3日(2018.8.3)

|                        |                    |

|------------------------|--------------------|

| (51) Int.Cl.           | F 1                |

| HO 1 S 5/026 (2006.01) | HO 1 S 5/026 6 1 8 |

| HO 1 S 5/227 (2006.01) | HO 1 S 5/227       |

| GO 2 B 6/12 (2006.01)  | GO 2 B 6/12 3 0 1  |

請求項の数 3 (全 9 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2015-8745 (P2015-8745)      |

| (22) 出願日  | 平成27年1月20日 (2015.1.20)        |

| (65) 公開番号 | 特開2016-134522 (P2016-134522A) |

| (43) 公開日  | 平成28年7月25日 (2016.7.25)        |

| 審査請求日     | 平成29年6月15日 (2017.6.15)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100082175<br>弁理士 高田 守                      |

| (74) 代理人  | 100106150<br>弁理士 高橋 英樹                     |

| (74) 代理人  | 100148057<br>弁理士 久野 淑己                     |

| (72) 発明者  | 境野 剛<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内        |

審査官 大和田 有軌

最終頁に続く

(54) 【発明の名称】光半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

n型半導体基板と、

前記n型半導体基板上に形成され、メサストライプ状に加工された活性層と、前記活性層上に形成されたp型クラッド層とを有する半導体レーザ部と、

前記n型半導体基板上において前記活性層の光出力側に形成され、メサストライプ状に加工された光導波路層と、前記光導波路層上に形成された上クラッド層とを有する光導波路部と、

前記活性層及び前記光導波路層の両側を埋め込む半導体の電流狭窄層と、

前記半導体レーザ部上に形成されたp型半導体層と、

前記光導波路部上に形成されたリーコ電流抑制層とを備え、

前記上クラッド層は、前記p型クラッド層よりキャリア濃度が低い第1の低キャリア濃度層と、前記第1の低キャリア濃度層上に形成された第1のF<sub>e</sub>ドープ半導体層とを有し、前記リーコ電流抑制層は、前記p型半導体層のサイドに配置された第2のF<sub>e</sub>ドープ半導体層を有し、

前記第1の低キャリア濃度層は前記p型クラッド層の側面に接する側壁部を有し、

前記第1のF<sub>e</sub>ドープ半導体層は、前記第1の低キャリア濃度層の前記側壁部を介して前記p型クラッド層のサイドに配置され、前記p型クラッド層に接していないことを特徴とする光半導体装置。

**【請求項 2】**

前記第2のF eドープ半導体層は前記p型半導体層の側面に接することを特徴とする請求項1に記載の光半導体装置。

**【請求項 3】**

前記リーク電流抑制層は、前記p型半導体層よりキャリア濃度が低い第2の低キャリア濃度層を更に有し

前記第2の低キャリア濃度層は前記p型半導体層の側面に接する側壁部を有し、

前記第2のF eドープ半導体層は、前記第2の低キャリア濃度層の前記側壁部を介して前記p型半導体層のサイドに配置され、前記p型半導体層に接していないことを特徴とする請求項1に記載の光半導体装置。10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体レーザ部と光導波路部を集積した光半導体装置において、半導体レーザ部と光導波路部の間の電気的分離と高い光結合効率を両立することができる光半導体装置に関する。

**【背景技術】****【0002】**

光半導体装置において、半導体レーザと光導波路や光変調器などを集積することにより小型化や高性能化が進んでいる。基板上に半導体レーザに代表される光能動素子と光導波路を集積した集積型光半導体装置が知られている。一般に集積型光半導体装置では集積された複数の構成間の電気的分離が行われる。半導体レーザ部及び光導波路部上に設けられたp型半導体層は半導体レーザ部に電流を供給する必要から高抵抗層ではない。そこで、半導体レーザ部と光導波路部の間においてp型半導体層に分離溝を設けることで、半導体レーザ部と光導波路部を電気的に分離した装置が提案されている（例えば、特許文献1参照）。

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特許第5463760号公報20

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

半導体レーザ部からの信号光を光導波路部に高い結合効率で結合する必要がある。しかし、半導体レーザ部と光導波路部を電気的に分離する分離溝を深くすると半導体レーザ部からの光を光導波路部に結合する際に光の反射や散乱が発生し、高い結合効率が得られないという問題がある。

**【0005】**

本発明は、上述のような課題を解決するためになされたもので、その目的は半導体レーザ部と光導波路部の間の電気的分離と高い光結合効率を両立することができる光半導体装置を得るものである。30

**【課題を解決するための手段】****【0006】**

本発明に係る光半導体装置は、n型半導体基板と、前記n型半導体基板上に形成され、メアストライプ状に加工された活性層と、前記活性層上に形成されたp型クラッド層とを有する半導体レーザ部と、前記n型半導体基板上において前記活性層の光出力側に形成され、メアストライプ状に加工された光導波路層と、前記光導波路層上に形成された上クラッド層とを有する光導波路部と、前記活性層及び前記光導波路層の両側を埋め込む半導体の電流狭窄層と、前記半導体レーザ部上に形成されたp型半導体層と、前記光導波路部上に形成されたリーク電流抑制層とを備え、前記上クラッド層は、前記p型クラッド層より40

キャリア濃度が低い第1の低キャリア濃度層と、前記第1の低キャリア濃度層上に形成された第1のFeドープ半導体層とを有し、前記リーキ電流抑制層は、前記p型半導体層のサイドに配置された第2のFeドープ半導体層を有し、前記第1の低キャリア濃度層は前記p型クラッド層の側面に接する側壁部を有し、前記第1のFeドープ半導体層は、前記第1の低キャリア濃度層の前記側壁部を介して前記p型クラッド層のサイドに配置され、前記p型クラッド層に接していないことを特徴とする。

【発明の効果】

【0007】

本発明では、半導体レーザ部上のp型半導体層のサイドに第2のFeドープ半導体層を設けたことにより、半導体レーザ部上のp型半導体層から光導波路部へのリーキ電流を抑制することができる。また、第2のFeドープ半導体層を設けても、半導体レーザ部からの光を光導波路部に結合する際に光の反射や散乱は発生しない。従って、半導体レーザ部と光導波路部の間の電気的分離と高い光結合効率を両立することができる。

【図面の簡単な説明】

【0008】

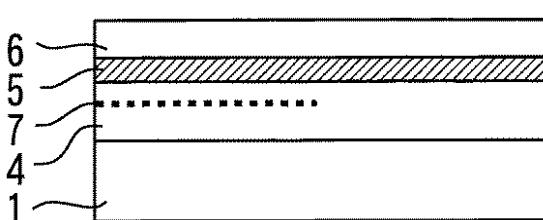

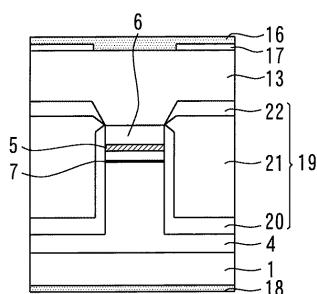

【図1】本発明の実施の形態1に係る光半導体装置を示す断面図である。

【図2】図1のI-I'I'I'に沿った断面図である。

【図3】図1のI'I'I'I'Vに沿った断面図である。

【図4】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図5】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図6】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図7】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図8】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図9】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図10】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図11】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図12】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図13】本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。

【図14】比較例に係る光半導体装置を示す断面図である。

【図15】本発明の実施の形態2に係る光半導体装置を示す断面図である。

【図16】本発明の実施の形態3に係る光半導体装置を示す断面図である。

【発明を実施するための形態】

【0009】

本発明の実施の形態に係る光半導体装置について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

【0010】

実施の形態1.

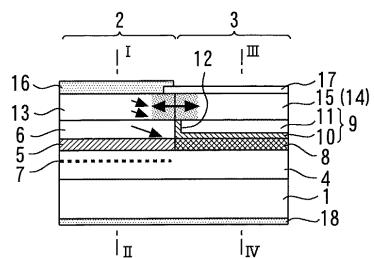

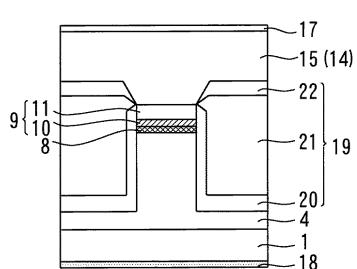

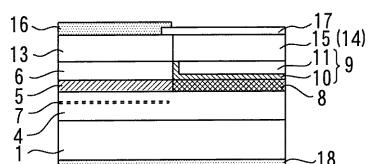

図1は、本発明の実施の形態1に係る光半導体装置を示す断面図である。図1は光半導体装置の共振器方向、即ちレーザ光の進行方向と平行に切断した断面図である。この光半導体装置は、n型InP基板1上に半導体レーザ部2と光導波路部3とが集積された集積型光半導体装置である。

【0011】

半導体レーザ部2は、n型InP基板1上に順に形成されたn型InPクラッド層4、活性層5、p型InPクラッド層6を有する。n型InPクラッド層4に回折格子7が形成されており、半導体レーザ部2は分布帰還型半導体レーザである。n型InPクラッド層4のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。活性層5は厚さ0.2μmのAlGaInAs歪量子井戸活性層である。p型InPクラッド層6のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。

【0012】

光導波路部3は活性層5の光出力側に形成されている。光導波路部3は、n型InP基

10

20

30

40

50

板1上に順に形成されたn型InPクラッド層4、光導波路層8、上クラッド層9を有する。光導波路層8は厚さ0.2μmのInGaAsP光導波層である。活性層5の端面は光導波路層8の端面と接し、活性層5からのレーザ光が光導波路層8を通って紙面右側に向かって進行する。

【0013】

上クラッド層9は、低キャリア濃度InP層10と、低キャリア濃度InP層10上に形成されたFeドープInP層11を有する。低キャリア濃度InP層10はp型InPクラッド層6よりキャリア濃度が低く、電気抵抗が高い。FeドープInP層11のキャリア濃度は $5 \times 10^{16} \text{ cm}^{-3}$ である。p型InPクラッド層6の厚さ0.2μmに対して、低キャリア濃度InP層10とFeドープInP層11の厚さはそれぞれ0.1μmである。 10

【0014】

低キャリア濃度InP層10は、光導波路層8の上面とp型InPクラッド層6の側面を連続的に被覆し、p型InPクラッド層6の側面に接する側壁部12を有する。FeドープInP層11は、低キャリア濃度InP層10の上面及び側面を連続的に被覆し、低キャリア濃度InP層10の側壁部12を介してp型InPクラッド層6のサイドに配置され、p型InPクラッド層6に接していない。

【0015】

p型InP層13が半導体レーザ部2上に形成されている。p型InP層13のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。リーク電流抑制層14が光導波路部3上、即ちFeドープInP層11及び低キャリア濃度InP層10の側壁部12上に形成されている。リーク電流抑制層14は、p型InP層13のサイドに配置されたFeドープInP層15を有する。FeドープInP層15はp型InP層13の側面に接する。FeドープInP層15のキャリア濃度は $5 \times 10^{16} \text{ cm}^{-3}$ である。 20

【0016】

p型InP層13上にはTi/Pt/Auのp型電極16が形成されている。FeドープInP層15上にはSiO<sub>2</sub>絶縁膜17が形成されている。n型InP基板1上の裏面にはTi/Pt/Auのn型電極18が形成されている。

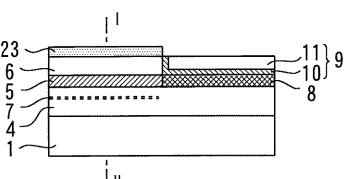

【0017】

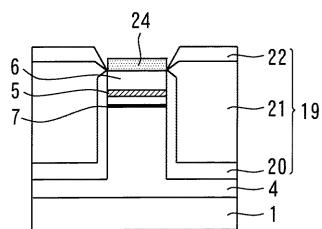

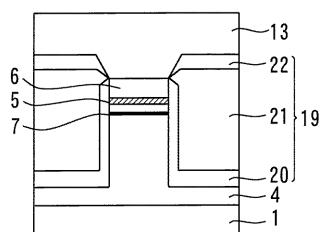

図2は図1のI-I'Iに沿った断面図である。即ち、図2は半導体レーザ部2を共振器方向と垂直に切断した断面図である。図3は図1のI'I'I-I'Vに沿った断面図である。即ち、図3は光導波路部3を共振器方向と垂直に切断した断面図である。半導体レーザ部2と光導波路部3の積層構造はメサストライプ状に加工されている。半導体の電流狭窄層19が活性層5及び光導波路層8の両側を埋め込む。電流狭窄層19は順に積層されたp型InP埋込み層20、FeドープInP埋込み層21、n型InP埋込み層22を有する。p型InP埋込み層20のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。FeドープInP埋込み層21のキャリア濃度は $5 \times 10^{16} \text{ cm}^{-3}$ である。n型InP埋込み層22のキャリア濃度は $5 \times 10^{18} \text{ cm}^{-3}$ である。 30

【0018】

図4～図13は、本発明の実施の形態1に係る光半導体装置の製造工程を示す断面図である。図7～図10は図6のI-I'Iに沿って切断した断面を示す。即ち、図7～図10は半導体レーザ部2を共振器方向と垂直に切断した断面図である。 40

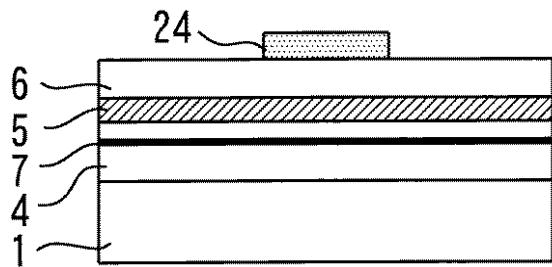

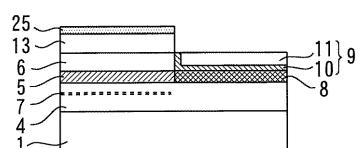

【0019】

まず、図4に示すように、n型InP基板1上にn型InPクラッド層4をMOCVD法により結晶成長させる。電子ビーム露光を用いて回折格子7を形成した後、n型InPクラッド層4を追加再成長する。n型InPクラッド層4上にAlGaInAs歪量子井戸の活性層5とp型InPクラッド層6を結晶成長させる。

【0020】

次に、図5に示すように、p型InPクラッド層6上にSiO<sub>2</sub>絶縁膜23を形成し、パターニング、ドライエッチングを行うことにより活性層5とp型InPクラッド層6の 50

紙面右側部分をエッティング除去する。

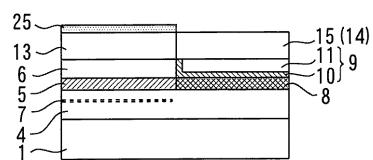

【0021】

次に、図6に示すように、エッティング除去した部分にInGaAsPの光導波路層8をMOCVD法により結晶成長させる。さらに、光導波路層8の上面及びp型InPクラッド層6の側面に対して低キャリア濃度InP層10をMOCVD法により結晶成長させる。FeドープInP層11をp型InPクラッド層6に接しないよう結晶成長させる。その後、SiO<sub>2</sub>絶縁膜23をエッティング除去する。

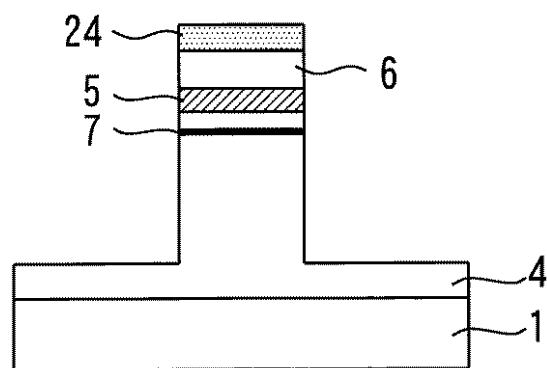

【0022】

次に、図7に示すように、SiO<sub>2</sub>絶縁膜24を成膜、パターニングする。次に、図8に示すように、ドライエッティング等によりリッジを形成する。次に、図9に示すようにp型InP埋込み層20、FeドープInP埋込み層21、n型InP埋込み層22をMOCVD法により結晶成長させる。その後、SiO<sub>2</sub>絶縁膜24をエッティング除去する。

10

【0023】

次に、図10に示すように、半導体レーザ部2のp型InP層13をMOCVD法により結晶成長させる。次に、図11に示すように、SiO<sub>2</sub>絶縁膜25を形成し、パターニング、ドライエッティングを行うことにより、p型InP層13の紙面右側部分をエッティング除去する。

【0024】

次に、図12に示すように、エッティング除去した部分にFeドープInP層15をMOCVD法により結晶成長させる。その後、SiO<sub>2</sub>絶縁膜25をエッティング除去する。次に、図13に示すように、SiO<sub>2</sub>絶縁膜17、p型電極16、n型電極18を形成する。以上の工程により本実施の形態に係る光半導体装置が製造される。

20

【0025】

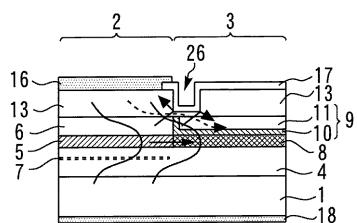

続いて、本実施の形態に係る光半導体装置の動作について説明する。半導体レーザ部2に電流を注入すると、p型InP層13とp型InPクラッド層6を介して活性層5に電流が流れ、活性層5でレーザ光が放射される。そのレーザ光は光導波路層8を通って図1の右方向へと進行し、出射される。

【0026】

続いて、本実施の形態の効果を比較例と比較して説明する。図14は比較例に係る光半導体装置を示す断面図である。比較例では光導波路部3上にFeドープInP層15ではなく、半導体レーザ部2上と同様にp型InP層13が形成されている。半導体レーザ部2と光導波路部3の間においてp型InP層13に分離溝26を設けることで、半導体レーザ部2と光導波路部3を電気的に分離している。その他の構成は本実施の形態と同様である。

30

【0027】

図2のような埋込層を用いた場合、半導体レーザ部2にて高い電流注入効率を得るためににはp型InPクラッド層6の厚さを50～200nm程度とする必要がある。半導体レーザ部2と光導波路部3の十分に電気的な分離を行うためには、分離溝26の底部をp型InPクラッド層6の上端から1μm程度まで接近させる必要がある。この時、半導体レーザ部2側からの導波光はp型InPクラッド層6の方向に広がりを持つため、その導波光が分離溝26の側面に干渉することで、反射や散乱を引き起こし、光導波路部3との光結合効率が十分に確保できない。

40

【0028】

また、光の反射や散乱を避けるために分離溝26の底部をp型InPクラッド層6の上端から離した場合、電気的な分離が不十分となり、一部の電流が図15の点線矢印に示すように光導波路部3側へと流れてしまう。この電流はレーザ光の発光に寄与せずにリーク電流成分となり、この電流リークが電流光出力特性を悪化させてしまう。

【0029】

これに対して、本実施の形態では、p型InP層13とFeドープInP層15の間に分離溝は形成されていない。その代わりに半導体レーザ部2上のp型InP層13のサイ

50

ドに高抵抗層として Fe ドープ InP 層 15 を設けたことにより、半導体レーザ部 2 上の p 型 InP 層 13 から光導波路部 3 へのリーク電流を抑制することができる。また、低キャリア濃度 InP 層 10 と Fe ドープ InP 層 11 も高抵抗層として作用する。そして、Fe ドープ InP 層 15 を設けても、半導体レーザ部 2 からの光を光導波路部 3 に結合する際に光の反射や散乱は発生しない。従って、半導体レーザ部 2 と光導波路部 3 の間の電気的分離と高い光結合効率を両立することができる。

#### 【0030】

また、半導体レーザ部 2 の p 型 InP クラッド層 6 と光導波路部 3 の Fe ドープ InP 層 11 の間に低キャリア濃度 InP 層 10 の側壁部 12 が存在するため、Fe と Zn の相互拡散による高抵抗化が進まない。従って、半導体レーザ部 2 の活性層 5 への電流注入阻害を抑制することができるため、半導体レーザ部 2 の電流光出力特性の悪化を防ぐことができる。

10

#### 【0031】

また、Fe ドープ InP 層 15 は p 型 InP 層 13 の側面に接する。半導体層中でドーパントとして用いられた Fe と Zn は相互拡散が極めて大きいため、Fe ドープ InP 層 15 と p 型 InP 層 13 との間で Fe と Zn の相互拡散が発生する。従って、両者の境界部分で p 型 InP 層 13 の p 型キャリア濃度が減少し、高抵抗化が進む。これにより、p 型 InP 層 13 と Fe ドープ InP 層 15 の間の抵抗が更に高くなるため、Fe ドープ InP 層 15 だけを高抵抗化した場合よりもリーク電流を低減することができる。

#### 【0032】

20

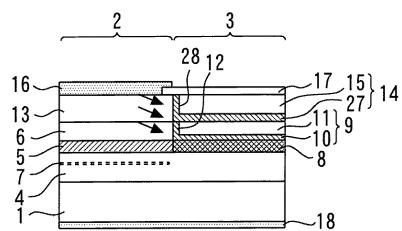

実施の形態 2 .

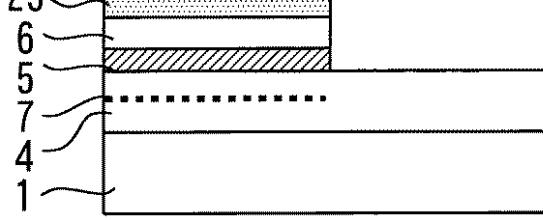

図 15 は、本発明の実施の形態 2 に係る光半導体装置を示す断面図である。本実施の形態では、リーク電流抑制層 14 は、p 型 InP 層 13 よりキャリア濃度が低い低キャリア濃度 InP 層 27 を更に有する。低キャリア濃度 InP 層 27 は p 型 InP 層 13 の側面に接する側壁部 28 を有する。Fe ドープ InP 層 15 は、低キャリア濃度 InP 層 27 の側壁部 28 を介して p 型 InP 層 13 のサイドに配置され、p 型 InP 層 13 に接していない。その他の構成は実施の形態 1 と同様である。

#### 【0033】

半導体レーザ部 2 上の p 型 InP 層 13 と光導波路部 3 上の Fe ドープ InP 層 15 の間に低キャリア濃度 InP 層 27 の側壁部 28 が存在するため、Fe と Zn の相互拡散による高抵抗化が進まない。従って、本来導電性が必要な半導体レーザ部 2 上の p 型 InP 層 13 の高抵抗化を防ぐことができる。これにより、半導体レーザ部 2 の活性層 5 への電流注入阻害を抑制しつつ、かつ半導体レーザ部 2 の p 型 InP 層 13 から光導波路部 3 へのリーク電流を抑制することができる。

30

#### 【0034】

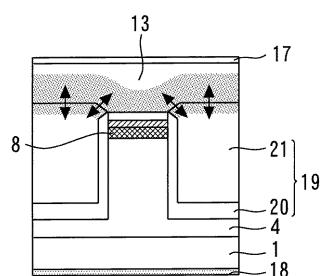

実施の形態 3 .

図 16 は、本発明の実施の形態 3 に係る光半導体装置を示す断面図である。図 16 は光導波路部 3 を共振器方向と垂直に切断した断面図である。p 型 InP 層 13 が半導体レーザ部 2 、光導波路部 3 、及び電流狭窄層 19 上に形成されている。

40

#### 【0035】

半導体レーザ部 2 の両側を埋め込む電流狭窄層 19 は、実施の形態 1 の図 2 と同様に p 型 InP 埋込み層 20 、Fe ドープ InP 埋込み層 21 、n 型 InP 埋込み層 22 を有する。一方、光導波路層 8 の両側を埋め込む電流狭窄層 19 は、p 型 InP 埋込み層 20 と Fe ドープ InP 埋込み層 21 である。

#### 【0036】

製造方法としては、実施の形態 1 と同様に埋込層を形成した後、絶縁膜などを用いてパターンニング、ドライエッチングなどで光導波路部 3 のみ n 型 InP 埋込み層 22 を除去する。その後、絶縁膜を除去し、光導波路部 3 上に Fe ドープ InP 層 15 の代わりに p 型 InP 層 13 を形成する。その他の工程は実施の形態 1 と同様である。

50

## 【0037】

本実施の形態では、光導波路層8の両側を埋め込む電流狭窄層19の最上層がFeドープInP埋込み層21であり、このFeドープInP埋込み層21がp型InP層13に接している。両者の間でFeとZnの相互拡散が起こり、p型InP層13の下部が高抵抗層として作用する。これにより、半導体レーザ部2のp型InP層13から光導波路部3へのリーク電流を抑制することができる。また、この構成では半導体レーザ部2からの光を光導波路部3に結合する際に光の反射や散乱は発生しない。従って、半導体レーザ部2と光導波路部3の間の電気的分離と高い光結合効率を両立することができる。

## 【0038】

なお、実施の形態1～3にかかる光半導体装置は半導体レーザ部2と光導波路部3が集積された光導波路集積型光半導体装置である。しかし、本発明はこれに限られるものではない。光変調器や光増幅器などの光能動素子と光導波路とが隣接して集積されている構成にも実施の形態1～3と同様の構成を適用することができる。また、製造方法や使用する材料は実施の形態1～3で示したものに限られず、同様の効果が得られれば、構成や製造方法は必ずしも上述の内容に限定するものではない。

## 【符号の説明】

## 【0039】

1 n型InP基板、2 半導体レーザ部、3 光導波路部、5 活性層、6 p型InPクラッド層、8 光導波路層、9 上クラッド層、10 低キャリア濃度InP層、11, 15 FeドープInP層、12, 28 側壁部、13 p型InP層、14 リーク電流抑制層、19 電流狭窄層、21 FeドープInP埋込み層、27 低キャリア濃度InP層

10

20

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2005-317659(JP,A)

特開2003-069136(JP,A)

特開2011-014712(JP,A)

特開2009-038120(JP,A)

特開2008-071906(JP,A)

特開2003-229635(JP,A)

特開2002-299752(JP,A)

特開平08-148758(JP,A)

特開平06-077583(JP,A)

欧州特許出願公開第02403077(EP,A1)

米国特許出願公開第2002/0009114(US,A1)

(58)調査した分野(Int.Cl., DB名)

|        |         |   |           |

|--------|---------|---|-----------|

| H 01 S | 5 / 0 0 | - | 5 / 5 0   |

| G 02 B | 6 / 1 2 | - | 6 / 1 4   |

| G 02 B | 6 / 4 2 | - | 6 / 4 3   |

| G 02 F | 1 / 0 0 | - | 1 / 1 2 5 |