(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4826626号

(P4826626)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月22日(2011.9.22)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1337 (2006.01)

G02F 1/1337 505

請求項の数 12 (全 15 頁)

(21) 出願番号

特願2008-311607 (P2008-311607)

(22) 出願日

平成20年12月5日 (2008.12.5)

(65) 公開番号

特開2010-134294 (P2010-134294A)

(43) 公開日

平成22年6月17日 (2010.6.17)

審査請求日

平成22年4月27日 (2010.4.27)

前置審査

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 石井 裕満

東京都八王子市石川町2951番地の5

カシオ計算機株式会社八王子技術センター

内

審査官 前川 慎喜

最終頁に続く

(54) 【発明の名称】 液晶表示素子

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電層として予め定めた方向に延伸するように配置されたゲート線と、

前記第1の導電層として配置された第1の補助容量電極と、

前記ゲート線にゲート電極が接続され、半導体層に形成されるチャネルのチャネル幅方

向が前記ゲート線の延伸する前記方向と平行に配置された薄膜トランジスタと、

前記第1の導電層よりも液晶層に近く、前記第1の導電層に対して絶縁層を介して第2

の導電層として配置された第1の画素電極と、

前記第2の導電層として、前記ゲート線の配置領域と前記第1の画素電極の配置領域と

の間の領域に少なくとも一部が配置された遮蔽電極と、

前記第1の導電層と前記第2の導電層との間の層として、前記遮蔽電極に対して少なく

とも一部が平面視して重なるように配置され、前記薄膜トランジスタのソース電極と前記

第1の画素電極とを電気的に接続する接続部と、

前記液晶層を介して前記第1の画素電極に対向し、前記遮蔽電極と等しい電位に設定さ

れる共通電極と、

を備え、

前記第1の補助容量電極は、少なくとも一部が前記第1の画素電極と平面視して重なり

、且つ、前記第1の画素電極の周囲を囲むように配置され、前記遮蔽電極と等しい電位に

設定され、

前記第1の補助容量電極と前記接続部とは平面視して重なる領域を有し、

10

20

前記遮蔽電極は、前記第1の画素電極に接触することなく、前記第1の補助容量電極と前記接続部との前記重なる領域を覆うように、前記ゲート線の延伸する前記方向に平行、且つ、前記薄膜トランジスタの前記チャネル幅方向に平行に配置されている、ことを特徴とする液晶表示素子。

【請求項2】

前記第1の画素電極との間に前記ゲート線が介在するように、前記第2の導電層として配置された第2の画素電極と、

前記第1の導電層として配置され、前記遮蔽電極と等しい電位に設定される第2の補助容量電極と、

を備え、

10

前記第2の補助容量電極は、少なくとも一部が前記第2の画素電極と平面視して重なり、且つ、前記第2の画素電極の周囲を囲むように配置されていることを特徴とする請求項1に記載の液晶表示素子。

【請求項3】

前記遮蔽電極は、前記第1の導電層と前記第2の導電層との間に配置された絶縁層に設けられたコンタクトホールを介して前記第2の補助容量電極に接続されていることを特徴とする請求項2に記載の液晶表示素子。

【請求項4】

前記コンタクトホールは、前記ゲート線と前記第2の画素電極との間の領域に形成されていることを特徴とする請求項3に記載の液晶表示素子。

20

【請求項5】

前記ゲート線は、前記第1の画素電極の配置方向とは異なる側に向かって前記ゲート配線から張り出した張出部を有し、

前記薄膜トランジスタは、前記張出部が前記ゲート電極になっていることを特徴とする請求項4に記載の液晶表示素子。

【請求項6】

前記薄膜トランジスタに対して前記コンタクトホールが前記ゲート線の延伸する前記方向に沿って隣接するように配置されていることを特徴とする請求項5に記載の液晶表示素子。

【請求項7】

30

前記ゲート線に対して交差するように配置され、前記薄膜トランジスタのドレイン電極に接続された信号線と、

前記第1の画素電極との間に前記信号線が介在するように、前記第2の導電層として配置された第2の画素電極と、

を備え、

前記遮蔽電極は、前記信号線を跨ぐようにして、少なくとも前記第2の画素電極の配置領域と前記ゲート線の配置領域との間の領域まで延伸されていることを特徴とする請求項1に記載の液晶表示素子。

【請求項8】

前記ゲート線に対して交差するように配置され、前記薄膜トランジスタのドレイン電極に接続された信号線と、

40

前記第1の画素電極との間に前記信号線が介在するように、前記第2の導電層として配置された第2の画素電極と、

を備え、

前記遮蔽電極は、前記ゲート線の延伸する前記方向に沿って、少なくとも前記第2の画素電極の配置領域と前記ゲート線の配置領域との間の領域まで延伸されていることを特徴とする請求項1に記載の液晶表示素子。

【請求項9】

前記液晶層における前記第1の画素電極に対応した領域が、前記遮蔽電極または前記第1の補助容量電極に与えられる電位で包囲されるように、前記遮蔽電極と前記第1の補助

50

容量電極とが配置されていることを特徴とする請求項1から8の何れかに記載の液晶表示素子。

【請求項10】

前記液晶層は、誘電率異方性が負の液晶分子からなることを特徴とする請求項1から9の何れかに記載の液晶表示素子。

【請求項11】

前記第1の画素電極は、複数のスリットが形成されていることを特徴とする請求項1から10の何れかに記載の液晶表示素子。

【請求項12】

前記接続部は、前記第1の補助容量電極と前記遮蔽電極とが平面視して重なる領域に、前記薄膜トランジスタにおける前記チャネル幅方向に沿う方向の長さが前記チャネル幅よりも長く形成された領域を有していることを特徴とする請求項1から11の何れかに記載の液晶表示素子。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶の配向を安定に制御した液晶表示素子に関する。

【背景技術】

【0002】

液晶表示素子は、間隔を開けて対向する一対の基板のうち一方の基板に、マトリックス状に設けられた複数の画素電極と、これらの複数の画素電極にそれぞれ対応して設けられて接続される複数の薄膜トランジスタと、各薄膜トランジスタにゲート信号とデータ信号とをそれぞれ供給する複数の走査線および複数の信号線と、を設ける一方、他方の基板に複数の画素電極と対向する共通の共通電極（対向電極）を設け、一対の基板の対向面にそれぞれに配向膜を設け、液晶を封入して構成されている。液晶表示素子は、画素毎に画素電極に電圧を印加することで液晶の配向を制御している。特に、特許文献1に開示されている垂直配向型の液晶表示素子では、一方の基板に突起を設け、画素電極に電圧を印加した際垂直配向状態の液晶分子が突起に向かって倒れることで安定に液晶配向を制御している。

20

【0003】

30

【特許文献1】特開2008-83389号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

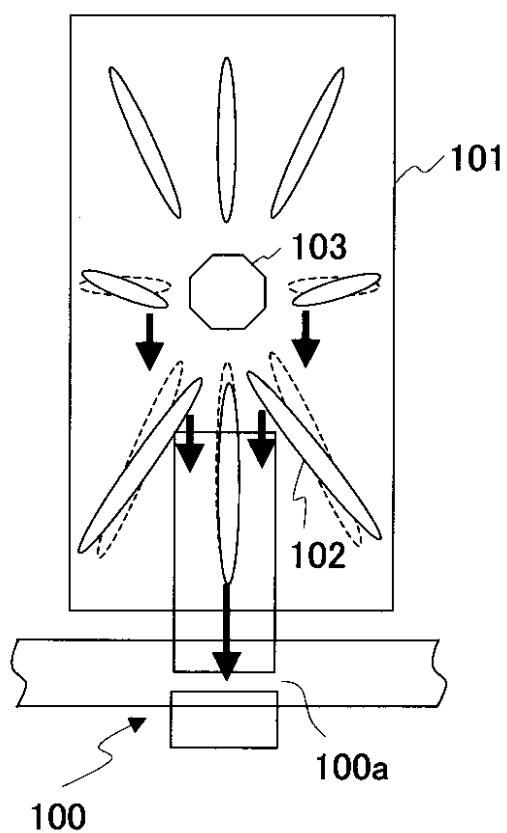

しかしながら、画素電極には薄膜トランジスタが接続されているため、薄膜トランジスタにおけるゲート電極からの電界漏洩が生じる。この電界漏洩により液晶分子が引き寄せられ画素全体としてみた場合、液晶が対称的に配向し難い。特に特許文献1のように垂直配向型液晶表示素子では突起を中心に液晶が配向することが必要となるが、図9に示すように、薄膜トランジスタ100に接続されている画素電極101上の液晶分子102はゲート電極100aによる電界の影響を受けて図の矢印に示す方向に引き寄せられ、液晶配向の中心が突起103ではなく、ゲート電極100a寄りとなる。これにより視野角性能が低下する。液晶表示パネルの表面などから外圧が加わり一時的にセルギャップが変化した際、配向中心が画素電極の中心からずれても薄膜トランジスタのゲート電位にトラップされ、配向中心が画素電極の中心に戻らず、所謂面押し性能が低下する。これらにより表示品質が悪くなる。

40

【0005】

本発明では、液晶分子がゲート電極による電界の影響を受けずに、表示品質を向上させた液晶表示素子を提供することを目的とする。

【課題を解決するための手段】

【0006】

50

上記目的を達成するために、請求項 1 に記載の発明は、第 1 の導電層として予め定めた方向に延伸するように配置されたゲート線と、前記第 1 の導電層として配置された第 1 の補助容量電極と、前記ゲート線にゲート電極が接続され、半導体層に形成されるチャネルのチャネル幅方向が前記ゲート線の延伸する前記方向と平行に配置された薄膜トランジスタと、前記第 1 の導電層よりも液晶層に近く、前記第 1 の導電層に対して絶縁層を介して第 2 の導電層として配置された第 1 の画素電極と、前記第 2 の導電層として、前記ゲート線の配置領域と前記第 1 の画素電極の配置領域との間の領域に少なくとも一部が配置された遮蔽電極と、前記第 1 の導電層と前記第 2 の導電層との間の層として、前記遮蔽電極に対して少なくとも一部が平面視して重なるように配置され、前記薄膜トランジスタのソース電極と前記第 1 の画素電極とを電気的に接続する接続部と、前記液晶層を介して前記第 1 の画素電極に対向し、前記遮蔽電極と等しい電位に設定される共通電極と、を備え、前記第 1 の補助容量電極は、少なくとも一部が前記第 1 の画素電極と平面視して重なり、且つ、前記第 1 の画素電極の周囲を囲むように配置され、前記遮蔽電極と等しい電位に設定され、前記第 1 の補助容量電極と前記接続部とは平面視して重なる領域を有し、前記遮蔽電極は、前記第 1 の画素電極に接触することなく、前記第 1 の補助容量電極と前記接続部との前記重なる領域を覆うように、前記ゲート線の延伸する前記方向に平行、且つ、前記薄膜トランジスタの前記チャネル幅方向に平行に配置されている、ことを特徴とする。

#### 【 0 0 0 7 】

請求項 2 に記載の発明は、請求項 1 に記載の液晶表示素子において、前記第 1 の画素電極との間に前記ゲート線が介在するように、前記第 2 の導電層として配置された第 2 の画素電極と、前記第 1 の導電層として配置され、前記遮蔽電極と等しい電位に設定される第 2 の補助容量電極と、を備え、前記第 2 の補助容量電極は、少なくとも一部が前記第 2 の画素電極と平面視して重なり、且つ、前記第 2 の画素電極の周囲を囲むように配置されていることを特徴とする。

請求項 3 に記載の発明は、請求項 2 に記載の液晶表示素子において、前記遮蔽電極は、前記第 1 の導電層と前記第 2 の導電層との間に配置された絶縁層に設けられたコンタクトホールを介して前記第 2 の補助容量電極に接続されていることを特徴とする。

請求項 4 に記載の発明は、請求項 3 に記載の液晶表示素子において、前記コンタクトホールは、前記ゲート線と前記第 2 の画素電極との間の領域に形成されていることを特徴とする。

請求項 5 に記載の発明は、請求項 4 に記載の液晶表示素子において、前記ゲート線は、前記第 1 の画素電極の配置方向とは異なる側に向かって前記ゲート配線から張り出した張出部を有し、前記薄膜トランジスタは、前記張出部が前記ゲート電極になっていることを特徴とする。

請求項 6 に記載の発明は、請求項 5 に記載の液晶表示素子において、前記薄膜トランジスタに対して前記コンタクトホールが前記ゲート線の延伸する前記方向に沿って隣接するように配置されていることを特徴とする。

#### 【 0 0 0 8 】

請求項 7 に記載の発明は、請求項 1 に記載の液晶表示素子において、前記ゲート線に対して交差するように配置され、前記薄膜トランジスタのドレイン電極に接続された信号線と、前記第 1 の画素電極との間に前記信号線が介在するように、前記第 2 の導電層として配置された第 2 の画素電極と、を備え、前記遮蔽電極は、前記信号線を跨ぐようにして、少なくとも前記第 2 の画素電極の配置領域と前記ゲート線の配置領域との間の領域まで延伸されていることを特徴とする。

請求項 8 に記載の発明は、請求項 1 に記載の液晶表示素子において、前記ゲート線に対して交差するように配置され、前記薄膜トランジスタのドレイン電極に接続された信号線と、前記第 1 の画素電極との間に前記信号線が介在するように、前記第 2 の導電層として配置された第 2 の画素電極と、を備え、前記遮蔽電極は、前記ゲート線の延伸する前記方向に沿って、少なくとも前記第 2 の画素電極の配置領域と前記ゲート線の配置領域との間の領域まで延伸されていることを特徴とする。

請求項 9 に記載の発明は、請求項 1 から 8 の何れかに記載の液晶表示素子において、前記液晶層における前記第 1 の画素電極に対応した領域が、前記遮蔽電極または前記第 1 の補助容量電極に与えられる電位で包囲されるように、前記遮蔽電極と前記第 1 の補助容量電極とが配置されていることを特徴とする。

請求項 10 に記載の発明は、請求項 1 から 9 の何れかに記載の液晶表示素子において、前記液晶層は、誘電率異方性が負の液晶分子からなることを特徴とする。

請求項 11 に記載の発明は、請求項 1 から 10 の何れかに記載の液晶表示素子において、前記第 1 の画素電極は、複数のスリットが形成されていることを特徴とする。

#### 【0009】

請求項 12 に記載の発明は、請求項 1 から 11 の何れかに記載の液晶表示素子において、前記接続部は、前記第 1 の補助容量電極と前記遮蔽電極とが平面視して重なる領域に、前記薄膜トランジスタにおけるチャネル幅方向に沿う方向の長さが前記チャネル幅よりも長く形成された領域を有していることを特徴とする。

#### 【発明の効果】

#### 【0012】

本発明によれば、表示品質を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

#### 【第 1 の実施形態】

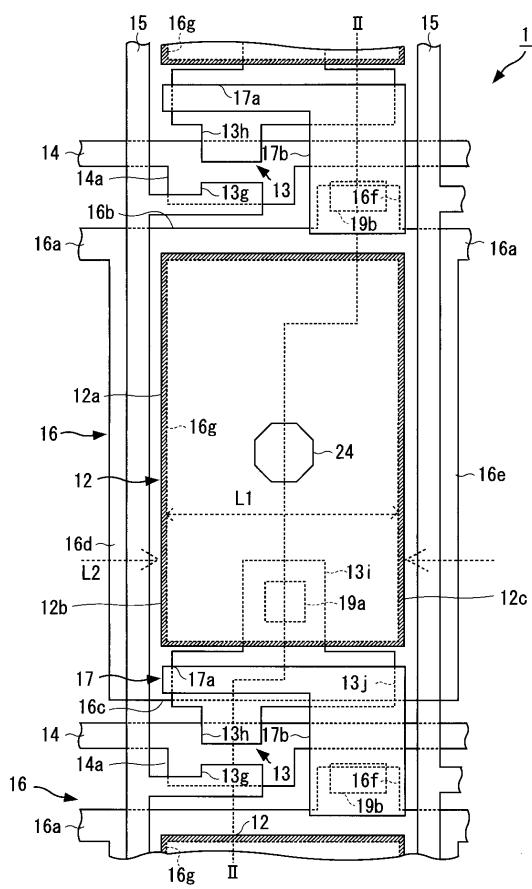

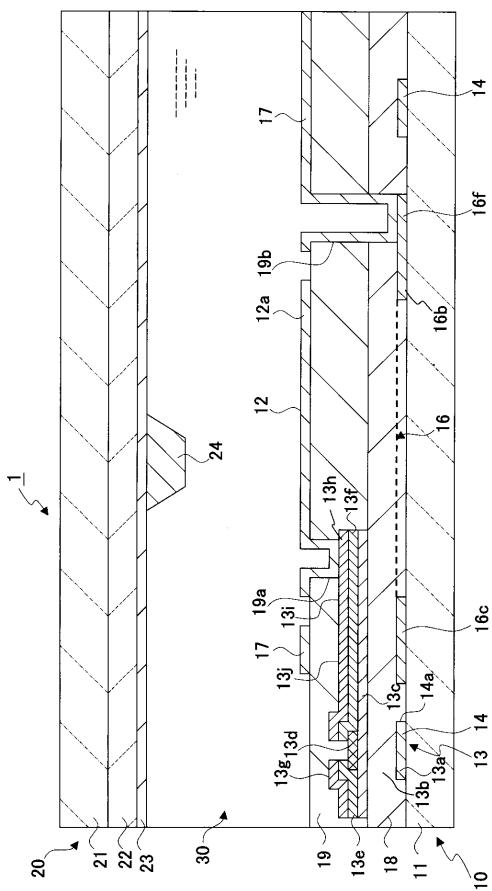

図 1 は本発明の第 1 の実施形態に係る液晶表示素子 1 の平面図、図 2 は図 1 における I-I 線に沿う断面図である。第 1 の実施形態に係る液晶表示素子 1 はアクティブマトリックス液晶表示素子であり、TFT 基板 10 と対向基板 20 とが予め所定の間隔を開けて対向して設けられ、TFT 基板 10 と対向基板 20 との間に液晶が封入され液晶層 30 が形成されている。

#### 【0014】

TFT 基板 10 は、透明基板 11 と、透明基板面内にマトリックス状に配置するよう設けられた複数の画素電極 12 と、複数の画素電極 12 のそれぞれに対応するよう設けられ、それぞれ対応する画素電極 12 に接続する複数の薄膜トランジスタ (TFT : Thin Film Transistor) 13 と、これら複数の薄膜トランジスタ 13 のそれぞれにゲート信号およびデータ信号を供給するよう行方向、列方向にそれぞれ設けられる複数のゲート線 14 および複数の信号線 15 と、複数の画素電極 12 のそれぞれに対して設けられる複数の補助容量電極 16 と、複数の画素電極 12 のそれぞれに対応して設けられその画素電極 12 に接続する薄膜トランジスタ 13 のゲート電極 13a と当該画素電極 12 との間に設けられる複数の遮蔽電極 17 と、TFT 基板 10 の表面に設けられる配向膜 (図示せず) と、を含んでいる。

一方、対向基板 20 は、透明電極 21 と、透明電極 21 面に設けられるカラーフィルター 22 と、このカラーフィルター 22 上に設けられる共通電極 (対向電極) 23 と、共通電極 23 上に少なくとも画素電極 12 毎に対応して設けられる複数の突起 24 と、対向基板 20 の表面即ち共通電極 23 および複数の突起 24 上に設けられる配向膜 (図示せず) と、を含んでいる。

#### 【0015】

TFT 基板 10 の構成について詳細に説明する。

ガラス基板などの透明基板 11 上に複数本のゲート線 14 が列方向に間隔を空けて並んで配置され、それぞれのゲート線 14 が行方向に配設されている。各ゲート線 14 には画素領域毎に線幅が太くなるよう張出部 14a が設けられ、ゲート電極 13a を構成している。図 1 に示す形態では、張出部 14a は列方向に隣り合う補助容量電極 16 側に張り出している。

#### 【0016】

透明基板 11 面には隣り合うゲート線 14, 14 同士の間で、枠状をなす補助容量電極 16 が設けられ、行方向に並ぶ補助容量電極 16, 16 同士が補助容量線 16a で接続さ

10

20

30

40

50

れ、液晶表示領域外まで延びるよう設けられている。詳細には、補助容量電極 16 は上辺部 16 b、下辺部 16 c、左辺部 16 d および右辺部 16 e で枠状に形成されており、行方向の画素領域毎の補助容量電極 16 のうち上辺部 16 b 同士を補助容量線 16 a が接続して液晶表示領域外まで延びている。補助容量線 16 a は液晶表示領域外に接続部（図示せず）が設けられ、共通電極 23 と同じ電圧が印加される。図 1 に示すように、補助容量電極 16 のうち上辺部 16 b は列方向に隣り合うゲート線側に張り出す張出部 16 f を有する。ここで、ゲート線 14 における張出部 14 a と補助容量電極 16 における張出部 16 f とは、行方向の左右何れかで互いに干渉しないよう、図 1 に示すように、張出部 14 a は左寄りに設けられ、張出部 16 f は右寄りに設けられる。図 1 に示す場合では補助容量 16 および補助容量線 16 a とゲート線 14 とは透明基板 11 面に設けられるため、同一の金属、例えば Cr などで形成することができる。

10

#### 【0017】

透明基板 11、ゲート線 14 並びに補助容量線 16 a および補助容量電極 16 を覆って第 1 の絶縁層 18 が形成されている。

第 1 の絶縁層 18 上には複数の信号線 15 が行方向に間隔を空けて並んで設けられ、それぞれの信号線 15 が列方向に配設されている。

#### 【0018】

隣り合うゲート線 14, 14 および信号線 15, 15 で囲まれる各領域は一つの画素領域を構成し、画素領域毎に薄膜トランジスタ 13 が設けられる。即ち、各画素領域の所定位置、図 1 に示す例では下側のゲート線 14 の一部がゲート電極 13 a となり、第 1 の絶縁層 18 のうちこのゲート電極 13 a を覆う部分がゲート絶縁膜 13 b となり、このゲート絶縁膜 13 b を覆うように半導体層 13 c が設けられ、ゲート電極 13 a の領域で半導体層 13 c 面にエッティングストッパー層 13 d が設けられ、このエッティングストッパー層 13 d 面を一部分覆うよう列方向に対向して延びる一対のオーミックコンタクト層 13 e, 13 f と、この一対のオーミックコンタクト層 13 e, 13 f を部分的にそれぞれ覆うようにドレイン電極 13 g およびソース電極 13 h が設けられる。

20

#### 【0019】

ここで、半導体層 13 c、一対のオーミックコンタクト層 13 e, 13 f、ソース電極 13 h は、後述するように画素電極 12 にコンタクトホール 19 a を介して接続するため、図 2 に示すように、台座部 13 i として画素電極 12 の下部まで部分的に延び、一方のオーミックコンタクト層 13 f を部分的に覆う部位と台座部 13 i とを接続部 13 j で接続している。この接続部 13 j は、画素領域内で左右の信号線 15, 15 近傍まで左右に延びている。

30

#### 【0020】

薄膜トランジスタ 13 の半導体層 13 c、エッティングストッパー層 13 d、一対のオーミックコンタクト層 13 e, 13 f、ドレイン電極 13 g およびソース電極 13 h の積層構造は第 1 の絶縁層 18 面上に形成され、前述の信号線 15 も第 1 の絶縁層 18 面上に形成されるため、信号線 15 も半導体層 13 c、一対のオーミックコンタクト層 13 e, 13 f、ドレイン電極 13 g およびソース電極 13 h の各層の積層構造を有し、薄膜トランジスタ 13 のプロセスと同時に形成される。

40

#### 【0021】

信号線 15、第 1 の絶縁層 18 および各画素領域の薄膜トランジスタ 13 上に第 2 の絶縁層 19 が形成されている。

第 2 の絶縁層 19 にはそれぞれの画素領域内でソース電極 13 h 上にコンタクトホール 19 a が形成されている。第 2 の絶縁層 19 の上面にはそれぞれの画素領域毎に画素電極 12 が設けられている。複数の画素電極 12 は、それぞれの画素領域内でコンタクトホール 19 a を介してソース電極 13 h と接続されている。画素電極 12 の外周縁 12 a が補助容量電極 16 の内周縁 16 g より外側にあり、画素領域内で画素電極 12 と補助容量電極 16 とは重なっている。図 1 においてハッチング部分は、画素電極 12 の外周縁 12 a と補助容量電極 16 の内周縁 16 gとの間、つまり重なり合う部分を模式的に示すもので

50

ある。この重なり合いにより補助容量  $C_s$  が形成される。

#### 【0022】

第1の実施形態では、さらに、同一の画素領域で、画素電極12に薄膜トランジスタ13のソース電極13hおよび半導体層13cを介して接続されるゲート電極13aの一部を構成するゲート線14と画素電極12との間を電気的に遮蔽する電極17が、画素電極12が設けられた上記第2の絶縁層19の上面に設けられている。この電極、即ち遮蔽電極17は、そのゲート線14に平行に沿って形成される直線部17aと、この直線部17aから隣り合う画素領域に張り出す張出部17bと、で略L字状をなしている。直線部17aの行方向の長さは、画素領域毎のソース電極13hの行方向幅より長い。別の表現をすれば、遮蔽電極17の直線部17aは、各画素電極12におけるゲート電極13aの長手方向、即ちゲート配線方向に平行な辺の長さ  $L_2$  を有してもよい。この長さ  $L_2$  は、各画素電極12の横方向(図の左右方向)の辺の長さでもある。また、各遮蔽電極17は、各画素電極12の左辺部12bと該左辺部12bに相対向する右辺部12cとそれぞれ重合する各補助容量電極16の左辺部16dおよび右辺部16e間に差し渡す長さを有するものもある。即ち、各遮蔽電極17は図1に示す距離  $L_1$  よりも長い。遮蔽電極17における張出部17bは、同一の画素領域内のゲート線14を乗り越えて張り出し、列方向に隣り合う画素領域における補助容量電極16の張出部16fの上に達している。第1の絶縁層18および第2の絶縁層19のうち補助容量電極16の張出部16fの領域にはコンタクトホール19bが形成されており、遮蔽電極17の張出部17bがコンタクトホール19bを介して列方向で隣り合う画素領域内の補助容量電極16における張出部16fと接続されている。このように、遮蔽電極17はゲート線14の上方を乗り越えて列方向に延設され、列方向に隣接する画素領域にコンタクトホール19bを介して列方向に隣接する画素領域内の補助容量電極16に接続されている。10

#### 【0023】

画素電極12と遮蔽電極17とは何れも第2の絶縁層19上に形成されているため、ITOなどの透明電極金属で、同時に形成することがプロセス上好ましいが、別に画素電極12と遮蔽電極17とは同一の層である必要はなく、断面構造において、遮蔽電極17より上層に画素電極12が設けられ、遮蔽電極17より下方に薄膜トランジスタ13の積層構造体が設けられてもよい。

#### 【0024】

複数の画素電極12、複数の遮蔽電極17および第2の絶縁層19上には垂直配向膜(図示せず)が設けられている。30

#### 【0025】

対向基板20、特にCF基板の構造について説明する。

透明基板21面にはRGBの各カラーフィルター22が設けられ、カラーフィルター22上に共通電極23が形成されている。共通電極23には、画素領域毎に、共通電極23に向かい合う画素電極12の中央部、即ち対角線の交点近傍に、樹脂でなる突起24が形成されている。複数の突起24および共通電極23には垂直配向膜(図示せず)が形成されている。

#### 【0026】

この液晶表示素子1においては、図示を省略するが、TFT基板10の下側に偏向板が設けられ、対向基板20の上側に偏光板が設けられ、両偏光板の透過軸は互いに直交している。TFT基板10の液晶表示領域外まで延設された補助容量線16aの接続部と対向基板20における共通電極23とは接続されており、補助容量線16aと共に共通電極23とにCOM(共通)電位が印加される。この場合、補助容量線16aと共に共通電極23とは接続されておらず、補助容量線16aと共に共通電極23、それぞれ、異なる導体路を介して電源供給回路に接続されていてもよい。40

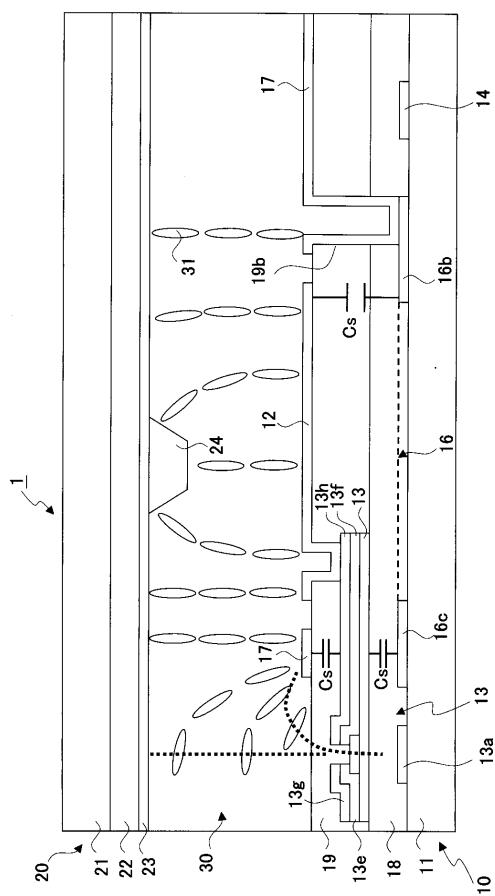

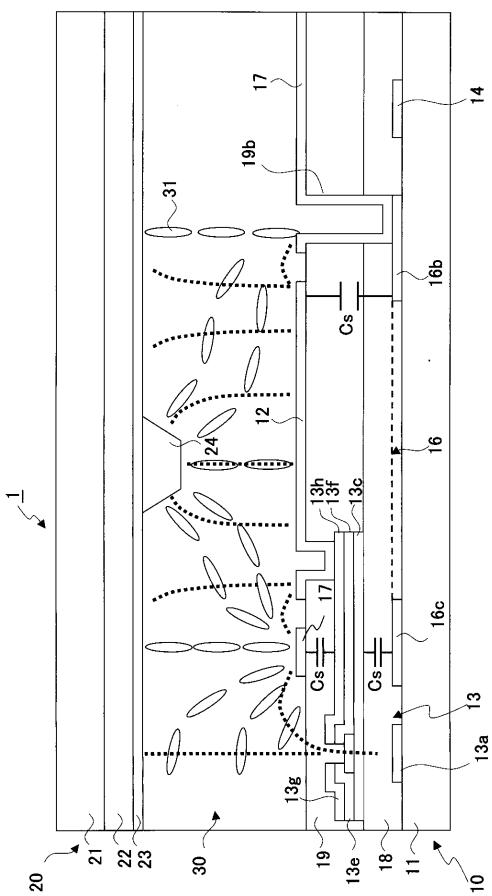

#### 【0027】

液晶表示素子1における遮蔽電極17の役割について説明する。

図3は、図2に示す断面構造において共通電極23と画素電極12との間に電位差が生50

じていない場合の液晶分子31の挙動を模式的に示す図であり、図4は、図2に示す断面構造において共通電極23と画素電極12との間に電位差が生じている場合の液晶分子31の挙動を模式的に示す図である。図5は共通電極23と画素電極12との間に電位差が生じている場合の液晶分子31の挙動を模式的に示す平面図である。

#### 【0028】

液晶表示素子1において、共通電極23と画素電極12との間に電位差が生じていない場合、即ち黒表示の場合、図3に示すように、一つの画素領域内では、画素電極12の上縁部と左右の各縁部の外側には、第1の絶縁層18および第2の絶縁層19を介して補助容量電極16が部分的に張り出しており、この補助容量電極16が共通電極23と外部で接続されていることから、この遮蔽電極17は共通電極23と同じ電位である。しかも、画素電極12の上側（図3では右側）の遮蔽電極17は、コンタクトホール19bを介して補助容量電極16と接続しており、かつ、補助容量電極16が共通電極23と外部で接続されていることから、この遮蔽電極17は共通電極23の電位と同じである。10

一方、画素電極12の下側（図3では左側）には遮蔽電極17が設けられ、この遮蔽電極は隣り合う画素領域まで張り出しコンタクトホール19bを介して補助容量電極16と接続しているため、この遮蔽電極17は共通電極23と同じ電位であって、しかも、画素電極12の下縁部は第2の絶縁層19を介して接続しているソース電極13hと同様、共通電極23と同電位である。

#### 【0029】

よって、画素電極12の全周縁部と共通電極23との間にある液晶分子31は、配向膜に対して垂直に立つように配向している。共通電極23側の突起24周辺では、液晶分子31が突起24上の配向膜の面に直交するように配向する。従って、一つの画素領域内の液晶分子31が突起24を中心軸として対称となり、配向中心位置が安定する。20

#### 【0030】

なお、第2の絶縁層19で薄膜トランジスタ13のゲート電極13aの領域にある液晶分子31は、ゲート電極13aに電圧が印加されると、ゲート電極13aと遮蔽電極17との間に電位差が生じて点線で図示するように電界（電気力線）が生じる。よって、ゲート電極13aの領域にある液晶分子31は電気力線に直交するように倒れ液晶分子31が乱れる。しかし、この領域にある液晶分子31は、薄膜トランジスタの素子特性を保つために、図示しない遮光膜が対向基板側に設けられるため、液晶分子31による配向の影響は表示品質に影響しない。30

#### 【0031】

他方、液晶表示素子1において、共通電極23と画素電極12との間に電位差が生じている場合、即ち白表示の場合、図4に示すように、一つの画素領域内において、画素電極12は、共通電極23に対し電位差を有すると、画素電極12の上側（図4では右側）の遮蔽電極17、画素電極12の下側（図4では左側）の遮蔽電極17および共通電極23との間にそれぞれ電位差があることになり、図4に点線で示すように電界（電気力線）が生じる。よって、この生じる電界に交わる方向に液晶分子31が配向する。しかしながら、画素電極12の上側（図4では右側）の遮蔽電極17と共通電極23とは同じ電位であり、画素電極12の下側（図4では左側）の遮蔽電極17と共通電極23とは同じ電位であり、かつ、画素電極12の左右の各縁部の外側には、第1の絶縁層18および第2の絶縁層19を介して補助容量電極16が部分的に張り出しており、この補助容量電極16が共通電極23と外部で接続されていることから、この遮蔽電極17は共通電極23と同じ電位である。画素電極12の領域で生じる電気力線が外部、例えば比較的大きな電圧が印加されるゲート電極13aからの影響を受けず、画素電極12の周りでは共通電極23との間では電界が生じないため、画素電極12の領域にある液晶分子31は、外部からの電界の影響を受けず、画素電極12と共通電極23との間の液晶分子31が突起24の中心軸側に倒れ込み、分割配向する。40

#### 【0032】

以上説明したように、画素電極12と共通電極23との間に電位差が生じても、共50

通電極 2 3 と画素電極 1 2 との間で画素電極の周囲は無電界状態が切れ目なく生じている。よって、画素電極 1 2 と共に通電極 2 3 との間の電位差の有無を問わず、配向中心位置が安定し、図 5 に示すように、突起 2 4 に向けて液晶分子 3 1 が倒れ、突起 2 4 回りの液晶分子 3 1 の対称性が崩れない。従って、綺麗な表示をすることができる。

#### 【 0 0 3 3 】

第 1 の実施形態に係る液晶表示素子 1 では、図 3 および図 4 に示すように、画素領域毎に、画素電極 1 2 の上縁部、左右縁部と補助容量電極 1 6 との間でそれぞれ補助容量 C s が形成され、かつ、画素電極 1 2 の下縁部とソース電極 1 3 h との間でも補助容量 C s が形成されるだけでなく、遮蔽電極 1 7 とソース電極 1 3 h との間でも補助容量 C s が形成される。つまり、断面構造で見た場合ソース電極 1 3 h の上下で遮蔽電極 1 7 、補助容量電極 1 6 とのそれぞの間に補助容量 C s が形成される。よって、遮蔽電極 1 7 を設けることで補助容量 C s の増加分だけ、補助容量電極 1 6 の面積を小さくすることができる。

10

#### 【 0 0 3 4 】

図示する例では、画素領域毎の遮蔽電極 1 7 は、対応する画素領域に対し列方向に隣接する後段の画素領域における補助容量電極 1 6 とコンタクトホール 1 9 b を介して接続している。画素領域毎の遮蔽電極 1 7 はその画素領域内の補助容量電極とコンタクトホールを介して接続してもよいことは図に示して説明するまでもない。

#### 【 0 0 3 5 】

#### 〔 第 2 の実施形態 〕

図 6 は本発明の第 2 の実施形態に係る液晶表示素子 2 の平面図である。第 2 の実施形態に係る液晶表示素子 2 は、第 1 の実施形態とは以下の点で異なる。なお、その他は第 1 の実施形態と同様なので、同一または対応するものには同一の符号を付してある。

20

第 2 の絶縁層 1 9 上に画素領域毎に遮蔽電極 4 7 b が設けられ、その遮蔽電極 4 7 b がその画素領域に設けられている画素電極 1 2 の下縁部と薄膜トランジスタ 1 3 のゲート電極 1 3 a を構成するゲート線 1 4 との間に設けられる。画素領域毎の遮蔽電極 4 7 b は、隣り合う行方向に並んで隣接する他の画素領域内の遮蔽電極 4 7 b と接続され、全体として遮蔽配線 4 7 として液晶表示領域の外部まで延びて設けられている。遮蔽配線 4 7 のうち液晶表示領域外部に延びている接続部は、対向基板 2 0 の共通電極 2 3 と接続される。よって、画素領域毎の遮蔽電極 4 7 b は共通電極 2 3 と同電位となる。

#### 【 0 0 3 6 】

この第 2 の実施形態では、図 1 に示す第 1 の実施形態のように画素領域毎で遮蔽電極 1 7 と補助容量電極 1 6 とをコンタクトホール 1 9 b を介して接続する必要はないため、画素領域内にそのコンタクトホールを形成できない場合に有効である。当然ではあるが、第 1 の実施形態のように、遮蔽電極とコンタクトホールを介して接続するために補助容量電極 1 6 にそれ用の張出部を設ける必要はない。

30

#### 【 0 0 3 7 】

第 2 の実施形態においても、第 1 の実施形態と同様、共通電極 2 3 と画素電極 1 2 との間に電位差が生じても生じなくても、共通電極 2 3 と各画素電極 1 2 との間に有る液晶分子 3 1 は、外部の電界の影響を受けず、突起を中心軸として配向中心の位置がずれることはない。

40

#### 【 0 0 3 8 】

#### 〔 第 3 の実施形態 〕

前述の第 2 の実施形態では、画素領域毎の遮蔽電極を行方向に接続して表示領域外まで延出して遮蔽電極配線としているが、画素領域毎の遮蔽電極を列方向に接続して表示領域外まで延出して遮蔽電極配線としてもよい。図 7 は本発明の第 3 の実施形態に係る液晶表示素子 3 の平面図である。なお、その他は第 1 の実施形態と同様なので、同一または対応するものには同一の符号を付してある。

#### 【 0 0 3 9 】

第 2 の絶縁層 1 9 上に画素領域毎に遮蔽電極 5 7 b が設けられ、その遮蔽電極 5 7 b がその画素領域に設けられている画素電極 1 2 の下縁部と薄膜トランジスタ 1 3 のゲート電

50

極 13 a を構成するゲート線 14との間に設けられる。画素領域毎の遮蔽電極 57 b は、隣り合う列方向に並んで隣接する他の画素領域内の遮蔽電極 57 b と接続され、全体として遮蔽配線 57 として液晶表示領域の外部まで延びて設けられている。遮蔽配線 57 のうち液晶表示領域外部に延びている接続部は、対向基板 20 の共通電極 23 と接続される。よって、画素領域毎の遮蔽電極 57 b は共通電極 23 と同電位となる。

この第3の実施形態では、図1に示す第1の実施形態のように画素領域毎で遮蔽電極 17 と補助容量電極 16 とをコンタクトホール 19 b を介して接続する必要はないため、画素領域内にそのコンタクトホールを形成できない場合に有効である。当然ではあるが、第1の実施形態のように、遮蔽電極とコンタクトホールを介して接続するために補助容量電極 16にそれ用の張出部を設ける必要はない。

10

#### 【0040】

第3実施形態においても、第1の実施形態および第2の実施形態と同様、共通電極 23 と画素電極 12との間に電位差が生じても生じなくても、共通電極 23 と各画素電極 12 との間にある液晶分子 31 は、外部の電界、特にゲート電極 13 a からの強い電界の影響を受けず、液晶分子 31 の配向が突起 24を中心として対称となり、配向の中心がずれることがない。

#### 【0041】

なお、第2の実施形態、第3の実施形態の何れの場合であっても、列方向または行方向に並ぶ遮蔽電極 47 b , 57 b のそれぞれを遮蔽配線 47 , 57 の一部で接続するだけではなく、部分的に、第1の実施形態で示すように、第1の絶縁層 18 および第2の絶縁層 19 を貫通するコンタクトホールを設け、透明基板 11 面に配設されている補助容量電極 16 または補助容量線と接続してもよい。この構造を採用すると加工歩留まりが良くなる。

20

#### 【0042】

本発明の実施形態は上述したものに限定されることなく、特許請求の範囲に記載した発明の範囲で次に説明するように種々変更することができる。

#### 【0043】

例えば、前述した何れの実施形態では、一つの画素電極 12 に対し突起 24 が一つ対応するように設けられているが、画素領域が図に示すように列方向に長い場合には、例えば図8に示すように、画素電極 62 を例えば3つに別れるように行方向にスリット 62 a を設け、画素電極 62 を3つの領域に分け、この細分化した領域毎に対向基板 20 側に突起 24 を設けるようにしてもよい。

30

#### 【0044】

例えば、第1乃至第3の実施形態では、TFT基板 10 、対向基板 20 の何れの基板にも形成されている配向膜は垂直配向膜であり、液晶が負の誘電異方性を有するものであるが、本発明の実施形態はこれに限られることなく、TFT基板 10 、対向基板 20 の何れの基板にも水平配向膜を形成して、液晶が正の誘電異方性を有するものであってもよい。この場合には、図示はしないが、共通電極 23 は対向基板に形成されず、TFT基板 10 側に画素電極と並んで形成されるものであり、要は、画素電極と共通電極間に液晶が介在して駆動表示する液晶表示素子に適用可能である。

#### 【0045】

40

また、例えば、第1乃至第3の実施形態では、薄膜トランジスタ 13 におけるドレイン電極 13 g を信号線 15 に接続し、薄膜トランジスタ 13 のソース電極 13 j を画素電極 12 にコンタクトホール 19 a を介して接続しているが、逆に、薄膜トランジスタ 13 のソース電極を信号線 15 に接続し、薄膜トランジスタ 13 のドレイン電極を画素電極 17 にコンタクトホール 19 a を介して接続してもよい。

#### 【図面の簡単な説明】

#### 【0046】

【図1】本発明の第1の実施形態に係る液晶表示素子の平面図である。

【図2】図1のI—I - II-II 線に沿う断面図である。

【図3】図1に示す液晶表示素子において画素電極と共通電極との間に電位差がない場合

50

における液晶分子の挙動を模式的に示す図である。

【図4】図1に示す液晶表示素子において画素電極と共通電極との間に電位差がある場合における液晶分子の挙動を模式的に示す図である。

【図5】図1に示す液晶表示素子において画素電極と共通電極との間に電位差が生じている場合の液晶分子の挙動を模式的に示す平面図である。

【図6】本発明の第2の実施形態に係る液晶表示素子の平面図である。

【図7】本発明の第3の実施形態に係る液晶表示素子の平面図である。

【図8】画素電極の変形例を示す平面図である。

【図9】本発明が解決しようとする課題を説明するための模式図である。

【符号の説明】

10

【0047】

1, 2, 3 : 液晶表示素子

10 : TFT基板

11 : 透明基板

12 : 画素電極

12a : 外周縁

13 : 薄膜トランジスタ

13a : ゲート電極

13b : ゲート絶縁膜

13c : 半導体層

20

13d : エッチングストッパー層

13e, 13f : オーミックコンタクト層

13g : ドレイン電極

13h : ソース電極

13i : 台座部

13j : 接続部

14 : ゲート線

14a : ゲート線の張出部

15 : 信号線

30

16 : 補助容量電極

16a : 補助容量線

16b : 上辺部

16c : 下辺部

16d : 左辺部

16e : 右辺部

16f : 張出部

16g : 補助容量電極16の内周縁

17 : 遮蔽電極

17a : 遮蔽電極の直線部

17b : 遮蔽電極の張出部

40

18 : 第1の絶縁層

19 : 第2の絶縁層

19a : コンタクトホール

19b : コンタクトホール

20 : 対向基板

21 : 透明電極

22 : カラーフィルター

23 : 共通電極

24 : 突起

30 : 液晶層

50

3 1 : 液晶分子

4 7 , 5 7 : 遮蔽電極配線

4 7 b , 5 7 b : 遮蔽電極

6 2 : 画素電極

6 2 a : スリット

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開平05-297412(JP,A)

特開2000-029059(JP,A)

特開2003-005214(JP,A)

特開2005-241923(JP,A)

特開2003-322865(JP,A)

特開平04-358129(JP,A)

特開平11-344728(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368