(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5105843号

(P5105843)

(45) 発行日 平成24年12月26日(2012.12.26)

(24) 登録日 平成24年10月12日(2012.10.12)

(51) Int.Cl.

F 1

|                    |                  |                |

|--------------------|------------------|----------------|

| <b>HO4N 5/351</b>  | <b>(2011.01)</b> | HO4N 5/335 51O |

| <b>HO4N 5/353</b>  | <b>(2011.01)</b> | HO4N 5/335 53O |

| <b>HO4N 5/235</b>  | <b>(2006.01)</b> | HO4N 5/235     |

| <b>HO4N 101/00</b> | <b>(2006.01)</b> | HO4N 101:00    |

請求項の数 12 (全 19 頁)

(21) 出願番号

特願2006-328839 (P2006-328839)

(22) 出願日

平成18年12月5日 (2006.12.5)

(65) 公開番号

特開2008-147713 (P2008-147713A)

(43) 公開日

平成20年6月26日 (2008.6.26)

審査請求日

平成21年12月4日 (2009.12.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 鈴木 将一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及び判定方法

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像素子を用いて画像を撮像する撮像装置において、外光のフリッカの周波数を判定する判定方法であって、

読み出し手段が、前記フリッカの周波数として予測される複数の周波数にそれぞれ対応する複数の時間差で、電荷蓄積時間の等しい電気信号をそれぞれ2フレーム続けて前記撮像素子から読み出すフリッカ検出用フレーム読み出し工程と、

前記読み出し手段が、表示装置に表示するための電気信号を前記撮像素子から読み出す表示用フレーム読み出し工程と、

判定手段が、前記フリッカ検出用フレーム読み出し工程で続けて読み出した前記2フレームの電気信号に基づいてフリッカの周波数を判定する判定工程とを有し、

前記フリッカ検出用フレーム読み出し工程と前記表示用フレーム読み出し工程を異なるタイミングで交互に実行することを特徴とする判定方法。

## 【請求項 2】

撮像素子を用いて画像を撮像する撮像装置において、外光のフリッカの周波数を判定する判定方法であって、

読み出し手段が、前記フリッカの周波数として予測される2種類の周波数にそれぞれ対応する2つの時間差で、電荷蓄積時間の等しい電気信号をそれぞれ2フレーム続けて前記撮像素子から読み出すフリッカ検出用フレーム読み出し工程と、

前記読み出し手段が、表示装置に表示するための電気信号を前記撮像素子から読み出す

10

20

表示用フレーム読み出し工程と、

判定手段が、前記フリッカ検出用フレーム読み出し工程で続けて読み出した前記 2 フレームの電気信号に基づいてフリッカの周波数を判定する判定工程とを有し、

前記フリッカ検出用フレーム読み出し工程と前記表示用フレーム読み出し工程を異なるタイミングで交互に実行することを特徴とする判定方法。

**【請求項 3】**

前記判定工程において、前記フリッカ検出用フレーム読み出し工程で続けて読み出した前記 2 フレームの電気信号の信号値の差が、前記複数の時間差の内の 1 つの時間差では予め設定された範囲内にあって、且つ、他の時間差では予め設定された範囲外にある場合に、前記信号値の差が前記予め設定された範囲内となる電気信号を読み出した時間差に対応する周波数を前記フリッカの周波数として判定することを特徴とする請求項 1 に記載の判定方法。

10

**【請求項 4】**

前記判定工程において、前記フリッカ検出用フレーム読み出し工程で続けて読み出した前記 2 フレームの電気信号の信号値の差が、前記 2 つの時間差の内の一方の時間差で予め設定された範囲外にある場合に、他方の時間差に対応する周波数を前記フリッカの周波数として判定することを特徴とする請求項 2 に記載の判定方法。

**【請求項 5】**

前記判定工程では、異なる 2 つの時間差において、前記信号値の差が共に予め設定された範囲内である場合に、フリッカが発生していないと判定することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の判定方法。

20

**【請求項 6】**

前記時間差は、1 / 100 秒及び 1 / 120 秒を含むことを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の判定方法。

**【請求項 7】**

入射する光学像を電気信号に変換することにより画像を撮像する撮像素子と、

外光のフリッカの周波数として予測される複数の周波数にそれぞれ対応する複数の時間差で、電荷蓄積時間の等しい電気信号をそれぞれ 2 フレーム続けてフリッカ検出用に前記撮像素子から読み出すとともに、表示装置に表示するための電気信号を表示用に前記撮像素子から読み出すように制御する読み出し制御手段と、

30

前記読み出し制御手段による制御により前記フリッカ検出用に前記撮像素子から続けて読み出した前記 2 フレームの電気信号に基づいてフリッカの周波数を判定する判定手段とを有し、

前記フリッカ検出用の読み出しと前記表示用の読み出しとを異なるタイミングで交互に実行することを特徴とする撮像装置。

**【請求項 8】**

入射する光学像を電気信号に変換することにより画像を撮像する撮像素子と、

外光のフリッカの周波数として予測される 2 種類の周波数にそれぞれ対応する 2 つの時間差で、電荷蓄積時間の等しい電気信号をそれぞれ 2 フレーム続けてフリッカ検出用に前記撮像素子から読み出すとともに、表示装置に表示するための電気信号を表示用に前記撮像素子から読み出すように制御する読み出し制御手段と、

40

前記読み出し制御手段による制御により前記フリッカ検出用に前記撮像素子から続けて読み出した前記 2 フレームの電気信号に基づいてフリッカの周波数を判定する判定手段とを有し、

前記フリッカ検出用の読み出しと前記表示用の読み出しとを異なるタイミングで交互に実行することを特徴とする撮像装置。

**【請求項 9】**

前記判定手段は、前記フリッカ検出用に続けて読み出した前記 2 フレームの電気信号の信号値の差が、前記複数の時間差の内の 1 つの時間差では予め設定された範囲内にあって、且つ、他の時間差では予め設定された範囲外にある場合に、前記信号値の差が前記予め

50

設定された範囲内となる電気信号を読み出した時間差に対応する周波数を前記フリッカの周波数として判定することを特徴とする請求項 7 に記載の撮像装置。

**【請求項 10】**

前記判定手段は、前記フリッカ検出用に続けて読み出した前記 2 フレームの電気信号の信号値の差が、前記 2 つの時間差の内の一方の時間差で予め設定された範囲外にある場合に、他方の時間差に対応する周波数を前記フリッカの周波数として判定することを特徴とする請求項 8 に記載の撮像装置。

**【請求項 11】**

前記判定手段は、異なる 2 つの時間差において、前記信号値の差が共に予め設定された範囲内である場合に、フリッカが発生していないと判定することを特徴とする請求項 7 乃至 10 10 のいずれか 1 項に記載の撮像装置。

**【請求項 12】**

前記時間差は、1 / 100 秒及び 1 / 120 秒を含むことを特徴とする請求項 7 乃至 1 1 のいずれか 1 項に記載の撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像素子を用いた撮像装置及び該撮像装置におけるフリッカ周波数の判定方法に関する。 20

**【背景技術】**

**【0002】**

近年では、複雑なタイミング発生回路を必要とせず、安価で且つ单一電源で動作し、消費電力も少ない等の理由により、デジタルカメラなどの撮像装置において C M O S センサを用いるケースが増えてきている。

**【0003】**

C M O S センサは、任意の領域のみの画像信号を読み出すことができるという、C C D 撮像素子には無い特徴を有する。このような利点の一方で、C M O S センサを所謂ローリングシャッタ駆動した場合、ライン毎に電荷の蓄積タイミングがずれるために、C C D 撮像素子には無いフレーム内フリッカ（以下、単に「フリッカ」と呼ぶ。）が発生するという欠点がある。 30

**【0004】**

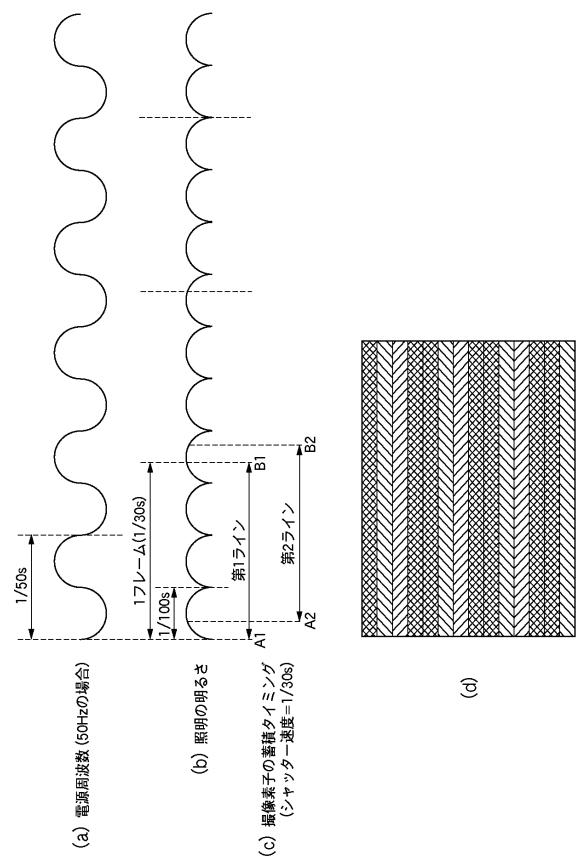

ここで、ローリングシャッタ駆動する場合に起こる、C M O S センサ特有のフリッカについて説明する。図 14 は電源周波数が 50 H z の場合の、フリッカの発生原理を説明するための図である。周波数が 50 H z の交流電源で蛍光灯等を点灯した場合（図 14 ( a )）、電源の周波数の 2 倍の周波数（100 H z ）で光量が変動する（図 14 ( b )）。 40

**【0005】**

このように明るさが周期的に変動する蛍光灯の下で、M O S 型撮像素子により電荷蓄積時間を 1 / 30 秒として撮像する場合の電荷蓄積タイミングを図 14 ( c ) に示す。この場合、図 14 ( c ) に示すように、読み出し点 A 1 から B 1 までの入射光量を積分した値が第 1 ラインの画素の出力信号になる。同様に、読み出し点 A 2 から B 2 までの入射光量を積分した値が第 2 ラインの画素の出力信号となる。以下、最終ラインまで同様である。このとき、ライン毎に照明の光量変化の周期に対する電荷蓄積時間の位相が異なるため、入射光量の積分値が異なってしまい、フレーム内で輝度変動（フリッカ）が現れる。このフリッカは、例えば、撮像素子が 480 ラインで構成される場合、1 ラインの読み出しに係る時間が 1 / 14400 秒（= 1 / 30 秒 ÷ 480 ライン）であるため、照明の光量変化に対して 144 ライン周期で蓄積開始タイミングの位相が揃う。そのため、この場合には 144 ライン周期の輝度レベルの変動となる（図 14 ( d )）。このように、C M O S センサをローリングシャッタ駆動した場合に、フレーム内で輝度差が生じてしまう。

**【0006】**

上述したフレーム内フリッカを防止するために、特許文献 1 には、蓄積タイミングの位 50

相に応じて各ラインの露光量を予測し、予測結果に基づいて各ラインの增幅係数を算出して対応するラインから読み出される画像信号に乗算することが記載されている。

#### 【0007】

また、上記問題を解決するための別の方法として、シャッタ速度に制限を設けることによりフリッカの発生を防ぐ技術が、例えば特許文献2に開示されている。特許文献2によれば、撮像信号から受光量を検出する機能を設け、シャッタスピードを電源周波数に対応させて固定し、シャッタ動作を行うことによりフリッカ除去を行う光量の範囲を複数の光量範囲に分割する。そして、各光量範囲毎にシャッタスピードを段階的に切り換える、各光量範囲内でシャッタスピードを電源周波数に対応させて固定することでフリッカの除去を行う。具体的には、電源周波数が50Hzの時にはシャッタ速度をn/100秒にし、また電源周波数が60Hzの時にはシャッタ速度(電荷蓄積時間)をn/120秒にする。このようにシャッタ速度を制御することで、ライン毎の入射光量の積分値が等しくなるため、フレーム内フリッカを防止することができる。さらに、各光量範囲内では、光量変化に応じてAGC回路のゲイン量を変化させることにより、シャッタスピードの段階的な切り換えによる露光量の変化を緩和し、滑らかな露光制御を行うことが開示されている。10

#### 【0008】

しかしながら、特許文献2にはフリッカの周波数の判定方法については具体的に述べられていない。このフリッカの周波数の判定方法の一例として、例えば特許文献3に、複数フレームを画素毎に加算平均し、さらに加算平均されたフレームを1ライン毎に画素加算した信号を離散フーリエ変換することで周波数判別を行う方法が開示されている。20

#### 【0009】

【特許文献1】特開2004-048616号公報

【特許文献2】特開2003-189172号公報

【特許文献3】特開2001-111887号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

特許文献3における複数フレームの加算平均は、背景を除去してフレーム内フリッカを抽出するために行っているのであるが、このためにフリッカ周波数を特定する処理に時間を要するという欠点を有する。30

#### 【0011】

本発明は上記問題点を鑑みてなされたものであり、撮像素子を用いて画像を撮像する撮像装置において、時間を掛けずにフリッカ周波数を判定できるようにすることを目的とする。

#### 【課題を解決するための手段】

#### 【0012】

上記目的を達成するために、撮像素子を用いて画像を撮像する撮像装置において、外光のフリッカの周波数を判定する本発明の判定方法は、読み出し手段が、前記フリッカの周波数として予測される複数の周波数にそれぞれ対応する複数の時間差で、電荷蓄積時間の等しい電気信号をそれぞれ2フレーム続けて前記撮像素子から読み出すフリッカ検出用フレーム読み出し工程と、前記読み出し手段が、表示装置に表示するための電気信号を前記撮像素子から読み出す表示用フレーム読み出し工程と、判定手段が、前記フリッカ検出用フレーム読み出し工程で続けて読み出した前記2フレームの電気信号に基づいてフリッカの周波数を判定する判定工程とを有し、前記フリッカ検出用フレーム読み出し工程と前記表示用フレーム読み出し工程を異なるタイミングで交互に実行する。40

#### 【0013】

また、本発明の撮像装置は、入射する光学像を電気信号に変換することにより画像を撮像する撮像素子と、外光のフリッカの周波数として予測される複数の周波数にそれぞれ対応する複数の時間差で、電荷蓄積時間の等しい電気信号をそれぞれ2フレーム続けてフリッカ検出用に前記撮像素子から読み出すとともに、表示装置に表示するための電気信号を50

表示用に前記撮像素子から読み出すように制御する読み出し制御手段と、前記読み出し制御手段による制御により前記フリッカ検出用に前記撮像素子から続けて読み出した前記2フレームの電気信号に基づいてフリッカの周波数を判定する判定手段とを有し、前記フリッカ検出用の読み出しと前記表示用の読み出しとを異なるタイミングで交互に実行する。

【発明の効果】

【0014】

本発明によれば、撮像素子を用いて画像を撮像する撮像装置において、時間を掛けずにフリッカ周波数を判定できるようにすることができる。

【発明を実施するための最良の形態】

【0015】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。 10

【0016】

<第1の実施形態>

撮像システムの構成

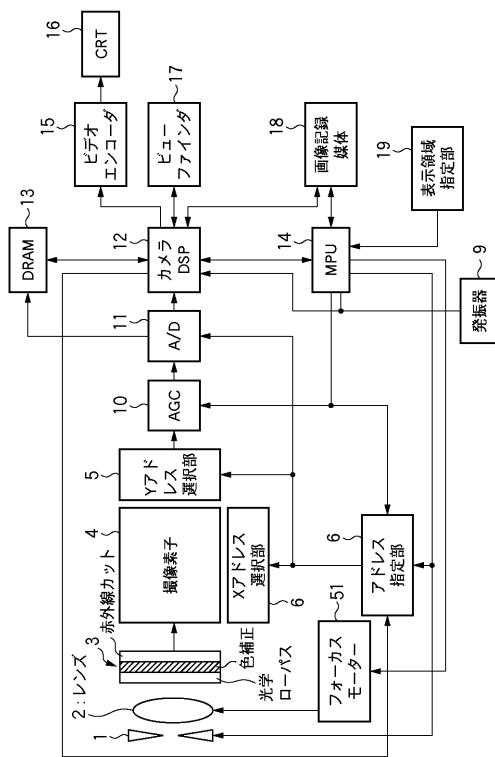

図1は、本実施の形態に係る撮像システムの構成を示すブロック図である。同図において、1は被写体からの入射光量を制御する絞り羽根、2はレンズである。図1ではレンズ2を1枚のレンズで示しているが、通常は複数枚のレンズにより構成されている。3はモアレ等を防ぐ為に光の高域周波数成分をカットする光学ローパス・フィルター、色補正フィルター、および赤外線をカットする為のフィルター等が組み合わされたフィルター群である。4はCMOSセンサ等の複数の画素からなる撮像素子であり、被写体からの光が絞り羽根1、レンズ2を介して撮像素子4上に入射すると、撮像素子4は光電変換を行い、入射光量に応じて得られた電気信号が各画素毎に蓄積される。 20

【0017】

5は撮像素子4のYアドレスを選択するYアドレス選択部、6は撮像素子4のXアドレスを選択するXアドレス選択部であり、アドレス指定部8により制御される。アドレス指定部8からの信号に基づいて、Xアドレス選択部6およびYアドレス選択部5により蓄積した電気信号を読み出す画素を2次元的に選択することができる。

【0018】

撮像素子4からの出力は、オートゲインコントロール(AGC)部10により電圧を制御され、A/D変換器11でデジタル信号に変換される。カメラDSP12は、動画または静止画の画像処理を行う。14はMPUであり、カメラDSP12による画像処理の際に使われるパラメータをカメラDSP12に設定したり、AE、AF制御を行ったりする。なお、実際のAF動作は、MPU14の制御に基づいて、フォーカスマーター51によりレンズ2のフォーカスレンズを光軸方向に動かすことにより行う。 30

【0019】

また、画像処理を行う際の一時的な記憶領域としてDRAM13が用いられ、また、不揮発性の記憶領域として画像記録媒体18が用いられる。画像記録媒体18としては、例えば、スマート・メディア、磁気テープ、または光ディスク等が用いられる。また、画像処理された画像の表示を行う為にビデオエンコーダ15及びCRT16等が設けられている。なお、CRT16は撮像装置と一体的に構成する必要は勿論無く、接続可能に構成しても構わない。また、ビデオエンコーダ15及びCRT16に加えて、又は、代わりに、プリンタを用いるようにしても良い。17はビューファインダであり、例えばLCD等により構成され、画像を撮影する前に被写体を確認したりするために用いられる。 40

【0020】

また、図1では、レンズ2が撮像装置と一体構成されているものについて説明したが、レンズ2を着脱可能なレンズユニットとして構成することも可能であることは言うまでもない。

【0021】

撮像素子の構成

次に本実施形態で用いる撮像素子の構成について説明する。 50

## 【0022】

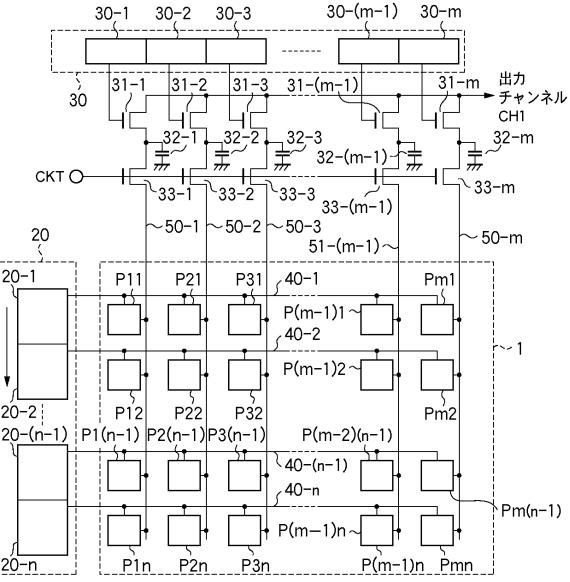

図2において、 $P_{11} \sim P_{mn}$  ( $m, n$  は自然数) は、2次元状に行列配置(マトリクス配置)された $m \times n$  個の画素を示している。撮像素子4は、これら複数画素 $P_{11} \sim P_{mn}$  からなる。垂直走査回路20は、ライン40-1～40-nを走査する回路であり、各ライン40-1～40-nに対応した複数のユニット20-1～20-nで構成されている。また、垂直走査回路20は、Yアドレス選択部5による制御に応じてラインを駆動する。水平走査回路30は、画素 $P_{11} \sim P_{mn}$  の内、垂直走査回路20により走査されたラインに接続された画素 $P_{1x} \sim P_{mx}$  ( $x$  は1～nの内のいずれか) から信号出力線50-1～50-mに導出された電気信号を水平方向に読み出すための回路である。この水平走査回路30は、信号出力線50-1～50-mにそれぞれ対応した複数のユニット30-1～30-mから構成されている。また、水平走査回路30は、Xアドレス選択部6により制御される。なお、各画素 $P_{11} \sim P_{mn}$  には、ライン40-1～40-n、信号出力線50-1～50-m以外の他のラインも接続されているが、ここでは図示を省略する。

## 【0023】

信号出力線50-1～50-mの水平走査回路30側の一端には、トランジスタ33-1～33-m、ラインメモリ32-1～32-m、トランジスタ31-1～31-mが、それぞれ図示の如く1組ずつ配設されている。トランジスタ33-1～33-mは、垂直走査回路20により選択された画素行の信号をラインメモリ32-1～32-mに転送するための転送スイッチとしての役割を担うものであり、制御用のクロックCKTによりオン/オフ制御されるように構成されている。以下、このトランジスタ33-1～33-mを「転送スイッチ」と称する。また、ラインメモリ32-1～32-mは、転送スイッチ33-1～33-mを介して画素 $P_{11} \sim P_{mn}$  から転送される画素信号を一時的に記憶するための容量素子からなる。

## 【0024】

トランジスタ31-1～31-mは、ラインメモリ32-1～32-mに記憶された画素信号を選択するための水平選択スイッチとしての役割を担うものである。トランジスタ31-1～31-mは、Xアドレス選択部6の制御に基づいて水平走査回路30から出力される信号によりオン/オフ制御されるように構成されている。以下、このトランジスタ31-1～31-mを「水平選択スイッチ」と称する。

## 【0025】

水平選択スイッチ31-1～31-mを介して読み出された画素信号は出力チャンネルCH1を介して出力される。なお本実施形態では出力チャンネルが一系統の撮像素子を用いて説明しているが、複数チャンネルを有する撮像素子にも本願発明を適用することが可能である。

## 【0026】

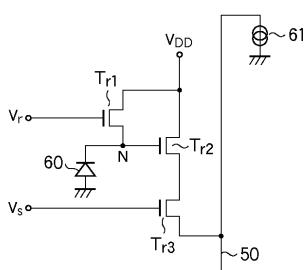

ここで、図3を参照して画素 $P_{11} \sim P_{mn}$  それぞれの構成例について説明する。

## 【0027】

図3に示されるように、画素 $P_{11} \sim P_{mn}$  はそれぞれ、フォトダイオード(PD)60と、PD60をリセットするためのトランジスタTr1を有する。更に、PD60の信号を增幅するトランジスタTr2と、この増幅した信号を対応する信号出力線50-1～50-mのいずれか(以下、「信号出力線50」と記す。)に読み出すためのトランジスタTr3が、図示のように接続されて構成されている。電流源61は、各信号出力線50-1～50-m毎に設けられており、電流源61とトランジスタTr2でフォローアンプを構成している。また、 $V_{DD}$ は電源である。なお、画素 $P_{11} \sim P_{mn}$ としては、図3に示す構成の他にも、公知の種々のタイプのものを採用することができる。

## 【0028】

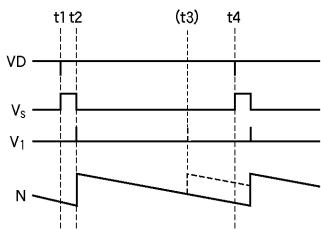

次に、図3に示す構成を有する画素の動作について、図4のタイミングチャートを参照して説明する。

## 【0029】

10

20

30

40

50

垂直同期信号 V D の立ち下がり ( t 1 ) に同期して、画素選択信号 V s が「 H 」レベルになると、選択用のトランジスタ T r 3 がオンとなる。これにより、それまでにノード N に蓄積された P D 6 0 の電荷が選択用のトランジスタ T r 3 を介して信号出力線 5 0 に読み出される。次いで、この画素選択信号 V s の立ち下がり ( t 2 ) に同期して画素リセット信号 V r が「 H 」レベルになると、リセット用のトランジスタ T r 1 がオフされ、ノード N に蓄積された P D 6 0 の電荷が電源レベルにリセットされる。画素リセット信号 V r が「 L 」に戻ってリセット用のトランジスタ T r 1 が O F F になった直後から、 P D 6 0 への光の入射に応じて発生した電荷が再び蓄積され、ノード N のレベルはリセットレベルから徐々に下がっていく。そして、次の垂直同期信号 V D の立ち下がり ( t 4 ) に同期して、次のフレームで画素選択信号 V s が「 H 」レベルになると、 P D 6 0 によりノード N に蓄積された電荷は信号出力線 5 0 に読み出される。なお、次のフレームで画素選択信号 V s が「 H 」となる前に、再度、画素リセット信号 V r を「 H 」レベルにすると（例えば、 t 3 ）、ノード N の電荷がリセットされ、当該タイミングから再び蓄積動作が開始されることになる（電子シャッタ）。

#### 【 0 0 3 0 】

##### 全画素読み出し制御

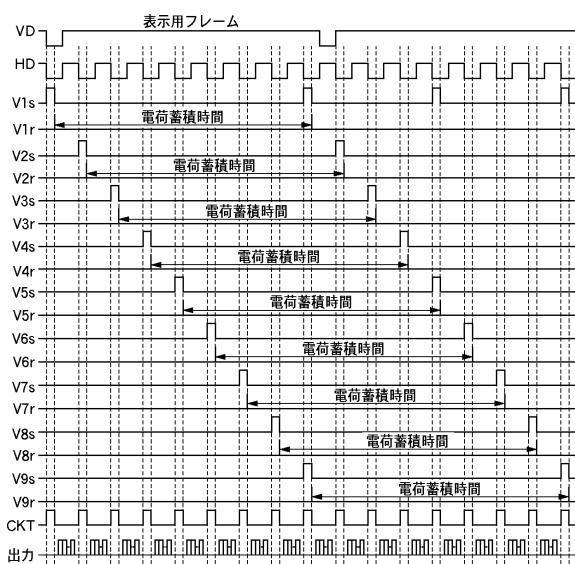

次に、図 5 のタイミングチャートを参照して、撮像素子 4 の画素 P 1 1 ~ P m n の順次読み出し方法について説明する。なお、図 5 では 9 行分の読み出し信号について示しているが、撮像素子 4 の全行の読み出しについて、同様の制御が行われる。

#### 【 0 0 3 1 】

V D は垂直同期信号、 H D は水平同期信号、 V 1 s ~ V 9 s は画素選択信号、 V 1 r ~ V 9 r は画素リセット信号、 C K T は転送スイッチ 3 3 - 1 ~ 3 3 - m に入力されるクロック、出力は出力チャンネルから出力される画素信号である。この順次読み出しの動作に入ると、 Y アドレス選択部 5 は、垂直走査回路 2 0 が各ユニット 2 0 - 1 ~ 2 0 - n を配列方向に順次走査を行うように制御する。先ず、水平プランキング期間（水平同期信号 H D が「 L 」レベルの期間）内に垂直走査回路 2 0 のユニット 2 0 - 1 から出力される画素選択信号 V 1 s を「 H 」レベルにして、 1 行目の画素 P 1 1 ~ P m 1 を選択する。この間、転送スイッチ 3 3 - 1 ~ 3 3 - m に入力されるクロック C K T は「 H 」レベルである為、選択された 1 行目の画素 P 1 1 ~ P m 1 の画素信号は、ラインメモリ 3 2 - 1 ~ 3 2 - m に記憶される。

#### 【 0 0 3 2 】

この後、画素選択信号 V 1 s が「 L 」となるタイミングで画素リセット信号 V 1 r が「 H 」レベルとなり、画素 P 1 1 ~ P m 1 の電荷（即ち、ノード N ）がリセットされる。この後、水平有効期間（水平同期信号 H D が「 H 」レベルの期間）内に、 X アドレス選択部 6 は、水平走査回路 3 0 が各ユニット 3 0 - 1 ~ 3 0 - m を配列方向に順次走査を行うように制御する。つまり、 1 画素ずつ順番に、水平転送スイッチ 3 1 - 1 ~ 3 1 - m をオンさせる水平選択信号を出力させる。これにより、ラインメモリ 3 2 - 1 ~ 3 2 - m に記憶された 1 行目の画素 P 1 1 ~ m 1 の各画素信号が、水平選択スイッチ 3 1 - 1 ~ 3 1 - m を介して出力チャンネル C H 1 より出力される。

#### 【 0 0 3 3 】

次の水平プランキング期間内で垂直走査回路 2 0 より画素選択信号 V 2 s が「 H 」レベルとなると、 2 行目の画素 P 1 2 ~ P m 2 が選択される。この間、転送スイッチ 3 3 - 1 ~ 3 3 - m に入力されるクロック C K T が「 H 」レベルである為、選択された画素 P 1 2 ~ P m 2 の画素信号は、ラインメモリ 3 2 - 1 ~ 3 2 - m に記憶される。この後、画素リセット信号 V 2 r が「 H 」レベルとなり、画素 P 1 2 ~ P m 2 の電荷がリセットされる。この後、水平有効期間内に、 X アドレス選択部 6 は、水平走査回路 3 0 が各ユニット 3 0 - 1 ~ 3 0 - m を配列方向に順次走査を行うように制御する。つまり、 1 画素ずつ順番に、水平転送スイッチ 3 1 - 1 ~ 3 1 - m をオンさせる水平選択信号を出力させる。これにより、ラインメモリ 3 2 - 1 ~ 3 2 - m に記憶された 2 行目の画素 P 1 2 ~ P m 2 の各画素信号が、水平選択スイッチ 3 1 - 1 ~ 3 1 - m を介して出力チャンネル C H 1 より出力され

10

20

30

40

50

る。

#### 【0034】

このように、各行の画素リセット信号  $V1r \sim V9r$  により画素  $P1y \sim Pmy$  ( $y$  は 1 ~ 9 のいずれかを示す。) 即ち、各行のノード  $N$  がリセットされた後、次の各行の画素選択信号  $V1s \sim V9s$  が「H」レベルの間までが、電荷蓄積時間となる。

#### 【0035】

これ以降、同様にして水平プランキング期間中に各行の画素が順次選択され、水平有効期間中に行毎の画素信号が順次出力されることで、全画素の画素信号が順次読み出される。

#### 【0036】

##### フリッカ周波数の判定

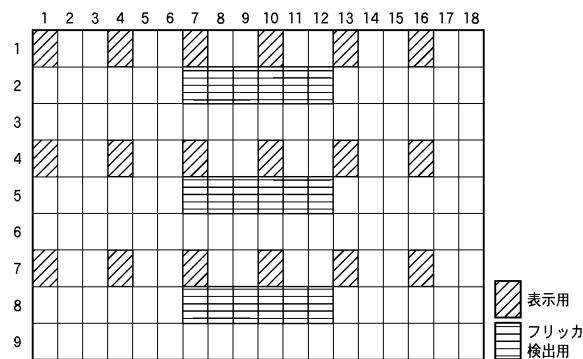

次に本第1の実施形態におけるフリッカ周波数の判定方法について説明する。本第1の実施形態では、フリッカ周波数の判定を行うためのフリッカ検出用画像(フレーム)の読み出しを、EVF表示等に用いる表示用画像(フレーム)の読み出しの前または後のタイミングで行う場合について説明する。

#### 【0037】

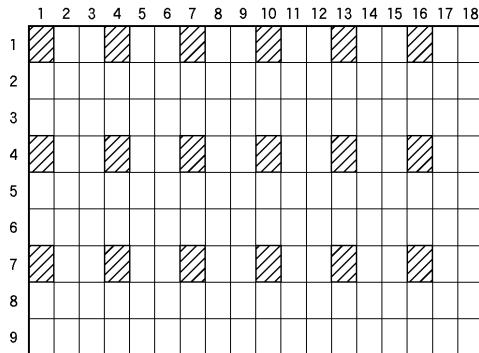

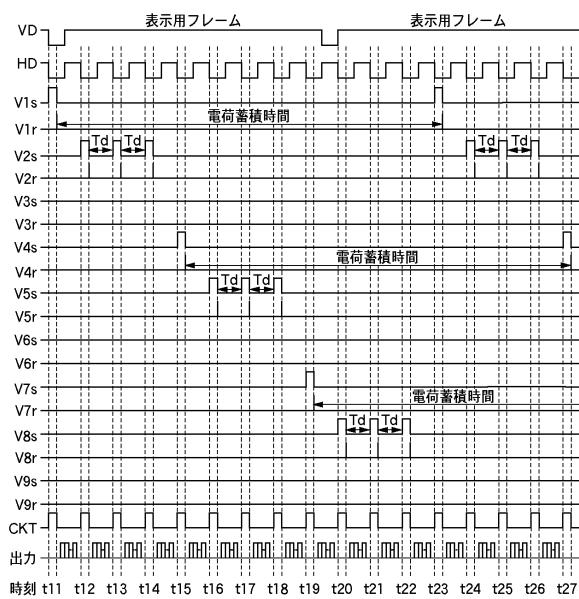

図6は表示用フレームの読み出しパターン例を示しており、水平1/3間引き読み出し、垂直1/3間引き読み出しである。また、図7はフリッカ検出用フレームの読み出しパターン例を示しており、水平中央部読み出し、垂直1/3間引き読み出しである。なお、図6及び図7では、読み出す画素を斜線により示している。図8は図6及び図7に示す画素信号を3フレーム周期で読み出すタイミングを説明するためのタイミングチャートである。なお、図6～図8では、9行18列分の画素について説明しているが、撮像素子4の全画素の読み出しについて、同様の制御が行われる。

#### 【0038】

本第1の実施形態では、フリッカ検出用フレームとして、電荷蓄積時間を1/100秒または1/120秒としたフレームを2フレーム続けて撮像し、得られた2つのフレームに共通した領域の輝度値を比較することで、フリッカの周波数を判定する。このように電荷蓄積時間を1/100秒または1/120秒とすることで、フレーム間の蓄積タイミングを1/100秒または1/120秒ずらすことができる。この時、表示用フレームの電荷蓄積時間を1/100秒または1/120秒にしてしまうと、室内等の暗い環境下では高いゲインをかける必要があるためにノイズが悪化することが考えられる。そこで、本第1の実施形態では、表示用フレームを読み出す前または後にフリッカ検出用フレームを読み出すことで、表示用フレームの蓄積時間に制限がかからないようにする。このように用途に応じた複数種類のフレームを順番に読み出す方式について以下に説明する。

#### 【0039】

本第1の実施形態では、図8に示すように、まず、2フレーム分、図7で斜線で示す画素をフリッカ検出用フレームとして読み出し、次の3フレーム目で、図6で斜線で示す画素を表示用フレームとして読み出す。以降、フリッカ検出用フレームを2フレーム分読み出し、次に、表示用フレームを1フレーム分読み出す処理を繰り返す。本第1の実施形態では、フリッカ検出用フレームの読み出しにおいて選択される行と表示用フレームの読み出しにおいて選択される行とは共通しており、この例では1、4、7行目を順番に選択する。更に各行について、フリッカ検出用フレームとしては中央部の画素(この例では7~12列目)のみの信号が読み出され、表示用フレームとしては2画素を間引いた画素(この例では1、4、7、10、13、16列目)の信号が、それぞれ読み出される。なお、読み出す行や列は図6及び図7に限るものではない。

#### 【0040】

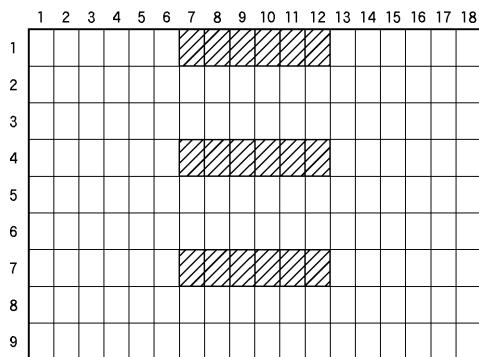

次に、図8のタイミングチャートを参照して、第1の実施形態に係る上述したフリッカ検出用フレームと表示用フレームの読み出し動作について、更に詳細に説明する。

#### 【0041】

$VD$  は垂直同期信号、 $HD$  は水平同期信号、 $V1s \sim V9s$  は画素選択信号、 $V1r \sim V9r$  は

10

20

30

40

50

画素リセット信号、C K Tは転送スイッチに入力されるクロック、出力は出力チャンネルから出力される画素信号である。

#### 【0042】

1フレーム目では、フリッカ検出用フレームの読み出しを行う。フリッカ検出用フレームの読み出し時には、V Dを100Hzまたは120Hzに設定することにより、電荷蓄積時間T dを1/100秒または1/120秒とする。また、図7に示すように、3行から各行6画素分の画素信号を読み出すため、H Dとしては、ラインメモリ32-1~32-mから6画素分の画素信号を読み出し可能な駆動速度内であって、300Hzまたは360Hzより速い周波数であれば良い。図8では300Hzまたは360Hzとして示しているが、撮像素子4の画素構成や読み出し行及び列数に応じて適宜変更することができる。10

#### 【0043】

先ず、垂直走査回路20は、各ユニット20-1~20-nの配列方向に沿って、1行目の走査を行う。即ち、水平プランキング期間（水平同期信号H Dが「L」レベルの期間）内に垂直走査回路20のユニット20-1から出力される画素選択信号V1sを「H」レベルにする。これにより、1行目の画素P11~Pm1のトランジスタTr3がONとなり、1行目が選択される。この間、転送スイッチ33-1~33-mに入力されるクロックC K Tは「H」レベルである為、選択された1行目の画素P11~Pm1の画素信号は、ラインメモリ32-1~32-mに記憶される。なお、ここでラインメモリ32-1~32-mに記憶された画素信号は、後述するように1フレーム前の表示用フレームの画素信号として3列おきに読み出される。20

#### 【0044】

この後、画素選択信号V1sが「L」となるタイミングで画素リセット信号V1rが「H」レベルとなり、画素P11~Pm1の電荷（即ち、ノードN）がリセットされる。その後、水平有効期間（水平同期信号H Dが「H」レベルの期間）内に、Xアドレス選択部6は、水平走査回路30のユニット30-7~30-12からのみ、順次水平選択信号を出力するように制御する。これにより、1行目の画素P11~Pm1の内、選択された7~12列目の画素の信号が、水平選択スイッチ31-7~31-12を介して出力チャンネルCH1より出力される。30

#### 【0045】

これ以降、同様に水平プランキング期間中に4行目、7行目の画素が順次選択され、水平有効期間中に行毎の選択された列（7~12列目）の画素信号が出力されることで、図7に示されるような読み出しがなされる。

#### 【0046】

2フレーム目も1フレーム目と同じように読み出しを行う。2フレーム目もフリッカ検出用フレームであるため、垂直同期信号V Dの周波数は1フレーム目と同じ周波数の100Hzまたは120Hz、電荷蓄積時間T dは1/100秒または1/120秒である。

#### 【0047】

3フレーム目では、表示用フレームの読み出しを行う。表示用フレームでは、垂直同期信号V Dの周波数は、例えば露出値に応じて、表示に適した明るさの画像を得ることができるよう蓄積時間となるように変更する。他に、ビューファインダ17やCRT16等の表示装置の規格に基づいて、予め設定された周波数にするなど、適宜変更することができる。40

#### 【0048】

3フレーム目の表示用フレームの1行目の読み出しあは、その直前の2フレーム目のフリッカ検出用フレームで蓄積された1行目の画素P11~Pm1の画素信号が、水平プランキング期間中に、ラインメモリ32-1~32-mに記憶されてから開始される。

#### 【0049】

画素選択信号V1sが「L」となるタイミングで画素リセット信号V1rが「H」レベルとなり、画素P11~Pm1（即ち、ノードN）の電荷がリセットされる。その後、水平有50

効期間（水平同期信号HDが「H」レベルの期間）内に、Xアドレス選択部6は、水平走査回路30の各ユニット30-1、30-4、30-7、30-10、30-13、30-16からのみ、順次水平選択信号を出力するように制御する。これにより、1行目の画素P11～Pm1の内、選択された1、4、7、10、13、16列目の画素の信号が、水平選択スイッチ31-1、31-4、31-7、31-10、31-13、31-16を介して出力チャンネルCH1より出力される。

#### 【0050】

これ以降、同様に水平プランギング期間中に4行目、7行目の画素が順次選択され、水平有効期間中に行毎の選択された列（1、4、7、10、13、16列目）の画素信号が出力されることで、図6に示されるような読み出しがなされる。

10

#### 【0051】

上述したようにして、2回のフリッカ検出用フレームの読み出し、1回の表示用フレームの読み出しを繰り返す。勿論、表示用フレームを読み出した後、フリッカ検出用フレームを読み出す順番でも構わない。

#### 【0052】

またフリッカ検出用フレームを高速に読み出すために、フリッカ検出用フレーム読み出し時は駆動周波数を上げる方式を採用してもよい。

#### 【0053】

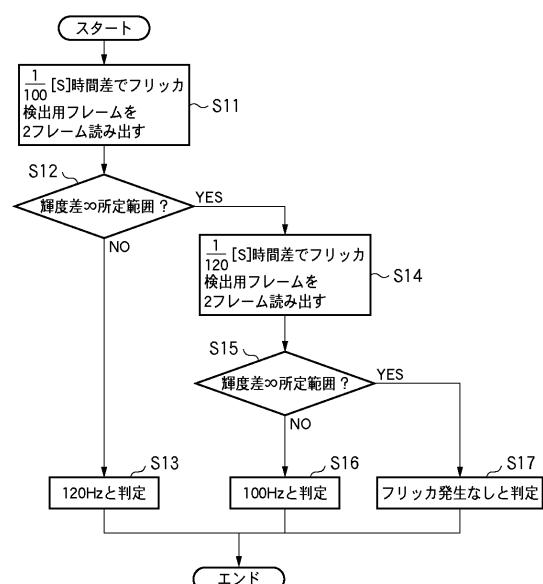

次に、上記で説明した1/100秒もしくは1/120秒、蓄積タイミングに時間差のついた2つのフリッカ検出用フレームの画像を用いて、フリッカの周波数を判定する方法について、図9のフローチャート用いて説明する。

20

#### 【0054】

図9において、先ず、上述したようにして1/100秒蓄積タイミングに時間差を付けて電荷を蓄積した2フレーム分のフリッカ検出用フレームを読み出す（ステップS11）。そして、読み出した2フレームの画像に共通した領域（例えば、図7に示す領域）の輝度値を比較する（ステップS12）。このとき、2フレームの画像の蓄積タイミングの時間差は1/100秒であるため、背景が大きく変化している可能性は低い。なお、この輝度値を算出するための領域は、背景の影響をさらに除去するために、受光領域全てを水平方向に積分させる。

#### 【0055】

30

ステップS12における輝度値の比較結果、2つのフリッカ検出用フレーム間の輝度値の差（輝度差）が予め設定された範囲外にある（例えば、輝度差の絶対値が閾値よりも大きい）と判断した場合は、フレーム内フリッカが発生していると判定する。この時、蓄積時間が1/100秒でフレーム内フリッカが発生していることから、120Hzのフリッカが発生していると判定する（ステップS13）。そこで次の表示用フレームにて、120Hzで光量が変動する光源下でフリッカの発生を抑制することのできるシャッタ速度、例えば、シャッタ速度がN/120秒（Nは整数）となるように設定する。

#### 【0056】

一方、ステップS12における輝度値の比較結果、2つのフレーム間の輝度差が予め設定された範囲内にある（例えば、輝度差の絶対値が閾値以下）と判断した場合、光源は100Hzの蛍光灯もしくはフリッカの発生しない外光のどちらかである。そこで、次のフリッカ検出用フレームの読み出しタイミングで、1/120秒、蓄積タイミングに時間差をつけて、1/120秒を蓄積時間とする2フレーム分のフリッカ検出用フレームを読み出す（ステップS14）。そして、読み出した2フレームの画像に共通した領域（例えば、図7に示す領域）の輝度値を比較する（ステップS15）。

40

#### 【0057】

ステップS15における輝度値の比較結果、2つのフレーム間の輝度差が予め設定された範囲外にある（例えば、輝度差の絶対値が閾値よりも大きい）と判断した場合は100Hzのフリッカが発生していると判定する。そこで次の表示用フレームにて、100Hzで光量が変動する光源下でフリッカの発生を抑制することのできるシャッタ速度、例えば

50

、シャッタ速度がN / 100秒（Nは整数）となるように設定する。

【0058】

一方、ステップS15における輝度値の比較結果、2つのフレーム間の輝度差が予め設定された範囲内にある（例えば、輝度差の絶対値が閾値以下）と判断した場合はフリッカが発生していないと判定する。この場合、次の表示用フレームのシャッタ速度に制限を設ける必要が無い。

【0059】

上記のフリッカ周波数判定方法により、シャッタ速度をフリッカが発生しない値にリアルタイムで変更することが可能になる。

【0060】

なお、図9に示す上記処理では、フリッカ検出用フレームの読み出し時に、ステップS11で先に100Hz時間差を付けて読み出し、輝度差が所定範囲内にある場合に、ステップS14で120Hz時間差を付けて読み出す場合について説明した。しかしながら、本発明はこれに限るものではなく、先に120Hz時間差を付けて読み出すようにしてもよく、また、時間差も100Hz及び120Hzに限るものではない。検出したいフリッカ周波数に対応する時間差を付けてフリッカ検出用フレームを読み出し、輝度値を比較すればよい。

【0061】

また、一旦フリッカ周波数を判定した後のフリッカ検出用フレームの読み出し及び判定処理は、目的に応じて様々な応用が考えられる。例えば、フリッカ検出用フレームの読み出しを行わないように制御しても、検出したフリッカ周波数に対応する時間差でフリッカ検出用フレームを読み出すようにしても良い。他に、撮影中に光源が変わることを考慮して、時間差を変更しながらフリッカ検出用フレームを読み出す処理を続けても、間欠的にフリッカ検出用フレームを読み出すように制御しても良い。このように、一旦フリッカ周波数を判定した後に行われる処理は、本願発明の範囲を限定するものではない。

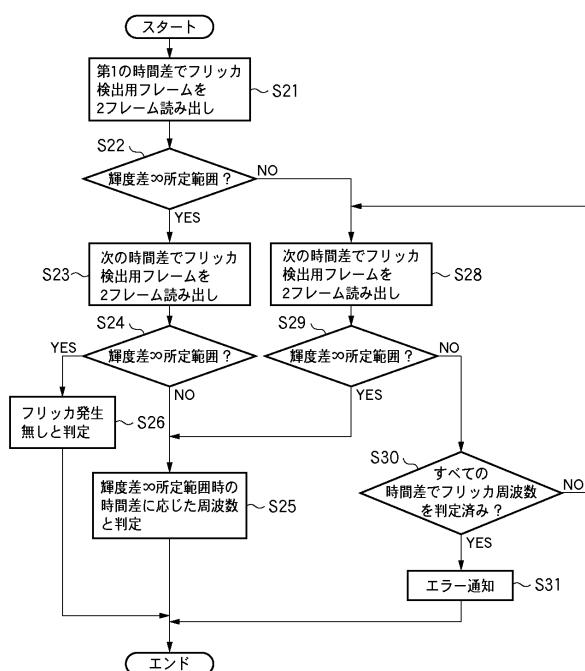

【0062】

<第2の実施形態>

上記第1の実施形態では、光源の光量変動の周波数が100Hzまたは120Hzの2種類である場合のフリッカ周波数の判定方法について説明した。しかしながら、本発明は2種類の周波数の判定に限るものではなく、3種類以上の周波数の判定に適用することができる。その場合の判定方法について、図10のフローチャートを参照して説明する。図10に示す判定方法は図9に示す判定方法に変わって行われるもので、撮像システムの構成及びその他の処理は第1の実施形態と同じであるため、その説明を省略する。

【0063】

本第2の実施形態では、判定対象である3種類以上のフリッカ周波数を、MPU14のメモリや、不図示のメモリに予め記憶してあるものとする。

【0064】

先ず、前記メモリに記憶してある複数の周波数の内、第1の周波数に対応する蓄積タイミングの時間差で、フリッカ検出用フレームを2フレーム分読み出す（ステップS21）。そして、読み出した2フレームの画像に共通した領域（例えば、図7に示す領域）の輝度値を比較する（ステップS22）。

【0065】

ステップS22における比較結果、輝度差が予め設定された範囲内にある（例えば、輝度値の差の絶対値が閾値以下）と判断した場合、次の周波数に対応する蓄積タイミングの時間差でフリッカ検出用フレームを2フレーム分読み出す（ステップS23）。そして、読み出した2フレームの画像に共通した領域（例えば、図7に示す領域）の輝度値を比較する（ステップS24）。2つのフレーム間の輝度差が予め設定された範囲外にある（例えば、輝度値の差の絶対値が閾値よりも大きい）と判断した場合は、輝度値が予め設定された範囲内にあったときの時間差に応じた周波数を、フリッカ周波数として判定する（ステップS25）。一方、輝度差が予め設定された範囲内にある場合、フリッカが発生して

10

20

30

40

50

いないと判定する（ステップS26）。

**【0066】**

また、ステップS22における輝度値の比較結果、2つのフレーム間の輝度差が予め設定された範囲外にある（例えば、輝度値の差の絶対値が閾値よりも大きい）と判断した場合は、ステップS28に進む。ステップS28では、次の周波数に対応する蓄積タイミングでフリッカ検出用フレームを2フレーム分読み出し、読み出した2フレームの画像に共通した領域（例えば、図7に示す領域）の輝度値を比較する（ステップS29）。2つのフレーム間の輝度差が予め設定された範囲内にある（例えば、輝度値の差の絶対値が閾値以下）と判断した場合、現在の周波数をフリッカ周波数として判定する（ステップS25）。一方、輝度差が予め設定された範囲外にある（例えば、輝度値の差の絶対値が閾値よりも大きい）と判断した場合は、予め記憶されている全ての周波数に対応した時間差でフリッカ判定処理を終了したか判断する（ステップS30）。全ての周波数に対応した時間差で終了していなければ、ステップS28に戻って次の周波数に対応した時間差で上記処理を繰り返し、終了していれば、フリッカ判定処理に失敗した旨のエラー通知を行ってから（ステップS31）、処理を終了する。10

**【0067】**

このように、1つの時間差で得られたフレーム間の輝度差が所定範囲内にあって、且つ、少なくとも他の1つの時間差で得られたフレーム間の輝度差が同じ所定範囲外にある場合、輝度差が範囲内にある時間差に対応する周波数をフリッカ周波数として判定する。また、2種類の時間差でフレームを読み出しても、輝度差が所定範囲内にある場合には、フリッカが発生していないと判断する。20

**【0068】**

このように第2の実施形態によれば、複数の光源の周波数について、フリッカ周波数を判定することができる。

**【0069】**

<第3の実施形態>

次に、本発明の第3の実施形態について説明する。

**【0070】**

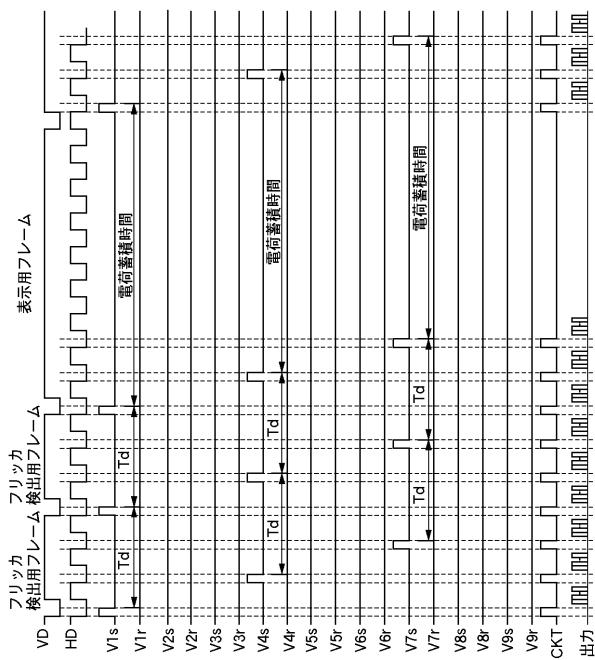

第1の実施形態では、フリッカ検出用フレームを2フレーム読み出した後、表示用フレームを1フレーム読み出していた。第3の実施形態では表示用フレームで画像として使用しないラインをフリッカ検出用画像として読み出すことで、高フレームレート化を図ることを目的とする。30

**【0071】**

図11は、本第3の実施形態において読み出す画素の一例を示す図であり、表示用画像は水平1/3間引き読み出し、垂直1/3間引き読み出しどとする。この例では1、4、7行目を順番に選択する。また、フリッカ検出用画像は水平中央部読み出し、垂直1/3間引き読み出しどとするが、読み出す行は、表示用画像に用いられない行である。この例では2、5、8行目を順番に選択する。

**【0072】**

なお第3の実施形態の撮像システムの構成及びフリッカ周波数判定方法は第1または第2の実施形態と同じであるためその説明を割愛し、以下に撮像素子4からの読み出し動作について、図12のタイミングチャートを参照しながら説明する。40

**【0073】**

V Dは垂直同期信号、H Dは水平同期信号、V1s～V9sは画素選択信号、V1r～V9rは画素リセット信号、C K Tは転送スイッチに入力されるクロック、出力は出力チャンネルから出力される画素信号である。

**【0074】**

先ず、垂直走査回路20は、各ユニット20-1～20-nの配列方向に沿って、1行目の走査を行う。即ち、水平プランギング期間（水平同期信号H Dが「L」レベルの期間）内に垂直走査回路20のユニット20-1から出力される画素選択信号V1sを「H」レ50

ベルにする。これにより、1行目の画素P<sub>11</sub>～P<sub>m1</sub>のトランジスタTr3がONとなり、1行目が選択される。この間、転送スイッチ33-1～33-mに入力されるクロックCKTは「H」レベルである為、選択された1行目の画素P<sub>11</sub>～P<sub>m1</sub>の画素信号は、ラインメモリ32-1～32-mに記憶される。なお、ここでラインメモリ32-1～32-mに記憶された画素信号は、1フレーム前の表示用フレームの画素信号である。

#### 【0075】

この後、画素選択信号V1sが「L」となるタイミングで画素リセット信号V1rが「H」レベルとなり、画素P<sub>11</sub>～P<sub>m1</sub>の電荷（即ち、ノードN）がリセットされる。その後、水平有効期間（水平同期信号HDが「H」レベルの期間）内に、Xアドレス選択部6は、水平走査回路30の各ユニット30-1、30-4、30-7、30-10、30-13、30-16からのみ、順次水平選択信号を出力するように制御する。これにより、1行目の画素P<sub>11</sub>～P<sub>m1</sub>の内、選択された1、4、7、10、13、16列目の画素の信号が、水平選択スイッチ31-1、31-4、31-7、31-10、31-13、31-16を介して出力チャンネルCH1より出力される。この出力された値は、表示用画像の1ライン目として、DRM13や不図示のメモリに確保された表示用画像記憶領域に格納する。10

#### 【0076】

2ライン目ではフリッカ検出用画像として1/100秒もしくは1/120秒、蓄積タイミングに時間差のある2つの画像を読み出す。図12において、蓄積時間Tdは1/100秒もしくは1/120秒である。先ず、時刻t12において水平プランキング期間内で画素選択信号V2sを「H」レベルにし、2行目の画素P<sub>12</sub>～P<sub>m2</sub>を選択する。この間、転送スイッチ33-1～33-mに入力されるクロックCKTは「H」レベルである為、選択された画素P<sub>12</sub>～P<sub>m2</sub>の画素信号は、ラインメモリ32-1～32-mに記憶される。ただし、ラインメモリ32-1～32-mに記憶された画素信号は使用することが無いので、破棄する。20

#### 【0077】

この後、画素選択信号V2sが「L」となるタイミングで画素リセット信号V2rが「H」レベルとなり、画素P<sub>12</sub>～P<sub>m2</sub>の電荷（即ち、ノードN）がリセットされる。次の水平プランキング期間内（時刻t13）で、画素選択信号V2sを「H」レベルにし、2行目の画素P<sub>12</sub>～P<sub>m2</sub>を選択する。この間、転送スイッチ33-1～33-mに入力されるクロックCKTは「H」レベルである為、選択された画素P<sub>12</sub>～P<sub>m2</sub>の画素信号は、ラインメモリ32-1～32-mに記憶される。そして、画素選択信号V2sが「L」となるタイミングで画素リセット信号V2rが「H」レベルとなり、画素P<sub>12</sub>～P<sub>m2</sub>の電荷（即ち、ノードN）がリセットされる。この後、水平有効期間（水平同期信号HDが「H」レベルの期間）内に、Xアドレス選択部6は、水平走査回路30がユニット30-7～30-12からのみ、順次水平選択信号を出力するように制御する。これにより、2行目の画素P<sub>12</sub>～P<sub>m2</sub>の内、選択された7～12列目の画素の画素信号が、水平選択スイッチ31-7～31-12を介して出力チャンネルCH1より出力される。この出力された値を第1のフリッカ検出用画像の1ライン目として、DRM13や不図示のメモリに確保された第1のフリッカ検出用画像記憶領域に格納する。30

#### 【0078】

さらに同様の方法で時刻t14から第2のフリッカ検出用画像の1ライン目の画素信号を出力チャンネルCH1に出力し、DRM13や不図示のメモリに確保された第2のフリッカ検出用画像記憶領域に格納する。

#### 【0079】

これ以降、表示用画像としては水平プランキング期間中に4行目、7行目の画素が順次に選択され、水平有効期間中に行毎の選択された列（各1、4、7、10、13、16列目）の画素信号が出力され、表示用画像記憶領域に順次格納される。またフリッカ検出用画像に関しても水平プランキング期間中に5行目、8行目の画素が順次に選択され、水平有効期間中に行毎の選択された列（7～12列目）の画素信号が出力され、第1および第4050

2 のフリッカ検出用画像記憶領域に順次格納される。

**【 0 0 8 0 】**

上述したようにして第 1 および第 2 のフリッカ検出用画像記憶領域に格納された第 1 及び第 2 のフリッカ検出用画像を用いて、図 9 のフローチャートを参照して上記第 1 の実施形態で説明したようにして、フリッカの周波数を特定する。

**【 0 0 8 1 】**

上記第 3 の実施形態によれば、表示用画像の読み出し時にフリッカ検出用画像を読み出すことができる。

**【 0 0 8 2 】**

<変形例 >

10

上記第 1 乃至第 3 の実施形態では、表示用フレームまたは画像、2 つのフリッカ検出用フレームまたは画像をそれぞれ読み出し、デジタル信号に変換してメモリに格納する場合について説明していた。しかしフリッカ検出のためには  $T_d$  秒差がついた出力値の差分値が分かればよい。そこでアナログ信号をデジタル信号に変換せず電圧の状態で差分値を検出することで、フリッカ検出の高速化を図ることができる。

**【 0 0 8 3 】**

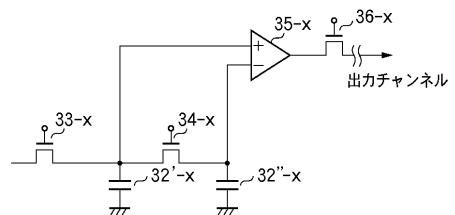

図 13 は図 2 の各水平選択スイッチ  $31 - x$  と転送スイッチ  $33 - x$  ( $x$  は正の整数) 間をラインメモリ  $32' - x$ 、 $32'' - x$  およびトランジスタ  $34 - x$ 、差動アンプ  $35 - x$  で置き換えたものである。トランジスタ  $34 - x$  は、ラインメモリ  $32' - x$  に蓄積された電荷をラインメモリ  $32'' - x$  に転送するためのスイッチを担う。例えば、第 3 の実施形態の図 12 のタイミングチャートにおいて、第 1 のフリッカ検出用画像の蓄積が終了し、クロック CKT が H レベルになると、ラインメモリ  $32' - x$  に電荷が蓄積される。

20

**【 0 0 8 4 】**

さらに第 2 のフリッカ検出用画像用に電荷蓄積を行っている期間に、トランジスタ  $34 - x$  をオンすることで第 1 のフリッカ検出用画像の電荷がラインメモリ  $32'' - x$  に蓄積される。さらに第 2 のフリッカ検出用画像の蓄積が終了し、クロック CKT が H レベルになるとラインメモリ  $32' - x$  に電荷が蓄積される。すると  $35 - x$  の差動アンプの出力はラインメモリ  $32' - x$  および  $32'' - x$  の電圧の差分値が出力される。さらに水平選択スイッチ  $31 - x$  をオンすることで  $T_d$  秒時間差のある 2 つのフリッカ検出用画像の差分値が出力チャンネル CH1 を介して出力される。このようにして出力された差分値に基づいて、フリッカ周波数を判定することができる。

30

**【 0 0 8 5 】**

上記の通り本変形例によれば、フリッカ周波数の判定をより高速に行うことができる。

**【 図面の簡単な説明 】**

**【 0 0 8 6 】**

**【 図 1 】** 本発明の第 1 の実施形態における撮像システムの構成を示すブロック図である。

**【 図 2 】** 本発明の第 1 の実施形態における撮像素子の構成例を示す図である。

**【 図 3 】** 本発明の第 1 の実施形態における撮像素子の各画素の構成を示す回路図である。

**【 図 4 】** 本発明の第 1 の実施形態における撮像素子の 1 画素の駆動タイミングを示すタイミングチャートである。

40

**【 図 5 】** 本発明の第 1 の実施形態における撮像素子の順次走査を説明する為のタイミングチャートである。

**【 図 6 】** 本発明の第 1 の実施形態における表示用フレームの読み出し画素の一例を示す概念図である。

**【 図 7 】** 本発明の第 1 の実施形態におけるフリッカ検出用フレームの読み出し画素の一例を示す図である。

**【 図 8 】** 本発明の第 1 の実施形態におけるフリッカ検出時の撮像素子の読み出しタイミングを説明するためのタイミングチャートである。

**【 図 9 】** 本発明の第 1 の実施形態におけるフリッカ周波数判定方法の手順を示すフロー

50

ヤートである。

【図10】本発明の第2の実施形態におけるフリッカ周波数判定方法の手順を示すフロー

チャートである。

【図11】本発明の第3の実施形態における表示用フレーム及びフリッカ検出用フレーム

の読み出し画素の一例を示す図である。

【図12】本発明の第3の実施形態におけるフリッカ検出時の撮像素子の読み出しタイミ

ングを説明するためのタイミングチャートである。

【図13】本発明の変形例におけるフレーム間の輝度差を検出するための構成例を示す回

路図である。

【図14】フリッカの発生原理を説明するための図である。

【符号の説明】

【0087】

- 1 : 絞り羽根

- 2 : レンズ

- 3 : フィルター群

- 4 : 撮像素子

- 5 : Y アドレス選択部

- 6 : X アドレス選択部

- 7 : タイミング調整部

- 8 : アドレス指定部

- 10 : オートゲインコントロール部

- 11 : A / D 変換器

- 12 : カメラDSP

- 13 : DRAM

- 14 : MPU

- 15 : ビデオエンコーダ

- 16 : CRT

- 17 : ビューファインダ

- 18 : 画像記録媒体

- 51 : フォーカスマーター

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

---

フロントページの続き

審査官 鈴木 肇

(56)参考文献 特開2002-084466(JP,A)

特開2006-287361(JP,A)

特開2001-119708(JP,A)

特開2004-048616(JP,A)

特開2003-163832(JP,A)

特開2006-245784(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257