(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5322668号

(P5322668)

(45) 発行日 平成25年10月23日(2013.10.23)

(24) 登録日 平成25年7月26日(2013.7.26)

(51) Int.Cl.

F 1

H01L 21/8244 (2006.01)

H01L 27/10 381

H01L 27/11 (2006.01)

H01L 21/30 570

H01L 21/027 (2006.01)

請求項の数 3 (全 12 頁)

(21) 出願番号

特願2009-10653 (P2009-10653)

(22) 出願日

平成21年1月21日(2009.1.21)

(65) 公開番号

特開2010-171106 (P2010-171106A)

(43) 公開日

平成22年8月5日(2010.8.5)

審査請求日

平成23年5月19日(2011.5.19)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100103263

弁理士 川崎 康

(74) 代理人 100107582

弁理士 関根 賀

(74) 代理人 100118843

弁理士 赤岡 明

(74) 代理人 100108785

弁理士 箱崎 幸雄

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法およびフォトマスク

## (57) 【特許請求の範囲】

## 【請求項 1】

第1および第2の領域を有する半導体基板上にマスク材を形成する工程と、前記第1の領域の前記マスク材上に芯材をパターン形成する工程と、前記芯材の両側面に側壁マスクを形成した後、前記芯材を除去する工程と、前記芯材を除去した後、前記第1の領域の前記マスク材に前記側壁マスクのパターンを転写する工程と、

前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とを同時に行う工程と、を含み、

前記芯材のパターン形成は、クリティカルデザインレベルのフォトマスクを用いたフォトリソグラフィ技術を用いて行われ、

前記第1の領域の前記マスク材への前記側壁マスクのパターンの転写は、ノンクリティカルデザインレベルのフォトマスクを用いたフォトリソグラフィ技術を用いて前記第2の領域の前記マスク材上に前記所定のパターンよりも大きいパターンを有するレジスト膜を形成した後、前記レジスト膜をマスクとして用いたエッチングにより行われ、

前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とは、クリティカルデザインレベルのフォトマスクを用いたフォトリソグラフィ技術を用いて行われる半導体装置の製造方法。

## 【請求項 2】

前記第1の領域での前記マスク材のトリミングでは、リング状パターンをトリミングしてラインアンドスペースパターンに加工する請求項1に記載の半導体装置の製造方法。

## 【請求項 3】

前記第1の領域のトリミングされた前記マスク材のパターンと、前記第2の領域の前記マスク材の前記所定のパターンとを前記半導体基板に同時に転写し、前記第1の領域にS R A Mに用いられるフィン、前記第2の領域に周辺回路の形成される活性領域を形成する工程、

をさらに含む請求項1または2に記載の半導体装置の製造方法。

## 【発明の詳細な説明】

10

## 【技術分野】

## 【0001】

本発明は、半導体装置の製造方法およびフォトマスクに関する。

## 【背景技術】

## 【0002】

従来、芯材と呼ばれるダミーパターンの側面に側壁を形成し、芯材を除去した後に側壁を下層の被加工材のエッチングマスクとして用いて微細パターンを半導体基板上に加工する技術が知られている。この側壁からなるマスクの幅は、側壁形状に加工する前の側壁マスクの材料膜の厚さや加工時のエッチング時間により決定されるため、比較的精度の高い寸法制御が可能である。この方法は、従来広く用いられているレジスト塗布と光露光の組み合わせによるエッチングマスクの形成方法よりも、マスクの寸法のばらつきを少なくすることができる（例えば、非特許文献1参照）。

20

## 【0003】

しかし、側壁マスクはその形成方法上、芯材の周辺を囲うようなリング状のパターンとなってしまうため、被加工材にラインアンドスペースと呼ばれる直線状パターンを形成するためのマスクとして用いるためには、パターンカットマスク、もしくはトリミングマスクと呼ばれるマスクを用いて再度リソグラフィ工程とエッチング工程を課すことにより、側壁マスクをトリミングしてラインアンドスペースのパターンに加工する必要がある。

## 【0004】

特に、ラインアンドスペースのパターンを応用して、FinFETで構成されるS R A Mセルのフィンを形成する場合には、芯材形成用のパターンング用フォトマスクおよび側壁マスクのトリミング用フォトマスクとして、極微細なパターンを有するクリティカルデザインレベルのマスクが用いられなければならない。そのためにマスクのコストを含む全體の製造コストが高くなり、また、これらのフォトマスクを用いたフォトリソグラフィ工程も、リソグラフィとしては難度の高い、そしてコストも高い手法（液浸リソグラフィなど）を用いなければならない。

30

## 【先行技術文献】

## 【非特許文献】

## 【0005】

【非特許文献1】A. Kaneko et al., IEDM Tech. Dig. pp. 863-866, 2005.

40

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明の目的は、極微細なパターンを有するS R A M領域のフィンと周辺回路領域の活性領域とを低コストかつ正確なデザインで形成することのできる半導体装置の製造方法、およびその製造方法に用いられるフォトマスクを提供することにある。

## 【課題を解決するための手段】

## 【0007】

本発明の一態様は、第1および第2の領域を有する半導体基板上にマスク材を形成する工程と、前記第1の領域の前記マスク材上に芯材をパターン形成する工程と、前記芯材の

50

両側面に側壁マスクを形成した後、前記芯材を除去する工程と、前記芯材を除去した後、前記第1の領域の前記マスク材に前記側壁マスクのパターンを転写する工程と、前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とを同時に行う工程と、を含む半導体装置の製造方法を提供する。

#### 【0008】

本発明の他の態様は、半導体基板上に、リング状パターンが形成された領域とパターンのない領域とを有するマスク材を形成する工程と、被加工材のリング状パターンをトリミングしてラインアンドスペースパターンに加工するためのパターンと、前記被加工材のパターンのない領域にパターンを形成するためのパターンと、を有するフォトマスクを用いたフォトリソグラフィ技術を用いて、前記マスク材の前記リングパターンのラインアンドスペースパターンへの加工と、前記マスク材の前記パターンのない領域への所定のパターンの形成を同時に行う工程と、前記マスク材の前記ラインアンドスペースパターンおよび前記所定のパターンを前記半導体基板に転写する工程と、を含む半導体装置の製造方法を提供する。

10

#### 【0009】

本発明の他の態様は、被加工材のリング状パターンをトリミングしてラインアンドスペースパターンに加工するためのパターンと、前記被加工材のパターンのない領域にパターンを形成するためのパターンと、を有するフォトマスクを提供する。

#### 【発明の効果】

20

#### 【0010】

本発明によれば、極微細なパターンを有するS R A M領域のフィンと周辺回路領域の活性領域とを低コストかつ正確なデザインで形成することのできる半導体装置の製造方法、およびその製造方法に用いられるフォトマスクを提供することができる。

#### 【図面の簡単な説明】

#### 【0011】

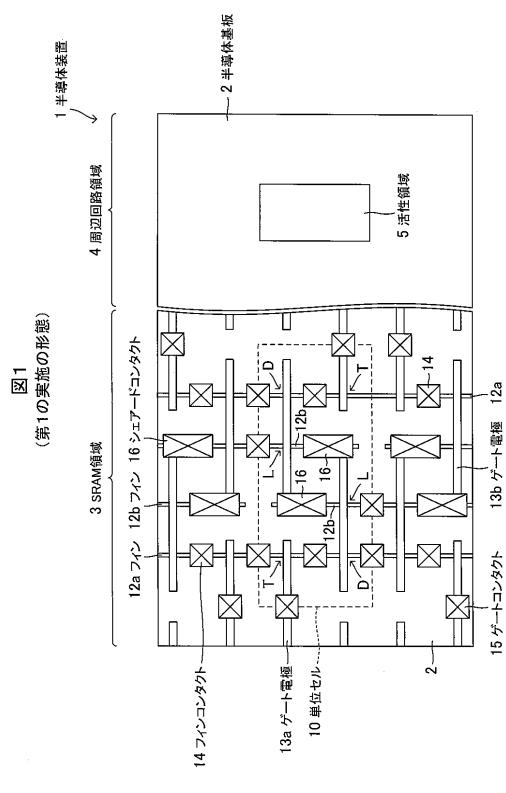

【図1】本発明の実施の形態に係る半導体装置1の上面図。

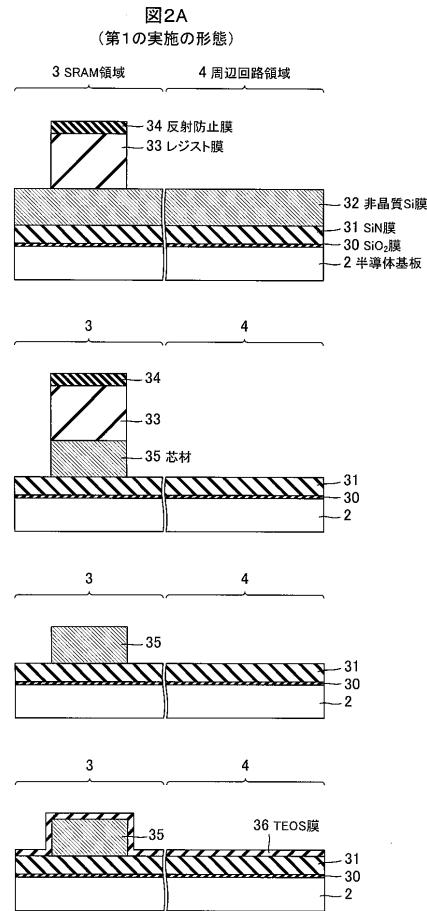

【図2A】(a)～(d)は、本発明の実施の形態に係る半導体装置の製造工程を示すフィンの長さ方向に垂直な方向の断面図。

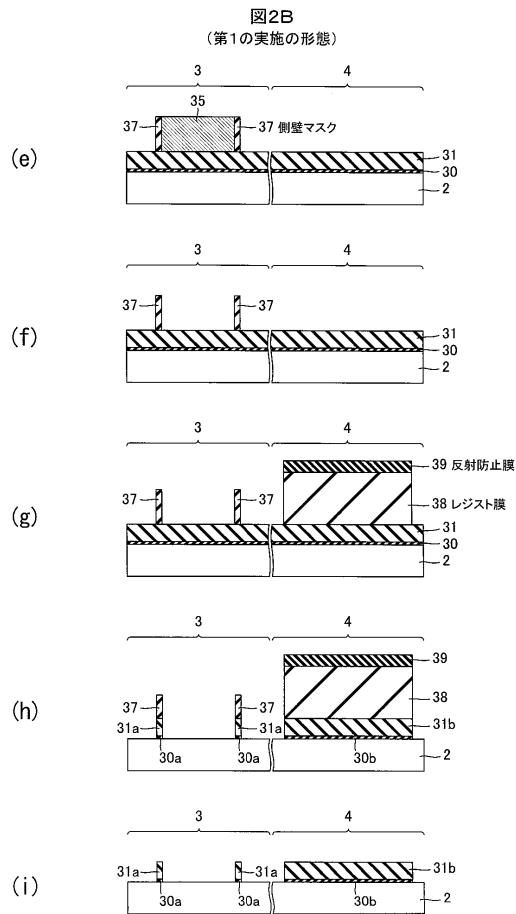

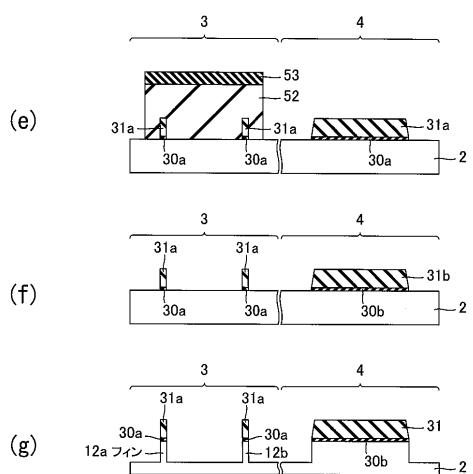

【図2B】(e)～(i)は、本発明の実施の形態に係る半導体装置の製造工程を示すフィンの長さ方向に垂直な方向の断面図。

30

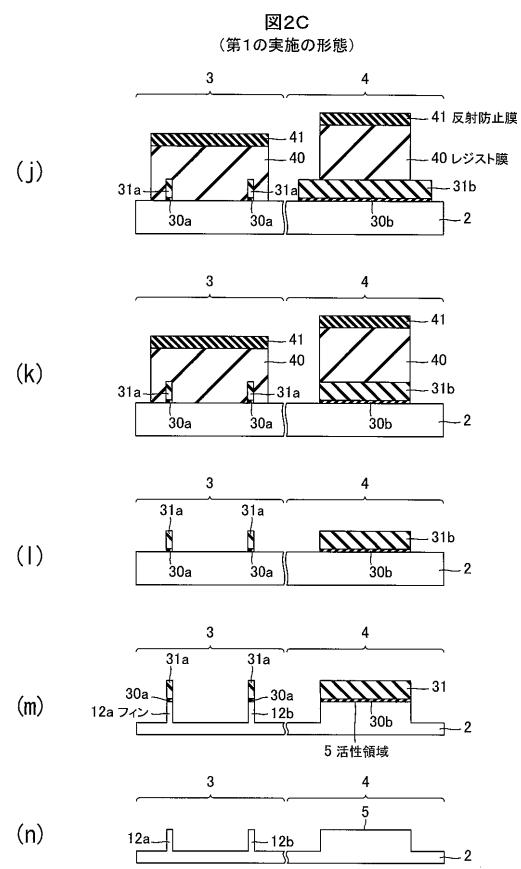

【図2C】(j)～(n)は、本発明の実施の形態に係る半導体装置の製造工程を示すフィンの長さ方向に垂直な方向の断面図。

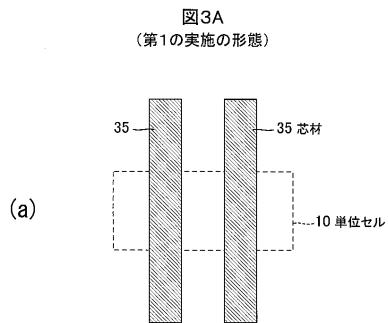

【図3A】(a)～(c)は、本発明の実施の形態に係る半導体装置のS R A M領域の製造工程を示す上面図。

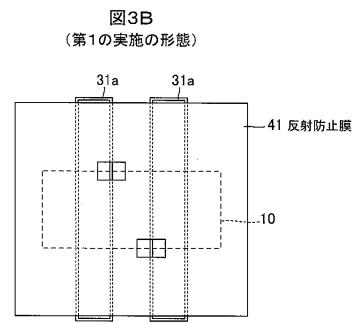

【図3B】(d)～(f)は、本発明の実施の形態に係る半導体装置のS R A M領域の製造工程を示す上面図。

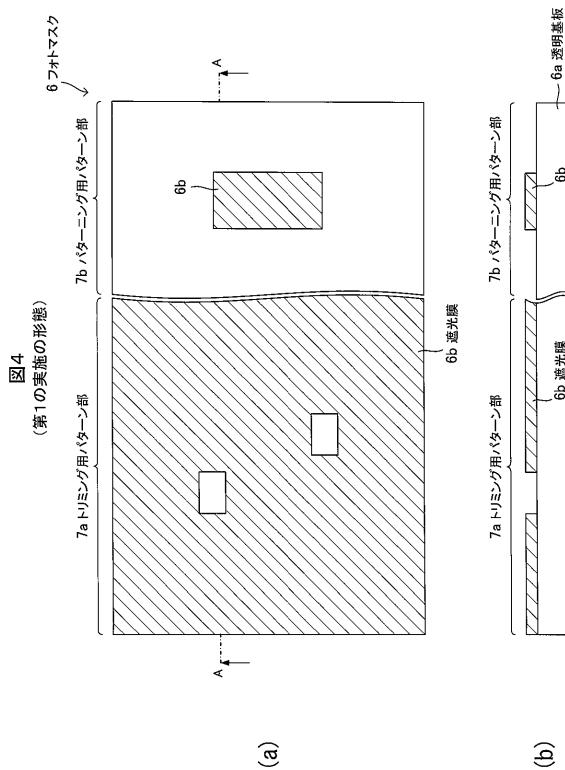

【図4】(a)、(b)は、本発明の実施の形態に係るフォトマスクの上面図および断面図。

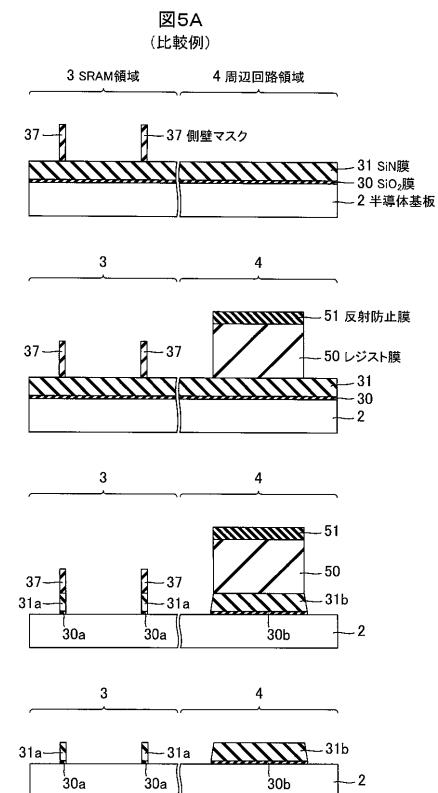

【図5A】(a)～(d)は、比較例としての従来の一般的な方法による半導体装置の製造方法を示す断面図。

40

【図5B】(e)～(g)は、比較例としての従来の一般的な方法による半導体装置の製造方法を示す断面図。

#### 【発明を実施するための形態】

#### 【0012】

#### 〔実施の形態〕

#### (半導体装置の構成)

図1は、本発明の実施の形態に係る半導体装置1の上面図である。半導体装置1は、S R A M(Static Random Access Memory)が形成されるS R A M領域3と、活性領域5にフリップフロップやセンサアンプ等の周辺回路(図示しない)が形成される周辺回路領域

50

4とを半導体基板2上に有する。

【0013】

S R A M領域3には、S R A Mが形成される。なお、本実施の形態においては、一例として、フィン型トランジスタから構成される6トランジスタ型のS R A Mについて説明する。6トランジスタ型のS R A Mは、1つの単位セル10にn型のトランスマニアトランジスタ、n型のドライバトランジスタ、p型のロードトランジスタをそれぞれ2つずつ有する。

【0014】

S R A M領域3には、n型のトランスマニアトランジスタT、n型のドライバトランジスタD、およびp型のロードトランジスタLの3種類のトランジスタと、トランスマニアトランジスタTとドライバトランジスタDのソース・ドレイン領域(図示しない)を含むフィン12aと、ロードトランジスタLのソース・ドレイン領域(図示しない)を含むフィン12bと、トランスマニアトランジスタTに用いられるゲート電極13a、ドライバトランジスタDとロードトランジスタLに共通に用いられるゲート電極13bが形成される。

10

【0015】

半導体基板2には、S i基板、S i G e基板、もしくは部分選択エピタキシャル成長法等によりこれらを組み合わせた基板等を用いることができる。

【0016】

フィン12a、12bは、例えば、半導体基板2の表面をエッチング加工することにより形成され、単結晶S i、単結晶S i G e等からなる。また、フィン12a、12bは、ゲート電極13aまたはゲート電極13bの両側に、ソース領域およびドレイン領域を含む。

20

【0017】

n型のトランスマニアトランジスタT、ドライバトランジスタDのソース・ドレイン領域にはA s、P等のn型不純物、p型のロードトランジスタLのソース・ドレイン領域にはB、B F<sub>2</sub>等のp型不純物が含まれる。

【0018】

また、フィン12a、12bの上面の所定の位置には、ソース領域またはドレイン領域に接続されるフィンコンタクト14が形成されている。フィンコンタクト14は、各部のソース領域またはドレイン領域と、上層の配線とを電気的に接続する。

30

【0019】

ゲート電極13aは、フィン12aの両側面にゲート絶縁膜を介して接触する。また、ゲート電極13bは、フィン12a、12bの両側面にゲート絶縁膜を介して接触する。フィン12a、12bのゲート電極13aまたはゲート電極13bがゲート絶縁膜を介して接触する領域は、チャネル領域として働く。

【0020】

ゲート電極13a、13bは、例えば、導電型不純物を含む多結晶シリコンまたは多結晶シリコンゲルマニウムからなる。ゲート電極13a、13bには、n型のトランスマニアトランジスタT、ドライバトランジスタDの領域にA s、P等のn型不純物、p型のロードトランジスタLの領域にB、B F<sub>2</sub>等のp型不純物が含まれる。

40

【0021】

なお、ゲート電極13a、13bの表面にシリサイド層が形成されていてもよい。また、ゲート電極13a、13bは、全体がシリサイド化したフルシリサイド電極であってもよい。また、ゲート電極13a、13bは、W、T a、T i、H f、Z r、R u、P t、I r、M o、A l、N i等やこれらの化合物等からなるメタルゲート電極であってもよい。また、メタルゲート電極部と多結晶S i電極部の積層構造を有してもよい。また、ゲート電極13a、13bの側面には、絶縁材料からなるゲート側壁が形成されていてもよい。

【0022】

また、ゲート電極13aの上面の所定の位置には、ゲートコンタクト15が形成されて

50

いる。ゲートコンタクト 15 は、ゲート電極 13a と上層の配線とを電気的に接続する。また、ゲート電極 13b およびフィン 12b の上面には、これらに共用されるコンタクトであるシェアードコンタクト 16 が形成される。シェアードコンタクト 16 は、ゲート電極 13b およびフィン 12b と、上層の配線とを電気的に接続する。

【0023】

フィン 12b は、単位セル 10 のシェアードコンタクト 16 側の境界上で分断される。

【0024】

(半導体装置の製造)

図 2A (a) ~ (d)、図 2B (e) ~ (i)、図 2C (j) ~ (n) は、本発明の実施の形態に係る半導体装置の製造工程を示すフィンの長さ方向に垂直な方向の断面図である。また、図 3A (a) ~ (c)、図 3B (d) ~ (f) は、半導体装置 1 の S R A M 領域 3 の製造工程を示す上面図である。ここで、図 3A (a) は図 2A (c)、図 3A (b) は図 2B (e)、図 3A (c) は図 2B (g)、図 3B (d) は図 2C (j)、図 3B (e) は図 2C (l) に対応する。

10

【0025】

まず、図 2A (a) に示すように、半導体基板 2 上の S R A M 領域 3 および周辺回路領域 4 に、SiO<sub>2</sub> 膜 30、SiN 膜 31、非晶質 Si 膜 32、レジスト膜 33、および反射防止膜 34 を積層した後、レジスト膜 33 および反射防止膜 34 に後述する芯材 35 のパターンを形成する。

20

【0026】

SiO<sub>2</sub> 膜 30、SiN 膜 31、非晶質 Si 膜 32、レジスト膜 33、および反射防止膜 34 は、C V D (Chemical Vapor Deposition) 法等により成膜される。また、レジスト膜 33 および反射防止膜 34 は、液浸リソグラフィ法等のフォトリソグラフィ法および R I E (Reactive Ion Etching) 法等のエッチング法の組み合わせによりパターニングされる。

【0027】

芯材 35 のパターンは、極微細なパターンである。そのため、レジスト膜 33 および反射防止膜 34 のパターニングには、極微細なクリティカルデザインレベルと呼ばれるデザインレベルのフォトマスクが用いられる。

30

【0028】

一般的に、クリティカルデザインレベルのフォトマスクは、あまり微細でないデザインレベル（以下、ノンクリティカルデザインレベルと記す）のフォトマスクよりも製造コストが高く、フォトマスクを用いたフォトリソグラフィ工程自体に費やされる費用も高い。

【0029】

次に、図 2A (b) に示すように、レジスト膜 33 および反射防止膜 34 をマスクとして非晶質 Si 膜 32 にエッチングを施し、非晶質 Si 膜 32 を芯材 35 に加工する。

【0030】

次に、図 2A (c) および図 3A (a) に示すように、レジスト膜 33 および反射防止膜 34 をエッチングにより除去する。

40

【0031】

次に、図 2A (d) に示すように、C V D 法等により、芯材 35 の上面および側面をコソフォーマルに覆うように T E O S 膜 36 を形成する。

【0032】

次に、図 2B (e) および図 3A (b) に示すように、R I E 法等により、T E O S 膜 36 を芯材 35 の側面に位置する部分を残して除去し、側壁マスク 37 を形成する。この段階では、側壁マスク 37 はリング状のパターンを有する。

【0033】

次に、図 2B (f) に示すように、ウェットエッチング等により芯材 35 を除去する。

【0034】

次に、図 2B (g) および図 3A (c) に示すように、SiN 膜 31 上にレジスト膜 3

50

8 および反射防止膜 3 9 を積層した後、これらを周回路領域 4 に選択的に残すようにパターニングする。レジスト膜 3 8 および反射防止膜 3 9 は、ノンクリティカルデザインレベルのフォトマスクを用いたフォトリソグラフィ法および RIE 法等のエッチング法により、後の工程で形成する活性領域 5 よりも大きなパターンに形成される。

【0035】

次に、図 2B (h) に示すように、側壁マスク 3 7、レジスト膜 3 8 および反射防止膜 3 9 をマスクとして SiO<sub>2</sub> 膜 3 0 および SiN 膜 3 1 にエッチングを施す。

【0036】

ここで、SiO<sub>2</sub> 膜 3 0 および SiN 膜 3 1 の SRAM 領域 3 において、側壁マスク 3 7 のパターンを転写された部分をそれぞれ SiO<sub>2</sub> 膜 3 0 a および SiN 膜 3 1 a、周回路領域 4 においてレジスト膜 3 8 および反射防止膜 3 9 のパターンを転写された部分を SiO<sub>2</sub> 膜 3 0 b および SiN 膜 3 1 b とする。

10

【0037】

次に、図 2B (i) に示すように、エッチングにより側壁マスク 3 7、レジスト膜 3 8 および反射防止膜 3 9 を除去する。

【0038】

次に、図 2C (j) および図 3B (d) に示すように、半導体基板 2 上の全面にレジスト膜 4 0 および反射防止膜 4 1 を積層した後、これらをパターニングする。

【0039】

レジスト膜 4 0 および反射防止膜 4 1 は、クリティカルデザインレベルのフォトマスクを用いた液浸リソグラフィ法等のフォトリソグラフィ法によりパターニングされ、SRAM 領域 3 においては SiN 膜 3 1 a に形成されたパターンをトリミングするためのパターン、周回路領域 4 においては活性領域 5 のパターンが形成される。ここで、SiN 膜 3 1 a に形成されたパターンのトリミングとは、SiN 膜 3 1 a の長方形のリング状のパターンの長手方向の端部を除去してフィン 12 a、12 b のパターンに分けることと、フィン 12 b のパターンを単位セル 10 のシェアードコンタクト 16 側の境界上で分断することをいう。

20

【0040】

図 4 (a) は、このフォトリソグラフィ工程で用いられるフォトマスク 6 の上面図である。また、図 4 (b) は、図 4 (a) に示される切断面 A - A におけるフォトマスク 6 の断面図である。

30

【0041】

フォトマスク 6 は、透明基板 6 a および透明基板 6 a 上のパターン形成された遮光膜 6 b を有する。遮光膜 6 b に形成されたパターンは、フィン 12 b のパターンをトリミングするための開口パターンを含むトリミング用パターン部 7 a、および活性領域 5 のパターンを形成するためのパターンを含むパターニング用パターン部 7 b を含む。なお、遮光膜 6 b は、光を完全には遮らない、半透明な材料から形成されてもよい。

【0042】

次に、図 2C (k) に示すように、レジスト膜 4 0 および反射防止膜 4 1 をマスクとして SiO<sub>2</sub> 膜 3 0 b および SiN 膜 3 1 b にエッチングを施し、SiN 膜 3 1 a のパターンをトリミングと、SiN 膜 3 1 b への活性領域 5 のパターンの転写とを同時に行う。

40

【0043】

次に、図 2C (l) および図 3B (e) に示すように、エッチングによりレジスト膜 4 0 および反射防止膜 4 1 を除去する。なお、レジスト膜 4 0 および反射防止膜 4 1 を除去した後、必要に応じて、フィン 12 a、12 b のパターンが形成された SiN 膜 3 1 a の幅を細める工程を行ってもよい。

【0044】

次に、図 2C (m) に示すように、SiO<sub>2</sub> 膜 3 0 a、3 0 b および SiN 膜 3 1 a、3 1 b をマスクとして用いて半導体基板 2 にエッチングを施し、フィン 12 a、12 b および活性領域 5 を形成する。

50

## 【0045】

次に、図2C(n)に示すように、エッティングによりSiO<sub>2</sub>膜30a、30bおよびSiN膜31a、31bを除去する。

## 【0046】

次に、図3B(f)に示すように、ゲート電極13a、13b、フィンコンタクト14、ゲートコンタクト15、およびシェアードコンタクト16を形成する。また、図示しないが、活性領域5にフリップフロップやセンサアンプ等の周辺回路を形成する。

## 【0047】

## (比較例)

図5A(a)～(d)、図5B(e)～(g)は、比較例としての従来の一般的な方法による半導体装置の製造方法を示す断面図である。この比較例は、活性領域5をパターン形成するためのマスク材パターンの形成、およびSiN膜31aに形成されたパターンをトリミングするためのマスク材パターンの形成を別工程で行う点において、実施の形態と異なる。なお、この比較例において形成する半導体装置は、本実施の形態の半導体装置1と同様の構成を有するものとする。

## 【0048】

まず、図5A(a)に示すように、図2A(a)～図2B(f)に示した芯材4を除去するまでの工程を実施の形態と同様に行う。

## 【0049】

次に、図5A(b)に示すように、SiN膜31上にレジスト膜50および反射防止膜51を積層した後、これらを周辺回路領域4に選択的に残すようにパターニングする。ここで、レジスト膜50および反射防止膜51には、クリティカルデザインレベルのフォトマスクを用いた液浸リソグラフィ法等のフォトリソグラフィ法およびRIE法等のエッティング法により、活性領域5のパターンが形成される。

## 【0050】

次に、図5A(c)に示すように、側壁マスク37、レジスト膜38および反射防止膜39をマスクとしてSiO<sub>2</sub>膜30およびSiN膜31にエッティングを施す。

## 【0051】

ここで、SiO<sub>2</sub>膜30およびSiN膜31のSRAM領域3において側壁マスク37のパターンを転写された部分をそれぞれSiO<sub>2</sub>膜30aおよびSiN膜31a、周辺回路領域4においてレジスト膜38および反射防止膜39のパターンを転写された部分をSiO<sub>2</sub>膜30bおよびSiN膜31bとする。

## 【0052】

次に、図5A(d)に示すように、エッティングによりレジスト膜50および反射防止膜51を除去する。

## 【0053】

次に、図5B(e)に示すように、半導体基板2上の全面にレジスト膜52および反射防止膜53を積層した後、これらにSiN膜31aに形成されたパターンをトリミングするためのパターンを形成する。ここで、レジスト膜52および反射防止膜53は、クリティカルデザインレベルのフォトマスクを用いたフォトリソグラフィ法およびRIE法等のエッティング法によりパターニングされる。

## 【0054】

次に、図5B(f)に示すように、エッティングによりレジスト膜52および反射防止膜53を除去する。

## 【0055】

次に、図5B(g)に示すように、SiO<sub>2</sub>膜30a、30bおよびSiN膜31a、31bをマスクとして用いて半導体基板2にエッティングを施し、フィン12a、12bおよび活性領域5を形成する。なお、その後の工程は実施の形態と同様である。

## 【0056】

## (実施の形態の効果)

10

20

30

40

50

上述した比較例においては、実施の形態と異なり、Fin 12a、12b のパターンと活性領域 5 のパターンとを SiO<sub>2</sub> 膜 30 および SiN 膜 31 に同時にパターニングする。このとき、図 5A (c) に示すように、SiN 膜 31b の側面は垂直に加工されず、テープー形状となるおそれがある。

#### 【0057】

これは、大きさの異なる Fin 12a、12b のパターンと活性領域 5 のパターンとでは、寸法変換差（フォトマスク上のパターンと、実際に被加工材に形成されるパターンの寸法差）が異なるためである。この場合、活性領域 5 の大きさがフォトマスクのパターンの大きさと異なってしまう。なお、SiN 膜 31b の側面を垂直に形成しようとすると、SiN 膜 31a の側面が垂直にならず、逆テープー形状となるおそれがある。

10

#### 【0058】

一方、本実施の形態においては、Fin 12a、12b のパターンと活性領域 5 のパターンとを別工程で SiO<sub>2</sub> 膜 30 および SiN 膜 31 に形成するため、それぞれのパターンの寸法変換差に基づいて、エッチング時にそれぞれ適したエッチング条件の補正を行うことができる。その結果、SiN 膜 31a、31b の側面を垂直に加工し、Fin 12a、12b および活性領域 5 の正確なパターンを形成することができる。

#### 【0059】

また、比較例においては、芯材 35 のパターンを形成する工程、レジスト膜 50 および反射防止膜 51 に活性領域 5 のパターンを形成する工程、およびレジスト膜 52 および反射防止膜 53 に SiN 膜 31a に形成されたパターンをトリミングするためのパターンを形成する工程の合計 3 工程でクリティカルデザインレベルのフォトマスクが用いられる。

20

#### 【0060】

一方、実施の形態においては、芯材 35 のパターンを形成する工程、およびレジスト膜 40 および反射防止膜 41 に SiN 膜 31a に形成されたパターンをトリミングするためのパターンと活性領域 5 のパターンとを形成する工程の 2 工程のみでクリティカルデザインレベルのフォトマスクが用いられる。

#### 【0061】

すなわち、実施の形態では、比較例よりもクリティカルデザインレベルのフォトマスクが用いられる回数が少ないため、フォトマスクの製造コストや、半導体装置 1 のトータルの製造コストを低減することができる。

30

#### 【0062】

##### 【他の実施の形態】

本発明は、上記実施の形態に限定されず、発明の主旨を逸脱しない範囲内において種々変形実施が可能である。例えば、SiO<sub>2</sub> 膜 30、SiN 膜 31、非晶質 Si 膜 32 または TEOS 膜 36 の代わりに異なる材料からなる膜を用いてもよい。また、SiO<sub>2</sub> 膜 30 に相当する膜は用いなくてもよい。

#### 【0063】

また、上記実施の形態においては、微細なラインアンドスペースパターンおよびその周辺の微細なパターンを持つ部材として、SRAM に用いられる Fin および周辺回路領域の活性領域を例として説明したが、実際にはこれに限られるものではなく、上記実施の形態に示した半導体装置の製造方法を同様のパターンを有する部材の製造に適用することができる。

40

#### 【符号の説明】

#### 【0064】

1 半導体装置、2 半導体基板、3 SRAM 領域、4 周辺回路領域、5 活性領域、6 フォトマスク、7a トリミング用パターン部、7b パターニング用パターン部、12a、12b Fin、30、30a、30b SiO<sub>2</sub> 膜、31、31a、31b SiN 膜、35 芯材、37 側壁マスク

【図1】

図1

(第1の実施の形態)

【図2A】

図2A

(第1の実施の形態)

【図2B】

図2B

(第1の実施の形態)

【図2C】

図2C

(第1の実施の形態)

【図3A】

【図4】

### 【図3B】

【図5A】

## 【図 5 B】

図5B

(比較例)

---

フロントページの続き

(74)代理人 100137523

弁理士 出口 智也

(74)代理人 100124372

弁理士 山ノ井 傑

(74)代理人 100146123

弁理士 木本 大介

(74)代理人 100144967

弁理士 重野 隆之

(72)発明者 稲葉 聰

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 石坂 博明

(56)参考文献 特開2008-258360 (JP, A)

特開平07-193198 (JP, A)

特開2007-227454 (JP, A)

特表2008-535247 (JP, A)

特開2009-302546 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21/8229、21/8242-21/8247

27/10-27/115、27/28

51/05