(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-85891

(P2004-85891A)

(43) 公開日 平成16年3月18日(2004.3.18)

(51) Int.CI.<sup>7</sup>**G09G 3/36****G02F 1/133****G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 611F

G09G 3/20 612R

G09G 3/20 621A

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 8 O L (全 33 頁) 最終頁に続く

(21) 出願番号

特願2002-246781 (P2002-246781)

(22) 出願日

平成14年8月27日 (2002.8.27)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100080034

弁理士 原 謙三

(74) 代理人 100113701

弁理士 木島 隆一

(74) 代理人 100115026

弁理士 園谷 徹

(74) 代理人 100116241

弁理士 金子 一郎

(72) 発明者 森井 秀樹

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】表示装置および表示駆動回路の制御装置ならびに表示装置の駆動方法

## (57) 【要約】

【課題】最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことが可能な表示装置を提供する。

【解決手段】タイミングコントロールASICは、表示データがソースドライバから出力開始されるまでに存在する期間を利用し、データタイネーブル信号ENABの入力タイミングを基準にしてゲートスタートパルス信号GSPおよびゲートクロック信号GCKの1パルス目CK1を生成する。これらをゲートドライバに入力し、ダミーラインを駆動する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、

上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、

表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、

上記表示データとデータタイマーブル信号とクロック信号とが入力され、上記データタイマーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイマーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、

上記制御装置は、上記データタイマーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイマーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴とする表示装置。

**【請求項 2】**

上記列駆動タイミング信号は、上記行駆動信号を上記行ラインのそれぞれに順次出力するタイミングを決めるように上記行駆動回路内でシフトされる1パルスからなるスタートパルス信号と、上記スタートパルス信号をシフトさせるタイミングを決めるシフトクロック信号とを含んでおり、

上記制御装置は、上記データタイマーブル信号の入力タイミングで上記スタートパルス信号を生成開始し、上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように上記行駆動回路が上記スタートパルス信号を取り込むための上記シフトクロック信号の1クロック目を、上記入力タイミングから上記クロック信号のクロックを所定数カウントした時点で生成することを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

上記制御装置は、1水平期間の上記表示データを上記列駆動回路に入力完了した後の水平帰線期間分の経過期間内に、上記列駆動回路が上記列駆動信号を出力するタイミングを決める上記列駆動用タイミング信号である列駆動開始タイミング信号を上記列駆動回路に入力し、上記シフトクロック信号の上記1クロック目より後のクロックを上記列駆動開始タイミング信号に合わせて上記行駆動回路に入力することを特徴とする請求項2に記載の表示装置。

**【請求項 4】**

上記制御装置は、入力される上記表示データを1水平期間遅延させて上記列駆動回路に入力することを特徴とする請求項1に記載の表示装置。

**【請求項 5】**

表示に有効な上記画素に接続された上記行ラインは1050本であり、上記行駆動回路は263個の上記行駆動信号の出力端子を備えたドライバICが4個カスケード接続されたものであることを特徴とする請求項1ないし4のいずれかに記載の表示装置。

**【請求項 6】**

画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、

上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、

10

20

30

40

50

表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、

上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、

上記行駆動回路はドライバICがシステム・オン・フィルム構造により実装されたものであり、所定のドライバICにおける最終の上記行ラインに対応する上記行駆動信号の出力端子の次に設けられた出力端子から、ICチップの下方を通るように配線が引き回され、上記配線が上記表示パネルに設けられた最上段の上記行ラインよりもさらに上段にダミーの行ラインとして延設されていることを特徴とする表示装置。10

#### 【請求項 7】

画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、

表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路とを備える表示駆動回路を制御する、表示駆動回路の制御装置であって、20

上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力し、

上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴とする表示駆動回路の制御装置。30

#### 【請求項 8】

画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、

上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、

表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、40

上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置を駆動する表示装置の駆動方法であって、

上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する表示装置の駆動方法において、

上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水50

平期間の上記表示データを出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴とする表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、マトリクス型の表示装置の駆動に関するものである。

【0002】

【従来の技術】

マトリクス型の表示装置として、TFT（薄膜トランジスタ：Thin Film Transistor）が形成されたアクティブマトリクス基板および上記TFTを駆動するためのドライバIC（Integrated Circuit）を備えた液晶表示装置が広く知られている。

【0003】

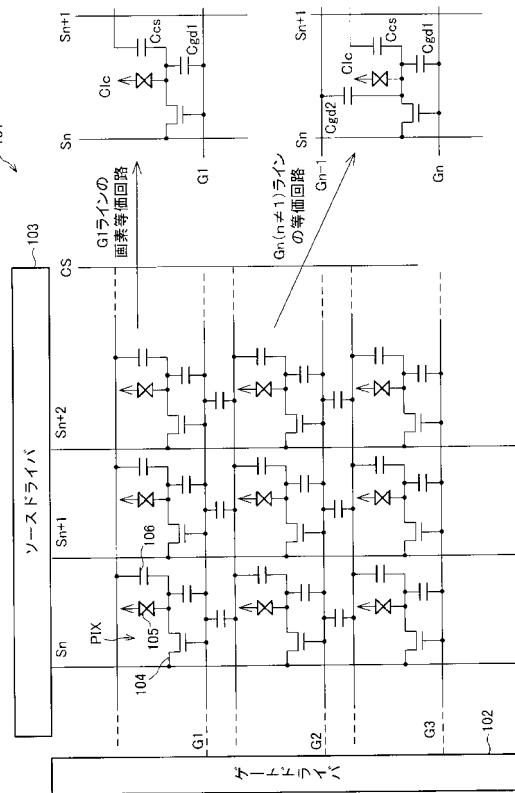

図18に、TFTアクティブマトリクス方式の液晶表示装置101の構成を示す。液晶表示装置101には、マトリクスの行駆動回路としてゲートドライバ102、列駆動回路としてソースドライバ103が設けられている。

【0004】

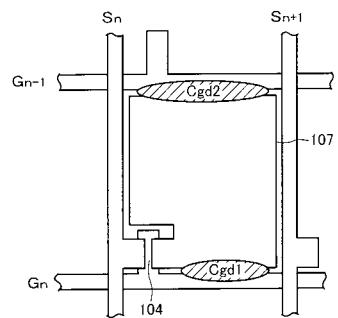

透明な基板上には、それぞれ複数本の、ゲートドライバ102によって駆動されるゲートライン $G_n \cdot G_{n+1} \cdot \dots$ （総称するときは、以下参照符Gで示す）と、ソースドライバ103によって駆動されるソースライン $S_n \cdot S_{n+1} \cdot \dots$ （総称するときは、以下参照符Sで示す）とが相互に直交するように形成されている。そして、これらの各ゲートラインGと各ソースラインSとが交差するそれぞれの箇所に画素PIXが形成されている。画素PIXは、TFT104、液晶105、補助容量106を備えている。また、ゲートラインGとソースラインSとによって区分された領域には、液晶105および補助容量106の一方の電極となる画素電極107（図19）が形成されており、この画素電極107はTFT104のドレイン電極に接続されている。第n行、第n列目の画素PIXでは、前記TFT104のソース電極は第n列目のソースライン $S_n$ に接続され、ゲート電極は第n行目のゲートライン $G_n$ に接続される。

【0005】

このように各画素PIXが形成される液晶表示装置101において、ゲートラインGと画素電極107との関係に着目すると、図18の液晶表示装置101は、第n行目のゲートライン $G_n$ が第n行目の画素電極107の下側に配置される、いわゆる下ゲート構造の液晶表示装置である。そして、前記画素電極107とゲートライン $G_n, G_{n-1}$ との間には、図19に示すようにそれぞれ寄生容量 $C_{gd1} \cdot C_{gd2}$ が形成されることになる。ここで、第1行目の画素について考えると、前記第n行目の画素におけるゲートライン $G_{n-1}$ に対応するゲートライン $G_0$ は形成されておらず、前記寄生容量 $C_{gd2}$ が形成されないことになる。図18に、第1行目（G1ライン）の画素と第2行目以降（ $G_n (n-1)$ ）の画素とにおいて、これらの寄生容量 $C_{gd1} \cdot C_{gd2}$ が形成されている場合の等価回路の相違を示す。

【0006】

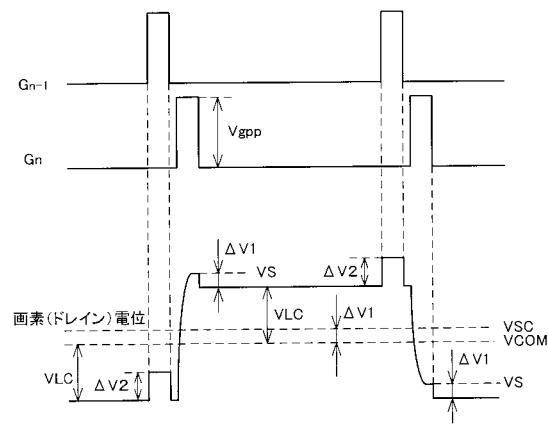

一方、図20に示すように、各ゲートラインGには振幅がV<sub>gpp</sub>のゲート信号が順次印加されるが、このゲート信号によってTFT104のドレインレベルが変動する。すなわち、第n行目の画素PIXにおいては、寄生容量 $C_{gd2}$ を介して、ゲートライン $G_{n-1}$ のゲート信号がTFT104のドレインレベルをV2だけ変動させ、寄生容量 $C_{gd1}$ を介して、ゲートライン $G_n$ のゲート信号がTFT104のドレインレベルをV1だけ変動させる。

【0007】

ここで、画素PIXの液晶の容量を $C_{lc}$ で示し、補助容量を $C_{cs}$ で示すとき、前記

10

20

30

40

50

V 2 , V 1 は、

$$V 1 = V g p p \times \{ C g d 1 / ( C l c + C c s + C g d 1 + C g d 2 ) \}$$

$$V 2 = V g p p \times \{ C g d 2 / ( C l c + C c s + C g d 1 + C g d 2 ) \}$$

と表すことができる。

【 0 0 0 8 】

そして、自段のゲートライン G n のゲート信号によって引起される V 1 は、TFT 104 のドレンインレベルの振幅の中心 V c o m を、ソース信号の振幅の中心 V s c から該 V 1 だけ低くするように作用し、前段のゲートライン G n - 1 のゲート信号によって引起される V 2 は、液晶 105 への印加電圧の実効値を増加させるように作用する。

【 0 0 0 9 】

第 1 行目の画素 P I X では、前述のように寄生容量 C g d 2 を形成する前段のゲートライン G 0 が存在しないので、前記 V 2 は発生せず、該第 1 行目の画素 P I X のみ、他の行に比べて液晶 105 への印加電圧の実効値が低くなる。この実効値の差が問題であり、該 V 2 が大きい場合や、高温または低温状態など、表示装置の駆動条件が悪化すると、該第 1 行目の画素 P I X のみ、他の画素 P I X に比べて表示の明るさが変わって見えるという問題が生じる。たとえば、ノーマリーホワイト液晶である場合には、該第 1 ラインは輝線化する。

【 0 0 1 0 】

そこで、上記課題を解決するために、たとえば特開平 9 - 288260 号公報および特開平 8 - 43793 号公報には、下ゲート構造のパネルに、第 1 行目の画素に近接して、有効表示領域外には、該第 1 行目の画素と残余の画素との上記のような非対称性を補償するためのダミーライン G 0 を形成することが記載されている。前記ゲートライン G 1 ~ G m は出力端子 O G 1 ~ O G m からのゲート信号でそれぞれ駆動されるとともに、増加したダミーライン G 0 は最終 m 行目のゲートライン G m と並列に接続されて同時に駆動される。以下、これを従来技術 1 とする。

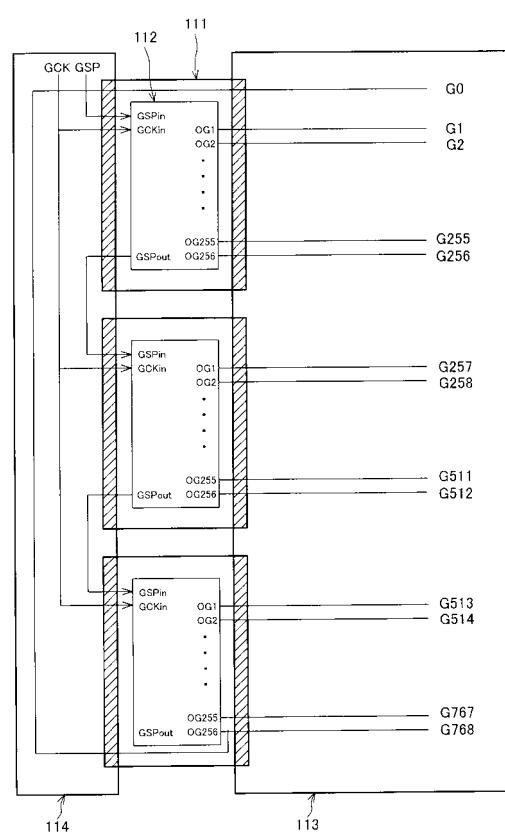

【 0 0 1 1 】

従来技術 1 によるゲートドライバ 102 の構成例を図 21 に示す。この場合のゲートドライバ 102 は TAB ( Tape Automated Bonding ) 方式によって T C P ( Tape Carrier Package ) 111 上に搭載されたドライバ I C 112 が複数個カスケード接続されたものである。ゲートドライバ 102 は、画素 P I X ... 、ゲートライン G ... 、およびソースライン S ... が形成された液晶パネル 113 とプリント基板 114 とを接続している。各ドライバ I C 112 は端子 O G 1 ~ O G 256 の 256 個の出力端子を有しており、同図はこれが 3 個接続された場合の構成を示している。

【 0 0 1 2 】

各ドライバ I C 112 においては、プリント基板 114 を介して端子 G S P i n にゲートスタートパルス信号 G S P が、また端子 G C K i n にゲートクロック信号 G C K が入力される。また、各ドライバ I C 112 は、内部のシフトレジスタでシフトさせたゲートスタートパルス信号 G S P を端子 G S P o u t から出力して、プリント基板 114 を介して次段のドライバ I C 112 の端子 G S P i n に入力される。そして、最終段のドライバ I C 112 の最終ラインの端子 O G 256 からは、ゲートライン G のみならず、プリント基板 114 を介して液晶パネル 113 の最上段まで配線が引き回されている。この最上段に引き回された配線がダミーライン G 0 である。このような構成により、ダミーライン G 0 およびゲートライン G 1 ~ G 768 が形成される。

【 0 0 1 3 】

図 21 のゲートドライバ 102 の信号のタイミングチャートを図 22 に示す。ゲートスタートパルス信号 G S P はゲートクロック信号 G C K のタイミングによってシフトされていき、シフトされる過程で順次端子 O G 1 、端子 O G 2 、... 、端子 O G 256 と、ゲートライン G にゲート信号が出力される。あるドライバ I C 112 の端子 O G 256 からゲート信号が出力されるときには、端子 G S P o u t からゲートスタートパルス信号 G S P が出力されて、次段のドライバ I C 112 の端子 G S P i n に入力される。

## 【0014】

しかし、この従来技術1では、最終mライン目のゲートラインGmを駆動する出力端子OGmのドライバ回路だけ負荷が約2倍になり、ゲート信号波形が鈍るという問題がある。また、図22でプリント基板114を介して配線したように、ダミーラインG0とゲートラインGmとを接続するバイパスラインが必要となり、液晶パネル113やフレキシブルのプリント基板の構造が複雑になるという問題もある。とりわけ、昨今では液晶表示装置の低コスト化・軽量化・薄型化のため、ゲート側のプリント基板やフレキシブルのプリント基板、コネクタなどをなくし、液晶パネル上およびゲートドライバTCP上にゲートドライバ側の電源・信号線を構成する構造（以下、ゲート基板省略構造と呼ぶ）が採用されるようになった。この構造では、ゲートドライバに入力する電源や信号の配線を、ソースドライバ側から一層構造の配線パターンによって形成しており、図21のように最終mライン目からダミーラインG0まで配線を引き回すスペースを確保することができないという問題を抱えている。10

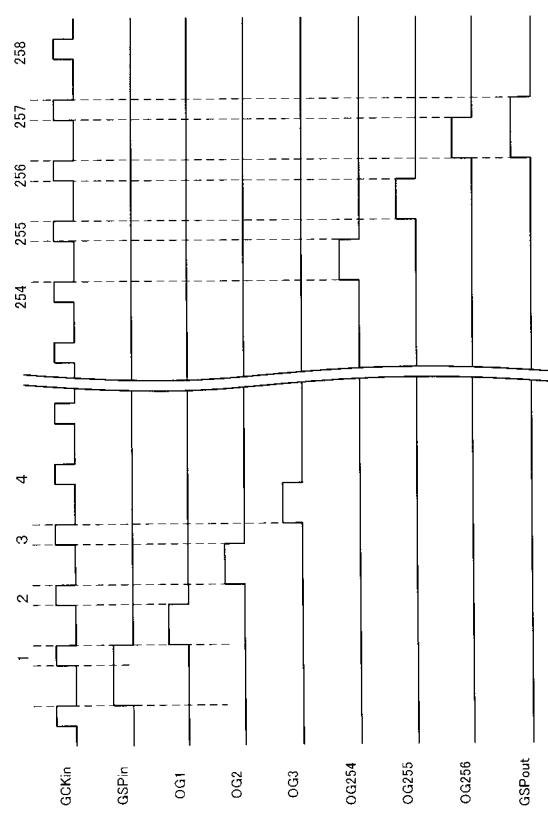

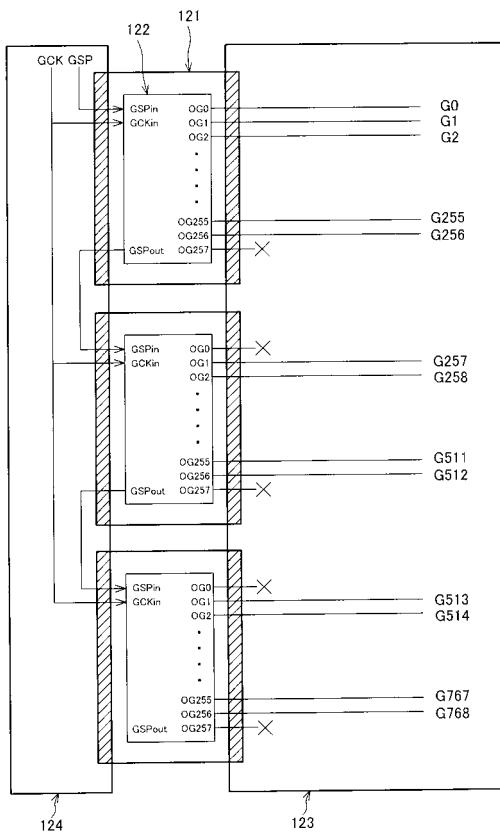

## 【0015】

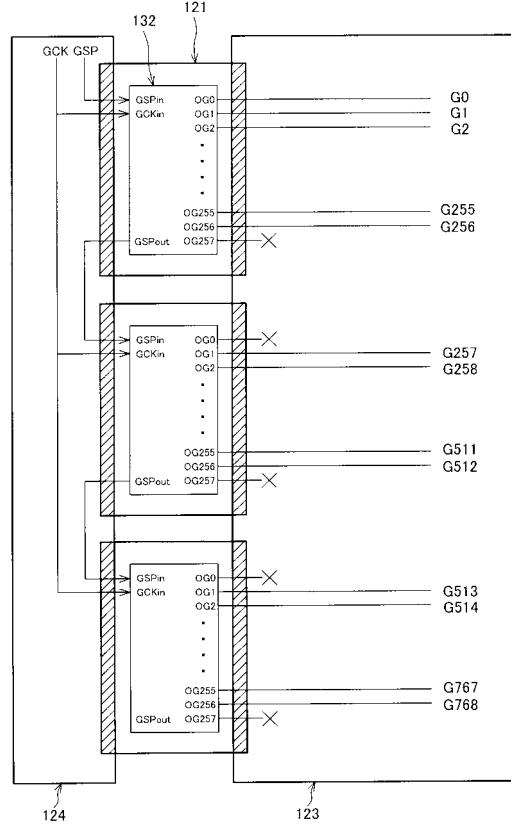

そこで、図23に示すように、前記ダミーラインG0を個別に駆動可能なように出力端子数を増加させたゲートドライバICが開発され、上記の問題を解決している。以下、これを従来技術2とする。図23の構成例では、各TCP121のドライバIC122は、図21のドライバIC112よりも多い端子OG0～OG257を備えている。各段のドライバIC122では端子OG1～OG256をそれぞれゲートラインGとする。そして、1段目のドライバIC122では端子OG0にダミーラインG0を接続する。2段目および3段目のドライバIC122では端子OG0・OG257を使用しない。ゲートスタートパルス信号GSPおよびゲートクロック信号GCKはプリント基板124を介して入力されるが、ダミーラインG0をドライバIC122の端子OG0から駆動するようにしたので、最終段のドライバIC122からプリント基板124を介して液晶パネル123の最上段にダミーラインG0用の配線を引き回す必要がない。20

## 【0016】

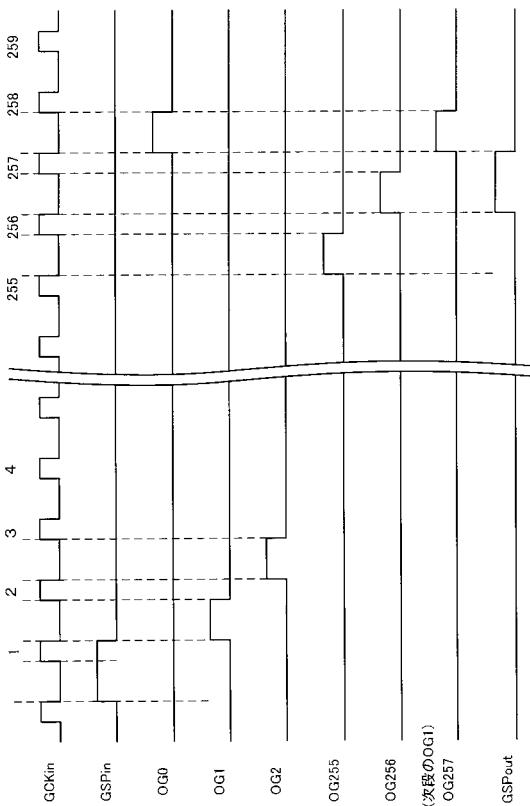

図23のゲートドライバ102の信号のタイミングチャートを図24に示す。最初に端子OG0にゲート信号が出力され、ゲートスタートパルス信号GSPが順次シフトされていく。端子OG256からゲート信号が出力された後にはゲートスタートパルス信号GSPは次段のドライバIC122に入力されて、そのドライバICの端子OG1からゲート信号が出力される。30

## 【0017】

この従来技術2を、図25に示すように、図24のようなプリント基板124を用いずにTCP121および液晶パネル123のみを介してドライバIC122への配線を形成するゲート基板省略構造に適用することもできる。この場合においても、ダミーラインG0用の配線の引き回しは必要ないため、この構造にてゲート基板省略構造の液晶表示装置が実現・量産されている。

## 【0018】

しかしながら、従来技術2の構造では、ダミーラインG0用の出力を駆動するためのゲートスタートパルス信号GSPを、ゲートドライバ102およびソースドライバ103の駆動を制御するための信号を生成するタイミングコントロールASICに、入力データ信号DATA-inおよびデータタイマーブル信号ENABが入力されるまでにゲートドライバ102に入力する必要がある。タイミングコントロールASICによる制御方法には、垂直同期信号および水平同期信号を利用したタイミング制御方式（以下、HVモードと呼ぶ）と、垂直同期信号および水平同期信号を利用せずデータタイマーブル信号ENABのみでタイミングを制御する方式（以下、V-ENABモードと呼ぶ）とがある。次に、HVモードとV-ENABモードについて、図26および図27を用いて説明する。40

## 【0019】

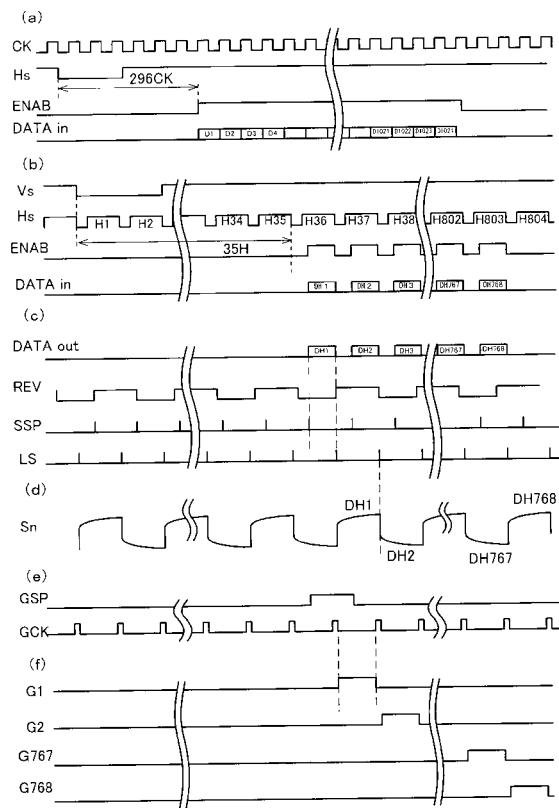

まずHVモードについて図26のタイミングチャートを用いて説明する。

## 【0020】

同図 (a) はタイミングコントロール A S I C に入力される水平駆動用の信号を示す。1 水平期間の信号のタイミングを示しており、クロック信号 C K の入力タイミングを用い、水平同期信号 H s の入力から 296 クロック目でデータタイネーブル信号 E N A B が立ち上がり、1 水平期間分のデータ D 1 · D 2 · ... · D 1 0 2 4 が入力される。また、同図 (b) はタイミングコントロール A S I C に入力される垂直駆動用の信号を示す。1 垂直期間の信号のタイミングを示しており、垂直同期信号 V s の入力から 35 水平期間分が経過するとデータタイネーブル信号 E N A B が立ち上がり、この立ち上がっている各水平期間に入力データ信号 D A T A i n の1 水平期間分のデータ D H 1 · D H 2 · ... · D H 7 6 8 が入力される。

## 【0021】

10

同図 (c) はタイミングコントロール A S I C が output する水平駆動用の信号を示す。ソースドライバ 103 に出力するデータ D H 1 · D H 2 · ... · D H 7 6 8 と、1 水平期間ごとに信号レベルを反転させるための液晶駆動極性反転信号 R E V と、ソースドライバ 103 内でシフトさせるソーススタートパルス信号 S S P と、ソーススタートパルス信号 S S P のシフトタイミングに基づいてサンプリングされた各データをラッチして各ソースライン S に出力するためのラッチストローブ信号 L S を、ソースドライバ 103 に出力する。これにより、ソースドライバ 103 の出力波形は同図 (d) のようになる。

## 【0022】

20

同図 (e) はタイミングコントロール A S I C が output する垂直駆動用の信号を示す。ゲートドライバ 102 によって選択される各行の画素にソースドライバ 103 から出力されたデータ D H 1 · D H 2 · ... · D H 7 6 8 が順次書き込まれるようにゲート信号を出力するためのゲートスタートパルス信号 G S P と、ゲートスタートパルス信号 G S P をシフトさせるためのゲートクロック信号 G C K を、ゲートドライバ 102 に出力する。これにより、ゲートドライバ 102 は、同図 (f) に示すように、ゲートライン G にパルスのゲート信号を順次出力する。

## 【0023】

30

このように、H V モードでは、垂直同期信号 V S の入力から、ある定められた期間を有する水平同期信号 H s を所定数カウントし、その後、データタイネーブル信号 E N A B および入力データ信号 D A T A i n が入力される。従って、H V モードの場合には入力された垂直同期信号 V a および水平同期信号 H s から、ゲートスタートパルス信号 G S P を、ゲートライン G 1 を駆動する前にダミーライン G 0 を駆動するようなタイミングで生成することが可能である。

## 【0024】

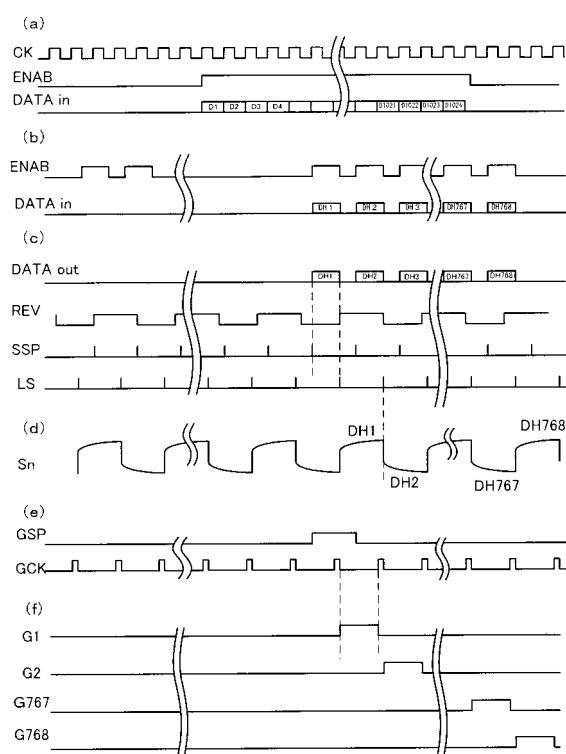

次に、V - E N A B モードについて図 27 のタイミングチャートを用いて説明する。

## 【0025】

30

同図 (a) は、タイミングコントロール A S I C に入力される水平駆動用の信号を示す。1 水平期間の信号のタイミングを示しており、水平同期信号は存在せず、クロック信号 C K が入力されている状態においてあるタイミングでデータタイネーブル信号 E N A B が入力され、1 水平期間分のデータ D 1 · D 2 · ... · D 1 0 2 4 が入力される。また、同図 (b) はタイミングコントロール A S I C に入力される垂直駆動用の信号を示す。垂直同期信号および水平同期信号は存在せず、あるタイミングで入力されるデータタイネーブル信号 E N A B の期間が各水平期間のデータ D H 1 · D H 2 · ... · D H 7 6 8 をソースドライバ 103 がサンプリングすべき期間に相当する。

40

## 【0026】

同図 (c) ~ (f) は図 26 と同様であるが、タイミングコントロール A S I C が output する信号のタイミングはデータタイネーブル信号 E N A B の入力タイミングを基準にして決定される。

## 【0027】

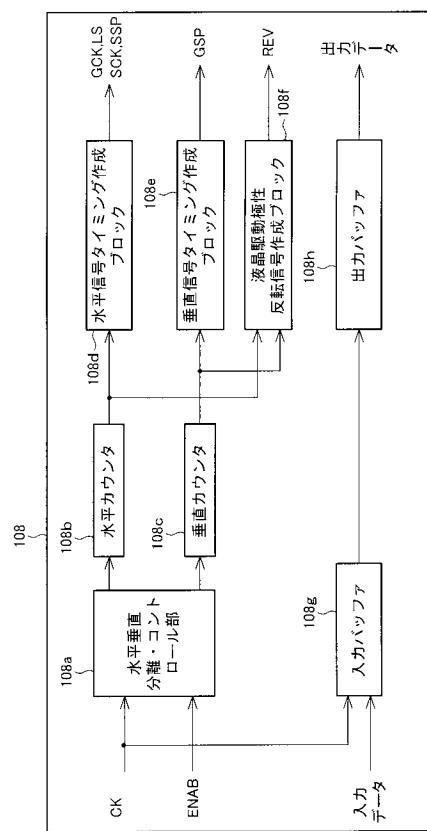

また、図 28 に、V - E N A B モードで制御する場合のタイミングコントロール A S I C の一例としてタイミングコントロール A S I C 108 の構成を示す。タイミングコントロ

50

ール A S I C 1 0 8 においては、水平垂直分離・コントロール部 1 0 8 a が、入力されるデータイネーブル信号 E N A B とクロック信号 C K とから、水平駆動用の基準タイミングと垂直駆動用の基準タイミングとを分離する。水平カウンタ 1 0 8 b は水平駆動用の基準タイミングからクロック信号 C K のクロックをカウントし、垂直カウンタ 1 0 8 c は垂直駆動用の基準タイミングから E N A B 信号の立ち上がりエッジをカウントする。水平信号タイミング作成ブロック 1 0 8 d は、水平カウンタ 1 0 8 b のカウント結果を基に、ゲートクロック信号 G C K、ラッチストローブ信号 L S、ソースクロック信号 S C K、およびソーススタートパルス信号 S S P を、垂直信号タイミング作成ブロック 1 0 8 e は、垂直カウンタ 1 0 8 c のカウント結果を基に、ゲートスタートパルス信号 G S P を生成して出力する。また、液晶駆動極性反転信号作成ブロック 1 0 8 f は、水平カウンタ 1 0 8 b および垂直カウンタ 1 0 8 c のカウント結果を基に、液晶駆動極性反転信号 R E V を生成して出力する。また、入力データ信号 D A T A i n はクロック信号 C K のタイミングで入力バッファ 1 0 8 g に入力され、出力バッファ 1 0 8 h から出力データとして出力される。

【 0 0 2 8 】

このように、V - E N A B モードの場合には、H V モードの場合のような垂直同期信号および水平同期信号がタイミングコントローラ A S I C に入力されないため、1 ライン目のデータ D H 1 が入力されるタイミングで入力されたデータイネーブル信号 E N A B のパルスから、ゲートスタートパルス G S P 信号を作成せざるをえない。

【 0 0 2 9 】

従って、従来技術 2 の構造では、V - E N A B モードで動作させようとすると、ゲートライン G 1 のゲート信号の前にダミーライン G 0 を駆動する信号を出力するようにゲートスタートパルス信号 G S P を生成することができず、従って、V - E N A B モードで動作させることができないという問題を抱えている。とりわけ、昨今では V - E N A B モードでの動作を要求されることが多くなり、早急なる対策が求められていた。

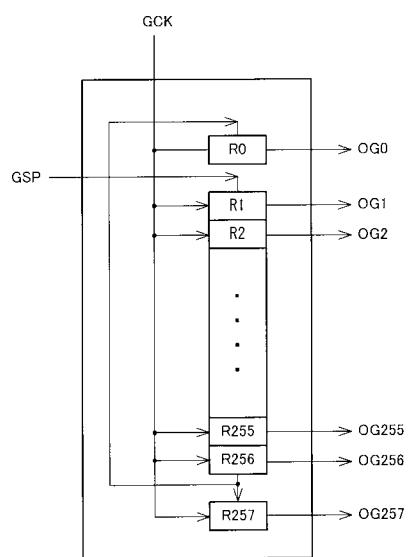

【 0 0 3 0 】

そこで、特開 2 0 0 1 - 2 8 2 1 7 0 号公報では、ゲートドライバ I C 内部に工夫をこらし、端子配列とは異なる順に連続してゲート信号を出力することにより従来技術 1 および従来技術 2 の欠点を補っている。この公報の構成を図 2 9 に示す。同図 ( a ) のゲートドライバ 1 0 2 は、図 2 3 のゲートドライバ 1 0 2 のドライバ I C 1 2 2 をドライバ I C 1 3 2 で置き換えたものである。図 3 0 にドライバ I C 1 3 2 の内部構成を示す。ゲートスタートパルス信号 G S P は内部のシフトレジスタを R 1 R 2 ... R 2 5 6 R 0 の順で転送される。また、図 3 1 に示すように、R 2 5 6 に転送されたときの端子 O G 2 5 6 による最終ゲートライン G 2 5 6 の駆動と同時に、端子 G S P o u t からゲートスタートパルス信号 G S P が次段のドライバ I C 1 3 2 に入力される。そして、前段のダミーライン G 0 を駆動するタイミングで、次段のドライバ I C 1 3 2 の端子 O G 1 によりゲートライン G 2 5 7 を駆動する。以下、これを従来技術 3 とする。

【 0 0 3 1 】

【発明が解決しようとする課題】

しかしながら、従来技術 3 のゲートドライバ 1 0 2 のドライバ I C 1 3 2 は、最初から I C に設けられている出力端子の順番とは異なる順番でゲート出力を行うという特別な仕様により構成される必要があるため、設けられている出力端子の順番でゲート出力を行う既存のドライバ I C を用いることができない。すなわち、図 2 9 を用いて説明すると、初段のドライバ I C 1 3 2 に、端子 O G 0 O G 1 O G 2 ... O G 2 5 6 という出力端子が設けられている順番でゲート信号を出力するドライバ I C を用いることができない。従って、従来技術 3 を実施しようとすると各種の解像度に対応したゲートドライバ I C を最初から開発せざるを得ず、開発費用及び開発日数が大幅に増加してしまうという問題が発生する。このように、最初からドライバ I C に設けられている出力端子についてはその順番で駆動するという、既存のドライバ I C を利用したダミーライン G 0 の駆動技術が求められている。

【 0 0 3 2 】

10

20

30

40

50

本発明は上記従来の問題点に鑑みなされたものであり、その目的は、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データイネーブル信号により表示タイミングが支配されるモード即ちV-E N A Bモードで表示を行うことが可能な表示装置、および表示駆動回路の制御装置、ならびに表示装置の駆動方法を提供することにある。

【0033】

【課題を解決するための手段】

本発明の表示装置は、上記課題を解決するために、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータイネーブル信号とクロック信号とが入力され、上記データイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、上記制御装置は、上記データイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴としている。

【0034】

上記の発明によれば、制御装置は、列駆動回路が1垂直期間の最初の水平期間の表示データに対応した列駆動信号を出力開始するまでの間に、行駆動回路が最上段の行駆動信号の出力端子に行駆動信号を出力するように、データイネーブル信号の入力タイミングを基準して、データイネーブル信号およびクロック信号から行駆動タイミング信号を生成して行駆動回路に入力する。

【0035】

従って、行駆動回路の最上段の行駆動信号の出力端子が、最上段の有効画素の寄生容量を他の画素と同等にするために設けられたダミーの行ラインに接続されている場合には、データイネーブル信号により表示タイミングが支配されるモードで表示を行おうとするときに、最初の水平期間の列駆動信号を列駆動ラインに出力する前にダミーの行ラインを駆動することができる。すなわち、ダミーの行ラインを駆動した後、行ラインを上から下に向かって順番に駆動する。これにより、行駆動回路を、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成することができる。また、ダミーの行ラインは最上段の出力端子に接続されればよいので、従来のようにドライバICの他の出力端子から長い配線を迂回させて引き回して設ける必要がない。従って、表示パネル外に行駆動回路への配線用のプリント基板が設けられていなくてもダミーの行ラインを駆動することができる。

【0036】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データイネーブル信号により表示タイミングが支配されるモードで表示を行うことが可能な表示装置を提供することができる。

【0037】

10

20

30

40

50

また、従来技術3のように行ラインとダミーの行ラインとの2本のラインを同時に駆動する必要がないため、行駆動信号波形のなまりなどが生じることがなく、表示品位の低下を回避することができる。さらに、既存のドライバICを利用することができるため、マルチベンダー化が可能である。

【0038】

さらに本発明の表示装置は、上記課題を解決するために、上記列駆動タイミング信号は、上記行駆動信号を上記行ラインのそれぞれに順次出力するタイミングを決めるように上記行駆動回路内でシフトされる1パルスからなるスタートパルス信号と、上記スタートパルス信号をシフトさせるタイミングを決めるシフトクロック信号とを含んでおり、上記制御装置は、上記データイネーブル信号の入力タイミングで上記スタートパルス信号を生成開始し、上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように上記行駆動回路が上記スタートパルス信号を取り込むための上記シフトクロック信号の1クロック目を、上記入力タイミングから上記クロック信号のクロックを所定数カウントした時点で生成することを特徴としている。

10

【0039】

上記の発明によれば、行駆動回路が、スタートパルス信号をシフトクロック信号によりシフトさせることにより行ラインを順次駆動していく駆動回路である場合に、制御装置にデータイネーブル信号が入力されるタイミングでスタートパルス信号を生成開始し、その後クロック信号のクロックを所定数カウントした時点でシフトクロック信号の1クロック目を生成し、ダミーの行ラインを駆動するために行駆動回路がスタートパルス信号を取り込むようにすることができる。従って、行駆動回路に用いるドライバICのセットアップホールド時間に合わせて、上記クロックのカウント数を定めることができ、ドライバICの特性に応じてダミーの行ラインを駆動することができる。

20

【0040】

さらに本発明の表示装置は、上記課題を解決するために、上記制御装置は、1水平期間の上記表示データを上記列駆動回路に入力完了した後の水平帰線期間分の経過期間内に、上記列駆動回路が上記列駆動信号を出力するタイミングを決める上記列駆動用タイミング信号である列駆動開始タイミング信号を上記列駆動回路に入力し、上記シフトクロック信号の上記1クロック目より後のクロックを上記列駆動開始タイミング信号に合わせて上記行駆動回路に入力することを特徴としている。

30

【0041】

上記の発明によれば、データイネーブル信号どうしの間には水平帰線期間が設けられているが、制御装置が表示データを列駆動回路に入力完了した時点で列駆動回路に列駆動開始タイミング信号を出力させるのではなく、入力完了した時点からさらに経過する水平帰線期間内に列駆動開始タイミング信号を出力させる。そして、制御装置は、この出力タイミングに合わせてシフトクロック信号の1クロック目より後のクロックを行駆動回路に入力する。

【0042】

従って、シフトクロック信号の1クロック目でスタートパルス信号が取り込まれたときに、ダミーの行ラインを駆動する時間を長くすることができ、他の行ラインの駆動時間と同等にすることができる。

40

【0043】

さらに本発明の表示装置は、上記課題を解決するために、上記制御装置は、入力される上記表示データを1水平期間遅延させて上記列駆動回路に入力することを特徴としている。

【0044】

上記の発明によれば、制御装置が、入力される表示データを1水平期間遅延させて列駆動回路に入力するので、制御装置にデータイネーブル信号が入力されるタイミングから列駆動回路が1垂直期間の最初の水平期間の列駆動信号を出力開始するまでの期間を長くすることができ、ダミーの行ラインを駆動する時間を容易に十分長くすることができる。

【0045】

50

さらに本発明の表示装置は、上記課題を解決するために、表示に有効な上記画素に接続された上記行ラインは1050本であり、上記行駆動回路は263個の上記行駆動信号の出力端子を備えたドライバICが4個カスケード接続されたものであることを特徴としている。

【0046】

上記の発明によれば、表示に有効な上記画素に接続された1050本の行ラインにダミーの行ラインを加えた1051本のラインを、合計 $263 \times 4 = 1052$ 本の行駆動信号の出力端子を有するカスケード接続のドライバICで駆動するので、使用しない出力端子が少なく、ICチップサイズの縮小および最適化が容易で、低コスト化を図ることができる。

10

【0047】

また、本発明の表示装置は、上記課題を解決するために、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータタイナーブル信号とクロック信号とが入力され、上記データタイナーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイナーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、上記行駆動回路はドライバICがシステム・オン・フィルム構造により実装されたものであり、所定のドライバICにおける最終の上記行ラインに対応する上記行駆動信号の出力端子の次に設けられた出力端子から、ICチップの下方を通るように配線が引き回され、上記配線が上記表示パネルに設けられた最上段の上記行ラインよりもさらに上段にダミーの行ラインとして延設されていることを特徴としている。

20

【0048】

上記の発明によれば、行駆動回路の所定のドライバICにおける最終の行ラインに対応する行駆動信号の出力端子の次に設けられた出力端子から、システム・オン・フィルム構造を利用してICチップの下方を通るように配線が引き回れて、表示パネルに設けられた最上段の行ラインよりもさらに上段に延設されたダミーの行ラインは、最上段の有効画素の寄生容量をその他の画素と同等にするためのダミーの行ラインとすることができます。従って、表示パネル外に行駆動回路への配線用のプリント基板が設けられていなくてもダミーの行ラインを設けることができる。

30

【0049】

そして、このダミーの行ラインの駆動は、上記所定のドライバICの出力端子を設けられている順番で駆動した後に行えばよいので、データタイナーブル信号により表示タイミングが支配されるモードで表示を行おうとするときに、ダミーの行ラインを他の行ラインより先に駆動する必要がない。これにより、ドライバICには、設けられている順番で出力端子を駆動する既存のドライバICを用いることができる。

40

【0050】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイナーブル信号により表示タイミングが支配されるモードで表示を行うことが可能な表示装置を提供することができる。さらに、既存のドライバICを利用することができるため、マルチベンダー化が可能である。

【0051】

50

また、本発明の表示駆動回路の制御装置は、上記課題を解決するために、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路とを備える表示駆動回路を制御する、表示駆動回路の制御装置であって、上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力し、上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴としている。

10

#### 【0052】

上記の発明によれば、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことができる。

20

#### 【0053】

また、本発明の表示装置の駆動方法は、上記課題を解決するために、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置を駆動する表示装置の駆動方法であって、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する表示装置の駆動方法において、上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記表示データを出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力することを特徴としている。

30

#### 【0054】

上記の発明によれば、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことができる。

40

## 【0055】

## 【発明の実施の形態】

## 〔実施の形態1〕

本発明の実施の一形態について図1ないし図4に基づいて説明すれば、以下のとおりである。

## 【0056】

本実施の形態に係る液晶表示装置（表示装置）は、 $1024 \times 768$  の画素を有するXGAのTFTアクティブマトリクス方式の液晶表示装置である。タイミングコントロールASIC（制御装置）、ゲートドライバ（行駆動回路）、ソースドライバ（列駆動回路）、および液晶パネル（表示パネル）が配置されているという全体の構成は従来の技術で説明したものと同様である。画素の構成も、従来の技術で説明した下ゲート構造である。また、この液晶表示装置は、ゲート基板省略構造であり、V-ENABLEモードで動作する。

## 【0057】

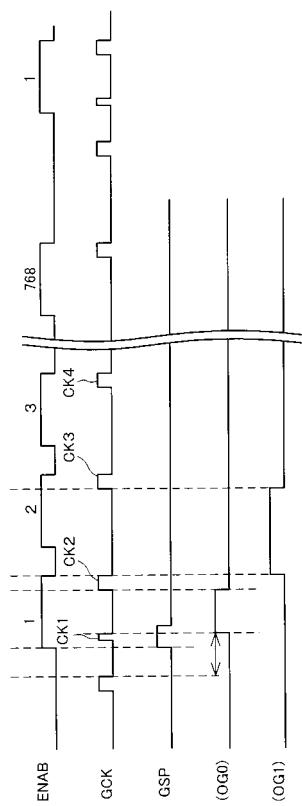

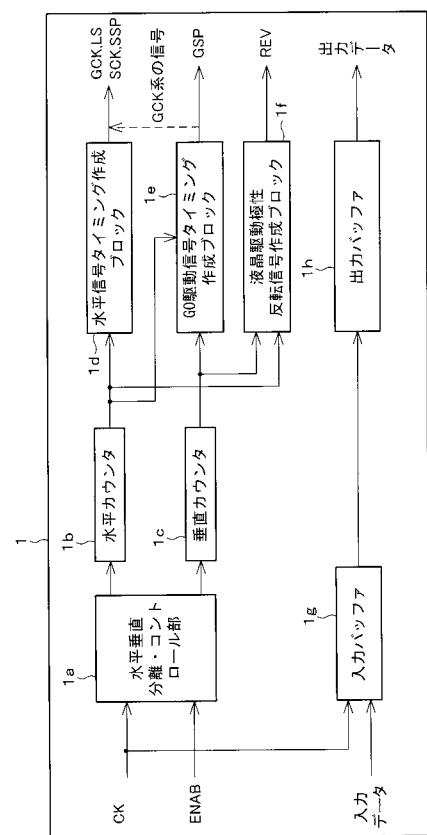

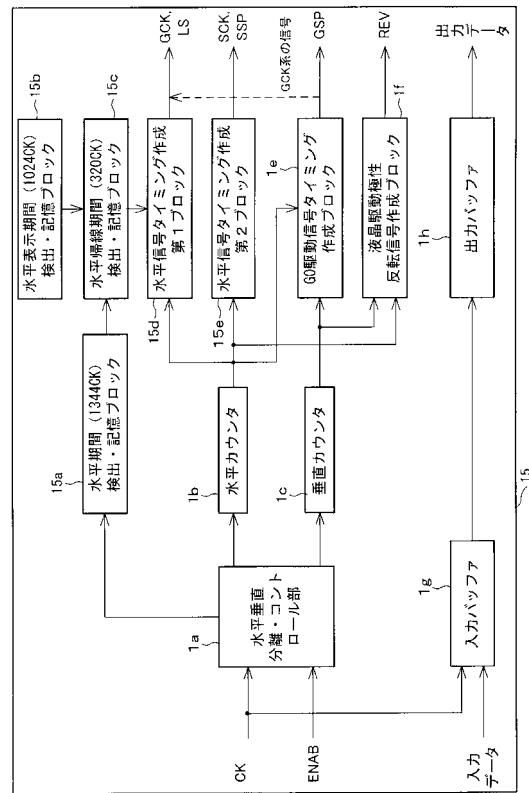

図2に、本実施の形態におけるタイミングコントロールASIC（以下、コントロールICと称する）1の構成を示す。コントロールIC1は、水平垂直分離・コントロール部1a、水平カウンタ1b、垂直カウンタ1c、水平信号タイミング作成ブロック1d、G0駆動信号タイミング作成ブロック1e、液晶駆動極性反転信号作成1f、入力バッファ1g、および出力バッファ1hを備えている。

## 【0058】

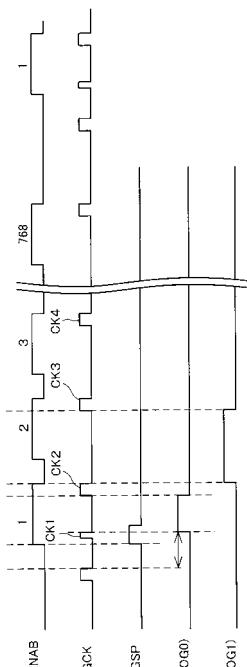

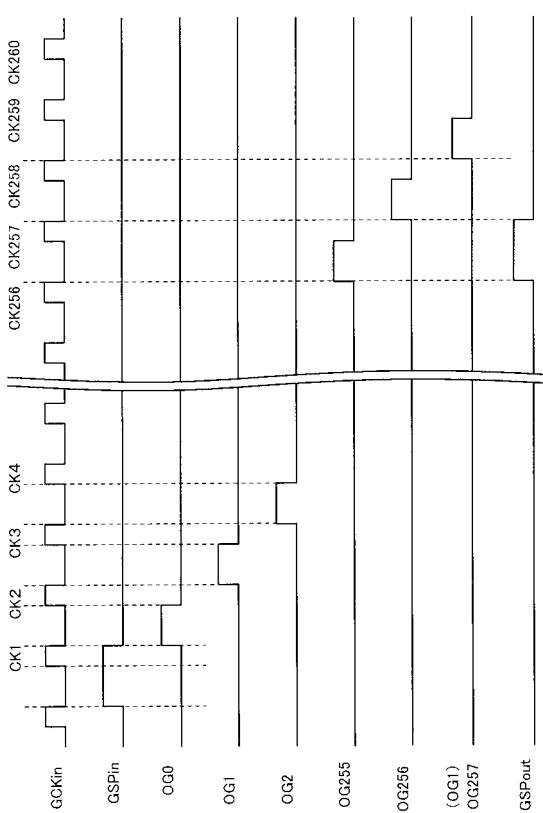

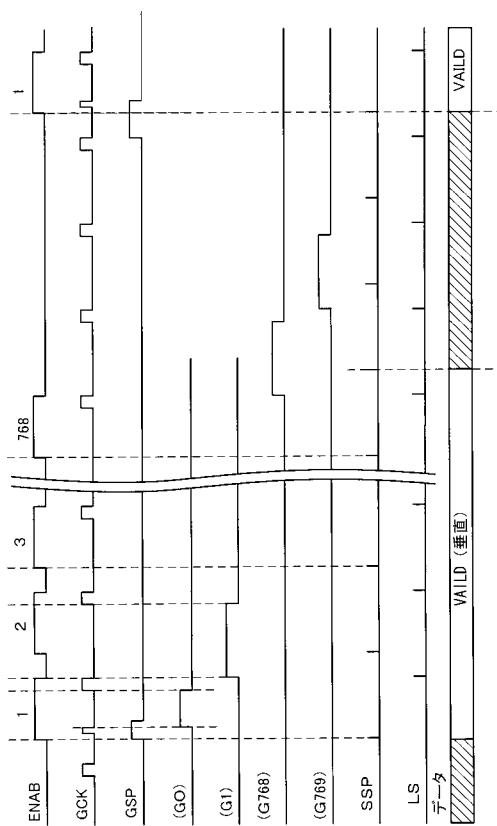

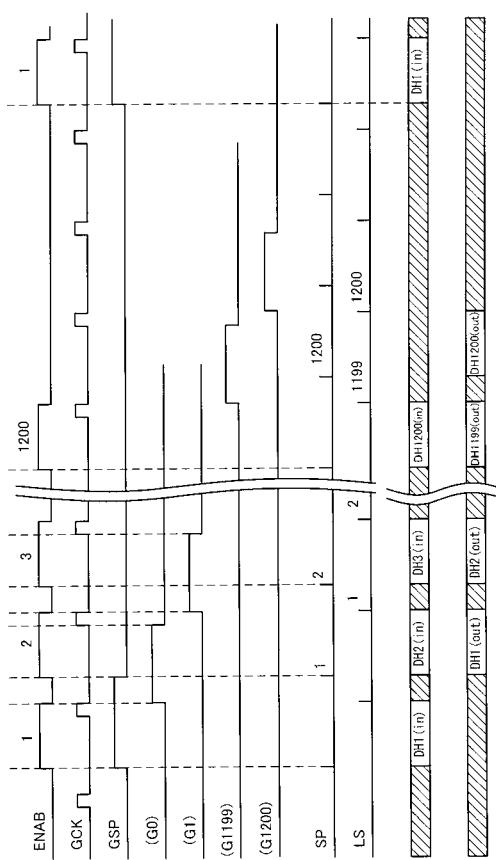

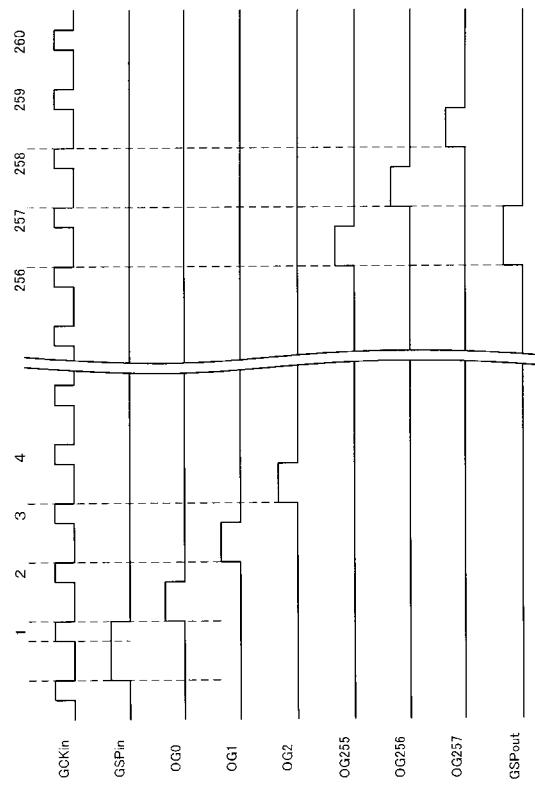

水平垂直分離・コントロール部1aは、入力されるデータタイネーブル信号ENABLEとクロック信号CKとから、水平駆動用の基準タイミングと垂直駆動用の基準タイミングとを分離する。水平カウンタ1bは、水平垂直分離・コントロール部1aによって分離された水平駆動用の基準タイミングから、クロック信号CKのクロックをカウントする。垂直カウンタ1cは、水平垂直分離・コントロール部1aによって分離された垂直駆動用の基準タイミングから、ENABLE信号の立ち上がりエッジをカウントする。水平信号タイミング作成ブロック1dは、水平カウンタ1bのカウント結果を基に、ゲートクロック信号（行駆動用タイミング信号）GCK、ラッチストローブ信号（列駆動用タイミング信号）LS、表示データサンプリングクロックであるソースクロック信号（列駆動用タイミング信号）SCK、および表示データサンプリング開始信号であるソーススタートパルス信号（列駆動用タイミング信号）SSPを生成して出力する。このとき、ゲートクロック信号GCKとして、図1に示すようにデータタイネーブル信号ENABLEの入力タイミング（立ち上がりタイミング）から所定クロック数のカウント後に立ち上がってデータタイネーブル信号ENABLEの立ち下がりタイミングで立ち下がるパルスCK2・CK3・CK4…の他に、これらの前に、1垂直期間の最初の水平期間に対応するデータタイネーブル信号ENABLEの入力タイミングからわずかな所定クロック数のカウント後に立ち上がって、その所定クロック数後に立ち下がるパルスCK1が生成される。

## 【0059】

G0駆動信号タイミング作成ブロック1eは、水平カウンタ1bおよび垂直カウンタ1cのカウント結果を基に、ゲートスタートパルス信号（行駆動用タイミング信号）GSPを生成して出力する。このとき、ゲートスタートパルス信号GSPは、図1に示すように、1垂直期間の最初の水平期間に対応するデータタイネーブル信号ENABLEの入力タイミングで立ち上がり、上述のパルスCK1が立ち下がった後に立ち下がるパルスである。

## 【0060】

また、液晶駆動極性反転信号作成ブロック1fは、水平カウンタ1bおよび垂直カウンタ1cのカウント結果を基に、液晶駆動極性反転信号REVを生成して出力する。また、入力バッファ1gは、クロック信号CKのタイミングで入力データ信号（表示データ）を取り込む。出力バッファ1hは、入力バッファ1gから入力データ信号を受け取って出力する。

## 【0061】

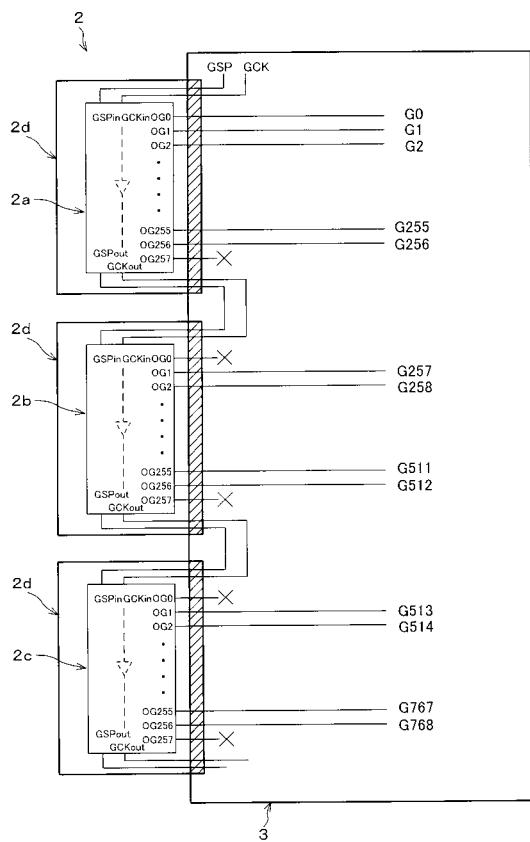

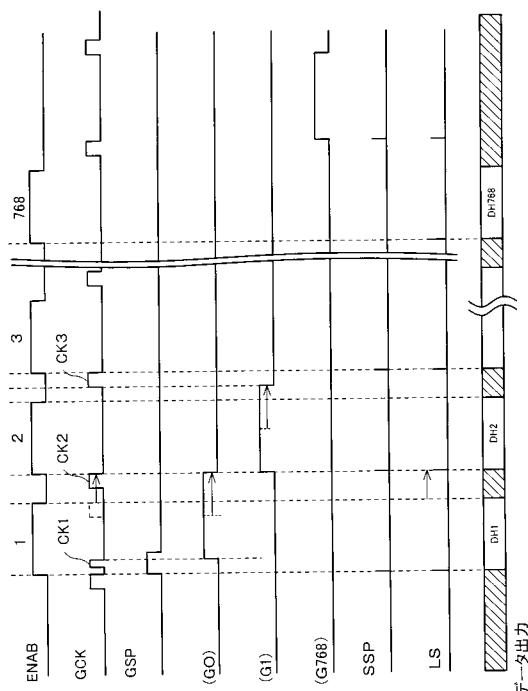

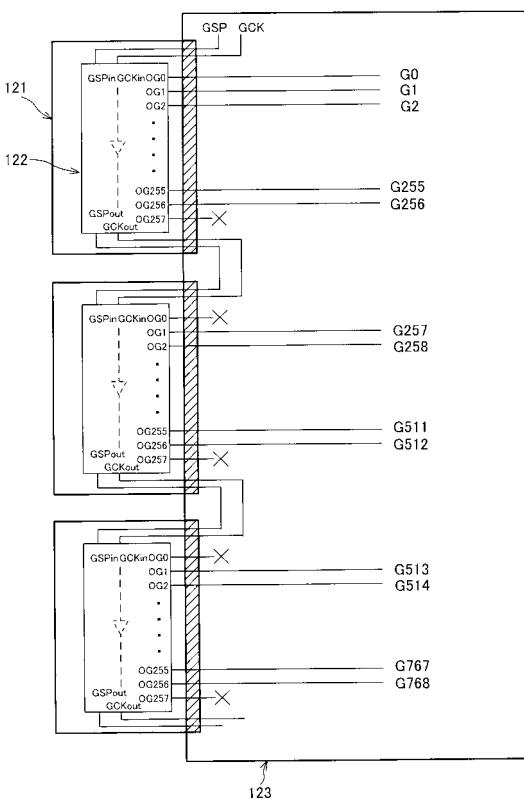

次に、図3に、本実施の形態におけるゲートドライバ2の構成を示す。ゲートドライバ2

10

20

30

40

50

は液晶パネル3のゲートライン(行ライン)を駆動する。液晶パネル3には、有効画素に接続された768本のゲートラインG1・G2・…・G768が設けられている他、ゲートラインG1のさらに上段にダミーのゲートラインとなるダミーラインG0が設けられており、ゲートドライバ2はこれら769本のラインを駆動するために、258個の出力端子を有するドライバICを3個カスケード接続された状態で備えている。液晶パネル3の上下端に余剰出力端子が偏らないように、256出力単位でカスケード接続されている。なお、257出力でもドライバICと液晶パネルとの結線を変更すれば対応は可能であるが、後述する実施の形態3でダミー画素付ダミーラインを駆動する構成に拡張することを考慮して258出力としている。

## 【0062】

10

上記3つのドライバICを、液晶パネル3の最上段側(ダミーラインG0側)から順に、ドライバIC2a、ドライバIC2b、ドライバIC2cとする。ドライバIC2a・2b・2cはそれぞれTAB方式によりキャリアアーテープ2d上に実装され、TCPとなっている。ゲート信号(行駆動信号)が出力可能な出力端子は、ドライバIC2a・2b・2cのそれぞれに端子OG0・OG1・OG2・…・OG257として設けられている。

## 【0063】

ドライバIC2aでは、端子OG0がダミーラインG0に、端子OG1・OG2・…・OG256が順にゲートラインG1・G2・…・G256に、それぞれ接続されており、端子OG257は使用されない。ドライバIC2bでは、端子OG1・OG2・…・OG256が順にゲートラインG257・G258・…・G512に、それぞれ接続されており、端子OG0・OG257は使用されない。ドライバIC2cでは、端子OG1・OG2・…・OG256が順にゲートラインG513・G514・…・G768に、それぞれ接続されており、端子OG0・OG257は使用されない。

20

## 【0064】

また、ドライバIC2aには、コントロールIC1からゲートスタートパルス信号GSPおよびゲートクロック信号(シフトクロック信号)GCKがソースドライバ側から液晶パネル3を介して、端子GSPin・GCKinに入力される。なお、ゲートクロック信号GCKは、ICチップ内のバッファを介して自己転送されるようになっていてもよいが、SOF(System On chip)構造を利用してICチップの下方で信号が転送されるようなSOF配線が備えられていてもよい。

30

## 【0065】

ゲートスタートパルス信号GSPおよびゲートクロック信号GCKは、ドライバIC2aの端子GSPout・GCKoutから出力され、ドライバIC2bの端子GSPin・GCKinに入力され、同様にして、ドライバIC2cにも転送される。このようにしてカスケード接続がなされている。

40

## 【0066】

本実施の形態では、V-ENABモード時において、1ライン目の表示データをソースドライバICへデータ転送するのによそ1水平周期必要であることを利用し、ソースドライバICが1ライン目の表示データをサンプリングしている期間にダミーラインG0を駆動するように、コントロールIC1は1ライン目のデータイネーブル信号ENABが入力されれば直ちにダミーラインG0を駆動するためのゲートスタートパルス信号GSPおよびゲートクロック信号GCKを出力する。

## 【0067】

コントロールIC1からゲートスタートパルス信号GSPの“High”的パルスが入力されると、図4に示すように、ゲートクロック信号GCKの立ち下がりタイミングでゲートスタートパルス信号GSPのサンプリングが行われ、そのサンプリング信号がドライバIC2a・2b・2cの内部のシフトレジスタで、各端子OGn(n=0, 1, …, 256)に転送される。ドライバIC2aの端子OG0には、図4のゲートクロック信号GCKのパルスCK1の立ち下がりタイミングでゲート信号の出力が開始され、パルスCK2の立ち上がりタイミングまで出力が継続される。この期間にダミーラインG0が駆動され

50

る。

【0068】

その後、端子OG1にはパルスCK2の立ち下がりタイミングからパルスCK3の立ち上がりタイミングまで、端子OG2にはパルスCK3の立ち下がりタイミングからパルスCK4の立ち上がりタイミングまで、といったように各端子にゲート信号が順次出力され、ゲートラインGが順次駆動される。端子OG1にゲート信号が出力開始されると同時に、コントロールIC1からソースドライバにラッチストローブ信号LSが入力され、1垂直期間の最初の水平期間の表示データに対応する書き込み信号がソースドライバから出力される。このようにしてゲート信号の出力期間に画素に書き込み信号が書き込まれていく。そして、ドライバIC2aの端子OG255にゲート信号が出力されると同時に、端子GSPoutからゲートスタートパルス信号GSPが出力され、ドライバIC2aの端子OG256の次にドライバIC2bの端子OG1にゲート信号が出力される。

10

【0069】

このように、本実施の形態に係る液晶表示装置によれば、コントロールIC1は、ソースドライバが1垂直期間の最初の水平期間の表示データに対応した書き込み信号を出力開始するまでの間に、ゲートドライバ2が最上段のゲート信号の出力端子OG0にゲート信号を出力するように、データイネーブル信号ENA Bの入力タイミングを基準して、データイネーブル信号ENA Bおよびクロック信号CKからゲートスタートパルス信号GSPおよびゲートクロック信号GCKを生成してゲートドライバ2に入力する。

20

【0070】

従って、V-ENA Bモードで表示を行おうとするときに、最初の水平期間の書き込み信号をソースラインSに出力する前にダミーラインG0を駆動することができる。すなわち、ダミーラインG0を駆動した後、ゲートラインGを上から下に向かって順番に駆動する。これにより、ゲートドライバ2を、設けられている順番で出力端子が駆動される既存のドライバIC2a・2b・2cを用いて構成することができる。また、ダミーラインG0は最上段の出力端子OG0に接続されればよいので、従来のようにドライバICの他の出力端子から長い配線を迂回させて引き回して設ける必要がない。従って、ゲート基板省略構造でもダミーラインG0を駆動することができる。

20

【0071】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データイネーブル信号により表示タイミングが支配されるモードで表示を行うことができる。さらに、既存のドライバICを利用することができるため、マルチベンダー化が可能である。

30

【0072】

また、本実施の形態に係る液晶表示装置によれば、コントロールIC1にデータイネーブル信号ENA Bが入力されるタイミングでスタートパルス信号GSPを生成開始し、その後クロック信号CKのクロックを所定数カウントした時点でゲートクロック信号GCKの1クロック目であるパルスCK1を生成し、ダミーラインG0を駆動するためにゲートドライバ2がスタートパルス信号GSPを取り込むようになっている。従って、ゲートドライバ2に用いるドライバIC2aのセットアップホールド時間に合わせて、上記クロックのカウント数を定めることができ、ドライバIC2aの特性に応じてダミーラインG0を駆動することができる。

40

【0073】

図1で説明すると、ダミーラインG0のゲート信号波形は、ゲートラインGm(m=0)のゲート信号波形よりもおよそ水平帰線期間だけ短いパルス波形である。このゲート信号の短くなる期間は、例えば、XGA解像度でVESA標準タイミングで規定すれば、1水平周期が20.7μsecであるのに対しておよそ5μsecであるが、ダミーラインG0の駆動期間は、寄生容量による画素電極電位の変動を2行目以降の画素と同等にする効

50

果が得られるように適宜決めればよく、特にある値に限定されるものではない。例えば上記の数値例は、液晶表示装置が C S O N C O M ( C s オンコモン ) 構造である場合に好適に使用することができる。

【 0 0 7 4 】

なお、ノート P C 用液晶表示装置などのように狭額縁を求められる仕様に対してゲート基板省略構造を採用する場合、必然的にゲートドライバ I C を駆動するための電源・信号配線が細くなり、その結果ゲート駆動電源の配線抵抗が高くなる傾向にあるが、従来技術 3 の図 3 2 の例でいえばゲートライン G 2 5 7 を駆動するタイミングでドライバ I C は 2 本のゲートラインを同時に駆動しており、ゲート電源に流れる電流はこのタイミングのみ 2 倍になりゲート信号波形のなまりなどが生じ、その結果、そのゲートラインの画素が異常に見えるなどの輝度ムラを生じ、表示品位低下が顕在化する問題がある。

【 0 0 7 5 】

これに対して本実施の形態に係る液晶表示装置によれば、従来技術 3 のようにゲートライン G とダミーライン G 0 との 2 本のラインを同時に駆動する必要がないため、ゲート信号波形のなまりなどが生じることがなく、表示品位の低下を回避することができる。

【 0 0 7 6 】

〔 実施の形態 2 〕

本発明の他の実施の形態について図 5 ないし図 7 に基づいて説明すれば以下のとおりである。なお、前記実施の形態 1 で述べた構成要素と同じ機能を有する構成要素については同じ符号を付し、その説明を省略する。

【 0 0 7 7 】

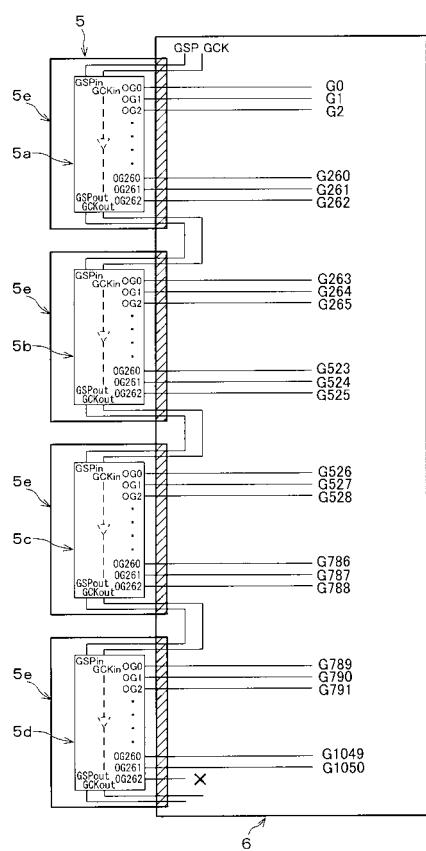

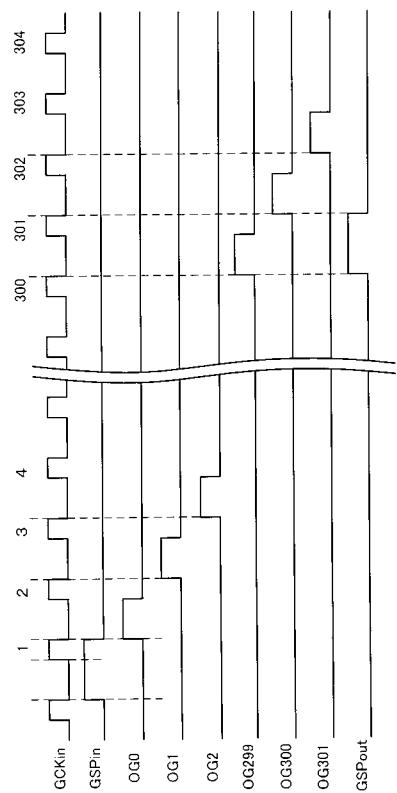

本実施の形態に係る液晶表示装置は、実施の形態 1 で述べた液晶表示装置を  $1400 \times 1050$  の画素を有する S X G A + の液晶表示装置としたものである。これに伴い、図 5 に示すようにゲートドライバ 5 および液晶パネル 6 を備えている。

【 0 0 7 8 】

ゲートドライバ 5 は、263 出力のドライバ I C 5 a · 5 b · 5 c · 5 d をそれぞれ T A B 方式によりキャリアアテーブ 5 e 上に実装して T C P を構成し、カスケード接続したものである。液晶パネル 6 にはダミーライン G 0 と、ゲートライン G 1 · G 2 · ... · G 1 0 5 0 とが形成されており、これらにドライバ I C 5 a · 5 b · 5 c の端子 O G 0 · O G 1 · ... O G 2 6 2 と、ドライバ 5 d の端子 O G 0 · O G 1 · ... · O G 2 6 1 とが接続されている。使用しない端子はドライバ I C 5 d の端子 O G 2 6 2 のみである。

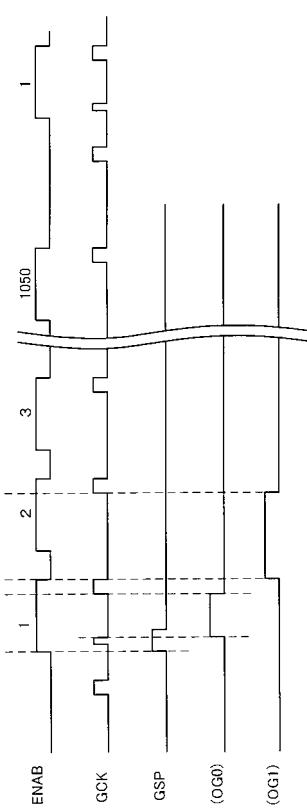

【 0 0 7 9 】

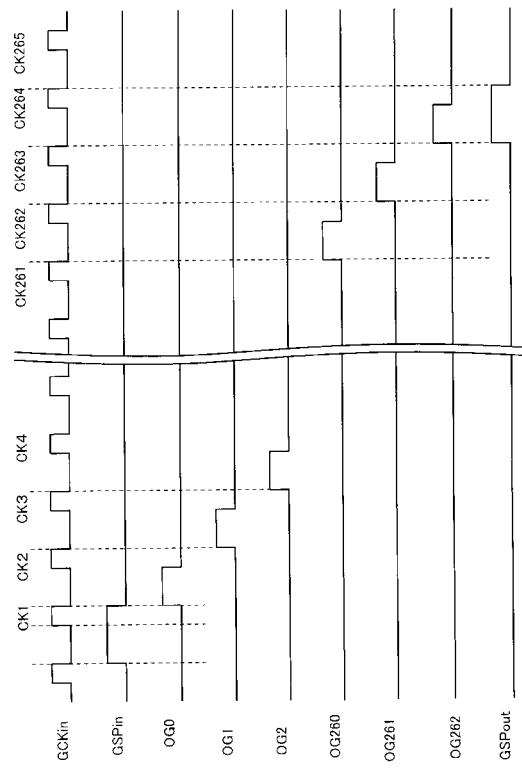

この場合のコントロール I C 1 の信号を図 6 に示す。データイネーブル信号 E N A B が 1 垂直期間に 1050 個入力され、ゲートスタートパルス信号 G S P およびゲートクロック信号 G C K は図 1 と同様である。また、ゲートドライバ 5 の信号を図 7 に示す。端子 O G 0 からの順次駆動については図 4 と同様であり、端子 O G 2 6 2 の駆動時に端子 G S P o u t からスタートパルス信号 G S P を出力して次段のドライバ I C に入力する。

【 0 0 8 0 】

すなわち、本実施の形態では、263 出力であってかつ 263 出力単位でカスケード接続する一般的なゲートドライバ I C を採用することができ、従来技術 3 で述べたような特殊仕様であるゲートドライバ I C を開発する必要はない。

【 0 0 8 1 】

また、従来技術 3 のようにダミーライン G 0 に接続された端子 O G 0 を最終の端子の次に駆動するドライバ I C を用いて、表示に有効な上記画素に接続された 1050 本のゲートライン G にダミーライン G 0 を加えた 1051 本のラインを駆動しようとすれば、264 出力ないしは 265 出力のドライバ I C が必要である。これに対して、本実施の形態に係る液晶表示装置では、上記 1051 本のラインを、合計  $263 \times 4 = 1052$  本のゲート信号の出力端子を有するカスケード接続のドライバ I C 5 a · 5 b · 5 c · 5 d で駆動するので、使用しない出力端子が少なく、I C チップサイズの縮小および最適化が容易で、低コスト化を図ることができる。

## 【0082】

## 〔実施の形態3〕

本発明のさらに他の実施の形態について図8および図9に基づいて説明すれば以下のとおりである。なお、前記実施の形態1および2で述べた構成要素と同じ機能を有する構成要素については同じ符号を付し、その説明を省略する。

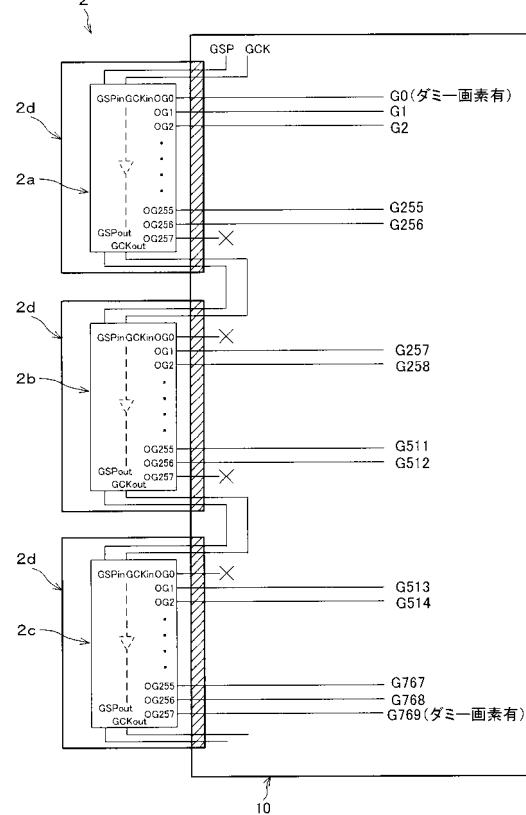

## 【0083】

本実施の形態に係る液晶表示装置は、図8に示すように、パネルの長期信頼性向上のため最上段の有効画素の上および最下段の有効画素の下に、それぞれダミー画素付きのダミーラインG0・G769を備えた液晶パネル10を駆動するタイプであり、それ以外の構成は実施の形態1と同様である。

## 【0084】

従来技術3で説明したダミーラインG0の駆動方式ではゲートラインG257の表示データがダミーラインG0に接続されたダミー画素に書き込まれるため、動画データなどフレーム間で異なる映像データを表示した場合、ダミーラインG0に接続されたダミー画素の対向DC電圧レベルが不安定となってしまう。

## 【0085】

一方、本実施の形態におけるダミーラインG0の駆動方式では、図9の斜線を施した領域で表される垂直帰線期間に、サンプリングした表示データをダミーラインG0の駆動タイミングで出力することが可能なため、安定した電圧を画素に印加可能となる。

## 【0086】

また、垂直帰線期間にサンプリングさせる映像データは、例えば、ノーマリーホワイトパネルの場合に白データ、ノーマリーブラックパネルの場合に黒データなどとすることができる。

## 【0087】

## 〔実施の形態4〕

本発明のさらに他の実施の形態について図10および図11に基づいて説明すれば以下のとおりである。なお、前記実施の形態1ないし3で述べた構成要素と同じ機能を有する構成要素については同じ符号を付し、その説明を省略する。

## 【0088】

本実施の形態に係る液晶表示装置は、コントロールICが内部に1水平期間のクロック数を記憶する回路を有し、この回路を利用して液晶駆動タイミング信号となるゲートクロック信号GCK、ラッチストローブ信号LSの出力タイミングを後ろにずらし、ダミーラインG0の駆動時間を他のゲートラインGと同等にする。

## 【0089】

図10に、本実施の形態におけるコントロールIC15の構成を示す。コントロールIC(制御装置)15は、水平垂直分離・コントロール部1a、水平カウンタ1b、垂直カウンタ1c、G0駆動信号タイミング作成ブロック1e、液晶駆動極性反転信号作成ブロック1f、入力バッファ1g、出力バッファ1h、水平期間検出・記憶ブロック15a、水平表示期間検出・記憶ブロック15b、水平帰線期間検出・記憶ブロック15c、水平信号タイミング作成第1ブロック15d、および水平信号タイミング作成第2ブロック15eを備えている。

## 【0090】

水平期間検出・記憶ブロック15aは、水平垂直分離・コントロール部1aに入力されたデータイネーブル信号ENA Bの入力タイミングからクロック信号CKのクロックをカウントして記憶し、1水平期間(例えば1344クロック分)の終了タイミングを知らせる出力を行う。水平表示期間検出・記憶ブロック15bは、データイネーブル信号ENA Bの入力タイミングからクロック信号CKのクロックをカウントして記憶し、1水平期間のうちの書き込み信号を画素に書き込む期間(例えば1024クロック分)の終了タイミングを知らせる出力を行う。水平帰線期間検出・記憶ブロック15cは、水平表示期間検出・記憶ブロック15bから入力された書き込み期間の終了タイミングから水平帰線期間の

10

20

30

40

50

開始タイミングを認識し、水平期間検出・記憶ブロック 15 a から入力された 1 水平期間の終了タイミングから、水平帰線期間（例えば 320 クロック分）の終了タイミングを認識する。

【0091】

水平信号タイミング作成第 1 ブロック 15 d は、水平カウンタ 1 b のカウント結果と、水平帰線期間検出・記憶ブロック 15 c から入力された水平帰線期間の開始タイミングおよび終了タイミングから、ゲートクロック信号 GCK およびラッチストローブ信号 LS を生成して出力する。このとき、図 11 に示すように、ゲートクロック信号 GCK のパルス CK2・CK3・…を、水平帰線期間内に立ち下がるように、ここでは水平帰線期間の終了タイミングで立ち下がるように生成する。そして、ラッチストローブ信号 LS を、次のデータイネーブル信号 ENAB がコントロール I C 15 に入力されるタイミングで生成する。これにより、ダミーライン G0 の駆動時間は、実施の形態 1 で説明した駆動時間から、次のデータイネーブル信号 ENAB がコントロール I C 15 に入力されるタイミングまでの水平帰線期間分だけ延長され、その他のゲートライン G の駆動時間と同等にすることができる。画素への書き込み開始タイミングもその分だけ遅くなる。タイミングの変化を図 11 中に矢印で示す。

【0092】

また、水平信号タイミング作成第 2 ブロック 15 e は、水平カウンタ 1 b のカウント結果から、ソースクロック信号 SCK およびソーススタートパルス信号 SSP を生成して出力する。

10

20

【0093】

以上の構成によれば、表示データに遅延などの特別な処理を施す必要もなく、コントロール I C のロジック小変更により、ダミーライン G0 の駆動時間を長くすることが可能となる。

【0094】

このような構成は、例えば、CS ON GATE (Cs オンゲート) のような寄生容量による電圧変動分 V2 が大きな画素構造に対して使用することができる。

30

【0095】

〔実施の形態 5〕

本発明のさらに他の実施の形態について図 12 ないし図 14 に基づいて説明すれば以下のとおりである。なお、前記実施の形態 1 ないし 4 で述べた構成要素と同じ機能を有する構成要素については同じ符号を付し、その説明を省略する。

30

【0096】

本実施の形態に係る液晶表示装置は、SOF (システムオンフィルム) 構造を利用してダミーライン G0 を駆動する構成である。これに伴い、図 12 に示すように、ゲートドライバ 21 および液晶パネル 22 を備える。また、コントロール I C は図 28 のコントロール I C 108 である。

40

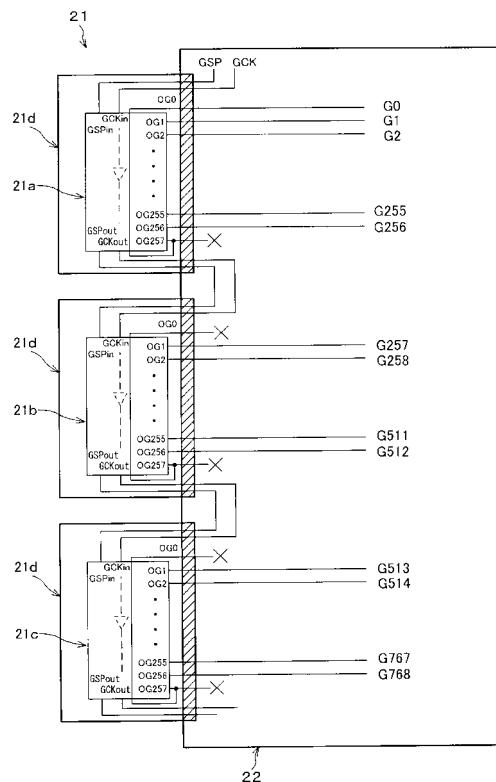

【0097】

ゲートドライバ 21 は、端子 OG1 ~ OG257 を備えたドライバ I C 21a・21b・21c がそれぞれフィルム 21d 上に実装されて SOF 構造とされた状態でカスケード接続されたものである。ドライバ I C 21a の端子 OG257、すなわちドライバ I C 21a における最終のゲートライン G256 に対応する端子 OG256 の次に設けられた端子からは、ドライバ I C 21a チップの下方を通り配線が引き回されている。この配線がフィルム 21d の出力端子としての端子 OG0 から、液晶パネル 22 に設けられた有効画素の最上段のゲートライン G1 よりもさらに上段に延設されてダミーライン G0 となっている。ドライバ I C 21b・21c も同様に製造されたものであり、端子 OG257 から取り出された配線が I C チップの下方を引き回されて、端子 OG1 の上まで延びているが、この端子はここでは使用されない。

【0098】

従って、ドライバ I C 21a では、端子 OG1 OG2 ... OG256 OG0 の順で

50

ゲート信号が出力される。

【0099】

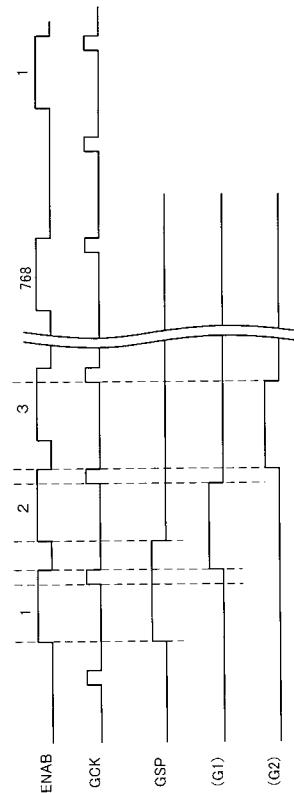

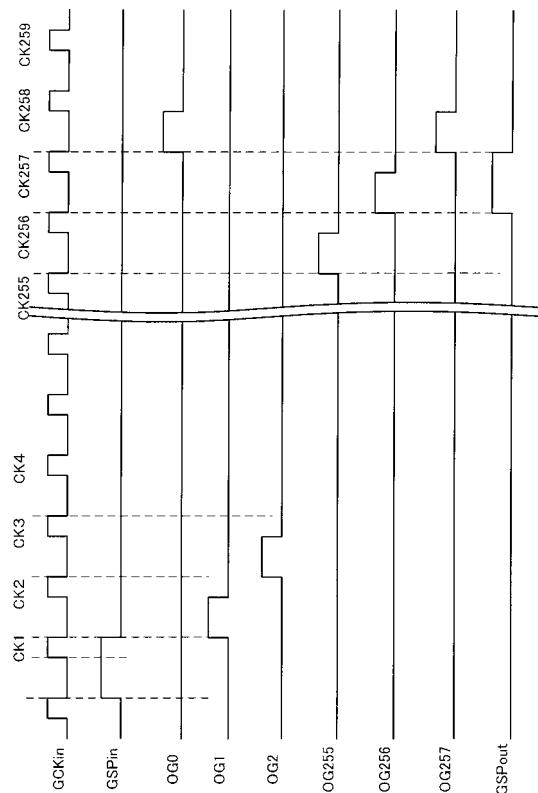

図13にコントロールIC108の信号を示す。ダミーラインG0はゲートラインG256の次に駆動するため、実施の形態1ないし4で述べたような、最初にダミーラインG0を駆動するためのゲートスタートパルス信号GSPおよびゲートクロック信号GCKを生成する必要はなく、ゲートラインG1から順に駆動する通常のゲートスタートパルス信号GSPおよびゲートクロック信号GCKとなっている。また、図14にゲートドライバ21の信号を示す。ドライバIC21aの端子OG256を駆動すると同時に端子GSPoutからゲートスタートパルス信号GSPを次段のドライバIC21bへ入力し、ダミーラインG0とゲートラインG257とを同時に駆動する。

10

【0100】

本実施の形態によれば、液晶パネル22外にゲートドライバ21への配線用のプリント基板が設けられていなくてもダミーラインG0を設けることができる。そして、このダミーラインG0の駆動は、ドライバIC21aの出力端子を設けられている順番で駆動した後に行えばよいので、V-ENABモードで表示を行おうとするときに、ダミーラインG0を他のゲートラインGより先に駆動する必要がない。これにより、ドライバIC21a・21b・21cには、設けられている順番で出力端子を駆動する既存のドライバICを用いることができる。また、このようなドライバICに、端子OG257が設けられているように、出力端子数を増加させた従来型のゲートドライバICを利用して、従来技術3と同等の駆動波形を得ることが可能である。

20

【0101】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイマーブル信号により表示タイミングが支配されるモードで表示を行うことが可能になる。

【0102】

〔実施の形態6〕

本発明のさらに他の実施の形態について図15ないし図17に基づいて説明すれば以下のとおりである。なお、前記実施の形態1ないし5で述べた構成要素と同じ機能を有する構成要素については同じ符号を付し、その説明を省略する。

30

【0103】

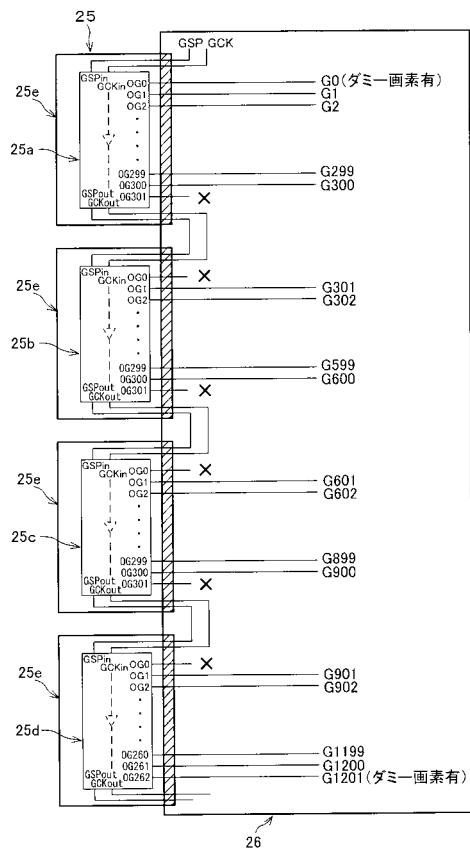

図15に、本実施の形態に係る液晶表示装置のゲートドライバ25および液晶パネル26の構成を示す。また図示しないが、コントロールIC(制御装置)は映像データを保持するラインメモリを内蔵している。

【0104】

この液晶表示装置は1600×1200画素を有するUXGAのTFTアクティブマトリックス方式で、ゲートドライバ25は302出力の4個のドライバIC25a・25b・25c・25dを300出力単位でカスケード接続したものである。4個のカスケード接続により1202出力が利用可能となっている。各ドライバICは、それぞれキャリアテーブ25e上にTAB方式により実装され、TCPが構成されている。また、液晶パネル26には、最上段の有効画素の上および最下段の有効画素の下にそれぞれダミーラインG0・G1201が設けられ、これらにはダミー画素が接続されている。

40

【0105】

UXGAなど超高解像度の映像フォーマットでは、映像データのデータ転送速度が160MHz程度になっており、ソースドライバICのデータ転送速度が間に合わない場合が非常に多い。そこで、コントロールIC内部にラインメモリを内蔵し、一旦1水平期間の映像データをラインメモリに格納した後、映像データを並び替え、ソースドライバICが映像データをサンプリングすることができるようデータ転送速度を落としてソースドライバICにデータを転送する。従って図16に示すように、第1ラインであるゲートラインG

50

0 の映像データ D H 1 ( i n ) は、第 1 水平期間 ( E N A B ( 1 ) ) に一旦コントロール I C にサンプリングされた後、第 2 水平期間 ( E N A B ( 2 ) ) にソースドライバ I C によって映像データ D H 1 ( o u t ) としてサンプリングされる。サンプリング終了後、ラッピング信号 L S の入力によってソースドライバ I C は映像データ D H 1 ( o u t ) に相当するアナログ電圧を出力する。

#### 【 0 1 0 6 】

これに合わせるように、コントロール I C は図 1 6 のようにデータイネーブル信号 E N A B の E N A B ( 1 ) の入力タイミングから E N A B ( 2 ) の入力タイミングまでをパルス期間とするゲートスタートパルス信号 G S P を生成する。また、コントロール I C は、各 E N A B 期間の終了タイミングで立ち下がるようにゲートクロック信号 G C K を生成する。これにより、ゲートドライバ 2 5 は、図 1 7 に示すようにダミーライン G 0 と各ゲートライン G とで期間が等しいゲート信号を順次出力する。

10

#### 【 0 1 0 7 】

本実施の形態では、実施の形態 1 ないし 5 と比較すると映像データをソースドライバ I C に入力するタイミングが 1 水平期間遅れているため、実施の形態 1 に記載しているように 1 ライン目のデータイネーブル信号 E N A B を認識してからすぐにダミーライン G 0 にゲート信号が出力されるようなゲートスタートパルス信号 G S P およびゲートクロック信号 G C K を生成して出力する必要がない。また、実施の形態 4 に記載しているように 1 水平期間のクロック数を記憶し液晶駆動タイミングを後ろにずらす必要もない。コントロール I C から出力されるゲートスタートパルス信号 G S P がゲートドライバ 2 5 によって取り込まれるタイミングを 1 水平期間近く後にずらすだけで、ダミーライン G 0 を駆動することが可能となる。

20

#### 【 0 1 0 8 】

このように、本実施の形態によれば、コントロール I C が、入力される映像データをラインメモリを用いて 1 水平期間遅延させてソースドライバに入力するので、コントロール I C にデータイネーブル信号 E N A B が入力されるタイミングからソースドライバが 1 垂直期間の最初の水平期間の書き込み信号を出力開始するまでの期間を長くすることができ、ダミーライン G 0 を駆動する時間を容易に十分長くすることができる。

#### 【 0 1 0 9 】

以上、実施の形態 1 から 6 まで述べた。本発明は液晶表示装置に限らず、行ラインと列ラインとを駆動するマトリクス型の表示装置に広く適用することができる。また、列駆動回路による列ラインへの出力の仕方は、線順次でも点順次でも構わない。

30

#### 【 0 1 1 0 】

#### 【 発明の効果 】

本発明の表示装置は、以上のように、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータイネーブル信号とクロック信号とが入力され、上記データイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、上記制御装置は、上記データイネーブル信号の入力タイミングから上記列駆動回路が 1 垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力する構成である。

40

50

## 【0111】

それゆえ、データイネーブル信号により表示タイミングが支配されるモードで表示を行おうとするときに、最初の水平期間の列駆動信号を列駆動ラインに出力する前にダミーの行ラインを駆動することができる。すなわち、ダミーの行ラインを駆動した後、行ラインを上から下に向かって順番に駆動する。これにより、行駆動回路を、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成することができる。また、ダミーの行ラインは最上段の出力端子に接続されればよいので、従来のようにドライバICの他の出力端子から長い配線を迂回させて引き回して設ける必要がない。従って、表示パネル外に行駆動回路への配線用のプリント基板が設けられていなくてもダミーの行ラインを駆動することができる。

10

## 【0112】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データイネーブル信号により表示タイミングが支配されるモードで表示を行うことが可能な表示装置を提供することができるという効果を奏する。

## 【0113】

また、従来技術3のように行ラインとダミーの行ラインとの2本のラインを同時に駆動する必要がないため、行駆動信号波形のなまりなどが生じることがなく、表示品位の低下を回避することができるという効果を奏する。さらに、既存のドライバICを利用することができますため、マルチベンダー化が可能であるという効果を奏する。

20

## 【0114】

さらに本発明の表示装置は、以上のように、上記列駆動タイミング信号は、上記行駆動信号を上記行ラインのそれぞれに順次出力するタイミングを決めるように上記行駆動回路内でシフトされる1パルスからなるスタートパルス信号と、上記スタートパルス信号をシフトさせるタイミングを決めるシフトクロック信号とを含んでおり、上記制御装置は、上記データイネーブル信号の入力タイミングで上記スタートパルス信号を生成開始し、上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように上記行駆動回路が上記スタートパルス信号を取り込むための上記シフトクロック信号の1クロック目を、上記入力タイミングから上記クロック信号のクロックを所定数カウントした時点で生成する構成である。

30

## 【0115】

それゆえ、行駆動回路に用いるドライバICのセットアップホールド時間に合わせて、上記クロックのカウント数を定めることができ、ドライバICの特性に応じてダミーの行ラインを駆動することができるという効果を奏する。

## 【0116】

さらに本発明の表示装置は、以上のように、上記制御装置は、1水平期間の上記表示データを上記列駆動回路に入力完了した後の水平帰線期間分の経過期間内に、上記列駆動回路が上記列駆動信号を出力するタイミングを決める上記列駆動用タイミング信号である列駆動開始タイミング信号を上記列駆動回路に入力し、上記シフトクロック信号の上記1クロック目より後のクロックを上記列駆動開始タイミング信号に合わせて上記行駆動回路に入力する構成である。

40

## 【0117】

それゆえ、シフトクロック信号の1クロック目でスタートパルス信号が取り込まれたときに、ダミーの行ラインを駆動する時間を長くすることができ、その他の行ラインの駆動時間と同等にすることができるという効果を奏する。

## 【0118】

さらに本発明の表示装置は、以上のように、上記制御装置は、入力される上記表示データを1水平期間遅延させて上記列駆動回路に入力する構成である。

## 【0119】

50

それゆえ、制御装置にデータタイネーブル信号が入力されるタイミングから列駆動回路が1垂直期間の最初の水平期間の列駆動信号を出力開始するまでの期間を長くすることができ、ダミーの行ラインを駆動する時間を容易に十分長くすることができるという効果を奏する。

【0120】

さらに本発明の表示装置は、以上のように、表示に有効な上記画素に接続された上記行ラインは1050本であり、上記行駆動回路は263個の上記行駆動信号の出力端子を備えたドライバICが4個カスケード接続されたものである構成である。

【0121】

それゆえ、使用しない出力端子が少なく、ICチップサイズの縮小および最適化が容易で10、低コスト化を図ることができるという効果を奏する。

【0122】

また、本発明の表示装置は、以上のように、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置において、上記行駆動回路はドライバICがシステム・オン・フィルム構造により実装されたものであり、所定のドライバICにおける最終の上記行ラインに対応する上記行駆動信号の出力端子の次に設けられた出力端子から、ICチップの下方を通り配線が引き回され、上記配線が上記表示パネルに設けられた最上段の上記行ラインよりもさらに上段にダミーの行ラインとして延設されている構成である。

【0123】

それゆえ、表示パネル外に行駆動回路への配線用のプリント基板が設けられていなくてもダミーの行ラインを設けることができる。そして、このダミーの行ラインの駆動は、上記所定のドライバICの出力端子を設けられている順番で駆動した後に行えばよいので、データタイネーブル信号により表示タイミングが支配されるモードで表示を行おうするときに、ダミーの行ラインを他の行ラインより先に駆動する必要がない。これにより、ドライバICには、設けられている順番で出力端子を駆動する既存のドライバICを用いることができる。

【0124】

以上により、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバICを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことが可能な表示装置を提供することができるという効果を奏する。さらに、既存のドライバICを利用することができるため、マルチベンダー化が可能であるという効果を奏する。

【0125】

また、本発明の表示駆動回路の制御装置は、以上のように、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タ

10

20

30

40

50

タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路とを備える表示駆動回路を制御する、表示駆動回路の制御装置であって、上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記列駆動回路に入力し、上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記列駆動信号を出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力する構成である。10

【0126】

それゆえ、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバI Cを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことができるという効果を奏する。

【0127】

また、本発明の表示装置の駆動方法は、以上のように、画素が行ラインと列ラインとの交差点に対応してマトリクス型に形成されている表示パネルと、上記表示パネルの上記行ラインを駆動するための行駆動用タイミング信号が入力され、上記行ラインを駆動する行駆動信号を上記行駆動用タイミング信号に基づいて、画素に接続された上記行ラインのそれぞれに順次出力する行駆動回路と、表示データと上記表示パネルの列ラインを駆動するための列駆動用タイミング信号とが入力され、画素に接続された上記列ラインに上記表示データに対応した列駆動信号を上記列駆動用タイミング信号に基づいて出力する列駆動回路と、上記表示データとデータタイネーブル信号とクロック信号とが入力され、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する制御装置とを備える表示装置を駆動する表示装置の駆動方法であって、上記データタイネーブル信号および上記クロック信号から上記行駆動用タイミング信号を生成して上記行駆動回路に入力するとともに、上記データタイネーブル信号および上記クロック信号から上記列駆動用タイミング信号を生成して上記表示データとともに上記列駆動回路に入力する表示装置の駆動方法において、上記データタイネーブル信号の入力タイミングから上記列駆動回路が1垂直期間の最初の水平期間の上記表示データを出力開始するまでの間に上記行駆動回路の最上段の上記行駆動信号の出力端子に上記行駆動信号が出力されるように、上記データタイネーブル信号の入力タイミングを基準にして上記行駆動タイミング信号を生成して上記行駆動回路に入力する構成である。30

【0128】

それゆえ、最上段にダミーの行ラインが設けられた表示パネルの行駆動を行う行駆動回路として、表示パネル外にプリント基板がない状態で配線接続された構造であって、かつ、設けられている順番で出力端子が駆動される既存のドライバI Cを用いて構成されている駆動回路を用いて、データタイネーブル信号により表示タイミングが支配されるモードで表示を行うことができる。40

【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係る液晶表示装置のタイミングコントロールA S I Cに関する信号のタイミングチャートである。

【図2】本発明の第1の実施の形態に係る液晶表示装置のタイミングコントロールA S I Cの構成を示すブロック図である。

【図3】本発明の第1の実施の形態に係る液晶表示装置のゲートドライバとその周辺との

10

20

30

40

50

構成を示す平面図である。

【図4】図3のゲートドライバに関する信号のタイミングチャートである。

【図5】本発明の第2の実施の形態に係る液晶表示装置のゲートドライバとその周辺との構成を示す平面図である。

【図6】本発明の第2の実施の形態に係る液晶表示装置のタイミングコントロールASICに関する信号のタイミングチャートである。

【図7】図5のゲートドライバに関する信号のタイミングチャートである。

【図8】本発明の第3の実施の形態に係る液晶表示装置のゲートドライバとその周辺との構成を示す平面図である。

【図9】本発明の第3の実施の形態に係る液晶表示装置のタイミングコントロールASICに関する信号のタイミングチャートである。 10

【図10】本発明の第4の実施の形態に係る液晶表示装置のタイミングコントロールASICの構成を示すブロック図である。

【図11】図11のタイミングコントロールASICに関する信号のタイミングチャートである。

【図12】本発明の第5の実施の形態に係る液晶表示装置のゲートドライバとその周辺との構成を示す平面図である。

【図13】本発明の第5の実施の形態に係る液晶表示装置のタイミングコントロールASICに関する信号のタイミングチャートである。 20

【図14】図12のゲートドライバに関する信号のタイミングチャートである。

【図15】本発明の第6の実施の形態に係る液晶表示装置のゲートドライバとその周辺との構成を示す平面図である。

【図16】本発明の第6の実施の形態に係る液晶表示装置のタイミングコントロールASICに関する信号のタイミングチャートである。

【図17】図15のゲートドライバに関する信号のタイミングチャートである。

【図18】従来の液晶表示装置の構成を示す回路ブロック図である。

【図19】図18の液晶表示装置に寄生容量が生じることを説明する画素の平面図である。

【図20】図18の液晶表示装置に生じた寄生容量による画素電極電位の変動を説明する電圧波形図である。 30

【図21】従来の液晶表示装置のゲートドライバとその周辺との第1の構成を示す平面図である。

【図22】図21のゲートドライバに関する信号のタイミングチャートである。

【図23】従来の液晶表示装置のゲートドライバとその周辺との第2の構成を示す平面図である。

【図24】図23のゲートドライバに関する信号のタイミングチャートである。

【図25】従来の液晶表示装置のゲートドライバとその周辺との第3の構成を示す平面図である。

【図26】(a)ないし(f)は、従来の液晶表示装置のHVモードでの表示動作を説明する信号のタイミングチャートである。 40

【図27】(a)ないし(f)は、従来の液晶表示装置のV-ENABLEモードでの表示動作を説明する信号のタイミングチャートである。

【図28】従来の液晶表示装置のタイミングコントロールASICの構成を示すブロック図である。

【図29】従来の液晶表示装置のゲートドライバとその周辺との第4の構成を示す平面図である。

【図30】図29のゲートドライバのドライバIC内部の構成を示すブロック図である。

【図31】図29のゲートドライバに関する信号のタイミングチャートである。

【符号の説明】

3、6、10、22、26 液晶パネル（表示パネル）

2、5、21、25 ゲートドライバ（行駆動回路）

5a ~ 5d ドライバ I C

C K クロック信号

E N A B データイネーブル信号

G ゲートライン（行ライン）

S ソースライン（列ライン）

G S P ゲートスタートパルス信号（行駆動用タイミング信号、スタートパルス信号）

G C K ゲートクロック信号（行駆動用タイミング信号、シフトクロック信号） 10

L S ラッチストローブ信号（列駆動用タイミング信号）

S C K ソースクロック信号（列駆動用タイミング信号）

S S P ソーススタートパルス信号（列駆動用タイミング信号）

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

26

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 2 2 D |

| G 0 9 G | 3/20 | 6 8 0 G |

| G 0 9 G | 3/20 | 6 8 0 H |

F ターム(参考) 2H093 NA45 NA46 NA53 NC16 NC23 NC26 NC34 ND09 ND34 ND35

ND42 ND54

5C006 AA16 AC11 AC26 AF22 AF35 AF50 AF59 AF72 BB16 BB27

BC03 BC13 BC22 BC24 BF04 BF05 BF07 BF11 BF22 BF27

BF29 EB05 FA16 FA22 FA37 FA38 FA41 FA52

5C080 AA10 BB05 DD05 DD23 DD25 DD27 FF11 GG12 JJ02 JJ03

JJ04