(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6156015号

(P6156015)

(45) 発行日 平成29年7月5日(2017.7.5)

(24) 登録日 平成29年6月16日(2017.6.16)

(51) Int.Cl.

F 1

H O 1 L 21/338 (2006.01)

H O 1 L 29/80

H

H O 1 L 29/812 (2006.01)

H O 1 L 29/778 (2006.01)

請求項の数 9 (全 8 頁)

(21) 出願番号

特願2013-197261 (P2013-197261)

(22) 出願日

平成25年9月24日 (2013.9.24)

(65) 公開番号

特開2015-65233 (P2015-65233A)

(43) 公開日

平成27年4月9日 (2015.4.9)

審査請求日

平成28年7月13日 (2016.7.13)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 岡崎 拓行

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 加茂 宣卓

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに対向する第1及び第2の主表面を持つSi基板と、

前記Si基板の前記第1の主表面上に形成され、 $A_{1-x}Ga_{1-x}N(0 \leq x \leq 1)$ からなるバッファ層と、前記バッファ層の上に形成され、 $A_{1-y}Ga_{1-y}N(0 \leq y \leq 1, x < y)$ からなるエピタキシャル結晶成長層と、

前記エピタキシャル結晶成長層に形成されたトランジスタと、

前記Si基板の前記第2の主表面から前記バッファ層に達する貫通孔に充填され、前記バッファ層と同じ組成比xの $A_{1-x}Ga_{1-x}N$ からなる充填材とを備え、

前記貫通孔及び前記充填材は、前記トランジスタのソース電極の下方には設けられておらず、前記トランジスタのゲート電極及びドレイン電極の下方に設けられていることを特徴とする半導体装置。

## 【請求項 2】

前記Si基板の前記第2の主表面から前記トランジスタのソースパッドに達するソースバイアホールの内壁と前記Si基板の前記第2の主表面に設けられ、前記ソースパッドに接続された金属膜を更に備えることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

前記Si基板はn型であり、前記トランジスタのソースパッドの直下の前記バッファ層及び前記エピタキシャル結晶成長層に設けられた開口を介して前記ソースパッドが前記S

i 基板に直接コンタクトしていることを特徴とする請求項1に記載の半導体装置。

**【請求項 4】**

前記 S i 基板は n 型であり、前記トランジスタのソース電極の直下の前記バッファ層及び前記エピタキシャル結晶成長層に設けられた開口を介して前記ソース電極が前記 S i 基板に直接コンタクトしていることを特徴とする請求項1に記載の半導体装置。

**【請求項 5】**

前記 S i 基板の抵抗率は  $10^4$  cm 以下であることを特徴とする請求項 1 ~ 4 の何れか 1 項に記載の半導体装置。

**【請求項 6】**

前記バッファ層は AlN であることを特徴とする請求項 1 ~ 5 の何れか 1 項に記載の半導体装置。 10

**【請求項 7】**

互いに対向する第 1 及び第 2 の主表面を持つ S i 基板の前記第 1 の主表面上に、  $Al_x Ga_{1-x} N$  ( $0 < x < 1$ ) からなるバッファ層を形成する工程と、

前記バッファ層の上に、  $Al_y Ga_{1-y} N$  ( $0 < y < 1, x = y$ ) からなるエピタキシャル結晶成長層を形成する工程と、

前記エピタキシャル結晶成長層にトランジスタを形成する工程と、

前記バッファ層をストッパー層として用いて、前記第 2 の主表面から前記 S i 基板をエッチングして貫通孔を形成する工程と、

前記貫通孔に前記バッファ層と同じ組成比 x の  $Al_x Ga_{1-x} N$  からなる充填材を充填する工程とを備え。 20

前記貫通孔及び前記充填材を、前記トランジスタのソース電極の下方には設けず、前記トランジスタのゲート電極及びドレイン電極の下方に設けることを特徴とする半導体装置の製造方法。

**【請求項 8】**

前記充填材を充填する工程は、

前記充填材を前記 S i 基板の前記第 2 の主面上及び前記貫通孔内に形成する工程と、

前記 S i 基板の前記第 2 の主面上に形成された前記充填材を削って平坦化する工程とを有することを特徴とする請求項7 に記載の半導体装置の製造方法。

**【請求項 9】**

前記充填材の充填にスパッタ又は CVD を用いることを特徴とする請求項7 又は 8 に記載の半導体装置の製造方法。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、 S i 基板上に設けた GaN 又は AlGaN からなるエピタキシャル結晶成長層に形成された電界効果トランジスタ、及び電界トランジスタを有する MMIC に関する。

**【背景技術】**

**【0002】**

S i 基板上に GaN 又は AlGaN からなるエピタキシャル結晶成長層を形成し、そのエピタキシャル結晶成長層に電界効果トランジスタを形成した半導体装置が知られている（例えば、特許文献 1, 2 参照）。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【特許文献 1】** 特開 2009 - 206142 号公報

**【特許文献 2】** 特開 2010 - 67662 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

従来の半導体装置では、トランジスタ部、パッド部、配線部、受動回路部の下は、数  $\mu$  m の厚みの GaN 又は AlGaN を含むエピ層を介して、100  $\mu$  m 程度の Si 基板が存在している。Si 基板の抵抗率は、高抵抗のものでも  $10^4$  cm 程度であり、高周波帯域用の半導体装置に用いられている半絶縁性 GaAs 基板や SiC 基板に比べ、4 ~ 5 衍も抵抗率が低い。このため、回路部における導体損失が大きくなってしまう。

**【0005】**

通常、半導体装置は基板裏面をグランドにするが、GaN 系エピ層は通常数  $\mu$  m 程度の厚さしかない。このため、Si 基板の抵抗率が低いと、ドレイン電極と基板裏面との間の浮遊容量 (Cds) が、通常高周波帯域用の増幅器に用いられる半絶縁性の GaAs 基板又は SiC 基板を用いた半導体装置よりも大きくなり、高周波特性が劣化する。10

**【0006】**

また、Si の熱伝導率は  $1.5 \text{ W/cm} \cdot \text{K}$  程度であり、GaN 又は AlGaN 系半導体装置の基板として用いられる SiC に比べ、熱伝導率が低い。このため、トランジスタ内部にて発生した熱が逃げにくく、半導体装置の熱抵抗が上昇してしまう。特に高出力用増幅器として用いる場合、動作時のジャンクション温度が上昇してしまい信頼性の低下を招く問題がある。

**【0007】**

このため、特許文献 1、2 では、Si 基板の一部を Si よりも絶縁性が高く、かつ熱伝導率が高い充填材で充填させることで、回路部の導体損失を低減し、トランジスタ下部における浮遊容量 (Cds など) の増大を抑制して高周波特性を向上させていた。Si 基板を残さない方が高耐圧・高周波動作できるため、これらの文献では Si 基板の裏面からエピタキシャル結晶成長層に達する貫通孔を形成し、その貫通孔に充填材を充填していた。しかし、エピタキシャル結晶成長層と充填材の格子定数が異なり、欠陥が発生するため、充填材を堆積させるのが難しいという問題があった。20

**【0008】**

本発明は、上述のような課題を解決するためになされたもので、その目的は回路部の導体損失を低減し、高周波特性と信頼性を向上させ、充填材を堆積させるのが容易な半導体装置及びその製造方法を得るものである。

**【課題を解決するための手段】****【0009】**

本発明に係る半導体装置は、互いに対向する第 1 及び第 2 の主表面上に形成され、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) からなるバッファ層と、前記バッファ層の上に形成され、 $\text{Al}_y\text{Ga}_{1-y}\text{N}$  ( $0 < y < 1$ ,  $x \neq y$ ) からなるエピタキシャル結晶成長層と、前記エピタキシャル結晶成長層に形成されたトランジスタと、前記 Si 基板の前記第 2 の主表面から前記バッファ層に達する貫通孔に充填され、前記バッファ層と同じ組成比  $x$  の  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  からなる充填材とを備え、前記貫通孔及び前記充填材は、前記トランジスタのソース電極の下方には設けられておらず、前記トランジスタのゲート電極及びドレイン電極の下方に設けられていることを特徴とする。40

**【発明の効果】****【0010】**

本発明では Si 基板の貫通孔にバッファ層と同じ組成比  $x$  の  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  からなる充填材を充填させるため、回路部の導体損失を低減し、高周波特性と信頼性を向上させ、充填材を堆積させるのが容易である。

**【図面の簡単な説明】****【0011】**

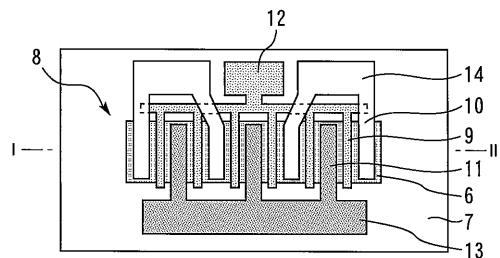

【図 1】本発明の実施の形態 1 に係る半導体装置を示す上面図である。

【図 2】図 1 の I - II に沿った断面図である。

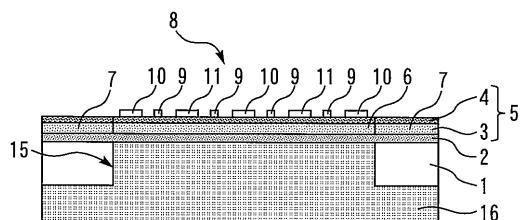

【図 3】本発明の実施の形態 2 に係る半導体装置を示す断面図である。50

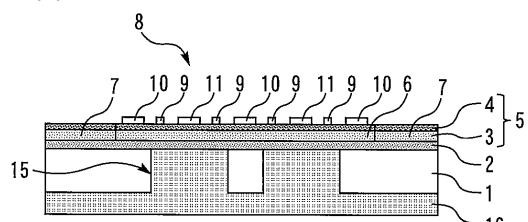

【図4】本発明の実施の形態3に係る半導体装置を示す断面図である。

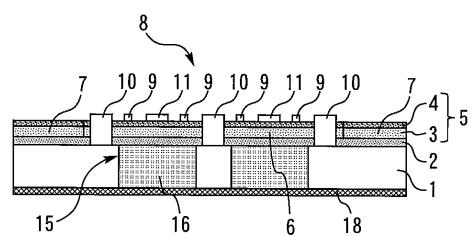

【図5】本発明の実施の形態4に係る半導体装置を示す断面図である。

【図6】本発明の実施の形態5に係る半導体装置を示す断面図である。

【図7】本発明の実施の形態6に係る半導体装置を示す断面図である。

【図8】本発明の実施の形態7に係る半導体装置を示す断面図である。

**【発明を実施するための形態】**

**【0012】**

本発明の実施の形態に係る半導体装置及びその製造方法について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

10

**【0013】**

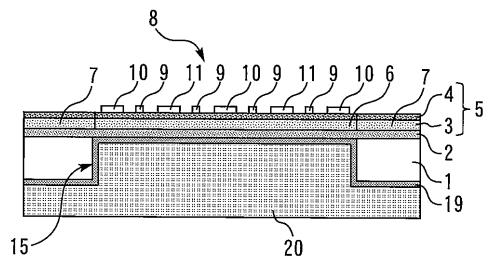

**実施の形態1.**

図1は、本発明の実施の形態1に係る半導体装置を示す上面図である。図2は図1のI-I'に沿った断面図である。Si基板1は互いに対向する第1及び第2の主表面を持つ。AlNからなるバッファ層2がSi基板1の第1の主表面上の全面に均一に形成されている。バッファ層2上に、順に積層されたGaN層3とAlGaN層4を有するエピタキシャル結晶成長層5が形成されている。

**【0014】**

エピタキシャル結晶成長層5の一部に活性層領域6が形成され、活性層領域6の周りに絶縁領域7が絶縁注入などにより形成されている。トランジスタ8がエピタキシャル結晶成長層5に形成されている。具体的には、活性層領域6上に、ゲート電極9と、その両側に配置されたソース電極10とドレイン電極11とにより一对を成す電界効果トランジスタが並列に並んでいる。これら活性層領域6と3つの電極が並列に並んだ領域にて動作領域を形成している。この動作領域を挟み対局する位置に1つ以上のゲートパッド12と1つ以上のドレインパッド13が配置されている。

20

**【0015】**

動作領域内の全てのゲート電極9は、動作領域の外側で一つにまとめられ、ゲートパッド12に接続され、同様に動作領域内の全てのドレイン電極11は、動作領域の外側で一つにまとめられ、ドレインパッド13に接続される。また、ソース電極10は、通常ゲートパッド12の横に設けられたソースパッド14に接続される。ソース電極10とソースパッド14を接続する配線電極は、ゲート電極9を束ねている配線電極上に絶縁膜及び空気を介して配置されている。

30

**【0016】**

Si基板1の第2の主表面からバッファ層2に達する貫通孔15が設けられている。この貫通孔15にAlNからなる充填材16が充填されている。なお、各層の上記の物質は一例に過ぎず、バッファ層2は $Al_xGa_{1-x}N$ (0 < x < 1)、エピタキシャル結晶成長層5は $Al_yGa_{1-y}N$ (0 < y < 1)、充填材16はバッファ層2と同じ組成比xの $Al_xGa_{1-x}N$ からなる。

**【0017】**

続いて、上記の半導体装置の製造方法を説明する。まず、Si基板1の第1の主表面上にAlNのバッファ層2を形成する。次に、バッファ層2の上にエピタキシャル結晶成長層5を形成する。次に、エピタキシャル結晶成長層5にトランジスタ8を形成する。次に、Si基板1の第2の主面において、活性層領域6の下方以外の領域をレジストでマスキングした後、バッファ層2をストッパー層として用いて、第2の主表面から活性層領域6の下のSi基板1の一部をSF6などのフッ素系ガスによりドライエッチングして貫通孔15を形成する。次に、スパッタ又はCVDを用いて、貫通孔15にAlNの充填材16を充填する。

40

**【0018】**

本実施の形態では、Si基板1の一部を除去して、Siよりも絶縁性が高く、かつ熱伝導率が高い $Al_xGa_{1-x}N$ からなる充填材16で充填する。これにより、回路部の導

50

体損失を低減し、トランジスタ下部における浮遊容量（ $C_{dS}$ など）の増大を抑制して高周波特性を向上させることができる。また、トランジスタ8内部から発生する熱を充填材16を介して効率よくパッケージの金属ベースへと放熱させることができるために、信頼性の低下を防ぐことができる。

#### 【0019】

また、充填材16はバッファ層2と同じ組成比×の $Al_xGa_{1-x}N$ からなる。従つて、バッファ層2と充填材16が格子整合しているため、充填材16の堆積が容易である。

#### 【0020】

また、従来装置では、高周波特性を少しでもよくするために、抵抗率が $10^2 \sim 10^4$  cmの高抵抗Si基板を用いていた。しかし、本実施の形態では、トランジスタ下部及び回路部、配線部の下は、絶縁性が高い材料で充填されているため、それ以外の部分でSi基板1の抵抗率が低くても、半導体装置の高周波特性には影響を与えない。そこで、Si基板1の抵抗率を $10^4$  cm以下としても、半絶縁性基板並みの優れた高周波特性を得ることができる。10

#### 【0021】

通常、高出力用の増幅器として用いられる半導体装置においては、高出力を得るために動作電圧を10V以上の高電圧状態で動作させことが多い。そこで、p型のSi基板1を用いてもよい。これにより、高電界がかかるゲート・ドレイン間に発生したホールをソース電極10の下のp型のSi基板1から短距離にて裏面に引き抜くことができる。よって、高電界印加時にトランジスタ内部で生じたホールが、特にゲート電極9下のエピタキシャル結晶成長層内に溜まるのを抑制できる。この結果、活性層領域6にて均一に信頼性の向上を図ることができる。20

#### 【0022】

また、窒化物のバッファ層2をストッパー層として用いてSi基板1をエッチングすることで、貫通孔15の形成が容易になる。

#### 【0023】

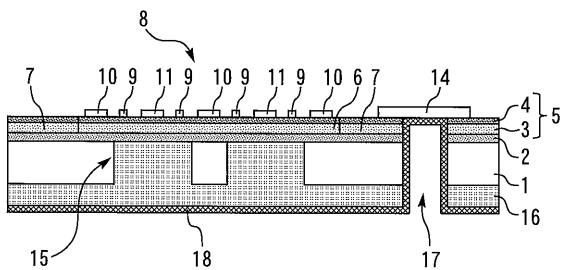

実施の形態2.

図3は、本発明の実施の形態2に係る半導体装置を示す断面図である。本実施の形態では、貫通孔15及び充填材16は、ソース電極10の下方には設けられておらず、トランジスタ8のドレイン電極11の下方に設けられている。30

#### 【0024】

高周波特性の劣化の原因となるのは、ドレイン電極11と基板裏面との間の容量 $C_{dS}$ の増大であるため、ドレイン電極11においてSi基板1の一部を除去して充填材16で置き換えるべきである。これにより、実施の形態1と同様に高周波特性を向上することができる。さらに、充填材16として堆積するAlN層の厚みは実施の形態1では数μm程度であるが、本実施の形態では更に薄くすることができるため、充填材16の形成が容易である。

#### 【0025】

実施の形態3.

図4は、本発明の実施の形態3に係る半導体装置を示す断面図である。Si基板1の第2の主表面からトランジスタ8のソースパッド14に達するソースバイアホール17が絶縁領域7に設けられている。Auメッキなどの金属膜18が、ソースバイアホール17の内壁とSi基板1の第2の主表面に設けられ、ソースパッド14に接続されている。金属膜18により接地点までの距離を減らすことができるため、ソースインダクタンスを低減し、高周波特性を向上させることができる。40

#### 【0026】

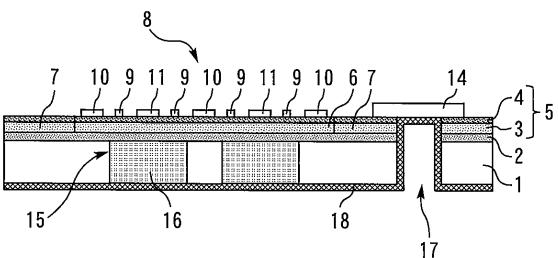

実施の形態4.

図5は、本発明の実施の形態4に係る半導体装置を示す断面図である。充填材16を充填する際に、まず充填材16をSi基板1の第2の主面上及び貫通孔15内に形成する。

次に、S i 基板 1 の第 2 の主表面に形成された充填材 1 6 を研削又は C M Pなどを用いて削って平坦化する。ドレイン電極 1 1 下のみ充填材 1 6 を埋めこんだ状態でソースバイアホール 1 7 を形成する。基板裏面の余分な A 1 N を削り取ることでフラットな裏面を形成できるため、アセンブリ性に優れた半導体装置を得ることができる。

【0027】

実施の形態 5 .

図 6 は、本発明の実施の形態 5 に係る半導体装置を示す断面図である。n 型の S i 基板 1 を用いる。絶縁領域 7 内のソースパッド 1 4 の直下のバッファ層 2 及びエピタキシャル結晶成長層 5 に設けられた開口を介してソースパッド 1 4 が n 型の S i 基板 1 に直接コンタクトしている。これにより、表面のソースパッド 1 4 は n 型の S i 基板 1 を介して基板裏面の金属膜 1 8 と接続されるため、ソースバイアホール 1 7 が不要となる。よって、実施の形態 4 と同様の効果を得つつ、半導体装置作製工程を簡略化することができる。10

【0028】

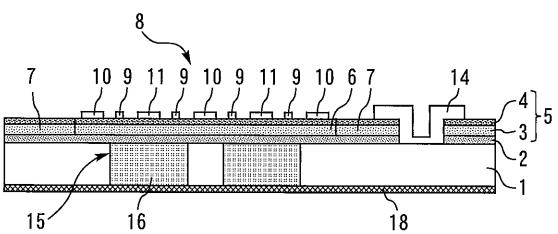

実施の形態 6 .

図 7 は、本発明の実施の形態 6 に係る半導体装置を示す断面図である。n 型の S i 基板 1 を用いる。活性層領域 6 内の各ソース電極 1 0 の直下のバッファ層 2 及びエピタキシャル結晶成長層 5 に設けられた開口を介してソース電極 1 0 が n 型の S i 基板 1 に直接コンタクトしている。これにより、表面のソース電極 1 0 は n 型の S i 基板 1 を介して基板裏面の金属膜 1 8 と接続されるため、絶縁領域 7 のソースパッド 1 4 が不要となり、チップパターンを縮小化できる。また、各ソース電極 1 0 から最短距離にて金属膜 1 8 までの導通が図れる。これにより、配線ロス、インダクタンスを低減することができ、更に高周波特性を向上させることができる。20

【0029】

実施の形態 7 .

図 8 は、本発明の実施の形態 7 に係る半導体装置を示す断面図である。実施の形態 1 の A 1 N からなる充填材 1 6 の代わりに、貫通孔 1 5 内に 1 層目にダイヤモンド薄膜 1 9 、2 層目に A 1 N 又は C u の充填材 2 0 を充填する。ダイヤモンドは半導体の中でも優れた絶縁性と熱伝導性を持つ。このため、高周波特性を更に向上させ、かつトランジスタ 8 内部から発生する熱を効率よく放熱させることができる。なお、ダイヤモンドだけで貫通孔 1 5 を埋め込むと費用がかかるので、2 層目に A 1 N 又は C u の充填材 2 0 を堆積させていいる。30

【符号の説明】

【0030】

1 S i 基板、2 バッファ層、5 エピタキシャル結晶成長層、8 トランジスタ、1

0 ソース電極、1 1 ドレイン電極、1 4 ソースパッド、1 5 貫通孔、1 6 , 2 0

充填材、1 7 ソースバイアホール、1 8 金属膜、1 9 ダイヤモンド薄膜

【 図 1 】

【図2】

( 3 )

【 図 7 】

【図8】

【図4】

【図5】

【 四 6 】

【 図 1 】

---

フロントページの続き

(72)発明者 野上 洋一

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 小山 英寿

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 宮國 晋一

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

審査官 棚田 一也

(56)参考文献 特開2013-008969(JP,A)

特開2010-098251(JP,A)

特開2001-274174(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/338

H01L 29/778

H01L 29/812