2020년10월08일

# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**G06F 12/02** (2018.01) **G06F 3/06** (2006.01)

(52) CPC특허분류

**G06F 12/0253** (2013.01) **G06F 12/0246** (2013.01)

(21) 출원번호 10-2019-0035088

(22) 출원일자 **2019년03월27일**

심사청구일자 없음

(11) 공개번호 10-2020-0115831

(四1) さのる

(71) 출원인

(43) 공개일자

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

나형주

경기도 용인시 기흥구 이현로29번길 72-1 성호샤 인힐즈아파트 133동 401호

박진

경기도 성남시 중원구 원터로69 8-1

(74) 대리인

김성남

전체 청구항 수 : 총 18 항

# (54) 발명의 명칭 컨트롤러, 메모리 시스템 및 그것의 동작 방법

#### (57) 요 약

본 발명은 반도체 장치에 관한 것으로, 보다 구체적으로는 컨트롤러, 메모리 시스템 및 그것의 동작 방법에 관한 것이다 본 발명의 일 실시예에 따르면, 각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치 및 불휘발성 메모리 장치를 제어하는 컨트롤러를 포함하는 메모리 시스템으로서, 컨트롤러는 복수의 슈퍼 블록 중 데이터의 쓰기 및 데이터 리드 성능 중 적어도 하나가 저하된 슈퍼 블록인 성능 저하 슈퍼 블록의 개수를 기반으로 불휘발성 메모리 장치의 더티 상태(Dirty State)를 판단하기 위한 더티 상태 임계값을 결정하고, 복수의 슈퍼 블록 중 쓰기 동작을 위해 할당 가능한 프리 슈퍼 블록들의 개수를 더티 상태 임계값과 비교하여 불휘발성 메모리 장치의 더티 상태 여부를 판단하여, 더티 상태로 판단되면 불휘발성 메모리 장치에 대해 가비지 컬렉션을 수행하는 메모리 시스템이 제공된다.

#### 대 표 도 - 도5

(52) CPC특허분류

**G06F 3/0658** (2013.01) G06F 2212/7205 (2013.01)

#### 명 세 서

#### 청구범위

#### 청구항 1

각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치 및 상기 불휘발성 메모리 장치를 제어하는 컨트롤러를 포함하는 메모리 시스템으로서,

상기 컨트롤러는,

상기 복수의 슈퍼 블록 중 데이터의 쓰기 및 데이터 리드 성능 중 적어도 하나가 저하된 슈퍼 블록인 성능 저하 슈퍼 블록의 개수를 기반으로 상기 불휘발성 메모리 장치의 더티 상태(Dirty State)를 판단하기 위한 더티 상태 임계값을 결정하고,

상기 복수의 슈퍼 블록 중 쓰기 동작을 위해 할당 가능한 프리 슈퍼 블록들의 개수를 상기 더티 상태 임계값과 비교하여 상기 불휘발성 메모리 장치의 더티 상태 여부를 판단하여,

상기 더티 상태로 판단되면 상기 불휘발성 메모리 장치에 대해 가비지 컬렉션을 수행하는 메모리 시스템.

### 청구항 2

제 1 항에 있어서,

상기 컨트롤러는,

상기 성능 저하 슈퍼 블록의 개수의 개수가 증가할수록 상기 더티 상태 임계값을 크게 결정하는 메모리 시스템.

#### 청구항 3

제 1 항에 있어서,

상기 컨트롤러는,

상기 성능 저하 슈퍼 블록의 개수가 적을수록 상기 더티 상태 임계값을 작게 결정하는 메모리 시스템.

#### 청구항 4

제 1 항에 있어서.

상기 성능 저하 슈퍼 블록은,

상기 성능 저하 슈퍼 블록을 구성하는 복수의 메모리 블록 중 적어도 하나가 인터리빙이 불가능한 슈퍼 블록인 것을 특징으로 하는 메모리 시스템.

#### 청구항 5

제 1 항에 있어서,

상기 성능 저하 슈퍼 블록은,

상기 복수의 슈퍼 블록 중 정상 슈퍼 블록 보다 작은 수의 메모리 블록을 포함하는 슈퍼 블록인 것을 특징으로 하는 메모리 시스템.

#### 청구항 6

제 1 항에 있어서,

상기 성능 저하 슈퍼 블록은,

상기 복수의 슈퍼 블록 중 정상 슈퍼 블록 보다 저장할 수 있는 데이터의 크기가 작은 슈퍼 블록인 것을 특징으로 하는 메모리 시스템.

#### 청구항 7

제 1 항에 있어서,

상기 컨트롤러는,

상기 가비지 컬렉션 동작을 우선적으로 수행하도록 상기 불휘발성 메모리 장치를 제어하는 메모리 시스템.

#### 청구항 8

제 1 항에 있어서,

상기 컨트롤러는,

상기 프리 슈퍼 블록들의 개수가 상기 더티 상태 임계값 미만이면, 상기 더티 상태로 판단하는 메모리 시스템.

#### 청구항 9

제 1 항에 있어서,

상기 컨트롤러는,

상기 프리 슈퍼 블록들의 개수가 상기 더티 상태 임계값 이상이면, 상기 더티 상태가 아닌 것으로 판단하는 메모리 시스템.

#### 청구항 10

각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치 및 상기 불휘발성 메모리 장치를 제어하는 컨트롤러를 포함하는 메모리 시스템의 동작 방법으로서,

상기 컨트롤러가 상기 복수의 슈퍼 블록 중 데이터의 쓰기 및 데이터 리드 성능 중 적어도 하나가 저하된 슈퍼 블록인 성능 저하 슈퍼 블록의 개수를 기반으로 상기 불휘발성 메모리 장치의 더티 상태(Dirty State)를 판단하 기 위한 더티 상태 임계값을 결정하는 단계;

상기 컨트롤러가 상기 복수의 슈퍼 블록 중 쓰기 동작을 위해 할당 가능한 프리 슈퍼 블록들의 개수를 상기 더 티 상태 임계값과 비교하여 상기 불휘발성 메모리 장치의 더티 상태 여부를 판단하는 단계; 및

상기 더티 상태로 판단되면 상기 불휘발성 메모리 장치가 상기 복수의 슈퍼 블록에 대해 가비지 컬렉션 동작을 수행하는 단계

를 포함하는 메모리 시스템 동작 방법.

#### 청구항 11

제 10 항에 있어서,

상기 더티 상태 임계값을 결정하는 단계는,

상기 성능 저하 슈퍼 블록의 개수의 개수가 증가할수록 상기 더티 상태 임계값을 크게 결정하는 메모리 시스템 동작 방법.

#### 청구항 12

제 10 항에 있어서,

상기 더티 상태 임계값을 결정하는 단계는,

상기 성능 저하 슈퍼 블록의 개수가 적을수록 상기 더티 상태 임계값을 작게 결정하는 메모리 시스템 동작 방법.

#### 청구항 13

제 10 항에 있어서,

상기 성능 저하 슈퍼 블록은,

상기 성능 저하 슈퍼 블록을 구성하는 복수의 메모리 블록 중 적어도 하나가 인터리빙이 불가능한 슈퍼 블록인 것을 특징으로 하는 메모리 시스템 동작 방법.

#### 청구항 14

제 10 항에 있어서,

상기 성능 저하 슈퍼 블록은,

상기 복수의 슈퍼 블록 중 정상 슈퍼 블록 보다 작은 수의 메모리 블록을 포함하는 슈퍼 블록인 것을 특징으로 하는 메모리 시스템 동작 방법.

#### 청구항 15

제 10 항에 있어서,

상기 성능 저하 슈퍼 블록은,

상기 복수의 슈퍼 블록 중 정상 슈퍼 블록 보다 저장할 수 있는 데이터의 크기가 작은 슈퍼 블록인 것을 특징으로 하는 메모리 시스템 동작 방법.

#### 청구항 16

제 10 항에 있어서,

상기 가비지 컬렉션 동작을 수행하는 단계는,

쓰기 커맨드 및 리드 커맨드에 우선하여 수행되는 것을 특징으로 하는 메모리 시스템 동작 방법.

#### 청구항 17

제 10 항에 있어서,

상기 더티 상태 여부를 판단하는 단계는,

상기 프리 슈퍼 블록들의 개수가 상기 더티 상태 임계값 미만이면, 상기 더티 상태로 판단하는 메모리 시스템 동작 방법.

#### 청구항 18

제 10 항에 있어서,

상기 더티 상태 여부를 판단하는 단계는,

상기 프리 슈퍼 블록들의 개수가 상기 더티 상태 임계값 이상이면, 상기 더티 상태가 아닌 것으로 판단하는 메모리 시스템 동작 방법.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 반도체 장치에 관한 것으로, 보다 구체적으로는 컨트롤러, 메모리 시스템 및 그것의 동작 방법에 관한 것이다.

#### 배경기술

- [0002] 최근 컴퓨터 환경에 대한 패러다임(paradigm)이 언제, 어디서나 컴퓨터 시스템을 사용할 수 있도록 하는 유비쿼터스 컴퓨팅(ubiquitous computing)으로 전환되고 있다. 이로 인해 휴대폰, 디지털 카메라, 노트북 컴퓨터 등과 같은 휴대용 전자 장치의 사용이 급증하고 있다. 이와 같은 휴대용 전자 장치는 일반적으로 메모리 장치를 이용하는 메모리 시스템을 사용한다. 메모리 시스템은 휴대용 전자 장치에서 사용되는 데이터를 저장하기 위해서 사용된다.

- [0003] 메모리 장치를 이용한 메모리 시스템은 기계적인 구동부가 없어서 안정성 및 내구성이 뛰어나며 정보의 액세스

속도가 매우 빠르고 전력 소모가 적다는 장점이 있다. 이러한 장점을 갖는 메모리 시스템은 USB(Universal Serial Bus) 메모리 장치, 다양한 인터페이스를 갖는 메모리 카드, UFS(Universal Flash Storage) 장치, 솔리드 스테이트 드라이브(Solid State Drive)를 포함한다.

### 발명의 내용

### 해결하려는 과제

[0004] 본 발명의 일 실시예는 메모리 시스템의 데이터 처리 성능을 향상시키는 기술을 제공하고자 한다.

#### 과제의 해결 수단

- [0005] 본 발명의 일 실시예에 따르면, 각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치 및 불휘발성 메모리 장치를 제어하는 컨트롤러를 포함하는 메모리 시스템으로서, 컨트롤러는 복수의 슈퍼 블록 중 데이터의 쓰기 및 데이터 리드 성능 중 적어도 하나가 저하된 슈퍼 블록인 성능 저하 슈퍼 블록의 개수를 기반으로 불휘발성 메모리 장치의 더티 상태(Dirty State)를 판단하기 위한 더티 상태 임계값을 결정하고, 복수의 슈퍼 블록 중 쓰기 동작을 위해 할당 가능한 프리 슈퍼 블록들의 개수를 더티 상태 임계값과 비교하여 불휘발성 메모리 장치의 더티 상태 여부를 판단하여, 더티 상태로 판단되면 불휘발성 메모리 장치에 대해 가비지 컬렉션을 수행하는 메모리 시스템이 제공된다.

- [0006] 본 발명의 일 실시예에 따르면, 각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치 및 불휘발성 메모리 장치를 제어하는 컨트롤러를 포함하는 메모리 시스템의 동작 방법으로서, 컨트롤러가 복수의 슈퍼 블록 중 데이터의 쓰기 및 데이터 리드 성능 중 적어도 하나가 저하된 슈퍼 블록인 성능 저하 슈퍼 블록의 개수를 기반으로 불휘발성 메모리 장치의 더티 상태(Dirty State)를 판단하기 위한 더티 상태 임계값을 결정하는 단계, 컨트롤러가 복수의 슈퍼 블록 중 쓰기 동작을 위해 할당 가능한 프리 슈퍼 블록들의 개수를 더티 상태 임계값과 비교하여 불휘발성 메모리 장치의 더티 상태 여부를 판단하는 단계 및 더티 상태로 판단되면 불휘발성 메모리 장치가 복수의 슈퍼 블록에 대해 가비지 컬렉션 동작을 수행하는 단계를 포함하는 메모리 시스템 동작 방법이 제공된다.

## 발명의 효과

[0007] 본 발명의 일 실시예에 따르면, 메모리 시스템의 데이터 처리 성능을 향상 시키는 것이 가능하게 된다.

#### 도면의 간단한 설명

[0008] 도 1은 본 발명의 실시 예에 따른 메모리 시스템의 구성을 예시적으로 나타낸 도면.

도 2는 본 발명의 일 실시예에 따른 불휘발성 메모리 장치에 포함된 데이터 저장 영역을 설명하기 위한 도면.

도 3 a 내지 3 d는 본 발명의 일 실시예에 따른 메모리 시스템의 동작을 설명하기 위한 도면.

도 4는 본 발명의 일 실시예에 따른 플래시 변환 계층을 설명하기 위한 도면.

도 5는 본 발명의 일 실시예에 따른 메모리 시스템의 동작을 설명하기 위한 도면.

도 6은 본 발명의 실시 예에 따른 솔리드 스테이트 드라이브(SSD)를 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면.

도 7은 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면.

도 8은 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면.

도 9는 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 네트워크 시스템을 예시적으로 나타낸 도면.

#### 발명을 실시하기 위한 구체적인 내용

[0009] 본 발명의 이점 및 특징, 그리고 그것을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 통해 설명될 것이다. 그러나 본 발명은 여기에서 설명되는 실시 예들에 한정되지 않고 다른 형태로 구체 화될 수도 있다. 단지, 본 실시 예들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여 제공되는 것이다.

- [0010] 명세서 전체에서, 어떤 부분이 다른 부분과 "연결"되어 있다고 할 때, 이는 "직접적으로 연결"되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 "간접적으로 연결"되어 있는 경우도 포함한다. 명세서 전체에서, 어떤 부분이 어떤 구성요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있는 것을 의미한다.

- [0011] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시 예들을 상세히 설명한다. 이 때, 첨부된 도면에서 동일한 구성 요소는 가능한 동일한 부호로 나타내고 있음에 유의해야 한다. 또한 본 발명의 요지를 흐리게 할 수 있는 공지 기능 및 구성에 대한 상세한 설명은 생략할 것이다.

- [0012] 이하, 첨부한 도면에 의거하여 본 발명의 바람직한 실시 예를 설명하도록 한다.

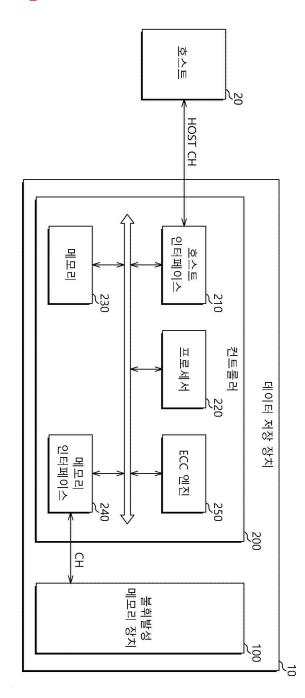

- [0013] 도 1은 본 발명의 실시 예에 따른 메모리 시스템(10)의 구성을 예시적으로 나타낸 도면이다.

- [0014] 도 1을 참조하면, 본 실시 예에 따른 메모리 시스템(10)은 휴대폰, MP3 플레이어, 랩탑 컴퓨터, 데스크탑 컴퓨터, 게임기, TV, 차량용 인포테인먼트(in-vehicle infotainment) 시스템 등과 같은 호스트(20)에 의해서 액세스되는 데이터를 저장할 수 있다.

- [0015] 메모리 시스템(10)은 호스트(20)와 연결되는 인터페이스 프로토콜에 따라서 다양한 종류의 저장 장치들 중 어느하나로 제조될 수 있다. 예를 들어, 메모리 시스템(10)은 솔리드 스테이트 드라이브(solid state drive, SSD), MMC, eMMC, RS-MMC, micro-MMC 형태의 멀티미디어 카드(multimedia card), SD, mini-SD, micro-SD 형태의 시큐어 디지털(secure digital) 카드, USB(universal storage bus) 저장 장치, UFS(universal flash storage) 장치, PCMCIA(personal computer memory card international association) 카드 형태의 저장 장치, PCI(peripheral component interconnection) 카드 형태의 저장 장치, PCI-E(PCI-express) 카드 형태의 저장 장치, CF(compact flash) 카드, 스마트 미디어(smart media) 카드, 메모리 스틱(memory stick) 등과 같은 다양한 종류의 저장 장치들 중 어느 하나로 구성될 수 있다.

- [0016] 메모리 시스템(10)은 다양한 종류의 패키지(package) 형태들 중 어느 하나로 제조될 수 있다. 예를 들어, 메모리 시스템(10)은 POP(package on package), SIP(system in package), SOC(system on chip), MCP(multi-chip package), COB(chip on board), WFP(wafer-level fabricated package), WSP(wafer-level stack package) 등과 같은 다양한 종류의 패키지 형태들 중 어느 하나로 제조될 수 있다.

- [0017] 메모리 시스템(10)은 불휘발성 메모리 장치(100) 및 컨트롤러(200)를 포함할 수 있다.

- [0018] 불휘발성 메모리 장치(100)는 메모리 시스템(10)의 저장 매체로서 동작할 수 있다. 불휘발성 메모리 장치(100)는 메모리 셀에 따라서 낸드(NAND) 플래시 메모리 장치, 노어(NOR) 플래시 메모리 장치, 강유전체 커패시터를 이용한 강유전체 램(ferroelectric random access memory, FRAM), 티엠알(tunneling magneto-resistive, TMR) 막을 이용한 마그네틱 램(magnetic random access memory, MRAM), 칼코겐 화합물(chalcogenide alloys)을 이용한 상 변화 램(phase change random access memory, PRAM), 전이 금속 화합물(transition metal oxide)을 이용한 저항성 램(resistive random access memory, ReRAM) 등과 같은 다양한 형태의 불휘발성 메모리 장치들 중어느 하나로 구성될 수 있다.

- [0019] 도 1에서는 메모리 시스템(10)이 하나의 불휘발성 메모리 장치(100)를 포함하는 것으로 도시하였으나, 이는 설명의 편의를 위한 것으로, 메모리 시스템(10)은 복수의 불휘발성 메모리 장치들을 포함할 수 있으며, 본 발명은 복수의 불휘발성 메모리 장치들을 포함하는 메모리 시스템(10)에 대해서도 동일하게 적용될 수 있다.

- [0020] 불휘발성 메모리 장치(100)는 복수의 비트라인들(도시되지 않음) 및 복수의 워드라인들(도시되지 않음)이 교차하는 영역들에 각각 배치되는 복수의 메모리 셀들을 갖는 메모리 셀 어레이(도시되지 않음)를 포함할 수 있다. 메모리 셀 어레이는 복수의 메모리 블록들을 포함할 수 있고, 복수의 메모리 블록들은 각각 복수의 데이터 페이지들을 포함할 수 있다.

- [0021] 예를 들어, 메모리 셀 어레이의 각 메모리 셀은 1 비트의 데이터를 저장하는 싱글 레벨 셀(single, level cell, SLC), 2 비트 이상의 데이터를 저장할 수 있는 멀티 레벨 셀(multi level cell, MLC)일 수 있다. 멀티 레벨 셀(MLC)은 2 비트의 데이터, 3 비트의 데이터, 4 비트의 데이터 등을 저장할 수 있다. 일반적으로, 2 비트의 데이터를 저장하는 메모리 셀을 멀티 레벨 셀(MLC)이라 하고, 3 비트의 데이터를 저장하는 메모리 셀을 트리플 레벨 셀(triple level cell, TLC)이라 하고, 4 비트의 데이터를 저장하는 메모리 셀을 쿼드 레벨 셀(quad level cell, QLC)이라 한다. 그러나, 본 실시 예에서는 설명의 편의를 위해 2 비트 내지 4 비트의 데이터를 저장하는 메모리 셀을 통칭하여 멀티 레벨 셀(MLC)이라 할 것이다.

- [0022] 일 실시예에서, 복수의 데이터 페이지는 하나의 데이터 페이지 그룹을 구성할 수 있다. 예를 들어, 데이터 페이지 그룹이 복수의 메모리 셀로 구성되고 각 메모리 셀이 N 개의 비트를 저장할 수 있으면, 데이터 페이지 그룹은 N 개의 데이터 페이지를 포함할 수 있다. 즉, 데이터 페이지 그룹을 구성하는 메모리 셀 각각이 2 개의 비트를 저장할 수 있는 MLC인 경우, 데이터 페이지 그룹은 LSB(Least Significant Bit) 페이지 및 MSB(Most Significant Bit) 페이지를 포함할 수 있다. 또한, 데이터 페이지 그룹을 구성하는 메모리 셀 각각이 3 개의 비트를 저장할 수 있는 TLC인 경우, 데이터 페이지 그룹은 LSB 페이지, CSB(Center Significant Bit) 페이지 및 MSB 페이지를 포함할 수 있다.

- [0023] 메모리 셀 어레이는 싱글 레벨 셀(SLC) 및 멀티 레벨 셀(MLC) 중 적어도 하나 이상을 포함할 수 있다. 또한, 메모리 셀 어레이는 2차원 수평 구조의 메모리 셀들을 포함할 수도 있고, 또는 3차원 수직 구조의 메모리 셀들을 포함할 수도 있다.

- [0024] 컨트롤러(200)는 메모리(230)에 로딩된 펌웨어 또는 소프트웨어의 구동을 통해서 메모리 시스템(10)의 제반 동작을 제어할 수 있다. 컨트롤러(200)는 펌웨어 또는 소프트웨어와 같은 코드 형태의 명령(instruction) 또는 알고리즘을 해독하고 구동할 수 있다. 컨트롤러(200)는 하드웨어, 또는 하드웨어와 소프트웨어가 조합된 형태로구현될 수 있다.

- [0025] 컨트롤러(200)는 호스트 인터페이스(210), 프로세서(220), 메모리(230), 메모리 인터페이스(240) 및 ECC 엔진 (250)을 포함할 수 있다.

- [0026] 호스트 인터페이스(210)는 호스트(20)의 프로토콜에 대응하여 호스트(20)와 메모리 시스템(10) 사이를 인터페이 성할 수 있다. 예를 들어, 호스트 인터페이스(210)는 시큐어 디지털(secure digital), USB(universal serial bus), MMC(multi-media card), eMMC(embedded MMC), PCMCIA(personal computer memory card international association), PATA(parallel advanced technology attachment), SATA(serial advanced technology attachment), SCSI(small computer system interface), SAS(serial attached SCSI), PCI(peripheral component interconnection), PCI-E(PCI Expresss), UFS(universal flash storage) 프로토콜 중 어느 하나를 통해 호스트(20)와 통신할 수 있다. 또한, 호스트 인터페이스 유닛(2211)은 호스트(2100)가 SSD(2200)를 범용 메모리 시스템, 예를 들면, 하드 디스크 드라이브(HDD)로 인식하도록 지원하는 디스크 에뮬레이션(disk emulation) 기능을 수행할 수 있다.

- [0027] 프로세서(220)는 마이크로 컨트롤 유닛(micro control unit)(MCU), 중앙 처리 장치(central processing unit)(CPU)로 구성될 수 있다. 프로세서(220)는 호스트(20)로부터 전송된 요청을 처리할 수 있다. 호스트(20)로부터 전송된 요청을 처리하기 위해서, 프로세서(220)는 메모리(230)에 로딩된 코드 형태의 명령(instruction) 또는 알고리즘, 즉, 펌웨어를 구동하고, 호스트 인터페이스(210), 메모리(230) 및 메모리 인터페이스(240) 등과 같은 내부 기능 블록들 및 불휘발성 메모리 장치(100)를 제어할 수 있다.

- [0028] 프로세서(220)는 호스트(20)로부터 전송된 요청들에 근거하여 불휘발성 메모리 장치(100)의 동작을 제어할 제어 신호들을 생성하고, 생성된 제어 신호들을 메모리 인터페이스(240)를 통해 불휘발성 메모리 장치(100)로 제공할 수 있다. 또한, 프로세서(220)는 호스트(2100)로부터 입력된 신호(SGL)를 분석하고 처리할 수 있다. 컨트롤 유 닛(2212)은 SSD(2200)를 구동하기 위한 펌웨어 또는 소프트웨어에 따라서 내부 기능 블럭들의 동작을 제어할 수 있다.

- [0029] 메모리(230)는 랜덤 액세스 메모리(RAM)으로 구성 되어 있고 컨트롤러(200) 내부에 있을 수도 있고 외부에 있을 수도 있다. 메모리(230)는 프로세서(220)에 의해서 구동되는 펌웨어를 저장할 수 있다. 또한, 메모리(230)는 펌웨어의 구동에 필요한 데이터, 예를 들면, 메타 데이터를 저장할 수 있다. 즉, 메모리(230)는 프로세서(220)의 동작 메모리(working memory)로서 동작할 수 있다. 또한, 메모리(230)는 호스트(20)로부터 불휘발성 메모리 장치(100)로 전송될 쓰기 데이터 또는 불휘발성 메모리 장치(100)로부터 호스트(20)로 전송될 읽기 데이터를 임시저장하기 위한 데이터 버퍼(data buffer)를 포함하도록 구성될 수 있다. 즉, 메모리(230)는 버퍼 메모리(buffer memory)로서 동작할 수 있다.

- [0030] 메모리 인터페이스(240)는 프로세서(220)의 제어에 따라 불휘발성 메모리 장치(100)를 제어할 수 있다. 메모리 인터페이스(240)는 메모리 컨트롤러로도 불릴 수 있다. 메모리 인터페이스(240)는 제어 신호들을 불휘발성 메모리 장치(100)로 제공할 수 있다. 제어 신호들은 불휘발성 메모리 장치(100)를 제어하기 위한 커맨드, 어드레스, 동작 제어 신호 등을 포함할 수 있다. 메모리 인터페이스(240)는 데이터 버퍼에 저장된 데이터를 불휘발성 메모리 장치(100)로 제공하거나, 불휘발성 메모리 장치(100)로부터 전송된 데이터를 데이터 버퍼에 저장할 수 있다.

- [0031] ECC 엔진(250)은 호스트(20)로부터 제공된 쓰기 데이터를 ECC(error correction code) 인코딩하여 패리티 (parity)를 생성할 수 있다. 이때, 불휘발성 메모리는 패리티가 부가된 쓰기 데이터를 저장할 수 있다. 또한, ECC 엔진(250)은 불휘발성 메모리 장치(100)로부터 리드된 읽기 데이터를 패리티(parity)를 이용하여 ECC(error correction code) 디코딩함으로써, 패리티가 제거된 읽기 데이터를 생성할 수 있다.

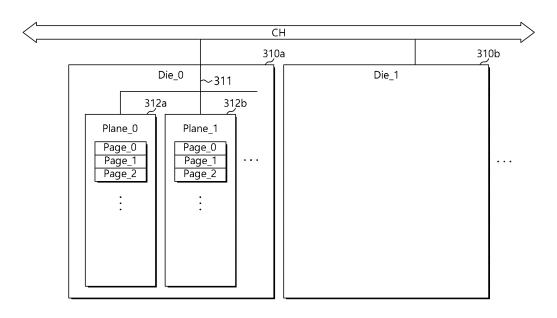

- [0032] 도 2는 본 발명의 일 실시예에 따른 불휘발성 메모리 장치에 포함된 데이터 저장 영역을 설명하기 위한 도면이다.

- [0033] 도 2를 참조하면, 불휘발성 메모리 장치(100)는 컨트롤러(200)와 연결되는 채널을 공유하는 복수의 다이 (Die)(310a, 310b)를 포함할 수 있으며, 각 다이는 채널과 연결되는 웨이(way)(311)를 공유하는 다수의 플레인 (plain)(312a, 312b)를 포함할 수 있고, 각 플레인은 복수의 데이터 페이지를 포함할 수 있다. 여기서, 데이터 페이지는 데이터를 읽거나 쓰는 최소 단위의 저장 영역을 의미할 수 있다. 또한, 소거 동작이 일괄적으로 이뤄지는 복수의 데이터 페이지 단위를 블록이라 하며, 하나로 관리되는 복수의 블록 단위를 슈퍼 블록이라고 한다. 따라서, 불휘발성 메모리 장치(100)에서 데이터 저장 영역은, 다이, 플레인, 슈퍼 블록, 블록, 데이터 페이지 등을 의미할 수 있으나, 이하 별도의 언급이 없는 한 데이터 저장 영역은 데이터 페이지를 의미하는 것을 예시로 설명한다.

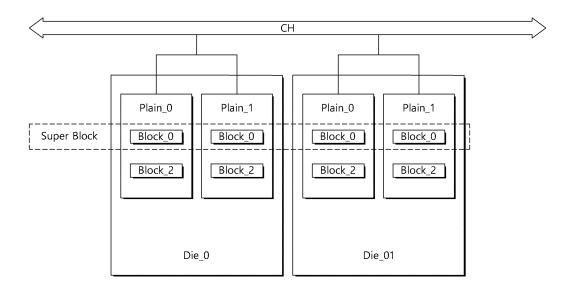

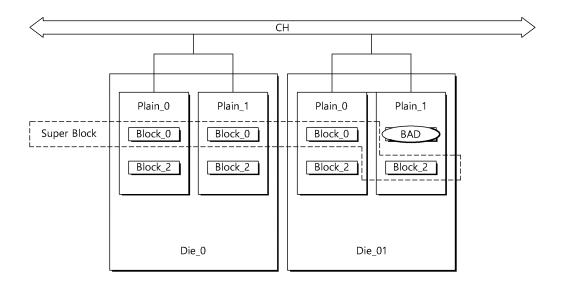

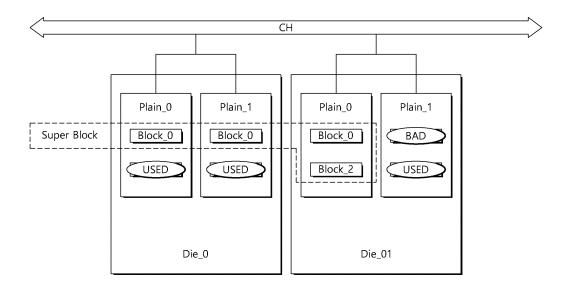

- [0034] 도 3 a 내지 3 d는 본 발명의 일 실시예에 따른 메모리 시스템의 동작을 설명하기 위한 도면이다.

- [0035] 도 3 a를 참조하면, 각각 두 개의 플레인(Plain\_0, Plain\_1)으로 구성된 두 개의 다이(Die\_0, Die\_1)을 포함하고, 여기서 각 플레인은 두 개의 메모리 블록(Block\_0, Block\_1)을 포함하는 불휘발성 메모리 장치의 예가 도시되어 있다. 도 3 a에 도시된 각 플레인의 첫 번째 메모리 블록(Block\_0)들은 하나의 그룹인 슈퍼 블(Super Block)록으로 관리될 수 있다. 이는 이하 설명할 정상 슈퍼 블록의 일 예에 해당할 수 있다.

- [0036] 도 3 b를 참조하면, 슈퍼 블록을 구성하는 메모리 블록 중 다이 1의 플레인 1에 포함된 첫 번째 메모리 블록이 배드 블록으로 된 경우, 배드 블록을 다이 1의 플레인 1에 포함된 두 번째 메모리 블록(Block\_2)로 대체한 슈퍼블록의 예가 도시되어 있다. 이 경우, 다이 1의 플레인 1에 포함된 두 번째 메모리 블록(Block\_2)은 다른 플레인에 포함된 첫 번재 메모리 블록과 인터리빙이 가능하므로, 쓰기 동작이나 리드 동작시 성능 저하가 발생하지 않을 수 있다. 이는 이하 설명할 정상 슈퍼 블록의 일 예에 해당할 수 있다.

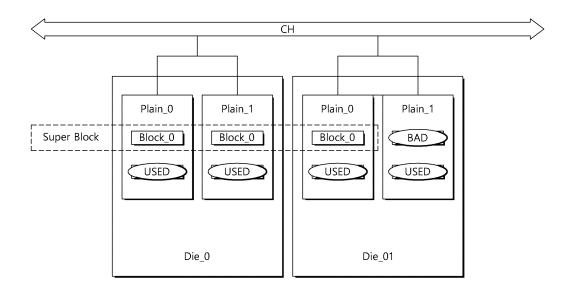

- [0037] 도 3 c를 참조하면, 슈퍼 블록을 구성하는 메모리 블록 중 다이 1의 플레인 1에 포함된 첫 번째 메모리 블록이 배드 블록으로 된 경우, 배드 블록을 대체하기 위한 블록이 다이 1의 플레인 0에 포함된 두 번째 블록만 존재하므로, 배드 블록을 다이 1의 플레인 0에 포함된 두 번째 블록으로 대체한 슈퍼 블록의 예가 도시되어 있다. 이경우, 슈퍼 블록을 구성하는 메모리 블록들 두 개의 블록이 다이 1의 프레인 0에 존재하여 인터리빙이 불가능하므로, 쓰기 동작이나 리드 동작시 속도 저하가 발생할 수 있다. 이는 이하 설명할 성능 제한 슈퍼 블록의 일 예에 해당할 수 있다.

- [0038] 도 3 d를 참조하면, 슈퍼 블록을 구성하는 메모리 블록 중 다이 1의 플레인 1에 포함된 첫 번째 메모리 블록이 배드 블록으로 된 경우, 배드 블록을 대체하기 위한 스페어 메모리 블록이 존재하지 않아 세 개의 메모리 블록으로 구성된 슈퍼 블록의 예가 도시되어있다. 이 경우, 슈퍼 블록을 구성하는 메모리 블록을 개수가 작아지므로, 슈퍼 블록이 저장할 수 있는 데이터의 크기는 작아진다. 이는 이하 설명할 성능 제한 슈퍼 블록의 일 예에 해당할 수 있다.

- [0039] 이하, 슈퍼 블록에 포함된 메모리 블록들 중 일부 메모리 블록이 배드 블록에 해당하여 도 3 c 및 3 d에 따른 성능 제한 슈퍼 블록이 생성된 것을 전제로 설명한다.

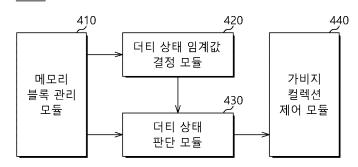

- [0040] 도 4는 본 발명의 일 실시예에 따른 플래시 변환 계층을 설명하기 위한 도면이다.

- [0041] 도 4를 참조하면, 본 발명의 일 실시예에 따른 플래시 변환 계층은 쓰기 동작시 데이터를 저장하기 위해 할당 가능한 슈퍼 블록인 프리 슈퍼 블록의 개수가 일정한 개수 이하가 되는 불휘발성 메모리 장치(100)의 더티 상태 (dirty state)를 판단하여, 불휘발성 메모리 장치(100)에 대해 가비지 컬렉션(Garbage Collection) 동작을 제어하기 위해, 메모리 블록 관리 모듈(410), 더티 상태 임계값 결정 모듈(420), 더티 상태 판단 모듈(430) 및 가비지 컬렉션 제어 모듈(440)을 포함할 수 있다.

- [0042] 메모리 블록 관리 모듈(410)은 각각 복수의 메모리 블록으로 구성되는 복수의 슈퍼 블록을 포함하는 불휘발성 메모리 장치(100)의 메모리 블록 정보를 관리할 수 있다. 구체적 예로, 메모리 블록 관리 모듈(410)은 불휘발성 메모리 장치(100)에 포함된 메모리 블록들 중 적어도 하나에 대한 쓰기, 읽기 및 소거 동작을 수행한 정보를 관

리하며, 이러한 메모리 블록 정보를 기반으로 슈퍼 블록을 구성하는 메모리 블록의 배드 블록 여부를 판단하고, 배드 블록을 포함하는 슈퍼 블록을 도 3 B 내지 D에 따른 정상 슈퍼 블록 또는 성능 저하 슈퍼 블록으로 관리할 수 있다.

- [0043] 일 실시예에서, 메모리 블록 관리 모듈(410)은 불휘발성 메모리 장치(100)에 포함된 복수의 슈퍼 블록들 중 정상 슈퍼 블록 및 성능 저하 슈퍼 블록의 주소 등의 인덱스를 리스트에 등록하여 관리할 수 있다.

- [0044] 또한, 메모리 블록 관리 모듈(410)은 쓰기 동작시 쓰기 데이터가 저장될 메모리 블록을 할당할 수 있다. 구체적 예로, 메모리 블록 관리 모듈(410)은 불휘발성 메모리 장치(100)에 포함된 복수의 슈퍼 블록들 중 프리 슈퍼 블록을 쓰기 데이터가 저장될 슈퍼 블록으로 할당할 수 있다.

- [0045] 일 실시예에서, 메모리 블록 관리 모듈(410)은 프리 슈퍼 블록들 중 정상 슈퍼 블록을 성능 슈퍼 블록에 우선하여 쓰기 데이터가 저장될 슈퍼 블록으로 할당할 수 있다. 이는 정상 슈퍼 블록을 우선적으로 사용하여 메모리시스템(10)의 성능 저하를 피하기 위함이다.

- [0046] 더티 상태 임계값 결정 모듈(420)은 불휘발성 메모리 시스템(10)이 더티 상태인지 여부를 판단하기 위한 더티 상태 임계값을 결정할 수 있다. 구체적으로, 더티 상태 임계값 결정 모듈(420)은 성능 저하 슈퍼 블록의 수를 기반으로 더티 상태 임계값을 결정할 수 있다. 예를 들어, 더티 상태 임계값 결정 모듈(320)은 프리 슈퍼 블록들 중 성능 저하 슈퍼 블록의 개수가 클수록 더티 상태 임계값을 크게 결정할 수 있다. 또한, 더티 상태 임계값 결정 모듈(420)은 프리 슈퍼 블록들 중 성능 저하 슈퍼 블록의 개수가 작을 수록 더티 상태 임계값을 크게 결정할 수 있다. 이는 프리 슈퍼 블록들의 수가 많이 남아 있더라도, 프리 슈퍼 블록들 중 정상 슈퍼 블록들이 우선적으로 할당되는 경우, 프리 슈퍼 블록들 중 성능 저하 슈퍼 블록의 개수가 많이 포함될 수 있어 더티 상태시가비지 컬렉션의 성능을 저하시키므로, 불휘발성 메모리 장치(100)를 더 빨리 더티 상태로 판정하여 가비지 컬렉션 동작을 수행하기 위함이다.

- [0047] 일 실시예에서, 더티 상태 임계값은 아래 수학식 1에 따라 결정될 수 있다. 여기서, N은 성능 저하 슈퍼 블록의 개수가 0인 경우의 더티 상태 임계값을 의미하고, L은 성능 저하 슈퍼 블록의 개수 또는 이에 비례하는 값을 의미할 수 있으며, N 및 L은 메모리 시스템(10)의 제조, 사용 단계 등에 따라 상이하게 설정 또는 가변될 수 있다.

### 수학식 1

# [0048] 더티상태임계값(T)=N+L

- [0049] 더티 상태 판단 모듈(430)은 불휘발성 메모리 장치(100)에 포함된 복수의 슈퍼 블록 중 프리 슈퍼 블록의 개수를 더티 상태 임계값과 비교하여, 불휘발성 메모리 장치(100)가 더티 상태인지 여부를 판단할 수 있다. 구체적으로, 더티 상태 판단 모듈(430)은 프리 슈퍼 블록의 개수가 더티 상태 임계값 이상이면, 불휘발성 메모리 장치(100)가 더티 상태가 아닌 것으로 판단할 수 있다. 또한, 더티 상태 판단 모듈(330)은 프리 슈퍼 블록의 개수가더티 상태 임계값 미만이면, 불휘발성 메모리 장치(100)가 더티 상태인 것으로 판단할 수 있다.

- [0050] 가비지 컬렉션 제어 모듈(3440)은 불휘발성 메모리 장치(100)가 더티 상태로 판단되면, 불휘발성 메모리 장치 (100)에 대한 가비지 컬렉션 동작을 수행할 수 있다.

- [0051] 일 실시예에서, 가비지 컬렉션 제어 모듈(440)은 불휘발성 메모리 장치(100)가 더티 상태로 판단된 경우, 메모리 시스템(10)의 다른 동작에 우선하여 가비지 컬렉션 동작을 수행하도록 불휘발성 메모리 장치(100)를 제어할 수 있다.

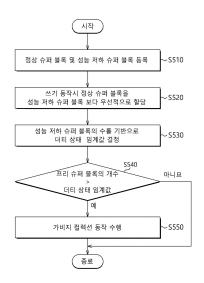

- [0052] 도 5는 본 발명의 일 실시예에 따른 메모리 시스템(10)의 동작을 설명하기 위한 도면이다.

- [0053] 도 5를 참조하면, 단계 S510에서 메모리 시스템(10)은 복수의 슈퍼 블록 중 성능 저하 슈퍼 블록을 등록하여 관리할 수 있다. 구체적 예로, 컨트롤러(200)는 불휘발성 메모리 장치(100)에 포함된 복수의 슈퍼 블록 중 성능 저하 슈퍼 블록들을 판단하고, 성능 저하 슈퍼 블록으로 판단된 슈퍼 블록들을 리스트에 등록할 수 있다.

- [0054] 단계 S520에서, 메모리 시스템(10)은 프리 슈퍼 블록들 중 정상 슈퍼 블록을 성능 저하 슈퍼 블록 보다 우선적으로 할당하여, 쓰기 동작을 수행할 수 있다. 구체적 예로, 컨트롤러(200)는 호스트(20)로부터 쓰기 커맨드 및 쓰기 데이터가 수신되면, 프리 슈퍼 블록 중 정상 슈퍼 블록을 성능 제한 보다 우선적으로 쓰기 데이터가 저장

될 메모리 블록으로 할당할 수 있다. 이때, 불휘발성 메모리 장치(100)는 할당된 메모리 블록에 쓰기 데이터를 저장하는 쓰기 동작을 수행할 수 있다.

- [0055] 단계 S530에서, 메모리 시스템(10)은 성능 저하 슈퍼 블록의 개수를 기반으로 더티 상태 임계값을 결정할 수 있다. 구체적 예로, 컨트롤러(200)는 프리 슈퍼 블록 중 성능 저하 슈퍼 블록의 개수가 클수록, 더티 상태 임계값을 크게 결정할 수 있다. 또한, 컨트롤러(200)는 프리 슈퍼 블록 중 성능 저하 슈퍼 블록의 개수가 작을수록, 더티 상태를 임계값을 작게 결정할 수 있다.

- [0056] 단계 S540에서, 메모리 시스템(10)은 프리 슈퍼 블록의 개수를 기반으로 불휘발성 메모리 장치(100)의 더티 상태 여부를 판단할 수 있다. 구체적 예로, 컨트롤러(200)는 불휘발성 메모리 장치(100)에 포함된 복수의 메모리 블록 중 프리 슈퍼 블록의 개수를 더티 상태 임계값과 비교하여, 프리 슈퍼 블록의 개수가 더티 상태 임계값 이상이면 불휘발성 메모리 장치(100)가 더티 상태가 아닌 것으로 판단할 수 있다. 또한, 컨트롤러(200)는 프리 슈퍼 블록의 개수가 더티 상태 임계값 미만이면, 불휘발성 메모리 장치(100)가 더티 상태인 것으로 판단할 수 있다.

- [0057] 단계 S550에서, 메모리 시스템(10)은 가비지 컬렉션 동작을 수행할 수 있다. 구체적 예로, 컨트롤러(200)는 불휘발성 메모리 장치(100)가 더티 상태로 판단된 경우, 불휘발성 메모리 장치(100)가 가비지 컬렉션 동작을 수행하도록 제어할 수 있다. 이에 따라 불휘발성 메모리 장치(100)는 복수의 메모리 블록에 대한 가비지 컬렉션 동작을 수행할 수 있다.

- [0058] 일 실시예에서, 컨트롤러(200)는 다른 동작에 우선하여 가비지 컬렉션 동작을 수행하도록, 불휘발성 메모리 장치(100)를 제어할 수 있다.

- [0059] 도 6은 본 발명의 실시 예에 따른 솔리드 스테이트 드라이브(SSD)를 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면이다. 도 6을 참조하면, 데이터 처리 시스템(2000)은 호스트(2100)와 솔리드 스테이트 드라이브 (solid state drive)(2200)(이하, SSD라 칭함)를 포함할 수 있다.

- [0060] SSD(2200)는 컨트롤러(2210), 버퍼 메모리 장치(2220), 불휘발성 메모리 장치들(2231~223n), 전원 공급기 (2240), 신호 커넥터(2250) 및 전원 커넥터(2260)를 포함할 수 있다.

- [0061] 컨트롤러(2210)는 SSD(2200)의 제반 동작을 제어할 수 있다.

- [0062] 버퍼 메모리 장치(2220)는 불휘발성 메모리 장치들(2231~223n)에 저장될 데이터를 임시 저장할 수 있다. 또한, 버퍼 메모리 장치(2220)는 불휘발성 메모리 장치들(2231~223n)로부터 읽혀진 데이터를 임시 저장할 수 있다. 버 퍼 메모리 장치(2220)에 임시 저장된 데이터는 컨트롤러(2210)의 제어에 따라 호스트(2100) 또는 불휘발성 메모 리 장치들(2231~223n)로 전송될 수 있다.

- [0063] 불휘발성 메모리 장치들(2231~223n)은 SSD(2200)의 저장 매체로 사용될 수 있다. 불휘발성 메모리 장치들 (2231~223n) 각각은 복수의 채널들(CH1~CHn)을 통해 컨트롤러(2210)와 연결될 수 있다. 하나의 채널에는 하나 또는 그 이상의 불휘발성 메모리 장치가 연결될 수 있다. 하나의 채널에 연결되는 불휘발성 메모리 장치들은 동일한 신호 버스 및 데이터 버스에 연결될 수 있다.

- [0064] 전원 공급기(2240)는 전원 커넥터(2260)를 통해 입력된 전원(PWR)을 SSD(2200) 내부에 제공할 수 있다. 전원 공급기(2240)는 보조 전원 공급기(2241)를 포함할 수 있다. 보조 전원 공급기(2241)는 서든 파워 오프(sudden power off)가 발생되는 경우, SSD(2200)가 정상적으로 종료될 수 있도록 전원을 공급할 수 있다. 보조 전원 공급기(2241)는 전원(PWR)을 충전할 수 있는 대용량 캐패시터들(capacitors)을 포함할 수 있다.

- [0065] 컨트롤러(2210)는 신호 커넥터(2250)를 통해서 호스트(2100)와 신호(SGL)를 주고 받을 수 있다. 여기에서, 신호 (SGL)는 커맨드, 어드레스, 데이터 등을 포함할 수 있다. 신호 커넥터(2250)는 호스트(2100)와 SSD(2200)의 인 터페이스 방식에 따라 다양한 형태의 커넥터로 구성될 수 있다.

- [0066] 도 7은 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면이다. 도 7을 참조하면, 데이터 처리 시스템(3000)은 호스트(3100)와 메모리 시스템(3200)을 포함할 수 있다.

- [0067] 호스트(3100)는 인쇄 회로 기판(printed circuit board)과 같은 기판(board) 형태로 구성될 수 있다. 비록 도 시되지 않았지만, 호스트(3100)는 호스트의 기능을 수행하기 위한 내부 기능 블럭들을 포함할 수 있다.

- [0068] 호스트(3100)는 소켓(socket), 슬롯(slot) 또는 커넥터(connector)와 같은 접속 터미널(3110)을 포함할 수 있

- 다. 메모리 시스템(3200)은 접속 터미널(3110)에 마운트(mount)될 수 있다.

- [0069] 메모리 시스템(3200)은 인쇄 회로 기판과 같은 기판 형태로 구성될 수 있다. 메모리 시스템(3200)은 메모리 모듈 또는 메모리 카드로 불릴 수 있다. 메모리 시스템(3200)은 컨트롤러(3210), 버퍼 메모리 장치(3220), 불휘발성 메모리 장치(3231~3232), PMIC(power management integrated circuit)(3240) 및 접속 터미널(3250)을 포함할 수 있다.

- [0070] 컨트롤러(3210)는 메모리 시스템(3200)의 제반 동작을 제어할 수 있다. 컨트롤러(3210)는 도 6에 도시된 컨트롤러(2210)와 동일하게 구성될 수 있다.

- [0071] 버퍼 메모리 장치(3220)는 불휘발성 메모리 장치들(3231~3232)에 저장될 데이터를 임시 저장할 수 있다. 또한, 버퍼 메모리 장치(3220)는 불휘발성 메모리 장치들(3231~3232)로부터 읽혀진 데이터를 임시 저장할 수 있다. 버 퍼 메모리 장치(3220)에 임시 저장된 데이터는 컨트롤러(3210)의 제어에 따라 호스트(3100) 또는 불휘발성 메모 리 장치들(3231~3232)로 전송될 수 있다.

- [0072] 불휘발성 메모리 장치들(3231~3232)은 메모리 시스템(3200)의 저장 매체로 사용될 수 있다.

- [0073] PMIC(3240)는 접속 터미널(3250)을 통해 입력된 전원을 메모리 시스템(3200) 내부에 제공할 수 있다. PMIC(3240)는, 컨트롤러(3210)의 제어에 따라서, 메모리 시스템(3200)의 전원을 관리할 수 있다.

- [0074] 접속 터미널(3250)은 호스트의 접속 터미널(3110)에 연결될 수 있다. 접속 터미널(3250)을 통해서, 호스트 (3100)와 메모리 시스템(3200) 간에 커맨드, 어드레스, 데이터 등과 같은 신호와, 전원이 전달될 수 있다. 접속 터미널(3250)은 호스트(3100)와 메모리 시스템(3200)의 인터페이스 방식에 따라 다양한 형태로 구성될 수 있다. 접속 터미널(3250)은 메모리 시스템(3200)의 어느 한 변에 배치될 수 있다.

- [0075] 도 8은 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 데이터 처리 시스템을 예시적으로 나타낸 도면이다. 도 8을 참조하면, 데이터 처리 시스템(4000)은 호스트(4100)와 메모리 시스템(4200)을 포함할 수 있다.

- [0076] 호스트(4100)는 인쇄 회로 기판(printed circuit board)과 같은 기판(board) 형태로 구성될 수 있다. 비록 도 시되지 않았지만, 호스트(4100)는 호스트의 기능을 수행하기 위한 내부 기능 블럭들을 포함할 수 있다.

- [0077] 메모리 시스템(4200)은 표면 실장형 패키지 형태로 구성될 수 있다. 메모리 시스템(4200)은 솔더 볼(solder ball)(4250)을 통해서 호스트(4100)에 마운트될 수 있다. 메모리 시스템(4200)은 컨트롤러(4210), 버퍼 메모리 장치(4220) 및 불휘발성 메모리 장치(4230)를 포함할 수 있다.

- [0078] 컨트롤러(4210)는 메모리 시스템(4200)의 제반 동작을 제어할 수 있다. 컨트롤러(4210)는 도 6에 도시된 컨트롤러(2210)와 동일하게 구성될 수 있다.

- [0079] 버퍼 메모리 장치(4220)는 불휘발성 메모리 장치(4230)에 저장될 데이터를 임시 저장할 수 있다. 또한, 버퍼 메모리 장치(4220)는 불휘발성 메모리 장치들(4230)로부터 읽혀진 데이터를 임시 저장할 수 있다. 버퍼 메모리 장치(4220)에 임시 저장된 데이터는 컨트롤러(4210)의 제어에 따라 호스트(4100) 또는 불휘발성 메모리 장치(4230)로 전송될 수 있다.

- [0080] 불휘발성 메모리 장치(4230)는 메모리 시스템(4200)의 저장 매체로 사용될 수 있다.

- [0081] 도 9는 본 발명의 실시 예에 따른 메모리 시스템을 포함하는 네트워크 시스템(5000)을 예시적으로 나타낸 도면이다. 도 9를 참조하면, 네트워크 시스템(5000)은 네트워크(5500)를 통해서 연결된 서버 시스템(5300) 및 복수의 클라이언트 시스템들(5410~5430)을 포함할 수 있다.

- [0082] 서버 시스템(5300)은 복수의 클라이언트 시스템들(5410~5430)의 요청에 응답하여 데이터를 서비스할 수 있다. 예를 들면, 서버 시스템(5300)은 복수의 클라이언트 시스템들(5410~5430)로부터 제공된 데이터를 저장할 수 있다. 다른 예로서, 서버 시스템(5300)은 복수의 클라이언트 시스템들(5410~5430)로 데이터를 제공할 수 있다.

- [0083] 서버 시스템(5300)은 호스트(5100) 및 메모리 시스템(5200)을 포함할 수 있다. 메모리 시스템(5200)은 도 1의 메모리 시스템(10), 도 6의 메모리 시스템(2200), 도 7의 메모리 시스템(3200) 및 도 8의 메모리 시스템(4200)으로 구성될 수 있다.

- [0084] 본 발명이 속하는 기술분야의 통상의 기술자는 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있으므로, 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적

이 아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태 가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

# 부호의 설명

[0085] 10: 메모리 시스템 100: 불휘발성 메모리 장치

200: 컨트롤러 210: 호스트 인터페이스

220: 프로세서 230: 메모리

240: 메모리 인터페이스

# 도면

# 도면1

# 도면3a

# 도면3b

# 도면3c

# 도면3d

# 도면4

# $\mathsf{FTL}$

# <u>2000</u>

# 도면7

# 4000

# 도면9

# 5000