#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

(10) International Publication Number

#### (43) International Publication Date 13 April 2006 (13.04.2006)

(51) International Patent Classification: **H04B 10/158** (2006.01) G06F 1/16 (2006.01) G02B 6/00 (2006.01)

(21) International Application Number:

PCT/US2005/034147

(22) International Filing Date:

21 September 2005 (21.09.2005)

(25) Filing Language: (26) Publication Language: English English

(30) Priority Data:

10/954,902

30 September 2004 (30.09.2004)

- (71) Applicant (for all designated States except US): INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): LIU, Chien-Chang [-/US]; 1018 Grape Avenue, Sunnyvale, CA 94087 (US). CHENG, Heng-Ju [US/US]; 1683 Columbia Drive, Mountain View, CA 94040 (US).

# WO 2006/039203 A1

- (74) Agent: VINCENT, Lester, J.; Blakely, Sokoloff, Taylor & Zafman, 12400 Wilshire Blvd., 7th Floor, Los Angeles, CA 90025 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT,

[Continued on next page]

#### (54) Title: MECHANISM TO SELECT BANDWIDTH IN AN OPTICAL RECEIVER CIRCUIT

(57) Abstract: An optical receiver circuit is disclosed. This receiver included in receiver optical sub-assembly (ROSA) adjusts bandwidth based on a voltage level detection at a receiver signal strength indication (RSSI) pin, or rate-adaptively adjusts the bandwidth of optical receiver circuit based on operation data rate.

# WO 2006/039203 A1

RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# MECHANISM TO SELECT BANDWIDTH IN AN OPTICAL RECEIVER CIRCUIT FIELD OF THE INVENTION

[0001] The present invention relates to fiber optic communication; more particularly, the present invention relates to optical receivers.

#### 5 BACKGROUND

10

15

[0002] More frequently, optical input/output (I/O) is being used in computer systems to transmit data between system components. Optical I/O is able to attain higher system bandwidth with lower electromagnetic interference than conventional I/O methods. In order to implement optical I/O, optical transceivers transmit and receive radiant energy to/from a waveguide, such as optical fibers.

[0003] However, in an optical transceiver circuit, the most encountered problem is the selection of preamplifier bandwidth. If the preamplifier (e.g., trans-impedance amplifier (TIA)) has too much bandwidth, the optical sensitivity and gain on the jitter performance will be degraded. Nevertheless, the optical sensitivity can be improved by reduce the bandwidth of TIA. Therefore, most designers pursue optimizing the bandwidth according to the different data rates. Typically, the TIA is designed to have a bandwidth of 0.7 \* bit rate.

[0004] Current ROSA (Receiver optical sub assembly) typically have five output pins (Vcc, GND, out+, out- and RSSI (receiver signal strength indication)). The RSSI pin is designed to generate the current output proportional to the received optical signal. Thus, there is no pin to select the bandwidth in the TIA inside the ROSA.

# BRIEF DESCRIPTION OF THE DRAWINGS

5

10

[0005] The present invention will be understood more fully from the detailed description given below and from the accompanying drawings of various embodiments of the invention. The drawings, however, should not be taken to limit the invention to the specific embodiments, but are for explanation and understanding only.

|    | [0006]     | Figure 1 illustrates one embodiment of a system;                  |

|----|------------|-------------------------------------------------------------------|

|    | [0007]     | Figure 2 illustrates one embodiment of a receiver circuit;        |

|    | [0008]     | Figure 3 illustrates another embodiment of a receiver circuit;    |

| 15 | [0009]     | Figure 4 illustrates one embodiment of a rate selection circuit;  |

|    | [0010]     | Figure 5 illustrates one embodiment of waveforms for various data |

|    | rates; and |                                                                   |

[0011] Figure 6 illustrates one embodiment of a ROSA circuit.

#### **DETAILED DESCRIPTION**

5

20

[0012] According to one embodiment, a fiber optic communication mechanism is disclosed. Reference in the specification to "one embodiment" or "an embodiment" means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. The appearances of the phrase "in one embodiment" in various places in the specification are not necessarily all referring to the same embodiment.

[0013] In the following description, numerous details are set forth. It will be apparent, however, to one skilled in the art, that the present invention may be practiced without these specific details. In other instances, well-known structures and devices are shown in block diagram form, rather than in detail, in order to avoid obscuring the present invention.

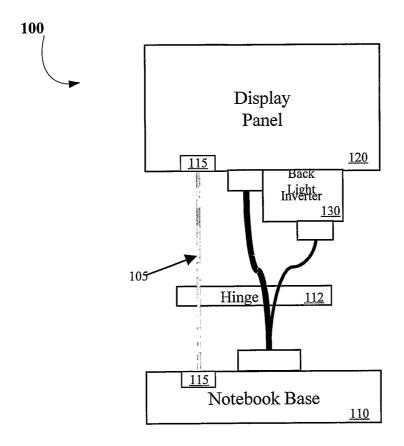

[0014] Figure 1 is a block diagram of one embodiment of a computer system 100. Computer system 100 is a notebook computer that includes a notebook base 110 attached to a display panel 120 via a hinge 112. System 100 also includes a back light inverter 130 coupled to panel 120 for lighting display 120.

[0015] According to one embodiment, base 110 and display panel 120 are also coupled via a waveguide 105. Waveguide 105 transmits radiant energy between base 110 and display panel 120 via receivers 115. Receivers 115 are

implemented to receive data from waveguide 105. In one embodiment,

waveguide 105 includes one or more optical fibers. However, other embodiments

may feature other types of waveguides.

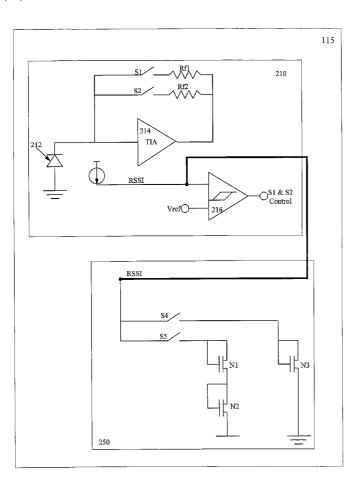

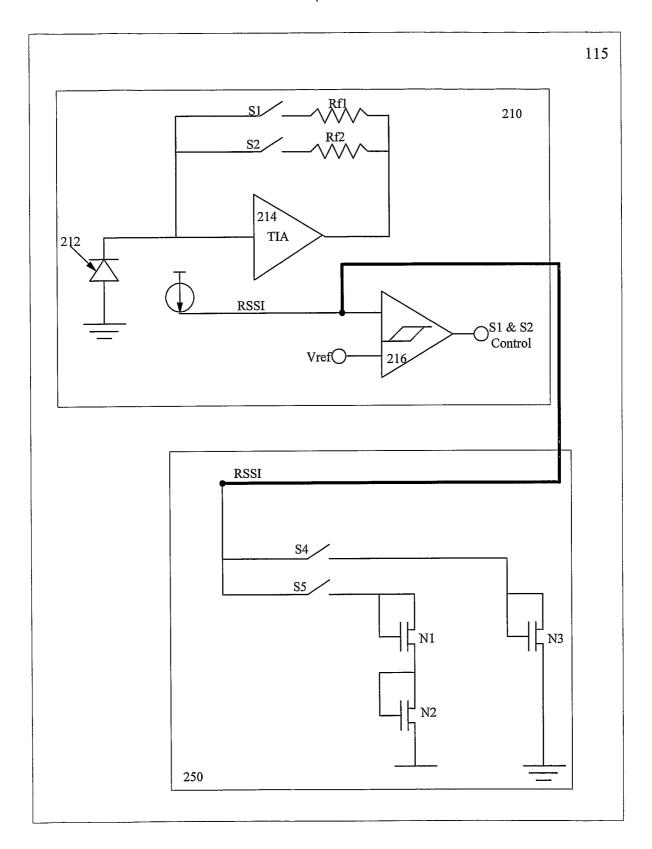

[0016] Figure 2 illustrates one embodiment of a receiver 115. Receiver 115 includes a ROSA circuit 210 and a bandwidth adjustment circuit 250. ROSA circuit 210 includes active components that are implemented to receive an optical input. Particularly, circuit 210 includes a diode 212, a trans-impedance amplifier (TIA) 214, a comparator 216, switches S1 and S2, and feedback resistors Rf1 and Rf2 coupled to S1 and S2, respectively.

5

- 10 [0017] Diode 212 converts a received optical input signal into an electrical signal. In one embodiment, diode 212 is a positive, intrinsic, negative (PIN) diode. However, in other embodiments, diode 212 may be implemented with an Avalanche Photodiode (APD). TIA 214 receives the converted signal from diode 212 and amplifies the signal.

- 15 [0018] According to one embodiment, the bandwidth of TIA 214 may be adjusted to optimize the signal based on the system data rate. Accordingly, comparator 216 within circuit 210, and bandwidth adjustment circuit 250 are implemented to optimize the TIA 214 bandwidth. In one embodiment, comparator 216 receives a reference voltage (Vref) from bandwidth adjustment circuit 250 and compares the voltage to a voltage corresponding to a voltage

received from the RSSI pin. As discussed above, the RSSI pin is designed to generate a current output proportional to the received optical signal.

[0019] In one embodiment, if the RSSI pin voltage is greater than Vref comparator 216 closes S1, and if the RSSI pin voltage is less than Vref, S2 is closed.

- 5 Thus, TIA 214 will have one feedback resistance if the RSSI pin voltage is greater, and another resistance if the RSSI pin voltage is less than Vref.

- [0020] Bandwidth adjustment circuit 250 indicates to ROSA circuit 210 which data rate is to be used. For example, bandwidth adjustment circuit 250 indicates whether the data rate is 2Gb/sec or 4Gb/sec. Circuit 250 includes NMOS transistors N1-N3. In one embodiment, each of the transistors has the same characteristics. Transistors N1 and N2 are coupled to a switch S5, while transistor N3 is coupled to a switch S4. Both switches are coupled to the RSSI pin to receive current.

10

- [0021] According to one embodiment, switch S4 is closed if the system is to operate at a 2Gb/sec. As a result, the voltage buildup at the RSSI pin will be approximately equivalent to the voltage threshold (Vt) plus the source-drain voltage (Vds) if S4 is closed. Similarly, switch S5 is closed if the system is to operate at a 4Gb/sec. Thus, the voltage buildup at the RSSI pin will be approximately equivalent to the voltage threshold 2\*(Vt + Vds) if S5 is closed.

- 20 [0022] In operation, the system user would close (turn on) either switch S4 or S5 prior to operation of receiver 115 since the system data rate is known. For

instance, if S1 is turned on it is known that the incoming data rate is 2Gb/s data. Therefore, the RSSI voltage will be Vt + Vds above ground. If the data stream is 4Gb/s, S2 is turned on, while S1 is off. Thus, the RSSI voltage will be 2\*(Vt+Vds). At ROSA circuit 210 comparator 216 controls S1 and S2 by telling whether the voltage is higher or lower than Vref. In one embodiment, Vref is equal to 2\*Vt.

5

10

[0023] If the RSSI voltage is higher than 2 Vt, the bandwidth can be selected by adjusting the feedback resistor of TIA 214. The feedback resistor is selected in effect by closing S1 or S2, depending upon which has the optimized resistance. In one embodiment, Rf1 has a lower resistance. Thus, S1 is closed by comparator 216 for 4Gb/s data stream.

[0024] If the RSSI voltage is lower than 2 Vt, 2Gb/s data rate operation occurs. Accordingly, resistor Rf2 is selected by closing S2. By using this technique, no additional pin is required at receiver 115 for optimization of TIA bandwidth selection.

15 [0025] Although described with respect to 2Gb/sec and 4Gb/sec, one of ordinary skill will appreciate that other data rates may be implemented (e.g., 1Gb/sec and 2Gb/sec) in other embodiments. Also, in other embodiments, the NMOS transistors may be replaced with PMOS transistors.

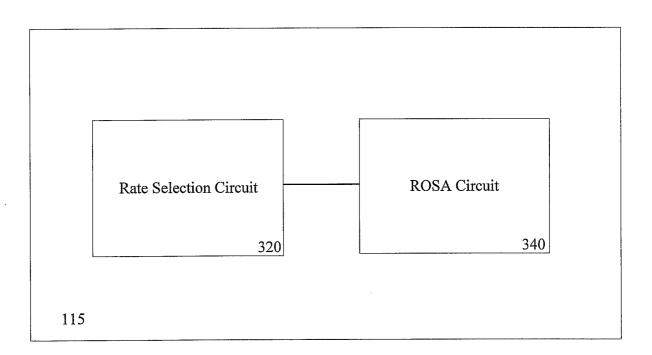

[0026] According to a further embodiment, receiver 115 may implement

automatic TIA data rate selection. Figure 3 illustrates another embodiment of a

receiver 115. In this embodiment, a rate selection circuit 320 is coupled to a ROSA

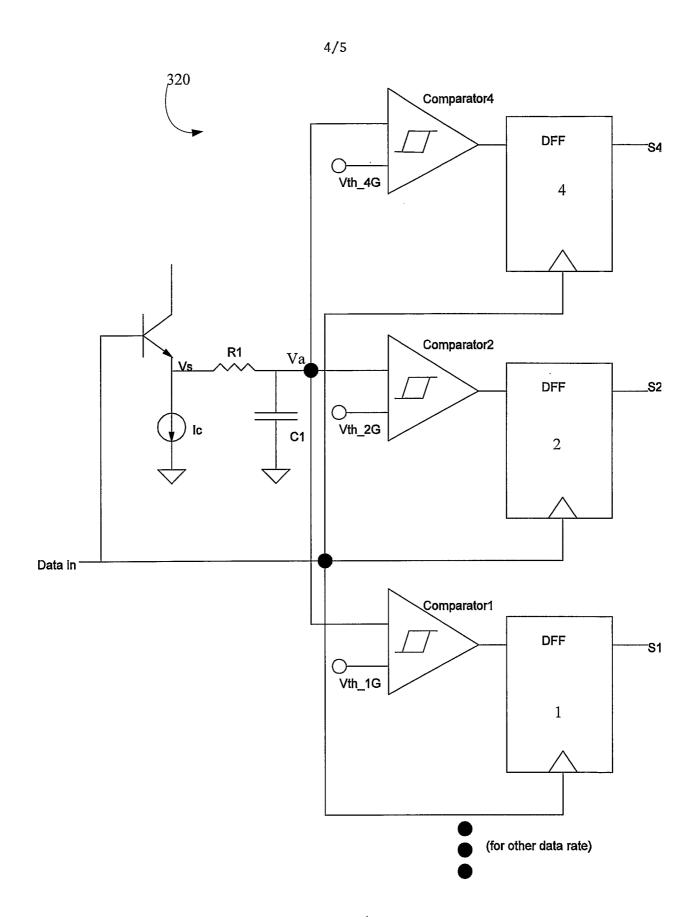

circuit 340 to select the data rate at ROSA circuit 340. **Figure 4** illustrates one embodiment of rate selection circuit 320.

[0027] Selection circuit 320 includes three D flip flops (DFF1, DFF2 and DFF4) that receive data. Each DFF has a corresponding output. According to one embodiment, each DFF has an input coupled to the output of a comparator. For example, comparators 1, 2 and 4 are coupled to DFFs 1, 2 and 4, respectively. Further, each of the comparators is coupled to a node Va, which is coupled to a capacitor C1 and a transistor, via resistor R1.

5

[0028] Assuming the input data has a high pulse (logic 1), the nodal voltage Va will be charged to a fixed voltage Vhigh-VBE. The charge is stored in capacitor C1. Subsequently, when the data input is switched to low (logic 0), the voltage on C1 starts to drop at a fixed rate by Qc1/Ic. Thus, the nodal voltage drops to different voltage levels based upon the data rate.

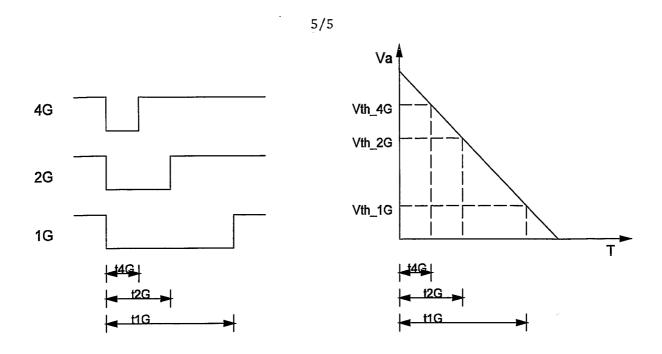

[0029] Figure 5 illustrates one embodiment of waveforms for various data

15 rates. As shown in Figure 5, the shortest wave pulse for a 1Gb/sec signal is twice

as long as that for a 2Gb/sec signal, and four times that of a 4Gb/sec signal.

Similarly, the wave pulse for a 2Gb/sec signal is twice as long as that for a 4Gb/sec

signal. Therefore, the voltage drop for shortest wave pulse for a 4Gb/sec signal is

two times slower than for 2Gb/sec and twice that of 1Gb/sec.

20 [0030] Since the approximate time constants are known, the threshold voltage for each comparator may be set accordingly. For example, if the highest

data rate is at 4Gb/sec, the node voltage after the 0 pulse will drop above Vth\_4G causing the D flip flop coupled to each comparator to have an output of logic 1.

Thus the logic values of comparators 4, 2 and 1 are (1,1,1).

[0031] Similarly, if the data rate is at 2Gb/sec, comparator 4 would be off

and comparator 2, and comparator 1 would be on. Thus, the logic state of the

three comparators would be (0,1,1). If the data rate is at 1Gb/sec, the nodal

voltage Va would only be higher than Vth\_1G thus only comparator 1 would be

high. Therefore, the logic state is (0,0,1). If the data rate is slower than 1Gb/sec,

all of these three comparators are off and the logic state is (0,0,0). Table 1 table

below summarizes the above results.

Table 1

| Data rate | Comparator 4 | Comparator 2 | Comparator 1 |

|-----------|--------------|--------------|--------------|

| 4Gb/s     | 1            | 1            | 1            |

| 2Gb/s     | 0            | 1            | 1            |

| 1Gb/s     | 0            | 0            | 1            |

| < 1Gb/s   | 0            | 0            | 0            |

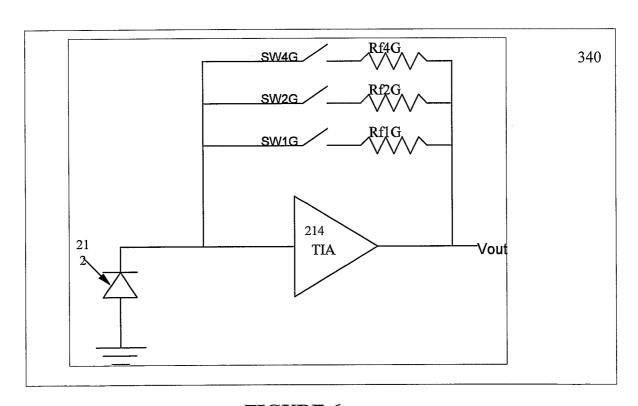

[0032] Figure 6 illustrates one embodiment of ROSA circuit 340. Circuit 340 includes diode 212 and TIA 214. In addition, feedback switches SW1G, SW2G and SW4G are included, each being coupled to respective feedback resistors Rf1G, Rf2G and Rf4G, respectively.

[0033] By using **Table 1**, logic is generated to control the selection of the feedback resistor at TIA 214. For instance, if the logic state is (111), switch

SW4G is closed. If the logic state from the three comparators is (011), switch SW2G is turned on. Thus, the TIA bandwidth is selected for 2Gb/s operation. Similarly, if all the logic state is (001), switch SW1G is closed to optimize the bandwidth of TIA 214 for a 1Gb/s data stream. The beauty of this design is that it can automatically adjust the bandwidth without external pin selection.

5

[0034] Although described above with respect to a notebook computer implementation, receivers 115 may be used in various applications. For instance, system 100 may include printed circuit boards (PCBs). In one embodiment, receivers 115 may be used at one PCB to couple optical I/O from another PCB.

The two PCBs may be included within the same computer system, or may be located at different systems and coupled via a network.

[0035] Whereas many alterations and modifications of the present invention will no doubt become apparent to a person of ordinary skill in the art after having read the foregoing description, it is to be understood that any particular embodiment shown and described by way of illustration is in no way intended to be considered limiting. Therefore, references to details of various embodiments are not intended to limit the scope of the claims which in themselves recite only those features regarded as the invention.

#### **CLAIMS**

5

20

What is claimed is:

1. A receiver comprising:

an optical receiver circuit to adjust bandwidth based on a voltage level at a receiver signal strength indication (RSSI) pin; and

a bandwidth adjustment circuit to indicate an operation data rate by detecting the voltage level on the RSSI pin.

- 2. The receiver of claim 1 wherein the ROSA circuit comprises:

- a trans-impedance amplifier (TIA); and

- a comparator to adjust the bandwidth based on the voltage applied to the RSSI pin.

- 3. The receiver of claim 2 wherein the ROSA circuit further comprises:

a first resistor coupled to the output of the TIA;

a first switch coupled to the first resistor and the input of the TIA;

a second resistor coupled to the output of the TIA; and

a second switch coupled to the second resistor and the input of the TIA.

- 4. The receiver of claim 3 wherein the comparator selects the first resistor by closing the first switch if the voltage applied to the RSSI pin is greater than a reference voltage, and selects the second resistor by closing the second switch if the voltage applied to the RSSI pin is less than a reference voltage.

5. The receiver of claim 1 further comprising a diode coupled to the TIA.

- 6. The receiver of claim 3 wherein the bandwidth adjustment circuit comprises:

- a third switch coupled to the RSSI pin; and

- 5 a fourth switch coupled to the RSSI pin.

- 7 The receiver of claim 6 wherein the bandwidth adjustment circuit further comprises:

- a first transistor coupled to the third switch;

- a second transistor coupled to the fourth switch; and

- a third transistor coupled between the fourth switch and ground.

- 8. The receiver of claim 7 wherein the first transistor applies a first voltage to the RSSI pin whenever the third switch is closed.

- 9. The receiver of claim 8 wherein the second transistor and the third transistor apply a second voltage to the RSSI pin whenever the fourth switch is closed.

- 10. A method comprising:

15

comparing a voltage applied to a receiver signal strength indication (RSSI) pin at an optical receiver circuit in a receiver optical sub-assembly (ROSA) to a reference voltage; and

adjusting the bandwidth based of the ROSA circuit based on the voltage.

- 11. The method of claim 10 further comprising:

- applying a first voltage to the RSSI pin if optical input/output (I/O) is being received at a first data rate; and

- applying a second voltage to the RSSI pin if I/O is being received at a second data rate.

- 12. The method of claim 11 wherein comparing the voltage comprises:

selecting a first feedback resistor if the first voltage is applied to the RSSI

pin; and

- selecting a second feedback resistor if the second voltage is applied to the RSSI pin.

- 13. A system comprising:

- a notebook computer base;

- a first receiver coupled to the notebook base;

- a waveguide coupled to the first transceiver;

- a second receiver coupled to the waveguide; and

- a display panel coupled to the second receiver;

- wherein the first receiver and the second receiver each include:

a receiver optical sub-assembly (ROSA) circuit to adjust bandwidth based on a voltage level at a receiver signal strength indication (RSSI) pin; and

a bandwidth adjustment circuit to indicate an operation data rate by applying the voltage level to the RSSI pin.

- 14. The system of claim 13 wherein the ROSA circuit comprises:

a trans-impedance amplifier (TIA); and

a comparator to adjust the bandwidth base on the voltage applied to the

- RSSI pin.

- 15. The system of claim 14 wherein the ROSA circuit further comprises:

a first resistor coupled to the output of the TIA;

a first switch coupled to the first resistor and the input of the TIA;

a second resistor coupled to the output of the TIA; and

a second switch coupled to the second resistor and the input of the TIA.

- 15 16. The system of claim 15 wherein the bandwidth adjustment circuit comprises:

- a third switch coupled to the RSSI pin; and a fourth switch coupled to the RSSI pin.

17 The system of claim 16 wherein the bandwidth adjustment circuit further comprises:

- a first transistor coupled to the third switch;

- a second transistor coupled to he fourth switch; and

- a third transistor coupled between the fourth switch and ground.

- 18. The system of claim 17 wherein the first transistor applies a first voltage to the RSSI pin whenever the third switch is closed.

- 19. The system of claim 18 wherein the second transistor and the third transistor apply a second voltage to the RSSI pin whenever the fourth switch is closed.

- 20. A receiver comprising:

10

a receiver optical sub-assembly (ROSA) circuit to receive optical input/output (I/O) data; and

a control circuit to automatically adjust the operating bandwidth of the ROSA circuit based on the I/O data rate.

- 21. The receiver of claim 20 wherein the ROSA circuit comprises:

- a trans-impedance amplifier (TIA);

- a first resistor coupled to the output of the TIA;

- a first switch coupled to the first resistor and the input of the TIA;

a second resistor coupled to the output of the TIA; and a second switch coupled to the second resistor and the input of the TIA.

- 22. The receiver of claim 21 wherein the control circuit selects first resistor by closing the first switch whenever the control circuit detects a first I/O data rate.

- 5 23. The receiver of claim 22 wherein the control circuit selects the first resistor by closing the first switch whenever the control circuit detects a first I/O data rate.

- 24. The receiver of claim 23 wherein the control circuit selects the second resistor by closing the second switch whenever the control circuit detects a second I/O data rate.

- The receiver of claim 24 wherein the ROSA circuit further comprises:

a third resistor coupled to the output of the TIA; and

a third switch coupled to the third resistor and the input of the TIA.

- 26. The receiver of claim 25 wherein the control circuit selects the third resistor by closing the third switch whenever the control circuit detects a third I/O data rate.

- 27. The receiver of claim 26 wherein the control circuit comprises:

- a first flip-flop;

- a second flip-flop; and

- a third flip-flop.

28. The receiver of claim 25 wherein the control circuit closes the first switch is closed whenever the output of the first, second and third flip-flops are high, the second switch is closed whenever the output of the second and third flip-flops are high, and the third switch is closed whenever the output of the first flip-flop is high.

- 29. The receiver of claim 27 wherein the control circuit further comprises:

- a first comparator coupled to the first flip-flop;

5

- a second comparator coupled to the second flip-flop; and

- a third comparator coupled to the third flip-flop.

1/5

FIGURE 1

2/5

FIGURE 2

3/5

410

FIGURE 3

FIGURE 4

FIGURE 5

FIGURE 6

## INTERNATIONAL SEARCH REPORT

International Application No

PCT\_US2005/034147 a. classification of subject matter H04B10/158 G02I G06F1/16 G02B6/00 According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) HO4B GO2B G06F Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) EPO-Internal C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Category ° 1-12US 4 608 542 A (SIEGEL ET AL) χ 26 August 1986 (1986-08-26) 20 - 29column 1, line 5 - column 1, line 10 column 2, line 38 - column 2, line 50 column 2, line 61 - column 4, line 35 13 - 19Υ US 5 917 968 A (WOOD ET AL) 13 - 1929 June 1999 (1999-06-29) figure 8 US 2003/002108 A1 (AMES STEPHEN JOHN ET 1-12, χ 20-29 AL) 2 January 2003 (2003-01-02) paragraph '0006! - paragraph '0007! paragraph '0026!; figure 1 Further documents are listed in the continuation of box C. Patent family members are listed in annex. ° Special categories of cited documents: \*T\* later document published after the international filing date or priority date and not in conflict with the application but "A" document defining the general state of the art which is not cited to understand the principle or theory underlying the considered to be of particular relevance invention "E" earlier document but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) involve an inventive step when the document is taken alone "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such docu-"O" document referring to an oral disclosure, use, exhibition or ments, such combination being obvious to a person skilled in the art. other means document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of mailing of the international search report Date of the actual completion of the international search

Name and mailing address of the ISA

3 January 2006

Fax: (+31-70) 340-3016

European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

13/01/2006

Phillips, S

Authorized officer

## INTERNATIONAL SEARCH REPORT

International Application No

PCTJUS2005/034147

|            | etion) DOCUMENTS CONSIDERED TO BE RELEVANT                                                             | Del                   |  |

|------------|--------------------------------------------------------------------------------------------------------|-----------------------|--|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                     | Relevant to claim No. |  |

| Х          | WO 2004/051888 A (CENTILLIUM COMMUNICATIONS, INC) 17 June 2004 (2004-06-17) paragraph '0004!; figure 1 | 1-12,<br>20-29        |  |

| A          | US 2003/066947 A1 (ALWAN JIM ET AL)<br>10 April 2003 (2003-04-10)<br>abstract; figure 6                | 1-29                  |  |

| A          | US 2004/076360 A1 (CHEN WEI-YUNG WAYNE ET AL) 22 April 2004 (2004-04-22) abstract; figure 1            | 1-29                  |  |

| A          | US 4 574 249 A (WILLIAMS ET AL) 4 March 1986 (1986-03-04) abstract; figures 49,51                      | 1-29                  |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

|            |                                                                                                        |                       |  |

#### INTERNATIONAL SEARCH REPORT

Iformation on patent family members

International Application No

PCT/US2005/034147

| Patent document cited in search report |       | Publication<br>date | Patent family<br>member(s)       | Publication date         |

|----------------------------------------|-------|---------------------|----------------------------------|--------------------------|

| US 4608542                             | A     | 26-08-1986          | NONE                             |                          |

| US 5917968                             | Α     | 29-06-1999          | NONE                             |                          |

| US 2003002108                          | A1    | 02-01-2003          | JP 3650377 B2<br>JP 2003115894 A | 18-05-2005<br>18-04-2003 |

| WO 2004051888                          | Α     | 17-06-2004          | AU 2003293092 A1                 | 23-06-2004               |

| US 2003066947                          | A1    | 10-04-2003          | NONE                             |                          |

| US 2004076360                          | A1    | 22-04-2004          | NONE                             |                          |

| US 4574249                             | <br>А | 04-03-1986          | NONE                             |                          |