(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7374622号**

**(P7374622)**

(45)発行日 令和5年11月7日(2023.11.7)

(24)登録日 令和5年10月27日(2023.10.27)

(51)国際特許分類

|         |                 |     |         |             |

|---------|-----------------|-----|---------|-------------|

| G 0 6 F | 1/3209(2019.01) | F I | G 0 6 F | 1/3209      |

| B 4 1 J | 29/38 (2006.01) |     | B 4 1 J | 29/38 1 0 4 |

| H 0 4 N | 1/00 (2006.01)  |     | H 0 4 N | 1/00 8 8 5  |

| G 0 6 F | 1/3231(2019.01) |     | G 0 6 F | 1/3231      |

| G 0 6 F | 1/3234(2019.01) |     | G 0 6 F | 1/3234      |

請求項の数 12 (全12頁)

(21)出願番号 特願2019-112318(P2019-112318)

(22)出願日 令和1年6月17日(2019.6.17)

(65)公開番号 特開2020-204916(P2020-204916)

A)

(43)公開日 令和2年12月24日(2020.12.24)

審査請求日 令和4年6月2日(2022.6.2)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

(74)代理人 100124442

弁理士 黒岩 創吾

(72)発明者 笹原 奈音

東京都大田区下丸子3丁目30番2号キ

ャノン株式会社内

審査官 松浦 かおり

最終頁に続く

(54)【発明の名称】 情報処理装置

**(57)【特許請求の範囲】****【請求項1】**

少なくとも第1電力モードと前記第1電力モードより省電力の第2電力モードとに移行可能な第1制御手段と、

所定の復帰要因を検知し第1の信号を出力する検知手段と、

前記検知手段から出力された前記第1の信号に関する情報を記憶する記憶部を有し、前記記憶部に記憶された前記情報に基づいて第2の信号を出力する第2制御手段と、

前記第2制御手段から出力された前記第2の信号に従って、前記第1制御手段を前記第2電力モードから前記第1電力モードに移行させる第3の信号を出力する第3制御手段と、を備え、

前記第3制御手段は、前記第1電力モードに移行した前記第1制御手段が前記第2電力モードへ移行するときに、前記記憶部に所定の値を設定するよう制御することにより前記第2制御手段の前記記憶部に記憶された前記第1の信号に関する情報をクリアすることを特徴とする情報処理装置。

**【請求項2】**

前記第3制御手段は、前記第2の信号を受信すると、前記第2制御手段から前記第2の信号の出力を無効にする制御を行い、前記第1制御手段により前記第2電力モードから前記第1電力モードに移行すると、前記第2制御手段から前記第2の信号の出力を有効にする制御を行うことを特徴とする請求項1に記載の情報処理装置。

**【請求項 3】**

前記第2制御手段は、前記第1の信号を受信すると、前記第2の信号の出力が有効であることに応じて、前記第3制御手段に、前記第2の信号を出力することを特徴とする請求項2に記載の情報処理装置。

**【請求項 4】**

前記第3制御手段は、前記第1制御手段により前記第2電力モードから前記第1電力モードに移行すると、前記記憶部の前記第1の信号に関する情報をクリアにするよう制御し、その後、前記第2制御手段から前記第2の信号の出力を有効にする制御を行うことを特徴とする請求項2又は3に記載の情報処理装置。

**【請求項 5】**

前記第1制御手段は、前記第2電力モードへ移行するときに、動作停止状態である前記第3制御手段を動作可能状態にして、動作可能状態になった前記第3制御手段は、前記記憶部に前記所定の値を設定するよう制御することを特徴とする請求項1乃至4のいずれか1項に記載の情報処理装置。

**【請求項 6】**

前記動作停止状態とは、リセット信号が入力されている状態であって、前記動作可能状態は、前記リセット信号が入力されていない状態であることを特徴とする請求項5に記載の情報処理装置。

**【請求項 7】**

前記検知手段は、ユーザからの所定の操作を検知する入力部コントローラであることを特徴とする請求項1乃至6の何れか1項に記載の情報処理装置。

10

**【請求項 8】**

前記検知手段は、外部装置であるU S Bホストが送信したデータを受信するU S Bホストコントローラであることを特徴とする請求項1乃至6の何れか1項に記載の情報処理装置。

**【請求項 9】**

前記検知手段は、ネットワークから送信されたデータを受信するネットワークコントローラであることを特徴とする請求項1乃至6の何れか1項に記載の情報処理装置。

**【請求項 10】**

用紙に画像を印刷する印刷手段をさらに備えることを特徴とする請求項1乃至9の何れか1項に記載の情報処理装置。

20

**【請求項 11】**

原稿の画像を読み取る読み取り手段をさらに備えることを特徴とする請求項1乃至10の何れか1項に記載の情報処理装置。

**【請求項 12】**

少なくとも第1電力モードと前記第1電力モードより省電力の第2電力モードとに移行可能な情報処理装置の制御方法であって、

所定の復帰要因を検知し第1の信号を出力する検知工程と、

受信した前記第1の信号に関する情報を記憶する記憶部を有し、前記記憶部に記憶された前記情報に基づいて第2の信号を出力する第2制御工程と、

受信した前記第2の信号に従って、前記情報処理装置を前記第2電力モードから前記第1電力モードに移行させる第3の信号を出力する第3制御工程と、を備え、

前記第3制御工程では、前記第1電力モードに移行した前記情報処理装置が前記第2電力モードへ移行するときに、前記記憶部に所定の値を設定するよう制御することにより前記記憶部に記憶された前記第1の信号に関する情報をクリアにすることを特徴とする情報処理装置の制御方法。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

50

本発明は、復帰要因を検知したときに記憶される情報を記憶する記憶部を初期化することが可能な情報処理装置に関する。

【背景技術】

【0002】

画像形成装置などの情報処理装置は、ネットワークインターフェースやUSB(Universal Serial Bus)インターフェース等に代表される通信インターフェースを介して、外部機器と通信可能に接続される。画像形成装置は、外部機器から受け取った画像データをプリントする機能を備えている。

【0003】

画像形成装置などの情報処理装置は、消費電力を抑えるために通常電力状態の他に、省電力状態を有している。省電力状態においては、通常電力状態のときに動作するメインCPU(Central Processing Unit)やメモリを有するメインシステムの全体又は一部への電力供給が停止される。省電力状態においては、省電力状態から復帰させるために必要なサブCPUやサブCPUに割り込み信号を出力する割り込みコントローラなどの一部のサブシステムのみに電力が供給される。

10

【0004】

画像形成装置は、ユーザによる所定の操作や外部機器からの所定のデータ等に基づいて、省電力状態から通常電力状態に復帰する。省電力状態で動作するサブシステムは、外部機器が送信した所定のデータを検知して、メインシステムを復帰させる。また、省電力状態で動作するサブシステムは、ユーザによる所定の操作を検知して、メインシステムを復帰させる。特許文献1には、メインシステム及びサブシステムを備え、省電力状態において、メインシステムへの電力供給が停止される複合機が開示されている。

20

【先行技術文献】

【特許文献】

【0005】

【文献】特開2005-267099号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ある復帰要因を検知することによって情報処理装置が省電力状態から復帰している最中に、サブシステムが別の復帰要因を検知した場合、メインシステムを復帰させるための情報がサブシステムに保留されたままになってしまうことがある。当該情報がサブシステムに保留されたままになると、次に、情報処理装置が省電力状態に移行したときに、サブシステムが保留されていた情報に基づいて、即座にメインシステムを復帰させてしまう。

30

【0007】

そこで、本発明は、上記の課題を解決するためになされたもので、本発明の目的は、省電力状態に移行した直後にサブシステムに保留された情報によって省電力状態から復帰するのを防止することが可能な情報処理装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記の目的を達成するために、本発明の情報処理装置は、少なくとも第1電力モードと第1電力モードより省電力の第2電力モードとに移行可能な第1制御手段と、所定の復帰要因を検知し第1の信号を出力する検知手段と、検知手段から出力された第1の信号に関する情報を記憶する記憶部を有し、記憶部に記憶された情報に基づいて第2の信号を出力する第2制御手段と、第2制御手段から出力された第2の信号に従って、第1制御手段を第2電力モードから第1モードに移行させる第3の信号を出力する第3制御手段と、を備え、第3制御手段は、第1制御手段が第2電力モードへ移行するときに、前記記憶部に所定の値を設定するよう制御することにより第2制御手段の記憶部に記憶された前記第1の信号に関する情報をクリアにする。

40

【発明の効果】

50

**【 0 0 0 9 】**

本発明によれば、省電力状態に移行した直後に第2制御手段に保留された情報によって省電力状態から復帰するのを防止することができる。

**【図面の簡単な説明】****【 0 0 1 0 】**

【図1】画像形成装置のハードウェアブロック図である。

【図2】割り込みコントローラ及びその周辺デバイスを説明するためのブロック図である。

【図3】割り込みコントローラの詳細を示したブロック図である。

【図4】USBデバイスコントローラの詳細図である。

【図5】画像形成装置が省電力状態へ移行する処理を示したシーケンス図である。 10

【図6】画像形成装置が省電力状態から復帰する処理を示したシーケンス図である。

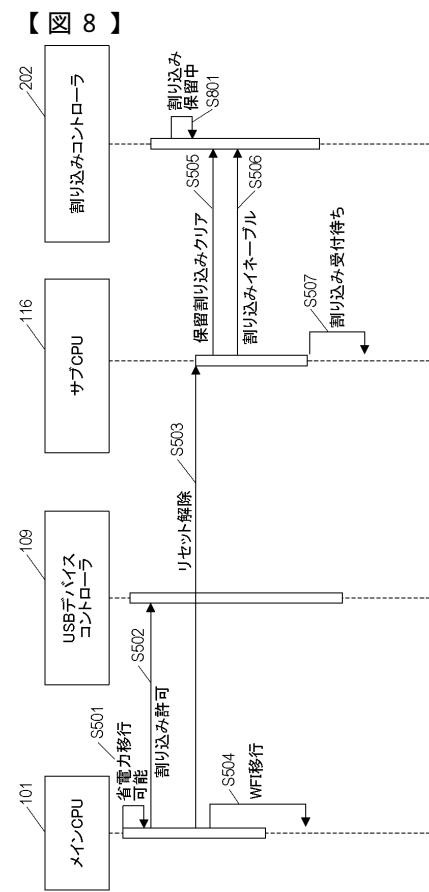

【図7】保留された値をクリアした直後に再度割り込み信号が入力される例を示したシーケンス図である。

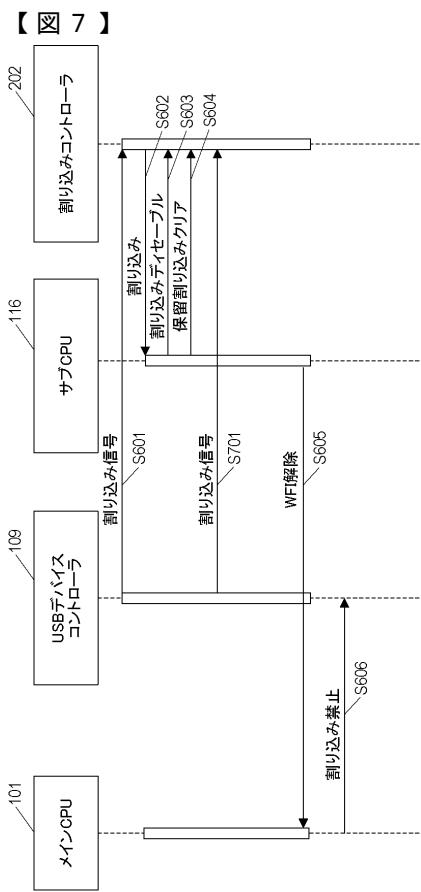

【図8】保留されたレジスタの値をクリアする処理を示したシーケンス図である。

**【発明を実施するための形態】****【 0 0 1 1 】**

以下、本発明を実施するための形態について図面を用いて説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものでなく、また実施形態で説明されている特徴の組み合わせのすべてが発明の解決手段に必須のものとは限らない。

**【 0 0 1 2 】**

図1は、画像形成装置のハードウェアブロック図である。図1を参照して、画像形成装置1の全体構成を説明する。 20

**【 0 0 1 3 】**

画像形成装置1は、メインCPU101と、システムバス102と、サブCPU116と、を備えている。メインCPU101は、ソフトウェアを実行する。システムバス102は、メインCPU101や他のユニットがデータを送受信するための経路である。サブCPU116は、画像形成装置1が省電力状態のときに各ハードウェアからの割り込みを監視する。メインCPU101は、少なくとも第1電力モードと第1電力モードより省電力の第2電力モード（例えば、WFI状態）とに移行可能である。サブCPU116は、割り込み信号が入力されると、メインCPU101を起床させる機能を有する。画像形成装置1は、メインCPU101が実行するソフトウェア、サブCPU116が実行するソフトウェア、画像形成装置1が動作するために必要なデータベース、及び、一時保存ファイルを格納するeMMC103を備える。eMMC103は、HDD(Hard Disk Drive)やSSD(Solid State Drive)といった大容量不揮発性のメモリでも構わない。画像形成装置1は、プログラムが展開され、プログラム動作時の変数や各ユニットからDirect Memory Access(DMA)で転送されるデータの格納領域となるRAM(Random Access Memory)104を備える。また、画像形成装置1は、サブCPU116が実行するプログラムが展開されるRAM117を備える。このRAM117には、画像形成装置1を復帰させたデバイスを特定するための情報が記憶される。メインCPU101は、RAM117にもアクセスすることが可能である。 30

**【 0 0 1 4 】**

画像形成装置1は、ネットワーク上の他の機器と通信を行うネットワークコントローラ105と、ネットワークケーブルが接続されるネットワークI/F106と、を備える。また、画像形成装置1は、USBデバイスとの通信を行うUSBホストコントローラ107と、USBデバイスやUSBケーブルが接続されるUSBホストI/F108と、を備えている。図1では、USBホストI/F108は1つのみであるが、複数あっても良い。また、画像形成装置1は、USBホストと通信を行うUSBデバイスコントローラ109と、USBホストが接続されたUSBケーブルが接続されるUSBデバイスI/F110と、を備えている。画像形成装置1がUSBデバイスとして機能するとき、USBホス 40

10

20

30

40

50

トが送信した印刷データを U S B デバイス I / F 1 1 0 を介して U S B デバイスコントローラ 1 0 9 が受信する。また、画像形成装置 1 が U S B デバイスとして機能するとき、U S B デバイスコントローラ 1 0 9 は、画像形成装置 1 でスキャンした画像データを U S B デバイス I / F 1 1 0 を介して U S B ホストに送信する。

#### 【 0 0 1 5 】

画像形成装置 1 は、ディスプレイ 1 1 2 と、ディスプレイに表示を行うディスプレイコントローラ 1 1 1 と、を備える。ディスプレイ 1 1 2 は、各種画面を表示する。画像形成装置 1 は、ユーザからの入力を受け付ける入力部 1 1 4 と、入力部 1 1 4 を制御する入力部コントローラ 1 1 3 と、を備える。入力部 1 1 4 は、例えば、キーボード、マウス、1 0 キー、カーソルキー、タッチパネルである。入力部 1 1 4 がタッチパネルである場合、ディスプレイ 1 1 2 の表面にタッチパネルが装着されることになる。画像形成装置 1 は、時計機能、アラーム機能、タイマー機能等を有するリアルタイムクロック（以下、R T C ）1 1 5 を備える。

10

#### 【 0 0 1 6 】

画像形成装置 1 は、プリント機能、スキャン機能、コピー機能、データ送信機能などを有するマルチファンクション装置である。画像形成装置 1 は、原稿の画像をスキャンするスキャン機能を有するスキャナ（読み取手段）1 1 9 と、スキャナ 1 1 9 でスキャンされた画像データをシステムバス 1 0 2 に送信するスキャナ I / F 1 1 8 と、を備えている。また、画像形成装置 1 には、用紙に画像を印刷するプリント機能を有するプリンタ（印刷手段）1 2 1 と、プリンタ 1 2 1 に画像データを送・信するプリンタ I / F 1 2 0 と、を備えている。

20

#### 【 0 0 1 7 】

図 2 は、割り込みコントローラ及びその周辺デバイスを説明するためのブロック図である。U S B デバイスコントローラ 1 0 9 、ネットワークコントローラ 1 0 6 、入力部コントローラ 1 1 3 の各ハードウェアは、割り込みコントローラ 2 0 1 及び割り込みコントローラ 2 0 2 に、割り込み信号 a 1 , a 2 , b 1 , b 2 , c 1 , c 2 を送信する。メイン C P U 1 0 1 は、割り込みコントローラ 2 0 1 から入力される割り込み信号 d に基づいて、ハンドラを起動し、各ハードウェアに対してレジスタ設定やデータ通信等の処理を行う。サブ C P U 1 1 6 は、割り込みコントローラ 2 0 2 から入力される割り込み信号 f に基づいて、割り込みハンドラを起動し、省電力状態からの復帰に必要な処理を行う。なお、割り込み信号を出力するハードウェアは、U S B デバイスコントローラ 1 0 9 、ネットワークコントローラ 1 0 6 、入力部コントローラ 1 1 3 に限らない。例えば、スキャナ 1 1 9 によって読み取られる原稿を検知するセンサ、R T C 1 1 5 、図示しない人感センサ、等が割り込み信号を出力しても良い。

30

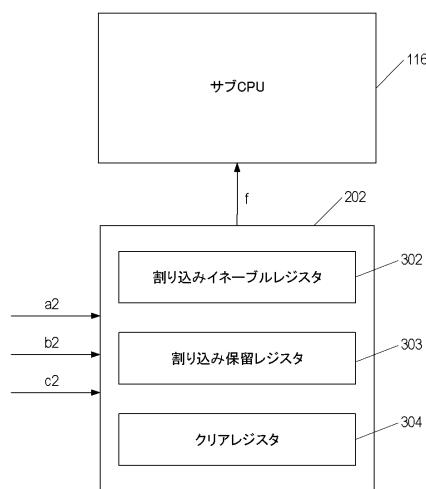

#### 【 0 0 1 8 】

図 3 は、割り込みコントローラ 2 0 2 の詳細を示したブロック図である。割り込みコントローラ 2 0 2 は、複数の記憶部であるレジスタを有している。入力される割り込み信号 a 2 , b 2 , c 2 は、割り込み保留レジスタ 3 0 3 に保留される。割り込み保留レジスタ 3 0 3 は、複数のビットを持ち、各ビットに対してハードウェアが割り当てられている。例えば、割り込み保留レジスタは、U S B デバイスコントローラ 1 0 9 用のビットを持ち、U S B デバイスコントローラ 1 0 9 からの割り込み信号 a 2 が入力されると、当該 U S B デバイスコントローラ 1 0 9 用のビットが 1 となる。また、割り込み保留レジスタ 3 0 3 は、ネットワークコントローラ 1 0 6 用のビットを持ち、ネットワークコントローラ 1 0 6 からの割り込み信号 b 2 が入力されると、当該ネットワークコントローラ 1 0 6 用のビットが 1 となる。また、割り込み保留レジスタ 3 0 3 は、入力部コントローラ 1 1 3 用のビットを持ち、入力部コントローラ 1 1 3 からの割り込み信号 c 2 が入力されると、当該入力部コントローラ 1 1 3 用のビットが 1 となる。割り込み保留レジスタ 3 0 3 がハードウェア毎にビットを持つことによって、どのハードウェアから割り込み信号が入力されたのかを判別することが可能となる。サブ C P U 1 1 6 は、どのハードウェアから割り込み信号が入力されたかを判定して、R A M 1 1 7 に割り込み信号を出力したハードウェア

40

50

を特定する情報を記憶する。サブCPU116は、割り込み信号fが入力されると、割り込み保留レジスタ303を参照して、どのデバイスからの割り込みかを特定し、その情報をRAM117に記憶する。

#### 【0019】

割り込みイネーブルレジスタ302は、ハードウェアからの割り込みを有効または無効に設定する。割り込みイネーブルレジスタ302も、割り込み保留レジスタ303と同様に複数のビットを持ち、これらの複数のビットは、割り込み保留レジスタ303の複数のビットと対応する関係になっている。割り込みイネーブルレジスタ302の所定のビットが1(有効)になっていれば、当該所定のビットに対応する割り込み保留レジスタ303のビットに基づいて、サブCPU116に割り込み信号fが出力される。一方、割り込みイネーブルレジスタ302の所定のビットが0(無効)になっていれば、当該所定のビットに対応する割り込み保留レジスタ303のビットが1であっても、サブCPU116に割り込み信号fは出力されない。

10

#### 【0020】

クリアレジスタ304は、割り込み保留レジスタ303に設定されたビットをクリアする。ビットのクリアとは、ビットの値を初期値に設定することである。クリアレジスタ304も、割り込み保留レジスタ303と同様に複数のビットを持ち、これらの複数のビットは、割り込み保留レジスタの複数のビットと対応する関係になっている。クリアレジスタ304の所定のビットに1を書き込むと、当該所定のビットに対応する割り込み保留レジスタ303のビットが0にクリアされる。割り込み保留レジスタ303に保留されている値は、クリアレジスタ304のビットに1が書き込まれるまで、保留されたままとなる。

20

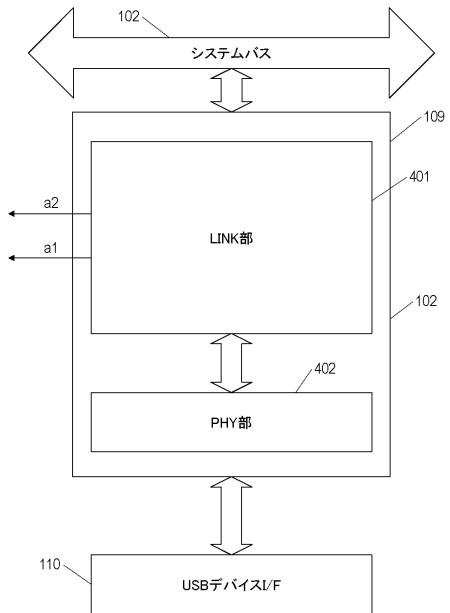

#### 【0021】

図4は、USBデバイスコントローラ109の詳細図である。USBデバイスコントローラ109は、LINK部401と、PHY部402と、を有している。LINK部401は、システムバス102を介して、メインCPU101等とのデータ通信を行う。また、LINK部401は、USBデバイスとして機能するためのディスクリプタ情報を保持する機能、割り込み信号a1, a2を出力する機能を持つ。PHY部402は、USBデバイスI/F110を介して、外部のUSBホストとデータ通信を行うための機能を持つ。なお、ネットワークコントローラ105および入力部コントローラ113も、USBデバイスコントローラ109と同様の機能を有しているが、その説明は割愛する。

30

#### 【0022】

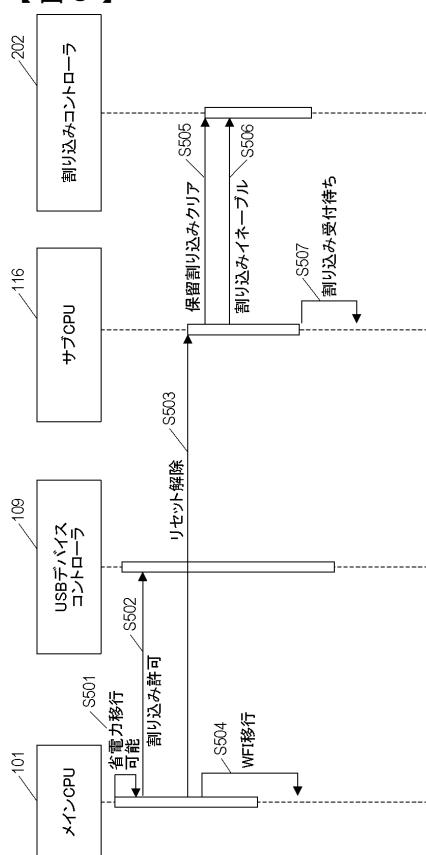

図5は、画像形成装置1が省電力状態へ移行する処理を示したシーケンス図である。

#### 【0023】

省電力状態への移行条件を満たすと、メインCPU101が省電力状態への移行が可能だと判断する(S501)。省電力状態への移行条件は、例えば、図示しない省電力状態への移行を行うためのキーの操作、入力部114が操作されずに経過した時間が閾値となつた、等である。省電力状態への移行が可能だと判定すると、メインCPU101は、USBデバイスコントローラ109に対して割り込みを許可する(S502)。この割り込みの許可とは、具体的には、メインCPU101が、USBデバイスコントローラ107の所定のレジスタに対して、割り込みを許可する情報として、1に書き込むことである。そして、メインCPU101は、サブCPU116のリセットを解除する(S503)。つまり、リセット信号をHighレベルにする。リセットが解除されたサブCPU116は、動作可能状態となる。リセット中(リセット信号がLowレベルの間)は、サブCPU116は、動作停止状態となっている。また、メインCPU101は、第1電力モードから第1電力モードより省電力の第2電力モードに移行する。この第2電力モードは、例えば、Wait For Interrupt(WFI)状態である(S504)。WFI状態は、待機状態であってメインCPU101の消費電力を抑えることができるモードである。WFI状態で割り込み信号eが入力されると、メインCPU101は、WFI状態から通常状態に復帰する。リセットが解除されたサブCPU116は、RAM117に展開されていたプログラムを予め定められたアドレスから読み出して、実行する。ここで、

40

50

本実施形態では、サブCPU116は、割り込みコントローラ202に保留されたレジスタをクリアする処理を行う(S505)。S505の保留された割り込みをクリアする処理は、割り込みコントローラ202の割り込みクリアレジスタ304のビットに1を書き込む処理である。サブCPU116は、割り込み保留レジスタ303の全てのビットをクリアしてもよいし、特定のビットのみをクリアしても良い。

#### 【0024】

次に、サブCPU116は、割り込みコントローラ202からの割り込みをイネーブルする処理を行う(S506)。S506の割り込みをイネーブルする処理は、割り込みコントローラ202の割り込みイネーブルレジスタ303のビットに1を書き込む処理である。サブCPU116は、割り込みイネーブルレジスタ303の全てのビットに1を書き込んでも良いし、特定のビットのみに1を書き込んでも良い。その後、サブCPU116は、待機状態となり(S507)、割り込みコントローラ202からの割り込み信号fが入力されるまで待機する。

10

#### 【0025】

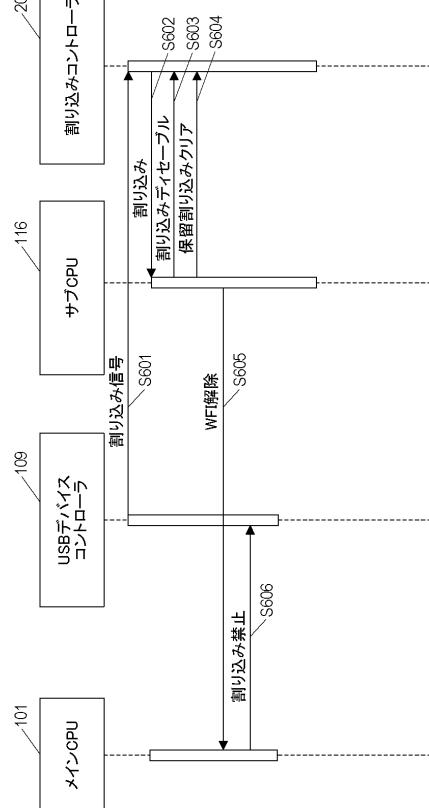

図6は、画像形成装置1が省電力状態から復帰する処理を示したシーケンス図である。

#### 【0026】

USBデバイスコントローラ109が、USBデバイスI/F110を介して、パケットを受信すると、パケットを受信したUSBデバイスコントローラ109が、割り込みコントローラ202に対して、割り込み信号a2を出力する(S601)。USBデバイスコントローラ109は、復帰要因として、パケットの受信を検知すると、割り込み信号a2を出力する。なお、USBデバイスコントローラ109は、パケットの内容に関わらず割り込み信号a2を出力しても良いし、パケットが特定のパケットであるときに割り込み信号a2を出力しても良い。

20

#### 【0027】

割り込み信号a2が入力された割り込みコントローラ202は、サブCPU116に対して割り込み信号fを出力する(S602)。割り込み信号fが入力されたサブCPU116は、割り込みコントローラ202からの割り込みをディセーブルする処理を行う(S603)。S603のディセーブル処理は、割り込みコントローラ202の割り込みイネーブルレジスタの所定のビットに0を書き込む処理である。そして、サブCPU116は、割り込みコントローラ202に保留されている値をクリアする処理を実行する(S604)。S604のクリアする処理は、割り込みコントローラ202のクリアレジスタ304の所定のビットに0を書き込む処理である。クリアレジスタ304の所定のビットに0が書き込まれると、割り込み保留レジスタ303の対応する所定のビットがクリアされる。

30

#### 【0028】

そして、サブCPU116は、メインCPU101に割り込み信号eを出力することで、メインCPU101は、WFI状態から復帰する(S605)。WFI状態から復帰したメインCPU101は、USBデバイスコントローラ109に対して、割り込み禁止の設定をする(S606)。

#### 【0029】

図7は、割り込みコントローラ202に保留された値をクリアした直後に再度割り込み信号が入力される例を示した図である。サブCPU11が、割り込みコントローラ202に保留された値をクリアする処理を実行した後に(S604)、再度、USBデバイスコントローラ109が、USBデバイスI/F110を介して、パケットを受信する。そうすると、パケットを受信したUSBデバイスコントローラ109が、割り込みコントローラ202に対して、割り込み信号a2を出力する(S701)。このとき、割り込み保留レジスタ303の所定のビットが1となる。サブCPU116が割り込みコントローラ202からの割り込みをディセーブルにしているため、割り込みコントローラ202は、割り込み信号fを出力しない。そして、割り込みコントローラ202の割り込み保留レジスタ303の所定のビットがクリアされない。

40

#### 【0030】

50

図8は、S701によって保留されたレジスタの値をクリアする処理を示した図である。上記したように、割り込みコントローラ202の割り込み保留レジスタ303の所定のビットはクリアされていない(S801)。この状況で、省電力状態への移行条件を満たすと、サブCPU116は、割り込みコントローラ202に保留された割り込みをクリアする処理を行う(S505)。これにより、クリアされなかった割り込み保留レジスタ303の所定のビットがクリアされる。その結果、S506で割り込みコントローラ202からの割り込みをイネーブルする処理を行っても、省電力状態に移行した画像形成装置1が即座に省電力状態から復帰しない。

#### 【0031】

##### (その他の実施例)

上記した実施形態では、S505においてサブCPU116が割り込み保留レジスタ303の所定のビットをクリアしたが、メインCPU101が割り込み保留レジスタ303の所定のビットをクリアしても良い。また、メインCPU101やサブCPU116以外のデバイスが割り込み保留レジスタ303の所定のビットをクリアしても良い。

#### 【0032】

また、上記した実施形態では、S501のメインCPUがEFI状態への移行条件に従って、割り込み保留レジスタ303の所定のビットをクリアしたが、当該所定のビットをクリアするタイミングは、上記した移行条件に限定されない。例えば、S506の割り込みイネーブル後の所定のタイミングで、当該所定のビットをクリアすればよい。また、定期的に所定のビットをクリアしても良い。

#### 【0033】

上記した実施形態では、本発明の情報処理装置の一例として画像形成装置について説明したが、本発明の情報処理装置は、画像形成装置に限定されない。例えば、本発明の電子機器は、ノートPC、タブレットPC、デスクトップPC、スマートフォン、自動車、空調機、遊技機、ロボットなど種々の情報処理装置に適用可能である。

#### 【0034】

本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体を、システムあるいは装置に供給することによっても達成される。この場合、そのシステムあるいは装置のコンピュータ（またはCPUやMPU）が記録媒体に格納されたプログラムコードを読み出し実行することにより、上記機能が実現されることとなる。なお、この場合、そのプログラムコードを記憶した記録媒体は本発明を構成することになる。

#### 【0035】

プログラムコードを供給するための記録媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

#### 【0036】

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現される場合に限られない。例えば、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているOS（オペレーティングシステム）などが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれる。

#### 【0037】

さらに、記録媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれた後、前述した実施形態の機能が実現される場合も含まれる。つまり、プログラムコードがメモリに書き込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によって実現される場合も含まれる。

#### 【符号の説明】

10

20

30

40

50

【 0 0 3 8 】

## 1 画像形成装置

101 メイン C P U

## 105 ネットワークコントローラ

109 USBデバイスコン

113 入力部コン

## 1 1 6 サブ C P U

202 割り込みコントローラ

### 302 割り込みイネーブルレ

303 割り込み保留レ

3 0 4

【 図 面 】

10

【 2 】

The diagram illustrates the system architecture with the following components and their connections:

- Main CPU** (101) and **Sub CPU** (116) are connected by a bidirectional arrow labeled **e**.

- 割り込みコントローラ** (Interrupt Controller) (201) and **割り込みコントローラ** (Interrupt Controller) (202) are connected to both the Main CPU (101) and Sub CPU (116).

- USBデバイスコントローラ** (USB Device Controller) (109) and **ネットワークコントローラ** (Network Controller) (106) are connected to the **割り込みコントローラ** (201).

- 入力部コントローラ** (Input Port Controller) (113) is connected to the **割り込みコントローラ** (202).

- Arrows indicate the direction of data flow: **a1** from **USBデバイスコントローラ** to **割り込みコントローラ** (201); **a2** from **USBデバイスコントローラ** to **Sub CPU** (116); **b1** from **ネットワークコントローラ** to **割り込みコントローラ** (201); **b2** from **ネットワークコントローラ** to **Sub CPU** (116); **c1** from **入力部コントローラ** to **割り込みコントローラ** (202); and **c2** from **入力部コントローラ** to **Sub CPU** (116).

20

30

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2009-260918(JP,A)

特開2018-157603(JP,A)

特開2000-183894(JP,A)

特開2016-158174(JP,A)

特開昭58-097758(JP,A)

米国特許出願公開第2011/0235535(US,A1)

特開2011-205580(JP,A)

- (58)調査した分野 (Int.Cl., DB名)

- G06F 1/26 - 1/3296

G06F 3/09 - 3/12

B41J 29/00 - 29/70

H04N 1/00