(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第4176769号 (P4176769)

(45) 発行日 平成20年11月5日(2008.11.5)

(24) 登録日 平成20年8月29日(2008.8.29)

(21) ± 34 1 1 /3420 1 0) 1 2 0 11 (2000:0:

(51) Int.Cl. HO3K 19/0175 (2006.01)

HO3K 19/00 101K

請求項の数 42 (全 18 頁)

(21) 出願番号 特願2005-517223 (P2005-517223) (86) (22) 出願日 平成17年1月14日 (2005.1.14)

(86) 国際出願番号 PCT/JP2005/000328

(86) 国際出願番号 PCI/JP2005/00032 (87) 国際公開番号 W02005/071838

(87) 国際公開日 平成17年8月4日 (2005.8.4) 審査請求日 平成18年5月10日 (2006.5.10) (31) 優先権主張番号 特願2004-12717 (P2004-12717)

(32) 優先日 平成16年1月21日 (2004.1.21)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

|(74)代理人 100081938

弁理士 徳若 光政

(72)発明者 工藤 良太郎

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

||(72)発明者 立野 孝治

茨城県日立市大みか町七丁目1番1号 株

式会社日立製作所 日立研究所内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】電圧クランプ回路、スイッチング電源装置、半導体集積回路装置及び電圧レベル変換回路

# (57)【特許請求の範囲】

# 【請求項1】

入力電圧が供給される入力端子と、

上記入力端子にソース,ドレイン経路の一方が接続され、ゲートに所定電圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた電流源とを有し、

上記電流源と並列形態にキャパシタが設けられ、

上記MOSFETのソース,ドレイン経路の他方から出力電圧を得ることを特徴とする電圧クランプ回路。

# 【請求項2】

請求項1において、

上記キャパシタは、上記MOSFETのドレイン,ソース間寄生容量に対して十分大きな容量値を持つようにされてなるMOS容量であり、

上記電流源はゲートとソースが接続されたディプレッション型MOSFETであることを特徴とする電圧クランプ回路。

# 【請求項3】

請求項2において、

上記出力電圧は、上記入力電圧よりも小さな電源電圧で動作する第1CMOSインバータ回路の入力に伝えられることを特徴とする電圧クランプ回路。

# 【請求項4】

請求項1において、

上記電圧クランプ回路は、半導体集積回路装置に搭載され、

上記入力端子は、半導体集積回路装置の外部端子であり、静電気破壊防止回路が設けられてなることを特徴とする電圧クランプ回路。

# 【請求項5】

請求項4において、

上記第1CMOSインバータ回路の出力信号は、次段の第2CMOSインバータ回路の 入力に伝えられ、

かかる第2CMOSインバータ回路の出力信号は、上記第2CMOSインバータ回路の入力端子との回路の接地電位との間に設けられたMOSFETのゲートに帰還され、上記第1CMOSインバータ回路がヒステリシス伝達特性を持つようにされてなることを特徴とする電圧クランプ回路。

# 【請求項6】

請求項5において、

上記MOSFETは、Nチャネル型とされ、

上記入力電圧は、正の電圧であることを特徴とする電圧クランプ回路。

#### 【請求項7】

請求項1において、

上記電流源は直流的な電流成分を流すことが可能なことを特徴とする電圧クランプ回路

20

30

40

10

#### 【請求項8】

請求項7において、

上記出力電圧は、上記入力電圧よりも小さな電源電圧で動作する入力回路の入力部に伝えられ、上記所定電圧は、上記電源電圧であり、

上記入力回路は上記キャパシタと並列形態に容量成分を持っていることを特徴とする電 圧クランプ回路。

# 【請求項9】

請求項1において、

上記MOSFETの基板は上記MOSFETのソース,ドレイン経路の他方と接続されていることを特徴とする電圧クランプ回路。

# 【請求項10】

入力電圧が供給される入力ノードにソース,ドレイン経路の一方が接続され、ゲートに 所定電圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた 直流的な電流成分を流すことが可能な電流源とを有し、

上記電流源と並列形態にキャパシタが設けられ、

上記MOSFETのソース,ドレイン経路の他方から出力電圧を得ることを特徴とする 電圧レベル変換回路。

# 【請求項11】

請求項10において、

上記キャパシタは、上記MOSFETのドレイン,ソース間寄生容量に対して十分大きな容量値を持つようにされてなるMOS容量であり、

上記電流源はゲートとソースが接続されたディプレッション型MOSFETであることを特徴とする電圧レベル変換回路。

# 【請求項12】

請求項11において、

上記出力電圧は、上記入力電圧よりも小さな電源電圧で動作する第1CMOSインバータ回路の入力に伝えられ、

上記所定電圧は、上記電源電圧であることを特徴とする電圧レベル変換回路。

# 【請求項13】

請求項10において、

上記電圧レベル変換回路は、一つの半導体基板上に搭載されることを特徴とする電圧レベル変換回路。

# 【請求項14】

請求項13において、

上記電圧レベル変換回路は、半導体集積回路装置に搭載され、

上記入力ノードは半導体集積回路装置の外部端子であり、静電気破壊防止回路が設けられてなることを特徴とする電圧レベル変換回路。

# 【請求項15】

請求項12において、

上記第1CMOSインバータ回路の出力信号は、次段の第2CMOSインバータ回路の 入力に伝えられ、

かかる第2CMOSインバータ回路の出力信号は、上記第2CMOSインバータ回路の入力端子と回路の接地電位との間に設けられたMOSFETのゲートに帰還され、上記第1CMOSインバータ回路がヒステリシス伝達特性を持つようにされてなることを特徴とする電圧レベル変換回路。

### 【請求項16】

請求項12において、

上記MOSFET及びディプレッションMOSFETは、Nチャネル型とされ、

上記入力電圧及び電源電圧は、正の電圧であることを特徴とする電圧レベル変換回路。

# 【請求項17】

請求項10において、

上記出力電圧は、上記入力電圧よりも小さな電源電圧で動作する入力回路の入力部に伝えられ、

上記所定電圧は、上記電源電圧であり、

上記入力回路は、上記キャパシタと並列形態に容量成分を持っていることを特徴とする 電圧レベル変換回路。

# 【請求項18】

請求項10において、

上記MOSFETの基板は上記MOSFETのソース,ドレイン経路の他方と接続されていることを特徴とする電圧レベル変換回路。

#### 【請求項19】

インダクタと、

上記インダクタに直列形態に設けられて出力電圧を形成する第1キャパシタと、

入力電圧をスイッチング制御することにより上記インダクタに流す電流を制御する第 1 スイッチ素子と、

上記第1スイッチ素子がオフ状態のときにオン状態であるような時間を有するようスイッチング動作が行われ、上記電流を制御する第2スイッチ素子と、

入力電圧に対応した第一の電圧により動作し、上記第1スイッチ素子を駆動する第1駆 動回路と、

第二の電圧により動作し、上記第2スイッチ素子を駆動する第2駆動回路と、

上記第1キャパシタから得られる上記出力電圧が所定電圧となるようにPWM信号を形成する制御回路と、

上記入力電圧又は第二の電圧以下の第三の電圧で動作し、上記 P W M 信号を受けて上記第 1 駆動回路と第 2 駆動回路の駆動信号を形成する制御論理回路とを備え、

上記制御論理回路は、

上記第1スイッチ素子のための駆動信号を上記第三の電圧に対応して電圧クランプ して上記第2駆動回路の入力に帰還する第1電圧クランプ回路と、上記第2スイッチ素子 のための駆動信号を上記第三の電圧に対応して電圧クランプして上記第1駆動回路の入力 10

20

. .

30

40

に帰還する第2電圧クランプ回路とを備えて上記第1と第2スイッチ素子が同時にオン状態とならないようにスイッチング制御を行うものであり、

上記第1及び第2電圧クランプ回路それぞれは、

入力ノードと、

上記入力ノードにソース,ドレイン経路の一方が接続され、ゲートに上記第三の電圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた電流源とを有し、

上記MOSFETのソース,ドレイン経路の他方から上記入力ノードからの信号を 電圧クランプした帰還信号を得ることを特徴とするスイッチング電源装置。

【請求項20】

請求項19において、

第3電圧クランプ回路を有し、

上記第3電圧クランプ回路は、

上記スイッチング電源装置の有効/無効(ON/OFF)を制御するための入力信号が供給される入力ノードと、

上記入力ノードにソース,ドレイン経路の一方が接続され、ゲートに上記第三の電圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた電流源と、

上記MOSFETのソース,ドレイン経路の他方から上記入力信号を電圧クランプ した制御信号を得ることを特徴とするスイッチング電源装置。

# 【請求項21】

請求項19において、

上記電流源には、並列形態に第 2 キャパシタが設けられてなることを特徴とするスイッチング電源装置。

# 【請求項22】

請求項21において、

上記第2キャパシタは、上記MOSFETのドレイン,ソース間寄生容量に対して十分大きな容量値を持つようにされてなるMOS容量であり、

上記電流源はゲートとソースが接続されたディプレッション型MOSFETであることを特徴とするスイッチング電源装置。

#### 【請求項23】

請求項19において、

上記電流源は直流的な電流成分を流すことが可能なことを特徴とするスイッチング電源 装置。

# 【請求項24】

請求項23において、

上記電流源と並列形態に第2キャパシタが設けられることを特徴とするスイッチング電源装置。

# 【請求項25】

請求項24において、

上記帰還信号は、上記駆動信号よりも小さな上記第三の電圧で動作する上記制御論理 回路の入力部に伝えられていることを特徴とするスイッチング電源装置。

# 【請求項26】

入力電圧を降圧して出力電圧を形成するための電流を制御する第1スイッチ素子と、 上記電流を流す為の端子と、

上記第1スイッチ素子がオフ状態のときにオン状態であるような時間を有するようスイッチング動作が行われ、上記電流を制御する第2スイッチ素子と、

上記入力電圧に対応した第一の電圧により動作し、上記第1スイッチ素子を駆動する第

10

20

30

30

40

#### 1駆動回路と、

第二の電圧により動作し、上記第2スイッチ素子を駆動する第2駆動回路と、

上記入力電圧又は第二の電圧以下の第三の電圧で動作し、上記第1スイッチ素子と第二スイッチ素子のための制御用信号を受けて上記第1駆動回路と第2駆動回路の駆動信号を 形成する制御論理回路とを備え、

上記制御論理回路は、

上記第1スイッチ素子のための駆動信号を上記第三の電圧に対応して電圧レベル変換して上記第2駆動回路の入力に帰還する第1電圧レベル変換回路と、上記第2スイッチ素子のための駆動信号を上記第三の電圧に対応して電圧レベル変換して上記第1駆動回路の入力に帰還する第2電圧レベル変換回路とを備えて上記第1と第2スイッチ素子が同時にオン状態とならないようにスイッチング制御を行うものであり、上記第1スイッチ素子と、上記端子と、上記第2スイッチ素子と、上記第1駆動回路と、上記第2駆動回路と、上記制御論理回路とが一つのパッケージに封止され、

上記制御用信号はPWM信号であり、

上記第1及び第2電圧レベル変換回路それぞれは、

上記駆動信号が供給される入力ノードと、

<u>上記入力ノードにソース,ドレイン経路の一方が接続され、ゲートに上記第三の電</u>圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた直流的な電流成分を流すことが可能な電流源と、

上記MOSFETのソース,ドレイン経路の他方から上記駆動信号を電圧レベル変換した帰還信号を得るものであることを特徴とする半導体集積回路装置。

# 【請求項27】

請求項26において、

上記半導体集積回路装置は更に第3電圧レベル変換回路を有し、

上記第3電圧レベル変換回路は上記一つのパッケージに封止され、

上記第3電圧レベル変換回路は、

上記半導体集積回路装置の有効 / 無効 (ON / OFF) を制御するための入力信号が供給される入力端子と、

上記入力端子にソース,ドレイン経路の一方が接続され、ゲートに上記第三の電圧が与えられたMOSFETと、

上記MOSFETのソース,ドレイン経路の他方と回路の接地電位との間に設けられた直流的な電流成分を流すことが可能な電流源と、

上記MOSFETのソース,ドレイン経路の他方から上記入力信号を電圧レベル変換した制御信号を得ることを特徴とする半導体集積回路装置。

# 【請求項28】

請求項26において、

上記電流源には、並列形態にキャパシタが設けられてなることを特徴とする半導体集積 回路装置。

# 【請求項29】

請求項28において、

上記キャパシタは、上記MOSFETのドレイン,ソース間寄生容量に対して十分大きな容量値を持つようにされてなるMOS容量であり、

上記電流源はゲートとソースが接続されたディプレッション型MOSFETであることを特徴とする半導体集積回路装置。

# 【請求項30】

請求項26において、

上記帰還信号は、上記駆動信号よりも小さな上記第三の電圧で動作する上記制御論理回路の入力部に伝えられていることを特徴とする半導体集積回路装置。

# 【請求項31】

20

10

30

40

請求項26において、

上記電流はインダクタと上記インダクタに直列形態に設けられた容量により上記出力電圧を形成するために上記入力電圧の生成部から上記インダクタに流す電流であることを特徴とする半導体集積回路装置。

# 【請求項32】

入力電圧が供給される入力端子と、

上記入力端子にソース、ドレイン経路の一方が接続されゲートに所定電圧が与えられた MOSFETと、

上記MOSFETのソース、ドレイン経路の他方と回路の接地電位との間に設けられた 部位とを有し、

上記MOSFETのソース、ドレイン経路の他方から出力電圧を得るものであり、

上記入力電圧が上記所定電位に対応する電圧以上であった場合には、上記ソース、ドレイン経路の他方から上記所定電位に対応する上記出力電圧が出力され、

上記部位は上記接地電位よりも大きい電圧が上記ソース、ドレイン経路の他方に印加されている場合には、上記ソース、ドレイン経路の他方の電圧が上記接地電位に近づくような電流が流れる事が可能に構成され、

上記部位と並列形態にキャパシタが設けられてなることを特徴とする電圧レベル変換回 【請求項33】

請求項32において、

上記入力電圧が上記所定電位に対応する電圧未満であった場合には、上記ソース、ドレイン経路の他方から上記入力電圧に対応する上記出力電圧が出力されることを特徴とする電圧レベル変換回路。

# 【請求項34】

請求項32において、

上記接地電位に近づくような電流は、上記電圧レベル変換回路の不良と見なされない程度の微小な電流であることを特徴とする電圧レベル変換回路。

# 【請求項35】

請求項32において、

上記部位はゲートとソースが接続されたディプレッション型MOSFETであることを 特徴とする電圧レベル変換回路。

# 【請求項36】

請求項32において、

上記部位はポリシリコンで形成された抵抗素子であることを特徴とする電圧レベル変換回路。

# 【請求項37】

請求項32において、

上記キャパシタは、上記MOSFETのドレイン,ソース間寄生容量に対して十分大きな容量値を持つようにされてなるMOS容量であることを特徴とする電圧レベル変換回路

# 【請求項38】

請求項26において、

上記第1スイッチ素子は第一の半導体基板上に構成されていて、

上記第2スイッチ素子は第二の半導体基板上に構成されていて、

上記第一の半導体基板と上記第二の半導体基板とが上記一つのパッケージに封止されていることを特徴とする半導体集積回路装置。

# 【請求項39】

請求項38において、

上記第1駆動回路と上記第2駆動回路と上記制御論理回路とは第三の半導体基板上に形成されていて、

上記第三の半導体基板が上記一つのパッケージに封止されていることを特徴とする半導

10

20

30

40

#### 体集積回路装置。

# 【請求項40】

請求項26において、

上記第1スイッチ素子と、上記第2スイッチ素子と、上記第1駆動回路と、上記第2駆動回路と、上記制御論理回路とが一つの半導体基板上に構成されており、上記一つの半導体基板が上記一つのパッケージに封止されていることを特徴とする半導体集積回路装置。

#### 【請求項41】

請求項26において、

上記半導体集積回路装置の有効 / 無効を制御するための入力信号が供給される第一制御端子と、

10

20

30

上記PWM信号を受ける第二制御端子と、

上記第二の電圧を供給する為の電源端子とを有し、

上記電源端子に外部から電源を供給することにより上記第二の電圧を所定の範囲で任意 に設定可能であることを特徴とする半導体集積回路装置。

# 【請求項42】

請求項41において、

上記入力電圧を検出する為の検出回路を有し、検出結果に従って上記制御論理回路を制御することを特徴とする半導体集積回路装置。

#### 【発明の詳細な説明】

#### 【技術分野】

[00001]

この発明は、電圧クランプ回路(電圧レベル変換回路)、スイッチング電源装置及びそれに用いられる半導体集積回路装置に関し、例えば、高電圧を低電圧に変換するスイッチング電源装置に用いられるものに適用して有効な技術に関するものである。

#### 【背景技術】

[0002]

MOSFETを用いた電圧クランプ回路の例として、特開平6-69435号公報、特開平5-327465号公報に記載のものがある。

【特許文献 1 】特開平 6 - 6 9 4 3 5 号公報

【特許文献2】特開平5-327465号公報

【発明の開示】

【発明が解決しようとする課題】

[0003]

上記公報記載の電圧クランプ回路においては、MOSFETのクランプした出力電圧を 形成する出力側ノードがフローティングとなっており、そこにリーク電流が流れ込んで出 カノード側がゲート電圧以上に上昇しまうと、電圧クランプ動作が行われなくなる等問題 を有する。

[0004]

本発明の目的は、簡単な構成で安定的に動作する電圧クランプ回路と、高速動作を可能としたスイッチング電源装置を提供することにある。この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

40

# 【課題を解決するための手段】

# [0005]

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。すなわち、入力電圧が供給される入力端子にソース,ドレイン経路の一方を接続し、ゲートに制限すべき所定電圧を与え、ソース,ドレイン経路の他方と回路の接地電位との間に電流源を設けたMOSFETを用いて、上記ソース,ドレイン経路の他方から入力電圧に対応したクランプ出力電圧を得る。

# [0006]

インダクタにキャパシタを直列形態に接続して平滑出力電圧を形成し、入力電圧から上

記インダクタに流す電流を制御して上記出力電圧が所定電圧となるようにする第1スイッチ素子がオフ状態のときに上記インダクタに発生する逆起で上を所定電位にクランプする第2スイッチ素子を備えたスイッチ」と高電圧信号により取動し、上記第2スイッチ素子を第2駆動回路により上記高電圧により駆動し、上記入力を表子を第2駆動回路により上記高電圧により駆動によりも低い低電圧で動作し、上記キャパシタから得られる出力電圧が所定電圧とおりもにといいまりも低い低電圧で動作し、上記キャパシタから得られる出力電圧が所定電圧のまたのと第2を設け、上記第1を対応して上記第1を動画路の駆動信号を形成する制プの路を設け、上記第1スイッチ素子の駆動信号を形成する対応して上記第1を設定と、上記第1を表別では、上記第1を表別では、上記第1を表別では、上記第1を表別では、上記第1を表別では、上記第1を表別では、上記第1を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、上記を表別では、デートに上記に、上記を表別では、デレイン経路の他方を接続に電流源を設けたMOSFETを用いて、上記ソース、デレイン経路の他方から駆動信号に対応した帰還信号を得る。

#### 【発明の効果】

# [0007]

高速かつ低消費電力で安定的に電圧クランプ動作を行うようにすることができる。

【発明を実施するための最良の形態】

#### [00008]

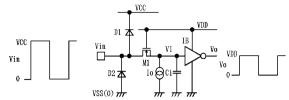

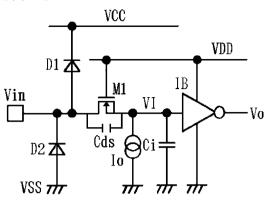

図1には、この発明に係る電圧クランプ回路の一実施例の回路図が示されている。同図の電圧クランプ回路は、半導体集積回路装置の外部入力端子から供給される高い信号振幅 VCCの入力信号Vinを、半導体集積回路装置に形成される入力回路IBの動作電圧V DDレベルに対応した入力電圧VIに電圧クランプする入力回路に向けられている。

#### [0009]

入力端子Vinには、静電破壊防止回路としてのダイオードD1とD2が設けられる。特に制限されないが、この実施例の入力回路を有する半導体集積回路装置は、高い電圧VCCと、それよりも低い電圧VDDの2つの電源端子を有する。上記ダイオードD1は、上記入力端子Vinと高電源端子VCCとの間に設けられ、上記ダイオードD2は、上記入力端子Vinと回路の接地電位VSSとの間に設けられる。特に制限されないが、上記電源電圧VCCは、約12Vのような高い電圧であり、上記電源電圧VDDは約5Vのような低い電圧である。図1において、記号Vinは入力端子及び入力信号の両方の意味で用いている。

# [0010]

上記入力端子Vinは、入力ノードである電圧クランプ回路を構成するNチャネルMOSFETM1の一方のソース,ドレイン経路に接続される。このMOSFETM1のゲートには、制限すべき電圧として電源電圧VDDが供給される。上記MOSFETM1のソース,ドレイン経路の他方から上記電源電圧VDDによりクランプされた出力電圧が得られ、入力回路IBの入力端子に伝えられる。この実施例では、上記MOSFETM1による電圧クランプ動作を安定的に行うようにするために、上記ソース,ドレイン経路の他方と回路の接地電位との間に直流的な電流成分を流すことが可能な電流源Ioが設けられる。また、上記電流源Ioに対して並列形態にキャパシタCiが設けられる。

# [0011]

この実施例では、入力端子Vinは、同図に波形として示されているようにVCC-0V(12V-0V)のような大きな信号振幅の入力信号が供給され、上記MOSFETM1のソース,ドレイン経路の他方からは、(VDD-Vth)-0Vのように電源VDDにより制限された小さな信号振幅に変換される。そして、入力回路IBを通した出力信号Voは、同図に波形として示されているようにVDD-0V(5V-0V)のようなCMOS振幅とされる。ここで、VthはMOSFETM1のしきい値電圧である。もし、MOSFETM1の基板が入力端子Vinに接続されていたら、MOSFETM1は入力端

10

20

30

40

子Vinから入力回路IBの方向のダイオードが接続されているのと同じ働きとなり、電圧クランプ効果が得られない。又、MOSFETM1の基板をVSSに接続しても構わないものの、基板バイアス効果によりしきい値電圧Vthが高くなり、次段の入力回路IBの論理スレッショルドに入力端子Vinからの入力信号が到達しないことにより誤動作を起こす恐れがある。よって本実施例ではMOSFETM1は、電気的に基板から分離されたP型ウェル領域に形成され、かかるP型ウェル(チャネル領域)は、上記MOSFETM1の出力側であるソース,ドレイン経路の他方に接続されている。そうすることにより、安定的にクランプ動作を行う事ができる。

# [0012]

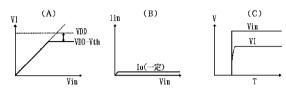

図2には、この発明に係る電圧クランプ回路の動作を説明するための特性図が示されている。図2(A)は、入出力電圧特性図であり、入力電圧Vinが0VからVCCに向かって変化した場合、出力電圧VIはVDD・Vthまでは入力電圧Vinに対応して変化するが、入力電圧VinがVDD・Vth以上に上昇しても、出力電圧VIはVDD・Vthの一定レベルとなり電圧クランプ動作が行われる。

### [0013]

図 2 ( B ) は、入力電圧・電流特性図であり、入力電圧 V i n の上昇に対して電流源 I o による一定電流しか流れない。これにより電流源 I o の電流値に対応して低消費電力を図ることができる。ちなみに、抵抗素子とダイオード等の定電圧素子を用いて電圧クランプ動作を行われることもできるが、この場合には、回路の高速化のために抵抗素子の抵抗値を小さくすると、入力電流 I i が増大してしまう。逆に、低消費電力のために抵抗素子の抵抗値を大きくすると、回路の高速化が犠牲になってしまう。

#### [0014]

図2(C)は、電圧変化特性である。この実施例では、MOSFETM1のソース,ド経路を通して入力信号Vinが伝えられるために、入力電圧Vinの立ち上がりにほぼ同期してクランプ出力電圧VIが変化するものとなる。前記図2(B)及び図2(C)により、本願発明の電圧クランプ回路においては、高速化と低消費電力化を両立して図ることができる。

#### [0015]

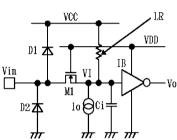

図3には、この発明の電圧クランプ回路を説明するための等価回路図が示されている。 同図に示すように、MOSFETM1の出力側のノードV1に、回路の絶縁不良等による 高抵抗LRによるリーク電流経路が形成された場合、電流源Ioが存在しない場合には、 電圧クランプ動作が不能に陥ってしまうが、電流源Ioを設けることより上記出力ノード VIの電位上昇が抑えられて安定的な電圧クランプ動作が行われる。このため、電流源I oは、不良と見做されないリーク電流よりも大きな微小電流に設定すればよく、図2(B)のように低消費電力化を図ることができる。

# [0016]

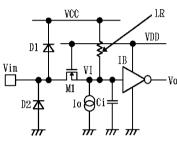

図4には、この発明の電圧クランプ回路を説明するための等価回路図が示されている。同図に示すように、MOSFETM1のソース,ドレイン間には、寄生容量Cdsが存在する。この寄生容量Cdsによって、入力信号VinがVCCのような高電圧に変化したときに、カップリングによって出力側VIを電源電圧VDD以上に変化させてしまうという問題が生じる。これを回避するために、電流源Ioに並列形態にキャパシタCiが設けられる。これによって、寄生容量CdsとキャパシタCiが直列形態に接続されて、その容量比の逆比に対応して入力電圧Vinを分圧して上記出力側VIが電源電圧VDD以上にならないようにすることができる。なお、入力回路IBには、入力回路を構成するMOSFETM1の他方の端子と接地電圧VSSとの間やMOSFETM1の他方の端子と電源電圧VDDとの間等に存在するが、かかるゲート容量のみでは上記のようにカップリングによって出力側VIが電源電圧VDD以上に変化してしまう。そのために、上記キャパシタCiは、入力回路IBの入力容量と比べても十分に大きなものとされる。

# [0017]

50

10

20

30

10

20

30

40

50

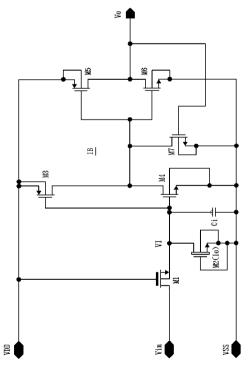

図5には、この発明に係る電圧クランプ回路の一実施例の具体的回路図が示されている。MOSFETM1は、前記図1のMOSFETM1と同じであり、キャパシタCiはMOS容量により構成される。入力回路IBは、PチャネルMOSFETM3とNチャネルMOSFETM3とNチャネルMOSFETM4からなる入力側のCMOSインバータ回路と、PチャネルMOSFETM5とNチャネルMOSFETM6からなる出力側のCMOSインバータ回路の縦列回路から構成される。特に制限されないが、出力側のCMOSインバータ回路の入力端子と回路の接地電位との間には、NチャネルMOSFETM7が設けられ、ゲートに出力信号Voが帰還される。

# [0018]

これにより、入力側のCMOSインバータ回路は、出力信号VoがロウレベルのときにMOSFETM7がオフ状態となり、MOSFETM3とM4のコンダクタンス比に対応した第1の論理しきい値を持つようにされる。これに対して、出力信号VoがハイレベルのときにMOSFETM7がオン状態となり、MOSFETM4とMOSFETM7が列形態となり、上記第1の論理しきい値よりも低い論理しきい値電圧に変化する。これにより、入力回路IBにおいは、入力信号がロウレベルからハイレベルに変化するときは上記高い第1論理しきい値電圧となり、ハイレベルからロウレベルに変化するときは上記にい第2論理しきい値電圧となり、ハイレベルからロウレベルに変化するとこれによって、入力信号Vinが上記第1論理しきい値電圧以上になると、それよりも低い第2論理しきい値電圧以下にならなければ出力信号Voが変化しなくなるので、入力信号Vinが入力回路の論理しきい値電圧付近のときにノイズが発生してもそれに応答して出力信号Voが変化しないから、安定した入力信号の取り込みが可能になる。

#### **[** 0 0 1 9 ]

この実施例では、電流源Ioがディプレッション型のNチャネルMOSFETM2により構成される。このMOSFETM2は、ゲートとソースが接続されることによって定電流動作を行うものとなる。この電流源Ioは、ゲートに所定電圧が印加されたエンハンスメント型のNチャネルMOSFETで構成してもよいし、ポリシリコン層等で構成された高抵抗素子で構成してもよい。同図においては、前記静電気破壊防止用のダイオードは省略されている。

# [0020]

キャパシタCiを構成するMOSFETは、特に制限されないが、PチャネルMOSFETのゲート容量が用いられる。このゲート容量は、例えばMOSFETM4等の通常のMOSFETの数10個分相当のMOSFETを用いて構成され、約1pFのような容量値を持つように形成される。ちなみに、このときのMOSFETM1はチャネル幅Wが20μm、チャネル長Lが800nmのように、MOSFETM2はチャネル幅Wが20μm、チャネル長Lが8μmのようにそれぞれ大きなサイズに形成される。これに対して、CMOSインバータ回路を構成するNチャネルMOSFETM4は、チャネル幅Wが8μm、チャネル長Lが2μmのように、NチャネルMOSFETM6は、チャネル幅Wが7μm、チャネル長Lが800nmのようにそれぞれ小さなサイズとされる。

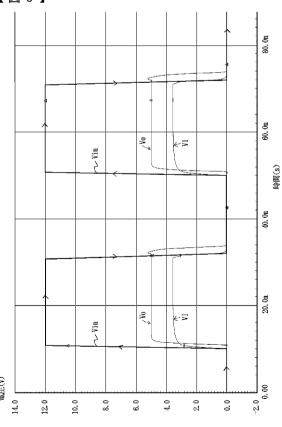

# [0021]

図6には、この発明に係る電圧クランプ回路を説明するための動作波形図が示されている。図6においては、入力電圧Vin、クランプ電圧VI及び出力電圧Voの実際の測定波形図が示されている。電圧クランプ回路は、前記図5に示した回路であり、入力電圧Vinは0-12 Vのような高振幅であり、低電圧VDDは5 Vである。同図に示すように、入力電圧Vinに対してVDD・Vth(MOSFETM1のしきい値電圧)のようなクランプ電圧VIが得られ、前記ヒステリシス特性を持つ2つCMOSインバータ回路を通してCMOSレベルの出力電圧Voを得ることができる。

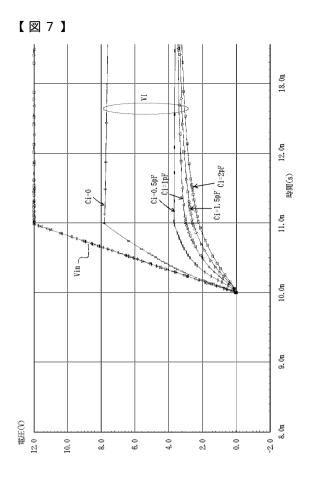

#### [0022]

図7には、この発明に係る電圧クランプ回路におけるキャパシタCiの容量値をパラメータとする入力電圧Vinとクランプ電圧VIとの関係を示す立ち上がり特性図が示されている。キャパシタCi= 0、つまりはキャパシタCiを接続しない状態では、MOSF

ETM1のソース,ドレイン間の寄生容量 C d s によるカップリングによってクランプ電圧 V I が約7.8Vも上昇してしまい、その後に前記電流源 I o によって放電が行われて徐々に低下する。つまり、MOSFETM3とM4によるCMOSインバータ回路の入力容量が小さく、上記寄生容量 C d s との分圧によって上記約7.8Vも上昇してしまうものとなる。

# [0023]

上記キャパシタCiの容量値をCi=0.5pFのとき、Ci=1pFのとき、Ci=1.5pFのとき、Ci=2pFのときのように、クランプ電圧VIは約3.6V、3V、2.6V、2.2Vのように抑えられる。キャパシタCiは、入力回路の入力容量でもあるので、容量値を大きくするとMOSFETM1を通したクランプ電圧VIまでの充電時間、あるいは立ち下がり時の放電時間が長くなるので、この実施例では必要最小と考えられるCi=1pFに設定するものである。上記寄生容量Cdsでのカップリング動作は、上記キャパシタCiの容量値を適当に設定することにより、そのカップリングを利用してクランプ電圧VIの立ち上がり、立ち下がりを高速にすることができるようになる。

# [0024]

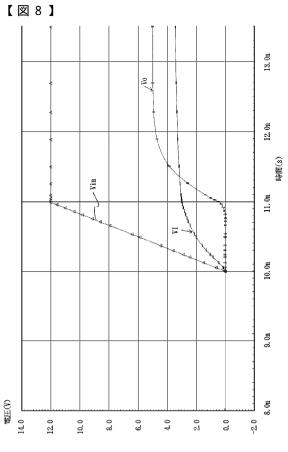

図 8 には、この発明に係る電圧クランプ回路の入力電圧 Vinの立ち上がり特性図が示さ

れている。同図は、図6の立ち上がり部分の時間を拡大して示している。この実施例の電圧クランプ回路は、入力電圧Vinが0Vから12Vまで1nsで立ち上がりと、それとほぼ同じ時間で前記寄生容量Cdsでのカップリングによって3V付近まで立ち上がり、MOSFETM1での充電動作によって最終的にはVDD(5V)・Vthまで立ち上がる。2段のCMOSインバータ回路からなる入力回路IBでは、2ns程度の信号伝達遅延時間を持って出力電圧Voをハイレベルに立ち上げるものとなる。

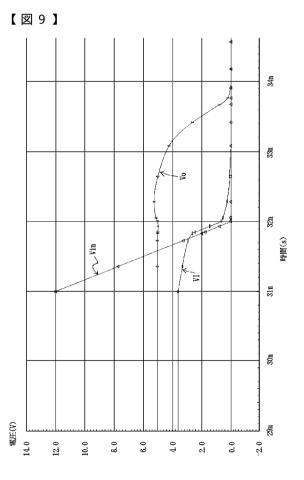

#### [0025]

図9には、この発明に係る電圧クランプ回路の入力電圧Vinの立ち下がり特性図が示されている。同図は、図6の立ち下がり部分の時間を拡大して示している。この実施例の電圧クランプ回路は、入力電圧Vinが12Vから0Vまで1nsで立ち下がり、それとほぼ同じ時間で前記寄生容量CdsでのカップリングとMOSFETM1での放電動作によって入力回路IBの論理しきい値電圧以下まで立ち下がる。最終的に0Vにするには、更に1nsを費やしているが、前記のように入力回路IBからみると上記のように0Vに等しいものである。2段のCMOSインバータ回路からなる入力回路IBでは、2ns程度の信号伝達遅延時間を持って出力電圧Voをロウレベルに立ち下げるものとなる。

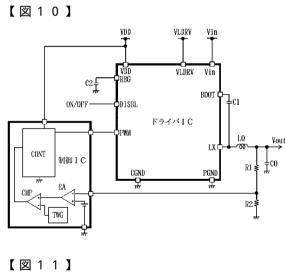

#### [0026]

図10には、この発明に係る電圧クランプ回路が用いられるスイッチング電源装置の一実施例のブロック図が示されている。この実施例のスイッチング電源装置は、制御ICとドライバICとからなり、高電圧からなる入力電圧Vinを低電圧からなる出力電圧Voutに降圧する降圧型スイッチング電源である。特に制限されないが、100 Vの商用交流電圧を12 Vのような直流電圧に変換して形成された高電圧を、マイコクロコンピュータを構成するCPU(中央処理装置)、メモリ回路等の動作に用いられる約3 V程度の低電圧に更に変換するのが上記降圧型スイッチング電源である。

# [0027]

インダクタLOにキャパシタCOを直列形態に接続して平滑出力電圧Voutを形成し、約12Vのような入力電圧Vinから上記インダクタLOに流す電流を制御して上記出力電圧Voutが所定電圧となるようにするドライバICの第1スイッチ素子と、上記第1スイッチ素子がオフ状態のときに上記インダクタLOに発生する逆起電圧を所定電位(PGND)にクランプする第2スイッチ素子が設けられる。上記上記出力電圧Voutが所定電圧となるようにするために、抵抗R1とR2で分圧されて出力電圧Voutが制御ICに設けられたエラーアンプEAに供給され、所定電圧と比較される。このエラーエンプEAの出力電圧と、三角波発生回路TWGで形成された三角波とは電圧比較回路CMPに供給されて、その出力信号が制御回路CONTに伝えられてPWM(パルス幅変調)信

10

20

30

40

号が形成される。このPWM信号は、上記ドライバICの上記第1スイッチ素子と第2スイッチ素子の制御信号として用いられる。つまり、PWM信号により上記第1スイッチ素子のオン期間を制御して上記インダクタLOに流す電流の制御が行われる。

# [0028]

制御ICは、特に制限されないが、12Vのような高電圧VDDが供給されるが、上記エラーエンプの入力電圧は、小さな電圧であることから内部電源回路により5V程度の低電圧を形成し、前記エラーアンプEA、コンパレータCMP及び三角波発生回路TWGと、上記PWM信号を形成する制御回路CONTが動作させられる。それ故、制御ICは、5Vのような低電圧を直接供給するものであってもよい。

#### [0029]

上記ドライバICにおいて、上記電源電圧端子VDDには、特に制限されないが、入力電圧Vinと同じ12Vのような高電圧が供給される。端子REGは、後述する内部降圧電源回路Regの出力電圧安定化のためのキャパシタC2が接続される外部端子であり、端子VLDRVは、後述するように上記第2スイッチ素子を駆動する駆動回路の動作電圧が供給される。端子BOOTは、後述するように上記第1スイッチ素子を駆動する駆動回路の動作電圧を昇圧するためのブートストラップ容量C1が接続される。この容量C1の他方の電極には、インダクタLOが設けられる出力端子LXに接続される。端子DISBL

は、ドライバICの動作制御(ON/OFF)を行う動作制御信号が入力される。

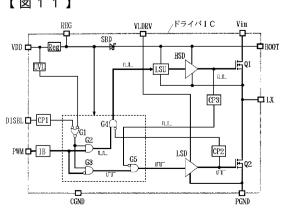

# [0030]

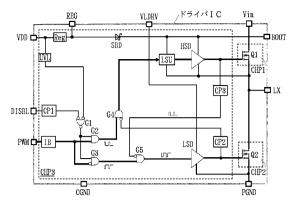

図11には、図10のドライバICの一実施例のブロック図が示されている。上記第1スイッチ素子は、パワーMOSFETQ1により構成され、第1駆動回路(ハイサイドドライバ)HSDにより上記入力電圧Vinに対応した昇圧電圧信号により駆動される。つまり、MOSFETQ1は、Nチャネル型で構成されているので、ゲートに入力電圧Vinに対応した駆動電圧を供給したのでは、しきい値電圧分だけ出力電圧が低下してしまう

# [0031]

そこで、インダクタLOに対して入力電圧Vinを供給できるようにするために、MOSFETQ1がオフ状態のときに、つまりは、出力端子LXがクランプ用のスイッチ素子であるMOSFETQ2のオン状態によりほぼ回路の接地電位PGNDにあるとき、ショットキーバリアダイオードSBDを通して内部電源Regにより形成された約5Vのような電圧でブートストラップ容量C1を充電する。そして、MOSFETQ2がオフ状態となり、MOSFETQ1がオン状態になると、ブートストラップ容量C1に蓄えられた電圧だけ端子BOOTの電圧が上昇に伴い上記ブートストラップ容量C1に蓄えられた電圧だけ端子BOOTの電圧が上昇し、それが第1駆動回路HSDを通してMOSFETQ1のゲートに伝えられる。これにより、MOSFETQ1のゲートには、入力電圧Vinに対しても上記ブートストラップ容量C1に蓄えられた電圧だけ高くなり、出力端子LXの電圧は電圧Vinまで高くすることができる。

# [0032]

この実施例では、上記第2スイッチ素子であるMOSFETQ2は第2駆動回路(ロウサイドドライバ)LSDにより上記高電圧により駆動することが可能とされる。つまり、端子VLDRVから与えられた電圧で第2駆動回路LSDを動作させるようにしている。上記端子VLDRVには、前記のような12Vを印加してもよいし、5V程度の低電圧を供給してもよい。これはユーザーにおいて任意に設定できるようにするものである。上記12Vのような高電圧で動作させた場合には、MOSFETQ2をオン抵抗値を小さくでき、スイッチング電源における無効電流を小さくできる。

#### [0033]

前記制御ICにおいては、上記入力電圧よりも低い低電圧で動作する制御回路CONTにより、上記キャパシタCOから得られる出力電圧Voutが所定電圧(例えば3V程度)となるようにPWM信号を形成する。ドライバICにおいては、上記第1駆動回路HS

10

20

30

40

Dと第2駆動回路LSDの駆動信号を形成する制御論理回路は、同図において点線で示したように、電源回路Regにより形成した低電圧で動作させられるゲート回路G1~G5から構成される。スイッチング電源においては、上記第1スイッチ素子であるMOSFETQ1と第2スイッチ素子であるMOSFETQ2は、貫通電流による素子破壊を防ぐ為に同時にオン状態にならないようにするデッドタイムを設けることが必要である。

# [0034]

そこで、第1スイッチ素子であるMOSFETQ1のゲートに供給される駆動信号を前記図1又は図5で示した電圧クランプ回路CP3により上記低電圧に対応して電圧クランプ回路CP3の入力ノードに入力されるMOSFETQ1のゲートに供給される駆動信号を電圧クランプして上記第2駆動回路LSDに伝えられる入力信号を形成するゲート回路G5の帰還信号とする。上記第2スイッチ素子であるMOSFETQ2のゲートに供給される駆動信号を前記図1又は図5で示した電圧クランプ回路CP2により上記低電圧に対応して電圧クランプ回路CP2の入力ノードに入力されるMOSFETQ2のゲートに供給される駆動信号を電圧クランプして上記第1駆動回路HSDに伝えられる入力信号を形成するゲート回路G4の帰還信号とする。つまり、電圧クランプ回路CP3とCP2は、上記のような高振幅の駆動信号を低振幅の信号に変換するレベルシフト回路として動作し、第1と第2スイッチ素子が同時にオン状態とならないように、いいかえるならばMOSFETQ1をオフ状態にする信号を受けてMOSFETQ2をオン状態にしてデッドタイムを設定する。

# [0035]

この実施例では、前記のようなレベルシフト動作を行う回路として、電圧クランプ回路を用いている。この実施例の電圧クランプ回路は、その伝達特性が高速であり、MOSFETQ1とQ2とが同時にオン状態とならないようにするデットタイムを小さく設定することができる。つまり、スイッチング周期が同じならば、デッドタイムが小さい分だけより高い精度での電圧制御が可能になるものである。

### [0036]

ゲート回路G4の出力信号は、前記のように低電圧信号であるので、高電圧信号に変換するレベルシフト回路LSUを介して上記第1駆動回路HSDの入力信号とされる。また、かかるレベルシフト回路LSU及び第1駆動回路HSDは、出力端子LXの電位が回路の基準電位とされる。上記制御論理回路や、電源回路Reg及びPWMの入力回路IBや次に説明する電圧クランプ回路CP1やロウレベルへ検出回路UVLは、端子CGNDから供給される回路の基準電位とされる。つまり、これらの回路の接地電位CGNDを前記インダクタの逆起電圧をクランプするための接地電位PGNDと分けることにより、動作の安定化を図るものである。

# [0037]

ドライバICの動作の有効/無効(ON/OFF)を制御するDISBLからの入力信号は、 $5 V \sim 1 2 V$ の信号振幅での使用が可能にされる。それ故、1 2 Vのような高い信号振幅で動作させられる場合を想定して、図1で示したような電圧クランプ回路CP1が設けられる。そうすることにより、1 2 Vのような高い信号振幅での動作においても低消費電力での動作が可能となる。もしも、5 Vのような低電圧の入力信号が供給された場合には、実質的なクランプ動作は行われないが、動作そのものには何ら影響を与えない。

# [0038]

上記のような実施例によると、高速かつ低消費電力で安定的に電圧クランプ動作を行うようにすることができ、又入力電圧の変化に高速応答する電圧クランプ動作によって、スイッチング電源装置の第1スイッチ素子と第2スイッチ素子の切り替えのデッドタイムの短縮化が可能となる。

# [0039]

図12には、図10のドライバICの他の一実施例のブロック図が示されている。この実施例では、ドライバICは、3つのシリコンチップが一つのパッケージに封止されて構

10

20

30

40

成させれたマルチチップモジュール構造とされる。つまり、パワーMOSFETQ1及びMOSFETQ2は、同図で点線で示したようにそれぞれ別のシリコン等の半導体基板上(シリコンチップ)CHP1とCHP2に形成し、上記パワーMOSFETQ1及びMOSFETQ2以外のドライバICを構成する回路を一つのシリコン等の半導体基板上(シリコンチップ)CHP3に形成して、これらが一つのパッケージに封止されて上記ドライバICが構成される。このようなマルチチップモジュール構成のドライバICにおいては、前記図11に示したようにドライバICを構成する全ての回路を一つの半導体基板上に形成するのに比べて、低コストで高性能な製品を作る事ができる。

# [0040]

以上本発明者によってなされた発明を、前記実施形態に基づき具体的に説明したが、本発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能である。例えば、図1、図6において、MOSFETM1のサイズ、キャパシタCiの容量値及び電流源Ioの電流は、電圧クランプ用途に応じて適宜に設定されるものである。この発明は、電圧クランプ回路(電圧レベル変換回路)及びスイッチング電源装置それに用いられる半導体集積回路装置に広く利用できる。

#### 【図面の簡単な説明】

# [0041]

- 【図1】この発明に係る電圧クランプ回路の一実施例を示す回路図である。

- 【図2】この発明に係る電圧クランプ回路の動作を説明するための特性図である。

- 【図3】この発明の電圧クランプ回路を説明するための等価回路図である。

- 【図4】この発明の電圧クランプ回路を説明するための等価回路図

- 【図5】この発明に係る電圧クランプ回路の一実施例を示す具体的回路図である。

- 【図6】この発明に係る電圧クランプ回路を説明するための動作波形図である。

- 【図7】この発明に係る電圧クランプ回路における入力電圧とクランプ電圧との関係を示す特性図である。

- 【図8】この発明に係る電圧クランプ回路の入力電圧の立ち上がり特性図である。

- 【図9】この発明に係る電圧クランプ回路の入力電圧の立ち下がり特性図である。

- 【図10】この発明に係る電圧クランプ回路が用いられるスイッチング電源装置の一実施例を示すブロック図である。

- 【図11】図10のドライバICの一実施例を示すブロック図である。

- 【図12】図10のドライバICの他の一実施例を示すブロック図である。

# 【符号の説明】

#### [0042]

D 1 , D 2 … ダイオード、M 1 ~ M 6 … M O S F E T、 I o … 電流源、 C i … キャパシタ、 C d s … 寄生容量、 I B … 入力回路、 C P N T … 制御回路、 E A … エラーアンプ、 C M P … 電圧比較回路、 T W G … 三角波発生回路、 C I … ブートストラップ容量、 L O … インダクタ、 C O , C 1 … キャパシタ、 H S D … 第 1 駆動回路、 L S D … 第 2 駆動回路、 C P 1 ~ C P 3 … 電圧クランプ回路、 R e g … 電源回路、 L S U … レベルシフト回路、 G 1 ~ G 5 … ゲート回路、 S B D … ショットキーバリアダイオード、 Q 1 , Q 2 … パワーM O S F E T (第 1 ,第 2 スイッチ素子), C H P 1 ~ C H P 3 … シリコンチップ。

20

10

30

# 【図1】

# 【図2】

# 【図3】

【図5】

【図4】

【図6】

# 【図12】

# フロントページの続き

# (56)参考文献 特開平08-008707(JP,A)

特開昭50-110536(JP,A)

特開2003-347921(JP,A)

特開2000-196433(JP,A)

特開平10-163826(JP,A)

特開昭57-129534(JP,A)

特開2000-357949(JP,A)

特開2003-142999(JP,A)

# (58)調査した分野(Int.CI., DB名)

H03K19/00,19/01-19/082,19/092-19/096

H03K17/00-17/70