(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3871916号

(P3871916)

(45) 発行日 平成19年1月24日(2007.1.24)

(24) 登録日 平成18年10月27日(2006.10.27)

(51) Int.C1.

F 1

|             |              |                  |             |             |             |

|-------------|--------------|------------------|-------------|-------------|-------------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b> | <b>K</b>    |

| <b>G09F</b> | <b>9/30</b>  | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b> | <b>338</b>  |

| <b>H01L</b> | <b>27/32</b> | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b> | <b>365Z</b> |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>623B</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>624B</b> |

請求項の数 6 (全 35 頁) 最終頁に続く

(21) 出願番号 特願2001-330199 (P2001-330199)

(22) 出願日 平成13年10月29日 (2001.10.29)

(65) 公開番号 特開2002-202756 (P2002-202756A)

(43) 公開日 平成14年7月19日 (2002.7.19)

審査請求日 平成16年10月25日 (2004.10.25)

(31) 優先権主張番号 特願2000-328751 (P2000-328751)

(32) 優先日 平成12年10月27日 (2000.10.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 濱本 穎広

(56) 参考文献 特開昭60-198872 (JP, A)

(58) 調査した分野 (Int.Cl., DB名)

G09G 3/30, 3/20

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の薄膜トランジスタとEL素子とを有する画素と、

信号線と、

前記第1の薄膜トランジスタが形成された基板と同一基板上に前記第1の薄膜トランジスタと同時に形成された第2の薄膜トランジスタと、

オペアンプとを有し、

前記第2の薄膜トランジスタは、ダイオード接続されて前記オペアンプの反転入力端子と出力端子の間に接続され、

前記オペアンプの出力は、前記信号線に接続され、

前記第1の薄膜トランジスタのゲートには、前記信号線から信号が入力され、

前記第1の薄膜トランジスタのドレイン電流によって、前記EL素子に流れる電流が制御されることを特徴とする表示装置。

## 【請求項 2】

第1の薄膜トランジスタとEL素子とを有する画素と、

信号線と、

前記第1の薄膜トランジスタと特性が等しい第2の薄膜トランジスタと、

オペアンプとを有し、

前記第2の薄膜トランジスタは、ダイオード接続されて前記オペアンプの反転入力端子と出力端子の間に接続され、

10

20

前記オペアンプの出力は、前記信号線に接続され、

前記第1の薄膜トランジスタのゲートには、前記信号線から信号が入力され、

前記第1の薄膜トランジスタのドレイン電流によって、前記EL素子に流れる電流が制御されることを特徴とする表示装置。

**【請求項3】**

第1の薄膜トランジスタとEL素子とを有する画素と、

信号線と、

前記第1の薄膜トランジスタと極性、閾値電圧、実効移動度、及びゲート絶縁膜の単位面積あたりの静電容量が等しい第2の薄膜トランジスタと、

オペアンプとを有し、

10

前記第2の薄膜トランジスタは、ダイオード接続されて前記オペアンプの反転入力端子と出力端子の間に接続され、

前記オペアンプの出力は、前記信号線に接続され、

前記第1の薄膜トランジスタのゲートには、前記信号線から信号が入力され、

前記第1の薄膜トランジスタのドレイン電流によって、前記EL素子に流れる電流が制御されることを特徴とする表示装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記信号線は、第3の薄膜トランジスタを介して一定の電位が与えられることを特徴とする表示装置。

20

**【請求項5】**

請求項1乃至請求項4のいずれか一項において、

前記表示装置を用いたことを特徴とする電子機器。

**【請求項6】**

請求項1乃至請求項4のいずれか一項において、

前記表示装置を用いたことを特徴とするビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ、画像再生装置、ゲーム機、ナビゲーションシステム、パーソナルコンピュータ、携帯情報端末、携帯電話または電子書籍。

**【発明の詳細な説明】**

**【0001】**

30

**【発明の属する技術分野】**

本発明は、画素毎にTFT(薄膜トランジスタ)とEL素子を配置した、アクティブマトリクス型EL表示装置に関する。特に、EL素子に流れる電流をアナログ的に変化させて階調を表現するアナログ階調方式のアクティブマトリクス型EL表示装置に関する。

**【0002】**

なお、本明細書において、EL素子とは、一重項状態からの発光(蛍光)をおこなうものと、三重項状態からの発光(燐光)をおこなうものの両方を含むものとする。

**【0003】**

**【従来の技術】**

近年、情報通信の活発化により、情報通信機器の需要が高まっている。ここで、これらの情報通信機器には、画像を表示するための表示装置が欠かせない。表示装置としては、自発光素子であるEL素子を用いたEL表示装置が注目されている。

40

**【0004】**

ここで、表示部の大型化及び高精細化に伴い、画素毎にTFTを配置したアクティブマトリクス型の表示装置が主流となりつつある。

**【0005】**

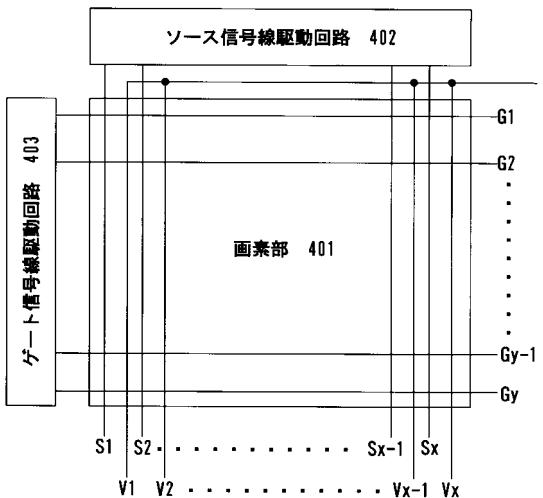

図4にアクティブマトリクス型EL表示装置のブロック図を示す。画素部401の周りに、ソース信号線駆動回路402、ゲート信号線駆動回路403が配置されている。ソース信号線駆動回路402から出力される信号は、ソース信号線S1～Sxに入力され、各画素に伝達される。また、ゲート信号線駆動回路403から出力される信号は、ゲート信号

50

線 G<sub>1</sub> ~ G<sub>y</sub> に入力され、各画素に伝達される。ソース信号線に平行に電源供給線（電源線）V<sub>1</sub> ~ V<sub>x</sub> が配置され各画素に電流を供給する。

#### 【0006】

ここで、表示装置を小型化し、また作製上のコストも低減するために、画素部及び駆動回路部（ソース信号線駆動回路及びゲート信号線駆動回路）を1つの基板上に作製する試みがなされている。この際、多結晶半導体層を用いて、画素部及び駆動回路部の TFT を作製する。

#### 【0007】

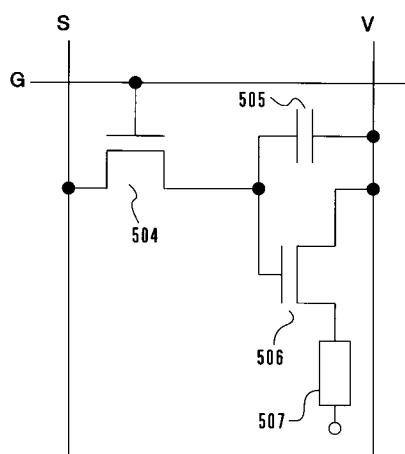

図4のアクティブマトリクス型EL表示装置の画素の構造についての例を図5に示す。

#### 【0008】

スイッチング用 TFT 504 のゲート電極はゲート信号線 G<sub>1</sub> ~ G<sub>y</sub> のうちの1本 G に接続され、ソース領域もしくはドレイン領域の一方は、ソース信号線 S<sub>1</sub> ~ S<sub>x</sub> のうちの1本 S に接続され、もう一方はコンデンサ 505 の一方の電極及び EL 駆動用 TFT 506 のゲート電極に接続されている。コンデンサ 505 の電極でスイッチング用 TFT 504 と接続されていない側は、電源供給線 V<sub>1</sub> ~ V<sub>x</sub> のうちの1本 V に接続されている。EL 駆動用 TFT 506 のソース領域もしくはドレイン領域の一方は、電源供給線 V に接続されており、もう一方は EL 素子 507 に接続されている。

#### 【0009】

ゲート信号線 G が選択された画素において、ソース信号線 S の信号電位は導通状態になったスイッチング用 TFT 504 を介して、コンデンサ 505 の一方の電極に入力される。このコンデンサ 505 の電極間の電圧が EL 駆動用 TFT 506 のゲート電極に印加される。この印加電圧に応じて EL 駆動用 TFT 506 を介して電源供給線 V から EL 素子 507 に電流が流れ、EL 素子 507 は発光する。

#### 【0010】

ここで、EL 素子 507 の発光輝度は、EL 素子 507 を流れる電流にほぼ正比例する。そこで、EL 素子 507 に流れる電流を変化させることによって階調を表現することができる。

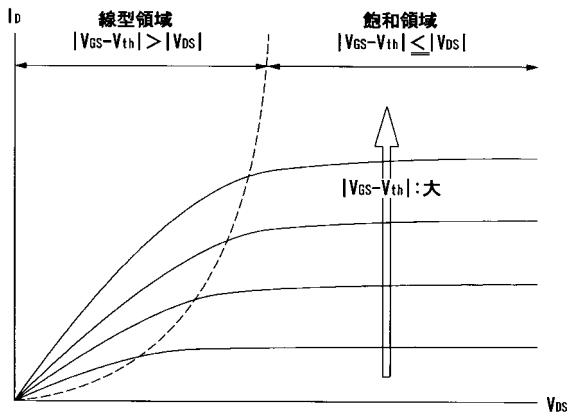

#### 【0011】

図5に示した表示装置では、EL 素子 507 に流れる電流は、EL 駆動用 TFT 506 を介して電源供給線 V より入力される。ここで一般に TFT のドレイン・ソース間電圧 V<sub>DS</sub> と、そのドレイン電流 I<sub>D</sub> とは、図8に示した様な関係を持っている。

#### 【0012】

図8には、異なるゲート電圧 V<sub>GS</sub> に対応する複数のグラフを示している。ゲート電圧 V<sub>GS</sub> と EL 駆動用 TFT 506 の閾値電圧 V<sub>th</sub> の差の絶対値 | V<sub>GS</sub> - V<sub>th</sub> | が大きくなるほど、言い換えればゲート電圧 V<sub>GS</sub> の絶対値 | V<sub>GS</sub> | が大きくなるほど、ドレイン電流 I<sub>D</sub> は大きくなる。

#### 【0013】

ゲート電圧 V<sub>GS</sub> と EL 駆動用 TFT 506 の閾値電圧 V<sub>th</sub> の差の絶対値 | V<sub>GS</sub> - V<sub>th</sub> | が、ドレイン・ソース間電圧 V<sub>DS</sub> の絶対値 | V<sub>DS</sub> | よりも大きい場合は、TFT は線型領域で動作し、ドレイン・ソース間電圧 V<sub>DS</sub> の絶対値 | V<sub>DS</sub> | 以下の場合は、飽和領域で動作する。

#### 【0014】

EL 駆動用 TFT 506 は、一般にドレイン・ソース間電圧 V<sub>DS</sub> の絶対値 | V<sub>DS</sub> | が、ゲート電圧 V<sub>GS</sub> と EL 駆動用 TFT 5006 の閾値電圧 V<sub>th</sub> の差の絶対値 | V<sub>GS</sub> - V<sub>th</sub> | 以上の、飽和領域で動作している。

#### 【0015】

飽和領域では、次の式1で示す様に、TFT のドレイン電流 I<sub>D</sub> は、ゲート電圧 V<sub>GS</sub> の2乗に比例する。

#### 【0016】

#### 【式1】

$$I_D = (1/2) \mu_0 C_0 (W_1/L_1) (V_{GS} - V_{th})^2$$

## 【0017】

ここで、 $V_{th}$ は閾値電圧である。 $\mu_0$ は実効移動度、 $C_0$ はゲート絶縁膜の単位面積あたりの静電容量、 $W$ はゲート幅、 $L$ はゲート長である。

## 【0018】

この式に従って、EL素子507に入力したい電流の平方根に比例したゲート電圧がTFTに印加されるように、ソース信号線Sに入力する電位を変化させることによって、所定の輝度でEL素子507を発光させる。

10

## 【0019】

## 【発明が解決しようとする課題】

画像表示する際、式1に従って、階調に応じた電位をソース信号線に入力する必要がある。

## 【0020】

しかし、外部より、一般に入力されるビデオ信号は、表現する輝度に対して線型に変化するアナログの電位である。このため、外部より入力されるビデオ信号を、そのままソース信号線に入力しても、正確に階調を表現することができない。

## 【0021】

そこで、ビデオ信号を予め、外部の補正回路によってEL駆動用TFTの特性に合わせて変換し、駆動信号とした後、ソース信号線駆動回路においてサンプリングし、各画素に出力して所定の階調を表現する手法がある。

20

## 【0022】

しかし、ソース信号線駆動回路に信号を入力する前に、こうしたビデオ信号の処理が必要なため、動作を複雑化する一因となっている。また、ソース信号線駆動回路とは、別に補正回路を設ける必要があり、表示装置の小型化を妨げる原因となっている。

## 【0023】

そこで、ビデオ信号を直接ソース信号線駆動回路に入力し、所定の階調を表現することを課題とする。

## 【0024】

30

## 【課題を解決するための手段】

本発明では、外部より入力され、サンプリングされたビデオ信号に対して、画素部のEL素子に流れる電流が線型に対応するソース信号線駆動回路を有する表示装置を提供する。

## 【0025】

これによって、ビデオ信号を直接入力して、容易に所定の階調を表現することができる。

## 【0026】

以下に本発明の構成を示す。

## 【0027】

本発明によって、

画素毎に、EL素子と、ソース信号線と、前記EL素子を駆動する駆動TFTとを有する表示装置において、

40

入力したアナログ信号電圧を電流に変換する手段と、

前記電流を、前記駆動TFTと同極性のTFTのゲート・ソース間電圧に変換する手段と、

、

前記ゲート・ソース間電圧を、ソース線信号として、前記ソース信号線に供給する手段と、

、

前記ソース線信号を、前記駆動TFTのゲート電極に供給し、前記駆動TFTにおいて前記ソース線信号を電流に変換し、前記EL素子を駆動する手段とを有することを特徴とする表示装置が提供される。

## 【0028】

50

本発明によって、

画素毎にソース信号線と、EL駆動用TFTと、電源供給線と、EL素子とを有し、前記ソース信号線の信号電圧が、前記EL駆動用TFTのゲート電極に入力され、前記電源供給線より、前記EL駆動用TFTのソース・ドレイン間を介してEL素子に電流が流れる表示装置において、

前記EL駆動用TFTと同じ極性の補正用TFTを有し、サンプリングしたアナログ信号電圧を、線型に対応する信号電流に変換し、前記信号電流を、前記補正用TFTのソース・ドレイン間に流すことによって、基準電位から前記補正用TFTのゲート・ソース間電圧だけ変化した駆動電圧を、ソース信号線に出力し、

前記電源供給線の電位を、前記基準電位として、前記EL駆動用TFTのゲート・ソース間電圧が、前記補正用TFTのゲート・ソース間電圧とほぼ等しくなることを特徴とする表示装置が提供される。

#### 【0029】

本発明によって、

画素毎にソース信号線と、EL駆動用TFTと、電源供給線と、EL素子とを有し、前記ソース信号線の信号電圧は、前記EL駆動用TFTのゲート電極に入力され、前記電源供給線より、前記EL駆動用TFTのソース・ドレイン間を介して前記EL素子に電流が流れる表示装置において、

信号入力線と、スイッチと、抵抗と、補正用TFTと、オペアンプとを有し、前記補正用TFTは、前記EL駆動用TFTと同じ極性を有し、前記抵抗は、第1の端子と第2の端子とを有し、前記オペアンプは、非反転入力端子と反転入力端子と出力端子とを有し、前記信号入力線は、前記スイッチを介して前記抵抗の第1の端子に接続され、前記抵抗の第2の端子は、前記オペアンプの反転入力端子及び前記補正用TFTのソース領域もしくはドレイン領域に接続され、

前記補正用TFTのソース領域もしくはドレイン領域で、前記オペアンプの反転入力端子に接続されていない側は、前記オペアンプの出力端子及び前記ソース信号線に接続され、前記補正用TFTのゲート電極は、前記補正用TFTのドレイン領域もしくはソース領域と接続されていることを特徴とする表示装置が提供される。

#### 【0030】

前記オペアンプの非反転入力端子の電位と、前記電源供給線の電位とを等しくすることを特徴とする表示装置であってもよい。

#### 【0031】

スイッチング用TFTを有し、

前記ソース信号線は、前記スイッチング用TFTのソース・ドレイン間を介して、前記EL駆動用TFTのゲート電極に接続されることを特徴とする表示装置であってもよい。

#### 【0032】

リセット用TFTを有し、

前記リセット用TFTのソース領域もしくはドレイン領域は、一方は、前記オペアンプの出力端子に接続され、もう一方は一定の電位が与えられていることを特徴とする表示装置であってもよい。

#### 【0033】

前記表示装置を用いることを特徴とするパーソナルコンピュータ、ビデオカメラ、ヘッドマウントディスプレイ、画像再生装置、携帯情報端末であってもよい。

#### 【0034】

##### 【発明の実施の形態】

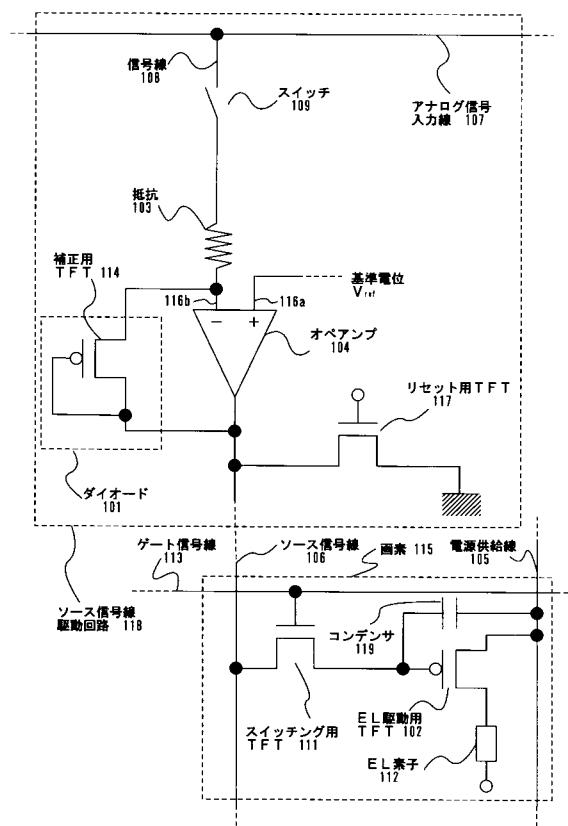

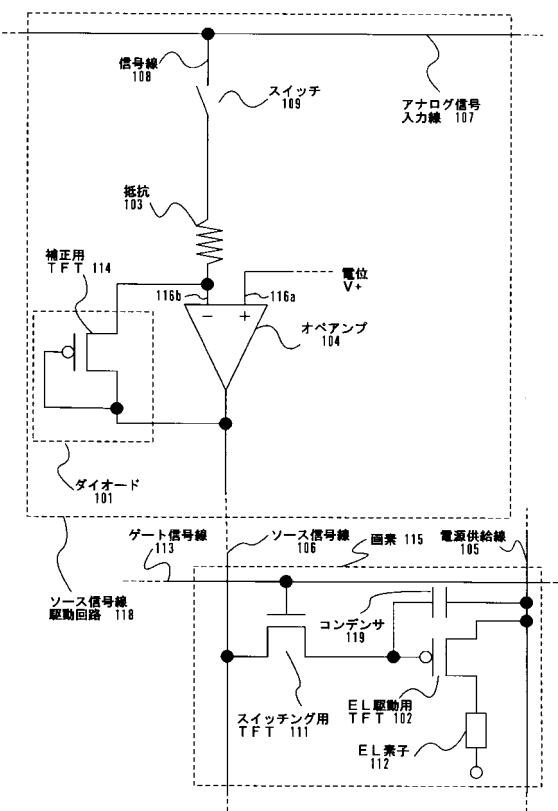

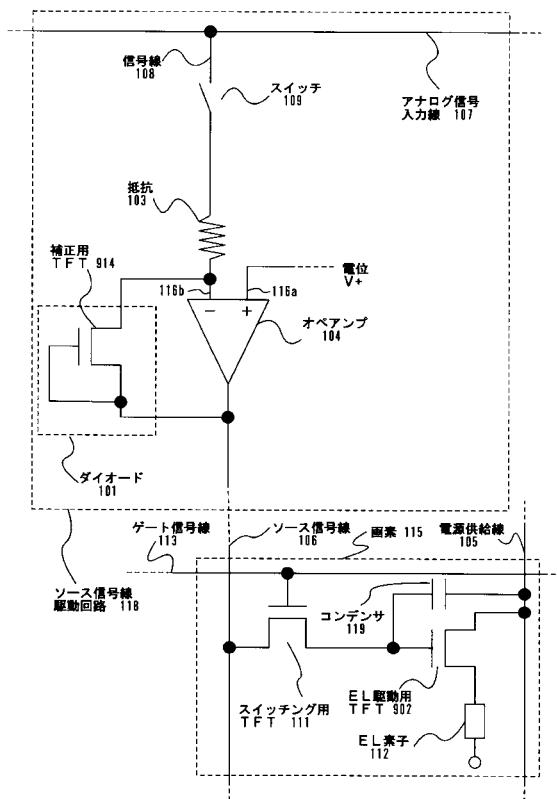

本発明の構成について、図1を用いて説明する。

#### 【0035】

図1において、本発明のEL表示装置の画素115と、その画素に信号を入力するソース

10

20

30

40

50

信号線駆動回路の一部 118 を示す。

**【0036】**

ソース信号線駆動回路の一部 118 は、ダイオード 101、抵抗 103、オペアンプ 104、アナログ信号入力線（信号入力線）107、信号線 108、スイッチ（スイッチング素子）109、リセット用 TFT 117 によって構成されている。また、ダイオード 101 は、ゲート電極とドレイン電極を電気的に接続した補正用 TFT 114 によって構成されている。

**【0037】**

なお、補正用 TFT 114 は、p チャネル型 TFT とする。また、リセット用 TFT 117 は、p チャネル型 TFT でも n チャネル型 TFT でもどちらでも良い。

10

**【0038】**

画素は、EL 駆動用 TFT 102、電源供給線（電源線）105、ソース信号線 106、ゲート信号線 113、スイッチング用 TFT 111、EL 素子 112 及びコンデンサ 119 によって構成されている。なお、EL 駆動用 TFT 102 は、p チャネル型 TFT である。また、スイッチング用 TFT 111 は、p チャネル型 TFT でも n チャネル型 TFT でもどちらでも良い。

**【0039】**

ここでは、EL 駆動用 TFT 及び補正用 TFT を p チャネル型 TFT としているが、EL 駆動用 TFT 及び補正用 TFT として n チャネル型 TFT を用いても良い。ただし、EL 駆動用 TFT 及び補正用 TFT の、極性を同一とし、閾値電圧をほぼ等しくする必要がある。

20

**【0040】**

アナログ信号入力線 107 に、信号線 108 が接続され、信号線 108 は、スイッチ 109 を介して抵抗 103 に接続されている。抵抗 103 は、オペアンプ 104 の反転入力端子 116b に接続されている。オペアンプ 104 の反転入力端子 116b は、補正用 TFT 114 のソース領域に接続されている。また、オペアンプ 104 の非反転入力端子 116a には、基準電位  $V_{ref}$  が入力される。オペアンプ 104 の出力端子は、補正用 TFT 114 のドレイン領域及びソース信号線 106 に接続されている。リセット用 TFT 117 のソース領域もしくはドレイン領域は、一方は、ソース信号線 106 に接続され、もう一方は、接地されている。

30

**【0041】**

スイッチング用 TFT 111 のゲート電極は、ゲート信号線 113 に接続され、スイッチング用 TFT 111 のソース領域もしくはドレイン領域のどちらか一方は、ソース信号線 106 に接続され、もう一方は、EL 駆動用 TFT 102 のゲート電極及びコンデンサ 119 の一方の電極に接続されている。EL 駆動用 TFT 102 のソース領域は、電源供給線 105 に接続され、ドレイン領域は EL 素子 112 の陽極に接続されている。コンデンサのもう一方の電極は電源供給線 105 に接続されている。EL 素子 112 の陰極は、基準電源線に接続されているが、ここでは基準電源線は図示していない。

**【0042】**

図 1 に示した表示装置の駆動方法について説明する。

40

**【0043】**

アナログ信号入力線 107 に入力されたビデオ信号の信号電圧  $V_{in}$  は、スイッチ 109 を開閉することによってサンプリングされ、信号線 108 に入力される。

**【0044】**

ここで、信号電位  $V_{in}$  は基準電位  $V_{ref}$  以上の値をとり、その値が大きい程、高い輝度を表す信号であるとする。

**【0045】**

ここで、オペアンプ 104 の反転入力端子 116b と出力端子がダイオード 101 を介して接続されているため、反転入力端子 116b の電位は、非反転入力端子 116a と等しくなる。つまり、反転入力端子 116b の電位は、基準電位  $V_{ref}$  と等しくなる。そのた

50

め、抵抗 103 間の電圧は、 $V_{in} - V_{ref}$  となり、式 2 に示す電流  $I_1$  が抵抗を流れる。

【0046】

【式 2】

$$I_1 = (V_{in} - V_{ref}) / R$$

【0047】

なお、電流  $I_1$  は、抵抗のアナログ信号入力線 107 に接続された側から反転入力端子 116b に接続された側に向かって流れる。

【0048】

ここで、R は抵抗 103 の抵抗値である。この電流  $I_1$  は、ダイオード 101 に入力される。ダイオード 101 を構成する補正用 TFT114 のドレイン電流が電流  $I_1$  に相当する。ここで、補正用 TFT114 は、ドレイン領域とゲート電極が接続されているため、ゲート電圧とドレイン・ソース間電圧が等しい。そのため補正用 TFT114 は、飽和領域で動作する。

【0049】

またこのとき、補正用 TFT114 は、p チャネル型 TFT であるから、オペアンプ 104 の反転入力端子 116b に接続されている側の電位が、オペアンプ 104 の出力端子に接続されている側の電位よりも高くなれば、導通状態にならない。

【0050】

そのため、オペアンプ 104 の反転入力端子 116b に接続された側が、ソース領域となり、オペアンプ 104 の出力端子に接続された側が、ドレイン領域になり、一方向のみに電流を流すダイオードとして用いられる。

【0051】

飽和領域で動作する TFTにおいては、先に示した式 1 が成立する。式 1 を変形し、ゲート電圧について解く。これにより、ドレイン電流が  $I_1$  の時のゲート電圧  $V_{GS1}$  を求めたものが、式 3 である。

【0052】

【式 3】

$$V_{GS1} = -\sqrt{2 I_1 (1/\mu_0 C_0) (L_1/W_1)} + V_{th1}$$

30

【0053】

なお、 $W_1$  は、補正用 TFT114 のゲート幅、 $L_1$  は補正用 TFT114 のゲート長である。また、 $V_{th1}$  は、補正用 TFT114 の閾値電圧である。

【0054】

ただしここでは、補正用 TFT114 は、p チャネル型 TFT であるのでゲート電圧  $V_{GS1}$  及び閾値電圧  $V_{th1}$  は、通常 0 以下の値となる。

【0055】

ここで、最初、リセット用 TFT117 が導通状態にあり、ソース信号線 106 の電位は 40 0 V であるとする。

【0056】

その後リセット用 TFT117 を非導通状態にすると、補正用 TFT114 のゲート電圧とドレイン・ソース間電圧は等しいため、ソース信号線には、基準電位  $V_{ref}$  から電圧  $V_{GS1}$  だけ変化した電位  $V_{ref} + V_{GS1}$  が入力される。

【0057】

ソース信号線 106 に電位  $V_{ref} + V_{GS1}$  を入力する前に、リセット用 TFT117 を導通状態にすることによって、ソース信号線 106 の電位を 0 V にしているのは、もし仮に、ある状態でのソース信号線 106 の電位が、その次にアナログ信号入力線 107 に入力された信号電位による、オペアンプ 104 の反転入力端子 116b の電位よりも高くなつて

40

50

しまった場合に、補正用 TFT114 のソース領域とドレイン領域が入れ替わり、補正用 TFT114 は、非導通状態となってオペアンプ 104 の入出力間の帰還が効かなくなってしまうのを防ぐためである。

#### 【0058】

なお、リセット用 TFT117 を導通状態にすることによって、オペアンプ 104 の出力端子に与えられる電位は、0 V に限らない。一般に、アナログ信号入力線に入力された信号の最も高い電位に対応する、ソース信号線に出力された最も低い電位（以下、最低電位  $V_{SLOW}$  と呼ぶ）以下に設定すればよい。つまり、リセット用 TFT117 を導通状態にすることによって、オペアンプ 104 の出力端子の電位を、最低電位  $V_{SLOW}$  以下に設定する。

10

#### 【0059】

p チャネル型 TFT である補正用 TFT が常に導通状態となるように、オペアンプの出力端子の電位を、最低電位  $V_{SLOW}$  に設定する動作を、本明細書中では、リセット動作と呼ぶこととする。

#### 【0060】

リセット動作は、帰線期間（水平帰線期間）中等に行うことができる。

#### 【0061】

ソース信号線 106 に入力された電位  $V_{ref} + V_{GS1}$  は、ゲート信号線 113 に信号が入力され、導通状態となったスイッチング用 TFT111 を介して、コンデンサ 119 及び EL 駆動用 TFT102 のゲート電極に入力される。ここで、電源供給線 105 の電位（電源電位）は、基準電位  $V_{ref}$  と同じに設定されている。よって、導通状態の EL 駆動用 TFT102 のソース領域は  $V_{ref}$  の電位となっている。

20

#### 【0062】

このとき、EL 駆動用 TFT102 のゲート電圧  $V_{GS2}$  は、補正用 TFT114 のゲート電圧  $V_{GS1}$  と等しくなる。

#### 【0063】

EL 駆動用 TFT102 も飽和領域で動作する場合、式 1 が成立するので、このときのドレイン電流  $I_2$  を求めたものが式 4 である。

#### 【0064】

#### 【式 4】

30

$$I_2 = (1/2) \mu_0 C_0 (W_2/L_2) (V_{GS1} - V_{th2})^2$$

#### 【0065】

ここで、 $V_{th2}$  は、EL 駆動用 TFT102 の閾値電圧とする。また、 $W_2$  及び  $L_2$  は、EL 駆動用 TFT102 のゲート幅及びゲート長である。

#### 【0066】

補正用 TFT114 と EL 駆動用 TFT102 の閾値電圧  $V_{th1}$  と  $V_{th2}$  はほぼ等しいとすると、次の式 5 に示すように、EL 駆動用 TFT102 のドレイン電流  $I_2$  は、これら 2 つの TFT の閾値電圧に依存しない。

40

#### 【0067】

#### 【式 5】

$$I_2 = I_1 (W_2/L_2) (L_1/W_1)$$

#### 【0068】

こうして、電流  $I_1$  に線型に対応する電流  $I_2$  を EL 素子 112 に入力することができる。

#### 【0069】

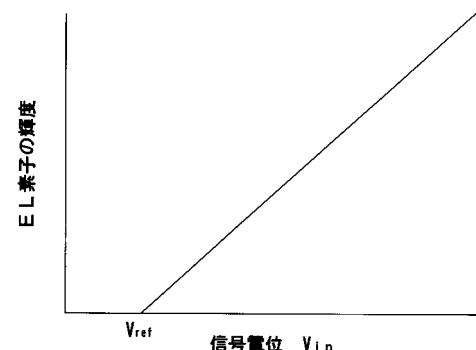

なお、電流  $I_1$  は式 2 より入力電位  $V_{in}$  に比例する。上記構成の EL 表示装置の映像信号の信号電位  $V_{in}$  と EL 素子の輝度の関係を示したグラフを図 2 に示す。横軸に映像信号の

50

信号電位  $V_{in}$  をとり、縦軸に E L 素子の輝度を示した。この様に、入力電圧  $V_{in}$  に線型に対応する輝度で E L 素子 1 1 2 を発光させることができる。

#### 【0070】

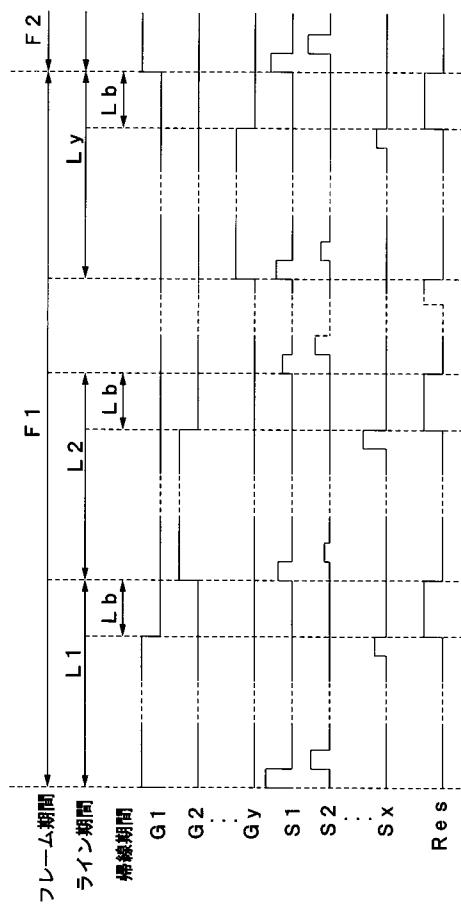

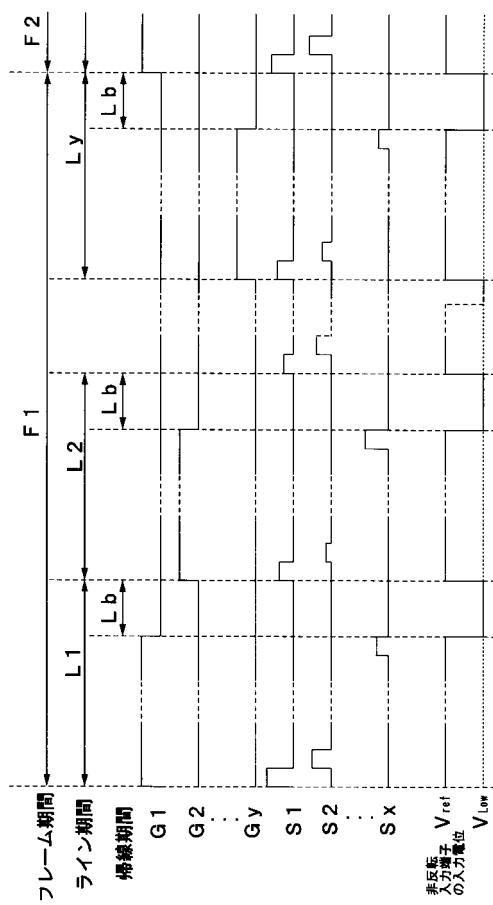

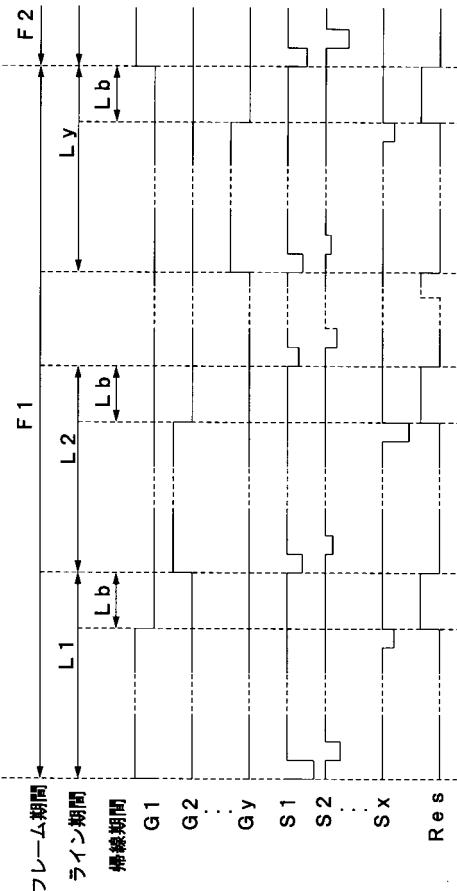

図 1 で示した構成の E L 表示装置を動作させる際のタイミングチャートを図 3 に示す。なお、この E L 表示装置は、 $x$  本のソース信号線  $S_1 \sim S_x$  を有し、 $x$  本の電源供給線  $V_1 \sim V_x$  を有し、 $y$  本のゲート信号線  $G_1 \sim G_y$  を有するものとする。

#### 【0071】

また、ここではスイッチング用 TFT 及びリセット用 TFT は  $n$  チャネル型 TFT とするが、 $p$  チャネル型 TFT を用いる場合は、ゲート信号線  $G_1 \sim G_y$  及びリセット用 TFT のゲート電極に入力する信号の位相を逆にすれば良い。

10

#### 【0072】

はじめゲート信号線  $G_1$  に信号が入力され、ゲート信号線  $G_1$  に接続された全てのスイッチング用 TFT が導通状態となる。このゲート信号線  $G_1$  が選択されている期間を第 1 のライン期間  $L_1$  と呼ぶことにする。第 1 のライン期間  $L_1$  の間に、アナログ信号入力線より入力された信号が、ソース信号線  $S_1 \sim S_x$  に順に入力される。この入力された信号電位に応じた輝度で E L 素子は発光する。

#### 【0073】

全てのソース信号線  $S_1 \sim S_x$  に信号が入力され終わると、再びソース信号線  $S_1$  から信号を入力するために、帰線期間  $L_b$  が設けられている。この帰線期間  $L_b$  の間に、リセット用 TFT のゲート電極に信号  $R_{es}$  が入力されて、リセット用 TFT は導通状態となり、全てのソース信号線  $S_1 \sim S_x$  の電位を  $0V$  にする。

20

#### 【0074】

その後、ゲート信号線  $G_2$  に信号が入力されて、ゲート信号線  $G_2$  に接続された全てのスイッチング用 TFT が導通状態となり、第 2 のライン期間  $L_2$  が始まる。第 1 のライン期間  $L_1$  の場合と同様に、第 2 のライン期間  $L_2$  の間にアナログ信号入力線より入力された信号が、ソース信号線  $S_1 \sim S_x$  に順に入力され、この入力された信号電位に応じた輝度で E L 素子は発光する。

#### 【0075】

全てのソース信号線  $S_1 \sim S_x$  に信号が入力され終わると、再びソース信号線  $S_1$  から信号を入力するために、帰線期間  $L_b$  が設けられている。この帰線期間  $L_b$  の間に、リセット用 TFT のゲート電極に信号  $R_{es}$  が入力されて、リセット用 TFT は導通状態となり、全てのソース信号線  $S_1 \sim S_x$  の電位を  $0V$  にする。

30

#### 【0076】

同様の操作を全てのゲート信号線  $G_1 \sim G_y$  について繰り返し、1 つの画像を表示する。1 つの画像を表示する期間を、1 フレーム期間と呼び、上記操作によって第 1 のフレーム期間  $F_1$  が終了する。

#### 【0077】

その後、再びゲート信号線  $G_1$  が選択されて、第 2 のフレーム期間  $F_2$  が始まる。

#### 【0078】

図 1 に示した本発明の E L 表示装置では、上記動作を繰り返して画像の表示を行う。

40

#### 【0079】

なお、図 1 9 のように、バッファ回路 1 9 0 を、スイッチ 1 0 9 と抵抗 1 0 3 の間に設けても良い。バッファ回路 1 9 0 は、バッファ 1 9 1 とコンデンサ 1 9 2 によって構成される。

#### 【0080】

#### 【実施例】

以下に、本発明の実施例について説明する。

#### 【0081】

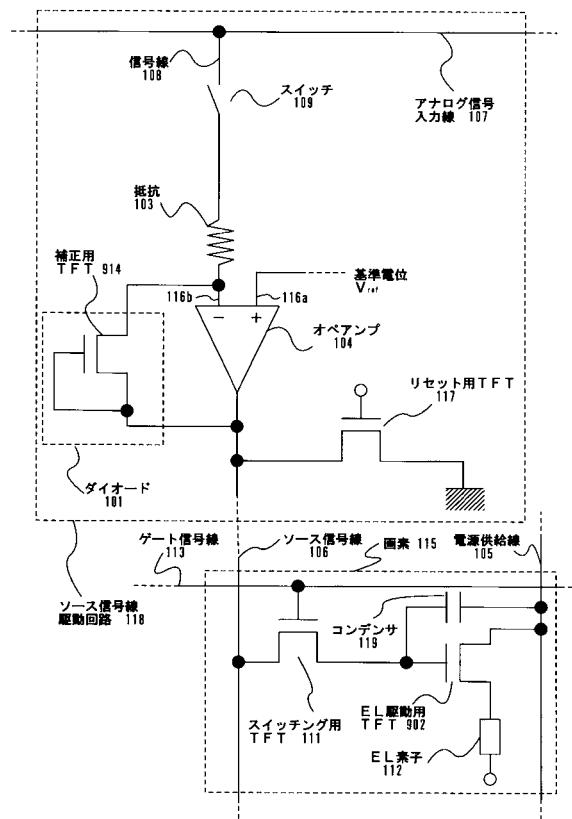

#### (実施例 1)

本実施例では、図 1 における補正用 TFT と E L 駆動用 TFT を  $n$  チャネル型 TFT で構

50

成した例について、図9を用いて説明する。なお、図1と同じ部分は、同じ符号を用いて示す。

#### 【0082】

図9において、本発明のEL表示装置の画素115と、その画素に信号を入力するソース信号線駆動回路の一部118を示す。

#### 【0083】

ソース信号線駆動回路118は、ダイオード101、抵抗103、オペアンプ104、アナログ信号入力線107、信号線108、スイッチ109、リセット用TFT117によって構成されている。また、ダイオード101は、ゲート電極とドレイン領域を電気的に接続した補正用TFT914によって構成されている。

10

#### 【0084】

なお、補正用TFT914は、nチャネル型TFTとする。また、リセット用TFT117は、pチャネル型TFTでもnチャネル型TFTでもどちらでも良い。

#### 【0085】

画素115は、EL駆動用TFT902、電源供給線105、ソース信号線106、スイッチング用TFT111、EL素子112、ゲート信号線113及びコンデンサ119によって構成されている。なお、EL駆動用TFT902は、nチャネル型TFTである。また、スイッチング用TFT111は、pチャネル型TFTでもnチャネル型TFTでもどちらでも良い。

#### 【0086】

アナログ信号入力線107に、信号線108が接続され、信号線108は、スイッチ109を介して抵抗103に接続されている。抵抗103は、オペアンプ104の反転入力端子116bに接続されている。オペアンプ104の反転入力端子116bは、補正用TFT914のソース領域に接続されている。また、オペアンプ104の非反転入力端子116aには、基準電位 $V_{ref}$ が入力される。オペアンプ104の出力端子は、補正用TFT914のドレイン領域及びソース信号線106に接続されている。リセット用TFT117のソース領域もしくはドレイン領域は、一方は、ソース信号線106に接続され、もう一方は、接地されている。

20

#### 【0087】

スイッチング用TFT111のゲート電極は、ゲート信号線113に接続され、スイッチング用TFT111のソース領域もしくはドレイン領域のどちらか一方は、ソース信号線106に接続され、もう一方は、EL駆動用TFT902のゲート電極及びコンデンサ119の一方の電極に接続されている。EL駆動用TFT902のソース領域は、電源供給線105に接続され、ドレイン領域はEL素子112の陰極に接続されている。コンデンサのもう一方の電極は電源供給線105に接続されている。EL素子112の陽極は、基準電源線に接続されているが、ここでは基準電源線は図示していない。

30

#### 【0088】

図9に示した表示装置の駆動方法について説明する。

#### 【0089】

アナログ信号入力線107に入力された映像信号の信号電位 $V_{in}$ は、スイッチ109を開閉することによってサンプリングされ、信号線108に入力される。

40

#### 【0090】

ここで、本実施例では、信号電位 $V_{in}$ は基準電位 $V_{ref}$ 以下の値を持ち、その値が小さいほど、大きな輝度を表す信号であるとする。

#### 【0091】

ここで、オペアンプ104の反転入力端子116bと出力端子がダイオード101を介して接続されているため、反転入力端子116bの電位は、非反転入力端子116aと等しくなる。つまり、反転入力端子116bの電位は、基準電位 $V_{ref}$ と等しくなる。そのため、抵抗103間の電圧は、 $V_{ref} - V_{in}$ となり、式6に示す電流 $I_1$ が抵抗を流れる。

#### 【0092】

50

## 【式6】

$$I_1 = (V_{ref} - V_{in}) / R$$

## 【0093】

なお、本実施例では、電流  $I_1$  は、抵抗のオペアンプ 104 の反転入力端子 116b に接続された側からアナログ信号入力線 107 に接続された側に向かって流れる。

## 【0094】

ここで、 $R$  は抵抗 103 の抵抗値である。この電流  $I_1$  は、ダイオード 101 を流れる。

ダイオード 101 を構成する補正用 TFT914 のドレイン電流が電流  $I_1$  に相当する。

ここで、補正用 TFT914 は、ドレイン領域とゲート電極が接続されているため、ゲート電圧とドレイン・ソース間電圧が等しい。そのため補正用 TFT914 は、飽和領域で動作する。

## 【0095】

またこのとき、補正用 TFT914 は、n チャネル型 TFT であるから、オペアンプ 104 の反転入力端子 116b に接続されている側の電位が、オペアンプ 104 の出力端子に接続されている側の電位よりも低くなければ、導通状態にならない。

## 【0096】

そのため、補正用 TFT914 は、オペアンプ 104 の反転入力端子 116b に接続された側が、ソース領域となり、オペアンプ 104 の出力端子に接続された側が、ドレイン領域になり、一方向のみに電流を流すダイオードとして用いられる。

## 【0097】

飽和領域で動作する TFT においては、先に示した式 1 が成立する。式 1 を変形し、ゲート電圧について解く。これにより、ドレイン電流が  $I_1$  の時のゲート電圧  $V_{GS1}$  を求めたものが、式 7 である。

## 【0098】

## 【式7】

$$V_{GS1} = \sqrt{2 I_1 (1/\mu_0 C_0) (L_1/W_1)} + V_{th1}$$

30

## 【0099】

なお、 $W_1$  は、補正用 TFT914 のゲート幅、 $L_1$  は補正用 TFT914 のゲート長である。また、 $V_{th1}$  は、補正用 TFT914 の閾値電圧である。

## 【0100】

ここで、最初、リセット用 TFT117 が導通状態にあり、ソース信号線 106 の電位は、0V であるとする。

## 【0101】

その後リセット用 TFT117 を非導通状態にすると、補正用 TFT914 のゲート電圧とドレイン・ソース間電圧は等しいため、ソース信号線 106 には、基準電位  $V_{ref}$  より電圧  $V_{GS1}$  だけ変化した電位  $V_{ref} + V_{GS1}$  が入力される。

40

## 【0102】

ソース信号線 106 に電位  $V_{ref} + V_{GS1}$  を入力する前に、リセット用 TFT117 によって、ソース信号線 106 の電位を 0V にしているのは、もしかしてある状態でのソース信号線 106 の電位が、その次に入力された信号電位によって変化した、オペアンプ 104 の反転入力端子 116b の電位よりも低くなってしまった場合に、補正用 TFT914 のソース領域とドレイン領域が入れ替わり、補正用 TFT914 は、非導通状態となってオペアンプ 104 の入出力間の帰還が効かなくなってしまうのを防ぐためである。この操作は、帰線期間（水平帰線期間）中におこなえばよい。

## 【0103】

なお、リセット用 TFT117 を導通状態にすることによって、オペアンプ 104 の出力

50

端子に与えられる電位は、0Vに限らない。一般に、アナログ信号入力線に入力された信号の最も低い電位に対応する、ソース信号線に出力された最も高い電位（以下、最高電位  $V_{SH_i}$  と呼ぶ）以上に設定すればよい。つまり、リセット用 TFT117 を導通状態にすることによって、オペアンプ 104 の出力端子の電位を、最高電位  $V_{SH_i}$  以上に設定する。

#### 【0104】

nチャネル型 TFT である補正用 TFT が常に導通状態となるように、オペアンプの出力端子の電位を、高い電位に設定する動作を、リセット動作と呼ぶことにする。

#### 【0105】

ソース信号線 106 に入力された電位  $V_{ref} + V_{GS1}$  は、ゲート信号線 113 に信号が入力され、導通状態となったスイッチング用 TFT111 を介して、コンデンサ 119 及び EL 駆動用 TFT902 のゲート電極に入力される。ここで、電源供給線 105 の電位（電源電位）は、基準電位  $V_{ref}$  と同じに設定されている。よって、導通状態の EL 駆動用 TFT902 のソース領域は  $V_{ref}$  の電位となっている。

#### 【0106】

このとき、EL 駆動用 TFT902 のゲート電圧  $V_{GS2}$  は、補正用 TFT914 のゲート電圧  $V_{GS1}$  と等しくなる。EL 駆動用 TFT902 も飽和領域で動作する場合、式 1 が成立するので、このときのドレイン電流  $I_2$  を求めたものが式 8 である。

#### 【0107】

#### 【式 8】

$$I_2 = (1/2) \mu_0 C_0 (W_2/L_2) (V_{GS1} - V_{th2})^2$$

10

#### 【0108】

ここで、 $V_{th2}$  は、EL 駆動用 TFT902 の閾値電圧とする。また、 $W_2$  及び  $L_2$  は、EL 駆動用 TFT902 のゲート幅及びゲート長である。

#### 【0109】

補正用 TFT914 と EL 駆動用 TFT902 の閾値電圧  $V_{th1}$  と  $V_{th2}$  がほぼ等しいとすると、次の式 9 に示すように、EL 駆動用 TFT902 のドレイン電流  $I_2$  は、これら 2 つの TFT の閾値電圧に依存しない。

30

#### 【0110】

#### 【式 9】

$$I_2 = I_1 (W_2/L_2) (L_1/W_1)$$

#### 【0111】

こうして、電流  $I_1$  に線型に対応する電流  $I_2$  を EL 素子 112 に入力することができる。

#### 【0112】

なお、電流  $I_1$  は式 6 より入力電位  $V_{in}$  に比例する。こうして、入力電位  $V_{in}$  に線型に対応する輝度で EL 素子 112 を発光させることができる。

40

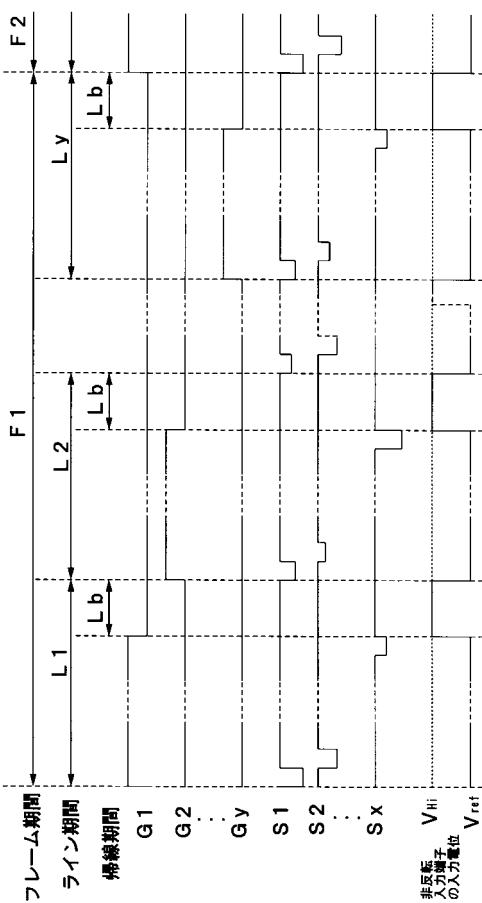

#### 【0113】

図 9 で示した構成の EL 表示装置を動作させる際のタイミングチャートを図 10 に示す。なお、この EL 表示装置は、x 本のソース信号線 S1 ~ Sx を有し、x 本の電源供給線 V1 ~ Vx を有し、y 本のゲート信号線 G1 ~ Gy を有するものとする。

#### 【0114】

また、ここではスイッチング用 TFT111 及びリセット用 TFT117 は n チャネル型 TFT とするが、p チャネル型 TFT を用いる場合は、ゲート信号線 G1 ~ Gy 及びリセット用 TFT117 のゲート電極に入力する信号の位相を逆にすれば良い。

#### 【0115】

はじめゲート信号線 G1 に信号が入力され、ゲート信号線 G1 に接続された全てのスイッ

50

チング用 T F T 1 1 1 が導通状態となる。このゲート信号線 G 1 が選択されている期間を第 1 のライン期間 L 1 と呼ぶことにする。第 1 のライン期間 L 1 の間に、アナログ信号入力線 1 0 7 より入力された信号が、ソース信号線 S 1 ~ S x に順に入力される。この入力された信号電位に応じた輝度で E L 素子 1 1 2 は発光する。

## 【 0 1 1 6 】

全てのソース信号線 S 1 ~ S x に信号が入力され終わると、再びソース信号線 S 1 から信号を入力するために、帰線期間 L b が設けられている。この帰線期間 L b の間に、リセット用 T F T 1 1 7 のゲート電極に信号 R e s が入力されて、リセット用 T F T 1 1 7 は導通状態となり、全てのソース信号線 S 1 ~ S x の電位を 0 V にする。

## 【 0 1 1 7 】

その後、ゲート信号線 G 2 に信号が入力されて、ゲート信号線 G 2 に接続された全てのスイッチング用 T F T 1 1 1 が導通状態となり、第 2 のライン期間 L 2 が始まる。第 1 のライン期間 L 1 の場合と同様に、第 2 のライン期間 L 2 の間にアナログ信号入力線 1 0 7 より入力された信号が、ソース信号線 S 1 ~ S x に順に入力され、この入力された信号電位に応じた輝度で E L 素子 1 1 2 は発光する。

## 【 0 1 1 8 】

全てのソース信号線 S 1 ~ S x に信号が入力され終わると、再びソース信号線 S 1 から信号を入力するために、帰線期間 L b が設けられている。この帰線期間 L b の間に、リセット用 T F T のゲート電極に信号 R e s が入力されて、リセット用 T F T は導通状態となり、全てのソース信号線 S 1 ~ S x の電位を 0 V にする。

## 【 0 1 1 9 】

同様の操作を全てのゲート信号線 G 1 ~ G y 全てについて繰り返し、1 つの画像を表示する。1 つの画像を表示する期間を、1 フレーム期間と呼び、上記操作によって第 1 のフレーム期間 F 1 が終了する。

## 【 0 1 2 0 】

その後、再びゲート信号線 G 1 が選択されて、第 2 のフレーム期間 F 2 が始まる。

## 【 0 1 2 1 】

図 1 に示した本発明の E L 表示装置では、上記動作を繰り返して画像の表示を行う。

## 【 0 1 2 2 】

( 実施例 2 )

本実施例では、図 1 とは異なった構成の駆動回路について説明する。

## 【 0 1 2 3 】

本実施例の構成の駆動回路を図 6 に示す。なお、図 1 と同じ部分は同じ符号を用いて示し、説明は省略する。図 6 においては、図 1 と異なり、リセット用 T F T 1 1 7 が配置されていない。

## 【 0 1 2 4 】

そのため、信号を入力する以前に、ソース信号線 1 0 6 の電位を、次に入力されるビデオ信号によるオペアンプ 1 0 4 の反転入力端子 1 1 6 b の電位より小さくしておく動作を別の手法で行う。この、信号を入力する以前に、ソース信号線 1 0 6 の電位を、次に入力されるビデオ信号によるオペアンプ 1 0 4 の反転入力端子 1 1 6 b の電位より小さくしておく動作を行う期間を、リセット期間と呼ぶことにする。

## 【 0 1 2 5 】

図 6 において、オペアンプ 1 0 4 の非反転入力端子 1 0 6 a に入力される電位  $V_+$  は、ビデオ信号をサンプリングする間は、基準電位  $V_{ref}$  に保たれる。一方、リセット期間において、電位  $V_{low}$  に下げられる。ここで、電位  $V_{low}$  は、外部より入力されるビデオ信号によってオペアンプ 1 0 4 の反転入力端子 1 1 6 b がどのような電位となってもその電位より低い値に設定する。

## 【 0 1 2 6 】

そのため、電位  $V_{low}$  は、基準電位  $V_{ref}$  以下の電位に設定される。

## 【 0 1 2 7 】

10

20

30

40

50

リセット期間において、オペアンプ 104 の非反転入力端子 106a は、電位  $V_{Low}$  になる。

**【0128】**

反転入力端子 106b の電位より非反転入力端子 106a の電位が小さくなるため、オペアンプ 104 は、低電源電位を出力する。こうして、オペアンプの出力端子は、十分に低い電位に保たれる。

**【0129】**

こうして、ソース信号線 106 の電位は  $V_{Low}$  以下となる。

**【0130】**

このリセット期間の後、オペアンプ 104 の非反転入力端子 116a の電位を再び  $V_{ref}$  に戻して、ビデオ信号を取り込めば、オペアンプ 104 の反転入力端子 116b の電位は、常に電位  $V_{Low}$  よりも高いので、ダイオード 101 は、導通状態のまま動作し、オペアンプ 104 は出入力間の帰還がかかって、非反転入力端子 116a と反転入力端子 116b の電位が等しくなるように動作する。

10

**【0131】**

このリセット期間は、帰線期間（水平帰線期間）中に設定すればよい。

**【0132】**

その他の動作については、発明の実施の形態と同様である。

**【0133】**

図 6 の構成の E-L 表示装置を動作させる際のタイミングチャートを図 7 に示す。なお、この E-L 表示装置は、 $x$  本のソース信号線  $S_1 \sim S_x$  を有し、 $x$  本の電源供給線  $V_1 \sim V_x$  を有し、 $y$  本のゲート信号線  $G_1 \sim G_y$  を有するものとする。

20

**【0134】**

なお、スイッチング用 TFT 111 は、n チャネル型 TFT とするが、p チャネル型 TFT を用いる場合は、ゲート信号線に入力される信号の位相を逆にすればよい。

**【0135】**

はじめゲート信号線  $G_1$  に信号が入力され、ゲート信号線  $G_1$  に接続された全てのスイッチング用 TFT 111 が導通状態となる。このゲート信号線  $G_1$  が選択されている期間を第 1 のライン期間  $L_1$  と呼ぶことにする。第 1 のライン期間  $L_1$  の間に、アナログ信号入力線 107 より入力された信号が、ソース信号線  $S_1 \sim S_x$  に順に入力される。この入力された信号電位に応じた輝度で E-L 素子 112 は発光する。

30

**【0136】**

全てのソース信号線  $S_1 \sim S_x$  に信号が入力され終わると、再びソース信号線  $S_1$  から信号を入力するために、帰線期間（水平帰線期間） $L_b$  が設けられている。この帰線期間  $L_b$  の間に、オペアンプ 104 の非反転入力端子 116a に電位  $V_{Low}$  が入力されて、全てのソース信号線  $S_1 \sim S_x$  の電位を  $V_{Low}$  以下にする。

**【0137】**

その後、ゲート信号線  $G_2$  に信号が入力されて、ゲート信号線  $G_2$  に接続された全てのスイッチング用 TFT 111 が導通状態となり、第 2 のライン期間  $L_2$  が始まる。第 1 のライン期間  $L_1$  の場合と同様に、第 2 のライン期間  $L_2$  の間にアナログ信号入力線 107 より入力された信号が、ソース信号線  $S_1 \sim S_x$  に順に入力され、この入力された信号電位に応じた輝度で E-L 素子 112 は発光する。

40

**【0138】**

全てのソース信号線  $S_1 \sim S_x$  に信号が入力され終わると、再びソース信号線  $S_1$  から信号を入力するために、帰線期間  $L_b$  が設けられている。この帰線期間  $L_b$  の間に、オペアンプ 104 の非反転入力端子 116a に電位  $V_{Low}$  が入力されて、全てのソース信号線  $S_1 \sim S_x$  の電位を  $V_{Low}$  以下にする。

**【0139】**

同様の操作を全てのゲート信号線  $G_1 \sim G_y$  について繰り返し、1 つの画像を表示する。1 つの画像を表示する期間を、1 フレーム期間と呼び、上記操作によって第 1 のフレーム

50

期間 F 1 が終了する。

【 0 1 4 0 】

その後、再びゲート信号線 G 1 が選択されて、第 2 のフレーム期間 F 2 が始まる。

【 0 1 4 1 】

図 6 に示した本発明の E L 表示装置では、上記動作を繰り返して画像の表示を行う。

【 0 1 4 2 】

( 実施例 3 )

本実施例では、図 9 とは異なった構成の駆動回路について説明する。

【 0 1 4 3 】

本実施例の構成の駆動回路を図 1 1 に示す。なお、図 9 と同じ部分は同じ符号を用いて示し、説明は省略する。図 1 1 においては、図 9 と異なり、リセット用 T F T 1 1 7 が配置されているない。

【 0 1 4 4 】

そのため、信号を入力する以前に、ソース信号線 1 0 6 の電位を、次に入力されるビデオ信号によるオペアンプ 1 0 4 の反転入力端子 1 1 6 b の電位より高くしておく動作を別の手法で行う。この、信号を入力する以前に、ソース信号線 1 0 6 の電位を、次に入力されるビデオ信号によるオペアンプ 1 0 4 の反転入力端子 1 1 6 b の電位より高くしておく動作を行う期間を、リセット期間と呼ぶこととする。

【 0 1 4 5 】

図 1 1 において、オペアンプ 1 0 4 の非反転入力端子 1 1 6 a に入力される電位  $V_+$  は、ビデオ信号をサンプリングする間は、基準電位  $V_{ref}$  に保たれる。一方、リセット期間において、電位  $V_{hi}$  に上げられる。ここで、電位  $V_{hi}$  は、外部より入力されるビデオ信号によってオペアンプ 1 0 4 の反転入力端子 1 1 6 b がどのような電位となってもその電位より高い値に設定する。

【 0 1 4 6 】

つまり、電位  $V_{hi}$  は、基準電位  $V_{ref}$  以上の電位に設定される。

【 0 1 4 7 】

反転入力端子 1 1 6 b の電位より非反転入力端子 1 1 6 a の電位が大きくなるため、オペアンプは、高電源電位を出力する。こうして、オペアンプの出力端子は、十分に高い電位に保たれる。

【 0 1 4 8 】

リセット期間において、オペアンプ 1 0 4 の出力電位は、電位  $V_{hi}$  以上になる。このリセット期間の後、オペアンプ 1 0 4 の非反転入力端子 1 1 6 a の電位を再び  $V_{ref}$  に戻して、ビデオ信号を取り込めば、オペアンプ 1 0 4 の反転入力端子 1 1 6 b の電位は、常に電位  $V_{hi}$  よりも低いので、ダイオード 1 0 1 は、導通状態のまま動作し、オペアンプ 1 0 4 は入出力間の帰還がかかって、非反転入力端子 1 1 6 a と反転入力端子 1 1 6 b の電位が等しくなるように動作する。

【 0 1 4 9 】

このリセット期間は、帰線期間（水平帰線期間）中に設定すればよい。

【 0 1 5 0 】

その他の動作については、実施例 1 と同様である。

【 0 1 5 1 】

図 1 1 の構成の E L 表示装置を動作させる際のタイミングチャートを図 1 2 に示す。なお、この E L 表示装置は、x - 1 本のソース信号線 S 1 ~ S x を有し、x - 1 本の電源供給線  $V_1 \sim V_x$  を有し、y - 1 本のゲート信号線 G 1 ~ G y を有するものとする。

【 0 1 5 2 】

なお、スイッチング用 T F T 1 1 1 は、n チャネル型 T F T とするが、p チャネル型 T F T を用いる場合は、ゲート信号線に入力される信号の位相を逆にすればよい。

【 0 1 5 3 】

はじめゲート信号線 G 1 に信号が入力され、ゲート信号線 G 1 に接続された全てのスイッ

10

20

30

40

50

チング用 T F T 1 1 1 が導通状態となる。このゲート信号線 G 1 が選択されている期間を第 1 のライン期間 L 1 と呼ぶことにする。第 1 のライン期間 L 1 の間に、アナログ信号入力線 1 0 7 より入力された信号が、ソース信号線 S 1 ~ S x に順に入力される。この入力された信号電位に応じた輝度で E L 素子 1 1 2 は発光する。

#### 【 0 1 5 4 】

全てのソース信号線 S 1 ~ S x に信号が入力され終わると、再びソース信号線 S 1 から信号を入力するために、帰線期間（水平帰線期間）L b が設けられている。この帰線期間 L b の間に、オペアンプ 1 0 4 の非反転入力端子 1 1 6 a に電位 V<sub>H*i*</sub> が入力されて、全てのソース信号線 S 1 ~ S x の電位を V<sub>H*i*</sub> 以上にする。

#### 【 0 1 5 5 】

その後、ゲート信号線 G 2 に信号が入力されて、ゲート信号線 G 2 に接続された全てのスイッチング用 T F T 1 1 1 が導通状態となり、第 2 のライン期間 L 2 が始まる。第 1 のライン期間 L 1 の場合と同様に、第 2 のライン期間 L 2 の間にアナログ信号入力線 1 0 7 より入力された信号が、ソース信号線 S 1 ~ S x に順に入力され、この入力された信号電位に応じた輝度で E L 素子 1 1 2 は発光する。

#### 【 0 1 5 6 】

全てのソース信号線 S 1 ~ S x に信号が入力され終わると、再びソース信号線 S 1 から信号を入力するために、帰線期間 L b が設けられている。この帰線期間 L b の間に、オペアンプ 1 0 4 の非反転入力端子 1 1 6 a に電位 V<sub>H*i*</sub> が入力されて、全てのソース信号線 S 1 ~ S x の電位を V<sub>H*i*</sub> 以上にする。

#### 【 0 1 5 7 】

同様の操作を全てのゲート信号線 G 1 ~ G y について繰り返し、1 つの画像を表示する。1 つの画像を表示する期間を、1 フレーム期間と呼び、上記操作によって第 1 のフレーム期間 F 1 が終了する。

#### 【 0 1 5 8 】

その後、再びゲート信号線 G 1 が選択されて、第 2 のフレーム期間 F 2 が始まる。

#### 【 0 1 5 9 】

図 1 1 に示した本発明の E L 表示装置では、上記動作を繰り返して画像の表示を行う。

#### 【 0 1 6 0 】

（実施例 4 ）

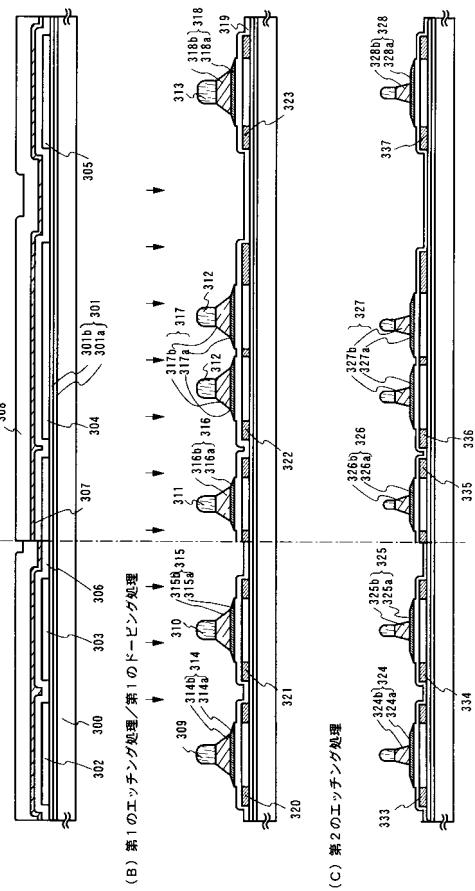

本実施例では、本発明の E L 表示装置において、同一基板上に画素部と、画素部の周辺に設ける駆動回路の T F T ( n チャネル型 T F T 及び p チャネル型 T F T を代表的に示す ) を同時に作製する方法について、図 1 4 ~ 図 1 7 を用いて詳細に説明する。

#### 【 0 1 6 1 】

まず、本実施例ではコーニング社の # 7 0 5 9 ガラスや # 1 7 3 7 ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミニノホウケイ酸ガラスなどのガラスからなる基板 3 0 0 を用いる。なお、基板 3 0 0 としては、透光性を有する基板であれば限定されず、石英基板を用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

#### 【 0 1 6 2 】

次いで、基板 3 0 0 上に酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの絶縁膜から成る下地膜 3 0 1 を形成する。本実施例では下地膜 3 0 1 として 2 層構造を用いるが、前記絶縁膜の単層膜または 2 層以上積層させた構造を用いても良い。下地膜 3 0 1 の一層目としては、プラズマ C V D 法を用い、SiH<sub>4</sub>、NH<sub>3</sub>、及び N<sub>2</sub>O を反応ガスとして成膜される酸化窒化珪素膜 3 0 1 a を 1 0 ~ 2 0 0 nm ( 好ましくは 5 0 ~ 1 0 0 nm ) 形成する。本実施例では、膜厚 5 0 nm の酸化窒化珪素膜 3 0 1 a ( 組成比 Si = 3 2 % 、 O = 2 7 % 、 N = 2 4 % 、 H = 1 7 % ) を形成した。次いで、下地膜 3 0 1 の二層目としては、プラズマ C V D 法を用い、SiH<sub>4</sub>、及び N<sub>2</sub>O を反応ガスとして成膜される酸化窒化珪素膜 3 0 1 b を 5 0 ~ 2 0 0 nm ( 好ましくは 1 0 0 ~ 1 5 0 nm ) の厚さに積層形成する。本実施例では、膜厚 1 0 0 nm の酸化窒化珪素膜 3 0 1 b ( 組成比 Si = 3 2 % 、

10

20

30

40

50

O = 5 9 %、 N = 7 %、 H = 2 % ) を形成した。

#### 【 0 1 6 3 】

次いで、下地膜上に半導体層 3 0 2 ~ 3 0 5 を形成する。半導体層 3 0 2 ~ 3 0 5 は、非晶質構造を有する半導体膜を公知の手段 (スパッタ法、 L P C V D 法、またはプラズマ C V D 法等) により成膜した後、公知の結晶化処理 (レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等) を行って得られた結晶質半導体膜を所望の形状にパターニングして形成する。この半導体層 3 0 2 ~ 3 0 5 の厚さは 2 5 ~ 8 0 n m (好ましくは 3 0 ~ 6 0 n m) の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくは珪素 (シリコン) またはシリコンゲルマニウム (Si<sub>x</sub>Ge<sub>1-x</sub> (X = 0 . 0 0 1 ~ 0 . 0 2)) 合金などで形成すると良い。本実施例では、プラズマ C V D 法を用い、5 5 n m の非晶質珪素膜を成膜した後、ニッケルを含む溶液を非晶質珪素膜上に保持させた。この非晶質珪素膜に脱水素化 (5 0 0 、 1 時間) を行った後、熱結晶化 (5 5 0 、 4 時間) を行い、さらに結晶化を改善するためのレーザーアニール処理を行って結晶質珪素膜を形成した。そして、この結晶質珪素膜をフォトリソグラフィ法を用いたパターニング処理によって、半導体層 3 0 2 ~ 3 0 5 を形成した。

10

#### 【 0 1 6 4 】

また、半導体層 3 0 2 ~ 3 0 5 を形成した後、 T F T の閾値電圧を制御するために微量な不純物元素 (ボロンまたはリン) のドーピングを行ってもよい。

#### 【 0 1 6 5 】

また、レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーや Y A G レーザー、 Y V O<sub>4</sub> レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数 3 0 H z とし、レーザーエネルギー密度を 1 0 0 ~ 4 0 0 m J / c m<sup>2</sup> (代表的には 2 0 0 ~ 3 0 0 m J / c m<sup>2</sup>) とする。また、 Y A G レーザーを用いる場合にはその第 2 高調波を用いパルス発振周波数 1 ~ 1 0 k H z とし、レーザーエネルギー密度を 3 0 0 ~ 6 0 0 m J / c m<sup>2</sup> (代表的には 3 5 0 ~ 5 0 0 m J / c m<sup>2</sup>) とすると良い。そして幅 1 0 0 ~ 1 0 0 0 μ m 、例えば 4 0 0 μ m で線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率 (オーバーラップ率) を 5 0 ~ 9 0 % として行えばよい。

20

#### 【 0 1 6 6 】

次いで、半導体層 3 0 2 ~ 3 0 5 を覆うゲート絶縁膜 3 0 6 を形成する。ゲート絶縁膜 3 0 6 はプラズマ C V D 法またはスパッタ法を用い、厚さを 4 0 ~ 1 5 0 n m として珪素を含む絶縁膜で形成する。本実施例では、プラズマ C V D 法により 1 1 0 n m の厚さで酸化窒化珪素膜 (組成比 Si = 3 2 %、 O = 5 9 %、 N = 7 %、 H = 2 %) で形成した。勿論、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

#### 【 0 1 6 7 】

また、酸化珪素膜を用いる場合には、プラズマ C V D 法で T E O S (Tetraethyl Orthosilicate) と O<sub>2</sub> とを混合し、反応圧力 4 0 P a 、基板温度 3 0 0 ~ 4 0 0 とし、高周波 (1 3 . 5 6 M H z) 電力密度 0 . 5 ~ 0 . 8 W / c m<sup>2</sup> で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後 4 0 0 ~ 5 0 0 の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

40

#### 【 0 1 6 8 】

次いで、図 1 4 (A) に示すように、ゲート絶縁膜 3 0 6 上に膜厚 2 0 ~ 1 0 0 n m の第 1 の導電膜 3 0 7 と、膜厚 1 0 0 ~ 4 0 0 n m の第 2 の導電膜 3 0 8 とを積層形成する。本実施例では、膜厚 3 0 n m の T a N 膜からなる第 1 の導電膜 3 0 7 と、膜厚 3 7 0 n m の W 膜からなる第 2 の導電膜 3 0 8 を積層形成した。 T a N 膜はスパッタ法で形成し、 T a のターゲットを用い、窒素を含む雰囲気内でスパッタした。また、 W 膜は、 W のターゲットを用いたスパッタ法で形成した。その他に 6 フッ化タンゲステン (W F<sub>6</sub>) を用いる

50

熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は $20\ \mu\text{cm}$ 以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9~ $20\ \mu\text{cm}$ を実現することができた。

#### 【0169】

なお、本実施例では、第1の導電膜307をTaN、第2の導電膜308をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜を用いてもよい。また、Ag、Pd、Cuからなる合金を用いてもよい。また、第1の導電膜をタンタル(Ta)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化チタン(TiN)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

#### 【0170】

次に、図14(B)に示すようにフォトリソグラフィ法を用いてレジストからなるマスク309~313を形成し、電極及び配線を形成するための第1のエッチング処理を行う。

20 第1のエッチング処理では第1及び第2のエッチング条件で行う。本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。ここでは、松下電器産業(株)製のICPを用いたドライエッチング装置(Model E645-ICP)を用いた。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチング条件によって、Wのテーパー角は、約26°となる。

#### 【0171】

この後、図14(B)に示すようにレジストからなるマスク309~313を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。第2のエッチング条件でのWに対するエッチング速度は58.97nm/min、TaNに対するエッチング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10~20%程度の割合でエッチング時間を増加させると良い。

#### 【0172】

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることで、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15~45°とすればよい。こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層314~318(第1の導電層314a~318aと第2の導電層314b~318b)を形

10

20

30

40

50

成する。319はゲート絶縁膜であり、第1の形状の導電層314～318で覆われない領域は20～50nm程度エッティングされ薄くなった領域が形成される。

#### 【0173】

そして、レジストからなるマスクを除去せずに第1のドーピング処理を行い、半導体層にn型を付与する不純物元素を添加する。(図14(B))ドーピング処理はイオンドープ法、若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を $1 \times 10^{13}$ ～ $5 \times 10^{15}$ atoms/cm<sup>3</sup>とし、加速電圧を60～100keVとして行う。本実施例ではドーズ量を $1.5 \times 10^{15}$ atoms/cm<sup>3</sup>とし、加速電圧を80keVとして行った。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いた。この場合、導電層314～318がn型を付与する不純物元素に対するマスクとなり、自己整合的に高濃度不純物領域320～323が形成される。高濃度不純物領域320～323には $1 \times 10^{20}$ ～ $1 \times 10^{21}$ atoms/cm<sup>3</sup>の濃度範囲でn型を付与する不純物元素を添加する。

#### 【0174】

次いで、図14(C)に示すようにレジストからなるマスクを除去せずに第2のエッティング処理を行う。ここでは、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を20/20/20(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッティング処理でのWに対するエッティング速度は124.62nm/min、TaNに対するエッティング速度は20.67nm/minであり、TaNに対するWの選択比は6.05である。従って、W膜が選択的にエッティングされる。この第2のエッティングによりWのテーパー角は70°となった。この第2のエッティング処理により第2の導電層324b～328bを形成する。一方、第1の導電層314a～318aは、ほとんどエッティングされず、第1の導電層324a～328aを形成する。

#### 【0175】

次いで図15(A)に示すように、第2のドーピング処理を行う。ドーピングは第2の導電層324b～328bを不純物元素に対するマスクとして用い、第1の導電層のテーパー部下方の半導体層に不純物元素が添加されるようにドーピングする。本実施例では、不純物元素としてP(リン)を用い、ドーズ量 $1.5 \times 10^{14}$ atoms/cm<sup>3</sup>、電流密度0.5μA、加速電圧90keVにてプラズマドーピングを行った。こうして、第1の導電層と重なる低濃度不純物領域329～333を自己整合的に形成する。この低濃度不純物領域329～333へ添加されたリン(P)の濃度は、 $1 \times 10^{17}$ ～ $5 \times 10^{18}$ atoms/cm<sup>3</sup>であり、且つ、第1の導電層のテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第1の導電層のテーパー部と重なる半導体層において、第1の導電層のテーパー部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。また、高濃度不純物領域333～337にも不純物元素が添加され、高濃度不純物領域333～337を形成する。

#### 【0176】

次いで、図15(B)に示すようにレジストからなるマスクを除去してからフォトリソグラフィー法を用いて、第3のエッティング処理を行う。この第3のエッティング処理では第1の導電層のテーパー部を部分的にエッティングして、第2の導電層と重なる形状にするために行われる。ただし、第3のエッティングを行わない領域には、図15(B)に示すようにレジスト(338、339)からなるマスクを形成する。

#### 【0177】

第3のエッティング処理におけるエッティング条件は、エッティングガスとしてCl<sub>2</sub>とSF<sub>6</sub>とを用い、それぞれのガス流量比を10/50(ccm)として第1及び第2のエッティングと同様にICPエッティング法を用いて行う。なお、第3のエッティング処理でのTaNに対するエッティング速度は、111.2nm/minであり、ゲート絶縁膜に対するエッチ

10

20

30

40

50

グ速度は、12.8 nm/minである。

#### 【0178】

本実施例では、1.3 Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。以上により、第1の導電層340a～342aが形成される。

#### 【0179】

上記第3のエッティングによって、第1の導電層340a～342aと重ならない不純物領域(LDD領域)343～345が形成される。なお、不純物領域(GOLD領域)346および347は、第1の導電層324aおよび326aと重なったままである。

10

#### 【0180】

また、第1の導電層324aと第2の導電層324bとで形成された電極は、最終的に駆動回路のnチャネル型TFTのゲート電極となり、また、第1の導電層340aと第2の導電層340bとで形成された電極は、最終的に駆動回路のpチャネル型TFTのゲート電極となる。

#### 【0181】

同様に、第1の導電層341aと第2の導電層341bとで形成された電極は、最終的に画素部のnチャネル型TFTのゲート電極となり、第1の導電層342aと第2の導電層342bとで形成された電極は、最終的に画素部のpチャネル型TFTのゲート電極となる。さらに第1の導電層326aと第2の導電層326bとで形成された電極は、最終的に画素部のコンデンサ(保持容量)の一方の電極となる。

20

#### 【0182】

このようにして、本実施例は、第1の導電層340a～342aと重ならない不純物領域(LDD領域)343～345と、第1の導電層324aおよび326aと重なる不純物領域(GOLD領域)346および347を同時に形成することができ、TFT特性に応じた作り分けが可能となる。

#### 【0183】

次に、レジストからなるマスク338及び339を除去した後、ゲート絶縁膜319をエッティング処理する。ここでエッティング処理は、エッティングガスにCHF<sub>3</sub>を用い、反応性イオンエッティング法(RIE法)を用いて行う。本実施例では、チャンバー圧力6.7Pa、RF電力800W、CHF<sub>3</sub>ガス流量35scmで第3のエッティング処理を行った。

30

#### 【0184】

これにより、高濃度不純物領域333～337の一部は露呈し、絶縁膜356a～356eが形成される。

#### 【0185】

次いで、新たにレジストからなるマスク348、349を形成して第3のドーピング処理を行う。この第3のドーピング処理により、pチャネル型TFTの活性層となる半導体層に前記導電型(n型)とは逆の導電型(p型)を付与する不純物元素が添加された不純物領域350～355を形成する。(図15(C))第1の導電層340a、326aおよび342aを不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に不純物領域を形成する。

40

#### 【0186】

本実施例では、不純物領域350～355はジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法で形成する。なお、この第3のドーピング処理の際には、nチャネル型TFTを形成する半導体層はレジストからなるマスク348、349で覆われている。第1のドーピング処理及び第2のドーピング処理によって、不純物領域350～355にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においてもp型を付与する不純物元素の濃度が $2 \times 10^{20} \sim 2 \times 10^{21}$ atoms/cm<sup>3</sup>となるようにドーピング処理することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問

50

題は生じない。

【0187】

以上までの工程でそれぞれの半導体層に不純物領域が形成される。

【0188】

なお、本実施例では、ゲート絶縁膜をエッチングした後で不純物（ボロン）のドーピングを行う方法を示したが、ゲート絶縁膜をエッチングしないで不純物のドーピングを行っても良い。

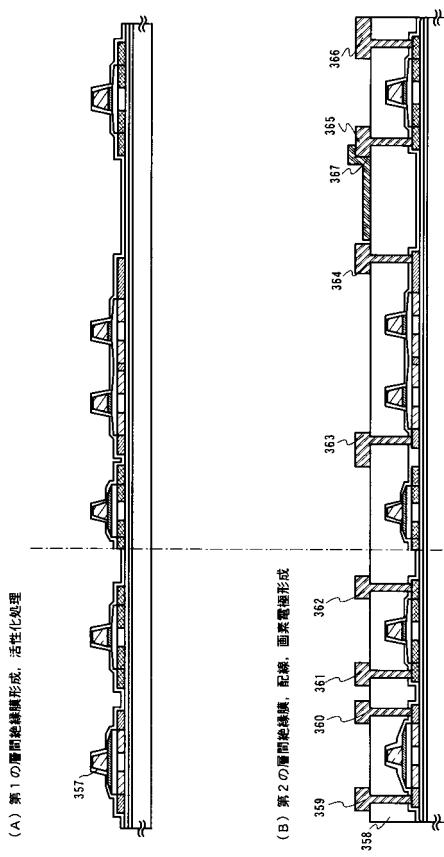

【0189】

次いで、レジストからなるマスク 348、349を除去して図16(A)に示すように第1の層間絶縁膜357を形成する。この第1の層間絶縁膜357としては、プラズマCVD法またはスパッタ法を用い、厚さを100～200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚150nmの酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜357は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

10

【0190】

次いで、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700、代表的には500～550で行えばよく、本実施例では550、4時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

20

【0191】

なお、本実施例では、上記活性化処理と同時に、結晶化の際に触媒として使用したニッケルが高濃度のリンを含む不純物領域にゲッタリングされ、主にチャネル形成領域となる半導体層中のニッケル濃度が低減される。このようにして作製したチャネル形成領域を有するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、良好な特性を達成することができる。

【0192】

また、第1の層間絶縁膜を形成する前に活性化処理を行っても良い。ただし、用いた配線材料が熱に弱い場合には、本実施例のように配線等を保護するため層間絶縁膜（シリコンを主成分とする絶縁膜、例えば窒化珪素膜）を形成した後で活性化処理を行うことが好ましい。

30

【0193】

その他、活性化処理を行った後でドーピング処理を行い、第1の層間絶縁膜を形成させても良い。

【0194】

さらに、3～100%の水素を含む雰囲気中で、300～550で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。本実施例では水素を約3%の含む窒素雰囲気中で410、1時間の熱処理を行った。この工程は層間絶縁膜に含まれる水素により半導体層のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

40

【0195】

また、活性化処理としてレーザーアニール法を用いる場合には、上記水素化を行った後、エキシマレーザーやYAGレーザー等のレーザー光を照射することが望ましい。

【0196】

次いで、図16(B)に示すように第1の層間絶縁膜357上に有機絶縁物材料から成る第2の層間絶縁膜358を形成する。本実施例では膜厚1.6μmのアクリル樹脂膜を形成した。次いで、各不純物領域333、336、350、352に達するコンタクトホールを形成するためのパターニングを行う。

【0197】

50

第2の層間絶縁膜358としては、珪素を含む絶縁材料や有機樹脂からなる膜を用いる。珪素を含む絶縁材料としては、酸化珪素、窒化珪素、酸化窒化珪素を用いることができ、また有機樹脂としては、ポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)などを用いることができる。

#### 【0198】

本実施例では、プラズマCVD法により形成された酸化窒化珪素膜を形成した。なお、酸化窒化珪素膜の膜厚として好ましくは1~5μm(さらに好ましくは2~4μm)とすればよい。酸化窒化珪素膜は、膜自身に含まれる水分が少ないためにEL素子の劣化を抑える上で有効である。

#### 【0199】

また、コンタクトホールの形成には、ドライエッチングまたはウエットエッチングを用いることができるが、エッチング時における静電破壊の問題を考えると、ウエットエッチング法を用いるのが望ましい。

#### 【0200】

さらに、ここでのコンタクトホールの形成において、第1層間絶縁膜及び第2層間絶縁膜を同時にエッチングするため、コンタクトホールの形状を考えると第2層間絶縁膜を形成する材料は、第1層間絶縁膜を形成する材料よりもエッチング速度の速いものを用いるのが好ましい。

#### 【0201】

そして、各不純物領域333、336、350、352とそれぞれ電気的に接続する配線359~366を形成する。そして、膜厚50nmのTi膜と、膜厚500nmの合金膜(A1とTiとの合金膜)との積層膜をパターニングして形成するが、他の導電膜を用いても良い。

#### 【0202】

次いで、その上に透明導電膜を80~120nmの厚さで形成し、パターニングすることによって透明電極367を形成する。(図16(B))

#### 【0203】

なお、本実施例では、透明電極として酸化インジウム・スズ(ITO)膜や酸化インジウムに2~20[%]の酸化亜鉛(ZnO)を混合した透明導電膜を用いる。

#### 【0204】

また、透明電極367は、ドレイン配線365と接して重ねて形成することによってEL駆動用TFTのドレイン領域と電気的な接続が形成される。

#### 【0205】

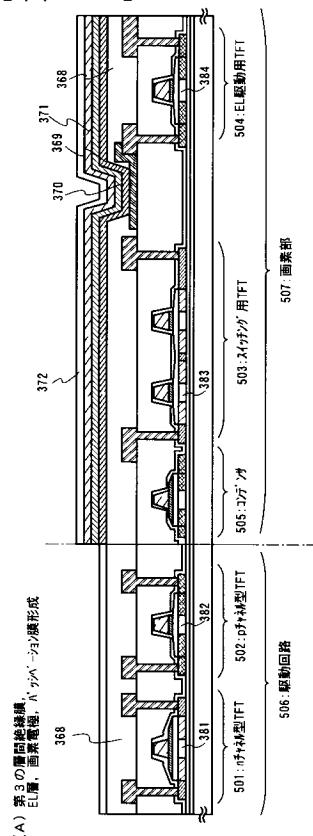

次に、図17(A)に示すように、珪素を含む絶縁膜(本実施例では酸化珪素膜)を500nmの厚さに形成し、透明電極367に対応する位置に開口部を形成して、バンクとして機能する第3の層間絶縁膜368を形成する。開口部を形成する際、ウエットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因するEL層の劣化が顕著な問題となってしまうため、注意が必要である。

#### 【0206】

なお、本実施例においては、第3の層間絶縁膜として酸化珪素でなる膜を用いているが、場合によっては、ポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)といった有機樹脂膜を用いることもできる。

#### 【0207】

次に、図17(A)で示すようにEL層369を蒸着法により形成し、更に蒸着法により陰極(MgAg電極)370および保護電極371を形成する。このときEL層369及び陰極370を形成するに先立って透明電極367に対して熱処理を施し、水分を完全に除去しておくことが望ましい。なお、本実施例ではEL素子の陰極としてMgAg電極を用いるが、公知の他の材料であっても良い。

#### 【0208】

10

20

30

40

50

なお、E L層369としては、公知の材料を用いることができる。本実施例では正孔輸送層(Hole transporting layer)及び発光層(Emitting layer)でなる2層構造をE L層とするが、正孔輸送層、正孔注入層、電子注入層若しくは電子輸送層のいずれかを設ける場合もある。このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。

#### 【0209】

本実施例では正孔輸送層としてポリフェニレンビニレンを蒸着法により形成する。また、発光層としては、ポリビニルカルバゾールに1, 3, 4-オキサジアゾール誘導体のPBDを30~40%分子分散させたものを蒸着法により形成し、緑色の発光中心としてクマリン6を約1%添加している。

10

#### 【0210】

また、保護電極371でもE L層369を水分や酸素から保護することは可能であるが、さらに好ましくはパッシベーション膜372を設けると良い。本実施例ではパッシベーション膜372として300nm厚の窒化珪素膜を設ける。このパッシベーション膜も保護電極371の後に大気解放しないで連続的に形成しても構わない。

#### 【0211】

また、保護電極371は陰極370の劣化を防ぐために設けられ、アルミニウムを主成分とする金属膜が代表的である。勿論、他の材料でも良い。また、E L層369、陰極370は非常に水分に弱いので、保護電極371までを大気解放しないで連続的に形成し、外気からE L層を保護することが望ましい。

20

#### 【0212】

なお、E L層369の膜厚は10~400nm(典型的には60~150nm)、陰極370の厚さは80~200nm(典型的には100~150nm)とすれば良い。

#### 【0213】

こうして図17(A)に示すような構造のE Lモジュールが完成する。なお、本実施例におけるE Lモジュールの作製工程においては、回路の構成および工程の関係上、ゲート電極を形成している材料であるTa、Wによってソース信号線を形成し、ソース、ドレイン電極を形成している配線材料であるAlによってゲート信号線を形成しているが、異なる材料を用いても良い。

#### 【0214】

また、nチャネル型TFT501及びpチャネル型TFT502を有する駆動回路506と、スイッチング用TFT503、E L駆動用TFT504及びコンデンサ505とを有する画素部507を同一基板上に形成することができる。

30

#### 【0215】

なお、本実施例においては、スイッチング用TFT503にnチャネル型TFT、E L駆動用TFT504にpチャネル型TFTを用い、E L素子の素子構成から下面出射となる構成を示したが、本実施例は、好ましい一形態にすぎず、これに限られる必要はない。

#### 【0216】

駆動回路506のnチャネル型TFT501はチャネル形成領域381、ゲート電極の一部を構成する第1の導電層324aと重なる低濃度不純物領域329(GOLD領域)とソース領域またはドレイン領域として機能する高濃度不純物領域333を有している。pチャネル型TFT502にはチャネル形成領域382、ゲート電極の一部を構成する第1の導電層340aと重ならない不純物領域353、ソース領域またはドレイン領域として機能する不純物領域350を有している。

40

#### 【0217】

画素部507のスイッチング用TFT503にはチャネル形成領域383、ゲート電極を形成する第1の導電層341aと重ならず、ゲート電極の外側に形成される低濃度不純物領域344(LDD領域)344とソース領域またはドレイン領域として機能する高濃度不純物領域336を有している。

#### 【0218】

50

画素部 507 の EL 駆動用 TFT504 にはチャネル形成領域 384、ソース領域またはドレイン領域として機能する高濃度不純物領域 352 および 355 を有している。また、コンデンサ 505 は、第一の導電層 326a と第二の導電層 326b を一方の電極として機能するように形成されている。

#### 【0219】

なお、本実施例においては、画素電極（陽極）上に EL 層を形成させた後、陰極を形成させる構造を示したが、画素電極（陰極）上に EL 層及び陽極を形成させる構造としても良い。ただし、この場合には、これまで説明した下面出射と異なり、上面出射の形態をとる。また、この時、EL 駆動用 TFT504 は、n チャネル型 TFT で形成するのが望ましい。

10

#### 【0220】

本実施例は、実施例 1 ~ 実施例 3 と自由に組み合わせて、実施することが可能である。

#### 【0221】

##### (実施例 5)

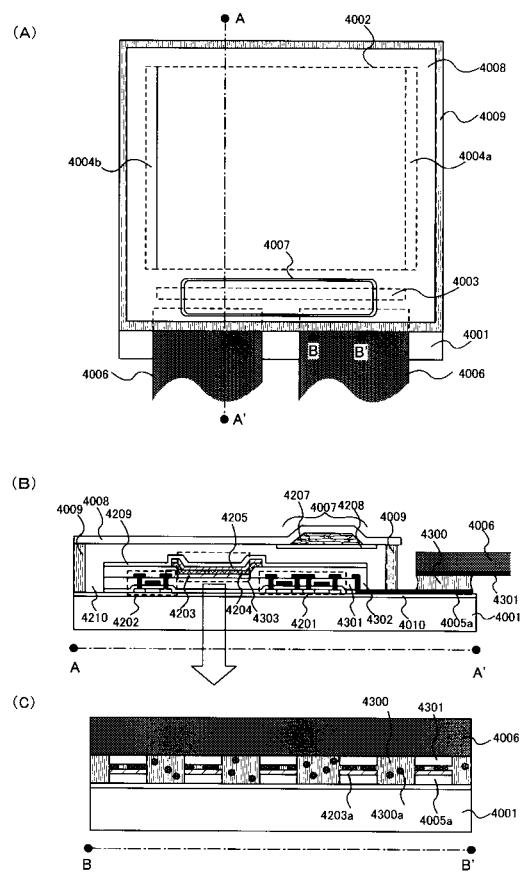

本実施例では、本発明を用いて EL 表示装置を作製した例について図 13 を用いて説明する。

#### 【0222】

図 13 (A) は、シーリング材によって封止することによって形成された EL 表示装置の上面図であり、図 13 (B) は、図 13 (A) の A - A' における断面図、図 13 (C) は図 13 (A) の B - B' における断面図である。

20

#### 【0223】

基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、4004b とを囲むようにして、シール材 4009 が設けられている。また画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b との上にシーリング材 4008 が設けられている。よって画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とは、基板 4001 とシール材 4009 とシーリング材 4008 とによって、充填材 4210 で密封されている。

#### 【0224】

また基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とは、複数の TFT を有している。図 13 (B) では代表的に、下地膜 4010 上に形成された、ソース信号線駆動回路 4003 に含まれる駆動 TFT (但し、ここでは n チャネル型 TFT と p チャネル型 TFT を図示する) 4201 及び画素部 4002 に含まれる EL 駆動用 TFT 4202 を図示した。

30

#### 【0225】

本実施例では、駆動 TFT 4201 には公知の方法で作製された p チャネル型 TFT 及び n チャネル型 TFT が用いられ、EL 駆動用 TFT 4202 には公知の方法で作製された p チャネル型 TFT が用いられる。また、画素部 4002 には EL 駆動用 TFT 4202 のゲートに接続された保持容量 (図示せず) が設けられる。

40

#### 【0226】

駆動 TFT 4201 及び EL 駆動用 TFT 4202 上には層間絶縁膜 (平坦化膜) 4301 が形成され、その上に EL 駆動用 TFT 4202 のドレインと電気的に接続する画素電極 (陽極) 4203 が形成される。画素電極 4203 としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したもの用いても良い。

#### 【0227】

そして、画素電極 4203 の上には絶縁膜 4302 が形成され、絶縁膜 4302 は画素電極 4203 の上に開口部が形成されている。この開口部において、画素電極 4203 の上

50

には E L (エレクトロルミネッセンス) 層 4 2 0 4 が形成される。E L 層 4 2 0 4 は公知の有機 E L 材料または無機 E L 材料を用いることができる。また、有機 E L 材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

#### 【0228】

E L 層 4 2 0 4 の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、E L 層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

#### 【0229】

E L 層 4 2 0 4 の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極 4 2 0 5 が形成される。また、陰極 4 2 0 5 と E L 層 4 2 0 4 の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、E L 層 4 2 0 4 を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極 4 2 0 5 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極 4 2 0 5 は所定の電圧が与えられている。

#### 【0230】

以上のようにして、画素電極(陽極) 4 2 0 3 、E L 層 4 2 0 4 及び陰極 4 2 0 5 からなるE L 素子 4 3 0 3 が形成される。そして E L 素子 4 3 0 3 を覆うように、絶縁膜 4 3 0 2 上に保護膜 4 2 0 9 が形成されている。保護膜 4 2 0 9 は、E L 素子 4 3 0 3 に酸素や水分等が入り込むのを防ぐのに効果的である。

#### 【0231】

4 0 0 5 a は電源供給線に接続された引き回し配線であり、E L 駆動用 T F T 4 2 0 2 のソース領域に電気的に接続されている。引き回し配線 4 0 0 5 a はシール材 4 0 0 9 と基板 4 0 0 1 との間を通り、異方導電性フィルム 4 3 0 0 を介して F P C 4 0 0 6 が有するF P C 用配線 4 3 0 1 に電気的に接続される。

#### 【0232】

シーリング材 4 0 0 8 としては、ガラス材、金属材(代表的にはステンレス材)、セラミック材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、F R P (F i b e r g l a s s - R e i n f o r c e d P l a s t i c s ) 板、P V F (ポリビニルフルオライド) フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルを P V F フィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

#### 【0233】

但し、E L 素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### 【0234】

また、充填材 4 2 1 0 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、P V C (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、P V B (ポリビニルブチラル) または E V A (エチレンビニルアセテート) を用いることができる。本実施例では充填材として窒素を用いた。

#### 【0235】

また充填材 4 2 1 0 を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておるために、シーリング材 4 0 0 8 の基板 4 0 0 1 側の面に凹部 4 0 0 7 を設けて吸湿性物質または酸素を吸着しうる物質 4 2 0 7 を配置する。そして、吸湿性物質または酸素を吸着しうる物質 4 2 0 7 が飛び散らないように、凹部カバー材 4 2 0 8 によって吸湿性物質または酸素を吸着しうる物質 4 2 0 7 は凹部 4 0 0 7 に保持されている。なお凹部カバー材 4 2 0 8 は目の細かいメッシュ状になっており、空気や水分は通し、

10

20

30

40

50

吸湿性物質または酸素を吸着しうる物質 4207 は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質 4207 を設けることで、EL 素子 4303 の劣化を抑制できる。

【0236】

図 13 (C) に示すように、画素電極 4203 が形成されると同時に、引き回し配線 4005a 上に接するように導電性膜 4203a が形成される。

【0237】

また、異方導電性フィルム 4300 は導電性フィラーレ 4300a を有している。基板 4001 と FPC 4006 とを熱圧着することで、基板 4001 上の導電性膜 4203a と FPC 4006 上の FPC 用配線 4301 とが、導電性フィラーレ 4300a によって電気的に接続される。

10

【0238】

本実施例は、実施例 1 ~ 実施例 4 と自由に組み合わせて実施することが可能である。

【0239】

(実施例 6)

本発明において、三重項励起子からの熒光を発光に利用できる EL 材料を用いることで、外部発光量子効率を飛躍的に向上させることができる。これにより、EL 素子の低消費電力化、長寿命化、および軽量化が可能になる。

【0240】

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。 (T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular Systems, ed. K.Honda, (Elsevier Sci.Pub., Tokyo, 1991) p.437.)

20

【0241】

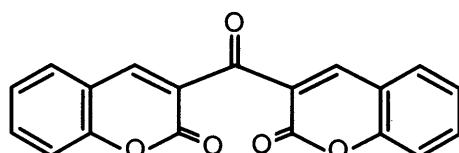

上記の論文により報告された EL 材料 (クマリン色素) の分子式を以下に示す。

【0242】

【化 1】

30

【0243】

(M.A.Baldo, D.F.O'Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.Forrest, Nature 395 (1998) p.151.)

【0244】

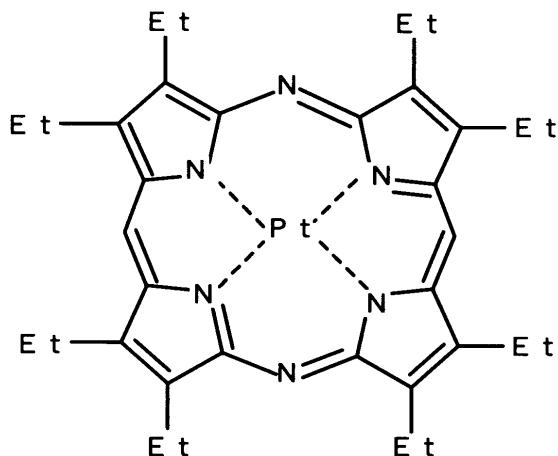

上記の論文により報告された EL 材料 (Pt 錯体) の分子式を以下に示す。

【0245】

【化 2】

40

10

## 【0246】

(M.A.Baldo, S.Lamansky, P.E.Burrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Lett., 75 (1999) p.4.) (T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.tsuchi, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.)

## 【0247】

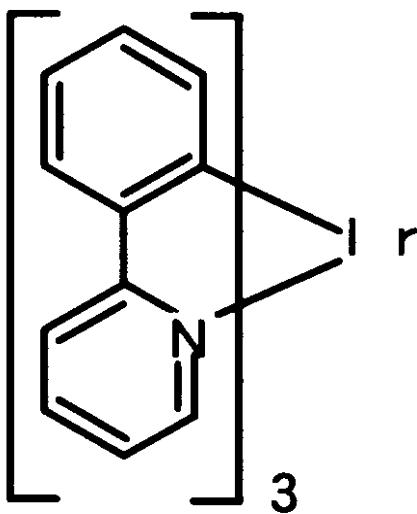

上記の論文により報告された E L 材料 (Ir錯体) の分子式を以下に示す。

20

## 【0248】

## 【化3】

30

## 【0249】

以上のように三重項励起子からの発光を利用できれば原理的には一重項励起子からの蛍光発光を用いる場合より 3 ~ 4 倍の高い外部発光量子効率の実現が可能となる。

## 【0250】

なお本実施例は、実施例 1 ~ 実施例 5 と自由に組み合わせて実施することが可能である。

## 【0251】

## (実施例 7)

本実施例では、本発明を用いて形成された表示装置を表示媒体として組み込んだ電子機器について説明する。

40

50

**【0252】**

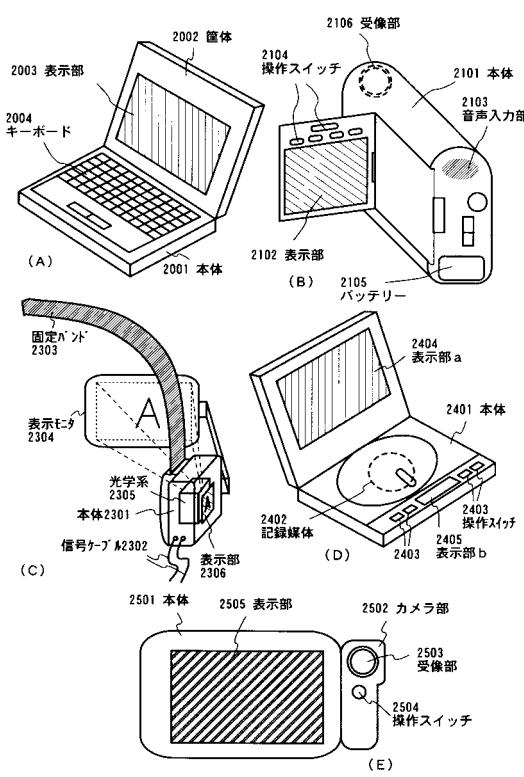

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ、ゲーム機、カーナビゲーション、パソコンコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図18に示す。

**【0253】**

図18（A）はパソコンコンピュータであり、本体2001、筐体2002、表示部2003、キーボード2004等を含む。本発明の表示装置はパソコンコンピュータの表示部2003に用いることができる。

**【0254】**

図18（B）はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明の表示装置はビデオカメラの表示部2102に用いることができる。

**【0255】**

図18（C）は頭部取り付け型の表示装置（ヘッドマウントディスプレイ）の一部（右片側）であり、本体2301、信号ケーブル2302、頭部固定バンド2303、表示モニタ2304、光学系2305、表示部2306等を含む。本発明の表示装置は頭部取り付け型の表示装置の表示部2306に用いることができる。

**【0256】**

図18（D）は記録媒体を備えた画像再生装置（具体的にはDVD再生装置）であり、本体2401、記録媒体（CD、LDまたはDVD等）2402、操作スイッチ2403、表示部（a）2404、表示部（b）2405等を含む。表示部（a）は主として画像情報を表示し、表示部（b）は主として文字情報を表示するが、本発明の表示装置は記録媒体を備えた画像再生装置の表示部（a）2404、（b）2405に用いることができる。なお、記録媒体を備えた画像再生装置としては、CD再生装置、ゲーム機器などに本発明を用いることができる。

**【0257】**

図18（E）は携帯型（モバイル）コンピュータであり、本体2501、カメラ部2502、受像部2503、操作スイッチ2504、表示部2505等を含む。本発明の表示装置は携帯型（モバイル）コンピュータの表示部2505に用いることができる。

**【0258】**

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することができる。また、本実施例の電子機器は実施例1～6のどのような組み合わせからなる構成を用いても実現することができる。

**【0259】****【発明の効果】**

EL素子に入力される電流が、映像信号（ビデオ信号）の信号電位と線型に対応しないため、階調を表現するのが困難になっていた。

**【0260】**

本発明では、上記構成によって映像信号の信号電位に線型に対応する輝度でEL素子を発光させることができる。これによって、階調表示を容易に実現する表示装置が提供される。

**【図面の簡単な説明】**

**【図1】** 本発明のEL表示装置の構成を示す回路図。

**【図2】** 本発明のEL表示装置の入力電圧とEL素子の輝度の関係を示す図。

**【図3】** 本発明のEL表示装置のタイミングチャートを示す図。

**【図4】** 従来のEL表示装置の構成を示す図。

**【図5】** 従来のEL表示装置の画素の構成を示す図。

**【図6】** 本発明のEL表示装置の構成を示す回路図。

**【図7】** 本発明のEL表示装置のタイミングチャートを示す図。

10

20

30

40

50

- 【図 8】 アナログ階調方式の E L 駆動用 TFT の動作領域を示す図。

- 【図 9】 本発明の E L 表示装置の構成を示す回路図。

- 【図 10】 本発明の E L 表示装置のタイミングチャートを示す図。

- 【図 11】 本発明の E L 表示装置の構成を示す図。

- 【図 12】 本発明の E L 表示装置のタイミングチャートを示す図。

- 【図 13】 本発明の E L 表示装置の上面図及び断面図。

- 【図 14】 本発明の E L 表示装置の作製工程を示す図。

- 【図 15】 本発明の E L 表示装置の作製工程を示す図。

- 【図 16】 本発明の E L 表示装置の作製工程を示す図。

- 【図 17】 本発明の E L 表示装置の作製工程を示す図。

- 【図 18】 本発明の E L 表示装置を用いた電子機器の図。

- 【図 19】 本発明の E L 表示装置の構成を示す回路図。

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【 図 9 】

【 図 1 0 】

【図11】

【図12】

【図13】

【図14】

【 図 1 5 】

【 図 1 6 】

【 図 1 7 】

【 図 1 8 】

【図19】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 D

H 05 B 33/14 A