(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5049467号

(P5049467)

(45) 発行日 平成24年10月17日(2012.10.17)

(24) 登録日 平成24年7月27日(2012.7.27)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO1L 21/336 (2006.01) | HO1L 29/78 627G |

| HO1L 29/786 (2006.01) | GO2F 1/1368     |

| GO2F 1/1368 (2006.01) | HO1L 21/20      |

| HO1L 21/20 (2006.01)  | HO1L 21/268 F   |

| HO1L 21/268 (2006.01) | HO1L 29/78 618C |

請求項の数 18 外国語出願 (全 13 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2005-87085 (P2005-87085)    |

| (22) 出願日     | 平成17年3月24日 (2005.3.24)        |

| (65) 公開番号    | 特開2005-286330 (P2005-286330A) |

| (43) 公開日     | 平成17年10月13日 (2005.10.13)      |

| 審査請求日        | 平成20年3月11日 (2008.3.11)        |

| (31) 優先権主張番号 | 093108422                     |

| (32) 優先日     | 平成16年3月26日 (2004.3.26)        |

| (33) 優先権主張国  | 台湾(TW)                        |

|           |                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 510134581<br>奇美電子股▲ふん▼有限公司<br>Chime i Innolux Corporation<br>台灣苗栗縣竹南鎮科學路160號 新竹<br>科學工業園區<br>No. 160 Kesyue Rd., Chu-Nan Site, Hsinchu<br>Science Park, Chu-Nan 350, Miao-Li County, Taiwan,<br>(74) 代理人 110000110<br>特許業務法人快友國際特許事務所 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】薄膜トランジスタと薄膜トランジスタ基板とそれらの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に設けられている薄膜トランジスタであって、

前記基板上に形成され、結晶端領域と少なくとも1つの核生成領域が規定され、前記核生成領域では第1の横幅を有するとともに前記結晶端領域では第2の横幅を有し、前記第1の横幅は前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記基板上に形成され、前記チャネル層を取り囲んでおり、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層との間に間隙を形成する少なくとも1つの温度勾配誘導体と、

前記基板上に形成されているとともに前記チャネル層を覆っているゲート絶縁層と、

前記ゲート絶縁層上に形成されているゲート電極と、

前記ゲート絶縁層上に形成されているとともに前記ゲート電極を覆っている第1の中間絶縁層と、

前記第1の中間絶縁層上に形成されているとともに前記ゲート絶縁層と前記第1の中間絶縁層を貫通して前記チャネル層に電気的に接続しているソース電極およびドレイン電極と、

を備える薄膜トランジスタ。

## 【請求項 2】

前記チャネル層は、多結晶シリコンおよび単結晶シリコンの少なくとも一方から形成さ

10

20

れていることを特徴とする請求項 1 の薄膜トランジスタ。

**【請求項 3】**

前記チャネル層は、水滴の形状、三角形状、扇形状、台形形状、王冠形状のいずれかであることを特徴とする請求項 1 又は 2 の薄膜トランジスタ。

**【請求項 4】**

前記温度勾配誘導体と前記チャネル層との間の間隙では、前記広幅部分における前記間隙の距離は、前記狭幅部分における前記間隙の距離よりも、短くなっていることを特徴とする請求項 1 から 3 のいずれか一項の薄膜トランジスタ。

**【請求項 5】**

前記温度勾配誘導体の前記狭幅部分に、鋸歯状の縁部が形成されていることを特徴とする請求項 1 から 4 のいずれか一項の薄膜トランジスタ。 10

**【請求項 6】**

前記第 1 の中間絶縁層上に形成されており、前記ゲート絶縁層および前記第 1 の中間絶縁層を貫通して前記チャネル層と電気的に接続しているソース電極およびドレイン電極と、

前記第 1 の中間絶縁層上に配設されており、前記ソース電極と前記ドレイン電極を覆つてあり、コンタクトホールが形成されている第 2 の中間絶縁層と、

前記第 2 の中間絶縁層上に形成されており、前記コンタクトホールに蒸着されている画素電極と、

が付加されている請求項 1 から 5 のいずれか一項の薄膜トランジスタ。 20

**【請求項 7】**

薄膜トランジスタを製造する方法であって、

基板上に初期チャネル層を形成する工程と、

前記初期チャネル層にパターン形成を行うことによって、有形チャネル層と少なくとも 1 つの温度勾配誘導体を形成する工程と、

前記有形チャネル層と前記温度勾配誘導体をアニールする工程と、

前記基板上に、前記有形チャネル層と前記温度勾配誘導体を覆うゲート絶縁層を形成する工程と、

前記ゲート絶縁層上にゲート電極を形成する工程と、

前記有形チャネル層に、P 型イオン ( P<sup>-</sup> ) および N 型イオン ( N<sup>+</sup> ) の少なくとも一方をイオン注入することによって、ソース領域と中間領域とドレイン領域を形成する工程と、 30

前記ゲート絶縁層上に、前記ゲート電極を覆う第 1 の中間絶縁層を形成する工程と、

前記ゲート絶縁層と前記第 1 の中間絶縁層を貫通する 2 つのコンタクトホールを形成することによって、前記ソース領域と前記ドレイン領域を露出させる工程と、

前記第 1 の中間絶縁層上に、前記 2 つのコンタクトホールの少なくとも一部を充填するソース電極とドレイン電極を形成する工程とを備え、

前記有形チャネル層は、結晶端領域と核生成領域が規定され、前記核生成領域で第 1 の横幅を有するとともに前記結晶端領域で第 2 の横幅を有し、前記第 1 の横幅が前記第 2 の横幅よりも狭いものであり、 40

前記温度勾配誘導体は、前記有形チャネル層の周囲の少なくとも一部に隣接し、前記有形チャネル層の前記結晶端領域に対応して位置する広幅部分および前記核生成領域に対応して位置する狭幅部分を備え、前記有形チャネル層との間に間隙を形成するものであり、

前記アニールする工程では、前記有形チャネル層における結晶粒子の成長が、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする製造方法。

**【請求項 8】**

前記有形チャネル層の前記狭幅部分は尖部を備えており、

前記有形チャネル層における結晶粒子の成長は、前記核生成領域で開始し、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする請求項 7 の製造方法。

**【請求項 9】**

前記第1の中間絶縁層上に、前記ソース電極と前記ドレイン電極を覆う第2の中間絶縁層を形成する工程と、

前記第2の中間絶縁層に、コンタクトホールを形成する工程と、

前記第2の中間絶縁層上および前記コンタクトホール内に画素電極を形成する工程と、

が付加されている請求項7の製造方法。

【請求項10】

薄膜トランジスタであって、

基板と、

前記基板上に形成され、核生成領域と結晶端領域が規定され、前記核生成領域では第1の横幅を有するとともに前記結晶端領域では第2の横幅を有し、前記第1の横幅が前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記基板上に形成され、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層との間に隙間を形成して隣接している温度勾配誘導体と、

を備える薄膜トランジスタ。

【請求項11】

前記チャネル層と前記温度勾配誘導体との間の隙間は、前記結晶端領域に隣接する位置において第1の距離を有しているとともに前記核生成領域に隣接する位置において第2の距離を有しており、

前記第1の距離は、前記第2の距離よりも短いことを特徴とする請求項10の薄膜トランジスタ。

【請求項12】

前記核生成領域は尖部を備えており、

前記狭幅部分には、前記尖部に対応して位置している開口部が形成されていることを特徴とする請求項10の薄膜トランジスタ。

【請求項13】

液晶表示装置を製造する方法であって、

基板を準備する工程と、

前記基板上に初期チャネル層を形成する工程と、

前記初期チャネル層の少なくとも一部を、有形チャネル層と、有形チャネル層に隣接する温度勾配誘導体に成形する工程と、

前記有形チャネル層と前記温度勾配誘導体をアニールする工程とを備え、

前記有形チャネル層は、第1の横幅を有する核生成領域と第2の横幅を有する結晶端領域が規定され、前記第1の横幅は前記第2の横幅よりも狭いものであり、

前記温度勾配誘導体は、前記有形チャネル層の前記結晶端領域に対応して位置する広幅部分および前記核生成領域に対応して位置する狭幅部分を備え、前記有形チャネル層との間に隙間を形成するものであり、

前記アニールする工程では、前記有形チャネル層における結晶粒子の成長が、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする製造方法。

【請求項14】

前記温度勾配誘導体は、前記初期チャネル層の少なくとも一部を除去することによって、前記初期チャネル層から形成することを特徴とする請求項13の製造方法。

【請求項15】

前記温度勾配誘導体と前記有形チャネル層との間の隙間は、前記核生成領域に隣接する位置において第1の距離であるとともに前記結晶端領域に隣接する位置において第2の距離であり、前記第1の距離は前記第2の距離よりも長いことを特徴とする請求項13又は14の製造方法。

【請求項16】

液晶表示装置であって、

10

20

30

40

50

第1の基板と、

第2の基板と、

第1の基板と第2の基板との間に挟持されている液晶層と、

前記第2の基板上に形成され、核生成領域および結晶端領域を備え、前記核生成領域で第1の横幅を有するとともに前記結晶端領域で第2の横幅を有し、前記第1の横幅は前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記第2の基板上に形成され、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層の周囲に間隙を形成して隣接している温度勾配誘導体と、

を備える液晶表示装置。

#### 【請求項17】

前記チャネル層と前記温度勾配誘導体との間の間隙は、前記結晶端領域に隣接する位置において第1の距離を有しているとともに前記核生成領域に隣接する位置において第2の距離を有しており、前記第1の距離は前記第2の距離よりも短いことを特徴とする請求項16の液晶表示装置。

#### 【請求項18】

前記核生成領域は尖部を備えており、

前記狭幅部分には、前記尖部に対応して位置する開口部が形成されていることを特徴とする請求項16又は17の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、薄膜トランジスタに関する。特に、有形のチャネル層と温度勾配誘導体とを備える薄膜トランジスタに関する。

##### 【背景技術】

##### 【0002】

低電力消費型の液晶表示装置では、高いコントラストや高い応答速度等という高性能な特性が得られることから、その駆動素子に薄膜トランジスタ（以下、TFTという）が利用されている。低電力消費型の液晶表示装置は、主にパーソナルコンピュータ（PC）やポータブルテレビジョン（TV）等に使用されている。TFTの市場規模は著しく拡大している。

多くのTFTでは、チャネル層用の半導体に、非晶質シリコン（以下、a-Siという）や多結晶シリコン（以下、p-Siという）を利用している。a-Siは、特定の結晶方向を有しない複数のシリコン結晶粒子によって構成される高純度のシリコン物質である。一方、p-Siは、種々の結晶方向を有する複数の単結晶シリコン小粒子によって構成される高純度のシリコン物質である。即ち、p-Siは、単結晶シリコンとa-Siの中間の高純度なシリコンといえる。電子移動度については、a-Siよりもp-Siの方が大きくなる。

##### 【0003】

a-Si層やp-Si層の蒸着は、核を生成する工程と、結晶粒子を成長させる工程と、結晶粒子群を凝集させる工程と、蒸着層を成長させる工程を備えている。具体的には、シリコン層の蒸着方法では、下記のステップが含まれている。即ち、原子が引付けられるステップと、引付けられた原子が層表面に拡散するステップと、引付けられた原子が適当な段階において凝集する工程と、それによって薄層が徐々に形成される工程と、その薄層が成長する工程が含まれている。結晶粒子の成長や結晶粒子の凝集や蒸着層の成長は、表面自由エネルギーによって左右される。表面自由エネルギーは、結晶粒子の成長に伴って徐々に減少する。引付けられた原子のシリコン層表面における拡散は、その表面温度に依存し、表面温度が高いときほど表面での拡散はより大きくなる。そのことから、表面温度が低いときよりも表面温度が高いときほど、結晶粒子をより大きく成長させるために、引

10

20

30

40

50

付けられた原子を理想的な位置へ凝集させることが容易となる。従って、結晶粒子径の大きさと表面温度との間には正の相関が存在する。そして、結晶粒子径が大きいほど、電子移動度は増加する。

#### 【0004】

「半導体デバイスを製造する方法」という名称の特許文献1には、半導体装置を製造する方法が開示されており、その内容は本明細書に引用される。特許文献1の方法には、下記の工程が含まれている。即ち、シリコンの結晶化を促進するための触媒金属元素を使用し、非晶質シリコン層又は部分的に結晶質の非晶質シリコン層を結晶化することによって、結晶質の第1のシリコン層を形成する工程と、V族元素を含有する第2のシリコン層を、第1のシリコン層の全面に直接的に形成する工程と、第1のシリコン層と第2のシリコン層に熱処理を施すことによって、触媒金属元素の少なくとも一部を第1のシリコン層から第2のシリコン層へゲッターリングする工程と、触媒金属元素がゲッターリングされた第2のシリコン層を除去する工程とが含まれる。しかしながら、この半導体装置では、チャネル層用の半導体にp-Siを利用しているので、電子移動度が低くなってしまう。10

【特許文献1】米国特許第6,436,745号明細書

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

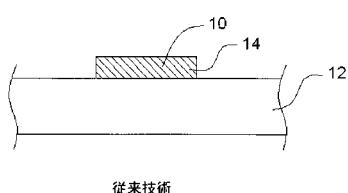

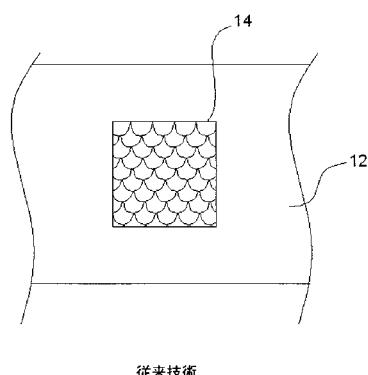

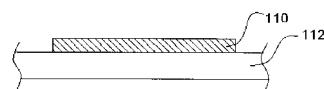

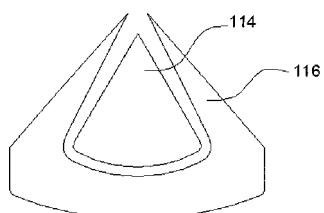

特許文献1の技術では、チャネル層用の半導体にp-Siを利用している。図1aと図1bに示すように、p-Siによる従来のチャネル層14は、プラズマ化学気相成長法によって、基板12上にp-Si層10を蒸着形成する工程と、フォトリソグラフィとエッチングによってp-Si層10にパターン形成を行う工程と、レーザアニール法によって結晶化する工程によって形成される。一般に、p-Si層は長方形の形状をしており、表面温度は全体的に均一に減少していく。そのことから、レーザアニール後において、熱エネルギー保持することが容易でない。その結果、p-Si結晶粒子が100マイクロメートルを超えて成長することは困難である。20

図1aと図1bに示すような従来のチャネル層14では、核生成がチャネル層14の多数箇所において生じることがある。核生成が多数箇所において生じると、多くの結晶粒子が形成されることとなり、結晶粒子のサイズは小さくなってしまう。多くの結晶粒子が形成されることは、多くの粒子境界が存在することとなり、電子移動度を減少させてしまうことになる。30

上記のことから、結晶粒子径が大きく、電子移動度が高い薄膜トランジスタが必要とされている。

#### 【課題を解決するための手段】

#### 【0006】

ここで開示する技術は、薄膜トランジスタと、薄膜トランジスタの製造方法に具現化することができる。簡単に述べると、とりわけ物理的に具現化する場合には、以下に記載する薄膜トランジスタに具現化することができる。この薄膜トランジスタは、基板上に形成されているチャネル層を備えている。チャネル層は、第1の横幅を有する核生成領域と、および第2の横幅を有する結晶端領域とを備えている。第1の横幅は、第2の横幅よりも狭い。この薄膜トランジスタは、基板上に形成されている温度勾配誘導体を備えている。温度勾配誘導体は、チャネル層の周囲に隣接しており、温度勾配誘導体とチャネル層の間には、間隙が形成されている。40

#### 【0007】

ここで開示する技術を具現化することによって、薄膜トランジスタの製造方法を提供することができる。その1つの製造方法は、基板を準備する工程と、初期チャネル層を基板上に形成する工程と、初期チャネル層の少なくとも一部によって有形チャネル層を形成する工程と、少なくとも有形チャネル層をアニールする工程と、有形チャネル層に隣接する温度勾配誘導体を形成する工程と、温度勾配誘導体によって有形チャネル層内に温度勾配を誘導する工程を備えている。有形チャネル層は、第1の横幅を有する核生成領域と、第50

2の横幅を有する結晶端領域とを備える形状に形成する。

この製造方法によると、温度勾配誘導体によって、有形チャネル層の核生成領域の方が、結晶端領域よりも、熱をより速く放散する。

#### 【発明を実施するための最良の形態】

##### 【0008】

ここで開示する技術の目的、方法、特徴、利点は、下記する詳細な説明と図面を参照することによって、当業者にとってより明らかになるものである。当業者にとって理解される他の目的、方法、特徴、利点の全ては、下記する説明に含まれているものであり、開示する技術範囲に含まれているものであって、添付した特許請求の範囲によって保護されるべきものである。

10

##### 【0009】

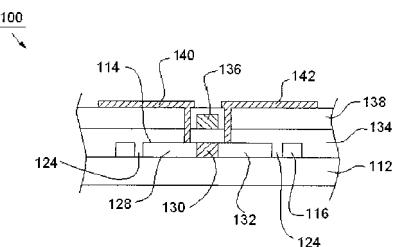

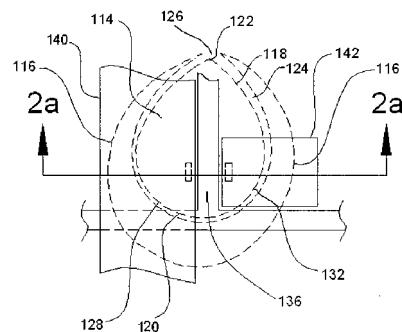

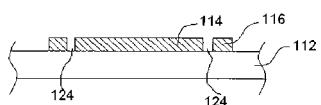

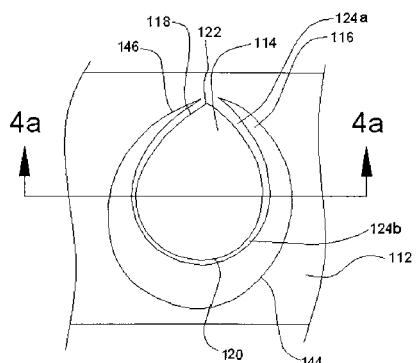

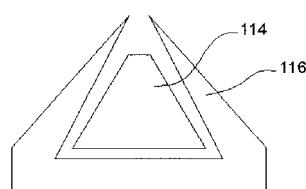

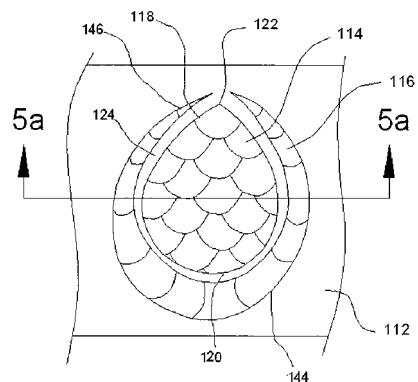

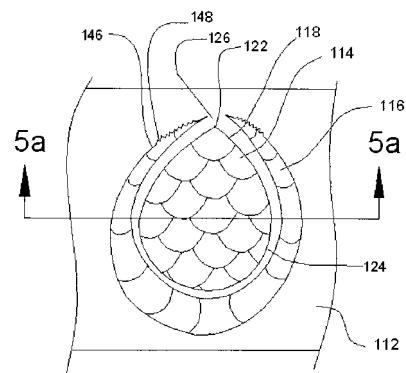

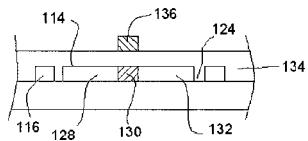

図2aと図2bに、一実施形態である薄膜トランジスタ100を示す。薄膜トランジスタ(TFT)100は、液晶表示装置に用いる薄膜トランジスタに適用することができる。TFT100は、チャネル層114と、温度勾配誘導体116を備えている。チャネル層114は、特定の形状を有している。温度勾配誘導体116は、チャネル層114の特定の形状に対して、ほぼ相補的な形状を有している。概していえば、温度勾配誘導体116の相補的な形状とは、温度勾配誘導体116が、チャネル層114の周囲にほぼ隣接する形状といえる。実施形態の一例として、チャネル層114と温度勾配誘導体116は、基板112上に形成することができる。また実施形態の一例として、温度勾配誘導体116は、チャネル層114の周囲にほぼ隣接する多結晶シリコン層によって形成することができる。

20

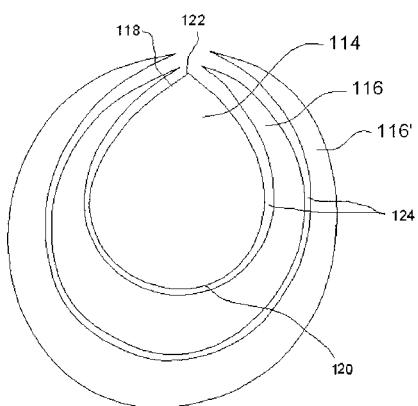

図2bに示すように、チャネル層114は水滴のような形状をしており、核生成領域118と、核生成領域118の略反対側に位置している結晶端領域120を備えている。結晶端領域120は、核生成領域118に比べて広い。核生成領域118は、核生成点122を備えている。以下で詳細に説明するように、チャネル層では、アニール処理が施されることによって、核生成領域118の核生成点122又はその近傍において再結晶化が生じる。その結晶粒子は、結晶端領域120に向けて成長する。チャネル層114は、例えば水滴形状や、三角形状や、扇形状や、台形状等に形成することができる。

##### 【0010】

チャネル層114と温度勾配誘導体116との間には、不定距離間隙124が伸びている。不定距離間隙124は、核生成点122にほぼ隣接する位置において、その間隙距離が最大となっている。典型的には、不定距離間隙124、即ち、チャネル層114と温度勾配誘導体116との間の距離は、核生成点122から離されている位置ほど、短くなっている。実施形態の一例として、温度勾配誘導体116に、開口部126を形成することができる。その開口部126は、核生成点122が開口部126に向けて位置するよう、核生成点122の位置に対応させて形成することができる。

30

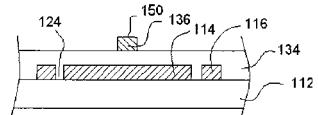

チャネル層114は、ソース領域128と、中間領域130と、ドレイン領域132を備えている。さらに、TFT100は、ゲート絶縁層134と、ゲート電極136と、第1の中間絶縁層138と、ソース電極140と、ドレイン電極142を備えている。ゲート絶縁層134は、基板112上に形成されており、チャネル層114と温度勾配誘導体116を覆っている。ゲート電極136は、ゲート絶縁層134上に形成されている。第1の中間絶縁層138は、ゲート絶縁層134上に形成されており、ゲート電極136を覆っている。ソース電極140とドレイン電極142は、第1の中間絶縁層138上に形成されているとともに、ゲート絶縁層134を貫通してソース領域128とドレイン領域132へそれぞれ電気的に接続している。本実施形態においては、温度勾配誘導体116が単一であることに限定されない。複数の温度勾配誘導体を形成することが可能であることは、いわゆる当業者にとって明らかである。

40

##### 【0011】

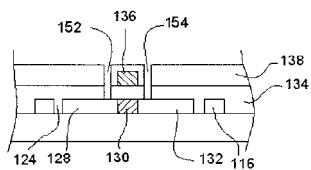

図3から図9に、薄膜トランジスタ100を製造する代表的な方法を示す。

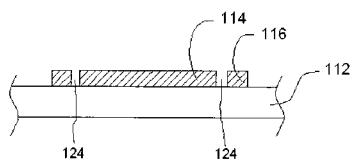

図3に示すように、プラズマ化学気相成長工程によって、高い反応温度、例えば、略5

50

75 ~ 650 により、初期チャネル層110を基板112上に蒸着形成する。プラズマ化学気相成長工程では、プラズマによって、気体分子が原子やイオンや原子群に分解される。

図4aに示すように、フォトリソグラフィとエッチング工程によって、初期チャネル層110にパターン形成を行い、チャネル層114と温度勾配誘導体116とチャネル層114および温度勾配誘導体116との間に位置する不定距離間隙124を形成する。チャネル層114では、核生成領域118と結晶端領域120が規定されている。結晶端領域120は、核生成領域118の核生成点122に対して略反対側に位置している。

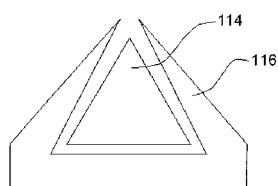

チャネル層114の形状は、水滴形状(図4bに示される)や、三角形状(図4cに示される)や、扇形状(図4dに示される)や、台形形状(図4eに示される)等とすることが可能である。説明を明瞭にするために、ここでは水滴形状に形成する実施形態について詳細に説明する。10

#### 【0012】

図4bに示すように、温度勾配誘導体116は、チャネル層114の周囲にほぼ隣接している。温度勾配誘導体116は、広幅部分144と狭幅部分146を有している。狭幅部分146には、開口部126が形成されている。狭幅部分146は核生成領域118に隣接しており、広幅部分144は結晶端領域120に隣接している。

典型的には、初期チャネル層110の一部を除去し、基板層112に向けて下方へと伸びる間隙124を形成することによって、チャネル層114が温度勾配誘導体116から独立し、チャネル層114が温度勾配誘導体116に接続することができないようになっている。不定距離間隙124では、温度勾配誘導体116の広幅部分144とチャネル層114の結晶端領域120との間ににおいて第1間隙距離124aを有しており、温度勾配誘導体116の狭幅部分146とチャネル層114の核生成領域118との間ににおいて第2間隙距離124bを有している。第1間隙距離124aは、第2間隙距離124bよりも短く設定されている。20

#### 【0013】

当業者にとって明らかなように、第1間隙距離124aと第2間隙距離124bとが相違することや、温度勾配誘導体116の形状等に起因して、結晶端領域120における放熱速度は、核生成領域118における放熱速度よりも遅くなる。単位体積当たりの表面積が大きい領域の方が、単位体積当たりの表面積が小さい領域よりも放熱速度が速いことから、温度勾配誘導体116の広幅部分144によって吸収された熱は、温度勾配誘導体116の狭幅部分によって吸収された熱よりも、放熱される速度が遅くなる。従って、温度勾配誘導体の広幅部分144では、その形状に起因して、温度勾配誘導体の狭幅部分146よりも放熱量が少なくなる。その結果、結晶端領域120が核生成領域118よりも広いことや、第1間隙距離124aが第2間隙距離124bよりも短いことから、核生成領域118では結晶端領域120よりも放熱速度が速くなる。図1bに示すチャネル層14に対して、チャネル層114では、核生成領域118の核生成点122から結晶端領域120に亘って、大きな温度勾配を持つこととなる。30

#### 【0014】

一般的に、チャネル層114における温度勾配によって、結晶粒子の成長は、核生成領域118の核生成点122において開始され、次いでチャネル層114の結晶端領域120に向けて進んでいく。即ち、結晶粒子の成長は、チャネル層114の一端側に位置する核生成点122において開始され、他端側に位置する結晶端領域120に向けて進む。結晶粒子の成長は、別の核生成点から成長した他の結晶粒子に衝突して妨害されない。それにより、結晶端領域120における結晶粒子は、従来のチャネル14(図1aと図1bを参照)における結晶粒子よりも大きく成長することができる。結晶端領域120において結晶粒子径が大きく成長することから、結晶端領域120における粒子の境界を少なくすることができ、チャネル層114における電子移動度を、従来のチャネル層14よりも大きくすることができる。40

#### 【0015】

50

図4 fに示すように、別の実施形態では、チャネル層114の周囲に温度勾配誘導体116がほぼ隣接しているとともに、その誘導体の周囲に第2の温度勾配誘導体116がほぼ隣接している構成とすることもできる。第2の温度勾配誘導体116は、温度勾配誘導体116の結晶端領域120に対する熱容量を効果的に増大する。それにより、チャネル層114において、核生成領域118の核生成点122と結晶端領域120との間ににおける温度勾配を増加させることができる。チャネル層114に、多結晶粒子、あるいは単結晶粒子さえも形成することができる。

#### 【0016】

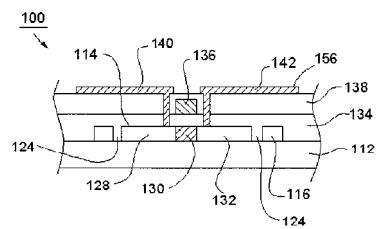

図5 aと図5 bに示すように、レーザアニール工程によって、チャネル層114と温度勾配誘導体116にアニール処理を実施する。レーザアニール工程によるエネルギーは、原子の振動を増大し、原子や分子の拡散を増大し、シリコン層において再配置される欠陥を増加させる。それにより、チャネル層114では、欠陥数が減少される処理が行われることとなり、チャネル層を単結晶化することも可能となる。具体的には、いわゆる当業者にとって周知のように、熱による放散は表面積と体積の関数である。狭幅部分146の体積に対する表面積の比は、広幅部分144の体積に対する表面積の比よりも大きいことから、狭幅部分146における放熱速度は、広幅部分144における放熱速度よりも大きい。その結果、温度勾配誘導体116がアニールされた後に、狭幅部分146の方が広幅部分144よりも速く冷却していくので、温度勾配誘導体116において温度勾配が形成される。

温度勾配誘導体116における温度勾配や、チャネル層114の形状や、不定距離間隙124等によって、チャネル層114内に温度勾配が誘導される。具体的には、チャネル層114の結晶領域120における温度は、核生成領域118の温度よりも高くなる。それにより、チャネル層114における結晶成長は、核生成領域118の核生成点122から結晶端領域120へ向けて進むこととなる。

#### 【0017】

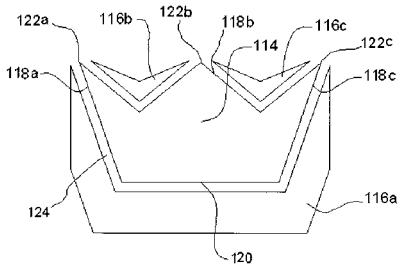

図5 cに示すように、実施形態の一例として、温度勾配誘導体116の狭幅部分146に、鋸歯状の縁部148を形成することができる。鋸歯状縁部148は、狭幅部分146の体積に対する表面積の比を増加することから、狭幅部分146における放熱速度を増大させることができ、温度勾配誘導体116における温度勾配を増大させることができる。

図5 dに示すように、実施形態の一例として、初期チャネル層110にパターン形成を行うことによって、略王冠状のチャネル層114と、複数の温度勾配誘導体116a、116b、116cを形成することができる。王冠状のチャネル層114は、複数の核生成領域118a、118b、118cを備えており、それぞれに核生成点122a、122b、122cが規定される。温度勾配誘導体116bは、王冠状チャネル層114の形状に対して相補的な形状をしており、核生成点122aと核生成点122bとの間に位置している。温度勾配誘導体116cは、王冠状チャネル層114の形状に対して相補的な形状をしており、核生成点122bと核生成点122cとの間に位置している。特許文献1の技術と比較すると、本開示技術による薄膜トランジスタの製造方法では、少ないレーザエネルギーを利用して、粒子径の大きい多結晶シリコン層を形成することができる。

#### 【0018】

図6に示すように、基板112やチャネル層114や温度勾配誘導体116上に、ゲート絶縁層134を形成する。また、ゲート絶縁層134上に第1の金属薄層150を形成し、フォトリソグラフィおよび/又はエッチング工程によってパターン形成を行い、ゲート電極136を形成する。

図7に示すように、イオン注入工程によって、チャネル層114にP型イオン(P<sup>-</sup>)又はN型イオン(N<sup>+</sup>)をイオン注入し、ソース領域128、中間領域130、ドレイン領域132を形成する。

図8に示すように、第1の中間絶縁層138を、ゲート絶縁層134とゲート電極136上に形成する。次いで、フォトリソグラフィとエッチング工程によって、2つのコンタクトホール152、154を、第1の中間絶縁層138とゲート絶縁層134に形成する

10

20

30

40

50

。コンタクトホール 152、154 は、ソース領域 128 とドレイン領域 132 の一部を露出する。

図 9 に示すように、第 1 の中間絶縁層 138 上に、第 2 の金属薄層 156 を、2 つのコンタクトホール 152、154 を充填するように形成する。フォトリソグラフィとエッチング工程によって第 2 の金属薄層 156 にパターン形成を行い、ソース電極 140 とドレイン電極 142 を形成する。

チャネル層 114 は、いくつかの実施形態において、結晶粒子径の大きい多結晶シリコン層や、単結晶シリコン層で形成することができる。それにより、チャネル層 114 は高い電子移動度を有することができる。

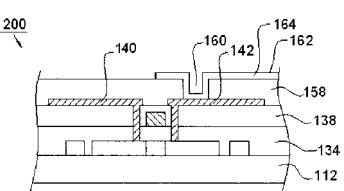

#### 【0019】

10

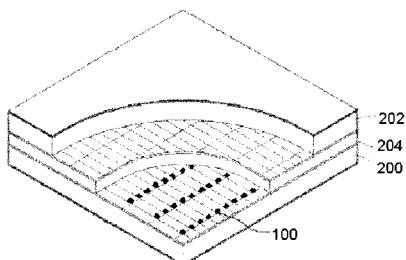

図 10 は、他の実施形態である薄膜トランジスタ基板 200 を示している。図 10 に示すように、薄膜トランジスタ基板 200 では、第 2 の中間絶縁層 158 が、第 1 の中間絶縁層 138 やソース電極 140 やドレイン電極 142 上に形成されている。コンタクトホール 160 は、フォトリソグラフィとエッチング工程によって、第 2 の中間絶縁層 158 に形成されている。コンタクトホール 160 は、第 2 の中間絶縁層 158 を貫通して伸びており、ドレイン電極 142 の一部を露出している。

第 2 の中間絶縁層 158 上とコンタクトホール 160 内に、透明導電性薄膜 162 が形成されている。透明導電性薄膜 162 は、ドレイン電極 142 と電気的に接続している。透明導電性薄膜 162 は、フォトリソグラフィとエッチング工程によって、パターン形成される。透明導電性薄膜 162 を、対応する薄膜トランジスタ 100 に電気的に接続することによって、本開示技術による薄膜トランジスタ基板 200 を形成することができる。

#### 【0020】

20

図 11 に示すように、本開示技術による液晶表示装置 (LCD) は、好ましくは、第 1 の基板 202 と、第 2 の基板 200 との間に挟持されている液晶層 204 を備えている薄膜トランジスタ (TFT) LCD である。本開示技術による第 1 の基板 202 は、カラーフィルタ (CF) 基板である。一方、第 2 の基板 200 は、上述の薄膜トランジスタ (TFT) 基板である。通常、基板間にセルギャップを形成するために、基板間にスペーサが形成されている。薄膜トランジスタ 100 や、上述の薄膜トランジスタ基板を備える液晶表示装置を提供できることは、当業者によって明らかである。

#### 【0021】

30

以上、本開示技術の好ましい実施形態に関して説明したが、本開示技術を限界するものではない。本開示技術の技術思想と特許請求の範囲から逸脱することなく、他の多くの変更、変形した形態を具現化することが可能であることは、当業者にとって明らかである。

#### 【図面の簡単な説明】

#### 【0022】

【図 1 a】従来技術による薄膜トランジスタの多結晶シリコン層の断面概略図である。

【図 1 b】従来技術による薄膜トランジスタの多結晶シリコン層の平面概略図である。

【図 2 a】本開示技術の一実施形態である薄膜トランジスタの断面概略図である。

【図 2 b】本開示技術の一実施形態である薄膜トランジスタの平面概略図である。

【図 3】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図 4 a】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図 4 b】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図 4 c】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図 4 d】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図 4 e】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図

40

50

である。

【図4 f】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図5 a】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図5 b】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図5 c】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。

【図5 d】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す平面概略図である。 10

【図6】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図7】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図8】本開示技術の一実施形態である薄膜トランジスタの製造方法を示す断面概略図である。

【図9】本開示技術の一実施形態である薄膜トランジスタ基板の断面概略図である。

【図10】本開示技術の一実施形態である薄膜トランジスタ基板の断面概略図である。

【図11】本開示技術の一実施形態である液晶表示装置の一部断面概略図である。 20

【図1 a】

【図1 b】

【図2 a】

【図2 b】

【図3】

【図 4 a】

【図 4 b】

【図 4 c】

【図 4 d】

【図 4 e】

【図 4 f】

【図 5 a】

【図 5 b】

【図 5 c】

【図 5 d】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(72)発明者 チン - ルン , テイン

台湾 74144 タイナン カウンティー タイナン サイエンス - ベースト インダストリア

ル パーク チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポ

レーション内

(72)発明者 チェン - チ , ワン

台湾 74144 タイナン カウンティー タイナン サイエンス - ベースト インダストリア

ル パーク チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポ

レーション内

審査官 西出 隆二

(56)参考文献 特開昭63-304615(JP,A)

特開昭60-066416(JP,A)

特開2004-063478(JP,A)

特開2003-008024(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

G02F 1/1368

H01L 21/20

H01L 21/268

H01L 29/786