(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4793602号

(P4793602)

(45) 発行日 平成23年10月12日(2011.10.12)

(24) 登録日 平成23年8月5日(2011.8.5)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO3M 1/14 (2006.01)  | HO3M 1/14 B    |

| HO3M 1/08 (2006.01)  | HO3M 1/08 A    |

| HO4N 5/378 (2011.01) | HO4N 5/335 780 |

請求項の数 14 (全 27 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2008-527759 (P2008-527759) |

| (86) (22) 出願日 | 平成19年7月31日 (2007.7.31)       |

| (86) 国際出願番号   | PCT/JP2007/064986            |

| (87) 国際公開番号   | W02008/016049                |

| (87) 国際公開日    | 平成20年2月7日 (2008.2.7)         |

| 審査請求日         | 平成22年5月28日 (2010.5.28)       |

| (31) 優先権主張番号  | 特願2006-208664 (P2006-208664) |

| (32) 優先日      | 平成18年7月31日 (2006.7.31)       |

| (33) 優先権主張国   | 日本国 (JP)                     |

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 特許権者 | 304023318<br>国立大学法人静岡大学<br>静岡県静岡市駿河区大谷836        |

| (74) 代理人  | 100088155<br>弁理士 長谷川 芳樹                          |

| (74) 代理人  | 100108257<br>弁理士 近藤 伊知良                          |

| (74) 代理人  | 100124800<br>弁理士 謙澤 勇司                           |

| (72) 発明者  | 川人 祥二<br>静岡県浜松市中区城北3丁目5-1 国立<br>大学法人静岡大学電子工学研究所内 |

| 審査官       | 柳下 勝幸                                            |

最終頁に続く

(54) 【発明の名称】 A／D変換器および読み出し回路

## (57) 【特許請求の範囲】

## 【請求項 1】

イメージセンサのためのA／D変換器であって、

前記イメージセンサからの信号を受ける入力と出力とを有しており、ノイズに係る成分を含む第1の信号の複数回の標本化および標本値の積分を第1の期間に行うと共に、前記イメージセンサの画素からの光誘起信号成分およびノイズに係る成分を含む第2の信号の複数回の標本化および標本値の積分を第1の信号に対する積分とは逆極性となるように第2の期間に行うためのゲインステージと、

前記ゲインステージの前記出力からの信号に応じた第1および第2の値を取りうるディジタル信号を提供するA／D変換回路と、

前記第1の値の出現回数に対応する信号を提供する回路と、

前記ディジタル信号に応答して制御信号を生成する論理回路と、

前記第1の期間に前記ゲインステージに所定の電圧信号の提供を行うと共に、前記第2の期間に前記ゲインステージに前記制御信号に応じた電圧信号の提供を行うD／A変換回路と

を備え、

前記ゲインステージは、

前記標本化のための第1のキャパシタと、

前記積分のための第2のキャパシタと、

前記第1のキャパシタに標本化された信号を前記第2のキャパシタへ積分するための演

10

20

算增幅回路と

を含む、ことを特徴とするA / D変換器。

【請求項2】

前記第1のキャパシタは、前記D / A変換回路に接続された一端および前記演算增幅回路の反転入力に接続された他端を有しており、

前記ゲインステージは、

前記演算增幅回路の非反転出力と前記反転入力との間に接続された第1の容量回路と、

前記入力と前記第1のキャパシタの前記一端との間に接続されており前記イメージセンサからの信号を標本化するための第1のスイッチと、

前記反転入力と前記非反転出力との間に接続された第1の帰還スイッチと

を含み、

前記第1の容量回路は、前記第2のキャパシタおよび第2のスイッチを有し、前記第2のキャパシタおよび第2のスイッチは直列に接続されている、ことを特徴とする請求項1に記載されたA / D変換器。

【請求項3】

前記ゲインステージは、前記ゲインステージの前記出力からの信号に応じたディジタル信号に対応して前記D / A変換回路から提供される電圧信号に用いて、前記第1および第2の期間の後の第3の期間に巡回A / D変換を行う、ことを特徴とする請求項1または請求項2に記載されたA / D変換器。

【請求項4】

前記A / D変換回路は、前記巡回A / D変換のために、前記ゲインステージの前記出力からの信号に応じた三値のディジタル信号を前記第3の期間に提供し、

前記ゲインステージは、

前記第1のキャパシタの前記一端と前記非反転出力との間に接続された別の帰還スイッチと、

前記第1のキャパシタの前記他端と前記反転入力との間に接続された転送スイッチとを含む、ことを特徴とする請求項3に記載されたA / D変換器。

【請求項5】

前記A / D変換回路は、前記ゲインステージの前記出力からの信号を第1および第2の参照信号と比較する比較器を含み、

前記比較器は、前記第1の参照信号を前記第2の期間に受け、

前記比較器は、前記第2の参照信号を前記第3の期間に受ける、ことを特徴とする請求項3または請求項4に記載されたA / D変換器。

【請求項6】

前記第2の参照信号の値は、前記第1の参照信号の値より小さい、ことを特徴とする請求項5に記載されたA / D変換器。

【請求項7】

前記第1のキャパシタは、前記標本化のために前記第1および第2の信号を受けるように設けられており、

前記ゲインステージは、前記D / A変換回路からの信号提供および前記第1のキャパシタへの標本化のいずれか一方に応答して、前記演算增幅回路を用いて前記第1の信号を前記第2のキャパシタへ積分し、

前記ゲインステージは、前記D / A変換回路からの信号提供および前記第1のキャパシタへの標本化のいずれか他方に応答して、前記演算增幅回路を用いて前記第2の信号を前記第2のキャパシタへ積分する、ことを特徴とする請求項1～請求項6のいずれか一項に記載されたA / D変換器。

【請求項8】

前記ゲインステージは、前記標本化のための第3のキャパシタおよび前記積分のための第4のキャパシタを更に含み、

前記第1および第3のキャパシタの一方は、前記標本化のために前記第1の信号を受け

10

20

30

40

50

るよう設けられており、

前記第1および第3のキャパシタの他方は、前記標本化のために前記第2の信号を受けるように設けられており、

前記演算增幅回路は、前記D/A変換回路からの信号に応答して、前記第1および第3のキャパシタに標本化された値を前記第2および第4のキャパシタに積分する、ことを特徴とする請求項1～請求項6のいずれか一項に記載されたA/D変換器。

**【請求項9】**

前記第3のキャパシタは、前記D/A変換回路に接続された一端および前記非反転入力に接続された他端を有しており、

前記ゲインステージは、

10

前記第1のキャパシタの前記一端と前記第3のキャパシタの前記一端との間に接続された第3のスイッチと、

前記第4のキャパシタおよび第4のスイッチを有し、前記演算增幅回路の非反転入力と前記演算增幅回路の反転出力との間に接続された第2の容量回路と、

前記非反転入力と前記反転出力との間に接続された第2の帰還スイッチと、

前記入力と前記第3のキャパシタの前記一端との間に接続されており前記イメージセンサからの信号を標本化するための第5のスイッチと

を更に含み、

前記第4のキャパシタおよび前記第4のスイッチは直列に接続されている、ことを特徴とする請求項8に記載されたA/D変換器。

20

**【請求項10】**

前記ゲインステージは、

前記D/A変換回路に接続された一端および前記非反転入力に接続された他端を有する第3のキャパシタと、

前記第1のキャパシタの前記一端と前記第3のキャパシタの前記一端との間に接続された第3のスイッチと、

第4のキャパシタおよび第4のスイッチを有し、前記演算增幅回路の非反転入力と前記演算增幅回路の反転出力との間に接続された第2の容量回路と、

前記非反転入力と前記反転出力との間に接続された第2の帰還スイッチと

を更に含み、

30

前記第4のキャパシタおよび前記第4のスイッチは直列に接続されている、ことを特徴とする請求項2～請求項7のいずれか一項に記載されたA/D変換器。

**【請求項11】**

前記A/D変換回路は、前記ゲインステージが前記第1および第2の期間の後の第3の期間に巡回A/D変換のための動作を行うために、前記ゲインステージの前記出力からの信号に応じた三値のデジタル信号を前記第3の期間に提供し、

前記ゲインステージは、

前記第1のキャパシタの前記他端と前記第3のキャパシタの前記他端との間に接続された第6のスイッチと、

前記第1のキャパシタの前記一端と前記非反転出力との間に接続された第3の帰還スイッチと、

40

前記第3のキャパシタの前記一端と前記反転出力との間に接続された第4の帰還スイッチと、

前記第1のキャパシタの前記他端と前記反転入力との間に接続された第1の転送スイッチと、

前記第3のキャパシタの前記他端と前記非反転入力との間に接続された第2の転送スイッチと

を含む、ことを特徴とする請求項10に記載されたA/D変換器。

**【請求項12】**

前記第1の容量回路において、前記第2のキャパシタの一端は前記反転入力に接続され

50

ており、前記第2のスイッチは前記第2のキャパシタの他端と前記非反転出力との間に接続されており、前記第1の容量回路は、前記第2のキャパシタの前記他端と前記第2のスイッチとの間の第1のノードに接続された第5のキャパシタを含む、ことを特徴とする請求項1～請求項11のいずれか一項に記載されたA/D変換器。

【請求項13】

前記画素はCMOSイメージセンサの画素であり、前記画素の浮遊拡散層がリセット状態に置かれたとき、前記画素からの信号により前記第1の信号が提供され、前記リセット後に前記浮遊拡散層が光誘起電荷の蓄積状態に置かれたとき、前記画素からの信号により前記第2の信号が提供される、ことを特徴とする請求項1～請求項12のいずれか一項に記載されたA/D変換器。

10

【請求項14】

前記イメージセンサの画素と前記ゲインステージの前記入力との間に接続され、前記第1および第2の信号を提供するプリアンプを更に備え、

前記プリアンプは、演算増幅回路と、該演算増幅回路の入力に接続された第1のキャパシタと、該演算増幅回路の出力と前記入力との間に接続された第2のキャパシタと、前記出力と前記入力との間に接続されたスイッチとを含み、前記第1および第2のキャパシタの容量比に応じて前記画素からの信号を増幅し、

前記第1の信号は前記プリアンプのノイズに係る成分を含み、

前記第2の信号は、0前記画素の浮遊拡散層がリセット状態にあるとき前記画素が提供する信号と、前記リセット状態の後に前記浮遊拡散層が光誘起電荷の蓄積状態にあるとき前記画素が提供する信号との差分を示す成分を前記プリアンプのノイズに係る成分に加えて含む、ことを特徴とする請求項1～請求項12のいずれか一項に記載されたA/D変換器。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CMOSイメージセンサのためのA/D変換器および読み出し回路に関する。

【背景技術】

【0002】

非特許文献1の回路では、カラムに接続された高利得アンプを用いてカラムからの信号を増幅することによって、信号に対するノイズの影響を少なくする。非特許文献2の回路では、ノイズの低減と広いダイナミックレンジとの両立を図るために、アンプが1倍の増幅率と8倍の増幅率を持っている。非特許文献3の回路は、低ノイズの信号読み出しを提供している。この読み出しへは、イメージセンサの周辺回路は、高利得のアンプを用いた2段のノイズキャンセル回路を含む。

30

【0003】

特許文献1には、A/D変換アレイ及びイメージセンサが記載されている。A/D変換アレイ及びイメージセンサでは、3個のキャパシタを用いて信号レベルとリセットレベルとの差を生成すると共にこの差をn倍に増幅する。また、特許文献2には、ディジタルノイズキャンセル機能をもつイメージセンサが記載されている。このイメージセンサでは、そのカラムにおいてアナログ領域でのノイズキャンセル回路を用いることなく、イメージアレイの信号レベルとリセットレベルのそれぞれのA/D変換を行ってディジタル値を生成した後に、その差を求めている。

40

【非特許文献1】A. Krymski, N. Khaliullin, H. Krymski, N. Khaliullin, H. Rhodes, "A 2e noise 1.3Megapixel CMOS sensor," Proc. IEEE workshop C CD and Advanced Image Sensors, Elmau, Germany.

【非特許文献2】M. Sakakibara, S. Kawahito, D. Handoko, N. Nakamura, H. Satoh, M. Higashi, K. Mabuchi, H. Sumi, "A high-sensitivity CMOS image sensor with gain-adaptive column amplifiers," IEEE J. Solid-State Circ

50

uits, vol. 40, no. 5, pp. 1147-1156, 2005.

【非特許文献 3】N. Kawai, S. Kawahito, "Noise analysis of high-gain low-noise column readout circuits for CMOS image sensors", IEEE Trans. Electron Devices, vol.51, no.2, pp.185-194 (2004).

【特許文献 1】特開2005-136540号公報

【特許文献 2】特開2006-25189号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

CMOSイメージセンサの最近の画質向上は著しい。CMOSイメージセンサは、カラムに接続された周辺回路を含み、この周辺回路は、増幅機能を備えた読み出し回路を用いてノイズを低減する。故に、この周辺回路を用いて、非常に低ノイズのイメージセンサが実現できる。上記の文献には、カラム処理回路による増幅を利用してノイズを低減することが記載されている。 10

【0005】

しかしながら、非特許文献1の回路において行われるような単純な増幅では、信号のダイナミックレンジが失われてしまい、この結果、高感度・低雑音化と大きなダイナミックレンジの両方を得ることができない。非特許文献2の回路では、アンプが2種類の利得しか持たないので、A/D変換のために必要な所望の階調を得ることには限界がある。非特許文献3は、アンプの利得を高くすることによって非常に低雑音にできる可能性が述べられているが、この方式も単純増幅であり、高感度・低雑音化と大きなダイナミックレンジの両立は困難である。 20

【0006】

本発明は、このような事情を鑑みて為されたものであり、CMOSイメージセンサの画素からの信号にノイズキャンセルを施すことが可能なA/D変換器および読み出し回路を提供することにある。

【課題を解決するための手段】

【0007】

本発明に係る一側面は、イメージセンサのためのA/D変換器である。A/D変換器は、(a)前記イメージセンサからの信号を受ける入力と出力とを有しており、ノイズに係る成分を含む第1の信号の複数回の標本化および標本値の積分を第1の期間に行うと共に、前記イメージセンサの画素からの光誘起信号成分およびノイズに係る成分を含む第2の信号の複数回の標本化および標本値の積分を第1の信号に対する積分とは逆極性となるように第2の期間に行うためのゲインステージと、(b)前記ゲインステージの前記出力からの信号に応じた第1および第2の値を取りうるディジタル信号を提供するA/D変換回路と、(c)前記第1の値の出現回数に対応する信号を提供する回路と、(d)前記ディジタル信号に応答して制御信号を生成する論理回路と、(e)前記第1の期間に前記ゲインステージに所定の電圧信号の提供を行うと共に、前記第2の期間に前記ゲインステージに前記制御信号に応じた電圧信号の提供を行うD/A変換回路とを備える。前記ゲインステージは、前記標本化のための第1のキャパシタと、前記積分のための第2のキャパシタと、前記第1のキャパシタに標本化された信号を前記第2のキャパシタへ積分するための演算増幅回路とを含む。 30

【0008】

本発明に係る別の側面は、イメージセンサのためのA/D変換器である。このA/D変換器は、(a)前記イメージセンサからの信号を受ける入力と出力とを有しており、ノイズに係る成分を含む第1の信号の複数回の標本化および標本値の積分を第1の期間に行うと共に、前記イメージセンサの画素からの光誘起信号およびノイズに係る成分を含む第2の信号の複数回の標本化および標本値の積分を第1の信号に対する積分とは逆極性となるように第2の期間に行うためのゲインステージと、(b)前記ゲインステージの前記出力からの信号に応じた第1および第2の値を取りうるディジタル信号を提供するA/D変換 40

回路と、(c)前記第1の値の出現回数に対応する信号を提供する回路と、(d)前記デジタル信号に応答して制御信号を生成する論理回路と、(e)前記第1の期間に前記ゲインステージに所定の電圧信号を提供すると共に、前記第2の期間に前記制御信号に応じて前記ゲインステージに電圧信号を提供するD/A変換回路とを備え、前記ゲインステージは、(a1)演算増幅回路と、前記D/A変換回路に接続された一端および前記演算増幅回路の反転入力に接続された他端を有する第1のキャパシタと、(a2)前記入力と前記第1のキャパシタの前記一端との間に接続されており前記イメージセンサからの信号を標本化するための第1のスイッチと、(a3)直列に接続された第2のキャパシタおよび第2のスイッチを有し、前記演算増幅回路の非反転出力と前記反転入力との間に接続された第1の容量回路と、(a4)前記反転入力と前記非反転出力との間に接続された第1の帰還スイッチとを含む。10

#### 【0009】

このA/D変換器によれば、ノイズに係る成分を含む第1の信号に対する複数回の標本化と積分および画素からの光誘起信号およびノイズに係る成分を含む第2の信号に対する複数回の標本化と、第1の信号とは逆極性での積分を第1及び第2の期間にそれぞれ行うので、第1の容量回路に蓄積された電荷は第1の信号と第2の信号との差分に関連づけられた積分値を表す。この差分は、画素の光誘起信号成分に対応しており、複数回の積分によりN倍(N:積分の回数)されるけれども、回路起因のランダムノイズ成分は $sqr t$ (N)倍('sqr t'は平方根を示す)される。このため、S/N比は $sqr t(N)$ 倍に改善される。また、A/D変換回路は、ゲインステージの出力からの信号に応じたデジタル信号の第1および第2の値のうち第1の値の出現回数に対応する信号を提供する。この出現回数は、A/D変換回路が、その入力に応答して出力した上位のA/D変換値に対応する。20

#### 【0010】

本発明に係るA/D変換器では、前記ゲインステージは、前記ゲインステージの前記出力からの信号に応じたデジタル信号に対応して前記D/A変換回路から提供される電圧信号に用いて、前記第1および第2の期間の後の第3の期間に巡回A/D変換を行うことが好ましい。

#### 【0011】

本発明に係るA/D変換器では、前記A/D変換回路は、前記ゲインステージの前記出力からの信号を第1および第2の参照信号と比較する比較器を含むことができる。前記比較器は、前記第1の参照信号を前記第2の期間に受け、前記比較器は、前記第2の参照信号を前記第3の期間に受ける。このA/D変換器では、前記第2の参照信号の値は、前記第1の参照信号の値より小さいことが好ましい。30

#### 【0012】

本発明に係るA/D変換器では、前記第1のキャパシタは、前記標本化のために前記第1および第2の信号を受けるように設けられており、前記ゲインステージは、前記D/A変換回路からの信号提供および前記第1のキャパシタへの標本化のいずれか一方に応答して、前記演算増幅回路を用いて前記第1の信号を前記第2のキャパシタへ積分し、前記ゲインステージは、前記D/A変換回路からの信号提供および前記第1のキャパシタへの標本化のいずれか他方に応答して、前記演算増幅回路を用いて前記第2の信号を前記第2のキャパシタへ積分する。40

#### 【0013】

本発明に係るA/D変換器では、前記ゲインステージは、前記標本化のための第3のキャパシタおよび前記積分のための第4のキャパシタを更に含むことができる。前記第1および第3のキャパシタの一方は、前記標本化のために前記第1の信号を受けるように設けられており、前記第1および第3のキャパシタの他方は、前記標本化のために前記第2の信号を受けるように設けられており、前記演算増幅回路は、前記D/A変換回路からの信号に応答して、前記第1および第3のキャパシタに標本化された値を前記第2および第4のキャパシタに積分する。50

## 【0014】

本発明に係るA/D変換器では、画素はCMOSイメージセンサの画素である。画素の浮遊拡散層がリセット状態にあるとき、画素からの信号により前記第1の信号が提供される。リセット後に画素の浮遊拡散層が光誘起電荷の蓄積状態にあるとき、画素からの信号により前記第2の信号が提供される。

## 【0015】

このA/D変換器によれば、画素の浮遊拡散層がリセット状態にあるとき、画素からの第1の信号の標本化が第1のキャパシタを用いて第1の期間内の標本化期間で行われると共に、標本化された信号は、D/A変換回路からの所定の参照電圧信号に応答して第1の容量回路の第2のキャパシタに第1の期間内の積分期間で転送される。標本化と積分とが第1の期間に交互に行われ、第2のキャパシタに蓄積された電荷は第1の信号の複数回の積分値を示す。前記リセット後に画素の浮遊拡散層が光誘起電荷の蓄積状態にあるとき、画素からの第2の信号の標本化が第1のキャパシタを用いて第2の期間内の標本化期間で行われ、同時に標本化された信号は、第1の容量回路の第2のキャパシタに転送される。第1のキャパシタは、D/A変換回路からの電圧信号に応答して第2の期間内の参照電圧標本化期間で標本化される。第2の期間では、画素の標本化と第2のキャパシタへの信号転送が同時に行われ、第1の期間とは逆極性での積分が行われる結果、第1の容量回路に蓄積された電荷は第1の信号と第2の信号との差分に関連づけられた積分値を表す。この差分は、画素の信号成分に対応しており、複数回の積分によりN倍されるけれども、ランダムノイズ成分は $sqr t (N)$ 倍される。また、A/D変換回路は、ゲインステージの出力からの信号に応じたデジタル信号の第1及び第2の値のうち第1の値の出現回数に対応する信号を提供する。この出現回数は、A/D変換回路が、その入力に応答して出力した上位のA/D変換値に対応する。

10

## 【0016】

本発明に係るA/D変換器では、A/D変換回路は、ゲインステージが第1および第2の期間の後の第3の期間に巡回A/D変換のための動作を行うために、ゲインステージの出力からの信号に応じた三値のデジタル信号を第3の期間に提供する。ゲインステージは、第1のキャパシタの一端と非反転出力との間に接続された別の帰還スイッチと、第1のキャパシタの他端と反転入力との間に接続された転送スイッチとを含むことができる。

20

## 【0017】

このA/D変換器によれば、第2の期間に経過のときに第1の容量回路に蓄積された電荷に巡回A/D変換を行う。第3の期間の標本化期間に別の帰還スイッチを介して第1のキャパシタに電荷を標本化する。第3の期間の転送期間にD/A変換回路からの電圧信号を第1のキャパシタに加えることによって電荷の再配置を行う。この結果、ゲインステージの出力に新たな電圧値が生成する。この電圧値に応答して、A/D変換回路が当該巡回サイクルにおけるデジタル信号を生成する。

30

## 【0018】

本発明に係るA/D変換器は、全差動構成であることができる。また、本発明に係る全差動構成のA/D変換器は第1および第2の期間の後に第3の期間に巡回A/D変換を行うことができる。

40

## 【0019】

本発明に係るA/D変換器では、第1の容量回路において、第2のキャパシタの一端は反転入力に接続されており、第2のスイッチは第2のキャパシタの他端と非反転出力との間に接続されており、第1の容量回路は、第2のキャパシタの他端と第2のスイッチとの間の第1のノードに接続された第5のキャパシタを含むことが好ましい。このA/D変換器によれば、第2のスイッチのスイッチングに起因するノイズ（例えば、第2のスイッチとして用いられたMOSアナログスイッチにおいては、チャージインジェクションノイズ）の電圧依存性を低減することができる。

## 【0020】

また、本発明に係るA/D変換器では、第2の容量回路において、第4のキャパシタの

50

一端は反転入力に接続されており、第4のスイッチは第4のキャパシタの他端と反転出力との間の第2のノードに接続されており、第2の容量回路は、第4のキャパシタの他端と第4のスイッチとの間の第2のノードに接続された第6のキャパシタを含むことができる。このA/D変換器によれば、第4のスイッチのスイッチングに起因するノイズ（例えば、第4のスイッチとして用いられたMOSアナログスイッチにおいては、チャージインジエクションノイズ）の電圧依存性を低減することができる。

#### 【0021】

本発明に係るA/D変換器は、CMOSイメージセンサの画素とゲインステージの入力との間に接続され、第1および第2の信号を提供するプリアンプを更に備えることできる。プリアンプは、演算増幅回路と、該演算増幅回路の入力に接続された第1のキャパシタと、該演算増幅回路の出力と入力との間に接続された第2のキャパシタと、出力と入力との間に接続されたスイッチとを含み、第1および第2のキャパシタの容量比に応じて画素からの信号を増幅する。第1の信号はプリアンプのノイズに係る成分を含み、第2の信号は、プリアンプのノイズに係る成分に加えて、画素がリセット状態に置かれたときの画素からの信号と画素が光誘起信号出力状態に置かれたときの画素からの信号との差分を示す成分を含む。

#### 【0022】

本発明に係る別の側面は、イメージセンサのための読み出し回路である。イメージセンサの画素は、画素がリセット状態にあるとき第1の信号を生成すると共に、画素が光誘起信号出力状態にあるとき第2の信号を生成する。この読み出し回路は、(a)演算増幅回路と、該演算増幅回路の入力に接続された第1のキャパシタと、該演算増幅回路の出力と入力との間に接続された第2のキャパシタを含み、第1および第2のキャパシタの容量比に応じて第1の信号および第2の信号を増幅するプリアンプと、(b)プリアンプの出力に接続された標本化スイッチを含み、増幅された第1の信号の複数回の積分を該標本化スイッチを用いて行うと共に増幅された第2の信号の複数回の積分を、第1の信号に対する積分とは逆極性となるように該標本化スイッチを用いて行うことによって、第1の信号と第2の信号との差分を増幅する積分器とを備える。

#### 【0023】

この読み出し回路によれば、増幅された第1の信号の複数回の積分を行うと共に、プリアンプの出力が逆極性になるように、増幅された第2の信号の複数回の積分を行うので、積分器は、第1の信号と第2の信号との差分を示す増幅された信号が差分を提供する。

#### 【0024】

本発明に係るA/D変換器は読み出し回路を更に備え、読み出し回路は、CMOSイメージセンサの画素とゲインステージの入力との間に接続されている。

#### 【0025】

本発明の上記の目的および他の目的、特徴、並びに利点は、添付図面を参照して進められる本発明の好適な実施の形態の以下の詳細な記述から、より容易に明らかになる。

#### 【発明の効果】

#### 【0026】

以上説明したように、本発明によれば、CMOSイメージセンサの画素からの信号にノイズキャンセルを施すことが可能なA/D変換器および読み出し回路が提供される。

#### 【図面の簡単な説明】

#### 【0027】

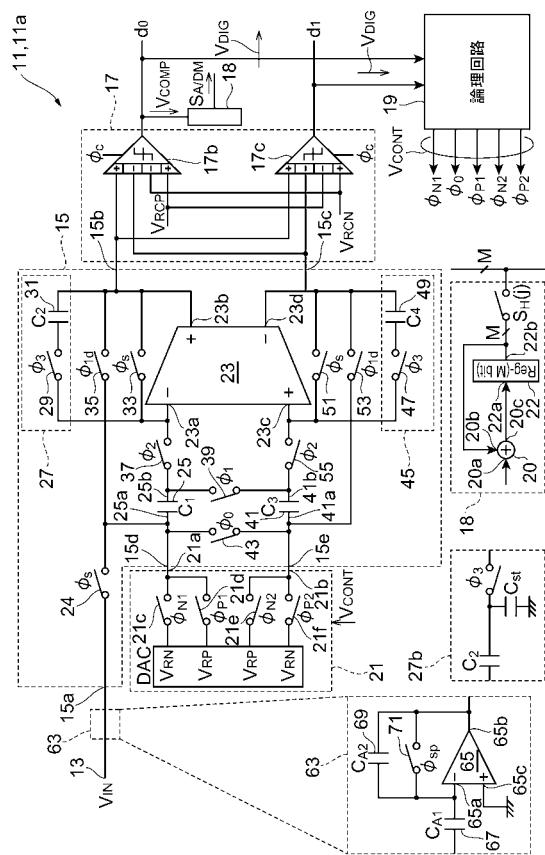

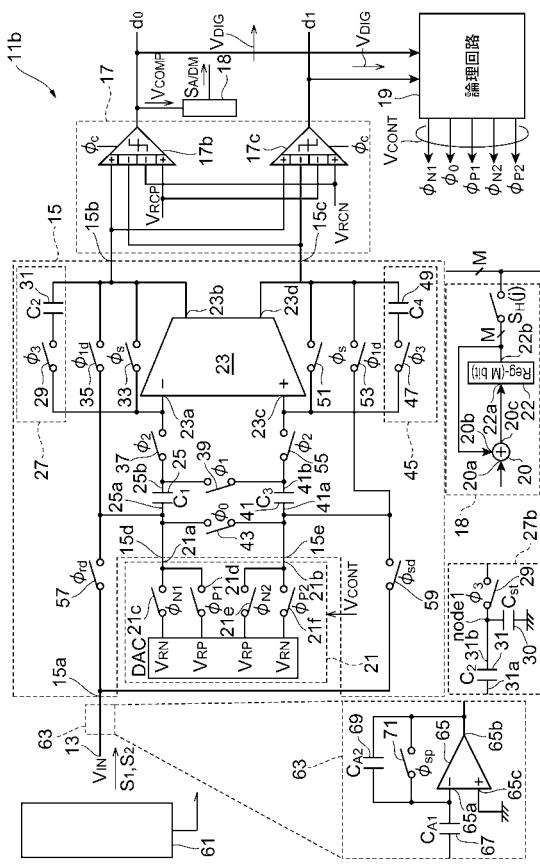

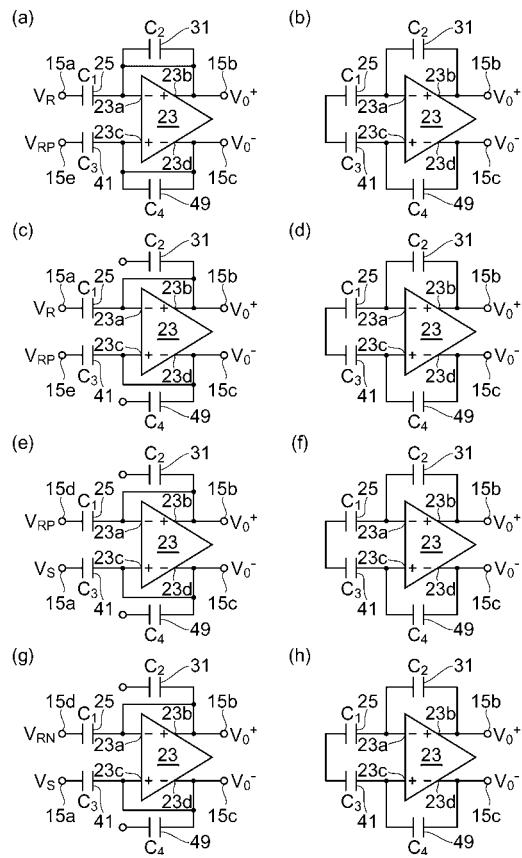

【図1】図1は、本実施の形態に係るA/D変換器の回路図である。

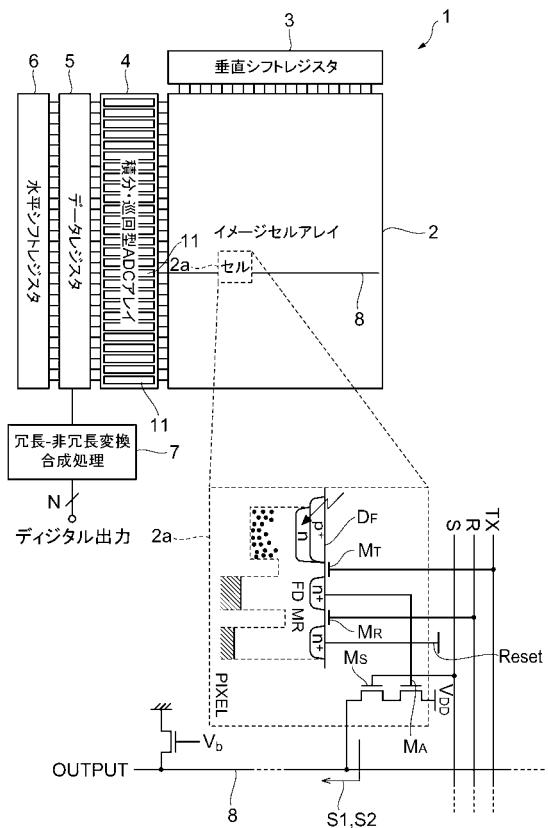

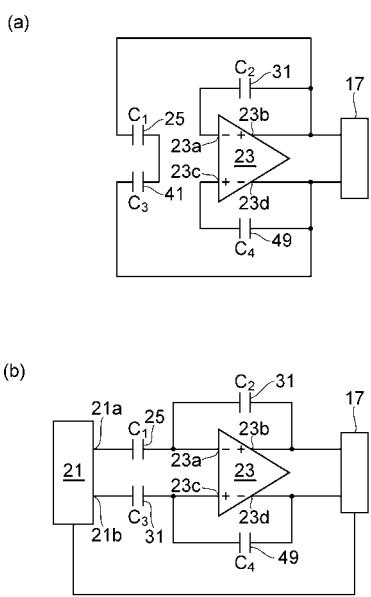

【図2】図2は、CMOSイメージセンサのブロックを示す図面である。

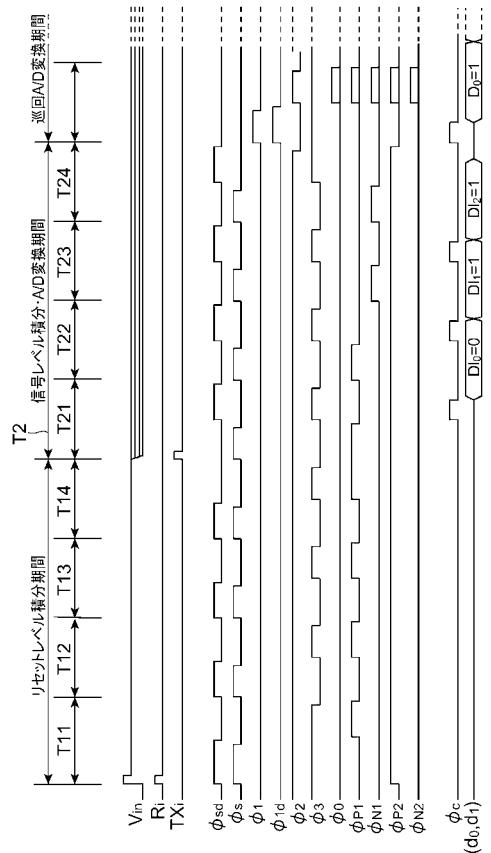

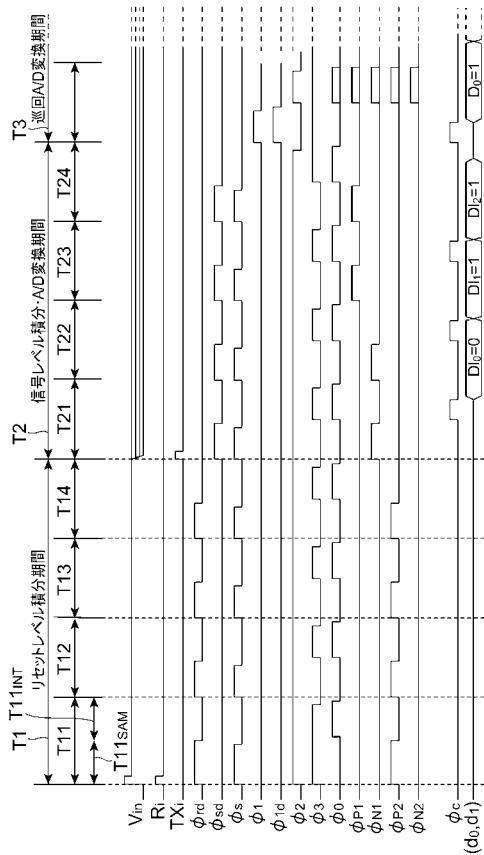

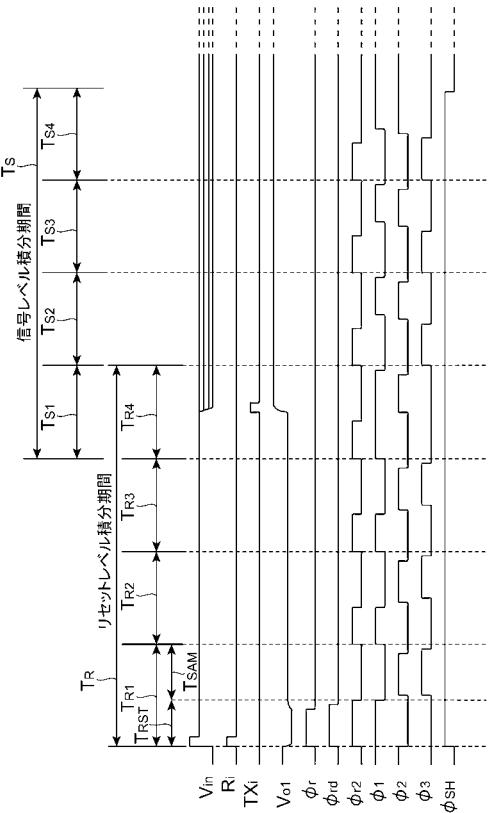

【図3】図3は、A/D変換器の動作のためのタイミングチャートを示す図面である。

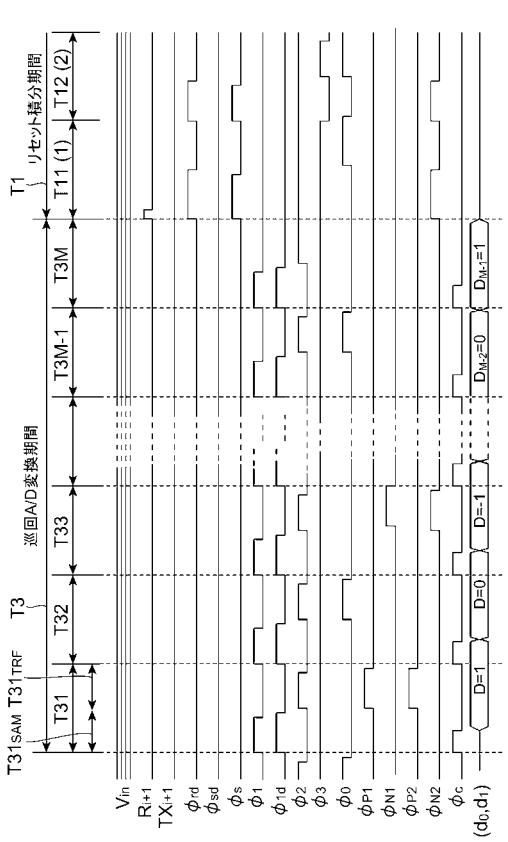

【図4】図4は、A/D変換器の動作のためのタイミングチャートを示す図面である。

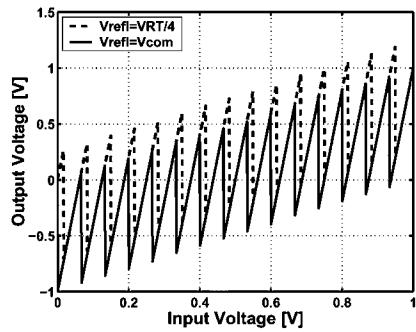

【図5】図5は、シミュレーションによるゲインステージの入出力特性を示す図面である。

【図6】図6は、本実施の形態に係るA/D変換器の回路図である。

10

20

30

40

50

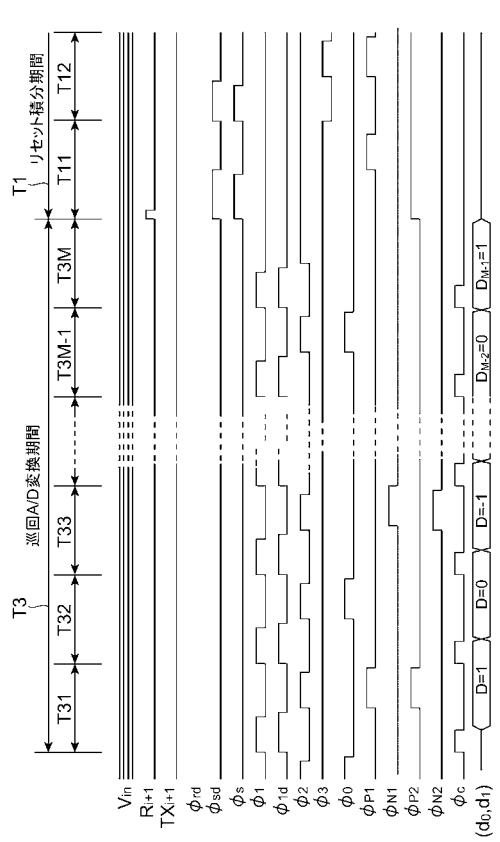

【図7】図7は、A/D変換器の動作のためのタイミングチャートを示す図面である。

【図8】図8は、A/D変換器の動作のためのタイミングチャートを示す図面である。

【図9】図9は、積分A/D変換の動作を示す図面である。

【図10】図10は、巡回A/D変換の動作を示す図面である。

【図11】図11は、イメージセンサの読み出し回路を示す図面である。

【図12】図12は、この読み出し回路のためのタイミングチャートを示す図面である。

【図13】図13は、CMOSイメージセンサを示す図面である。

【図14】図14は、多重積分読み出し回路の動作を示す図面である。

【図15】図15は、多重積分読み出し回路の動作を示す図面である。

【図16】図16は、プリアンプ利得と入力換算ノイズとの関係を示すグラフである。

10

【符号の説明】

【0028】

1 ... CMOSイメージセンサ、2 ... セルアレイ、2 a ... CMOSイメージセンサ画素、1 1、1 1 a、1 1 b ... A/D変換器、1 5 ... ゲインステージ、1 7 ... A/D変換回路、1 8 ... 信号  $S_{A/D_M}$  を提供する回路、1 9 ... 論理回路、2 1 ... D/A変換回路、2 3 ... 演算增幅回路、2 5、3 1、4 1、4 9 ... キャパシタ、2 4、2 9、3 3、4 3、4 7、5 1、5 3、5 5、5 9 ... スイッチ、2 7、2 7 b、4 5 ... 容量回路、6 3 ... プリアンプ、6 5 ... 演算增幅回路、6 7、6 9 ... キャパシタ、7 1 ... スイッチ、8 1 ... 読み出し回路、8 3 ... プリンアンプ、8 5 ... 積分器、8 7 ... 演算增幅回路、8 9、9 1 ... キャパシタ、9 5 ... スイッチ、9 7 ... 標本化スイッチ、8 9、1 0 3、1 0 9 ... キャパシタ、1 0 1 ... 容量回路、1 0 5、1 0 7、1 1 1、1 1 2 ... スイッチ

20

【発明を実施するための最良の形態】

【0029】

本発明の知見は、例示として示された添付図面を参照して以下の詳細な記述を考慮することによって容易に理解できる。引き続いて、添付図面を参照しながら、本発明のA/D変換器および読み出し回路に係る実施の形態を説明する。可能な場合には、同一の部分には同一の符号を付する。

【0030】

(第1の実施の形態)

30

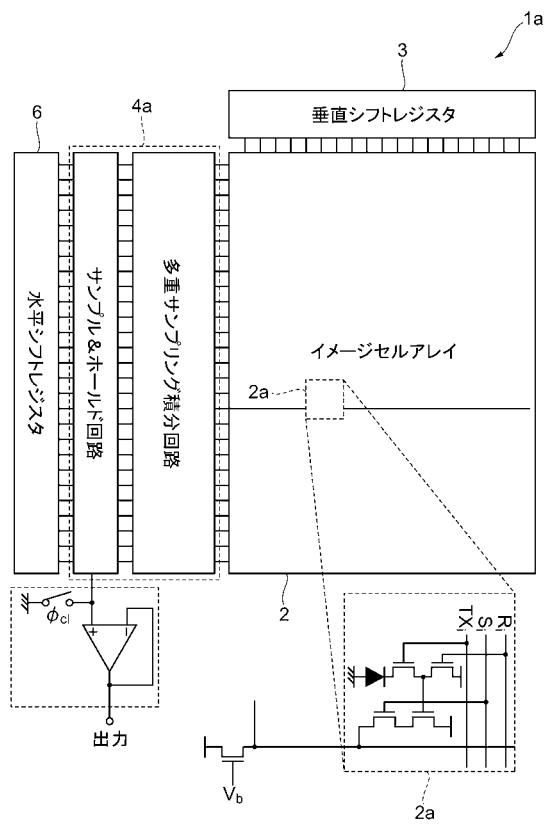

図1は、本実施の形態に係るA/D変換器の回路図である。本実施の形態では、A/D変換器11は、CMOSイメージセンサのために用いられる。図2は、CMOSイメージセンサのブロックを示す図面である。A/D変換器11は、CMOSイメージセンサ1において用いられる。CMOSイメージセンサ1では、セルアレイ2はCMOSイメージセンサ画素2aが行方向および列方向に配列されている。図2には、CMOSイメージセンサ画素2aの一例が示されている。画素2aは、リセット状態における第1の信号  $S_1$  と光誘起信号出力における第2の信号  $S_2$  とを生成する。A/D変換器11の入力13が画素2aに接続されている。A/D変換器11では、ゲインステージ15の入力15aは、画素2aからの信号を受ける。また、A/D変換器11は、第1の期間  $T_1$  に第1の信号  $S_1$  の複数回の標本化と標本値の積分を行うと共に第2の期間  $T_2$  に第2の信号  $S_2$  の複数回の標本化と標本値の積分を行う。A/D変換回路17は、第2の期間  $T_2$  において、ゲインステージ15の出力15bからの信号に応じたデジタル信号を提供し、このデジタル信号は第1および第2の値(例えば、「1」および「0」)を取りうる。また、A/D変換回路17は、1.5ビットのA/D変換のために比較器17b、17cを含む。回路18は、A/D変換回路17の出力(例えば比較器17bの出力)に接続されており、また第1の値(例えば「1」)の出現回数に対応する信号  $S_{A/D_M}$  を提供する。論理回路19は、第1の期間  $T_1$  および第2の期間  $T_2$  に、A/D変換回路17からの信号に応答して制御信号を生成する。D/A変換回路21は、制御信号  $V_{CONT}$  に応答して第1の期間  $T_1$  においてゲインステージ15に所定の電圧信号を提供すると共に、制御信号  $V_{CONT}$  に応答して電圧信号を第2の期間  $T_2$  にゲインステージ15に提供する。ゲイン

40

50

ステージ 15 は演算増幅回路 23 を含む。第 1 のキャパシタ 25 の一端 25a は D/A 変換回路 21 の出力 21a に接続されており、第 1 のキャパシタ 25 の他端 25b は演算増幅回路 23 の反転入力 23a に接続されている。第 1 のスイッチ 24 は、入力 13 とキャパシタ端 25a との間に接続されている。第 1 のスイッチ 24 は、クロック s に応答して動作し、また画素 2a からの信号を標本化するために用いられる。第 1 の容量回路 27 が反転入力 23a と非反転出力 23b との間に接続されている。第 1 の容量回路 27 では、直列に接続された第 2 のスイッチ 29 および第 2 のキャパシタ 31 が、反転入力 23a と非反転出力 23b との間に接続されている。第 2 のスイッチ 29 は、クロック 3 に応答して動作し、第 2 のキャパシタ 31 への積分のために用いられる。例えば、第 1 の容量回路 27 に替えて第 1 の容量回路 27b を用いることができる。第 1 の帰還スイッチ 33 が反転入力と非反転出力との間に接続されている。

#### 【0031】

図 2 を参照すると、CMOS イメージセンサ 1 では、セルアレイ 2 の行に垂直シフトレジスタ 3 が接続されており、セルアレイ 2 の列には A/D 変換器アレイ 4 が接続されている。A/D 変換器アレイ 4 は、アレイ状に配列された複数の A/D 変換器を含む。各 A/D 変換器として A/D 変換器 11 を使用できる。A/D 変換器アレイ 4 には、データレジスタ 5 が接続されており、画素 2a からの信号に対応する A/D 変換値がデータレジスタ 5 に格納される。データレジスタ 5 は、水平シフトレジスタ 6 からの信号に応答して、デジタル信号を冗長表現 - 非冗長表現変換回路 7 へ提供する。冗長表現 - 非冗長表現変換回路 7 は、画素 2a からの信号に対応した N ビットのデジタルコードを生成する。

#### 【0032】

画素 2a は、フォトダイオード D<sub>F</sub> が、イメージに関連する一画素分の光を受ける。選択トランジスタ M<sub>S</sub> のゲートは、行方向に伸びる行選択線 S に接続されている。リセットトランジスタ M<sub>R</sub> のゲートはリセット線 R に接続されている。転送トランジスタ M<sub>T</sub> のゲートは、行方向に伸びる転送選択線に接続されている。フォトダイオード D<sub>F</sub> の一端は転送トランジスタ M<sub>T</sub> を介して浮遊拡散層 F<sub>D</sub> に接続されている。浮遊拡散層 F<sub>D</sub> は、リセットトランジスタ M<sub>R</sub> を介してリセット電位線 R<sub>reset</sub> に接続されると共に、トランジスタ M<sub>A</sub> のゲートに接続されている。トランジスタ M<sub>A</sub> の一電流端子（例えばドレイン）は、選択トランジスタ M<sub>S</sub> を介して列線 8 に接続されている。トランジスタ M<sub>A</sub> は、浮遊拡散層 F<sub>D</sub> の電荷量に応じて電位を選択トランジスタ M<sub>S</sub> を介して列線に提供する。

#### 【0033】

この構造の画素において、ノイズキャンセル動作は、以下のように行われる。まず、リセット制御信号 R をリセットトランジスタ M<sub>R</sub> に提供し、浮遊拡散層 F<sub>D</sub> をリセットする。増幅トランジスタ M<sub>A</sub> を介して、このリセットレベルを読み出す。次いで、電荷転送制御信号 T<sub>x</sub> を転送トランジスタ M<sub>T</sub> に供給し、フォトダイオード D<sub>F</sub> から光誘起信号電荷を浮遊拡散層に転送する。この後、トランジスタ M<sub>A</sub> を介して、この信号レベルを読み出す。このリセットレベルと信号レベルの差は、図 1 に示されるような積分・巡回カスケード A/D 変換器を用いて求められる。これによって、画素 2a のトランジスタの特性ばらつきによる固定パターンノイズと、浮遊拡散層をリセットしたときに発生するリセットノイズといったノイズがキャンセルされる。

#### 【0034】

引き続き、このノイズキャンセル動作を説明する。図 3 および図 4 は、A/D 変換器の動作のためのタイミングチャートを示す図面である。まず、本 A/D 変換器の動作の理解を容易にするために、シングルエンド構成の演算増幅回路をゲインステージに用いる A/D 変換器を説明する。

#### 【0035】

A/D 変換器の入力はイメージセンサアレイ内の一画素からの信号を受ける。この回路は、画像のノイズキャンセル動作を行いながら信号の積分及び粗い A/D 変換（以下、「積分 A/D 変換」として参照する）を行う。積分 A/D 変換は第 1 及び第 2 の期間 T<sub>1</sub>、T<sub>2</sub> に行われる。その後に、積分出力に巡回 A/D 変換を施す。図 2 に示される積分 A/D 変換器の構成は、図 3 に示すように、積分回路 27 と巡回 A/D 変換回路 28 から構成される。

10

20

30

40

50

D変換では、一例として、第1の信号S1（例えば、リセットレベルを示す信号）を期間T11、T12、T13、T14の4期間に標本化すると共に、第2の信号S2（例えば、光誘起信号レベルを示す信号）を期間T21、T22、T23、T24の4期間に標本化する。これらの標本化により、積分A/D変換のための期間に、例えば2ビットのA/D変換値が提供される。標本化回数は例示であり、その回数は必要に応じて変更される。

【0036】

A/D変換器11では、このノイズ低減処理のために多数回の標本化による積分動作を行い、画素内の増幅トランジスタおよびノイズキャンセル回路において発生するランダムノイズを低減する。また、上位ビットを生成するA/D変換を行うので、ダイナミックレンジが確保される。

10

【0037】

A/D変換器11の入力13は、第1の期間T1のうちの期間T11の初期部分で画素の第1の信号S1（リセットレベル信号の値V<sub>r</sub>）を受ける。標本化期間T11<sub>SAM</sub>でクロックsに応答してスイッチ24、33が導通し、この信号は、キャパシタ25に標本化される。クロック3に従ってスイッチ29は導通している。積分期間T11<sub>INT</sub>に、クロックsに応答してスイッチ24、33が非導通にされ、また、スイッチ21dを導通させて、D/A変換回路21から所定の電圧信号V<sub>RP</sub>が第1のキャパシタ25に加えられると、標本化された信号はスイッチ29を介して第2のキャパシタ31に転送される。

20

【0038】

第1および第2のキャパシタ25、31がそれぞれキャパシタンスC1、C2を有し、例えばC1=C2であるとき、演算増幅回路23の出力23bには、

$$V_o = (V_r - V_{RP})$$

が生成される。標本化期間および積分期間のN回繰り返しにより、ゲインステージ15の容量回路27内に電荷が蓄積されて、演算増幅回路23の出力23bには、

$$V_o = N \times (V_r - V_{RP})$$

が生成される。容量回路27内に電荷は保存されている。

【0039】

逆極性での積分のため、第2の期間T2のうちの期間T21の初期部分T21<sub>SAM</sub>で、D/A変換回路21は制御信号V<sub>CONT</sub>のp<sub>1</sub>に応答してスイッチ21dを導通させ、またスイッチ33も導通させることによって、キャパシタ25に参照電圧V<sub>RP</sub>を標本化する。引き続き、A/D変換器11の入力13に、画素の第2の信号S2（信号レベル信号の値V<sub>s</sub>）を受ける。この信号S2は、標本化期間T21<sub>INT</sub>でクロックsに応答してスイッチ24が導通し、またクロック3に応答してスイッチ29は導通することによって、キャパシタ25に標本化されている参照電圧V<sub>RP</sub>と、受けたV<sub>s</sub>との差に比例した電荷が、スイッチ29を介して第2のキャパシタ29に転送される。初回の信号サンプルのとき、A/D変換回路17の動作に関係なく、D/A変換回路21が電圧V<sub>RP</sub>を発生する。

30

【0040】

この説明から理解されるように、図1に示されるA/D変換器における逆極性での積分では、電圧信号を受ける順番により極性が反転される。順極性の場合、標本化のために入力信号を第1のキャパシタ25の一端に受ける。第1のキャパシタ25に入力信号をサンプルした後に、第1のキャパシタ25（キャパシタンスC1）の一端に参照電圧を提供するように切り替えることによって、第2のキャパシタ31へ電荷を転送する。この手順により、電荷C1 × ((入力信号) - (参照電圧)) が第2のキャパシタ31に転送される。逆極性では、まず、先に第1のキャパシタ25の一端に参照電圧を受ける。第1のキャパシタ25の参照電圧をサンプルした後に、第1のキャパシタ25の一端に入力信号を提供するように切り替えることによって、第2のキャパシタ31へ電荷を転送する。電荷C1 × ((参照電圧) - (入力信号)) が第2のキャパシタ31に転送される。これらの式を比較すると、C1 × (参照電圧) と C1 × (入力信号) との順序が逆である。後ほど説

40

50

明されるように、入力を接続する端子を反転入力に与えるか、非反転入力に与えるかによつても順極性接続および逆極性接続を実現できる。

#### 【0041】

ゲインステージ15の出力は、比較器（本実施例では、A/D変換回路17内の比較器17bを用いる）に提供される。この比較器には積分A/D変換のための参照電圧 $V_{ref_I}$ を与える。比較器の比較結果 $V_{COMP}$ は論理回路19に提供され、論理回路19からの制御信号 $V_{CONT}$ に応じてD/A変換回路21が動作する。但し、初回の信号サンプルのとき、D/A変換回路21は、制御信号 $V_{CONT}$ に関係なく電圧 $V_{RP}$ を提供する。比較器は以下のように動作する：

$V_o > V_{ref_I}$ の時、 $V_{COMP} = 1$ であり、D/A変換回路21は積分期間に $V_{RP}$ を提供； 10

$V_o < V_{ref_I}$ の時、 $V_{COMP} = 0$ であり、D/A変換回路21は積分期間に $V_{RN}$ を提供。

標本化期間および積分期間のN回繰り返しにより、ゲインステージ15の容量回路27内に電荷が蓄積されて、 $N = N_1 + N_2$ であるので、演算增幅回路23の出力23bには、

$$V_o = N \times (V_r - V_{RP}) + N_1 \times (V_{RP} - V_s) + N_2 \times (V_{RN} - V_s)$$

$= N \times (V_r - V_s) - N_2 \times (V_{RP} - V_{RN})$

が生成される。値 $N_2$ は、比較器の出力に「1」が現れた回数を示しており、つまり、A/D変換回路は、ゲインステージの出力からの信号に応じたデジタル信号の第1および第2の値のうち第1の値の出現回数に対応する信号を提供する。この信号の値は、例えば 20

A/D変換回路17に接続された回路18を用いてカウントすることができる。A/D変換回路17から信号 $S_{A/D_M}$ として提供される。この値が、A/D変換値の上位ビットである。

#### 【0042】

図1には、回路18の一例が示されている。回路18は、第1および第2の入力20a、20b並びに出力20cを有する加算器20と、入力22aおよび出力22bを有するレジスタ（Mビット）22とを含む。加算器20の第1の入力20aは、A/D変換回路17のうちの一方の比較器17bからの信号を受ける。加算器20の第2の入力20bはレジスタ22の出力22bからの信号を受ける。加算器20は、受けた信号の加算結果（デジタル信号）をMビットのレジスタ22に提供する。レジスタ22は、積分A/D変換中に比較器17bからの信号 $V_{COMP}$ の値「1」および「0」が加算された加算結果を保持する。レジスタ22は、積分A/D変換が終了したとき、上位ビットを示す信号 $S_{A/D_M}$ を提供する。 30

#### 【0043】

このA/D変換器11によれば、第1のキャパシタ25を用いて第1の信号 $S_1$ の標本化が第1の期間 $T_1$ 内の標本化期間（例えば $T_{11 SAM}$ ）で行われると共に、標本化された信号は、D/A変換回路からの所定の電圧信号に応答して第2のキャパシタ31に第1の期間内の積分期間（例えば期間 $T_{11 INT}$ ）で転送される。第1の期間に標本化および積分が交互に行われ、第2のキャパシタ31に蓄積された電荷は第1の信号 $S_1$ の複数回の積分値を示す。第1のキャパシタ25を用いてD/A変換回路21からの電圧信号の標本化が第2の期間 $T_2$ 内の標本化期間（例えば期間 $T_{21 SAM}$ ）で行われると共に、標本化された信号は、第2の期間 $T_2$ 内の積分期間（例えば期間 $T_{21 INT}$ ）で第2の信号 $S_2$ に応答して第2のキャパシタ31に転送される。第2の期間 $T_2$ に標本化および積分が交互に行われ、第2のキャパシタ31に蓄積された電荷は第1の信号 $S_1$ と第2の信号 $S_2$ との差分に関連づけられた積分値を表す。この差分は、画素の信号成分に対応しており、複数回の積分によりN倍（N：積分の回数）されるけれども、ランダムノイズ成分は $\sqrt{N}$ 倍される。このため、S/N比は $\sqrt{N}$ 倍に改善される。 40

#### 【0044】

再び図1を参照しながら、A/D変換器11をさらに説明する。A/D変換回路17は、ゲインステージ15が第1および第2の期間 $T_1$ 、 $T_2$ の後の第3の期間 $T_3$ に巡回A

10

20

30

40

50

/ D 変換のための動作を行うために、ゲインステージ 15 の出力 15 b からの信号に応じた三値のデジタル信号  $V_{D\text{IG}}$  ( $V_{D\text{IG}}$  は (d0, d1) からなる) を第 3 の期間間に提供する。ゲインステージ 15 では、帰還スイッチ 35 がキャパシター端 25 a と非反転出力 15 b との間に接続されており、またクロック 1d に応答して動作する。第 1 のキャパシタ 25 の他端 25 b は、転送スイッチ 37 を介して反転入力 15 a および第 1 の容量回路 27 に接続されている。転送スイッチ 37 は、クロック 2 に応答して動作する。なお、キャパシタ他端 25 b にはスイッチ 39 が接続される。スイッチ 39 は、クロック 1 に応答して動作し、シングルエンド構成のゲインステージでは基準電位を提供するように接続される。

【0045】

10

この A / D 変換器 11 を用いて、第 3 の期間  $T_3$  に、第 2 の期間に経過のときに第 1 の容量回路に蓄積された電荷によって発生するゲインステージ出力 15 b に対して巡回 A / D 変換を行う。第 3 の期間の標本化期間  $T_{31\text{SAM}}$  に第 2 の帰還スイッチ 35 を介して第 1 のキャパシタ 25 に電荷を標本化する。第 3 の期間  $T_3$  の転送期間  $T_{31\text{TRF}}$  に D / A 変換回路 21 からの電圧信号を第 1 のキャパシタ 25 に加えることによって転送スイッチ 37 を介して第 1 のキャパシタ 25 から第 2 のキャパシタ 31 に電荷を転送し電荷の再配置を行う。この結果、ゲインステージ 15 の出力 15 b に新たな電圧値が生成される。ゲインステージ 15 からの信号は、A / D 変換回路 21 において 2 つの参照電圧  $V_{RCP}$ 、 $V_{RCN}$  と比較される。参照電圧  $V_{RCP}$ 、 $V_{RCN}$  は、それぞれ、例えば  $V_{RP}/4$ 、 $V_{RN}/4$  である。A / D 変換回路 17 の出力は、冗長ディジタルコードを提供し、この冗長ディジタルコードに応答して、制御回路 19 は、D / A 変換回路 21 を制御するための制御信号  $V_{CONT}$  を生成する。A / D 変換回路 17 が当該巡回サイクルにおけるディジタル信号を生成する。ゲインステージ 15 では、D / A 変換回路からの電圧信号に応答して、第 1 のキャパシタ 25 に標本化された電圧を増幅すると共に、D / A 変換回路 21 からの電圧信号を減算する。このため、 $i$  回目の巡回動作におけるゲインステージ 15 の出力は、キャパシタ 25、31 の容量値に関して  $C_1 = C_2$  が満たされたとき、

$$V_o(i) = 2 \times V_o(i-1) - V(i)$$

となり、D / A 変換回路 21 の出力  $V(i)$  は

$$V_{RP} (D(i) = +1)$$

$$0 (D(i) = 0)$$

$$V_{RN} (D(i) = -1)$$

20

である。なお、電圧  $V_{PR}$  は正の値とし、 $V_{RN} = -V_{RP}$  である。

このために、D / A 変換回路 21 は、電圧  $V_{RP}$ 、 $V_{RN}$  を提供する電圧源 21 a と、制御信号  $V_{CONT}$  に応答して電圧値を切り替えるスイッチ 21 c ~ 21 f および 43 とを含む。

ディジタル信号  $D(i)$  は、

$$D(i) = +1 (V_{RP}/4 < V_o(i-1))$$

$$D(i) = 0 (V_{RN}/4 < V_o(i-1) < V_{RP}/4)$$

$$D(i) = -1 (V_o(i-1) < V_{RN}/4)$$

である。電圧範囲の決定は、A / D 変換回路 17 の比較器 17 b、17 c を用いて行われる。巡回 A / D 変換動作において 12 ビットの分解能の A / D 変換値を得るために、11 回の巡回動作が必要である。

【0046】

40

図 5 は、シミュレーションにより求めたゲインステージの積分型 A / D 変換器として動作時における入出力特性を示す図面である。積分 A / D 変換（積分回数：16 回）において、参照電圧  $V_{refI}$  として 2 種類の値を用いてシミュレーションを行った結果が図 5 に示される。A / D 変換回路の比較器において積分 A / D 変換のための参照電圧として巡回 A / D 変換のための参照電圧（例えば 0.25 ボルト）を用いる場合、出力電圧のフルレンジが、1 ボルト（電源電圧）を越える。このため、積分 A / D 変換のための参照電圧は、巡回 A / D 変換のための参照電圧よりも低い値を用いることが好ましい。本シミュレ

50

ーションでは、参照電圧  $V_{COM}$  を用い、この値は例えば 0 ボルトである。図 5 から理解されるように、低照度から高照度の広い範囲にわたって積分 A / D 変換が可能である。また、低照度においては、S / N 比の改善と高ダイナミックレンジが実現される。積分回数 16 回、巡回 A / D 変換 11 回の動作では、積分 A / D 変換から 4 ビットのデジタルコードが生成され、1.5 ビット巡回 A / D 変換から 12 ビットのデジタルコードが生成される。この結果、16 ビットのデジタルコードが生成される。実際の S N R は、ノイズレベルにより決定され、見積もりによれば、14 ビット相当の A / D 変換が実現される。

#### 【 0 0 4 7 】

次いで、本実施の形態に係る A / D 変換器は、シングルエンド構成に替えて、全差動構成を有することができる。図 1 を再び参照しながら、全差動構成の A / D 変換器を説明する。全差動構成の A / D 変換器 11 a では、第 3 のキャパシタ 41 の一端 41 a は D / A 変換回路 21 の出力 21 b に接続され、また他端 41 b は、スイッチ 55 を介して非反転入力 23 c に接続される。第 3 のスイッチ 43 は、第 1 のキャパシタ 25 の一端 25 a と第 3 のキャパシタ 41 の一端 41 a との間に接続される。第 2 の容量回路 45 は、非反転入力 23 c と反転出力 23 d との間に接続されており、第 1 の容量回路 27 と同一の構成を有する。本実施例では、第 2 の容量回路 45 は、直列に接続された第 4 のスイッチ 47 および第 4 のキャパシタ 49 を有する。第 3 の帰還スイッチ 51 は、非反転入力 23 c と反転出力 23 d との間に接続される。このスイッチ 51 はクロック s に応答して動作し、第 4 のスイッチ 47 はクロック 3 に応答して動作する。A / D 変換器 11 a のゲインステージ 15 は、出力 15 b に加えて相補の出力 15 c を有する。

#### 【 0 0 4 8 】

A / D 変換器 11 a でも、積分 A / D 変換が第 1 および第 2 の期間 T1、T2 に行われる。また、A / D 変換器 11 a もシングルエンド構成の A / D 変換器と同様に動作する。これによって、このノイズキャンセル処理のために多数回の標本化による積分動作を行い、画素内の増幅トランジスタおよびノイズキャンセル回路において発生するランダムノイズを低減する。また、上位ビットを生成する A / D 変換を行うので、ダイナミックレンジが確保される。

#### 【 0 0 4 9 】

また、A / D 変換器 11 a は、第 3 の期間 T3 に巡回 A / D 変換を行うためには、以下の回路素子を備える。ゲインステージ 23 では、第 6 のスイッチ 39 が、第 1 のキャパシタ 25 の他端 25 b と第 3 のキャパシタ 41 の他端 41 b との間に接続される。第 4 の帰還スイッチ 53 が、第 3 のキャパシタ 41 の一端 41 a と反転出力 23 d との間に接続される。第 8 のスイッチ 55 が第 3 のキャパシタ 41 の他端 41 b と非反転入力 23 c との間に接続される。第 4 の帰還スイッチ 53 はクロック 1 d に応答して動作し、第 8 のスイッチ 55 は 2 に応答して動作する。

#### 【 0 0 5 0 】

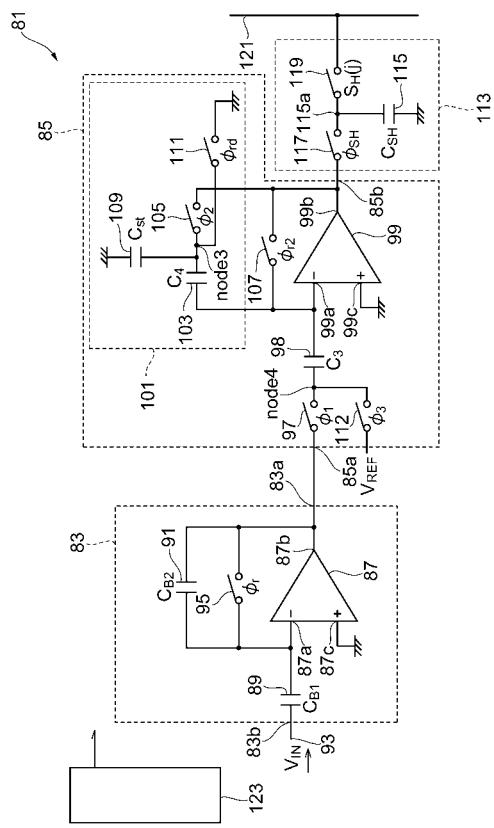

図 6 は、本実施の形態に係る A / D 変換器の回路図である。本実施の形態では、A / D 変換器 11 b は、A / D 変換器 11、11 a と同様に、CMOS イメージセンサのために用いられる。A / D 変換器 11 b は、スイッチ 24 に替えて、クロック r d に応答して動作するスイッチ 57 を含む。また、A / D 変換器 11 b は、入力 13 と第 3 のキャパシタ 41 の一端 41 a との間に接続されたスイッチ 59 を含み、このスイッチ 59 は、CMOS イメージセンサからの信号を標本化するために用いられる。このスイッチ 59 はクロック s d に応答して動作する。

#### 【 0 0 5 1 】

引き続き、このノイズキャンセル動作を説明する。図 7 および図 8 は、A / D 変換器の動作のためのタイミングチャートを示す図面である。A / D 変換器 11 b は、図 7 および図 8 に示されたタイミングチャートに従って動作する。このためのクロックは、クロック生成器 61 によって提供される。クロック生成器 61 と同様のクロック生成器が A / D 変換器 11、11 a のために用いられる。図 7 ~ 図 9 を参照しながら、A / D 変換器 11 b

10

20

30

40

50

の積分 A / D 変換を説明する。

【0052】

C MOSイメージセンサの画素からのリセットレベル信号  $V_r$  に複数回の標本化を施すことによって、ゲインステージ 15 を用いて該リセットレベル信号  $V_r$  を積分する。

【0053】

図 9 に示されるステップ (a) では、リセットレベル信号  $V_r$  を入力 15a に供給すると共に入力 15e に D / A 変換回路 21 からの所定の電圧信号  $V_{RP}$  を供給し、さらに帰還スイッチ 33、51 を導通させて演算增幅回路 23 の入力および出力を接続する。これにより、キャパシタ 31、49 の電荷がリセットされると共に、キャパシタ 25、41 にそれぞれ電圧  $V_r$ 、 $V_{RP}$  が標本化される。

10

【0054】

この後に、図 9 に示されるステップ (b) では、スイッチ 43 を導通させてキャパシタ 25、41 の一端を接続し、キャパシタ 25、41 に標本化された電圧をキャパシタ 31、49 に転送する。ゲインステージ 15 の出力 15b、15c にはそれぞれ  $V_o^+$ 、 $V_o^-$  が生成され、

$$V_o = V_o^+ - V_o^- \\ = V_r \times C_1 / C_2 - V_{RP} \times C_3 / C_4$$

が得られる。

【0055】

この後に、図 9 に示されるステップ (c) では、入力 15a、15e にはリセットレベル信号  $V_r$  および電圧信号  $V_{RP}$  が供給されている。キャパシタ 31、49 の電荷をリセットしないように、スイッチ 29、47 を非導通にすると共に帰還スイッチ演算 33、51 を導通させて演算增幅回路 23 の入力および出力を接続することによって、キャパシタ 25、41 にそれぞれ電圧  $V_r$ 、 $V_{RP}$  が標本化される。

20

【0056】

この後に、図 9 に示されるステップ (d) では、スイッチ 29、47 およびスイッチ 43 を導通させることによってキャパシタ 25、41 の一端を接続し、キャパシタ 25、41 に標本化された電圧をキャパシタ 31、49 に転送する。ゲインステージ 15 の出力 15b、15c にはそれぞれ  $V_o^+$ 、 $V_o^-$  が生成され、

$$V_o = V_o^+ - V_o^- \\ = (V_r \times C_1 / C_2 - V_{RP} \times C_3 / C_4) \times 2$$

が得られる。

30

【0057】

ステップ (c) および (d) を繰り返す。N 回の繰り返しにより、ゲインステージ 15 の出力 15b、15c にはそれぞれ  $V_o^+$ 、 $V_o^-$  が生成され、

$$V_o = V_o^+ - V_o^- \\ = (V_r \times C_1 / C_2 - V_{RP} \times C_3 / C_4) \times N$$

が得られる。

【0058】

引き続き、信号レベル電圧の標本化と積分を行う。まず、比較器 17b によって、ゲインステージ 15 の出力電圧を参照電圧  $V_{refI}$  と比較する。出力電圧が  $V_{refI}$  よりも小さい場合には、ステップ (e) 及び (f) の動作を行い、出力電圧が  $V_{refI}$  よりも大きいかまたは等しい場合には、ステップ (g) 及び (h) の動作を行う。信号レベル電圧の標本化は、ゲインステージ 15 の入力極性を反転する点に注意を要する。図 9 に示されるステップ (e) では、入力 15a、15e には電圧信号  $V_{RP}$  および信号レベル信号  $V_s$  が供給されている。キャパシタ 31、49 の電荷をリセットしないように、スイッチ 29、47 を非導通にすると共に帰還スイッチ 33、51 を導通させて演算增幅回路 23 の入力および出力を接続することによって、キャパシタ 25、41 にそれぞれ電圧  $V_{RP}$ 、 $V_s$  が標本化される。

40

【0059】

50

次いで、図9に示されるステップ(f)では、スイッチ29、47およびスイッチ43を導通させてキャパシタ25、41の一端を接続し、キャパシタ25、41に標本化された電圧をキャパシタ31、49に転送する。ゲインステージ15の出力15b、15cにはそれぞれ $V_o^+$ 、 $V_o^-$ が生成される。ゲインステージ15の出力からの信号は、A/D変換回路17に提供される。既にシングルエンド構成のA/D変換器の動作と同様に、A/D変換回路17において、ゲインステージ15の出力からの信号を参照電圧(例えば $V_{com}$ )と比較し、この比較結果に応じて、次のステップにおいてD/A変換回路21が供給する電圧信号を決定する。

#### 【0060】

図9に示されるステップ(g)では、キャパシタ31、49の電荷をリセットしないように、スイッチ29、47を非導通にすると共に帰還スイッチ演算33、51を導通させて演算増幅回路23の入力および出力を接続することによって、キャパシタ25、41にそれぞれ電圧 $V_{RN}$ 、 $V_S$ が標本化される。

#### 【0061】

この後に、図9に示されるステップ(h)では、スイッチ29、47およびスイッチ43を導通させてキャパシタ25、41の一端を接続し、キャパシタ25、41からキャパシタ31、49に標本化された電荷を転送する。

#### 【0062】

A/D変換回路17において、ゲインステージ15の出力からの信号を参照電圧(例えば $V_{com}$ )と比較し、この比較結果に応じて、次のステップにおいてD/A変換回路21が供給する電圧信号を決定し、その結果によってステップ(e)～(f)とステップ(g)～(h)の動作のどちらを選択し、選択した一連のステップを繰り返す。N回の繰り返しにより、ゲインステージ15の出力15b、15cにはそれぞれ $V_o^+$ 、 $V_o^-$ が生成される。A/D変換回路17がゲインステージ15の出力からの信号を判定し、N1回だけ、参照電圧を越えたとするとき、

$$\begin{aligned} V_o &= V_o^+ - V_o^- \\ &= N \times (V_r \times C_1 / C_2 - V_{RP} \times C_3 / C_4) \\ &+ N1 \times (V_{RP} \times C_1 / C_2 - V_S \times C_3 / C_4) \\ &+ N2 \times (V_{RN} \times C_1 / C_2 - V_S \times C_3 / C_4) \end{aligned}$$

が得られる。ここで、 $N = N1 + N2$ が満たされ、またD/A変換回路がN1回の積分において電圧 $V_{RP}$ を供給し、N2回の積分において電圧 $V_{RN}$ を供給している。

$$\begin{aligned} V_o &= V_o^+ - V_o^- \\ &= N \times (V_r \times C_1 / C_2 - V_S \times C_3 / C_4) \\ &+ N1 \times (C_1 / C_2 - C_3 / C_4) \times V_{RP} \\ &- N2 \times (V_{RP} \times C_1 / C_2 - V_{RN} \times C_3 / C_4) \end{aligned}$$

が得られる。 $C_1 = C_2 = C_3 = C_4$ が満たされるとき、

$$\begin{aligned} V_o &= V_o^+ - V_o^- \\ &= N \times (V_r - V_S) - N2 \times (V_{RP} - V_{RN}) \end{aligned}$$

が得られる。

#### 【0063】

この結果は、ノイズキャンセルされた信号( $V_r - V_S$ )が積分によってN倍に増幅されることを示している。積分された信号成分 $N \times (V_r - V_S)$ から参照電圧差( $V_{RP} - V_{RN}$ )のN2倍を差し引くことによって、画素からの信号をN倍に増幅しても、増幅された信号は所望の電圧範囲に収めることができることを意味する。また、N回の積分により、信号振幅が積分でN倍に増幅されると共にランダムノイズの振幅は $sqr t(N)$ 倍になるので、積分動作によって信号対ノイズ比(S/N比)が改善され、ノイズ低減効果が得られる。例えば、16回の積分によりS/N比で約4倍の改善が得られる。つまり相対的にノイズが1/4になる。

#### 【0064】

値N2は上位のディジタルコードである。この後に説明される巡回A/D変換をゲイン

10

20

30

40

50

ステージ 15 の残余信号に施せば、高い分解能を有する下位ディジタルコードが得られる。

【 0 0 6 5 】

図 10 は、巡回 A / D 変換の動作を示す図面である。図 10 のステップ ( a ) に示されるように、帰還スイッチ 35、53 を導通させて、ゲインステージ 15 の残余信号をキャパシタ 25、41 に標本化する。次いで、図 10 のステップ ( a ) に示されるように、制御信号  $V_{C O N T}$  に応じた電圧を D / A 変換回路 21 がキャパシタ 25、41 に加えて、キャパシタ 25、41 の電荷をキャパシタ 31、49 に転送すると共に電荷の再配置を行う。この結果、ゲインステージ 15 の出力に演算結果が生成される。A / D 変換回路 17 を用いてゲインステージ 15 の出力信号からディジタル信号を生成する。ステップ ( a ) および ( b ) を繰り返すことによって、所望のビット数の巡回 A / D 変換を行う。 10

【 0 0 6 6 】

第 1 及び第 2 の実施の形態の A / D 変換器 11、11a、11b において、図 1 及び図 6 に示されるように、容量回路 27、45 のための容量回路 27b を用いることができる。

【 0 0 6 7 】

容量回路 27 に替えて容量回路 27b を用いると、第 2 のキャパシタ 31 の一端 31a は反転入力 23a に接続される。第 2 のスイッチ 29 は第 2 のキャパシタ 31 の他端 31b と非反転出力 23b との間に接続される。容量回路 27b は、第 2 のキャパシタ 31 の他端 31b と第 2 のスイッチ 29 との間の第 1 のノード node 1 に接続されたキャパシタ 30 ( 容量値  $C_{S T}$  ) を含むことが好ましい。キャパシタ 30 によれば、第 2 のスイッチ 29 のスイッチングに起因するノイズ ( 例えば、第 2 のスイッチ 29 として用いられた MOS アナログスイッチにおいては、チャージインジェクションノイズの電圧依存性 ) を低減できる。 20

【 0 0 6 8 】

容量回路 45 に替えて容量回路 27b を用いると、第 2 のキャパシタ 31 の一端 31a は非反転入力 23c に接続される。第 2 のスイッチ 29 は第 2 のキャパシタ 31 の他端 31b と反転出力 23d との間に接続される。容量回路 27b がキャパシタ 30 を用いれば、同様に、チャージインジェクションノイズの電圧依存性 ) を低減できる。

【 0 0 6 9 】

また、第 1 および第 2 の実施の形態に係る A / D 変換器 11、11a、11b は、プリアンプ 63 を含むことができる。プリアンプ 63 は、CMOS イメージセンサの画素 2a とゲインステージ 15 の入力 15a との間に接続される。 30

【 0 0 7 0 】

プリアンプ 63 は、演算增幅回路 65 と、該演算增幅回路 65 の反転入力 65a に接続された第 1 のキャパシタ 67 と、該演算增幅回路 65 の出力 65b と入力 65a との間に接続された第 2 のキャパシタ 69 およびスイッチ 71 とを含み、第 1 および第 2 のキャパシタ 67、69 の容量比 ( $C_{A1} / C_{A2}$ ) に応じて第 1 および第 2 の信号 S1、S2 を增幅する。このプリアンプ 63 は、図 2 に示すようなイメージセンサアレイ 2 のカラムにアレイ状に並列に配置することが有効である。まず、クロック sp をアクティブにして、スイッチ 71 を導通させる。プリアンプ 63 の入力は、画素 2a からのリセットレベル信号  $V_r$  を受ける。この信号がキャパシタ 67 ( $C_{A1}$ ) に標本化される。その後に、スイッチ 71 を非導通にすると、そのとき、プリアンプ 63 は出力電圧  $V_{O U T1}$  を生成する。次いで、プリアンプ 63 の入力は、画素 2a からの信号レベル信号  $V_s$  を受ける。このときのプリアンプ 63 は出力電圧  $V_{O U T2}$  を生成する。 40

【 0 0 7 1 】

電圧  $V_{O U T1}$  は、プリアンプ 63 の入出力をクロック sp に応答したスイッチ 71 でショートしたことにより直流的に定まる電圧値 ( 動作点 )  $V_{S C}$  にノイズが重畠した電圧となり、次のように表される。

$$V_{O U T1} = V_{S C} + V_{N f} + V_{N 1} \quad ( 1 )$$

そのノイズ成分は、プリアンプ 6 3 の容量にサンプルされ固定値として表されるノイズ(フリーズノイズ)  $V_{nf}$  と、時間的に変動するノイズ  $V_{n1}$  とを含む。

【0072】

電圧  $V_{out2}$  は、次の成分を含む。

$$V_{out2} = (V_r - V_s) \times C_{A1} / C_{A2} + V_{sc} + V_{nf} + V_{n2} \quad (2)$$

第1項は、キャパシタ  $C_{A1}$  からキャパシタ  $C_{A2}$  への移動電荷であり、画素からのノイズレベル信号を受けたキャパシタ  $C_{A1}$  には、最初、電荷  $Q_{A1}(n) = C_{A1} \times (V_r - V_{sc})$  が格納されており、その後に画素からの信号レベル信号を受けると、キャパシタ  $C_{A1}$  には  $Q_{A1}(s) = C_{A1} \times (V_s - V_{sc})$  が格納され、この差分がキャパシタ  $C_{A2}$  に転送される。第1および第3項は、それぞれ、フリーズノイズ  $V_{nf}$  と、時間的に変動するノイズ  $V_{n2}$  とに対応する。 10

【0073】

つまり、2つのレベル  $V_s, V_r$  に共通なノイズ成分がキャンセルされ、差分 ( $V_r - V_s$ ) が、 $C_{A1}$  と  $C_{A2}$  の比で増幅される。増幅された  $(V_r - V_s) \times C_{A1} / C_{A2}$  にノイズ成分などが重畠されている。この2つの電圧レベル  $V_{out2}, V_{out1}$  に対して、多数回標本化を行って積分を行った後、差 ( $V_{out2} - V_{out1}$ ) を求める演算を行う。

【0074】

まず、電圧レベル  $V_{out2}, V_{out1}$  の差は、

$$V = V_{out2} - V_{out1} \\ = (V_r - V_s) \times C_{A1} / C_{A2} + V_{n2} - V_{n1} \quad (3)$$

と表される。

【0075】

この  $V$  は、両者の共通成分(アンプの動作点電圧と、フリーズノイズ成分)がキャンセルされる。このキャンセルが低ノイズ化において非常に重要である。式(2)は、画素からの信号に対するノイズキャンセル( $V_r$  と  $V_s$  の差を求める)動作が行われるが、フリーズノイズ成分が残ることを示す。一方、式(3)では、時間的に変動する成分  $V_{n1}$  と  $V_{n2}$  との間には相関がないので、その成分によるノイズは増加する。

【0076】

つまり、差  $V_{out2} - V_{out1}$  を求める演算によってノイズが低減できるかどうかは、それぞれのノイズの大きさによる。実際、大きな  $C_{A1} / C_{A2}$  を用いて利得を高めたプリアンプのノイズを計算してみると、ノイズ成分  $V_{nc}$  が支配的である。さらに、この計算結果は実際の測定により確認され、極めて高いノイズ低減が可能であることが明らかになった。測定の結果、 $C_{A1} / C_{A2}$  を大きくすると、式(2)に対応するキャンセルに比べて 40% 程度のノイズ低減効果が得られる。この測定では、 $C_{A1} / C_{A2} = 20$  を用いた。好ましくは、比  $C_{A1} / C_{A2}$  は 8 以上である。 30

【0077】

したがって、積分 A / D 変換において、 $V_{out1}$  および  $V_{out2}$  のそれぞれに対して、N回の積分を行うと、式(3)中のノイズ成分  $V_{n1}, V_{n2}$  が低減される。つまり、積分 A / D 変換では、式(3)の第1項  $(V_r - V_s) \times C_{A1} / C_{A2}$  は、N倍に増幅される一方で、ランダムなノイズ成分 ( $V_{n2}, V_{n1}$ ) は  $\sqrt{N}$  倍になるので、N回の積分によって S / N が  $\sqrt{N}$  倍向上する。別の言い方をすれば、入力換算のノイズが  $1 / \sqrt{N}$  になり、フリーズノイズの低減効果と合わせて極めて低雑音の読み出しが可能になる。なお、プリアンプは、全差動構成でも良いし、内部の演算増幅器の変わりにシングルエンド入力、シングルエンド出力のアンプを用いても良い。 40

【0078】

以上説明したように、本実施の形態では、A / D 変換器が提供される。このA / D 変換器では、特にイメージセンサのカラムへの集積化に適し、簡単な回路構成により、イメージセンサの信号の読み出しを低雑音で行いながら、広いダイナミックレンジをもった高分解能のデジタル値を出力する。そのために、イメージセンサの画素からの信号に、ノイ 50

ズキャンセルを行いながら、信号を多数回標本化して、積分による増幅を行うことによってノイズの低減を図る。また、上記の積分の中間結果（積分値を）を逐次に比較器によってある基準値と比較する。比較結果が基準値よりも積分値が大きいことを示す場合、積分値から所定の値を差し引くことによって、積分動作中に、A / D 変換器の出力が飽和するのを抑えると共に、この差し引いた回数を、粗いA / D 変換値として用いる。積分A / D 変換の後に、ノイズキャンセル及び積分に用いた回路を利用して巡回A / D 変換を行い、下位ビットのA / D 変換を行う。積分A / D 変換からの上位ビットと巡回A / D 変換からの下位ビットとを併せて高分解能のデジタルコードを得る。さらに、積分A / D 変換に先だってプリアンプを設け、プリアンプで発生するフリーズノイズを除去することによってさらに低雑音の信号読み出しを行う。

10

### 【0079】

（第2の実施の形態）

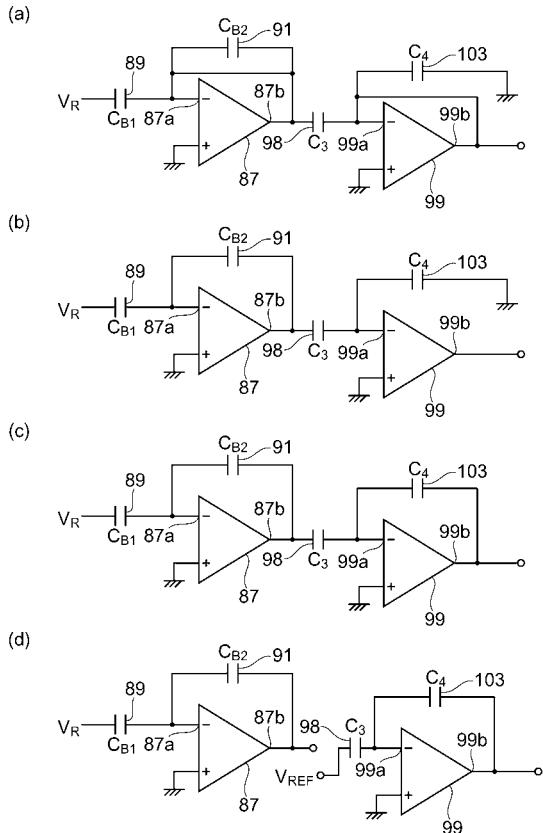

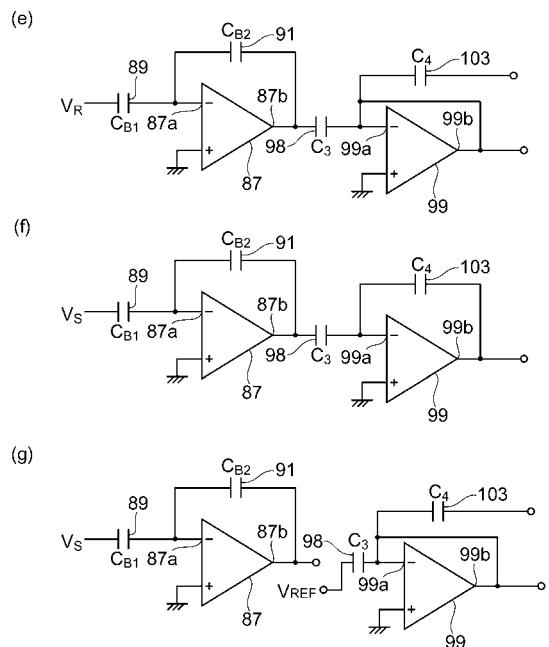

図11は、CMOSイメージセンサのための読み出し回路を概略的に示す図面である。図12は、この読み出し回路のためのタイミングチャートを示す。既に説明したように、CMOSイメージセンサの画素は、リセット状態における第1の信号と受光状態における第2の信号とを生成する。図13は、イメージセンサを示す図面である。この読み出し回路81は、プリアンプ83と、積分器85とを含む。プリアンプ83は、演算増幅回路87と、該演算増幅回路87の反転入力87aに接続された第1のキャパシタ89と、該演算増幅回路87の非反転出力87bと反転入力87aとの間に接続された第2のキャパシタ91を含む。プリアンプ83は、第1および第2のキャパシタ89、91の容量比に応じて、入力93に受けた第1の信号S1および第2の信号S2を増幅する。また、プリアンプ83は、演算増幅回路87の非反転出力87bと反転入力87aとの間に接続されたスイッチ95を含み、スイッチ95は、クロックrに応答する。演算増幅回路87の非反転入力87cは、例えば接地線といった基準電位線に接続されている。

20

### 【0080】

積分器85は、プリアンプ83の出力83aに接続された標本化スイッチ97を含み、また、増幅された第1の信号の複数回の積分を該標本化スイッチ97を用いて行うと共に増幅された第2の信号の複数回の積分を該標本化スイッチ97を用いて行うことによって、第1の信号と第2の信号との差分を増幅する。読み出し回路81によれば、増幅された第1の信号の複数回の積分を行うと共に、プリアンプ83の出力83aに積分器85の入力85aが逆極性になるように、増幅された第2の信号の複数回の積分を行うので、積分器85は、第1の信号S1と第2の信号S2との差分を示し増幅された信号を提供する。

30

### 【0081】

具体的には、積分器85では、該演算増幅回路99の反転入力99aとスイッチ97との間に第1のキャパシタ98が接続される。スイッチ97はクロック1に応答する。容量回路101が、該演算増幅回路99の非反転出力99bと反転入力99aとの間に接続される。容量回路101が、直列に接続された第2のキャパシタ103およびスイッチ105を含む。積分器85は、演算増幅回路99の非反転出力99bと反転入力99aとの間に接続されたスイッチ107を含み、スイッチ107は、クロックr2に応答する。また、容量回路101は、第2のキャパシタ103とスイッチ105との共通ノードnode3に接続されたリセットスイッチ111を含む。容量回路101は、共通ノードnode3に接続された一端を有するキャパシタ109を含み、キャパシタ109の他端は、例えば接地線といった基準電位線に接続されている。キャパシタ109は、リセットスイッチ111のスイッチングノイズの電圧依存性を低減するために役立つ。第1のキャパシタ98とスイッチ97との共通ノードnode4には、参照電圧VREFを供給するためにイッチ112が接続される。スイッチ112はクロック3に応答して動作する。

40

### 【0082】

積分器85の出力85bには、サンプル／ホールド(S/H)回路113が接続されており、S/H回路113は、保持キャパシタ115と、保持キャパシタ115の一端115aと積分器85の出力85bとの間に接続された標本化スイッチ117とを含む。保持

50

された信号は、同期スイッチ 119 を介して水平走査線 121 に接続されている。図 12 に示されたタイミングチャートのためのクロックは、クロック生成器 123 によって提供される。演算增幅回路 87、99 の非反転入力には、例えば接地電位といった基準電位が供給される。図 11 に示された読み出し回路 81 は、シングルエンド構成であるけれども、全差動構成の演算增幅回路をプリアンプおよび積分器のために用いることができる。また、積分器 85 の出力に A/D 変換器を接続して、例えば巡回 A/D 変換を行うこともできる。

#### 【0083】

図 13 は、イメージセンサ 1a のブロック図を示す。この読み出し回路 81 のアレイは、イメージセルアレイ 2 のカラムに設けられることができる。これにより、読み出し回路 81 は、簡単な回路構成によりイメージセンサの信号を低ノイズで読み出しえる。イメージセルアレイ 2 の画素 2a には、画素内電荷転送を行う方式を用いる。図 12 に示されるように、タイミングチャートは、リセットレベル積分期間  $T_R$  と信号レベル積分期間  $T_S$  とを含む。この実施例では、リセットレベル積分期間  $T_R$  は 4 つの期間  $T_{R1} \sim T_{R4}$  の各々で積分が行われ、また信号レベル積分期間  $T_S$  は 4 つの期間  $T_{S1} \sim T_{S4}$  の各々で積分が行われる。特に、リセットレベル積分期間  $T_R$  の期間  $T_{R1}$  の前半  $T_{RST}$  では、クロック  $r$  に応答して、プリアンプ 83 のリセットがスイッチ 95 を用いて行われる。期間  $T_{R1}$  の後半  $T_{SAM}$  では、標本化が行われる。本実施例では、リセットレベル積分期間  $T_R$  の期間  $T_{R4}$  は信号レベル積分期間  $T_S$  の期間  $T_{S1}$  と並列して行われる。このために、クロック 1 に応答してスイッチ 97 が期間  $T_{R4} \sim T_{S1}$  のほぼ全体にわたって導通している。信号レベル積分期間  $T_S$  では、クロック  $TX_1$  に応答して第 2 の信号  $S_2$  がプリアンプ 83 に提供される。プリアンプ 83 は、増幅された第 2 の信号  $S_2$  をクロック 1 に応答してスイッチ 97 を介してキャパシタ 98 に標本化する。リセットレベル積分期間  $T_R$  の期間  $T_{R4}$  および信号レベル積分期間  $T_S$  の期間  $T_{S1}$  では、クロック 1 のハイ期間が広くなっている。リセットレベル積分期間  $T_R$  では各期間の前半でクロック 1 はアクティブであるが、信号レベル積分期間  $T_S$  では各期間の後半でクロック 1 はアクティブである。これ故に、リセットレベル積分期間  $T_R$  での積分器 85 への積分は、リセットレベル積分期間  $T_R$  での積分器 85 への積分と逆極性に行われる。

#### 【0084】

画素 2a の第 1 の信号 (リセットレベル)  $S_1$  を出力に対して、プリアンプ 83 に標本化する。このとき、プリアンプ 83 では、リセットスイッチ 95 導通させキャパシタ 91 をリセットする。リセットの後に、リセットスイッチ 95 を開いたとき、プリアンプ 83 の出力 83a には、このリセット動作に伴うノイズが生成される。積分器 85 は、この第 1 の信号  $S_1$  を積分するために多数回の標本化を行う。

#### 【0085】

次いで、画素 2a の第 2 の信号 (信号レベル)  $S_2$  をプリアンプ 83 に加える。この信号は、プリアンプ 83 内のキャパシタ 89、91 の容量比によって増幅される。積分器 85 は、第 1 の信号  $S_1$  と第 2 の信号  $S_2$  との差を示す信号を生成する。このとき、積分器 85 は、プリアンプ 83 の出力 83a からの信号が逆極性となるように信号を多数回標本化することにより積分を行う。これらの処理の結果、積分器の出力は、プリアンプ 83 の出力 83a からの第 1 の信号  $S_1$  と第 2 の信号  $S_2$  との差を取りながら積分により増幅された信号を提供する。その積分結果を S/H 回路 113 でサンプルして記憶し、水平走査線 121 によって外部に読み出す。

#### 【0086】

次いで、多重サンプリング積分回路を用いたイメージセンサの動作を説明する。図 14 および図 15 は、多重積分読み出し回路の動作を示す図面である。図 12 に示されるタイミングチャートでは、4 回の標本化が行われているが、以下の一例の動作では、画素 2a からのリセットレベル、信号レベルに対して、それぞれ 2 回の積分を行う。引き続く説明では、第 1 および第 2 の信号  $S_1$ 、 $S_2$  として  $V_R$ 、 $V_S$  を用いる。

#### 【0087】

10

20

30

40

50

ステップ( a )では、プリアンプ 8 3 の入力 8 3 b に画素 2 a のリセットレベル信号  $V_R$  を加える。スイッチ 9 5 を介して演算增幅回路 8 7 の反転入力 8 7 a を非反転出力 8 7 b に接続して、キャパシタ 8 9 に信号  $V_R$  を標本化する。積分器 8 5 では、スイッチ 1 0 7 を導通させて演算增幅回路 9 9 の反転入力 9 9 a と非反転入力 9 9 b とを接続すると共に、クロック  $r_d$  に応答してスイッチ 1 1 1 を導通させる。これにより、キャパシタ 1 0 3 の電荷をリセットする。また、クロック 9 7 に応答してスイッチ 9 7 を導通させる。これにより、キャパシタ 9 8 の電荷をリセットする。

#### 【 0 0 8 8 】

ステップ( b )では、クロック  $r$  に応答してスイッチ 9 5 を非導通にすると共に、クロック  $r_2$  に応答してスイッチ 1 0 7 を非導通にする。キャパシタ 9 1 には、スイッチやアンプで発生した雑音成分がサンプルされ、出力 8 3 a に現れる。積分器 8 5 は、スイッチ 9 7 を介してプリアンプ 8 3 からの信号をキャパシタ 9 8 に標本化する。

#### 【 0 0 8 9 】

ステップ( c )では、積分器 8 5 のスイッチ 1 1 1 を非導通にすると共にスイッチ 1 0 5 を導通にして、キャパシタ 9 8 の電荷をキャパシタ 1 0 3 に積分する。この時、積分器 8 5 の出力には、次式の電圧が現れる。

$$V_o(1) = C_3 / C_4 \times V_{nd1}(1) + C_3 / C_4 \times C_{B1} / C_{B2} \times V_{npd}(1)$$

ここで、 $V_{nd1}(1)$ 、 $V_{npd}(1)$  は、それぞれプリアンプ 8 3 および画素 2 a のソースフォロワのノイズ成分（時間的に変動するノイズ）である。括弧内の数字は、ステップの順序に対応する。第 1 項はプリアンプ 8 3 に起因するノイズであり、第 2 項は画素 2 a に起因するノイズであり、このノイズはプリアンプ 8 3 によって増幅される。

#### 【 0 0 9 0 】

ステップ( d )では、クロック 1 に応答してスイッチ 9 7 を非導通にすると共に、クロック 3 に応答してスイッチ 1 1 2 を導通させる。積分器 8 5 のキャパシタ 9 8 に電圧  $V_{REF}$  を供給する。この電圧に対応する電荷がキャパシタ 9 8 からキャパシタ 1 0 3 へ移動する。この時、積分器 8 5 の出力には、次式の電圧が現れる。

$$V_o(1) = C_3 / C_4 \times (V_{nf1}(1) + V_{nd1}(1) - V_{REF}) + C_3 / C_4 \times C_{B1} / C_{B2} \times V_{npd}(1)$$

ここで、 $V_{nf1}(1)$  はプリアンプ 8 3 のフリーズノイズである。フリーズノイズは、キャパシタに標本化されて固定した電荷として存在し、時間的に変動しない。

#### 【 0 0 9 1 】

ステップ( e )では、クロック 2 に応答してスイッチ 1 0 5 を非導通にする。キャパシタ 1 0 3 の一端（積分器の出力に接続されるキャパシタ端子）が開放されているので、積分結果はキャパシタ 1 0 3 に保持される。また、クロック  $r_2$  に応答してスイッチ 1 0 7 を導通して、演算增幅回路 9 9 の反転入力 9 9 a を非反転出力 9 9 b に接続する。

#### 【 0 0 9 2 】

ステップ( f )では、読み出し回路 8 1 の入力 9 3 に第 2 の信号  $S_2$  を供給する。この信号  $S_2$  をプリアンプ 8 3 は増幅する。積分器 8 5 のキャパシタ 9 8 は、増幅された信号を受ける。この時、積分器 8 5 の出力には次の電圧が現れる。

$$V_o(1) = C_3 / C_4 \times (V_{nf1}(1) + V_{nd1}(1) - V_{REF} - V_{nd1}(3)) + C_3 / C_4 \times C_{B1} / C_{B2} \times (V_{npd}(1) - V_{npd}(3) + V_R - V_S)$$

#### 【 0 0 9 3 】

ステップ( g )では、クロック 1 に応答してスイッチ 9 7 を非導通にすると共に、クロック 3 に応答してスイッチ 1 1 2 を導通させる。積分器 8 5 のキャパシタ 9 8 に電圧  $V_{REF}$  を供給する。この電圧に対応する電荷がキャパシタ 9 8 からキャパシタ 1 0 3 へ移動する。この時、積分器 8 5 の出力には、次式の電圧が現れる。

$$V_o(1) = C_3 / C_4 \times (V_{nf1}(1) + V_{nd1}(1) - V_{REF} - V_{nd1}(3) - V_{nd1}(4) - V_{nf1}(1) + V_{REF}) + C_3 / C_4 \times C_{B1} / C_{B2} \times (V_{npd}(1) - V_{npd}(3) - V_{npd}(4) + 2 \times (V_R - V_S))$$

10

20

30

40

50

$$= C_3 / C_4 \times (V_{nd1}(1) - V_{nd1}(3) - V_{nd1}(4)) + C_3 / C_4 \times C_{B_1} / C_{B_2} \times (V_{npd}(1) - V_{npd}(3) - V_{npd}(4)) + 2 \times (V_R - V_S)$$

## 【0094】

これら一連の動作から、まず、プリアンプ83のフリーズノイズ成分 $V_{nf1}$ はキャンセルされる。また、N回の標本化により、入力信号( $V_R - V_S$ )がN倍に増幅される。積分により、時間変動するノイズ成分( $V_{npd}$ 、 $V_{nd1}$ )も積分されるけれども、時間変動するノイズ成分は無相関でランダムである。これ故に、N回の積分の結果、振幅で $sqr t(2 \times N - 1)$ 倍に増幅される一方で、信号成分( $V_R - V_S$ )は、信号 $V_R$ および $V_S$ それぞれN回の積分によりN倍に増幅される。

10

## 【0095】

加えて、プリアンプ83の利得(キャパシタ比 $C_{B_1} / C_{B_2}$ により決定される)を高くできるので、プリアンプ83の帯域制限の作用により、時間変動するノイズ成分は低減される。好ましくは、比 $C_{B_1} / C_{B_2}$ は8以上である。

## 【0096】

これらの2つの効果により、非常に低ノイズでの信号読み出しが可能となる。さらに、このように信号レベルおよびリセットレベルをそれぞれ多数回標本化して積分し両者の差を求める処理を行うことによって、 $1/f$ ノイズも低減される。

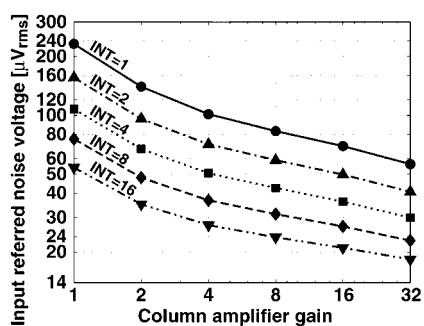

## 【0097】

図16は、ノイズ解析による見積もりを示すグラフである。図中の「INT」は積分回数を示す。図16を参照すると、プリアンプの利得が1であり、複数回の積分を行わないとき、熱ノイズおよび $1/f$ ノイズを含むトータル入力換算ノイズは $232 \mu V_{rms}$ であるけれども、プリアンプ利得が32倍であるとき、 $56.4 \mu V_{rms}$ にまで低減される。プリアンプ利得が32倍であると共に16回の積分を置こうとき、 $18.4 \mu V_{rms}$ にまで低減される。なお、変換ゲインが $60 \mu V/e$ と仮定しており、この値は等価ノイズ電子数では0.3以下に相当する。ノイズが等価電子数換算で0.3以下になれば、信号電子の数に応じて生じる離散的なレベルを大まかに識別できる。

20

## 【0098】

好適な実施の形態において本発明の原理を図示し説明してきたが、本発明は、そのような原理から逸脱することなく配置および詳細において変更され得ることは、当業者によって認識される。本発明は、本実施の形態に開示された特定の構成に限定されるものではない。したがって、特許請求の範囲およびその精神の範囲から来る全ての修正および変更に権利を請求する。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2005-269741(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00-1/88

H04N 5/378