(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4001460号

(P4001460)

(45) 発行日 平成19年10月31日(2007.10.31)

(24) 登録日 平成19年8月24日(2007.8.24)

(51) Int.C1.

F 1

|              |           |              |   |

|--------------|-----------|--------------|---|

| HO 1 J 31/12 | (2006.01) | HO 1 J 31/12 | C |

| HO 1 J 9/24  | (2006.01) | HO 1 J 9/24  | A |

| HO 1 J 29/87 | (2006.01) | HO 1 J 29/87 |   |

請求項の数 36 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-533887 (P2000-533887)  |

| (86) (22) 出願日 | 平成11年2月26日 (1999.2.26)        |

| (65) 公表番号     | 特表2002-505503 (P2002-505503A) |

| (43) 公表日      | 平成14年2月19日 (2002.2.19)        |

| (86) 國際出願番号   | PCT/US1999/004382             |

| (87) 國際公開番号   | W01999/044218                 |

| (87) 國際公開日    | 平成11年9月2日 (1999.9.2)          |

| 審査請求日         | 平成16年2月19日 (2004.2.19)        |

| (31) 優先権主張番号  | 09/032,127                    |

| (32) 優先日      | 平成10年2月27日 (1998.2.27)        |

| (33) 優先権主張国   | 米国(US)                        |

前置審査

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595168543<br>マイクロン テクノロジー、 インク。<br>アメリカ合衆国、 アイダホ州 83716<br>-9632, ポイズ, サウス フェデ<br>ラル ウエイ 8000 |

| (74) 代理人  | 100071010<br>弁理士 山崎 行造                                                                        |

| (72) 発明者  | キャセイ、 デビッド・エイ<br>アメリカ合衆国、 アイダホ州 83703<br>、 ポイズ、 ウォーターセッジ 5193                                 |

| (72) 発明者  | ブローニング、 ジミー・ジェイ<br>アメリカ合衆国、 アイダホ州 83706<br>、 ポイズ、 ペンシルバニア・ストリート、<br>エフ 814                    |

最終頁に続く

(54) 【発明の名称】 大領域F E D装置及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

所定のレベルの真空圧下において密閉されている大面積電界放出デバイス(F E D)であって、

大面積基板と、

前記基板の上に配置されたエミッタ電極構造であって、前記基板の実質的部分にわたって配置されているエミッタ電極構造と、

複数のグループのマイクロポイントであって、各グループのマイクロポイントが所定数のマイクロポイントを持ち、さらに、各グループのマイクロポイントが前記エミッタ電極構造上の離散位置に配置されているマイクロポイントと、

前記基板の上方に配置された絶縁層であって、この絶縁層を貫通し所定の範囲内の直径を持つ開口を持ち、この開口がマイクロポイントの少なくとも一部を囲む絶縁層と、

前記絶縁層上に配置された抽出構造であって、この抽出構造を貫通し所定の範囲内の直径を持つ開口を持ち、この開口がマイクロポイントの少なくとも一部を囲み、さらに、前記抽出構造内の前記開口が前記絶縁層内の前記開口と整列する抽出構造と、

前記抽出構造の上方に配置され、前記抽出構造から離隔されていて、光の所定の波長を透過させるフェースプレートと、

前記抽出構造に向かって前記フェースプレートの表面上に配置された第1導電層と、

第1導電層の上に配置されたマトリクス部材であって、ピクセル領域として機能する第1導電層表面の領域を画定し、前記ピクセル領域が、マイクロポイントのグループのマイ

10

20

クロポイントと整列するマトリクス部材と、

複数のピクセル領域内の前記第1導電層上に配置されたカソード発光材料であって、特定のピクセル領域にあるカソード発光材料が、前記ピクセル領域に関連するマイクロポイントから放出された電子を受け取るように整列するカソード発光材料と、

所定の位置にある前記フェースプレートと前記抽出構造との間に配置された複数のスペーサであって、前記FED内の前記真空圧によって引き起こされ、前記スペーサが遭遇する応力に対応する高さを持つスペーサとを備え、前記FEDの中央領域に近い少なくとも1つのスペーサは前記FEDの側壁に近い位置のスペーサの高さよりも大きな高さを有するデバイス。

【請求項2】

請求項1のデバイスにおいて、前記FEDの対角線方向のスクリーン寸法が25cm以上であるデバイス。

【請求項3】

請求項1のデバイスにおいて、前記抽出構造は電気的伝導性物質の連続層を含むデバイス。

【請求項4】

請求項1のデバイスにおいて、前記抽出構造は電気的に結合された複数の離隔部材を含むデバイス。

【請求項5】

請求項1のデバイスにおいて、前記マイクロポイントは低仕事関数の物質で被覆されているデバイス。 20

【請求項6】

請求項5のデバイスにおいて、前記低仕事関数の物質はセシウムを含むデバイス。

【請求項7】

請求項1のデバイスにおいて、前記スペーサは前記FED内で所定のパターンに配置されているデバイス。

【請求項8】

請求項1のデバイスにおいて、少なくとも1つのマイクロポイントは前記エミッタ電極構造上に四角形のパターンで配置されているデバイス。

【請求項9】

請求項1のデバイスにおいて、前記第1導電層はインジウムスズ酸化(ITO)層を含むデバイス。 30

【請求項10】

所定のレベルの真空圧下において密閉されている大面積電界放出デバイス(FED)であつて、

大面積基板と、

前記基板の上に配置されたエミッタ電極構造であって、前記基板の実質的部分にわたつて配置されているエミッタ電極構造と、

複数のグループのマイクロポイントであって、各グループのマイクロポイントが所定数のマイクロポイントを持ち、さらに、各グループのマイクロポイントが前記エミッタ電極構造上の離散位置に配置されている複数のグループのマイクロポイントと、 40

前記基板の上方に配置された絶縁層であって、前記絶縁層を貫通し所定の範囲内の直径を持つ開口を持ち、前記開口がマイクロポイントの少なくとも一部を囲む絶縁層と、

前記絶縁層上に配置された抽出構造であって、前記抽出構造を貫通し所定の範囲内の直径を持つ開口を持ち、前記開口がマイクロポイントの少なくとも一部を囲み、さらに、前記抽出構造内の前記開口が前記絶縁層内の前記開口と整列する抽出構造と、

前記抽出構造の上方に配置され、前記抽出構造から離隔されていて、光の所定の波長を透過させるフェースプレートと、

前記抽出構造に向かって前記フェースプレートの表面上に配置された第1導電層と、

前記第1導電層の上に配置されたマトリクス部材であって、ピクセル領域として機能す 50

る前記第1導電層表面の領域を画定し、前記ピクセル領域が、マイクロポイントのグループのマイクロポイントと整列するマトリックス部材と、

複数のピクセル領域内の前記第1導電層上に配置されたカソード発光材料であって、特定のピクセル領域にあるカソード発光材料が、前記ピクセル領域に関連するマイクロポイントから放出された電子を受け取るように整列するカソード発光材料と、

所定の位置にある前記フェースプレートと前記抽出構造との間に配置された複数のスペーサであって、前記FED内の前記真空圧によって引き起こされ、前記スペーサが遭遇する応力に対応する断面形状を持つ複数のスペーサとを備え、前記FEDの中央領域に近い少なくとも一つのスペーサの高さは、前記FEDの側壁に近い位置における前記スペーサの高さよりも高いデバイス。

10

【請求項11】

請求項10記載のデバイスにおいて、前記FEDの対角スクリーンサイズが、25cm以上であるデバイス。

【請求項12】

請求項9記載のデバイスにおいて、前記抽出構造が、導電材料の連続層を含むデバイス。

【請求項13】

請求項10記載のデバイスにおいて、前記抽出構造が、電気的に接続された複数の離間した部材を含むデバイス。

【請求項14】

請求項10記載のデバイスにおいて、前記マイクロポイントが、低仕事関数材料で被覆されているデバイス。

20

【請求項15】

請求項14記載のデバイスにおいて、前記低仕事関数材料が埋設されたセシウムを含むデバイス。

【請求項16】

請求項10記載のデバイスにおいて、前記スペーサが前記FED内に所定のパターンで配置されているデバイス。

【請求項17】

請求項16記載のデバイスにおいて、少なくとも一つのスペーサが、「+」字状断面形状を有するデバイス。

30

【請求項18】

請求項16記載のデバイスにおいて、少なくとも一つのスペーサが、「L」字状断面形状を有するデバイス。

【請求項19】

請求項16記載のデバイスにおいて、少なくとも一つのスペーサが、矩形断面形状を有するデバイス。

【請求項20】

請求項16記載のデバイスにおいて、少なくとも一つのスペーサが、「Iビーム」状断面形状を有するデバイス。

【請求項21】

請求項10記載のデバイスにおいて、マイクロポイントの少なくとも一つのグループが、エミッタ電極構造上に矩形パターンで配置されているデバイス。

40

【請求項22】

請求項10記載のデバイスにおいて、第1導電部材がインジウム錫酸化(ITO)層を含むデバイス。

【請求項23】

所定レベルの負圧下で封止された広領域電界放出デバイス(FED)の下部区画を広領域FEDの上部区画へ形成且つ結合させる方法であり、前記FEDの前記上部区画が、フェースプレートと、このフェースプレートの面上に配置された第1導電層と、この第1導電層の面上に配置されたマトリックス部材と、このマトリックス部材により覆われていない

50

領域における第1導電層上に配置されたカソード発光材料とを含む方法であって、

- (a) 所定の大きさの基板を形成する段階と、

- (b) 前記基板上にエミッタ電極構造を形成する段階と、

- (c) 前記エミッタ電極構造上にグループをなして形成されるように、前記エミッタ電極構造上に所定の高さ範囲で複数のマイクロポイントを形成する段階と、

- (d) 前記マイクロポイントを低仕事関数材料で被覆する段階と、

- (e) 前記基板、エミッタ電極構造、及び複数のマイクロポイント上に第1絶縁層を被着させる段階と、

- (f) 前記絶縁層上に第2導電層を被着させ、前記絶縁層と第2導電層との組合せ高さを少なくとも、最も高い被覆されたマイクロポイントと同じ高さにさせる段階と、

- (g) 前記絶縁層と第2導電層との組合せの厚さを前記FEDに亘って実質的に均一にさせる調節研磨段階と、

- (h) 前記被覆されたマイクロポイントを露呈させるように第2導電層及び前記絶縁層を貫通して開口をエッチングし、その開口の側壁を前記マイクロポイントから離間させる段階と、

- (i) 前記FEDの前記上部区画と前記下部区画との間に複数のスペーサを配置して前記上部区画と下部区画との間に所定の間隔を与え、前記スペーサは、それに加わる応力に比例する高さを有する段階とを含む方法。

【請求項24】

請求項23記載の方法において、前記調節研磨段階が化学的機械研磨を含む方法。

【請求項25】

請求項23記載の方法において、前記調節研磨段階が湿化学的エッチングを含む方法。

【請求項26】

請求項23記載の方法において、前記スペーサが前記FEDの前記上部区画と前記下部区画との間のパターンに配置されている方法。

【請求項27】

所定レベルの負圧下で封止された広領域電界放出デバイス(FED)の下部区画を広領域FEDの上部区画へ形成且つ結合させる方法であり、前記FEDの前記上部区画が、フェースプレートと、このフェースプレートの面上に配置された第1導電層と、この第1導電層の面上に配置されたマトリックス部材と、このマトリックス部材により覆われていない領域における第1導電層上に配置されたカソード発光材料とを含む方法であって、

- (a) 所定の大きさの基板を形成する段階と、

- (b) 前記基板上にエミッタ電極構造を形成する段階と、

- (c) 前記エミッタ電極構造上にグループをなして形成されるように、前記エミッタ電極構造上に所定の高さ範囲で複数のマイクロポイントを形成する段階と、

- (d) 前記マイクロポイントを低仕事関数材料で被覆する段階と、

- (e) 前記基板、エミッタ電極構造、及び複数のマイクロポイント上に第1絶縁層を被着させる段階と、

- (f) 前記絶縁層上に第2導電層を被着させ、前記組録層と第2導電層との組合せ高さを少なくとも、最も高い被覆されたマイクロポイントと同じ高さにさせる段階と、

- (g) 第2導電層の第1面を実質的に滑らかで平坦な第1面にする調整された研磨をなし、前記絶縁層と第2導電層との組合せの厚さを前記FEDに亘って実質的に均一にさせる調節研磨段階と、

- (h) 前記被覆されたマイクロポイントを露呈させるように第2導電層及び前記絶縁層を貫通して開口をエッチングし、その開口の側壁を前記マイクロポイントから離間させる段階と、

- (i) 前記FEDの前記上部区画と前記下部区画との間に複数のスペーサを配置して前記上部区画と下部区画との間に所定の間隔を与え、前記スペーサは、それに加わる応力に比例する断面形状を有する段階とを含む方法。

【請求項28】

10

20

30

40

50

請求項 2 7 記載の方法において、前記調節研磨段階が化学的機械研磨を含む方法。

【請求項 2 9】

請求項 2 7 記載の方法において、前記調節研磨段階が湿化学的エッティングを含む方法。

【請求項 3 0】

請求項 2 7 記載の方法において、前記スペーサが前記 F E D の前記上部区画と前記下部区画との間のパターンに配置されている方法。

【請求項 3 1】

請求項 1 記載のデバイスにおいて、前記電子放出源が低仕事関数材料に被覆されているデバイス。

【請求項 3 2】

請求項 1 0 記載のデバイスにおいて、前記電子放出源が低仕事関数材料に被覆されているデバイス。

【請求項 3 3】

請求項 2 3 記載の方法において、前記マイクロポイントが低仕事関数材料に被覆されている方法。

【請求項 3 4】

請求項 2 7 記載の方法において、前記マイクロポイントが低仕事関数材料に被覆されている方法。

【請求項 3 5】

請求項 1 記載のデバイスにおいて、前記デバイスの前記抵抗/キャパシタンス (R C) 時間が  $1 \mu s$  を含むデバイス。

【請求項 3 6】

請求項 1 0 記載のデバイスにおいて、前記デバイスの前記抵抗/キャパシタンス (R C) 時間が  $1 \mu s$  を含むデバイス。

【発明の詳細な説明】

【0 0 0 1】

政府権利

本発明は、アドヴァン・ストリサーチプロジェクトエージェンシー (A P R A) に与えられた契約番号第 D A B T 6 3 - 9 3 - C - 0 0 2 5 号の元になされた。政府は本発明の一定の権利を有する。

【0 0 0 2】

【産業上の利用分野】

本発明はフィールドエミッション装置 (F E D s) に関する。特に、本発明は、大領域 F E D 構造体及びそのような構造体の製造に関する。

【0 0 0 3】

【発明の背景】

最近コンピュータ及びその他の業界においては、フラットパネルディスプレを製造する優勢な技術は液晶ディスプレ (L C D s) 技術であり、また、現基準 (ベンチマーク) は、マトリックス L C D s である。A M L C D 技術を用いて製造されたフラットパネルディスプレの欠点は、コスト、電力消費、視野角度早く移動するビデオ画像の汚れ、動作温度範囲及び A M L C D のバックライトに水銀蒸気を用いる環境問題である。

【0 0 0 4】

対抗技術は陰極管 (C R T) 技術である。この技術領域では、実際的な平坦 C R T を開発するため過去 40 年において多くの試みがなされてきた。フラット C R T の開発では、光発生のために処理によって与えられる利点を用いることが望まれてきた。フラット C R T 開発の失敗の要點は、実際的なエレクトロンソース及び機械的構造の開発における複雑性が中心である。

【0 0 0 5】

近年における F E D 技術は、低電力、フラットパネルディスプレの開発技術を志向している。F E D 技術は、エレクトロンビームを可視光線に能率的にエネルギー変換するために

10

20

30

40

50

冷カソードエミッタ及び陰極冷光発生蛍光体のアレイを用いる点で有利である。フラットパネルディスプレ開発のためにF E D技術を用いる希望の一部は、それが高性能、低電力及び軽重量のフラットスクリーンディスプレを製造するために非常に生産的であるからである。フラットパネルディスプレの代わりに入手可能になったF E D技術と関連する最近の特定利点の中には、大領域1ミクロンリトグラフィ、大領域薄膜処理能力、電子放射マイクロポイントに関する高チップ密度、横方向抵抗層、新型のエミッタ構造体、材料及び低電圧蛍光体等がある。

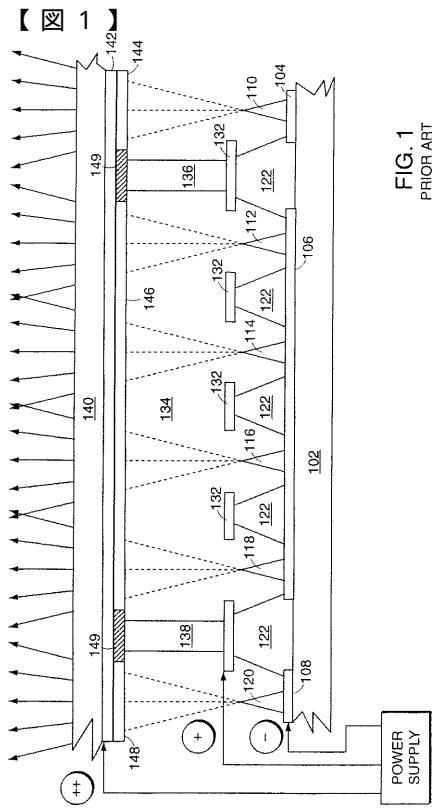

#### 【0006】

図1を参照すると、先行技術F E Dの代表的断面は、概して100で示される。周知の通りF E D技術は、主として冷カソードフィールドエミッション電子によって励起される陰極冷光発生蛍光体に基づき作動する。F E Dの一般的構造は、上方に薄い伝導層が堆積されるシリコン基盤、即ち、シリコンベースプレート102を含む。シリコンベースプレート102は、単一結晶シリコン層であり得る。

10

#### 【0007】

薄い伝導構造は、従来の方法でシリコンベースプレート102上に堆積される不純物添加された多結晶シリコンから形成され得る。この薄い伝導構造体は、エミッタ電極として役立つ。通常薄い伝導構造体は、電気的に接続されるストリップの形でシリコンベースプレート102上に堆積される。図1では、ストリップ104、106及び108の断面が示される。特定の装置に関するストリップ数は、F E Dのサイズ及び所望の作動に依存するであろう。

20

#### 【0008】

それぞれのエミッタ電極ストリップの予定位置には、隔置されたマイクロポイントのパターンが形成される。図1では、マイクロポイント110がストリップ104上に、マイクロポイント112、114、116及び118がストリップ106上に、マイクロポイント120がストリップ108上に示される。マイクロポイントのパターンに関しては、ストリップ106上には、マイクロポイント112、114、116及び118を含む16マイクロポイントの正方形パターンがその位置に堆積され得る。しかし、1つ又はそれ以上のマイクロポイントパターンが任意の場所に配置され得ることが理解される。マイクロポイントは、特定のパターンよりはむしろ無作為にも配置され得る。

30

#### 【0009】

各マイクロポイントは逆コーン（円錐）状であることが望ましい。各マイクロポイントの形成及び整形は、従来の方法でなされる。マイクロポイントは、例えば、シリコン又はモリブデンのような多数の材料で製造し得る。さらに、マイクロポイントの最適性能を保証するためにマイクロポイントのチップは低仕事関数材料量で被覆又は処理され得る。

#### 【0010】

その代わりに、構造体基盤、エミッタ電極及びマイクロポイントは以下の方法で形成され得る。単一結晶シリコン基盤はP型又はN型材料から製造され得る。次いで基盤は、基盤内に一連の細長い平行に伸びるストリップを形成するために、従来の方法で処理され得る。ストリップは事実上基盤のものとは逆の伝導型のウエル（空所）である。もし基盤それ自体がP型ならば、ウエルはN型でありその逆もある。ウエルは電気的に接続されF E D用のエミッタ電極を形成する。各伝導ウエルは、予定の幅及び深さ（それで基盤内に駆り立てられる）を有する。ストリップの数及び間隔は、基盤上に形成されるべきフィールドエミッションカソード位置の所望のサイズに合致するように決定される。ウエルは、それをおおってマイクロポイントが形成される場所である。ストリップを形成するために2方法のいずれかが用いられるかにかかわらず、結果的に得られる平行な伝導ストリップは、エミッタ電極として役立ちかつマトリックス構造体の列を形成する。

40

#### 【0011】

エミッタ電極を形成する2方法のいずれかが用いられた後絶縁層122が、エミッタ電極104、106、108及びストリップ上の予定の場所に配置されるマイクロポイントをおおって堆積される。絶縁層は、2酸化ケイ素（SiO<sub>2</sub>）のような誘電材料で作られ得

50

る。

**【 0 0 1 2 】**

伝導層は、絶縁層 122 をおおって堆積される。この伝導層は、抽出構造 132 を形成する。抽出構造 132 は、低電位電極であり、マイクロポイントから電子を引き出すために用いられる。抽出構造 132 は、クロム、モリブデン又は不純物添加ポリシリコン又はケイ化ポリシリコンで作られる。抽出構造 132 は、連続層又は平行ストリップとして形成され得る。もし、平行ストリップが抽出構造 132 を形成するならば、それは抽出グリッドと称され、ストリップはエミッタ電極ストリップ 104, 106 及び 108 と垂直に堆積される。抽出構造 132 を形成するために用いられるときには、ストリップはマトリックス構造の列をなす。連続層又はストリップのいずれが用いられるかにかわらず、一度いずれかが絶縁層上に堆積されると、マイクロポイントを囲むが、マイクロポイントから隔置されるように従来の方法で適切に腐食される。10

**【 0 0 1 3 】**

抽出及びエミッタ電極ストリップの各交差点又はエミッタ電極ストリップに沿った所望の位置において、連続抽出構造が用いられるとき、マイクロポイント又はそれらのパターンがエミッタストリップ上に堆積される。各マイクロポイント又はそれらのパターンは、スクリーンディスプレの 1 ピクセルが照射されることを意味する。

**【 0 0 1 4 】**

上記方法のいずれかにより、一度 FED の低部分が形成されると、フェースプレート 140 が、抽出構造 132 頂面上方に予定距離で固定される。概して、この距離は数百ミクロンである。この距離は、従来の方法で形成されるスペーサによって維持され得る。同スペーサは、以下の特性を有する。1) アノード(フェースプレート 140)及びカソード(エミッタ電極 104, 106, 108)間の電気的絶縁破壊を避けるために非伝導性又は抵抗性であ、2) 機械的に強く変形しにくく、3) 電子衝撃(低 2 次的放射量)下で安定、4) 500 程度の高焼結温度に耐えることが可能で、5) FED 作動と干渉しない程度に十分小さい。代表的スペーサ 136 及び 138 が図 1 に示される。20

**【 0 0 1 5 】**

フェースプレート 140 は、カソード冷光発生スクリーンであり、透明ガラス又は他の適切な材料から作られる。インジウム酸化錫(ITO)のような伝導材料は、抽出構造に面するガラス表面上に堆積される。ITO 層 142 は、FED のカソードとして役立つ。フェースプレート 140 及びベースプレート 102 間の領域 134 は高真空が保たれる。30

**【 0 0 1 6 】**

ブラックマトリックス 149 は、抽出構造 132 に面する ITO 層 142 の表面上に堆積される。

**【 0 0 1 7 】**

ブラックマトリックス 149 は、FED スクリーンディスプレイ用の個別ピクセル領域を定める。蛍光材料は、ブラックマトリックス 149 によって定められる適切な領域内の ITO 層 142 上に堆積される。ピクセルを定める代表的な蛍光材料は、144, 146 及び 148 で示される。ピクセル 144, 146 及び 148 は、蛍光材料が励起されることを意味するマイクロポイント又はそれらのグループがそのピクセルと整列されるように、抽出構造 132 の開口と一直線をなすようにされる。酸化亜鉛は、低エネルギー電子によって励起されるので、蛍光材料用の適切な材料である。40

**【 0 0 1 8 】**

1FED は、1つ又はそれ以上の電圧源を有し、それは FED の適切な作動のために、電極ストリップ 104, 106, 108、抽出構造 132 及び ITO 層 142 を 3 つの異なった電位に保つ。電極ストリップ 104, 106, 108 は「-」電圧に、抽出構造 132 は「+」電圧にかつ ITO 層 142 は「++」電圧に保たれる。このような電気的関係を用いると、抽出構造 132 はマイクロポイント 110, 112, 114, 116, 120 から電子放射流れを引き出し、その後 ITO 層 142 が自由化された電子を引き付ける。

**【0019】**

マイクロポイントのチップから発する電子放射流れは、それぞれのチップから円錐状に広がる。電子のあるものは蛍光体を90度でフェースプレートに打ち付けると同時にその他のものは各種の鋭角でそれを打ち付ける。

**【0020】****【発明が解決すべき課題】**

すぐ上で述べたFEDの基本的構造は、スクリーンの対角線サイズが5インチ未満ならスペーサを含まない。スクリーンサイズが5インチを超えると、エミッタ電極及びFED上への大気圧力下にあるフェースプレート間の正しい分離を維持するためにスペーサが必要とする。FED装置のサイズが増すにつれて、スペーサの必要性も増し、この分離を適切に維持するようにされる。スペーサの使用に代わるもののは、厚いガラスを用いることである。しかし、この厚いガラスは重くかつ高価である。

10

**【0021】**

スクリーン対角線サイズが1-5インチの小領域FED構造体の製造では、基盤上に配置される絶縁及び伝導層の厚さの実質的均一性を達成するか若しくは絶縁及び伝導層の開口内のエミッタ電極上に実質的に均一なマイクロポイントを形成するまでの困難性は殆どない。従来の堆積及び腐食技術がこのような製造に用いられてきた。これは、約8インチまでの対角線サイズを有するFEDに関してはこれまで概して真実であった。しかし、FEDの対角線サイズが8インチを超えるにつれて、以下に述べるスピンド(Spindt)処理によって均一なマイクロポイントを形成する上でこれまでかなりの困難性があった。

20

**【0022】**

上記問題及び困難性が何故存在するかについては各種の理由がありかつ大領域FEDに関しては所望のデザイン目標が達成されていなかった。大半の理由は、多数の開口を腐食しかつマイクロポイントと整列させる場合及び形成されるべきマイクロポイントが多数ある場合には、小領域FEDの製造を可能にする製造技術では不幸にして成功しないことがある。他の理由は、大領域FEDで高品質高解像度画像の製造を可能にするのに要する適切な特性を持たせるようなマイクロポイントが形成されないことがある。さらなる理由は、もし現技術が用いられるなら、製造コストが高いことである。なおさらなる理由は、大領域FEDの不適切な構造及びスペーサの配置である。これらの問題は、FEDが単色、256グレイスケール又はカラーであるかどうかにかかわらず存在する。

30

**【0023】**

必要な均一性及び性能を有するより安いFED構造体(基盤、絶縁、伝導層及びマイクロポイントから成る)を製造する試みは、多くの先行処理方法に頼ってきた。最良と考えられる処理は、1960年代の半ばに開発されたスピンド処理である。この処理が、高品質、高解像度画像を生成するマイクロポイント構造体の形成のための大領域FEDを製造するために用いられることが試みられてきた。この処理は、絶縁層をおおう伝導層の表面上に薄いモリブデンフィルム(膜)を堆積させることを要する、方向性モリブデン蒸発処理を用いる。このフィルムは、伝導及び絶縁層内に作られる開口直径より大きい厚さを有するのが望ましい。モリブデン処理によると、伝導及び絶縁層内の開口はモリブデンで閉じられ、次いでマイクロポイントが堆積されたモリブデンから開口内に形成される。即ち、マイクロポイントは、従来の処理段階によって伝導層の表面及び該空所内から不要なモリブデン材料を除去することによって形成される。これは希望的に、伝導及び絶縁層内の開口と整列される基盤上の実質的に均一なモリブデンコーンを残すであろう。しかし、この全処理は、堆積された薄膜の均一性及び腐食処理の精度に依存する。しかし、事実であったように、この処理は小領域FEDにとっては十分であるが、大領域に及ぶマイクロポイント形成の不均一性及び不整列の高百分率のために大領域FEDにとっては全く不十分である。

40

**【0024】**

FEDの対角線スクリーンサイズが10インチを超えて増えるにつれて、高品質、高解像度画像を有するFEDを生成する現技術でははっきりした問題がある。さらに、大領域F

50

FEDが適切に作動ためには抵抗/コンデンサ(RC)時間を克服する問題もある。これは、エミッタ電極によって形成される大コンデンサを充電するために比較的長い時間期間及び抽出構造をとるからである。

#### 【0025】

現技術の他の問題は、大領域FEDで用いられるべきスペーサである。ディスプレイが10インチを超えて増大すると、電極間に適切な間隔を維持する上で困難性がある。この問題を解決するために、フェースプレート及びエミッタ電極間をさらに広げ、所望の低電圧よりはむしろ2-6kVの増大されたアノード電圧を用いる欲求がある。このような装置では、空間間隔を維持するために大直径スペーサが用いられる。

#### 【0026】

代替案は、透明ガラス球を用いることであった。これは、より低いアノード電圧及びより小さいフェースプレート及びエミッタ電極間間隔の使用を可能にするのに十分であった。しかし、ガラス球のベース対高さ比の理由で、これらのスペーサの使用はFED解像度上の不利な影響があった。大きなガラス球を用いると、マイクロポイントから放射された電子のいくらかは、蛍光体ピクセル要素よりはむしろ球と接触する。これは、多くの電子が望まれていた画像部分の生成に用いられないであろう。ガラス球の使用は、使用され得るアノード電圧の量をも限定するであろう。さらに、ガラス球が用いられて低アノード電圧が印加されると、FEDの電力消費は、劇的に増大し、これは極めて望ましくない。他方、もし高アノード電圧がガラス球と共に用いられるなら、ガラス球は破壊されるであろう。

10

#### 【0027】

大領域FED内で用いる他の提案スペーサは、長い紙製の薄いスペーサであった。これらのスペーサは、250-500ミクロンの高さで、30-50ミクロンの厚さである。そのようなスペーサは、FEDの最狭側面の前兆に亘って伸びるであろう。これらのスペーサは、セラミックストリップから作られ、かなりもろい。容易に理解されるように、FEDスクリーンディスプレイの対角線寸法が増すにつれて、エミッタ電極及びフェースプレートを取り付けかつ整列させるか若しくは高真空中でアノード及びカソード間の分離を維持するためにセラミックスペーサが用いられる可能性は低下するであろう。

#### 【0028】

大領域FED内で能率的に作動することを可能にする構造体を持つ欲求がある。このような構造で作られる大領域FEDは、対角線スクリーンサイズが10インチ以上のものである。

20

#### 【0029】

##### 【発明の概要】

本発明は大面積FED及びその製造方法に関する。本発明の大面積FEDはスクリーンの対角寸法が10インチ以上のものをいう。

#### 【0030】

本発明の大面積FEDは、内部にエミッタ電極が形成される物質を有する。エミッタ電極は電気的に接続された多数の離間した平行な要素からなる。エミッタ電極を形成するこれらの要素は大面積FEDを横切る1つの方向に延伸する。平行な離間した要素の幅、数及び間隔はFEDに要求される要素に応じて決定される。

30

#### 【0031】

エミッタ電極の所定の位置において(この位置にピクセルを位置させる)、1又は2以上のマイクロポイントが形成される。これらのマイクロポイントは1μmの範囲の高さを有する。これらのマイクロポイントはエッチングによって形成される。これらのマイクロポイントは、大面積FEDのパフォマンスを大きく改善するように低ワーク機能材料で被覆された先端を少なくとも有する。大面積FEDにおいては、各位置において一般にマイクロポイントのパターンが存在する。

40

#### 【0032】

堆積、着床その他の適当な方法によってマイクロポイント上に置かれる低ワーク機能材料

50

は大面積 F E D の作動電圧を低くしつつ消費電力を減らす。形成プロセスにおける多様なステップのどのステップにおいてもマイクロポイントを被覆することができることもまた理解される。例えば、マイクロポイントは、陰極の完成の後に、イオン着床又は堆積といつたいかなる適当な方法によって被覆される。

#### 【 0 0 3 3 】

低ワーク機能材料はまた全大面積 F E D を横切るマイクロポイント間でより均一なパフォーマンスを与える。サーメット ( C r<sub>3</sub> S i + S i O<sub>2</sub> ) 、セシウム、ルビジウム、タンタル窒化膜、バリウム、クロムシリサイド、チタンカーバイドとニオブが使用できる低ワーク機能材料である。

#### 【 0 0 3 4 】

エミッタ電極要素上の被覆されたマイクロポイントは絶縁層及び導電層によって被覆される。これらの 2 つの層は組み合わされたとき最も高いマイクロポイントよりも大きな高さを有する。大面積 F E D のこの低い方の部分は、マイクロポイントと、導電層の表面の平らな肩によって生じるトポロジーを磨くために次に C M P プロセスを受ける。磨き終えた後、導電層と絶縁層は湿式化学エッティングを受けて、マイクロポイントを露出させるために導電層及び絶縁層の部分が取り除かれる。湿式化学エッティングは非常に制御しやすいプロセスであり、絶縁層と導電層の開口に関して所望の効果を保証することができる。湿式化学エッティングが一旦完了すると、導電層と絶縁層の開口はマイクロポイントに対して自己整合する。このプロセスはまた、物質上に形成されたマイクロポイントが一旦露出されるとそれらのサイズと形状を維持することを許容する。なぜならば、プロセスは露出しているマイクロポイントのいかなる部分をもエッティングしないからである。

10

#### 【 0 0 3 5 】

表面板が抽出構造の上に間隔をもって置かれる。表面版は透明なカソード発光スクリーンである。表面板は、観察者が見ることができるカソード発光光子の光を伝達することができる。

#### 【 0 0 3 6 】

表面板の底面に I T O 層が置かれる。I T O 層は電導性である。I T O 層はカソード発光光子からの光を透過させることができ F E D のアノードとして働く。

#### 【 0 0 3 7 】

ピクセル領域は I T O 層の表面の底部に形成される。各ピクセルはマイクロポイントのパターンと協働する。ピクセル領域はその内部に好ましいパターンで堆積した蛍光体材料を有する。作動の間に、蛍光体材料は低エネルギー電子によって励起される。

30

#### 【 0 0 3 8 】

ピクセルはブラックマトリックスによって分割される。ブラックマトリックスは光の伝達に対して不透明、かつ、電子の衝突によっては影響されない材料からなる。

#### 【 0 0 3 9 】

表面板は基板から所定距離離間している。この距離はスペーサによって確保される。好ましくは、表面板と基板との間の領域は高い真空中である。スペーサはそれが大面積 F E D の縁または中央領域に近い位置にあるかに依存して異なる高さを持つことができる。このようにスペーサを混ぜることにより、F E D 内の高真空中を考慮に入れて、表面板と基板との間の距離をほぼ均一に維持することができる。スペーサは、それにより大面積 F E D を効果的に区分けするようなパターンとしてまた構成される。更に、スペーサは、大面積 F E D 内の高真空中で表面板と基板との間の距離を適正に維持することを目的とする多様な断面形状を持つことができる。

40

#### 【 0 0 4 0 】

上に説明したように、大面積 F E D に関する本発明は次のものによって特徴づけられる。

( 1 ) 基板及び絶縁層上に置く導電層を均一にする C M P プロセスを使用すること、( 2 ) 導電層とアノードとの間に所望の均一なギャップを維持するようにスペーサを適当に使用すること(このことは高解像を達成することに役立つ)、( 3 ) マイクロポイントが低機能材料の被覆または着床を持つようにすること、( 4 ) F E D の接続ラインは低い抵抗

50

、低キャパシタンスであること。

【0041】

本発明の目的は、高品質の高解像イメージを作る大面積FED構造を提供することにある。

【0042】

本発明の他の目的は、比較的低アノード電圧で作動し低消費電力の大面積FEDを提供することにある。

【0043】

本発明の更に別の目的は、各マイクロポイントを囲む導電層と絶縁層に自己整合開口を作るために、堆積、化学機械式磨き(Chemical Mechanical Polishing:「CMP」)プロセス及び湿式化学エッティングを使用する大面積FEDを提供することにある。 10

【0044】

本発明の更に別の目的は、カソードアドレスラインに最も低い抵抗及びキャパシタンスを維持することにある。

【0045】

本発明の更に別の目的は、大面積FED内が高真空であるときに表面板と基板との距離をほぼ均一に維持するために異なる高さと形状を有するスペーサを使用する大面積FEDを提供することにある。

【0046】

これらの目的及びその他の目的は明細書の残りの部分で図面に言及しながら詳しく語られる。 20

【0047】

【発明の好ましい実施の形態】

本発明は、10インチ以上の対角スクリーン寸法を有する大面積FEDに関する。本発明はまた、10インチ以上の対角スクリーン寸法を有する大面積FEDを製造する方法を含む。

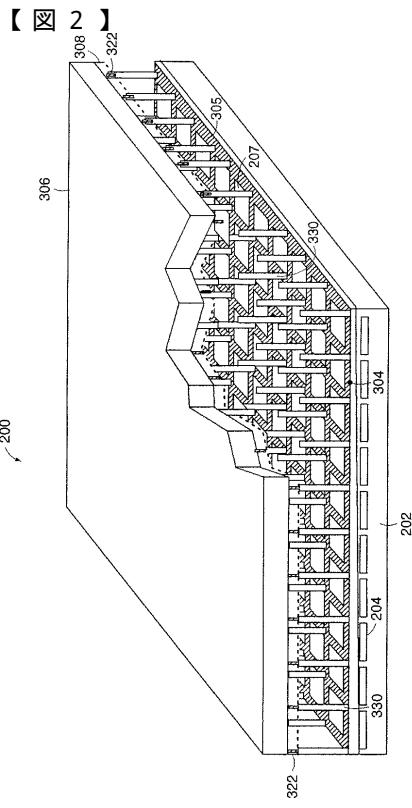

【0048】

図2に言及すると、本発明の大面積FEDの一部を番号200で示す。図2に示す一部は大面積FEDの中心に近いところのものである。図2に示すように、基板202はその内部またはその上部に形成されたエミッタ電極204を有する。一般にエミッタ電極204は、電気的に接続された多数の離間した平行な要素からなる。図2に示すように、大面積FEDにおいてエミッタ電極が覆わなければならない領域を与えるようにエミッタ電極をストリップ(帯)形状に形成することは特に有用である。平行な離間する要素の幅、数及び間隔は、例えば、解像度または対角スクリーン寸法といったような、FEDに要求される要素によって決定される。 30

【0049】

好ましくは、基板202はその上に堆積されたエミッタ電極204を有する。エミッタ電極204は本発明のFEDのカソードコンダクタである。要素またはストリップの使用は本発明の大面積FEDのRC回数を減少させるので、基板全体を覆う連続エミッタ電極よりも、十分に離間した平行な電極を使用するほうが好ましい。基板は単一構造とすることもでき、あるいは、横に配設された多数の部分から作ることもできる。本発明を実施するためにいずれの基板を用いることができる。 40

【0050】

上にピクセルが位置するエミッタ電極204上の所定位置において、エミッタ電極204上に1または2以上のマイクロポイントが形成される。これらのマイクロポイントはエミッタ電極204上に形成され、そして、それぞれが改良動作のための低ワーク機能材料コーティングを有する。好ましい実施の態様はマイクロポイントを形成するためにフォトリソグラフィを使用するが、マイクロポイントを形成するために、例えば、ミクロ球面又はビートといったランダムチップ形成プロセスのような他の方法を用いることもでき、それも本発明の範囲内である。 50

**【0051】**

エミッタ電極要素上に置かれたマイクロポイントは、 $1 \mu m$ の範囲の高さを有する背の高いマイクロポイントである。好ましくは、これらの背の高いマイクロポイントは従来技術のエッチングプロセスによって形成され、次に、本発明に従いマイクロポイント上に低ワーク機能材料コーティングが置かれる。これに続いて、エミッタ電極及び該電極上に被覆されたマイクロポイントを有する基板は、本発明による堆積、CMPプロセス及び湿式化学エッチング法による処理を受ける。この方法は、エミッタ電極要素上に形成されたマイクロポイントがそれらのサイズ及び鮮鋭度を維持し、かつ、本発明の大面積FEDにおける動作において改善されたパフォマンスを有することを許容する。マイクロポイントは形成プロセルの多様なステップのどのステップにおいてもコーティングできることが理解される。例えば、マイクロポイントは、カソードの完成後に、イオン着床又は堆積のようないかなる適当な方法によってコーティングされる。10

**【0052】**

大面積FEDに必要な高解像度を得るために、所定位置においてエミッタ電極要素上に形成されたマイクロポイントのパターンが存在する。例えば、図2における代表的な位置207において、 $15 \times 15$ の正方形パターンが与えられる。マイクロポイントのこのパターンは、エミッタ電極要素上のマイクロパターンの隣接するパターンから離れている。

**【0053】**

本発明の大面積FEDを詳細に説明する前に、本発明は以下のものによって特徴付けられることを理解されたい。(1)基板及び絶縁層上に置く導電層を均一にするCMPプロセスを使用すること、(2)導電層とアノードとの間に所望の均一なギャップを維持するようにスペーサを適当に使用すること(このことは高解像を達成することに役立つ)、(3)マイクロポイントが低機能材料の被覆または着床を持つようにすること、(4)FEDの接続ラインは低い抵抗、低キャパシタンスであること。20

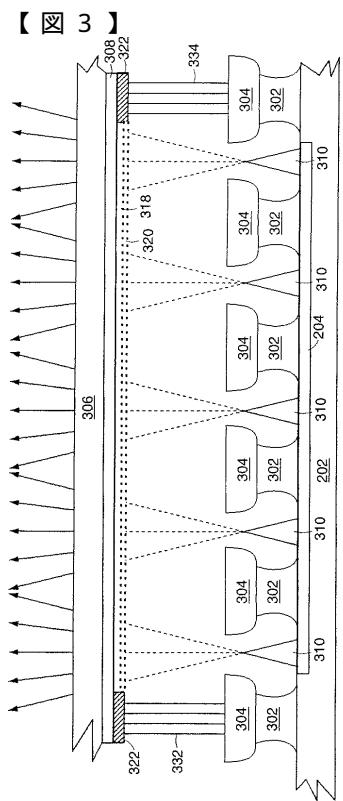

**【0054】**

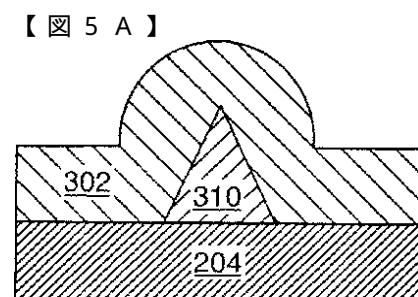

図2及び図3に言及して、本発明の大面積FEDを更に詳細に説明する。図3において、マイクロポイント310は、基板202に堆積しているエミッタ電極要素204上に堆積していることが示されている。これらのマイクロポイントは、マイクロポイントの $5 \times 5$ パターンの部分である。マイクロポイントの正方形パターンのみについて説明するが、その他のパターンを用いることができそれも本発明の範囲内である。30

**【0055】**

各マイクロポイントは絶縁層302によって囲まれている。絶縁層302は大面積FEDの正の電気要素を負うエミッタ電極から絶縁している。好ましくは、絶縁層302は二酸化シリコン(SiO<sub>2</sub>)から形成される。

**【0056】**

導電層304は絶縁層302上に堆積される。導電層は従来技術のセミコンダクタ製造方法を用いて絶縁層302上に堆積される。好ましくは、導電層304は化学処理されたポリシリコン、アモルファスシリコン又は珪素化されたポリシリコン(silicided polysilicon)から形成される。

**【0057】**

導電層304は、マイクロポイントから電子放出流を生じさせるためにマイクロポイントを囲む。好ましくは、導電層304は、絶縁層302上に堆積した一連の電気的に接続された平行な帯である。これらの帯は図2において番号305で示される。導電層304は抽出構造として働き、以下においてそのように言及する。40

**【0058】**

抽出構造304上に離間して表面板306が存在する。表面板306は、好ましくは透明ガラスからなるカソード発光スクリーンである。表面板306は、観察者が見ることができるとカソード発光光子の光を伝達することができなければならない。

**【0059】**

ITO層308は、抽出構造304に対面する表面板306の底面に配設される。ITO50

層 308 は、表面板 306 上に別個の層として配設され、あるいは表面板の一部として形成される導電材料の層である。ITO層 308 は、いかなる場合でもカソード発光光子からの光を透過させ、FED のためのアノードとして働く。

【 0 0 6 0 】

特に図3に言及して、ピクセル318は、抽出構造304に対向するITO層308の表面上に堆積していることが示される。図示のように、ピクセル318はマイクロポイントのパターンの上に配設されている。更に詳しく言えば、ピクセル318はマイクロポイント310の $5 \times 5$ パターンと関連する。

【 0 0 6 1 】

ピクセル領域は、ITO層308の底面に所望のパターンで堆積した蛍光材料320を有する。一般的に、番号318で示すようなピクセル領域は正方形であるが、所望とあらば他の形状とすることができます。使用される蛍光材料は好ましくは低エネルギー電子によって励起されるものである。好ましくは、蛍光材料に対する応答時間は2ms以下である。

【 0 0 6 2 】

ピクセルはブラックマトリックス 322 によって分割される。ブラックマトリックス 322 はいかなる適當な材料とすることができます。その材料は光を透過させることができるものであり電子の衝突によって影響されないものでなければならぬ。適當な材料の一例はコバルト酸化物である。

【 0 0 6 3 】

表面板 306 は基板 202 から離間している。この距離は所定のものであり、通常 200 - 1000 μm の範囲である。この距離は、図 2 にスペーサ 330 として示す、更に特別に図 3 にスペーサ 332 及び 334 として示すスペーサによって保持される。表面板 306 と基板 202 の間の領域は、好ましくは、高真空中である。

【 0 0 6 4 】

電子の流れがマイクロポイントから放出されてピクセルに向かうようにエミッタ電極、電子エミッタ構造及びITOに電力を与えるために、全てのFEDにおけるように、本発明の大面積FEDは1つの電源又は多数の電源に接続されている。

〔 0 0 6 5 〕

例えば、対角寸法が5インチの小面積FEDにおいてはスペーサの必要はない。なぜなら、FEDが高真空中であるときさえもアノードとカソード（ITO層と電子エミッタ）の完全な分離が基本FED構造によって維持されるからである。しかしながら、FEDが大きくなるにつれ、アノードとカソードが高真空中にあるときは、基本FED構造だけではそれらの所望の分離を保持することができない。従って、対角スクリーン寸法が大きくなるにつれ、アノードとカソードを分離させるためにスペーサが必要である。

[ 0 0 6 6 ]

5 - 8 インチの範囲の対角スクリーン寸法を有する F E D 内に置かれる通常のスペーサは円柱状の柱である。これらの柱は同じ高さでありアノードとカソード間の種々の位置に置かれる。大面積 F E D においては円柱状のスペーサは最適ではなく、異なる断面積のスペーサの方が好みしい。

[ 0 0 6 7 ]

大面積 F E D に関するこの問題を解決するために、スペーサ 3 3 2 , 3 3 4 のようなスペーサは絶縁層 3 0 2 又は抽出構造 3 3 4 と、ITO 層 3 0 8 との間にパターンとして置かれる。これらのスペーサは、F E D がスペーサのパターンに従い区分けされるようにカソードとアノードとの間に置かれる。F E D の中心近くの大面積 F E D の一部である図 2において、アノードとカソードの分離を維持するための多数のスペーサが示されている。その他の領域は、所望の分離を維持するために異なるパターンを持つことができる。そういった場合、スペーサ（これらは円柱状の柱であるが）は大面積 F E D 内の興味の領域に依存して種々のパターンを持つことができる。本発明に使用されるスペーサを米国特許第 5,110,838 号、第 5,205,770 号、第 5,232,549 号、第 5,232,863 号、第 5,405,791 号、第 5,433,794 号、第 5,486,126

号及び第5, 492, 234号に従い形成することができる。

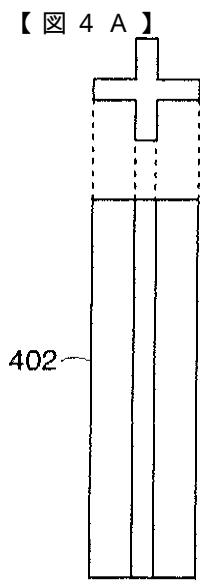

#### 【0068】

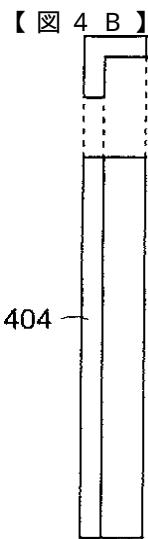

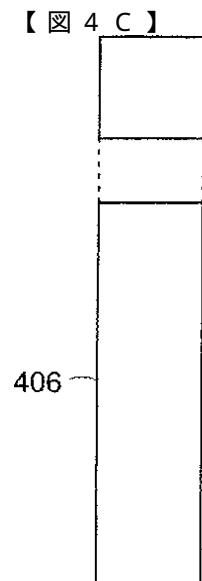

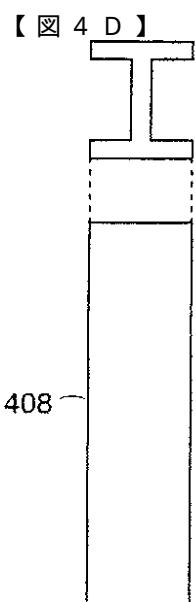

スペーサに加わる応力のため、それらはさまざまな断面形状を持つことができる。図4A、4B、4C及び4Dは、大面積のFEDに用いることのできるスペーサのための4つの断面形状を示す。図4Aは、402として、「+」形状のスペーサの側面断面図を示す。図4Bは、404として、「L」形状のスペーサの側面断面図を示す。図4Cは、406として、正方形のスペーサの側面断面図を示す。図4Dは、408として、「I鋼材」形状のスペーサの側面断面図を示す。しかし、それらは、大面積FEDに用いることのできるスペーサの可能性のある断面形状のほんのわずかなものである。大面積のFEDに必要な強度を与えてアノードとカソードとの間の離隔を維持するために他の形状も用いることができるることは理解されるであろう。10

#### 【0069】

また、大面積FEDのさまざまな位置に設けられたスペーサは、大面積FEDの全領域にまたがってアノードとカソードとの間に均一な離隔を維持するように異なる長さを持つことができる。例えば、大面積FEDの中央に近いスペーサは端部に近いスペーサよりもわずかに長くなるであろう。それらの極端な状態の間にあるスペーサは、端部の最も短いスペーサから中央の最も長いスペーサまで推移するように、だんだんと長さを変えることができる。FED内の高真空によるフェースプレートのわずかな歪みをその異なる長さのスペーサが補償することになる。そのわずかな歪みは、端部の近くではFEDの壁面構造がフェースプレートに実質的な補強を加えるのでその端部には生じないが、中央部に近いところに生じる。20

#### 【0070】

しかし、本願発明の範囲内における他のオプションとして、少ない数の異なる長さのスペーサを用いることによって提供されるようなものと同一の有効な離隔をアノードとカソードとの間に提供するような多数の「同一長さ」のスペーサを用いることができることを理解するであろう。ここで、マイクロポイントの製造の均一性並びに大面積FEDの全体にわたる絶縁層及び抽出構造における開口の整列を達成するように用いられるような、これまでに簡単に説明した低FED構造の製造方法を詳細に説明する。その方法は、大面積FEDの各マイクロポイント用の自己整列抽出構造を製造するために、デポジション（堆積）、化学機械研磨及びウエットケミカルエッチングの組み合わせを用いる。30

#### 【0071】

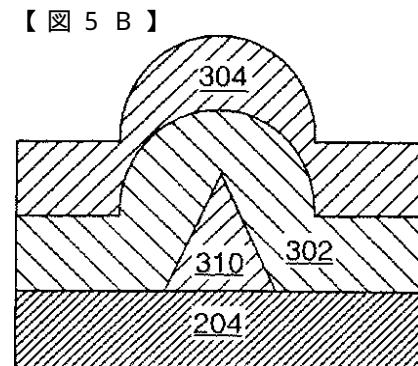

図5Aから図5Dを参照しながら、本願発明に係る方法を説明する。電気的に結合されたエミッタ電極素子204が基板202に形成されると、マイクロポイント310のパターンがそれらの素子の上に形成される。別の製造工程によるマイクロポイントの形成は、マイクロポイントの形成の全体に渡ってより優れた制御を提供するとともに、大面積FEDの広い面積の全面のマイクロポイントの優れた寸法の均一性を提供する。形成されたマイクロポイントは、図5Aに示されているように、ほぼ逆の円錐形状を持つ。そのマイクロポイントは望ましくはシリコンから形成される。

#### 【0072】

次に、適切な低仕事関数の物質がそのマイクロポイントの上に置かれる。その被覆は少なくともそのマイクロポイントのチップに行われる。適切な仕事関数の物質としては、サーメット( $\text{Cr}_3\text{Si} + \text{SiO}_2$ )、セシウム、ルビジウム、窒化タンタル、バリウム、ケイ化クロム、炭化チタニウム及びニオブがある。これらは、気化堆積のような従来の半導体製造方法又は以下に述べる望ましい方法を用いてマイクロポイント上に堆積される。他の適当な技術も用いることができることは理解すべきである。40

#### 【0073】

望ましくは、マイクロポイントを処理するために用いられる低仕事関数の物質はセシウムである。セシウムは望ましくは非常に低いエネルギーを用いて高ドーズ量でマイクロポイントに植え込みされる。これにより、大面積FEDの全体にわたるマイクロポイント間により良い均一性がもたらされる。その植え込まれたセシウムは大気圧下の高温度（50050

)で安定である。さらに、その方法によりより高い(又はより大きな)マイクロポイントを被覆すると、FEDがより低い作動電圧で作動できるようになる。マイクロポイントの低作動関数の処理は、望ましくは、堆積、CMP処理及びウエットケミカルエッティング活動が行われる前のマイクロポイントの形成後に行う。しかし、大面積FEDの製造の工程の間の他の時間に行うことは可能であることを理解すべきである。

#### 【0074】

マイクロポイント310が一旦被覆されると、図示のように、絶縁層302がそのマイクロポイント素子204及び基板202の全体に堆積される。望ましくは、絶縁層はSiO<sub>2</sub>から作られる。それに続いて、導電層304が、図5Bに示すように、絶縁層302の上に堆積される。望ましくは、導電層304はアモルファスシリコン又はポリシリコンから作られる。

10

#### 【0075】

絶縁及び導電層の厚さは、層の合計の厚さが元のマイクロポイントの高さよりも大きくなるように選択される。本願発明の方法は、シリコンがマイクロポイント及び導電層として望ましい材料の場合であっても、マイクロポイントと絶縁及び導電層との材料の選択に柔軟性に余裕をみている。

#### 【0076】

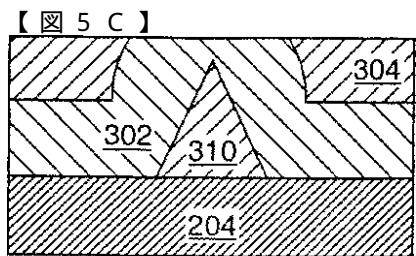

導電層304を絶縁層302の全体に堆積させた後は、その2つの層はCMP工程を用いて図5Cに示すように研磨される。その研磨工程は、大面積FEDの全表面をほぼ平らに研磨するという点で非常に制御自在である。その研磨の結果、絶縁及び導電層304がほぼ均一の厚さになる。大面積FEDの全体を横切るそれらの2つの層における均一の厚さの存在は、均一なマイクロポイント及び導電及び絶縁層の自己整列を助けることになる。CMPに関するさまざまな特許として、米国特許第5,186,670号、第5,209,816号、第5,229,331号、第5,240,552号、5,259,719号、第5,300,155号、第5,318,927号、第5,354,490号、第5,372,973号、第5,395,801号、第5,439,551号、第5,449,314号及び第5,514,245号がある。

20

#### 【0077】

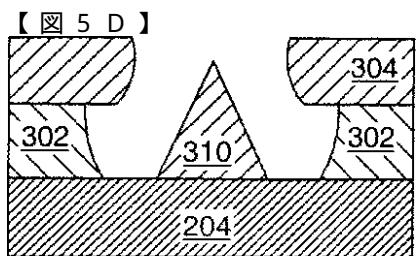

研磨工程に続いて、導電及び絶縁層には、図5Dに示すように、ウエットケミカルエッティングが行われる。導電及び絶縁層のウエットケミカルエッティングでは、各層からの物質が選択的に除去されてマイクロポイントを露出する。そのように行われる際に、導電及び絶縁層の開口がマイクロポイントと自己整列される。露出されたマイクロポイントはそれから熒光スクリーンを励起するための電子を放出できるようになる。

30

#### 【0078】

大面積FEDの構成要素を説明したので、ここから本願発明に係るFEDの動作特性を説明する。

#### 【0079】

60 - 75 Hzの再生速度及び256のグレースケールレベルの適切なビデオ応答のために、発光応答時間は、そのFEDにおける高解像度(1280 × 1024ピクセル)が得られるように制御されなければならない。高解像度を持つことが望ましい場合には、適切な応答時間は1 μsより小さいか又はそれと等しくなる。

40

#### 【0080】

FEDに関する応答時間は、304及び204のそれぞれにおける「行」及び「列」アドレスラインのRC(抵抗 × 静電容量)時間によって決定される。

#### 【0081】

最小の抵抗値を得るためにには、最小の抵抗値の導体、例えば、金、銀、アルミニウム、銅又は他の適当な物質を用い、さらに、その導体を厚く、例えば、0.2 μmより大きくし、又はある方法で、導体として機能するラインの断面積を大きくする。

#### 【0082】

静電容量は、列及び行の間の垂直方向距離と、それらの間の絶縁材料と、行及び列ライン

50

の重なる面積とによって決定される。背の高いエミッタチップ、例えば、0.6-2.5  $\mu\text{m}$ を用いると、厚い絶縁体を行及び列ラインの間に用いることができる。これにより、小さな(0.5  $\mu\text{m}$ 以下の)エミッタチップを用いた場合よりも、静電容量を2-5倍程度小さくすることができる。静電容量は絶縁材料の選択によって制御できるが、その材料は限定されているので、背の高いチップを用いることが望ましい。

#### 【0083】

従って、厚さ、高い伝導率のグリッド及びエミッタ電極並びに背の高いエミッタチップを選択すると、それらを用いなかった場合と比べて高速のRC時間を提供することになる。

#### 【0084】

ここで用いた用語及び表現は例示のために用いたものであり限定するものではない。そのような用語及び表現は、図示及び説明した特徴及びその一部と等価のものを排除するために用いることを意図するものではなく、本願発明の範囲内できさまざまな変更が可能であることを認識するであろう。

10

#### 【図面の簡単な説明】

【図1】 従来技術のFEDの部分断面図である。

【図2】 本発明に従う大面積FEDの一部を、一部を破断して示す部分上面斜視図。

【図3】 図2に示す大面積FEDの一部の部分断面図。

【図4】 図4Aは、「+」型のスペーサの側面及び断面図。図4Bは、「L」型のスペーサの側面及び断面図。図4Cは、正方形のスペーサの側面及び断面図。図4Dは、「Iビーム」型のスペーサの側面及び断面図。

20

【図5】 図5Aは、本発明に従う堆積、CMPプロセス及び湿式化学エッティング方法の第1ステップを示す図。

図5Bは、本発明に従う堆積、CMPプロセス及び湿式化学エッティング方法の第2ステップを示す図。

図5Cは、本発明に従う堆積、CMPプロセス及び湿式化学エッティング方法の第3ステップを示す図。

図5Dは、本発明に従う堆積、CMPプロセス及び湿式化学エッティング方法の第4ステップを示す図。

FIG. 1

PRIOR ART

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 5D

---

フロントページの続き

審査官 小林 紀史

- (56)参考文献 特開平01-260747(JP,A)

特開平05-266832(JP,A)

特開平05-274998(JP,A)

特開平06-342635(JP,A)

特表平08-507643(JP,A)

特開平09-106752(JP,A)

特開平09-179508(JP,A)

特開平09-274848(JP,A)

特開平09-306395(JP,A)

(58)調査した分野(Int.Cl., DB名)

- H01J 1/30 - 1/316

H01J 9/02

H01J29/10 - 29/34

H01J29/46

H01J31/00 - 31/06

H01J31/10 - 31/24