(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6918552号

(P6918552)

(45) 発行日 令和3年8月11日(2021.8.11)

(24) 登録日 令和3年7月27日(2021.7.27)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO4N 5/3745 (2011.01) | HO4N 5/3745 200 |

| HO4N 5/355 (2011.01)  | HO4N 5/355      |

| HO1L 27/146 (2006.01) | HO1L 27/146 A   |

請求項の数 6 (全 23 頁)

|                    |                              |           |                                            |

|--------------------|------------------------------|-----------|--------------------------------------------|

| (21) 出願番号          | 特願2017-75320 (P2017-75320)   | (73) 特許権者 | 000004352<br>日本放送協会<br>東京都渋谷区神南2丁目2番1号     |

| (22) 出願日           | 平成29年4月5日(2017.4.5)          | (74) 代理人  | 100097984<br>弁理士 川野 宏                      |

| (65) 公開番号          | 特開2018-85709 (P2018-85709A)  | (74) 代理人  | 100098073<br>弁理士 津久井 照保                    |

| (43) 公開日           | 平成30年5月31日(2018.5.31)        | (72) 発明者  | 新井 俊希<br>東京都世田谷区砧一丁目10番11号 日本放送協会 放送技術研究所内 |

| 審査請求日              | 令和2年3月3日(2020.3.3)           |           |                                            |

| (31) 優先権主張番号       | 特願2016-220202 (P2016-220202) |           |                                            |

| (32) 優先日           | 平成28年11月11日(2016.11.11)      |           |                                            |

| (33) 優先権主張国・地域又は機関 | 日本国(JP)                      |           |                                            |

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】 読出し制御回路、固体撮像素子、および撮像素子の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

固体撮像装置の読み出し制御回路において、光電変換部からの信号が蓄積される、容量値が相対的に小さく変換ゲインが大きい第1の浮遊拡散容量手段と、

該第1の浮遊拡散容量手段からの信号がオーバーフローゲートを経て入力され蓄積される、容量値が相対的に大きく変換ゲインが小さい第2の浮遊拡散容量手段とを備え、

該第1の浮遊拡散容量手段と該第2の浮遊拡散容量手段は、ともに、固有の画素出力回路を備え、前記第1および第2の浮遊拡散容量手段各々に係る前記画素出力回路は互いに並列に配置されており、該画素出力回路の各々からは、各水平走査(H)ライン毎に、同時に画素出力信号が出力されるように構成され、

前記光電変換部への入射光に対する、前記第1および第2の浮遊拡散容量手段各々に係る前記画素出力回路からの各前記画素出力信号を合成した合成後出力信号の傾きが、前記入射光が低強度側から高強度側に至る領域で大から小に変化する構成とされている、ことを特徴とする読み出し制御回路。

## 【請求項 2】

前記第1の浮遊拡散容量手段につき、転送トランジスタを含む4つのトランジスタを用いることにより、および前記第2の浮遊拡散容量手段につき、オーバーフローゲートを含む4つのトランジスタを用いることにより、各々構成されていることを特徴とする請求項1記載の読み出し制御回路。

## 【請求項 3】

10

20

前記第1の浮遊拡散容量手段につき、転送トランジスタを含まない3つのトランジスタを用いることにより、および前記第2の浮遊拡散容量手段につき、オーバーフローゲートを含む4つのトランジスタを用いることにより、各々構成されていることを特徴とする請求項1記載の読み出し制御回路。

**【請求項4】**

前記光電変換部が光電変換膜から構成されていることを特徴とする請求項3記載の読み出し制御回路。

**【請求項5】**

請求項1～4のうちいずれか1項記載の読み出し制御回路と、

前記固有の画素出力回路の各々から出力された信号を、対応する出力信号線に出力する

、該画素出力回路各々に応じて設けられた出力部とを備えたことを特徴とする固体撮像素子。

10

**【請求項6】**

請求項5記載の固体撮像素子を駆動する駆動方法であって、

前記第1の浮遊拡散容量手段と前記第2の浮遊拡散容量手段をリセットし、信号の蓄積期間に前記光電変換部から前記第1の浮遊拡散容量手段に光電子が移動する際に、

前記オーバーフローゲートのゲート電圧を所定の値として前記第1の浮遊拡散容量手段の飽和容量を設定し、前記第1の浮遊拡散容量手段から光電子が溢れた際には、この溢れた電子を前記第2の浮遊拡散容量手段へ移動させ、前記第1の浮遊拡散容量手段と前記第2の浮遊拡散容量手段について光電子量と変換ゲインにより定まる各信号電圧を、対応するソースフォロア素子によって各画素出力信号に変換し、この後、この2つの画素出力信号を、各々が対応する出力信号線に出力することを特徴とする固体撮像素子を駆動する駆動方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、読み出し制御回路、固体撮像素子、および撮像素子の駆動方法に関し、詳しくは、光電変換部により得られた光電子に基づく、感度が異なる複数の信号を、この後の信号処理部で合成され得るように出力する、読み出し制御回路、固体撮像素子、および撮像素子の駆動方法に関するものである。

30

**【背景技術】**

**【0002】**

従来、固体撮像素子、例えばCMOSイメージセンサにおいては、光電変換によって単位画素に蓄積された信号電荷の値に応じて、略線形な出力信号が得られるので、光電変換部の飽和信号量と暗時雑音の比からダイナミックレンジが決まってしまう。

**【0003】**

このような固体撮像素子では、低輝度の被写体にカメラレンズの絞りを合わせると高輝度の被写体の信号は飽和してしまい、逆に高輝度の被写体にカメラレンズの絞りを合わせると低輝度の被写体の信号は雑音に埋もれてしまうことから、高輝度、低輝度のいずれであっても良好な画像が得られる、十分に広いダイナミックレンジを有する画像素子が求められていた。

40

**【0004】**

そして、単にダイナミックレンジを拡大するだけではなく、次の(1)～(4)のような項目を満たした上でダイナミックレンジを拡大化することが求められていた。すなわち、(1)光電変換部を分割しないで解像度特性を優れたものとすることができる、(2)露光時間を分割しないで動画撮像特性を優れたものとし得ること、(3)高感度、高S/N化と広ダイナミックレンジ化のトレードオフを解消できること、および(4)超多画素において高フレーム周波数を読み出すことができること、が求められていた。

**【0005】**

ここで、入射光量に対する、出力信号量のダイナミックレンジを拡大するために、同一

50

の画素から長時間露光と短時間露光により得られた2つの信号を複数回読み出し、読み出された感度が異なる複数の信号を、撮像素子の後段の信号処理部で合成する方法が知られている（特許文献1、非特許文献1を参照）。

#### 【0006】

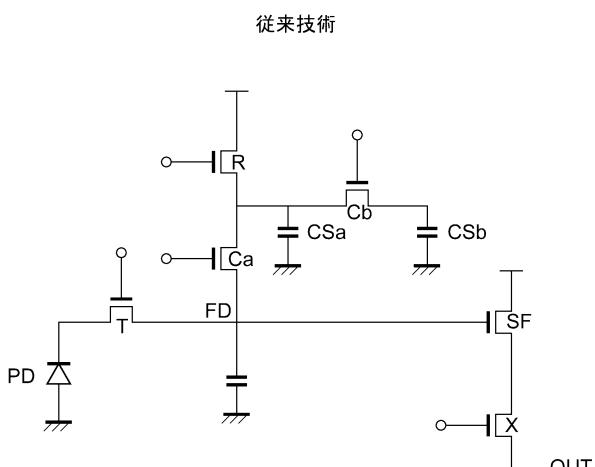

また、図22に示す従来技術においては、各画素は、光を受光して光電荷を生成するフォトダイオードPDと、このPDに隣接して設けられた光電荷を転送する転送トランジスタTと、このTを介して上記PDに接続して設けられたフローティングディフェュージョンFDと、露光蓄積動作時に上記PDから溢れ出た光電荷を上記Tを通じて蓄積する第1の蓄積容量CSaおよび第2の蓄積容量CSbと、を備える。さらに、これらの蓄積容量CSa、CSbの他、上記FD内の信号電荷を排出するためのリセットトランジスタRと、上記FDと上記CSaの間に設けられた第1の蓄積トランジスタCaと、上記CSaと上記CSbの間に設けられた第2の蓄積トランジスタCbと、上記FDと上記CSaと上記CSbの信号電荷を電圧として読み出すための増幅トランジスタSFと、このSFに接続して設けられ画素ないしは画素ブロックを選択するための選択トランジスタXとを備えている。10

#### 【0007】

このように構成された従来技術は、上記の構成の画素が2次元または1次元のアレイ状に複数個集積されており、各画素において、転送トランジスタT、第1の蓄積トランジスタCa、第2の蓄積トランジスタCb、リセットトランジスタRのゲート電極に、各駆動ラインが接続され、また、選択トランジスタXのゲート電極には行シフトレジスタから駆動される画素選択ラインが接続され、さらに、選択トランジスタXの出力側ソースに1つの出力ラインOUTが接続され、列シフトレジスタにより制御されて、いずれの信号もこの1つの出力ラインOUTを通して出力される（特許文献2を参照）。

【特許文献1】特許第3680366号公報

【特許文献2】特許第5066704号公報

【非特許文献1】Orly Yadid-Pecht and Eric R. Fossum, "Wide Intrascene Dynamic Range CMOS APS Using Dual Sampling", IEEE TRANSACTIONS ON ELECTRON DEVICES, Vol. 44, No.10, pp.1721-1723, Oct., 1997.

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、上記特許文献1等に記載の従来技術では、長時間露光と短時間露光による信号を合成する方法では、信号量は2倍にならないのに対して、読み出しのノイズは各々が積算されて2倍となることから、特に低照度においてはS/Nが劣化する。

また、長時間露光と短時間露光は互いに異なるタイミングで撮像するので、撮像時刻にずれが生じ、高速に動く被写体が互いにずれて見えるという問題が生じる。また、一画素あたりの読み出し回数が複数回になるので、最高フレーム周波数が低下する。

#### 【0009】

また、上記特許文献2に記載の従来技術では、蓄積容量素子を使用し飽和前信号と過飽和信号を読み出す手法であり、一画素あたりの読み出し回数が複数回となるので、最高フレーム周波数が低下する。40

#### 【0010】

本発明は上記の事情に鑑みなされたものであり、優れた動画撮像特性と解像度特性を実現し得、低照度において飽和レベルを狭めることなく線形かつ高S/Nの信号取得を可能にするとともに、高照度においては線形領域での良好なS/Nを可能にすることができる、ダイナミックレンジの拡大を図ることができるとともに最高フレーム周波数の低下を抑制し得る、読み出し制御回路、固体撮像素子、および撮像素子の駆動方法を提供することを目的とするものである。

#### 【課題を解決するための手段】

#### 【0011】

10

20

30

40

50

本発明の、読出し制御回路は、

固体撮像装置の読出し制御回路において、光電変換部からの信号が蓄積される、容量値が相対的に小さく変換ゲインが大きい第1の浮遊拡散容量手段と、

該第1の浮遊拡散容量手段からの信号がオーバーフローゲートを経て入力され蓄積される、容量値が相対的に大きく変換ゲインが小さい第2の浮遊拡散容量手段とを備え、

該第1の浮遊拡散容量手段と該第2の浮遊拡散容量手段は、ともに、固有の画素出力回路を備え、前記第1および第2の浮遊拡散容量手段各々に係る前記画素出力回路は互いに並列に配置されており、該画素出力回路の各々からは、各水平走査(H)ライン毎に、同時に画素出力信号が出力されるように構成され、

前記光電変換部への入射光に対する、前記第1および第2の浮遊拡散容量手段各々に係る前記画素出力回路からの各前記画素出力信号を合成した合成後出力信号の傾きが、前記入射光が低強度側から高強度側に至る領域で大から小に変化する構成とされていることを特徴とするものである。 10

また、前記第1の浮遊拡散容量手段につき、転送トランジスタを含む4つのトランジスタを用いることにより、および前記第2の浮遊拡散容量手段につき、オーバーフローゲートを含む4つのトランジスタを用いることにより、各々構成することができる。

また、前記第1の浮遊拡散容量手段につき、転送トランジスタを含まない3つのトランジスタを用いることにより、および前記第2の浮遊拡散容量手段につき、オーバーフローゲートを含む4つのトランジスタを用いることにより、各々構成することができる。この場合において、前記光電変換部が光電変換膜から構成されていることが好ましい。 20

#### 【0012】

また、本発明の固体撮像素子は、

上述した読出し制御回路と、

上述した固有の画素出力回路の各々からの出力信号を、対応する出力信号線に出力する、該画素出力回路に応じて設けられた出力部とを備えたことを特徴とするものである。

#### 【0013】

また、本願発明の撮像素子の駆動方法は、

上述した固体撮像素子を駆動する駆動方法であって、

前記第1の浮遊拡散容量手段と前記第2の浮遊拡散容量手段をリセットし、信号の蓄積期間に前記光電変換部から前記第1の浮遊拡散容量手段に光電子が移動する際に、 30

前記オーバーフローゲートのゲート電圧を所定の値として前記第1の浮遊拡散容量手段の飽和容量を設定し、前記第1の浮遊拡散容量手段から光電子が溢れた際には、この溢れた電子を前記第2の浮遊拡散容量手段へ移動させ、前記第1の浮遊拡散容量手段と前記第2の浮遊拡散容量手段について光電子量と変換ゲインにより定まる各信号電圧を、対応するソースフォロア素子によって各画素出力信号に変換し、この後、この2つの画素出力信号を、各々が対応する出力信号線に出力することを特徴とするものである。

#### 【発明の効果】

#### 【0014】

本発明の読出し制御回路および固体撮像素子によれば、第1の浮遊拡散容量手段は容量が小さく変換ゲインを大きくすることで、低照度において飽和レベルを狭めることなく線形かつ高S/Nの信号を取得することができる。第1の浮遊拡散容量手段から溢れた信号電荷はオーバーフローゲートを経て第2の浮遊拡散容量手段に流れる。第2の浮遊拡散容量手段は容量が大きく変換ゲインを小さくすることで、高照度においても線形領域での良好なS/Nを実現しながらダイナミックレンジを拡大することができる。 40

#### 【0015】

固体撮像素子から出力された上記2つの信号を後段の信号処理部で合成することにより、低照度状態では高S/Nであり、高照度状態では広ダイナミックレンジである信号とすることができる。

これらの2つの信号は、同一時刻に同一光電変換部で光信号を取得するので動画撮像特性と解像度特性において優れている。 50

なお、画素出力回路および信号出力線を複数本備えており、カラム信号処理回路は1出力線あたり1個に対応させることができ、最高フレーム周波数の低下を抑制し得る。

以上に説明した発明の効果は、本願発明の撮像素子の駆動方法によっても同様に奏することができる。

**【図面の簡単な説明】**

**【0016】**

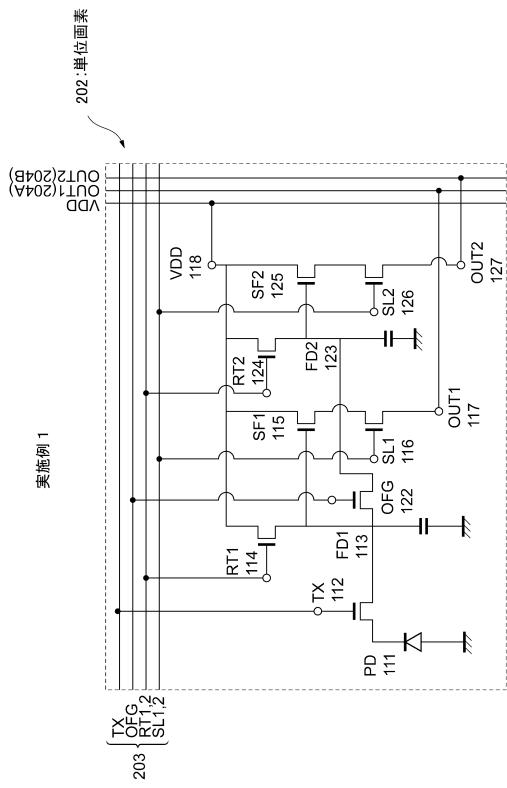

【図1】実施例1に係る単位画素の等価回路図を示すものである。

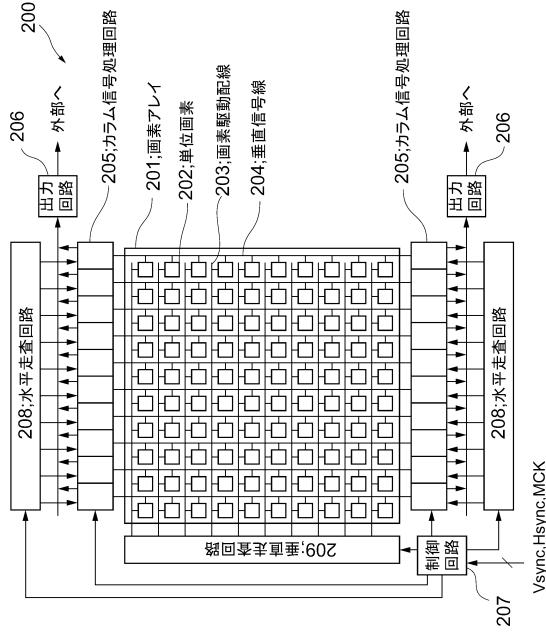

【図2】実施例1に係る単位画素の画素アレイを有する固体撮像素子のシステム構成図を示すものである。

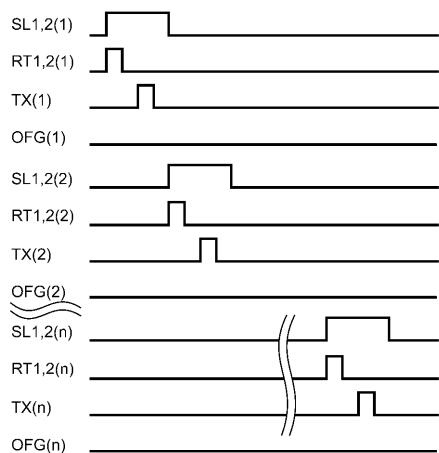

【図3】図1に示す実施例1の画素回路を用いて信号読出しを行った場合における画素回路への入力信号のタイムチャートである。 10

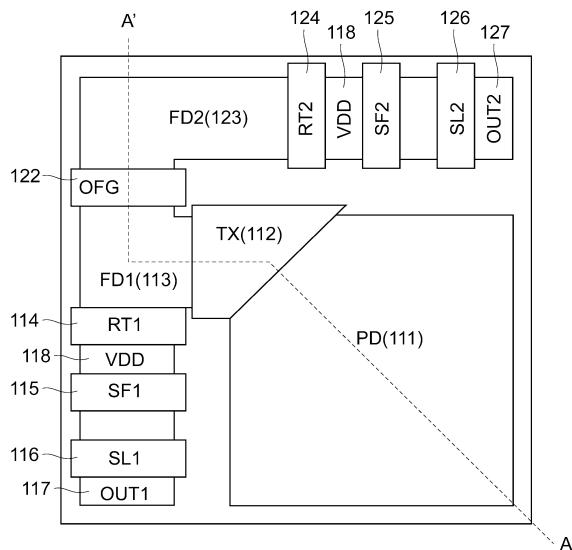

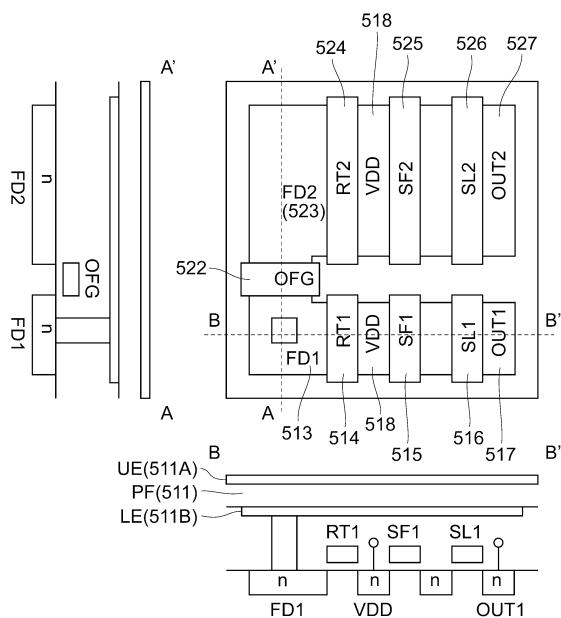

【図4】実施例1に係る、単位画素の平面模式図の一例を示すものである。

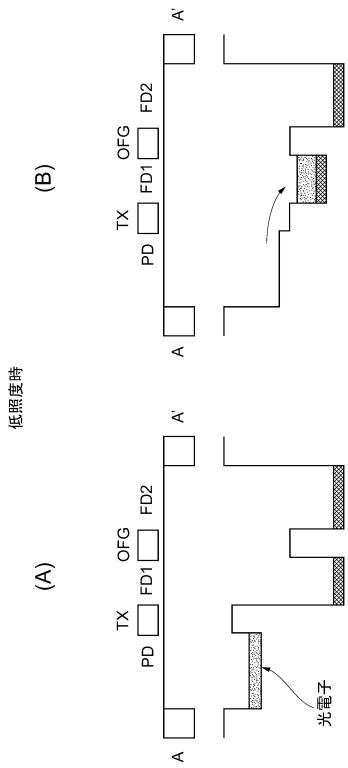

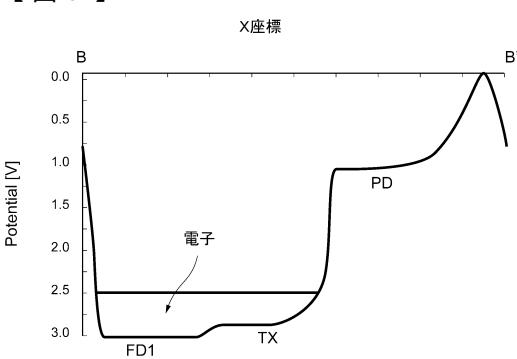

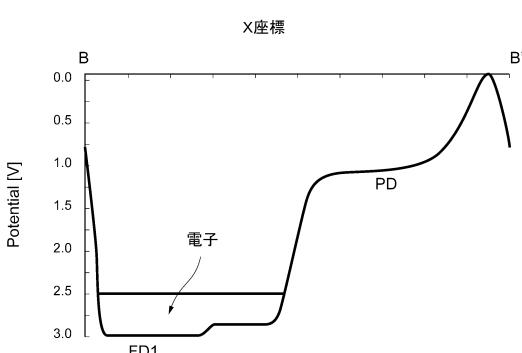

【図5】実施例1に関し、(A)は低照度での露光時におけるポテンシャル図を示すものであり、(B)は低照度での信号電荷の移動時におけるポテンシャル図を示すものである。

【図6】実施例1に関し、(A)は高照度での露光時におけるポテンシャル図を示すものであり、(B)は高照度での信号電荷の移動時におけるポテンシャル図を示すものである。

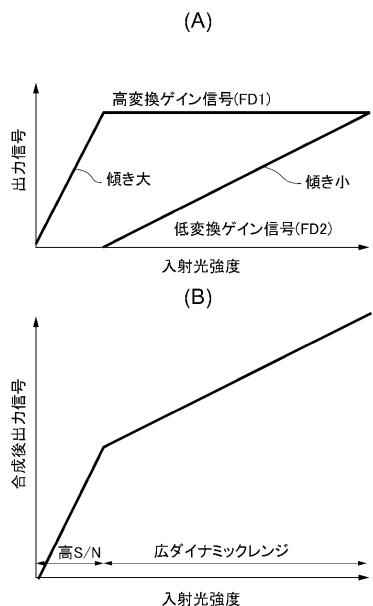

【図7】実施例1に関し、(A)は高変換ゲインの第1の浮遊拡散容量(FD1)を経て画素回路から出力される信号と低変換ゲインの第2の浮遊拡散容量(FD2)を経て画素回路から出力される信号との、入射光強度に対する関係を示す図であり、(B)は後段の信号処理部で合成した後の合成後出力信号の入射光強度に対する関係を示す図である。 20

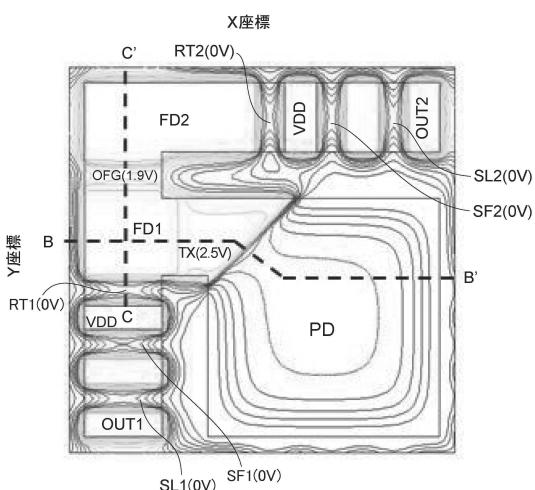

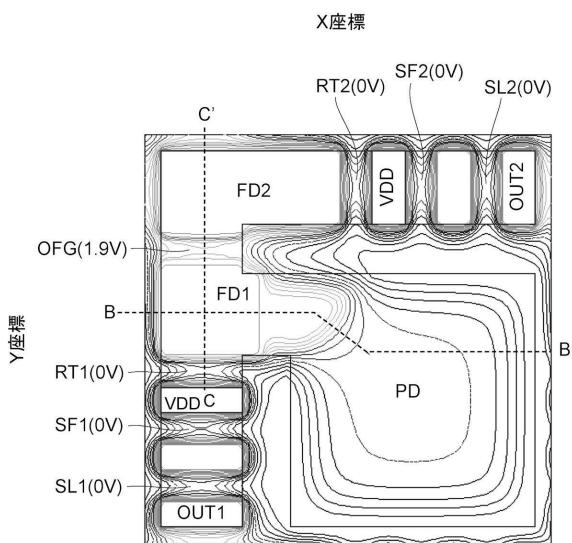

【図8】実施例1に係る、単位画素のポテンシャルシミュレーションによる結果を表す平面図である。

【図9】図8のB-B'線断面図である。

【図10】図8のC-C'線断面図である。

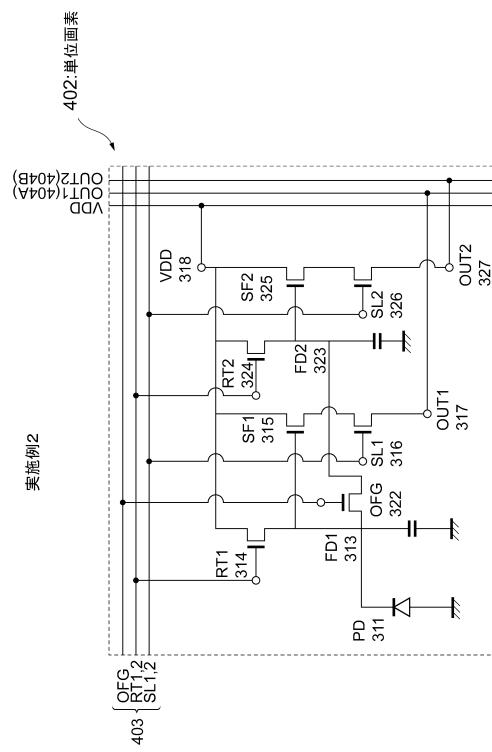

【図11】実施例2に係る単位画素の等価回路図を示すものである。

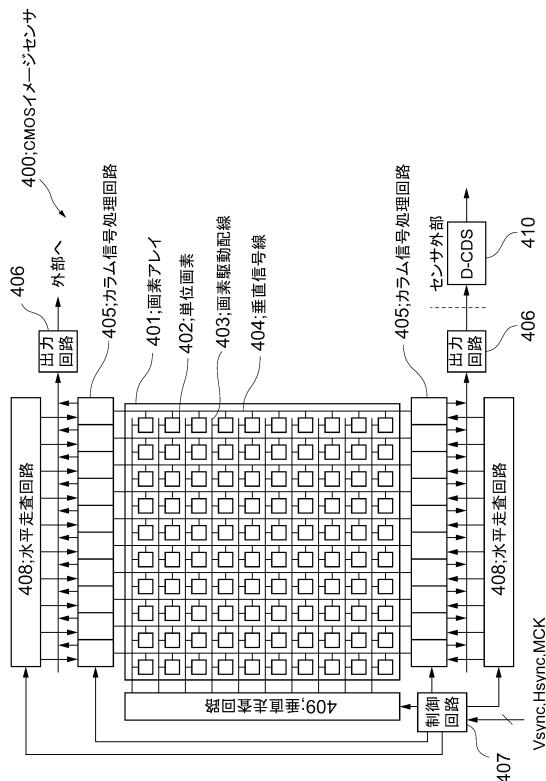

【図12】実施例2に係る単位画素の画素アレイを有する固体撮像素子のシステム構成図を示すものである。

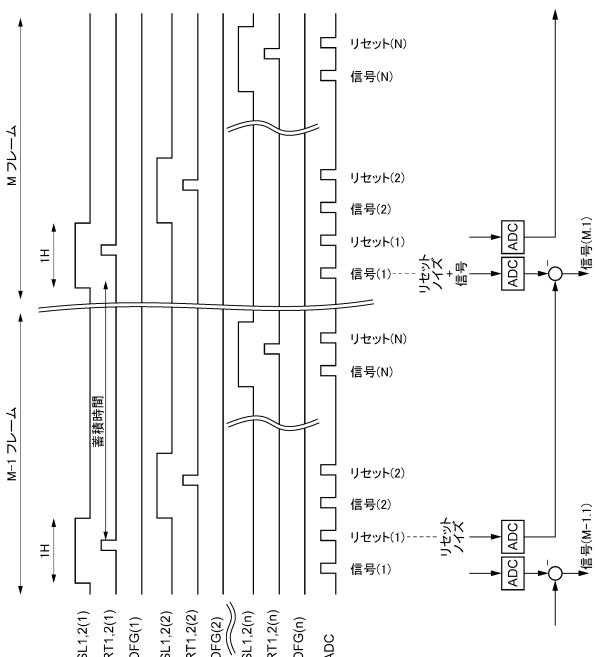

【図13】図11に示す実施例2を用いて信号読出しを行った場合における画素回路への入力信号のタイムチャートである。 30

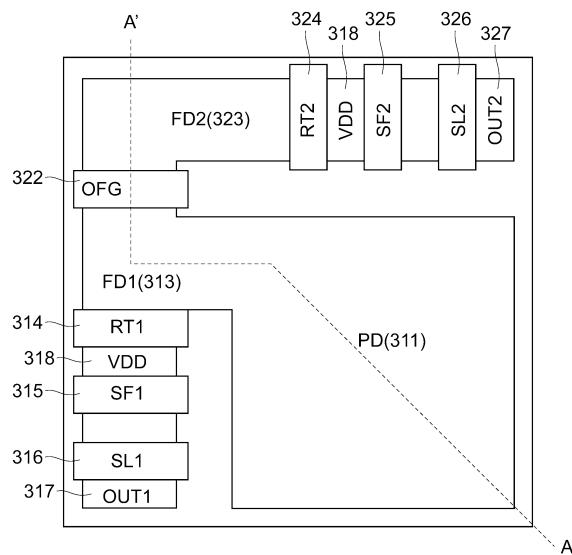

【図14】実施例2に係る、単位画素の平面模式図の一例を示すものである。

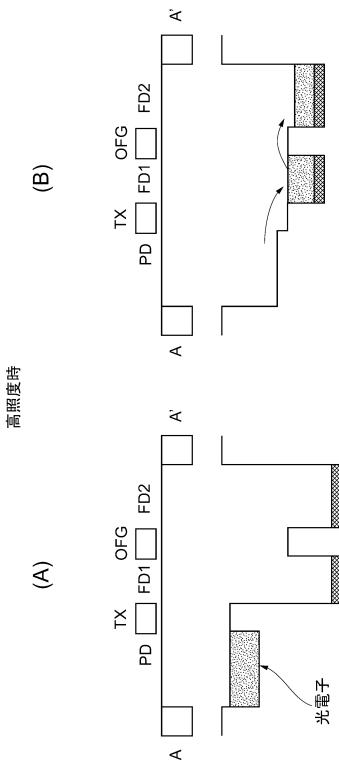

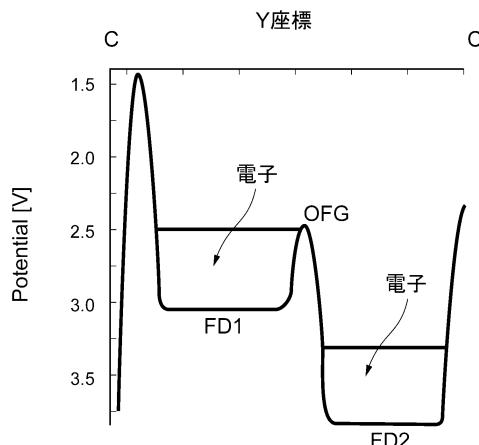

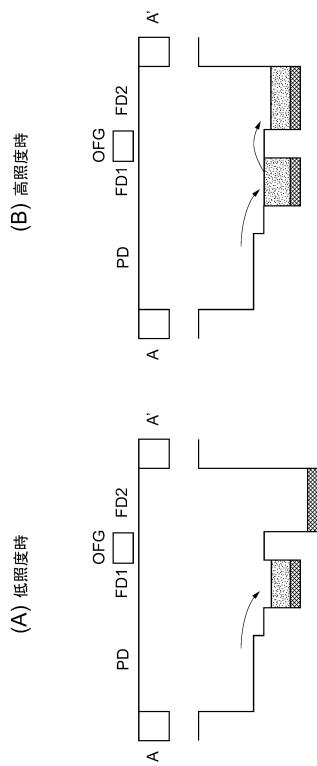

【図15】実施例2に関し、(A)は低照度での信号電荷の移動時におけるポテンシャル図を示すものであり、(B)は高照度での信号電荷の移動時におけるポテンシャル図を示すものである。

【図16】実施例2に係る、単位画素のポテンシャルシミュレーションによる結果を表す平面図である。

【図17】図16のB-B'線断面図である。

【図18】図16のC-C'線断面図である。

【図19】実施例3に係る単位画素の等価回路図を示すものである。 40

【図20】図19に示す実施例3を用いて信号読出しを行った場合における画素回路への入力信号のタイムチャートである。

【図21】実施例3に係る単位画素の平面模式図と断面模式図の一例を示すものである。

【図22】従来技術に係る固体撮像装置の単一画素の等価回路図を示すものである。

**【発明を実施するための形態】**

**【0017】**

以下、本発明の実施形態について、上記図面を参照しながら説明する。

**<実施例1>**

図2は、単位画素の画素アレイを有する固体撮像素子、具体的にはCMOSイメージセンサのシステム構成図である。CMOSイメージセンサ200は、光電変換素子を含む单 50

位画素 202 がアレイ状に 2 次元配列され、画素駆動配線 203、垂直信号線 204 と接続している画素アレイ 201 を有するとともに、周辺回路として、カラム信号処理回路 205、出力回路 206、制御回路 207、水平走査回路 208、垂直走査回路 209 から構成されている。

ここで、カラム信号処理回路 205 および水平走査回路 208 が、図中の上方および下方に配されているのは、片側に配された場合に比べ、フレーム周波数を 2 倍にすることができるという理由からである。

#### 【0018】

また、図 1 は、実施例 1 に係る CMOS イメージセンサに用いられる、画素回路（読み出し制御回路）の等価回路図を示すものである。

10

図 1 に示すように、本実施例における読み出し制御回路は、第 1 の信号経路および第 2 の信号経路の 2 系統の信号経路を備えている。

#### 【0019】

図 1 に示すように、光電変換素子であるフォトダイオード（PD）111 は転送トランジスタ（TX）112 を経て第 1 の浮遊拡散容量（FD1）113 に接続される。第 1 の浮遊拡散容量（FD1）113 は、オーバーフローゲート（OFG）122 を経て第 2 の浮遊拡散容量（FD2）123 に接続される。

#### 【0020】

第 1 の信号経路である、第 1 の浮遊拡散容量（FD1）113 の画素出力回路は、リセットトランジスタ 1（RT1）114、ソースフォロアトランジスタ 1（SF1）115、選択トランジスタ 1（SL1）116 で構成され、画素出力 1（OUT1）117 は垂直信号線 204A に接続されている。

20

#### 【0021】

一方、第 2 の信号経路である、第 2 の浮遊拡散容量（FD2）123 の画素出力回路は、リセットトランジスタ 2（RT2）124、ソースフォロアトランジスタ 2（SF2）125、選択トランジスタ 2（SL2）126 で構成され、画素出力 2（OUT2）127 は、上記とは別の垂直信号線 204B に接続されている。

#### 【0022】

リセットトランジスタ 1（RT1）114、ソースフォロアトランジスタ 1（SF1）115、リセットトランジスタ 2（RT2）124、ソースフォロアトランジスタ 2（SF2）125 の各ドレイン電極は、画素電源（VDD）118 に接続されている。

30

#### 【0023】

また、転送トランジスタ（TX）112、オーバーフローゲート（OFG）122、リセットトランジスタ 1（RT1）114、リセットトランジスタ 2（RT2）124、選択トランジスタ 1（SL1）116、選択トランジスタ 2（SL2）126 の各ゲート電極は、それぞれの画素駆動配線 203 に接続されている。

#### 【0024】

図 1 に示す単位画素 202 の画素回路（読み出し制御回路）において、フォトダイオード（PD）111 は、入射光の強度に応じた量の負電荷を蓄積する。このフォトダイオード（PD）111 のアノードは接地され、カソードは転送トランジスタ（TX）112、および第 1 の浮遊拡散容量（FD1）113 を介してソースフォロアトランジスタ 1（SF1）115 のゲートに接続される。転送トランジスタ（TX）112 のゲートは、垂直操作回路 209 からの画素駆動配線 203（TX）に接続され、転送信号が入力される。

40

#### 【0025】

第 1 の信号経路において、ソースフォロアトランジスタ 1（SF1）115 および選択トランジスタ 1（SL1）116 は、画素電源（VDD）118 と画素出力 1（OUT1）117との間に直列接続される。選択トランジスタ 1（SL1）116 のゲートは、垂直操作回路 209 からの画素駆動配線 203（SL1）に接続され、選択信号が入力される。リセットトランジスタ 1（RT1）114 は、画素電源（VDD）118 とソースフォロアトランジスタ 1（SF1）115 のゲートとの間に接続される。リセットトランジ

50

スタ1 (R T 1) 114 のゲートは、垂直操作回路 209 からの画素駆動配線 203 (R T 1) に接続され、リセット信号を入力される。

#### 【0026】

また、第1の浮遊拡散容量 (F D 1) 113 は、ソースフォロアトランジスタ1 (S F 1) 115 のゲートに接続される。

前述したように、第2の浮遊拡散容量 (F D 2) 123 は、オーバーフローゲート (O F G) 122 を経て第1の浮遊拡散容量 (F D 1) 113 に接続されており、第1の浮遊拡散容量 (F D 1) 113 に蓄積された電荷が、オーバーフローゲート (O F G) 122 から溢れると、第2の浮遊拡散容量 (F D 2) 123 に入力される。

#### 【0027】

第2の信号経路において、ソースフォロアトランジスタ2 (S F 2) 125 および選択トランジスタ2 (S L 2) 126 は、画素電源 (V D D) 118 と画素出力2 (O U T 2) 127との間に直列接続される。選択トランジスタ2 (S L 2) 126 のゲートは、垂直操作回路 209 からの画素駆動配線 203 (S L 2) に接続され、選択信号が入力される。リセットトランジスタ2 (R T 2) 124 は、画素電源 (V D D) 118 とソースフォロアトランジスタ2 (S F 2) 125 のゲートとの間に接続される。リセットトランジスタ2 (R T 2) 124 のゲートは、垂直操作回路 209 からの画素駆動配線 203 (R T 2) に接続され、リセット信号を入力される。

#### 【0028】

また、第2の浮遊拡散容量 (F D 2) 123 は、ソースフォロアトランジスタ2 (S F 2) 125 のゲートに接続される。

図3は、図1に示す画素回路（読み出し制御回路）202を用いて、信号読み出しを行った場合における、各トランジスタの入力信号を表すタイムチャートである。

#### 【0029】

図3において、各チャートは、選択トランジスタ1、2 (S L 1、2) 116、126、リセットトランジスタ1、2 (R T 1、2) 114、124、第1の転送トランジスタ (T X) 112、オーバーフローゲート (O F G) 122 の信号波形を示すものであり、S L、R T、T X および O F G の後段に記されたかっこの中の数字 ((1) から (n)) は、対応ライン(行)上の1行目から n 行目の単位画素であることを示している。

#### 【0030】

図3に示されるように、選択トランジスタ1、2 (S L 1、2) 116、126 がオン状態 (S L 1 と S L 2 が「H」レベル) の時にリセットトランジスタ1、2 (R T 1、2) 114、124 をオン状態 (R T 1 と R T 2 が「H」レベル) とすることで、第1、第2の浮遊拡散容量 (F D 1、2) 113、123 がリセットされる。このことは、全ての行について同じである。

転送トランジスタ (T X) 112 をオン状態 (T X (1) が「H」レベル) とすることで、フォトダイオード (P D) 111 の信号電荷が転送トランジスタ (T X) 112 を経て第1の浮遊拡散容量 (F D 1) 113 へ移動し、第1の浮遊拡散容量 (F D 1) 113 で信号電圧へ変換される。第1の浮遊拡散容量 (F D 1) 113 の飽和容量を超える信号電荷が流入してきた場合には、オーバーフローゲート (O F G) 122 を経て第2の浮遊拡散容量 (F D 2) 123 へ移動し、この第2の浮遊拡散容量 (F D 2) 123 で信号電圧へ変換される。

#### 【0031】

ここで、第1の浮遊拡散容量 (F D 1) 113 の容量を小さくして変換ゲインを高く設定し、第2の浮遊拡散容量 (F D 2) 123 の容量を大きくして変換ゲインを低く設定する。

オーバーフローゲート (O F G) 122 のゲート電圧 (閾値) は第1の浮遊拡散容量 (F D 1) 113 の飽和容量を所定の値に設定するため、電圧値を調整した上で所定の一定値に固定される。第1の浮遊拡散容量 (F D 1) 113 と第2の浮遊拡散容量 (F D 2) 123 の信号電圧はソースフォロアトランジスタ1 (S F 1) 115 とソースフォロアト

10

20

30

40

50

ランジスタ2(SF2)125のゲート電極へそれぞれ印加され、ソースフォロアトランジスタ1(SF1)115とソースフォロアトランジスタ2(SF2)125からの出力電流が、画素出力1(OUT1)と画素出力2(OUT2)から別々の垂直信号線204A、Bに出力される。

#### 【0032】

図4は、実施例1に係る単位画素の平面模式図の一例を示すものであり、図1の単位画素の等価回路図に対応させたものである。

すなわち、この平面模式図では、フォトダイオード(PD)111は、転送トランジスタ(TX)112、第1の浮遊拡散容量(FD1)113、リセットトランジスタ1(RT1)114および画素電源(VDD)118を介してソースフォロアトランジスタ1(SF1)115のゲートに接続される、ことが示されている。ソースフォロアトランジスタ1(SF1)115は、選択トランジスタ1(SL1)116を介して画素出力1(OUT1)117に接続される。

#### 【0033】

一方、この平面模式図では、フォトダイオード(PD)111は、転送トランジスタ(TX)112、オーバーフローゲート(OFG)122、第2の浮遊拡散容量(FD2)123、リセットトランジスタ2(RT2)124、画素電源(VDD)118を介してソースフォロアトランジスタ2(SF2)125のゲートに接続される、ことが示されている。ソースフォロアトランジスタ2(SF2)125は、選択トランジスタ2(SL2)126を介して画素出力2(OUT2)127に接続される。

#### 【0034】

図5は、低照度である場合について、図4における平面模式図のA-A'線断面を示すものであり、(A)は露光時について、(B)は信号電荷の移動時について、各々示すものである。

なお、各ポテンシャルが示されている部位の名称は、その部位の上方に記号にて示されている(図6において同じ)。

また、図中でクロスハッチングで示す部分は、元から、第1の浮遊拡散容量(FD1)113および第2の浮遊拡散容量(FD2)123に存在する電子量を示すものであり、梨地で示す部分は、フォトダイオード(PD)111中、またはフォトダイオード(PD)111から流入した光電子量を示すものである(図6において同じ)。

これらの図から明らかなように、低照度である場合には、フォトダイオード(PD)111の光電子の量が少ないため、転送トランジスタ(TX)112がオン状態のときには、光電子は第1の浮遊拡散容量(FD1)113に移動するだけで、第2の浮遊拡散容量(FD2)123には移動しない。このため第2の浮遊拡散容量(FD2)123は元の電圧VDDのままである。

#### 【0035】

一方、図6は、高照度である場合について、図4における平面模式図のA-A'線断面を示すものであり、(A)は露光時について、(B)は信号電荷の移動時について、各々示すものである。

これらの図から明らかなように、高照度である場合には、フォトダイオード(PD)111の光電子の量が多いため、転送トランジスタ(TX)112がオン状態のときには、光電子は第1の浮遊拡散容量(FD1)113に移動するのと同時に、この第1の浮遊拡散容量(FD1)113から溢れ、第2の浮遊拡散容量(FD2)123にも移動する。このため第2の浮遊拡散容量(FD2)123では元の電圧VDDから光電子量が増大した状態となる。

#### 【0036】

図7(A)は、第1の浮遊拡散容量FD1(113)を経て画素出力回路から出力される高変換ゲインの信号と、第2の浮遊拡散容量FD2(123)を経て画素出力回路から出力される低変換ゲインの信号の入射光強度に対する関係を示す図である。

また、図7(B)は、高変換ゲイン(FD1)の信号と低変換ゲイン(FD2)の信号

10

20

30

40

50

を、この固体撮像素子の外部における後段の信号処理部（図示されていない）において信号合成される信号（合成後出力信号）を入射光強度との関係において示す図である。

この図7（A）からも分かるように、高変換ゲイン（FD1）の信号は、一定の出力値で飽和し（飽和点）、この入射光強度のときに、丁度、低変換ゲイン（FD2）の信号が立ち上がる所以、この低変換ゲイン（FD2）の信号の立ち上がり点で、両信号を繋ぎ合わせるように合成すればよい。

図示するように、この合成後の信号は、低照度時には傾きが大となって、高S/Nとされ、一方、高照度時には傾きが小となって、広ダイナミックレンジとされる。したがって、1つの信号によって、相反する2つの特性を発揮させることができる。したがって、低輝度の被写体に合わせることで高輝度の被写体の信号が飽和してしまったり、高輝度の被写体に合わせることで低輝度の被写体の信号が雑音に埋もれてしまったり、というような不都合を回避することができる。

10

さらに、本実施例では、光電変換部を分割しないで解像度特性を優れたものとすることができ、露光時間を分割しないで動画撮像特性を優れたものとすることができる、さらに高感度、高S/N化と広ダイナミックレンジ化のトレードオフを解消することができる。

#### 【0037】

次に、図8は、単位画素のポテンシャルシミュレーションによる結果を表す平面図である。転送トランジスタ（TX）112のゲート電極には2.5V、オーバーフローゲート（OFG）122のゲート電極には1.9V、リセットトランジスタ1（RT1）114、リセットトランジスタ2（RT2）124、ソースフォロアトランジスタ1（SF1）115、ソースフォロアトランジスタ2（SF2）125、選択トランジスタ1（SL1）116、選択トランジスタ2（SL2）126のゲート電極には0Vが印加されている。

20

なお、図8中において、文字を挿入することによる煩雑さによって、各部を表す線等が見難くなることを避けるため、図8の各部の番号は省略している。

#### 【0038】

また、図9は、図8におけるB-B'線断面図である。図9の例では、フォトダイオード（PD）111に光電子が空の状態を示している。

すなわち、このB-B'線断面において、フォトダイオード（PD）111は、伝導帯の底に電子がたまっていない状態となっており、空の状態となっていることが示されている。一方、第1の浮遊拡散容量（FD1）113および転送トランジスタ（TX）112下部には、電子が所定量入っている状態が示されている。

30

#### 【0039】

一方、図10は、図8におけるC-C'線断面図である。図10の例では、第1の浮遊拡散容量（FD1）113において、電子が飽和した状態が示されている。

すなわち、第1の浮遊拡散容量（FD1）113は光電子が飽和状態（オーバーフローゲート（OFG）122が満杯状態）となっており、これ以上第1の浮遊拡散容量（FD1）113に光電子が入ってくると、この光電子は第2の浮遊拡散容量（FD2）123に流入する。なお、図10に示す状態では、第2の浮遊拡散容量（FD2）123はVDD=3.3Vの状態であって元の電子の状態であり、第1の浮遊拡散容量（FD1）113からの光電子はまだ流入していない状態とされている。

40

<実施例2>

#### 【0040】

以下、本発明の実施例2について、上記図面を参照しながら説明する。

なお、実施例2のものは実施例1のものと共通する部分も多いので、以下の説明において、実施例1の各部に付した番号に200を加えた番号を実施例1の各部に対応した実施例2の各部に付し、その詳しい説明は省略する場合がある。

図12は、実施例2に係る単位画素の画素アレイを有する固体撮像素子、具体的にはCMOSイメージセンサのシステム構成を示すものであって、実施例1について示す図2と対応するものである。CMOSイメージセンサ400は、光電変換素子を含む単位画素4

50

02がアレイ状に2次元配列され、画素駆動配線403、垂直信号線404と接続している画素アレイ401を有するとともに、周辺回路として、カラム信号処理回路405、センサ外部のデジタルCDS回路410と接続される出力回路406、制御回路407、水平走査回路408、および垂直走査回路409から構成されている。

ここで、カラム信号処理回路405および水平走査回路408が、図中の上方および下方に配されているのは、片側に配された場合に比べ、フレーム周波数を2倍にすることができるという理由からである。

#### 【0041】

また、図11は、実施例2に係るCMOSイメージセンサに用いられる、画素回路(読み出し制御回路)の等価回路図を示すものである。本等価回路は、光電変換部から信号電荷を読み出す画素回路が、前記第1の浮遊拡散容量手段につき、転送トランジスタは配置されていないのでトランジスタ3個から、および前記第2の浮遊拡散容量手段につきオーバーフローゲートを含めてトランジスタ4個から構成され、低照度状態では高S/N状態、高照度状態では広ダイナミックレンジ状態となる信号を生成する構成とされている。10

図11に示すように、実施例2における読み出し制御回路は、第1の信号経路および第2の信号経路の2系統の信号経路を備えている。

#### 【0042】

図11に示すように、光電変換素子であるフォトダイオード(PD)311は第1の浮遊拡散容量(FD1)313に接続される。第1の浮遊拡散容量(FD1)313は、オーバーフローゲート(OFG)322を経て第2の浮遊拡散容量(FD2)323に接続される。20

#### 【0043】

第1の信号経路である、第1の浮遊拡散容量(FD1)313の画素出力回路は、リセットトランジスタ1(RT1)314、ソースフォロアトランジスタ1(SF1)315、選択トランジスタ1(SL1)316で構成され、画素出力1(OUT1)317は垂直信号線404Aに接続されている。

#### 【0044】

一方、第2の信号経路である、第2の浮遊拡散容量(FD2)323の画素出力回路は、リセットトランジスタ2(RT2)324、ソースフォロアトランジスタ2(SF2)325、選択トランジスタ2(SL2)326で構成され、画素出力2(OUT2)327は、上記とは別の垂直信号線404Bに接続されている。30

#### 【0045】

リセットトランジスタ1(RT1)314、ソースフォロアトランジスタ1(SF1)315、リセットトランジスタ2(RT2)324、ソースフォロアトランジスタ2(SF2)325の各ドレイン電極は、画素電源(VDD)318に接続されている。

#### 【0046】

また、オーバーフローゲート(OFG)322、リセットトランジスタ1(RT1)314、リセットトランジスタ2(RT2)324、選択トランジスタ1(SL1)316、選択トランジスタ2(SL2)326の各ゲート電極は、それぞれの画素駆動配線403に接続されている。40

#### 【0047】

図11に示す単位画素402の画素回路(読み出し制御回路)において、フォトダイオード(PD)311は、入射光の強度に応じた量の負電荷を発生する。このフォトダイオード(PD)311のアノードは接地され、カソードは第1の浮遊拡散容量(FD1)313を介してソースフォロアトランジスタ1(SF1)315のゲートに接続される。

#### 【0048】

第1の信号経路において、ソースフォロアトランジスタ1(SF1)315および選択トランジスタ1(SL1)316は、画素電源(VDD)318と画素出力1(OUT1)317との間に直列接続される。選択トランジスタ1(SL1)316のゲートは、垂直操作回路409からの画素駆動配線403(SL1)に接続され、選択信号が入力され50

る。リセットトランジスタ1( R T 1 ) 3 1 4 は、画素電源( V D D ) 3 1 8 とソースフォロアトランジスタ1( S F 1 ) 3 1 5 のゲートとの間に接続される。リセットトランジスタ1( R T 1 ) 3 1 4 のゲートは、垂直操作回路4 0 9 からの画素駆動配線4 0 3 ( R T 1 ) に接続され、リセット信号を入力される。

#### 【 0 0 4 9 】

また、第1の浮遊拡散容量( F D 1 ) 3 1 3 は、ソースフォロアトランジスタ1( S F 1 ) 3 1 5 のゲートに接続される。

前述したように、第2の浮遊拡散容量( F D 2 ) 3 2 3 は、オーバーフローゲート( O F G ) 3 2 2 を経て第1の浮遊拡散容量( F D 1 ) 3 1 3 に接続されており、第1の浮遊拡散容量( F D 1 ) 3 1 3 に蓄積された電荷が、オーバーフローゲート( O F G ) 3 2 2 から溢れると、第2の浮遊拡散容量( F D 2 ) 3 2 3 に入力される。

10

#### 【 0 0 5 0 】

第2の信号経路において、ソースフォロアトランジスタ2( S F 2 ) 3 2 5 および選択トランジスタ2( S L 2 ) 3 2 6 は、画素電源( V D D ) 3 1 8 と画素出力2( O U T 2 ) 3 2 7 との間に直列接続される。選択トランジスタ2( S L 2 ) 3 2 6 のゲートは、垂直操作回路( 図12において番号4 0 9 が付されている：以下同じ ) からの画素駆動配線4 0 3 ( S L 2 ) に接続され、選択信号が入力される。リセットトランジスタ2( R T 2 ) 3 2 4 は、画素電源( V D D ) 3 1 8 とソースフォロアトランジスタ2( S F 2 ) 3 2 5 のゲートとの間に接続される。リセットトランジスタ2( R T 2 ) 3 2 4 のゲートは、垂直操作回路4 0 9 からの画素駆動配線4 0 3 ( R T 2 ) に接続され、リセット信号を入力される。

20

#### 【 0 0 5 1 】

また、第2の浮遊拡散容量( F D 2 ) 3 2 3 は、ソースフォロアトランジスタ2( S F 2 ) 3 2 5 のゲートに接続される。

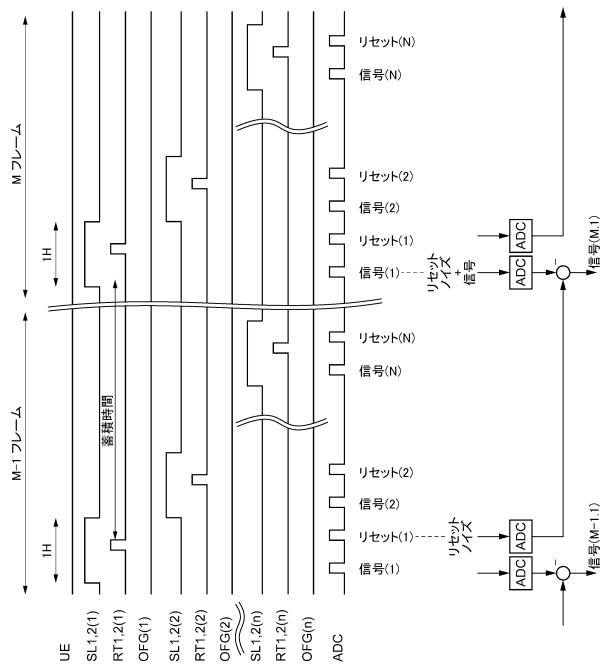

図13は、図11に示す画素回路( 読出し制御回路 ) 4 0 2 を用いて、信号読出しを行った場合における、各トランジスタの入力信号を表すタイムチャートである。

#### 【 0 0 5 2 】

図13において、各チャートは、選択トランジスタ1、2( S L 1、2 ) 3 1 6、3 2 6、リセットトランジスタ1、2( R T 1、2 ) 3 1 4、3 2 4、オーバーフローゲート( O F G ) 3 2 2 の信号波形を示すものであり、S L、R T およびO F G の後段に記されたかっこの中の数字( ( 1 ) から( n ) )は、対応ライン( 行 )上の1行目からn行目の単位画素であることを示している。A D C は、A D 変換器のサンプリングのタイミングを示している。従来技術では、画素回路がトランジスタ3個から構成される場合、駆動波形は後リセット方式のデジタル式相關二重サンプリング( デジタルC D S )によってリセットノイズを除去する。本方式は画素回路がトランジスタ3個から構成される場合からの改良であるので、駆動波形は後リセット方式のデジタルC D S によってリセットノイズを除去するようになっている。

30

#### 【 0 0 5 3 】

図13に示されるように、選択トランジスタ1、2( S L 1、2 ) 3 1 6、3 2 6 がオン状態( S L 1とS L 2 が「H」レベル)の時にリセットトランジスタ1、2( R T 1、2 ) 3 1 4、3 2 4 をオン状態( R T 1とR T 2 が「H」レベル)とすることで、第1、第2の浮遊拡散容量( F D 1、2 ) 3 1 3、3 2 3 がリセットされる。このことは、全ての行について同じである。

40

フォトダイオード( P D ) 3 1 1 の信号電荷は、第1の浮遊拡散容量( F D 1 ) 3 1 3 へ移動し、第1の浮遊拡散容量( F D 1 ) 3 1 3 で信号電圧へ変換される。第1の浮遊拡散容量( F D 1 ) 1 1 3 の飽和容量を超える信号電荷が流入してきた場合には、オーバーフローゲート( O F G ) 3 2 2 を経て第2の浮遊拡散容量( F D 2 ) 3 2 3 へ移動し、この第2の浮遊拡散容量( F D 2 ) 3 2 3 で信号電圧へ変換される。

#### 【 0 0 5 4 】

ここで、第1の浮遊拡散容量( F D 1 ) 3 1 3 の容量を小さくして変換ゲインを高く設

50

定し、第2の浮遊拡散容量(FD2)323の容量を大きくして変換ゲインを低く設定する。

オーバーフローゲート(OFG)322のゲート電圧(閾値)は第1の浮遊拡散容量(FD1)313の飽和容量を所定の値に設定するため、電圧値を調整した上で所定の一一定値に固定される。第1の浮遊拡散容量(FD1)313と第2の浮遊拡散容量(FD2)323の信号電圧はソースフォロアトランジスタ1(SF1)315とソースフォロアトランジスタ2(SF2)325のゲート電極へそれぞれ印加され、ソースフォロアトランジスタ1(SF1)315とソースフォロアトランジスタ2(SF2)325からの出力電流が、画素出力1(OUT1)と画素出力2(OUT2)から別々の垂直信号線404A、Bに出力される。10

#### 【0055】

図14は、実施例2に係る単位画素の平面模式図の一例を示すものであり、図11の単位画素の等価回路図に対応させたものである。

すなわち、この平面模式図では、フォトダイオード(PD)311は、第1の浮遊拡散容量(FD1)313、リセットトランジスタ1(RT1)314および画素電源(VDD)318を介してソースフォロアトランジスタ1(SF1)315のゲートに接続される、ことが示されている。ソースフォロアトランジスタ1(SF1)315は、選択トランジスタ1(SL1)316を介して画素出力1(OUT1)317に接続される。

#### 【0056】

一方、この平面模式図では、フォトダイオード(PD)311は、オーバーフローゲート(OFG)322、第2の浮遊拡散容量(FD2)323、リセットトランジスタ2(RT2)324、画素電源(VDD)318を介してソースフォロアトランジスタ2(SF2)325のゲートに接続される、ことが示されている。ソースフォロアトランジスタ2(SF2)325は、選択トランジスタ2(SL2)326を介して画素出力2(OUT2)327に接続される。20

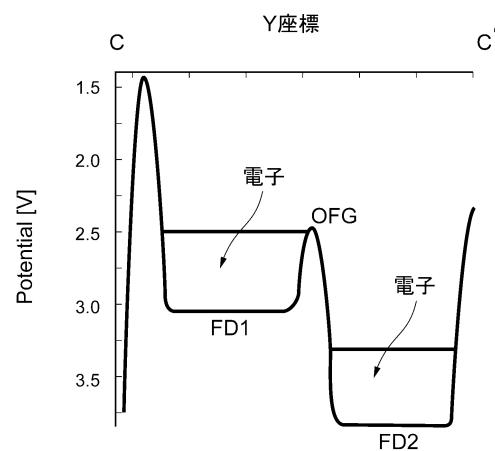

#### 【0057】

図15(A)は、低照度である場合について、平面模式図である図14のA-A'線断面を示すものであり、信号電荷の移動時について、示すものである。

なお、各ポテンシャルが示されている部位の名称は、その部位の上方に記号にて示されている。30

また、図中でクロスハッチングで示す部分は、第1の浮遊拡散容量(FD1)313および第2の浮遊拡散容量(FD2)323に存在する電子量を示すものであり、梨地で示す部分は、フォトダイオード(PD)311から流入した光電子量を示すものである。

これらの図から明らかに、低照度である場合には、フォトダイオード(PD)311の光電子の発生量が少ないため、光電子は第1の浮遊拡散容量(FD1)313に移動するだけで、第2の浮遊拡散容量(FD2)323には移動しない。このため第2の浮遊拡散容量(FD2)323は元の電圧VDDのままである。

#### 【0058】

一方、図15(B)は、高照度である場合について、図14におけるポテンシャル図のA-A'線断面を示すものであり、信号電荷の移動時について、示すものである。40

これらの図から明らかに、高照度である場合には、フォトダイオード(PD)311の光電子の発生量が多いため、光電子は第1の浮遊拡散容量(FD1)313に移動するのと同時に、この第1の浮遊拡散容量(FD1)313から溢れ、第2の浮遊拡散容量(FD2)323にも移動する。このため第2の浮遊拡散容量(FD2)323では元の電圧VDDから光電子量が増大した状態となる。

#### 【0059】

なお、本実施例において、第1の浮遊拡散容量FD1(313)を経て画素出力回路から出力される高変換ゲインの信号と、第2の浮遊拡散容量FD2(323)を経て画素出力回路から出力される低変換ゲインの信号の入射光強度に対する関係は、実施例1において図7を用いて行った説明と同様であるので、ここではその説明を省略する。50

**【0060】**

次に、図16は、単位画素のポテンシャルシミュレーションによる結果を表す平面図である。オーバーフローゲート(OFG)322のゲート電極には1.9V、リセットトランジスタ1(RT1)314、リセットトランジスタ2(RT2)324、ソースフォロアトランジスタ1(SF1)315、ソースフォロアトランジスタ2(SF2)325、選択トランジスタ1(SL1)316、選択トランジスタ2(SL2)326のゲート電極には0Vが印加されている。

実施例1における同様の図である図8と比べると、フォトダイオード(PD)311と第1の浮遊拡散容量(FD1)313との間に転送トランジスタ(TX)112が設けられていない点が相違している(図17について同じ)。

10

**【0061】**

また、図17は、図16におけるB-B'線断面図である。図17の例では、フォトダイオード(PD)311に光電子が空の状態を示している。

すなわち、このB-B'線断面において、フォトダイオード(PD)311は、伝導帯の底に電子がたまっていない状態となっており、空の状態となっていることが示されている。一方、第1の浮遊拡散容量(FD1)313下部には、電子が所定量入っている状態が示されている。

**【0062】**

一方、図16におけるC-C'線断面図である図18は、実施例1における図8のC-C'線断面図と同様であるので、図18の説明は省略する。

20

以上のように形成された実施例2においては、実施例1のものと共通した構成も多いが、互いに相違する部分も存在する。以下、この相違点を中心として列挙形式にて説明する。

**【0063】**

## &lt;実施例1と実施例2の相違点&gt;

実施例1は4トランジスタの画素回路を前提に広ダイナミックレンジ機能を持たせたものとしているのに対し、実施例2は3トランジスタの画素回路を前提に広ダイナミックレンジ機能を持たせたものとしている。したがって、実施例1と実施例2は、前提が4トランジスタの画素回路と3トランジスタの画素回路という点において、互いに相違する(下記相違点1)。

30

また、実施例1は、4トランジスタの画素回路に広ダイナミックレンジ機能を持たせたものであり、実施例2は、3トランジスタの画素回路に広ダイナミックレンジ機能を持たせたものであることから、互いに異なる画素回路に広ダイナミックレンジ機能を持たせたことによる作用効果の違いにおいて相違する(下記相違点2)。

**【0064】****[1] 相違点1****(1) 等価回路およびレイアウト**

実施例1のものでは、第1の浮遊拡散容量につき、転送トランジスタ(TX)、リセットトランジスタ1(RT1)、ソースフォロアトランジスタ1(SF1)、および選択トランジスタ1(SL1)の4つのトランジスタ(4トランジスタ方式)で構成されており、第2の浮遊拡散容量につき、オーバーフローゲート(OFG)、リセットトランジスタ2(RT2)、ソースフォロアトランジスタ2(SF2)、および選択トランジスタ2(SL2)の4つのトランジスタで構成されている。

40

これに対し、実施例2のものでは、転送トランジスタ(TX)が設けられておらず、第1の浮遊拡散容量につき、リセットトランジスタ1(RT1)、ソースフォロアトランジスタ1(SF1)、および選択トランジスタ1(SL1)の3つのトランジスタ(3トランジスタ方式)で構成されており、第2の浮遊拡散容量につき、オーバーフローゲート(OFG)、リセットトランジスタ2(RT2)、ソースフォロアトランジスタ2(SF2)、および選択トランジスタ2(SL2)の4つのトランジスタで構成されている。

ただし、上記実施例1において、転送トランジスタ(TX)をON状態に保持すること

50

で、実施例 2 のような 3 トランジスタ用の駆動手法を適用することができる。

#### ( 2 ) 駆動波形について

4 トランジスタ方式の実施例 1においては、リセットしてから信号を読む、前リセット方式を採用しているので、アナログ CDS を画素と A/D 変換器の間に配置して、リセットノイズを除去することができる。

これに対し、3 トランジスタ方式の実施例 2においては、信号を読んでからリセットする、後リセット方式を採用することになるので、アナログ CDS を画素と A/D 変換器の間に配置しても、リセットノイズを除去することができない。リセットノイズと 1 フレーム後の信号（信号 + リセットノイズ）との間に、リセットノイズに関する相関がある（リセットノイズが略同一レベル）ので、デジタル CDS を適用してリセットノイズを除去することができる。なお、デジタル CDS（図 12 のデジタル CDS 410 を参照）としてはセンサチップ外部にフレームメモリを配置することにより構成することができる。10

#### ( 3 ) 最高フレーム周波数について

3 トランジスタ方式の実施例 2において、デジタル CDS を採用している場合、リセットノイズと、1 フレーム後の信号（信号 + リセットノイズ）とを A/D 変換器で読み出し、両者の差を求め、リセットノイズを相殺して、1 フレーム分の画像信号としている（図 13 を参照）ので、画素以外の回路構成が同じ場合には、3 トランジスタ方式を採用した場合は、4 トランジスタ方式を採用した場合に比べて、最高フレーム周波数が 1/2 となる。20

#### ( 4 ) ノイズについて

4 トランジスタ方式のリセットノイズと信号（信号 + リセットノイズ）間のリセットノイズの相関性は、3 トランジスタ方式のリセットノイズと信号（信号 + リセットノイズ）間のリセットノイズの相関性よりも強いので、4 トランジスタ方式の方が CDS でのリセットノイズのキャンセル効果が大きい。20

#### ( 5 ) 飽和信号量について

4 トランジスタ方式の飽和信号量は、フォトダイオード（PD）の飽和電子量で規定される。露光時にフォトダイオード（PD）からあふれた電子は、浮遊拡散容量（FD）に移動し、リセット時に画素電源（VDD）に放出される。各フレームの蓄積期間にフォトダイオード（PD）からあふれた電子は使用されない。

一方、3 トランジスタ方式の飽和信号量は、浮遊拡散容量（FD）の飽和電子量で規定される。フォトダイオード（PD）が n- 型で不純物濃度が低いのに対し、浮遊拡散容量（FD）は n+ 型で不純物濃度が高いので、浮遊拡散容量（FD）は状態密度が高く、面積が小さくても、フォトダイオード（PD）よりも飽和電子量が大きい。各フレームの蓄積期間に浮遊拡散容量（FD）からあふれた電子は使用されない。30

#### ( 6 ) フォトダイオード（PD）の感度について

各画素にマイクロレンズを付設していない場合、フォトダイオード（PD）の感度はフォトダイオード（PD）の面積により規定される。これに対して、各画素にマイクロレンズを付設している場合、入射光が画素上に集光されるので、フォトダイオード（PD）の感度はフォトダイオード（PD）の面積よりもマイクロレンズの性能に大きく影響される。4 トランジスタ方式であるか、3 トランジスタ方式であるかによって、フォトダイオード（PD）の感度が大きく影響を受けるものではない。40

#### 【 0065 】

#### [ 2 ] 相違点 2

( 1 ) 実施例 1 に係る 4 トランジスタ画素回路を前提に広ダイナミックレンジ機能を持たせたもの（以下、広 DR 機能付き 4 Tr. 方式と称する場合がある）と、実施例 2 に係る 3 トランジスタ画素回路を前提に広ダイナミックレンジ機能を持たせたもの（以下、広 DR 機能付き 3 Tr. 方式と称する場合がある）とを比較する前に、広 DR 機能を付加することによる効果について言及する。

この効果としては、(A) 光電変換部を分割しないでも、解像度特性において優れていること、(B) 露光時間を分割しないでも、動画撮像特性において優れていること、(C) 50

) 画素出力信号において、高感度、高 S/N 化と、広ダイナミックレンジ化のトレードオフを解消し得ること、(D) 超多画素において高フレーム周波数化がされること、が挙げられる。

### (2) 広 D R 機能の具体的な構成および効果

第 1 の浮遊拡散容量 (FD1) と第 2 の浮遊拡散容量 (FD2) がオーバーフローゲート (OFG) により接続して構成され、第 1 の浮遊拡散容量 (FD1) の飽和電子量をオーバーフローゲート (OFG) のゲート電圧で調整するとともに、第 1 の浮遊拡散容量 (FD1) からあふれた電子を第 2 の浮遊拡散容量 (FD2) に移動させる。第 1 の浮遊拡散容量 (FD1) と第 2 の浮遊拡散容量 (FD2) は、各々の画素回路を介し、出力部 OUT1、2 から、互いに異なる信号を出力する。第 1 の浮遊拡散容量 (FD1) の面積は小さく電荷電圧変換係数が高く、一方、第 2 の浮遊拡散容量 (FD2) の面積は大きく電荷電圧変換係数が低い。低照度側は、第 1 の浮遊拡散容量 (FD1) のみを使用して高感度、高 S/N 信号とし、一方、高照度側は、第 1 の浮遊拡散容量 (FD1) および第 2 の浮遊拡散容量 (FD2) を使用して高感度、広 D R 信号とし、センサチップ外部で上記 2 つの信号を合成して、広 D R 信号を得る。10

なお、広 D R 機能付き 4 Tr. 方式と、広 D R 機能付き 3 Tr. 方式の、各広 D R 機能自体は同じである。

### (3) 最高フレーム周波数について

画素出力が 2 種類、設けられていることから、それぞれに対して A/D 変換器を配設することで、最高フレーム周波数の低下を抑制して、従来技術と同等のフレーム周波数とすることが可能である。20

### (4) ノイズ、飽和信号量、およびフォトダイオード (PD) の感度について

ノイズ、飽和信号量、およびフォトダイオード (PD) の感度については、上記相違点 1 と同様である。

### (5) 広 D R 機能付き 3 Tr. 方式に光電変換膜を用いる場合について

広 D R 機能付き 3 Tr. 方式は、光電変換膜を積層することによって以下のようない点を有している（下記実施例 3 を参照）。この場合、光電変換膜の膜材料は特に限定されるものではない。

光電変換膜を積層した広 D R 機能付き 3 Tr. 方式は、浮遊拡散容量 (FD) の n+ 型 Si と VIA の金属が、バリアが無い状態で接続されているので、リセットの動作時間と信号の読み出時間を短縮することができる（従来技術における 3 Tr. 方式の場合と同等とすることができる）。

なお、光電変換膜を積層した広 D R 機能付き 4 Tr. 方式は、構造として光電変換膜を積層することはできるが、フォトダイオード (PD) の n- 型 Si と VIA の金属が接続され、浮遊拡散容量 (FD) の n+ 型 Si と VIA の金属の間に、フォトダイオード (PD) の n- 型 Si が入り込み、バリアとして機能するので、リセットの動作時間と信号の読み出時間が長くなるため、問題がある。

また、実施例 2 に示すような、一般的のフォトダイオード (PD) を用いた広 D R 機能付き 3 Tr. 方式では、画素内においてトランジスタが 7 個存在し、これらトランジスタが占める面積割合が大きく、フォトダイオード (PD) の開口率が低くなってしまうため、マイクロレンズにより集光させることが必要であるが、後述する実施例 3 に示すような、光電変換膜を積層した広 D R 機能付き 3 Tr. 方式のものでは、マイクロレンズなしに開口率を約 100% にすることができる。40

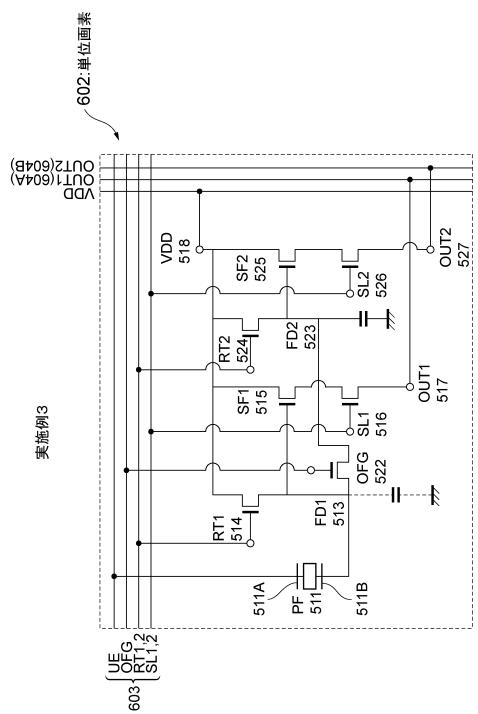

#### 【0066】

#### <実施例 3 >

上記実施例 2 において、フォトダイオード (PD) 311 を光電変換膜 (PF) 511 に置き換えることができるので、このようにフォトダイオード (PD) 311 の部分のみを光電変換膜 (PF) 511 に置き換えたものを実施例 3 として、以下に説明する。

#### 【0067】

図 19 に示すように、実施例 3 に係る単位画素 602 の画素アレイを有する固体撮像素子50

子、具体的にはC M O Sイメージセンサに用いられる、画素回路（読み出し制御回路）の等価回路図を示すものである。実施例3のものは、実施例2のものと共に通する部分も多いので、以下の説明においては、実施例2の各部に付した番号に200を加えた番号を、実施例2の各部に対応した実施例3の各部に付し、その詳しい説明は省略する場合がある。

#### 【0068】

図19に示すように、実施例3における光電変換部は、光電変換膜（P F）511とされている。光電変換膜（P F）511は、各単位画素602上に積層されており、第1の浮遊拡散容量（F D 1）513に接続される。

このように、光電変換膜を各単位画素602上に積層することにより、各単位画素602を配置するスペースを有效地に利用することができ、画素の密度を高めることができる。

#### 【0069】

図19に示す単位画素602の画素回路（読み出し制御回路）において、光電変換膜（P F）511は、入射光の強度に応じた量の負電荷を発生する。この光電変換膜（P F）511の上部電極（U E）511Aは画素駆動配線（U E）603に接続され、下部電極（L E）511Bは第1の浮遊拡散容量（F D 1）513を介してソースフォロアトランジスタ1（S F 1）515のゲートに接続される。

#### 【0070】

図20は、図19に示す画素回路（読み出し制御回路）を用いて、信号読み出しを行った場合における、各トランジスタの入力信号を表すタイムチャートを示すものである。

#### 【0071】

図20における各チャートは、実施例2において説明した図13における各チャート（最上部の上部電極（U E）のチャート以外）と同様であるので各チャートについての説明は省略する。

なお、上部電極（U E）には、常時、L信号が入力されることにより、光電変換膜がON状態であることが維持されるように構成されている。

#### 【0072】

図21は、単位画素の平面模式図と断面模式図の一例を示すものであり、図19の単位画素602の等価回路図に対応させたものである。

すなわち、この平面模式図と断面模式図では、光電変換膜（P F）511は、上部電極（U E）511Aおよび下部電極（L E）511Bによって挟まれた構造とされており、図19に示すように、上部電極（U E）511Aは画素駆動配線（U E）603に接続され、下部電極（L E）511Bは第1の浮遊拡散容量（F D 1）513に接続されている。実施例2の図14と比較すると、大きな面積を占めるフォトダイオード（P D）311が無いので、画素サイズの小型化を図ることができる。

#### 【0073】

また、この平面模式図と断面模式図では、下部電極（L E）511Bが第1の浮遊拡散容量（F D 1）513に接続され、第1の浮遊拡散容量（F D 1）513はオーバーフローゲート（O F G）522を経て第2の浮遊拡散容量（F D 2）523に接続される、これが示されている。

#### 【0074】

ここでは、光電変換膜（P F）511のキャリアは電子であり上部電極（U E）511Aに負電圧が印加されている場合について記載したが、キャリアが正孔であり上部電極（U E）に正電圧が印加されている場合についても同様の効果が得られる。

#### 【0075】

本実施形態の撮像装置、駆動方法および読み出し制御回路においては、上述したような構成とされたことで、低照度状態においては、飽和レベルを狭めることなく、線形かつ高S/Nの信号取得を行うことができ、高照度状態においては、線形領域での良好なS/Nを確保しつつダイナミックレンジを拡大することができる。

特に、低照度状態用と高照度状態用とで、それぞれが、画素出力回路と信号出力線を備えているため、同一時刻に同一光電変換部で得られた光信号を高フレーム周波数で読みだ

10

20

30

40

50

すことが可能であり、優れた動画撮像特性と解像度特性を有しつつ、超多画素を高フレーム周波数で読みだす撮像機器に対応することができる。

このような作用効果は、例えば、従来技術において説明した特許文献2（特許第5066704号公報）に記載のものに比べて、スーパーハイビジョン等のように、超多画素を高フレーム周波数で読みだす場合に、極めて有利である。

#### 【0076】

さらに、本発明の読み出し制御回路、固体撮像素子、および撮像素子の駆動方法としては、上記実施形態のものに限られるものではなく、その他の種々の態様のものを採用し得る。例えば、上記実施形態においては、画像出力回路部を2組、出力信号線を2つ、各々設けているが、これに替えて画像出力回路部を3組以上、出力信号線を3つ以上設けてよい。画像出力回路部を3組、出力信号線を3つとしたときは、高照度、中照度、低照度の各露光時に対応させることができる。10

#### 【0077】

また、各単位画素の等価回路構成としても図1、図11および図19に示す回路のものに限られるものではなく、その他の種々の態様のものに変更することが可能であり、各画素出力回路部におけるトランジスタの数を増加させることも可能である。

また、各浮遊拡散容量（FD1、2）113、123、313、323、513、523の飽和状態電圧（オーバーフローゲート（OFG）のゲート設定値）や各種トランジスタのゲート電圧としても、上記実施形態のものに限られるものではなく、適切な値に設定することが可能である。20

#### 【符号の説明】

#### 【0078】

|                          |                       |    |

|--------------------------|-----------------------|----|

| 111、311                  | フォトダイオード（P D）         |    |

| 112                      | 転送トランジスタ（T X）         |    |

| 113、313、513              | 第1の浮遊拡散容量（F D 1）      |    |

| 114、314、514              | リセットトランジスタ1（R T 1）    |    |

| 115、315、515              | ソースフォロアトランジスタ1（S F 1） |    |

| 116、316、516              | 選択トランジスタ1（S L 1）      |    |

| 117、317、517              | 画素出力1（O U T 1）        |    |

| 118、318、518              | 画素電源（V D D）           | 30 |

| 122、322、522              | オーバーフローゲート（O F G）     |    |

| 123、323、523              | 第2の浮遊拡散容量（F D 2）      |    |

| 124、324、524              | リセットトランジスタ2（R T 2）    |    |

| 125、325、525              | ソースフォロアトランジスタ2（S F 2） |    |

| 126、326、526              | 選択トランジスタ2（S L 2）      |    |

| 127、327、527              | 画素出力2（O U T 2）        |    |

| 200、400                  | C M O Sイメージセンサ        |    |

| 201、401                  | 画素アレイ                 |    |

| 202、402、602              | 単位画素                  |    |

| 203、403、603              | 画素駆動配線                | 40 |

| 204、204A、B、404A、B、604A、B | 垂直信号線                 |    |

| 205、405                  | カラム信号処理回路             |    |

| 206、406                  | 出力回路                  |    |

| 207、407                  | 制御回路                  |    |

| 208、408                  | 水平走査回路                |    |

| 209、409                  | 垂直走査回路                |    |

| 410                      | デジタルC D S             |    |

| 511                      | 光電変換膜（P F）            |    |

| 511A                     | 上部電極（U E）             |    |

| 511B                     | 下部電極（L E）             | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 10】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

## 【図22】

---

フロントページの続き

(56)参考文献 特開2003-134396(JP,A)

特開2015-103958(JP,A)

特開2008-035395(JP,A)

特開2013-031116(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11

H01L 27/146