(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4555642号

(P4555642)

(45) 発行日 平成22年10月6日(2010.10.6)

(24) 登録日 平成22年7月23日(2010.7.23)

(51) Int.Cl.

F 1

HO4N 5/335 (2006.01)

HO4N 5/335 780

HO4N 9/07 (2006.01)

HO4N 9/07 C

HO4N 101/00 (2006.01)

HO4N 101:00

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2004-262231 (P2004-262231)

(73) 特許権者 000000376

(22) 出願日 平成16年9月9日(2004.9.9)

オリンパス株式会社

(65) 公開番号 特開2006-80853 (P2006-80853A)

東京都渋谷区幡ヶ谷2丁目43番2号

(43) 公開日 平成18年3月23日(2006.3.23)

(74) 代理人 100106909

審査請求日 平成19年7月10日(2007.7.10)

弁理士 棚井 澄雄

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100101465

弁理士 青山 正和

(74) 代理人 100094400

弁理士 鈴木 三義

(74) 代理人 100086379

弁理士 高柴 忠夫

最終頁に続く

(54) 【発明の名称】信号処理回路

## (57) 【特許請求の範囲】

## 【請求項 1】

2次元に配列された画素から出力される画素信号のうち、複数の行に属する画素の画素信号を画素配列の順序とは異なる所定の順序で出力するように設計されたカラー撮像素子を用いて該カラー撮像素子の画素配列の順序でカラー撮像信号を処理するための信号処理回路であって、

前記カラー撮像素子から出力される画素信号を保持するラインメモリと、

該ラインメモリを制御するための書き込みアドレスと読み出しアドレスを生成するメモリ制御部を備え、

該メモリ制御部が生成する前記読み出しアドレスは、前記ラインメモリから読み出される前記画素信号の読み出し順序が、前記カラー撮像素子の画素配列の順序となるアドレスであり、

前記カラー撮像素子から最初に出力される行に属する画素の画素信号が前記ラインメモリから読み出されたとの書き込みアドレスが、非連続のアドレスであることを特徴とする信号処理回路。

## 【請求項 2】

前記メモリ制御部は、前記読み出しアドレスに追従して、前記書き込みアドレスを生成することを特徴とする請求項1に記載の信号処理回路。

## 【請求項 3】

前記カラー撮像素子は、ベイヤ配列の色フィルタが貼付された受光面を具備しているこ

10

20

とを特徴とする請求項1に記載の信号処理回路。

【請求項 4】

前記メモリ制御部は、前記読み出しアドレスと前記書き込みアドレスとを異なる周波数で発生させることを特徴とする請求項1に記載の信号処理回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子から出力されるカラー撮像信号に対して信号処理を行う信号処理回路に関し、特に撮像素子の画素配列とは異なる順番でカラー撮像信号を出力する撮像素子を用いた信号処理回路に関する。 10

【背景技術】

【0002】

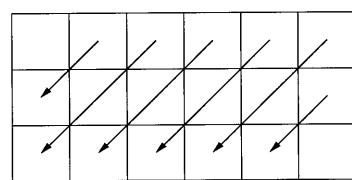

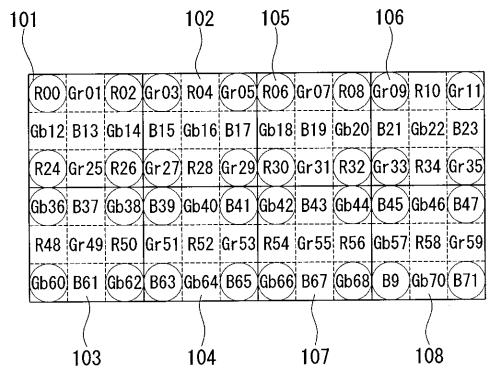

CCDやCMOSセンサ等の撮像素子を用いてカラー撮像信号を得て、デジタル信号として信号処理を行うデジタルカメラなどの撮像回路では、図14に示されるようなベイア配列で色が配置されている撮像素子からカラー撮像信号が水平ライン毎に出力される。例えばデジタルカメラにおいて静止画撮影を行う場合、全カラー撮像信号を読み出し、自動露出制御、自動焦点制御等の制御処理を行う。

【0003】

近年、デジタルカメラにも動画撮影機能が求められている。撮像素子で撮像したカラー撮像信号を上記のように水平ラインごとに読み出し、動画機能を実現する場合、読み出しに時間がかかり、テレビジョン信号と同程度の30fpsでの読み出しを実現することが困難である。動画機能を実現するために、水平方向に数ラインずつ間引いて読み出すことで、読み出しにかかる時間を短くする方式の撮像素子が提案されているが、必要な撮像データを間引くことになり、自動露出制御、自動焦点制御等の処理を行うのに適さない。 20

【0004】

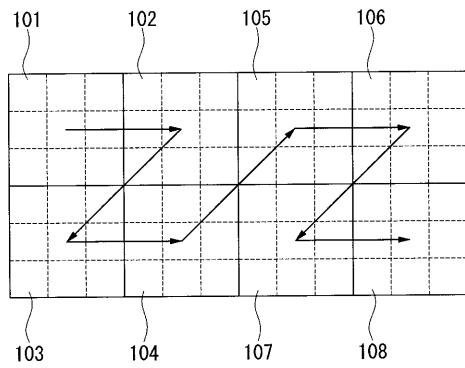

そこで、特許文献1に示されているように、水平方向および垂直方向を小ブロックに分割し、ブロック内ごとに同色のカラー撮像信号を加算することにより、必要なカラー撮像信号を間引かずに、データ数を削減する方式の撮像素子が提案されている。この撮像素子から、カラー撮像信号は以下のように出力される。図15に示されるように、撮像素子において、カラー撮像信号を水平方向3画素、垂直方向3画素ずつのブロックに分け、各ブロックの中央行と中央列を除く、印で囲まれた画素を加算する。図15においてブロック101でR00+R02+R24+R26、ブロック102でGr03+Gr05+Gr27+Gr29、ブロック103でGb36+Gb38+Gb60+Gb62、ブロック104でB39+B41+B63+B65・・・と色ごとに加算された結果が求められる。 30

【0005】

撮像素子において加算されたカラー撮像信号は、図16に示されるように、ブロック101、ブロック102、ブロック103、ブロック104、ブロック105、ブロック106、ブロック107、ブロック108・・・の順に出力される。このように水平方向および垂直方向に各色ごとに加算処理を行うことにより、撮像素子から出力されるカラー撮像信号の数を水平方向に1/3、垂直方向に1/3、合計1/9に少なくすることができ、動画時のような高速の読み出しに対応が可能となる。 40

【特許文献1】特開平11-234688号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかし、上記の撮像素子より出力されるカラー撮像信号は、図14に示される、水平方向に1ラインずつ出力する撮像素子の画素配列とは異なる順番で後段の処理回路に入力されるため、撮像素子の画素配列の順番でカラー撮像信号を処理することを前提にした信号 50

処理装置をそのまま使用することができないという問題があった。

#### 【0007】

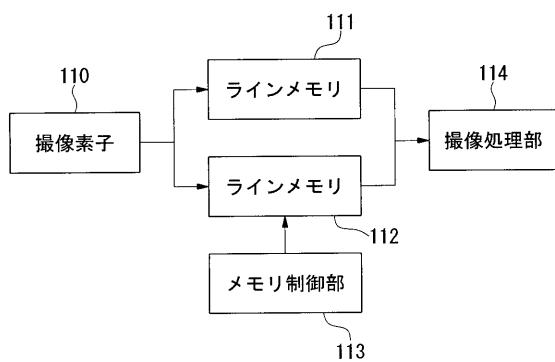

そこで、撮像素子から出力されるカラー撮像信号をメモリに保持し、カラー撮像信号の順序を入れ替えることにより、画素配列を変換する回路が用いられていた。図17は、画素配列を変換する信号処理回路の構成を示すブロック図である。図において撮像素子110は、図16に示される順番でカラー撮像信号を出力するように設計されている。ラインメモリ111および112は、撮像素子110から出力されるカラー撮像信号をそれぞれ1水平期間分保持する。ラインメモリ111は、撮像素子110から出力される奇数番目のラインのカラー撮像信号を保持し、ラインメモリ112は偶数番目のラインのカラー撮像信号を保持する。メモリ制御部113は、ラインメモリ111および112に対するカラー撮像信号の書き込みおよび読み出しを制御する。撮像処理部114は、ラインメモリ112からベイヤ形式に変換されて読み出されたカラー撮像信号を用いて、自動露出制御や自動焦点制御等の制御を行う。10

#### 【0008】

メモリ制御部113は、ラインメモリ111にカラー撮像信号を書き込んでいる期間においては、ラインメモリ112に書き込まれたカラー撮像信号を、撮像素子110の画素配列の順番になるように読み出す。また、これとは逆にラインメモリ112にカラー撮像信号を書き込んでいる期間においては、ラインメモリ111に書き込まれたカラー撮像信号を、撮像素子110の画素配列になるように読み出す。例えば、図16に示されるブロック101～ブロック108によって1ライン分のカラー撮像信号が構成されている場合には、ブロック101, 102, 105, 106, 103, 104, 107, 108の順でカラー撮像信号が読み出される。20

#### 【0009】

このように、図17に示される構成においては、1ライン分の撮像素子を保持する2つのラインメモリの動作を書き込みと読み出しとでラインごとに交互に切り替えることにより、配列を変換するようになされる。

#### 【0011】

本発明は、上述した課題に鑑みてなされたものであって、より簡単な装置構成を用いて、撮像素子の画素配列とは異なる配列で撮像信号を出力するように設計されたカラー撮像素子の撮像信号を、画素配列と同じ配列に変換することができる信号処理装置を提供することを目的とする。30

#### 【課題を解決するための手段】

#### 【0012】

本発明は上記の課題を解決するためになされたもので、2次元に配列された画素から出力される画素信号のうち、複数の行に属する画素の画素信号を画素配列の順序とは異なる所定の順序で出力するように設計されたカラー撮像素子を用いて該カラー撮像素子の画素配列の順序でカラー撮像信号を処理するための信号処理回路であって、前記カラー撮像素子から出力される画素信号を保持するラインメモリと、該ラインメモリを制御するための書き込みアドレスと読み出しアドレスを生成するメモリ制御部を備え、該メモリ制御部が生成する前記読み出しアドレスは、前記ラインメモリから読み出される前記画素信号の読み出し順序が、前記カラー撮像素子の画素配列の順序となるアドレスであり、前記カラー撮像素子から最初に出力される行に属する画素の画素信号が前記ラインメモリから読み出されたとの書き込みアドレスが、非連続のアドレスであることを特徴とする信号処理回路である。40

また、本発明の信号処理回路において、前記メモリ制御部は、前記読み出しアドレスに追従して、前記書き込みアドレスを生成することを特徴とする。

#### 【0014】

また、本発明の信号処理回路において、前記カラー撮像素子は、ベイヤ配列の色フィルタが貼付された受光面を具備していることを特徴とする。

#### 【0015】

また、本発明の信号処理回路において、前記メモリ制御部は、前記読み出しアドレスと前記書き込みアドレスとを異なる周波数で発生させることを特徴とする。

**【発明の効果】**

**【0016】**

本発明によれば、より簡単な装置構成を用いて、撮像素子の画素配列とは異なる配列で出力されるカラー撮像信号を、画素配列と同じ配列に変換することができる信号処理装置を提供するという効果が得られる。

**【発明を実施するための最良の形態】**

**【0017】**

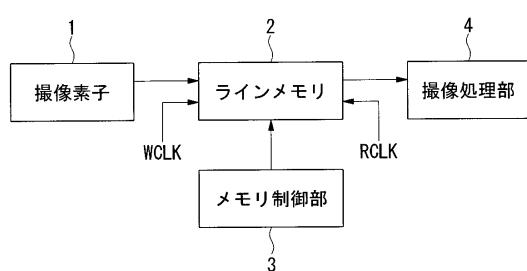

以下、図面を参照し、本発明を実施するための最良の形態について説明する。図1は、

10

本発明の第1の実施形態による信号処理回路の構成を示すブロック図である。以下、図中の各構成について説明する。撮像素子1は、2次元のベイヤ配列の色フィルタが貼付された受光面を備えている。図2は、ベイヤ配列の水平方向および垂直方向の複数画素によって1ブロックが構成される撮像素子1のカラー撮像信号(画素信号)の配列をブロックごとに示している。この撮像素子1は、図15に示されるような画素を色ごとに加算した結果を出力する。

**【0018】**

図2と図15との対応関係は、例えば図15に示されるブロック101が図2のBLK1に対応し、ブロック102がBLK3に対応するようになっている。BLK1においてカラー撮像信号のR成分を加算し、BLK2においてカラー撮像信号のGb成分を加算し、BLK3においてカラー撮像信号のGr成分を加算し、BLK4においてカラー撮像信号のB成分を加算するというように、各ブロックにおいて加算が行われる。また、各ブロックにおける数字は、加算された結果が撮像素子から出力される順番を示している。すなわち、撮像素子1からは、BLK1、BLK2、BLK3・・・の順番でカラー撮像信号が出力される。

**【0019】**

図1に戻り、ラインメモリ2は、撮像素子1から出力されるカラー撮像信号を1水平期間分保持する。ラインメモリ2にはカラー撮像信号の書き込み用クロックWCLKと、読み出し用のクロックRCLKとが供給される。本実施形態においては、書き込み用のクロックと読み出し用のクロックのクロック周波数が等しい場合について説明する。メモリ制御部3はラインメモリ2によるカラー撮像信号の書き込みと読み出しを制御する。撮像処理部4は、ラインメモリ2からベイヤ形式に変換されて読み出されたカラー撮像信号を用いて、自動露出制御や自動焦点制御等の制御を行う。ラインメモリ2は、撮像素子1から出力されるカラー撮像信号を、メモリ制御部3に従って、順次、保持し、この保持したカラー撮像信号を、撮像処理部4が要求する所定の順に読み出すことにより、ベイヤ形式に変換する。

**【0020】**

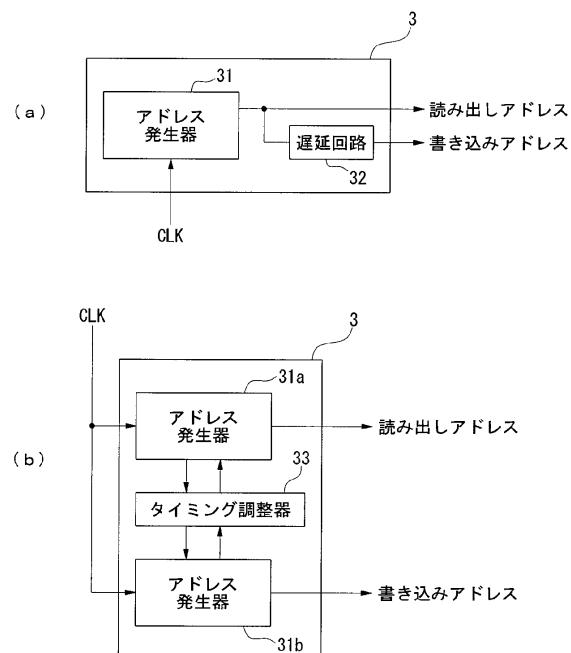

図3は、ラインメモリ2に対するカラー撮像信号の書き込みおよび読み出し用のアドレス制御に係るメモリ制御部3の構成を示すブロック図である。図3(a)において、アドレス発生器31は所定のクロックに同期して動作し、ラインメモリ2のアドレスを発生する。このアドレスはラインメモリ2の読み出しアドレスとして用いられる。また、この読み出しアドレスを示す信号は遅延回路32に入力され、遅延回路32によって所定期間だけ遅延させて出力される。遅延回路32から出力された信号は、ラインメモリ2の書き込みアドレスとして用いられる。

**【0021】**

図3(b)は、メモリ制御部3の、アドレス制御に係る他の構成例を示すブロック図である。図3(b)においては2つのアドレス発生器31aおよび31bが設けられている。アドレス発生器31aはラインメモリ2の読み出しアドレスを発生し、アドレス発生器31bはラインメモリ2の書き込みアドレスを発生し、それぞれ共通のクロックに同期して動作する。タイミング調整器33は、同一時点におけるラインメモリ2の読み出しアド

10

20

30

40

50

レスと書き込みアドレスが重ならないように、アドレス発生器 31a および 31b によるアドレス発生のタイミングを制御する。なお、本実施形態におけるメモリ制御部 3 の構成は、図 3(a) および (b) のどちらでもよい。

#### 【0022】

次に、本実施形態による信号処理回路の動作について説明する。なお、以下の説明において、撮像素子 1 より出力される 1 水平ラインを撮像ラインとする。下記において 3 撮像ライン目と記している場合、そのラインは、撮像素子 1 より出力される 3 番目の水平ラインを示す。また、ラインメモリ 2 より出力され、撮像処理部 4 において処理される 1 水平ライン(図 2 における行方向の 1 ライン)を処理ラインとする。

#### 【0023】

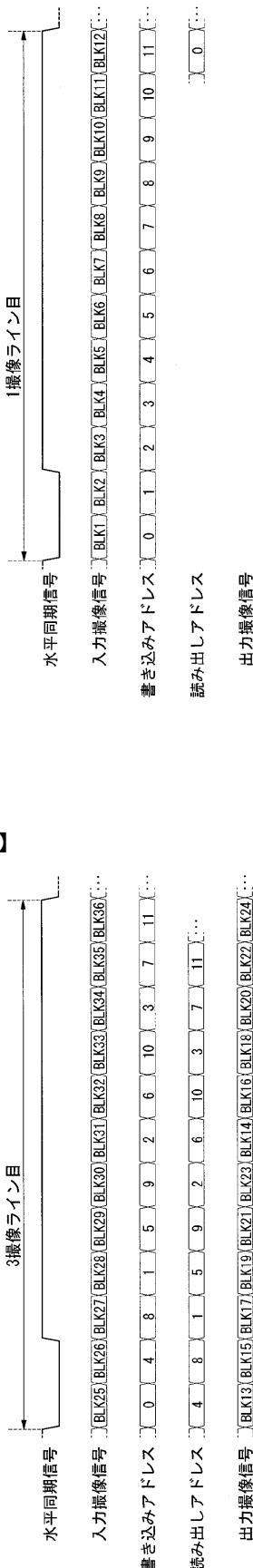

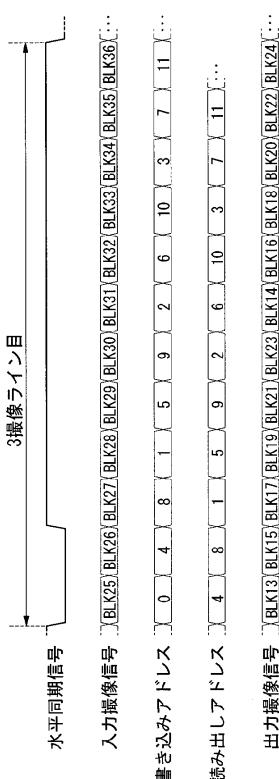

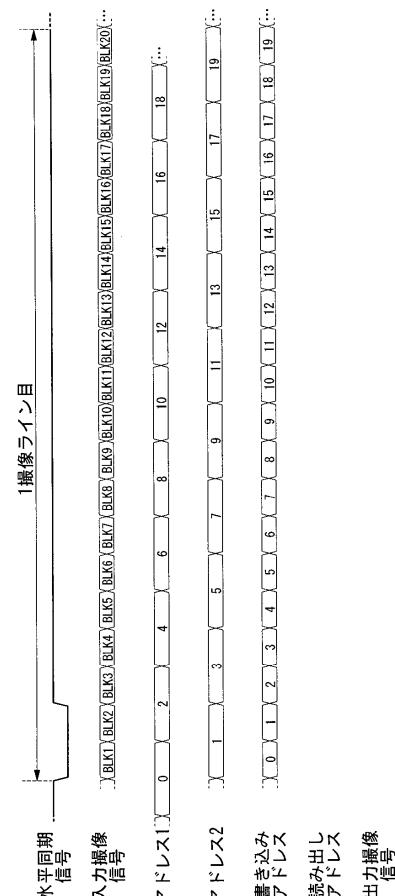

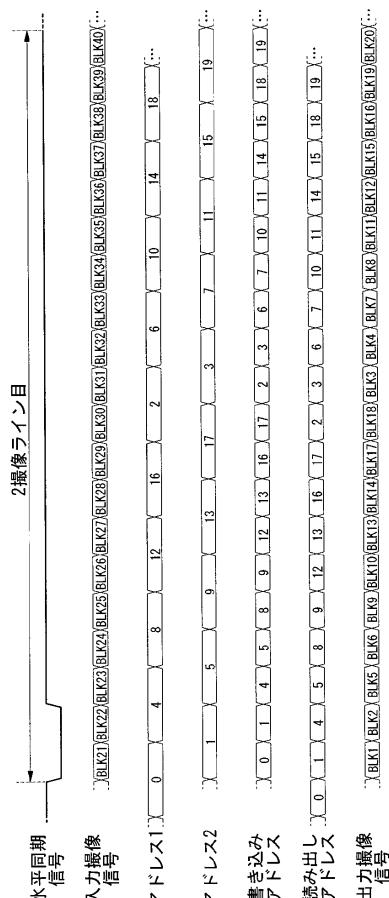

図 4～図 6 は、水平同期信号、ラインメモリ 2 に入力されるカラー撮像信号(入力撮像信号)、メモリ制御部 3 によって発生されるラインメモリ 2 の書き込みアドレス、読み出しアドレス、およびラインメモリ 2 から読み出されて出力されるカラー撮像信号(出力撮像信号)の各推移を示すタイミングチャートである。図 4 に示されるように、撮像素子 1 によって撮像された 1 撮像ライン目のカラー撮像信号はラインメモリ 2 にアドレスの先頭から順次、格納される。

#### 【0024】

図 5 に示されるように 2 撮像ライン目については、ラインメモリ 2 に書き込まれた 1 撮像ライン目のカラー撮像信号が、ベイヤ形式になるようにラインメモリ 2 から読み出される。すなわち、ラインメモリ 2 は、アドレス 0、2、4、6、8、10 に保持しているカラー撮像信号を読み出し、続いてアドレス 1、3、5、7、9、11 に保持しているカラー撮像信号を読み出し、この順でカラー撮像信号を後段の撮像処理部 4 へ出力する。また、ラインメモリ 2 は、カラー撮像信号を読み出した直後に、読み出した同じアドレスに 2 撮像ライン目のカラー撮像信号を書き込む。

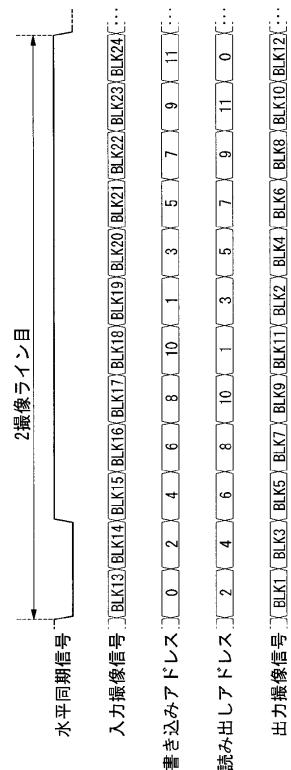

#### 【0025】

図 6 に示されるように 3 撮像ライン目においても同様に、ラインメモリ 2 に書き込まれた 2 撮像ライン目のカラー撮像信号が、ベイヤ形式になるようにラインメモリ 2 から読み出される。すなわち、ラインメモリ 2 は、アドレス 0、4、8、1、5、9 に保持しているカラー撮像信号を読み出し、続いてアドレス 2、6、10、3、7、11 に保持しているカラー撮像信号を読み出し、この順でカラー撮像信号を撮像処理部 4 へ出力する。また、ラインメモリ 2 は、カラー撮像信号を読み出した直後に、読み出した同じアドレスに 3 撮像ライン目のカラー撮像信号を書き込む。

#### 【0026】

上記の処理を繰り返すことにより、撮像素子 1 の画素配列とは異なる順番で入力されるカラー撮像信号を 1 撮像ライン分のみ保持する構成で、カラー撮像信号をベイヤ形式に変換することができる。

#### 【0027】

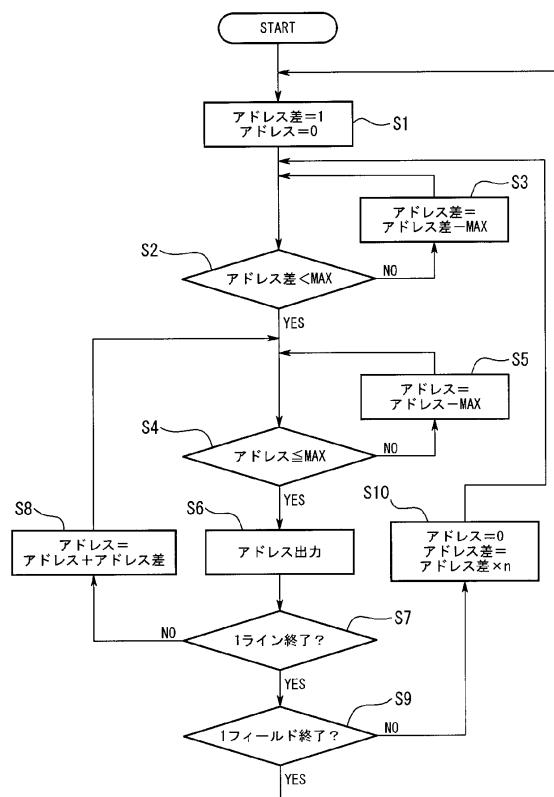

次に、上記の処理を実現するためのメモリ制御部 3 の動作を、図 7 のフローチャートを用いて説明する。図 7 に登場するアドレスは、メモリ制御部 3 がラインメモリ 2 に対して発生するアドレス(ここでは読み出しアドレスとする)を示す。アドレス差は、次のカラー撮像信号を保持するアドレスとの差分を示す。n は、撮像素子 1 より出力される撮像ラインの 1 ライン中に含まれる、撮像処理部 4 に送られる処理ライン数を示す。図 2 においては 2 となる。MAX は、ラインメモリ 2 に保持されるカラー撮像信号のアドレスの最大値を示す。図 2 においては 11 となる。

#### 【0028】

以下、図 7 を用いてメモリ制御部 3 の動作を説明する。信号処理回路の起動直後の状態においては、アドレス差は 1 であり、アドレスは 0 である(ステップ S1)。このアドレスは、図 4 の 1 撮像ライン目の最初のカラー撮像信号が入力されるラインメモリ 2 のアドレスを示す。続いて、メモリ制御部 3 はアドレス差が MAX よりも小さいかどうか判定する(ステップ S2)。アドレス差が MAX 以上であった場合には、メモリ制御部 3 は、現

在保持しているアドレス差からMAXを減算した値を新たなアドレス差とし(ステップS3)、ステップS2の判定を再度行う。

#### 【0029】

アドレス差がMAXよりも小さかった場合には、メモリ制御部3は、アドレスがMAX以下であるかどうか判定する(ステップS4)。アドレスがMAXよりも大きかった場合には、メモリ制御部3は、現在保持しているアドレス差からMAXを減算した値を新たなアドレス差とし(ステップS5)、ステップS4の判定を再度行う。アドレスがMAX以下であった場合には、メモリ制御部3は、現在保持しているアドレスを読み出しアドレスとしてラインメモリ2へ出力する(ステップS6)。

#### 【0030】

続いて、メモリ制御部3は、1撮像ライン分の処理が終了したかどうか判定する(ステップS7)。1撮像ライン分の処理が終了していない場合には、メモリ制御部3は、現在保持しているアドレスにアドレス差を加算した値を新たなアドレスとし(ステップS8)、ステップS4の判定を再度行う。一方、1撮像ライン分の処理が終了した場合には、メモリ制御部3は、1フィールド分の処理が終了したかどうか判定する(ステップS9)。1フィールド分の処理が終了した場合には、ステップS1に戻り、アドレスおよびアドレス差を初期化する。1フィールド分の処理が終了していない場合には、メモリ制御部3は、保持しているアドレスを初期化し、現在保持しているアドレス差にnを乗算した値を新たなアドレス差とし(ステップS10)、ステップS2の判定を再度行う。

#### 【0031】

以下、図4～図7を参照して、メモリ制御部3によるアドレスの発生について説明する。1撮像ライン目においてメモリ制御部3は、アドレス値が0、アドレス差が1の状態で動作を開始する(ステップS1)。この場合、ステップS6においてメモリ制御部3は現在のアドレス値を読み出しアドレスとしてラインメモリ2へ出力し、ステップS8においてアドレス値を順次1ずつカウントアップする。アドレス値が11になった場合には、1ライン分の処理が終了し、ステップS10へ進み、アドレス値が0、アドレス差が2となる。

#### 【0032】

2撮像ライン目においては、S8においてアドレス値が順次、2ずつカウントアップされ、アドレス値が12になったとき、ステップS4を経てステップS5において、アドレス値が1となる。その後、ステップS8においてメモリ制御部3はアドレス値を再度2ずつカウントアップし、アドレス値が11になった場合には、1ライン分の処理が終了し、ステップS10へ進み、アドレス値が0、アドレス差が4となる。メモリ制御部3は、3撮像ライン目以降も同様の演算を繰り返し、アドレス値を順次発生する。

#### 【0033】

なお、上述した動作において、メモリ制御部3の構成が図3(a)に示される構成である場合には、メモリ制御部3は、図7に示される動作に従ってラインメモリ2の読み出しアドレスを発生してラインメモリ2へ出力すると共に、読み出しアドレスを所定期間だけ遅延させて、書き込みアドレスとしてラインメモリ2へ出力する。また、メモリ制御部3の構成が図3(b)に示される構成である場合には、メモリ制御部3のアドレス発生器31aおよび31bは、図7に示される動作に従って、それぞれラインメモリ2の読み出しアドレスおよび書き込みアドレスを発生し、ラインメモリ2へ出力する。

#### 【0034】

本実施形態においては、書き込み用のクロックと読み出し用のクロックのクロック周波数が等しい場合について説明したが、書き込み用のクロックと読み出し用のクロックのクロック周波数を変え、撮像素子の動作周波数と読み出し先回路の動作周波数を変えてよい。

#### 【0035】

上述した本実施形態においては、ラインメモリ2に保持された前撮像ラインのカラー撮像信号を、その形式を変換して読み出す際に、読み出し処理においてカラー撮像信号が読

み出される領域と同一の領域に、入力されたカラー撮像信号を順次、書き込む。これを実現した本実施形態による信号処理回路は、撮像素子1より出力される1撮像ライン分のデータを保持するメモリと、このメモリから読み出されるカラー撮像信号の各画素の信号の順序が、撮像素子1から出力されたカラー撮像信号の各画素の信号の順序と異なる順序となるように、メモリに対する読み出しアドレスを発生すると共に、その読み出しアドレスに対応した領域からカラー撮像信号が読み出された後に空き領域となった領域に、撮像素子1から出力されたカラー撮像信号を書き込むための、メモリに対する書き込みアドレスを、読み出しアドレスに追従して発生するアドレス発生手段とを備えたことにより、撮像素子1の画素配列とは異なる配列で出力されるカラー撮像信号を、より簡易な構成を用いて、画素配列と同じ配列に変換することができる。

10

### 【0036】

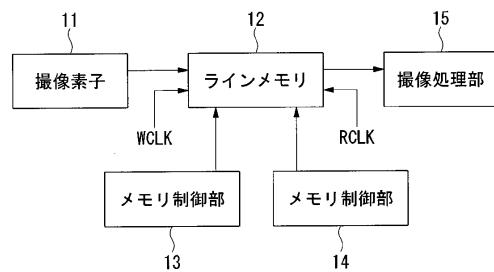

次に、本発明の第2の実施形態について説明する。図8は、本実施形態による信号処理回路の構成を示すブロック図である。撮像素子11は、2次元のベイヤ配列の色フィルタが貼付された受光面を備えている。ラインメモリ12は、撮像素子11から出力されるカラー撮像信号を1水平期間分保持する。ラインメモリ12にはカラー撮像信号の書き込み用クロックWCLKと、読み出し用のクロックRCLKとが供給される。本実施形態においては、書き込み用のクロックと読み出し用のクロックのクロック周波数が等しい場合について説明する。メモリ制御部13およびメモリ制御部14はラインメモリ12によるカラー撮像信号の書き込みおよび読み出し用のアドレスを発生する。

20

### 【0037】

撮像処理部15は、ラインメモリ12からベイヤ形式に変換されて読み出されたカラー撮像信号を用いて、自動露出制御や自動焦点制御等の制御を行う。ラインメモリ12は、撮像素子11から出力されるカラー撮像信号を、メモリ制御部13および14によって発生されるアドレスに従って、順次、保持し、この保持したカラー撮像信号を、撮像処理部15が要求する所定の順に読み出すことにより、ベイヤ形式に変換する。

### 【0038】

次に、本実施形態による信号処理回路の動作について、図15に示されるブロックを図16のように読み出す場合を例にとり、説明する。図9～図10は、水平同期信号、ラインメモリ12に入力されるカラー撮像信号（入力撮像信号）、メモリ制御部13によって発生されるアドレス1、メモリ制御部14によって発生されるアドレス2、ラインメモリ12の書き込みアドレス、読み出しアドレス、およびラインメモリ12から読み出されて出力されるカラー撮像信号（出力撮像信号）の各推移を示すタイミングチャートである。

30

### 【0039】

図9～図10におけるアドレス1は、メモリ制御部13によって生成される。アドレス1は図7に示されるアドレスの発生方法に従って発生することができる。この場合、初期のアドレスを0、アドレス差を2、nを2、MAXを18に設定する。また、メモリ制御部14によって生成されるアドレス2も同様に、初期のアドレスを1、アドレス差を2、nを2、MAXを19に設定することにより発生することができる。また、アドレス1、アドレス2のアドレスの演算は2画素に一度行われる。生成されたアドレス1、アドレス2を1画素ごとに切り替えることにより、ベイヤ形式でカラー撮像信号を出力することができる。

40

### 【0040】

図9に示されるように、撮像素子11によって撮像された1撮像ライン目のカラー撮像信号はラインメモリ12にアドレスの先頭から順次、格納される。

### 【0041】

図10に示されるように2撮像ライン目については、ラインメモリ12に書き込まれた1撮像ライン目のカラー撮像信号が、ベイヤ形式になるようにラインメモリ12から読み出される。すなわち、ラインメモリ12は、アドレス0、1、4、5、8、9…に保持しているカラー撮像信号を読み出し、この順でカラー撮像信号を後段の撮像処理部15へ出力する。また、ラインメモリ12は、カラー撮像信号を読み出した直後に、読み出し

50

た同じアドレスに 2 撮像ライン目のカラー撮像信号を書き込む。

【0042】

上記の処理を繰り返すことにより、撮像素子 11 の画素配列とは異なる順番で入力されるカラー撮像信号を 1 撮像ライン分のみ保持する構成で、カラー撮像信号をペイヤ形式に変換することができる。

【0043】

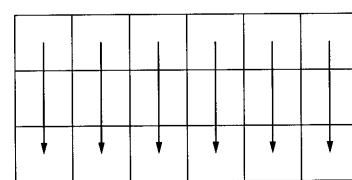

本実施形態においては、図 15 に示されるように奇数ラインに R、G r が入力され、偶数ラインに G b、B が入力された例について示したが、撮像素子 11 の画素配列によって動作が限定されるものではない。また、撮像素子 11 に原色フィルタを配置した例について示したが、図 13 に示されるような配列の補色フィルタを配置してもよい。また、図 2 の例では  $n = 2$  の場合について示したが、図 11 の例のように  $n = 2$  以外の場合にも適用が可能である。また、本実施形態においては、水平方向に 2 画素、垂直方向に 2 画素繰り返して出力する方法を、図 15 に示される画素配列に適用した場合の説明を行ったが、2 画素に限定されるものではない。10

【0044】

また図 2 のように、垂直方向に数処理ラインずつ繰り返してカラー撮像信号が出力される方式について説明を行ったが、図 12 に示されるように、カラー撮像信号がある規則性を持った形式で入力され、それを変換する場合などにも適用できる。また書き込み用のクロックと読み出し用のクロックの周波数が等しい場合について説明を行ったが、両者のクロック周波数が異なっていてもよい。また、撮像素子内で複数画素を加算する場合に関して説明したが、画素加算機能の有無に限定されるものではない。20

【0045】

上述した本実施形態によれば、アドレスを発生する 2 つのメモリ制御部 13 および 14 を設けることにより、カラー撮像信号を、図 2 に示されるような垂直方向に数ラインずつ繰り返す形式で出力する撮像素子だけではなく、水平方向、垂直方向ともに繰り返す形式で出力される撮像素子にも対応することができる。

【0046】

以上、図面を参照して本発明の実施形態について詳述してきたが、具体的な構成はこれらの実施の形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計変更等も含まれる。30

【図面の簡単な説明】

【0047】

【図 1】本発明の第 1 の実施形態による信号処理装置の構成を示すブロック図である。

【図 2】同第 1 の実施形態による信号処理装置が備える撮像素子 1 のカラー撮像信号の配列を示す参考図である。

【図 3】同第 1 の実施形態による信号処理装置が備えるメモリ制御部 3 の構成を示す参考図である。

【図 4】同第 1 の実施形態による信号処理装置の動作に係る各信号のタイミング図である。

【図 5】同第 1 の実施形態による信号処理装置の動作に係る各信号のタイミング図である40

【図 6】同第 1 の実施形態による信号処理装置の動作に係る各信号のタイミング図である。

【図 7】同第 1 の実施形態による信号処理装置が備えるメモリ制御部 3 の動作を示すフローチャートである。

【図 8】本発明の第 2 の実施形態による信号処理回路の構成を示すブロック図である。

【図 9】同第 2 の実施形態による信号処理装置の動作に係る各信号のタイミング図である。

【図 10】同第 2 の実施形態による信号処理装置の動作に係る各信号のタイミング図である。50

【図11】同第2の実施形態におけるカラー撮像信号の順序を示す参考図である。

【図12】同第2の実施形態におけるカラー撮像信号の順序を示す参考図である。

【図13】補色フィルタの色の配置を示す参考図である。

【図14】ペイヤ配列における色の配置を示す参考図である。

【図15】カラー撮像信号の削減方法を説明するための参考図である。

【図16】撮像素子からのカラー撮像信号の読み出しの順番を説明するための参考図である。

【図17】撮像素子から出力されるカラー撮像信号の順序を入れ替える従来の信号処理回路の構成を示すブロック図である。

【符号の説明】

10

【0048】

1, 11, 110... 撮像素子、2, 12, 111, 112... ラインメモリ、3, 13, 14, 113... メモリ制御部、4, 15, 114... 撮像処理部、31, 31a, 31b... アドレス発生器、32... 遅延回路、33... タイミング調整器。

【図1】

【図3】

【図2】

|       |       |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|

| $n=2$ | BLK1  | BLK3  | BLK5  | BLK7  | BLK9  | BLK11 |

|       | BLK2  | BLK4  | BLK6  | BLK8  | BLK10 | BLK12 |

|       | BLK13 | BLK15 | BLK17 | BLK19 | BLK21 | BLK23 |

|       | BLK14 | BLK16 | BLK18 | BLK20 | BLK22 | BLK24 |

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 囮 1 1 】

【图 1-2】

【 13 】

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| G | Y | G | Y | G | Y | G | Y |

| C | M | C | M | C | M | C | M |

| G | Y | G | Y | G | Y | G | Y |

| C | M | C | M | C | M | C | M |

| G | Y | G | Y | G | Y | G | Y |

| C | M | C | M | C | M | C | M |

【図14】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| R  | Gr | R  | Gr | R  | Gr | R  | Gr |

| Gb | B  | Gb | B  | Gb | B  | Gb | B  |

| R  | Gr | R  | Gr | R  | Gr | R  | Gr |

| Gb | B  | Gb | B  | Gb | B  | Gb | B  |

| R  | Gr | R  | Gr | R  | Gr | R  | Gr |

| Gb | B  | Gb | B  | Gb | B  | Gb | B  |

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 梁田 崇志

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

(72)発明者 田中 義信

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

(72)発明者 上野 晃

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

審査官 石坂 博明

(56)参考文献 特開平11-234688(JP,A)

特開2000-244944(JP,A)

特開平10-191185(JP,A)

特開2001-197509(JP,A)

特開2000-059800(JP,A)

特開平09-018763(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/335、9/04 - 9/11