**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H02M 3/335 (2006.01)

|           |             |

|-----------|-------------|

| (45) 공고일자 | 2007년05월31일 |

| (11) 등록번호 | 10-0723353  |

| (24) 등록일자 | 2007년05월23일 |

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2002-7000018   | (65) 공개번호   | 10-2002-0059326 |

| (22) 출원일자   | 2002년01월02일       | (43) 공개일자   | 2002년07월12일     |

| 심사청구일자      | 2005년06월30일       |             |                 |

| 번역문 제출일자    | 2002년01월02일       |             |                 |

| (86) 국제출원번호 | PCT/US2000/018086 | (87) 국제공개번호 | WO 2001/03279   |

| 국제출원일자      | 2000년06월30일       | 국제공개일자      | 2001년01월11일     |

(81) 지정국

국내특허 : 아랍에미리트, 안티구와바부다, 알바니아, 아르메니아, 오스트리아, 오스트레일리아, 아제르바이잔, 보스니아 헤르체고비나, 바베이도스, 불가리아, 브라질, 벨라루스, 캐나다, 스위스, 중국, 코스타리카, 쿠바, 체코, 독일, 덴마크, 도미니카, 알제리, 에스토니아, 스페인, 핀란드, 영국, 그鲁지야, 가나, 감비아, 크로아티아, 헝가리, 인도네시아, 이스라엘, 인도, 아이슬랜드, 일본, 케냐, 키르키즈스탄, 북한, 대한민국, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트비아, 모로코, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 모잠비크, 노르웨이, 뉴질랜드, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 싱가포르, 슬로베니아, 슬로바키아, 시에라리온, 타지키스탄, 투르크멘, 터키, 트리니아드토바고, 탄자니아, 우크라이나, 우간다, 미국, 우즈베키스탄, 베트남, 세르비아 앤 몬테네그로, 남아프리카, 짐바브웨,

AP ARIPO특허 : 가나, 감비아, 케냐, 레소토, 말라위, 모잠비크, 수단, 시에라리온, 스와질랜드, 탄자니아, 우간다, 짐바브웨,

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크멘,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 사이프러스, 독일, 덴마크, 스페인, 핀란드, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴,

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 기니 비사우, 말리, 모리타니, 나제르, 세네갈, 차드, 토고,

(30) 우선권주장

|                |             |        |

|----------------|-------------|--------|

| 60/142,102     | 1999년07월02일 | 미국(US) |

| 60/144,342     | 1999년07월16일 | 미국(US) |

| PCT/US00/07779 | 2000년03월23일 | 미국(US) |

| 09/534,641     | 2000년03월23일 | 미국(US) |

| 09/584,412     | 2000년05월31일 | 미국(US) |

(73) 특허권자

어드밴스드 에너지 인더스트리즈 인코포레이티드

미국 콜로라도 80525 포트 콜린즈 샤프 포인트 드라이브 1625

(72) 발명자

포터로버트엠.

미국콜로라도80525포트콜린즈샤프포인트드라이브1625어드밴스드에

너지인더스트리즈인코포레이티드

구로브게나디지.

미국콜로라도80525포트콜린즈샤프포인트드라이브1625어드밴스드에

너지인더스트리즈인코포레이티드

레데네브아나톨리브이.

미국콜로라도80525포트콜린즈샤프포인트드라이브1625어드밴스드에

너지인더스트리즈인코포레이티드

(74) 대리인

백덕열

이태희

(56) 선행기술조사문헌

|              |              |

|--------------|--------------|

| US 5406051 A | US 5019717 A |

| US 3848175 A |              |

**심사관 : 임창수**

전체 청구항 수 : 총 51 항

#### (54) DC 컴퓨터 구성요소로의 파워 전달을 제어하는 시스템

#### (57) 요약

컴퓨터 구성요소, 마이크로프로세서 등과 같은 DC 구성품에 대한 전원의 공급을 제어하기 위한 방법 및 장치가 기재되어 있다. 고속 부품, 저전압 및 대전류용에 적합하도록 전압 레귤레이션 모듈(112)이 설계된다. 실시예들은 특히, 특히 배전 시스템, 특히 대전류에서의 저전압이 요구되는 시스템과 같은 전자기기의 전원공급시 및 컴퓨터 애플리케이션 등에 있어서 일반적인 서브마이크로초 시간영역에 있어서도 부하의 도통시 신속히 변화하는 응용예에 특히 적합하다. 실시예 및 부요소는 저전압, 대전류 전자 부하를 위한 에너지 저장, 신속한 시간 변화로 전류를 공급하기 위한 능력, 매우 낮은 인덕턴스 접속의 제공, VRM(112) 등이 통전된 전자 부하(186)로부터 비교적 멀리 떨어져 위치되도록 하는 것, 및 피드백 제어 필요성 없이 부하를 가변시키면서 고주파 AC/DC 변환기(102)와 분리된 변압기로부터의 일정 전압을 제공한다.

#### 대표도

도 1a

#### 특허청구의 범위

#### 청구항 1.

- a. 선주파수를 갖는 AC 상용 전원을 공급하는 상용 전원 입력;

- b. 상기 AC 상용 전원을 DC 신호로 변환하는 선전압 정류 소자;

- c. 교류 전원 출력을 형성하는 상기 DC 신호에 응답하는 인버터 소자;

- d. 상기 인버터 소자를 제어하여 분배 주파수를 형성하는 주파수 드라이버;

- e. 상기 교류 전원 출력에 응답하며 적어도 1개의 분배 전압에서 적어도 1개의 분배 출력을 형성하는 전원 변압기 부재;

f. 상기 전원 변압기 부재에 응답하며 상기 인버터 소자로부터 전기적으로 원격 위치에서 컴퓨터 구성요소 전원을 공급하는 배전 시스템;

g.

- 1) 교류 전원 입력;

- 2) 상기 교류 전원 입력에 응답하는 적어도 1개의 전압 레귤레이션 모듈 변압기;

- 3) 상기 전압 레귤레이션 모듈 변압기 부재에 응답하는 제1 스위칭 전압 레귤레이션 모듈 정류 소자;

- 4) 상기 전압 레귤레이션 모듈 변압기에 응답하는 제2 스위칭 전압 레귤레이션 모듈 정류 소자;

- 5) 상기 제1 및 제2 스위칭 전압 레귤레이션 모듈 정류 소자가 응답하는 수동 정류기 제어부;

- 6) 상기 수동 정류기 제어가 응답하는 바이어스 입력;

- 7) 상기 제1 및 제2 전압 레귤레이션 모듈 정류기에 응답하는 제2 고조파 트랩; 및

- 8) 상기 제2 고조파 트랩에 응답하는 실질적으로 비용량성인 DC 출력 시스템을 포함하는, 상기 배전 시스템에 응답하는 적어도 1개의 전기적으로 원격인 전압 레귤레이션 모듈; 및

- h. 상기 DC 전원 출력에 응답하는 적어도 1개의 컴퓨터 구성요소를 포함하는, DC 전원 컴퓨터 시스템.

## 청구항 2.

제1항에 있어서, 상기 원격 DC 전원 공급 시스템에 응답하는 상기 컴퓨터 구성요소는 1.8V 초과 2V 이하, 1.5V 초과 1.8V 이하, 1.3V 초과 1.5V 이하, 1V 초과 1.3V 이하, 0.4V 초과 1V 이하 및 0V 이상 0.4V 이하로 구성되는 그룹으로부터 선택되는 공칭 DC 전압에서 동작하는 컴포넌트를 포함하는 DC 전원 컴퓨터 시스템.

## 청구항 3.

제2항에 있어서, 상기 컴퓨터 구성요소는 나노초당 0.2A, 나노초당 0.5A, 나노초당 1A, 나노초당 3A, 나노초당 10A 및 나노초당 30A로 구성되는 그룹으로부터 선택되는 레벨에서 상승하는 급속 전류 요구(rapid current demand)가 가능한 DC 전원 컴퓨터 시스템.

## 청구항 4.

제3항에 있어서, 상기 컴퓨터 구성요소는 15A 이상 20A 미만, 20A 이상 50A 미만, 50A 이상 100A 이하로 구성되는 그룹으로부터 선택되는 최대 전류에서 동작하는 컴포넌트를 포함하는 DC 전원 컴퓨터 시스템.

## 청구항 5.

제1항에 있어서, 상기 제1 및 제2 스위칭 전압 레귤레이션 모듈 정류 소자들이 응답하는 상기 수동 정류기 제어는 교류 제어 입력을 포함하는 DC 전원 컴퓨터 시스템.

## 청구항 6.

제5항에 있어서, 상기 교류제어 입력은 상기 제1 스위칭 전압 레귤레이션 모듈 정류 소자 및 상기 제2 스위칭 전압 레귤레이션 모듈 정류 소자가 응답하는 정현파 구동 시스템을 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 7.

제6항에 있어서, 상기 전압 레귤레이션 모듈은

- a. 제1 스위칭 전압 레귤레이션 모듈 정류 소자에 응답하는 제1 정류기 유도성 출력;

- b. 제2 스위칭 전압 레귤레이션 모듈 정류 소자에 응답하는 제2 정류기 유도성 출력; 및

- c. 제1 정류기 유도성 출력 및 상기 제2 정류기 유도성 출력에 응답하는 정류기 접합을 더 포함하며,

상기 제2 고조파 트랩은 상기 정류기 접합에 접속되는 병렬 인덕터 및 병렬 커패시터를 포함하는, DC 전원 컴퓨터 시스템.

### 청구항 8.

제7항에 있어서, 상기 전압 레귤레이션 모듈은 상기 전압 레귤레이션 모듈 변압기가 응답하는 교류 입력전압 레귤레이터를 더 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 9.

제8항에 있어서, 상기 교류 입력전압 레귤레이터는 가변 커패시터를 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 10.

제8항에 있어서, 상기 교류 입력전압 레귤레이터는 직렬 스위치 부재를 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 11.

제10항에 있어서, 상기 직렬 스위치 부재는 2개의 스위치 부재를 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 12.

제8항에 있어서, 상기 교류 입력전압 레귤레이터는 레귤레이터 분리 부재를 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 13.

제11항에 있어서, 상기 2개의 스위치 부재는 180도의 위상 관계에서 구동되는 스위치 부재들을 포함하는 DC 전원 컴퓨터 시스템.

### 청구항 14.

제8항에 있어서, 상기 전압 레귤레이션 모듈은 상기 제1 정류기 유도성 출력 및 상기 제2 정류기 유도성 출력 모두에 응답하는 DC출력 커플링을 더 포함하는 DC 전원 컴퓨터 시스템.

**청구항 15.**

제14항에 있어서, 상기 전압 레귤레이션 모듈은 제3 고조파 트랩을 더 포함하는 DC 전원 컴퓨터 시스템.

**청구항 16.**

제15항에 있어서 상기 전압 레귤레이션 모듈 변압기는 1차측을 가지며 상기 제3 고조파 트랩은 상기 전압 레귤레이션 모듈 변압기 부재의 상기 1차측에 전기적으로 접속되는 제3 고조파 트랩을 포함하는 DC 전원 컴퓨터 시스템.

**청구항 17.**

삭제

**청구항 18.**

삭제

**청구항 19.**

삭제

**청구항 20.**

삭제

**청구항 21.**

삭제

**청구항 22.**

삭제

**청구항 23.**

삭제

**청구항 24.**

삭제

**청구항 25.**

삭제

**청구항 26.**

삭제

**청구항 27.**

삭제

**청구항 28.**

삭제

청구항 29.

삭제

청구항 30.

삭제

청구항 31.

삭제

청구항 32.

삭제

청구항 33.

삭제

청구항 34.

삭제

청구항 35.

삭제

청구항 36.

삭제

청구항 37.

삭제

청구항 38.

삭제

청구항 39.

삭제

청구항 40.

삭제

청구항 41.

삭제

청구항 42.

삭제

청구항 43.

삭제

청구항 44.

삭제

청구항 45.

삭제

청구항 46.

삭제

청구항 47.

삭제

청구항 48.

삭제

청구항 49.

삭제

청구항 50.

삭제

청구항 51.

삭제

청구항 52.

삭제

청구항 53.

삭제

청구항 54.

삭제

청구항 55.

삭제

청구항 56.

삭제

청구항 57.

삭제

청구항 58.

삭제

청구항 59.

삭제

청구항 60.

삭제

청구항 61.

삭제

청구항 62.

삭제

청구항 63.

삭제

청구항 64.

삭제

청구항 65.

삭제

청구항 66.

삭제

청구항 67.

삭제

청구항 68.

삭제

청구항 69.

삭제

청구항 70.

삭제

청구항 71.

삭제

청구항 72.

삭제

청구항 73.

삭제

청구항 74.

삭제

청구항 75.

삭제

청구항 76.

삭제

청구항 77.

삭제

청구항 78.

삭제

청구항 79.

삭제

청구항 80.

삭제

청구항 81.

삭제

청구항 82.

삭제

청구항 83.

삭제

청구항 84.

삭제

청구항 85.

삭제

청구항 86.

삭제

청구항 87.

삭제

청구항 88.

삭제

청구항 89.

삭제

청구항 90.

삭제

청구항 91.

삭제

청구항 92.

삭제

청구항 93.

삭제

청구항 94.

삭제

청구항 95.

삭제

청구항 96.

삭제

청구항 97.

삭제

청구항 98.

삭제

청구항 99.

삭제

청구항 100.

삭제

청구항 101.

삭제

청구항 102.

삭제

청구항 103.

삭제

청구항 104.

삭제

청구항 105.

삭제

청구항 106.

삭제

청구항 107.

삭제

청구항 108.

삭제

청구항 109.

삭제

청구항 110.

삭제

청구항 111.

삭제

청구항 112.

삭제

청구항 113.

삭제

청구항 114.

삭제

청구항 115.

삭제

청구항 116.

삭제

청구항 117.

삭제

청구항 118.

삭제

청구항 119.

삭제

청구항 120.

삭제

청구항 121.

삭제

청구항 122.

삭제

청구항 123.

삭제

청구항 124.

삭제

청구항 125.

삭제

청구항 126.

삭제

청구항 127.

삭제

청구항 128.

삭제

청구항 129.

삭제

청구항 130.

삭제

청구항 131.

삭제

청구항 132.

삭제

청구항 133.

삭제

청구항 134.

삭제

청구항 135.

삭제

청구항 136.

삭제

청구항 137.

삭제

청구항 138.

삭제

청구항 139.

삭제

청구항 140.

삭제

청구항 141.

삭제

청구항 142.

삭제

청구항 143.

삭제

청구항 144.

삭제

청구항 145.

삭제

청구항 146.

삭제

청구항 147.

삭제

청구항 148.

삭제

청구항 149.

삭제

청구항 150.

삭제

청구항 151.

삭제

청구항 152.

삭제

청구항 153.

삭제

청구항 154.

삭제

청구항 155.

삭제

청구항 156.

삭제

청구항 157.

삭제

청구항 158.

삭제

청구항 159.

삭제

청구항 160.

삭제

청구항 161.

삭제

청구항 162.

삭제

청구항 163.

삭제

청구항 164.

삭제

청구항 165.

삭제

청구항 166.

삭제

청구항 167.

삭제

청구항 168.

삭제

청구항 169.

삭제

청구항 170.

삭제

청구항 171.

삭제

청구항 172.

삭제

청구항 173.

DC 컴퓨터 시스템의 전원공급 방법에 있어서,

- a. 선주파수를 갖는 AC 상용 전원을 공급하는 단계;

- b. 상기 AC 상용 전원을 DC 신호로 정류하는 단계;

- c. 상기 DC 신호를 반전시켜 교류 전원 출력을 설정하는 단계;

- d. 전기적 원격 위치로 전력을 분배하는 단계;

- e. 컴포넌트 DC 공급 전압을 설정하는 단계; 및

- f. 상기 컴포넌트 DC 공급 전압을 전기적 원격 컴퓨터 구성요소로 전송하는 단계;

- g. 상기 컴포넌트 DC 공급 전압으로부터 상기 컴퓨터 구성요소를 파워-온 시키는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

청구항 174.

제173항에 있어서, 상기 컴포넌트 DC 공급 전압을 전기적 원격 컴퓨터 구성요소로 전송하는 단계는, 1/2 인치 이상 1인치 미만, 1 인치 이상 2인치 미만으로 구성되는 군으로부터 선택된 거리에 걸쳐 상기 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 175.**

제173항에 있어서, 상기 컴포넌트 DC 공급 전압을 전송하는 단계는, 1.8V 이상 2V 미만, 1.5V 이상 1.8V 미만, 1.3V 이상 1.5V 미만, 1V 이상 1.3V 미만, 0.4V 이상 1V 미만, 및 0V 이상 0.4V 미만으로 구성되는 군으로부터 선택된 공칭 DC 전압으로 상기 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 176.**

제173항 또는 제175항에 있어서, 상기 컴포넌트 DC 공급 전압을 전송하는 단계는, 0.2 A/nsec, 0.5 A/nsec, 1 A/nsec, 3 A/nsec, 10 A/nsec, 및 30 A/nsec로 구성되는 군으로부터 선택된 레벨로 상승하는 급속한 전류 요구에 대처할 수 있는 DC 출력 시스템을 통해 상기 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 177.**

제173항 또는 제175항에 있어서, 상기 컴포넌트 DC 공급 전압을 전송하는 단계는, 15 A 이상 20A 미만, 20 A 이상 50A 미만, 50 A 이상 100A 이하로 구성되는 군으로부터 선택된 최대 전류에서 동작하는 DC 출력 시스템을 통해 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 178.**

제173항에 있어서, 상기 컴포넌트 DC 공급 전압을 전기적 원격 컴퓨터 구성요소로 전송하는 단계는, 실질적으로 비용량 성 DC 출력 시스템을 통해 상기 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 179.**

제178항에 있어서, 상기 컴포넌트 DC 공급 전압을 실질적으로 비용량성 DC 출력 시스템을 통해 전송하는 단계는, 0mF 이상 0.3 mF 미만, 0.3mF 이상 0.5 mF 미만, 0.5mF 이상 1 mF 미만, 1mF 이상 3 mF 미만, 3mF 이상 10 mF 미만, 응답 네트워크의 고유 커패시턴스, 컴포넌트 커넥터의 고유 리액턴스, 상기 컴퓨터 커넥터의 고유 커패시턴스 및 마이크로프로세서의 바이페이스 커패시턴스로 구성되는 군으로부터 선택된 유효 커패시턴스를 갖는 실질적으로 비용량성 DC 출력 시스템을 통해 상기 컴포넌트 DC 공급 전압을 전송하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 180.**

제173항에 있어서, 상기 컴포넌트 DC 공급 전압을 설정하는 단계를 실행하기 전에 상기 교류 전원 출력을 전기적으로 분리하는 단계를 더 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 181.**

제180항에 있어서, 상기 교류 전원 출력을 전기적으로 분리하는 단계는 상기 전기적 원격 위치에서 상기 교류 전원 출력을 변환하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

**청구항 182.**

제181항에 있어서, 상기 AC 상용 전원을 DC 신호로 정류하는 단계는, 구동 입력을 사용하여 적어도 하나의 정류 소자를 구동하는 단계를 포함하고 또한 상기 전기적 원격 위치에서 상기 구동 입력을 전기적으로 분리하는 단계를 더 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

### 청구항 183.

제173항, 제174항 및 제178항 중 어느 하나의 항에 있어서, 전기적 원격 위치로 전력을 분배하는 단계는 실질적으로 정현파 교류 신호 전력을 이용하는 단계를 더 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

### 청구항 184.

제183항에 있어서, 실질적으로 정현파 교류 신호 전력을 이용하는 단계는, 300 kHz 이상 500 kHz 미만의 주파수, 500 kHz 이상 1MHz 미만의 주파수, 1 MHz 이상 3 MHz 미만의 주파수, 3 MHz 이상 10 MHz 미만의 주파수, 10 MHz 이상 30 MHz 이하의 주파수, 제1 및 제2 스위칭 전압 레귤레이션 모듈 정류기의 고유 커페시턴스와 정합된 주파수, 상기 컴퓨터 구성요소의 고유 커페시턴스와 정합된 주파수, 상기 컨포넌트 커넥터의 고유 커페시턴스와 정합된 주파수, 정현파 구동 시스템의 고유 커페시턴스와 정합된 주파수로 구성되는 군으로부터 선택된 주파수에서 동작하는 실질적으로 정현파 교류 신호 전력을 이용하는 단계를 포함하는 DC 컴퓨터 시스템의 전원공급 방법.

### 청구항 185.

삭제

### 청구항 186.

삭제

### 청구항 187.

삭제

### 청구항 188.

삭제

### 청구항 189.

삭제

### 청구항 190.

삭제

### 청구항 191.

삭제

### 청구항 192.

삭제

### 청구항 193.

삭제

### 청구항 194.

삭제

청구항 195.

삭제

청구항 196.

삭제

청구항 197.

삭제

청구항 198.

삭제

청구항 199.

삭제

청구항 200.

삭제

청구항 201.

삭제

청구항 202.

삭제

청구항 203.

삭제

청구항 204.

삭제

청구항 205.

삭제

청구항 206.

삭제

청구항 207.

삭제

청구항 208.

삭제

청구항 209.

삭제

청구항 210.

삭제

청구항 211.

삭제

청구항 212.

삭제

청구항 213.

삭제

청구항 214.

삭제

청구항 215.

삭제

청구항 216.

삭제

청구항 217.

삭제

청구항 218.

삭제

청구항 219.

삭제

청구항 220.

삭제

청구항 221.

삭제

청구항 222.

삭제

청구항 223.

삭제

청구항 224.

삭제

청구항 225.

삭제

청구항 226.

삭제

청구항 227.

삭제

청구항 228.

삭제

청구항 229.

삭제

청구항 230.

삭제

청구항 231.

삭제

청구항 232.

삭제

청구항 233.

삭제

청구항 234.

삭제

청구항 235.

삭제

청구항 236.

삭제

청구항 237.

삭제

청구항 238.

삭제

청구항 239.

삭제

청구항 240.

삭제

청구항 241.

삭제

청구항 242.

삭제

청구항 243.

삭제

청구항 244.

삭제

청구항 245.

삭제

청구항 246.

삭제

청구항 247.

삭제

청구항 248.

삭제

청구항 249.

삭제

청구항 250.

삭제

청구항 251.

삭제

청구항 252.

삭제

청구항 253.

삭제

청구항 254.

삭제

청구항 255.

삭제

청구항 256.

삭제

청구항 257.

삭제

청구항 258.

삭제

청구항 259.

삭제

청구항 260.

삭제

청구항 261.

삭제

청구항 262.

삭제

청구항 263.

삭제

청구항 264.

삭제

청구항 265.

삭제

청구항 266.

삭제

청구항 267.

삭제

청구항 268.

삭제

청구항 269.

삭제

청구항 270.

삭제

청구항 271.

삭제

청구항 272.

삭제

청구항 273.

삭제

청구항 274.

삭제

청구항 275.

삭제

청구항 276.

삭제

청구항 277.

삭제

청구항 278.

삭제

청구항 279.

삭제

청구항 280.

삭제

청구항 281.

삭제

청구항 282.

삭제

청구항 283.

삭제

청구항 284.

삭제

청구항 285.

삭제

청구항 286.

삭제

청구항 287.

삭제

청구항 288.

삭제

청구항 289.

삭제

청구항 290.

삭제

청구항 291.

삭제

청구항 292.

삭제

청구항 293.

삭제

청구항 294.

삭제

청구항 295.

삭제

청구항 296.

삭제

청구항 297.

삭제

청구항 298.

삭제

청구항 299.

삭제

청구항 300.

삭제

청구항 301.

삭제

청구항 302.

삭제

청구항 303.

삭제

청구항 304.

삭제

청구항 305.

삭제

청구항 306.

삭제

청구항 307.

삭제

청구항 308.

삭제

청구항 309.

삭제

청구항 310.

삭제

청구항 311.

삭제

청구항 312.

삭제

청구항 313.

삭제

청구항 314.

삭제

청구항 315.

삭제

청구항 316.

삭제

청구항 317.

삭제

청구항 318.

삭제

청구항 319.

삭제

청구항 320.

삭제

청구항 321.

삭제

청구항 322.

삭제

청구항 323.

삭제

청구항 324.

삭제

청구항 325.

삭제

청구항 326.

삭제

청구항 327.

삭제

청구항 328.

삭제

청구항 329.

삭제

청구항 330.

삭제

청구항 331.

삭제

청구항 332.

삭제

청구항 333.

삭제

청구항 334.

삭제

청구항 335.

삭제

청구항 336.

삭제

청구항 337.

삭제

청구항 338.

삭제

청구항 339.

삭제

청구항 340.

삭제

청구항 341.

삭제

청구항 342.

삭제

청구항 343.

삭제

청구항 344.

삭제

청구항 345.

삭제

청구항 346.

삭제

청구항 347.

삭제

청구항 348.

삭제

청구항 349.

삭제

청구항 350.

삭제

청구항 351.

삭제

청구항 352.

삭제

청구항 353.

삭제

청구항 354.

삭제

청구항 355.

삭제

청구항 356.

삭제

청구항 357.

삭제

청구항 358.

a. 선주파수를 갖는 AC 상용 전원을 공급하는 상용 전원 입력;

b. 상기 AC 상용 전원을 DC 신호로 변환하는 선전압 정류 소자;

c. 반전 기간을 갖는 고유 용량 정합 주파수로 교류 전원 출력을 생성하는 상기 DC 신호에 응답하는 적어도 하나의 스위치를 갖는 스위치 모드 인버터 요소;

d. 적어도 상기 고유 용량 정합 주파수로 주파수를 생성하도록 상기 스위치 모드 인버터 요소를 제어하는 주파수 구동기;

e. 적어도 하나의 분배 전압에서 적어도 하나의 분배 출력을 생성하고 상기 교류 전원 출력에 응답하는 전원 변압기 부재;

f. 상기 전원 변압기 부재에 응답하며 상기 스위치 모드 인버터 요소로부터 전기적으로 원격 위치에서 컴퓨터 캠포넌트 전원을 공급하는 배전 시스템;

g. 캠포넌트 직류 전원전압을 필요로 하고 상기 인버터 기간내에 에너지 수요에 신속히 대처할 수 있는 적어도 하나의 저전압, 대전류 컴퓨터 캠포넌트; 및

h) 상기 저전압, 대전류 컴퓨터 캠포넌트 부근에 전기적으로 위치되고, 상기 배전 시스템에 응답하는 적어도 하나의 전기적으로 원격 전압 레귤레이션 모듈을 포함하고, 이 모듈은,

- 1) 교류 저전압 컴퓨터 컴포넌트 출력을 생성하는 적어도 하나의 전압 레귤레이션 모듈 트랜스포머 부재; 및

- 2) 상기 교류 저전압 컴퓨터 컴포넌트 출력을 상기 컴포넌트 직류 전원 전압으로 변환하고 그에 대해 상기 저전압, 대전류 컴퓨터 컴포넌트가 응답하는 적어도 하나의 전압 레귤레이션 모듈 정류기 요소를 포함하는, 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 359.**

제358항에 있어서, 상기 주파수 구동기는 고주파 구동기를 포함하는 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 360.**

제359항에 있어서, 상기 고주파 구동기는, 300 kHz 이상 500kHz 미만의 주파수, 500 kHz 이상 1MHz 미만의 주파수, 1 MHz 이상 3MHz 미만의 주파수, 3 MHz 이상 10MHz 미만의 주파수, 10 MHz 이상 30MHz 이하의 주파수로 구성되는 군으로부터 선택된 주파수로 동작하는 주파수 구동기를 포함하는 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 361.**

제358항에 있어서, 상기 적어도 하나의 저전압, 대전류 컴퓨터 컴포넌트는 바이패스 커패시터에 의해 영향을 받는 적어도 하나의 마이크로프로세서를 포함하는 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 362.**

제361항에 있어서, 상기 바이패스 커패시터는 상기 반전 주기내에 상기 컴퓨터 컴포넌트의 신속한 에너지 수요를 실질적으로 모두 공급하는, 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 363.**

제358항에 있어서, 상기 컴퓨터 시스템은 퍼스널 컴퓨터인, 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 364.**

제358항에 있어서, 상기 스위치 모드 인버터 요소가 응답하고 상기 컴퓨터 컴포넌트에 응답하는 고속 동작 응답 네트워크를 더 포함하고.,

상기 고속 동작 응답 네트워크는, 0mF 이상 0.3 mF 미만, 0.3mF 이상 0.5 mF 미만, 0.5mF 이상 1 mF 미만, 1mF 이상 3 mF 미만, 3mF 이상 10 mF 미만으로 구성되는 군으로부터 선택되는 유효 커패시턴스를 갖는 네트워크를 포함하는 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### **청구항 365.**

- a. 선주파수를 갖는 AC 상용 전원을 공급하는 상용 전원 입력;

- b. 상기 AC 상용 전원을 실질적으로 일정한 DC 신호로 변환하는 선전압 정류 요소;

- c. 적어도 하나의 교류 전원 출력을 생성하고 또한 상기 DC 신호에 응답하는 적어도 하나의 스위치를 갖는 스위치 모드 인버터 요소자;

- d. 상기 스위치 모드 인버터 요소를 제어하는 구동기;

- e. 상기 스위치 모드 인버터 소자로부터의 원격 위치에 실질적으로 사인 교류 전원을 제공하는 실질적으로 사인파의 교류 신호 배전 시스템; 및

- f, 상기 실질적으로 사인파의 교류 신호 배전 시스템에 응답하고 상기 컴퓨터 컴포넌트 근방에 위치되고 상기 실질적으로 사인 교류 전원을 실질적으로 일정한 직류 출력으로 변환하고 또한 적어도 하나의 컴퓨터 컴포넌트가 그에 응답하는 적어도 하나의 전압 레귤레이션 모듈 정류기 요소를 포함하는, 스위치 생성 DC 전원 컴퓨터 시스템.

#### 청구항 366.

- a. 전원;

- b. 고주파 구동기;

- c, 상기 고주파 구동기 및 상기 전원에 응답하고 상기 고주파 구동기는 상기 스위치가 천이 형태를 온/오프 시키도록 하고, 상기 적어도 하나의 스위치는 고주파 교류전원 출력을 생성하는, 적어도 하나의 스위치;

- d, 상기 고주파 교류 전원 출력에 응답하는 가변 부하; 및

- e, 상기 스위치의 고주파 교류 전원 출력에 응답하는, 실질적으로 부하 독립, 실질적으로 궤도 고정 패시브 응답 네트워크를 포함하는, 부하에 전원을 제공하기 위한, 고주파 전원 발생기.

#### 청구항 367.

- a. 전원;

- b. 고주파 구동기;

- c, 상기 고주파 구동기 및 상기 전원에 응답하고 상기 적어도 하나의 스위치는 고주파 교류 전원 출력을 생성하는, 적어도 하나의 스위치;

- d, 상기 고주파 교류 전원 출력에 응답하는 가변 부하; 및

- e, 상기 스위치의 고주파 교류 전원 출력에 응답하고, 또한 상기 가변부하에 관계없이 실질적으로 일정한 출력을 제공하는 패시브, 고효율, 일정 출력 응답 네트워크를 포함하는, 가변 부하에 전원을 제공하기 위한, 고주파 전원 발생기.

#### 청구항 368.

- a. 전원;

- b. 고주파 구동기;

- c, 상기 고주파 구동기 및 상기 전원에 응답하는 적어도 하나의 스위치를 갖고, 상기 스위치 모드 인버터는 소정 주파수로 교류 전원 출력을 생성하는, 스위치 모드 인버터;

d, 상기 교류 전원 출력에 응답하는 가변 부하; 및

e, 상기 스위치의 고주파 교류 전원 출력에 응답하고, 또한 상기 가변부하에 관계없이 실질적으로 일정한 엔드 포인트(end point)를 제공하는 패시브의 일정 엔드 포인트 응답 네트워크를 포함하는, 가변 부하에 전원을 제공하기 위한 무선 주파 전원 발생기.

### 청구항 369.

a. 전원;

b. 고주파 구동기;

c, 상기 고주파 구동기 및 상기 전원에 응답하고, 보디 다이오드 특징을 갖고, 고주파 교류 전원 출력을 생성하는, 적어도 하나의 스위치;

d, 상기 고주파 교류 전원 출력에 응답하는 가변 부하; 및

e, 상기 스위치의 고주파 교류 전원 출력에 응답하고, 또한 상기 보디 다이오드 특징이 도통 상태로 천이되지 않도록 하는 패시브의 도통 방지 응답 네트워크를 포함하는, 부하에 전원을 제공하기 위한, 고주파 전원 발생기.

### 청구항 370.

a. 전원;

b. 구동 진폭을 갖는 실질적으로 사인파의 교류 구동 요소;

c, 상기 교류 구동 요소 및 상기 전원에 응답하고, 소정 주파수로 교류 전원 출력을 생성하는, 복수의 스위치;

d, 상기 교류 구동 요소가 그에 응답하고, 또한 상기 구동 진폭에 응답하는 직접 구동 바이어스 변경 회로; 및

e, 상기 교류 전원 출력에 응답하는 부하를 포함하는, 무선 주파 전원 발생기.

### 청구항 371.

제366항, 제367항 또는 제369항 중 어느 하나의 항에 있어서, 상기 고주파 구동기는, 300 kHz 이상 500kHz 미만의 주파수, 500 kHz 이상 1MHz 미만의 주파수, 1 MHz 이상 3MHz 미만의 주파수, 3 MHz 이상 10 MHz 미만의 주파수, 10 MHz 이상 30 MHz 이하의 주파수로 구성되는 군으로부터 선택된 주파수로 동작하는 주파수 구동기를 포함하는 고주파 전원 발생기.

### 청구항 372.

제358항에 있어서, 상기 컴퓨터 컴포넌트는, 나노초당 0.2 암페어, 나노초당 0.5 암페어, 나노초당 1 암페어, 나노초당 3 암페어, 나노초당 10 암페어, 및 나노초당 30 암페어로 구성되는 군으로부터 선택되는 레벨로 상승하는 신속 전류 수요에 대처 가능한, 스위치 모드 생성 직류 전원 컴퓨터 시스템.

### 청구항 373.

제370항에 있어서, 상기 컴퓨터 컴포넌트는, 나노초당 0.2 암페어, 나노초당 0.5 암페어, 나노초당 1 암페어, 나노초당 3 암페어, 나노초당 10 암페어, 및 나노초당 30 암페어로 구성되는 군으로부터 선택되는 레벨로 상승하는 신속 전류 수요에 대처가능한, 무선 주파 전원 발생기.

### 청구항 374.

제366항, 제367항 또는 제369항 중 어느 하나의 항에 있어서, 상기 네트워크는, 0 mF 이상 0.3 mF 미만, 0.3 mF 이상 0.5 mF 미만, 0.5 mF 이상 1 mF 미만, 1 mF 이상 3 mF 미만, 3 mF 이상 10 mF 미만으로 구성되는 군으로부터 선택되는 유효 커파시턴스를 갖는 고속 동작 응답 네트워크를 포함하는, 고주파 전원 발생기.

### 청구항 375.

제366항, 제367항 또는 제369항 중 어느 하나의 항에 있어서, 상기 네트워크는,

- 0 이상 1 주기의 나이퀴스트 주파수 미만,

- 1 주기의 나이퀴스트 주파수 이상 2.5배 미만,

- 1 주기의 나이퀴스트 주파수의 2.5배 이상 5배 미만,

- 1 주기의 나이퀴스트 주파수의 5배 이상 10배 미만,

- 0 이상 1 주기의 상기 교류 전원 출력의 2배 미만,

- 1 주기의 상기 교류 전원 출력의 2배 이상 4배 미만,

- 0 이상 200 나노초 미만,

- 200나노초 이상 500 나노초 미만,

- 500 나노초 이상 1000 나노초 미만, 및

- 1000 나노초 이상 2000 나노초 미만,

으로 구성되는 군으로부터 선택된 1 주기의 기간내에 반응할 수 있는 응답 네트워크를 포함하는 고속 동작 응답 네트워크를 구비하는, 고주파 전원 발생기.

### 청구항 376.

제366항, 제367항 또는 제369항 중 어느 하나의 항에 있어서, 상기 부하는, 1.8 V 이상 2 V 미만, 1.5 V 이상 1.8 V 미만, 1.3 V 이상 1.5 V 미만, 1 V 이상 1.3 V 미만, 0.4 V 이상 1 V 미만, 및 0 V 이상 0.4 V 미만으로 구성되는 군으로부터 선택되는 정격 직류 전압에서 동작하는 부하를 포함하는, 고주파 전원 발생기.

### 청구항 377.

제376항에 있어서, 상기 부하는, 15 암페어 이상 20 암페어 미만, 20 암페어 이상 50 암페어 이하로 구성되는 군으로부터 선택되는 최대 전류로 동작하는 부하를 포함하는, 고주파 전원 발생기.

## 청구항 378.

제367항 또는 제369항에 있어서, 상기 스위치는 단일 스위치 증폭기의 일부인, 고주파 전원 발생기.

## 청구항 379.

제378항에 있어서, 상기 단일 스위치 증폭기는, E급 증폭기, AE급 증폭기, 및 C급 증폭기로 구성되는 군으로부터 선택되는 단일 스위치 증폭기의 일부인, 고주파 전원 발생기.

## 청구항 380.

a. 직류 입력 전압의 소스;

b. 소정 주파수에서 동작하고, 상기 스위치에 걸린 전압이 실질적으로 제로인 온 타임, 상기 스위치를 통한 전류가 실질적으로 제로인 오프 타임, 및 상기 온 타임 또는 상기 오프 타임에 비해 짧은, 상기 온 타임과 오프 타임간의 천이 타임을 갖는 적어도 하나의 스위치;

c. 제로에서 정격 최대로 변할 수 있는 부하 인덕턴스에 걸쳐 교류 출력 전압 파형 및 스위치 전압 파형을 생성하도록 상기 스위치의 동작에 응답하는 상기 스위치에 접속된 네트워크를 포함하고,

상기 온 및 오프 타임은 실질적으로 일정하고, 상기 온 타임의 개시에서 상기 스위치 전압 파형의 값은 상기 부하 콘덴서스의 값과 실질적으로 독립적인, 전력 변환 회로.

### 명세서

### 기술분야

본 발명은, 저전압 및 대전류를 요구하는 매우 다양한 회로의 파워-온 용도에 적용할 수 있다. 또한, 전류 변화를 빠르게 제공하는 능력이 제공된다. 특히, 2V 미만을 요구하고, 1V 미만을 요구하도록 연구된 마이크로프로세서 및 유사한 회로에 적용된다.

벽 컨버터 토플로지가 현재 마이크로프로세서의 파워-온에 사용되고 있다. 2.5V, 13A의 요구 사항에 대해, 300kHz의 스위칭 주파수가 부적절해지고 있다. 실질적인 단계 부하 변화를 만족시키기 위해서는, 큰 출력 커패시턴스가 요구되고 있다. 마이크로프로세서의 전압 요구 사항이 50A의 1.0V로 내려감에 따라, 종래의 기술 토플로지는 보다 부적절해지고 있다. 2.5배의 전압 강하(및 상이한 전압 허용 오차의 부수적인 강하), 및 4배의 전류 증가에 의하면, 상기 요구되는 단계 응답을 유지하기 위해 큰 출력 커패시터가 지금 필요로 되고 있다. 그러나, 마이크로프로세서 접속에 가까운 큰 커패시터 등을 위치시키는 것은 점차 어렵거나 불가능해지고 있다. 또한, 이러한 접근 비용은 전압이 감소됨에 따라 증가한다. 이러한 문제에 대한 한 가지 해결책은 전압 레귤레이션 모듈의 주파수를 증가시키는 것이다. 그러나, 이러한 구성에서 주파수가 증가할 때, 이 파형의 비공진 에지는 FET 출력 커패시턴스의 커뮤테이션 등의 문제점을 야기하고, 거의 메가헤르츠 이상의 상기 스위칭 주파수의 증가를 방해한다. 이 상황은, 마이크로프로세서 및 다른 저전압 전자부품이 개발되고, 이에 대해 적절한 파워를 제공하는 것이 점차 어려워짐에 따라, 빠르게 심각해지고 있다. 본 발명은 이러한 필요성에 대한 파워의 실현을 가능케 한다. 이는 높은 주파수를 가능케 하여, 고전류를 취급하도록 구성될 수 있다.

이 상황은, 마이크로프로세서 및 다른 저전압 전자부품이 개발되고, 이에 대해 적절한 파워를 제공하는 것이 점차 어려워짐에 따라, 빠르게 심각해지고 있다.

언급한 바와 같이, 본 발명은 특히 컴퓨터 시스템의 파워-온에 관한 것이다. 여기서, 스위치-모드 DC는 시스템의 내부 구성요소를 파워-온하기 위해 생성된다. 이는, 마이크로프로세서가 높은 디멘드 및 파워 변화를 갖는 새로운 디자인에서 특별한 응용 가능성을 갖는다. 이는 저전압, 대전류 전자부품의 파워-온 영역에 관한 것일 수 있다. 그러나, 상기와 같이, 본

발명은 연산 분야에 적용될 수 있으며, 다음 설명 중 대부분은 그와 관련해서 나타난다. 그러나, 다른 실시예는 연산 분야에 한정되지 않고, 전력을 흡수하는 다양한 전력 흡수 부하가 그 전력 흡수 특성을 급격하게 변화시킬 수 있는(즉, 그 임피던스가 빠른 변화를 받을 수 있는) 여러 가지 다양한 환경에 적용될 수 있음을 이해해야 한다. 또한, 전력 운반 컨덕터의 다이나믹 임피던스를 교차하여 강하될 수 있는 전압이 이러한 부하에 운반되는 전압의 중요한 부분이 되도록, 이러한 부하가 물리적으로 분리되어도, 적용될 수 있다. 또한, 디자인 트레이드 오프가 동작 전압의 안정된 감소를 강제하고 있는 애플리케이션에도 점차 적용될 수 있다. 이러한 상황은 연산 시스템뿐만 아니라, 원격통신, 레이더 시스템, 차량 전력 시스템 등에서 발생할 수 있다. 또한, 많은 다른 상황에서도, DC/AC 컨버터 그 자체가 애플리케이션을 가질 수 있다.

## 배경기술

연산 시스템의 구조는, 주로, 수백 킬로헤르츠에서 실행되는 최초의 4비트 칩으로부터 수백 메가헤르츠에서 실행되는 가장 최근의 것인 32 및 64비트 마이크로프로세서로의 발달에 의해, 최근에 많은 변화를 겪어 왔다. 칩 디자이너가 점점 빠른 속도를 추구함에 따라, 열 유출에 관한 문제점이 발생한다. 즉, 회로의 속도가 증가됨에 따라, 내부의 논리 스위치는 각각 보다 빠른 그 주변 커패시턴스를 디스챠지해야 한다. 상기 커패시턴스에 저장된 에너지는 (주어진 전압에서) 고정되어 있기 때문에, 속도가 증가됨에 따라, 스위치에서 소비되어야 하는 에너지가 스위치에 초당 여러 번 덤프된다. 초당 에너지가 전력으로서 정의되기 때문에, 따라서 스위치에서 손실된 전력은 주파수를 직접 증가시킨다.

반면, 커패시턴스에 저장된 에너지는 전압의 제곱에 따라 증가하므로, 2V로 차지된 커패시터는 3V로 차지된 동일한 커패시터에 저장된 에너지의 44%만 저장한다. 이러한 이유 때문에, 2V에서 동작하도록 설계된 마이크로컴퓨터는, 동일한 속도로 실행될 때, 3V로 동작하는 동일한 마이크로프로세서에 비해 적은 전력을 소비한다. 따라서, 마이크로프로세서의 동작 전압을 낮게 하려는 경향이 있다.

높은 동작 전압에 비해 저전압에서 동작되면, 다른 고려 사항이 낮은 최대 속도를 나타내는 마이크로프로세서를 야기한다. 즉, 회로가 전 속력으로 동작하고, 그 회로상의 전압이 단순하게 감소되면, 회로가 적절하게 동작하지 않아, 회로 속도("클록 속도")가 감소되어야 할 수도 있다. 전 속력 능력을 유지하고, 또한 저전압에서 동작하기 위해, 회로는 종종 작은 물리적 사이즈로 다시 설계된다. 또한, 회로의 사이즈가 감소되고, 층 두께도 감소됨에 따라, 동작 전압이 장치의 절연 산화물 층의 브레이크다운을 방지하기 위해 적절한 마진을 유지하도록 낮아질 필요가 있다. 지난 몇 해 동안, 이러한 단계가 마이크로프로세서 설계의 코스를 정의해왔다. 따라서, 그 제품에 대해 최대 속도를 추구하는 키 마이크로프로세서 디자이너는 다음의 고려 사항:

- 고속 칩은 좀 더 금전적 가치가 있고;

- 고속 칩은 열을 좀 더 손실해야 하고;

- 그 열의 제거에는 한계가 있고;

- 저전압은 주어진 속도에서 발생되는 열을 감소시키며;

- 작은 장치가 주어진 전압에서 보다 빠르게 실행되는 것을 트레이드 오프하기 위해 상당한 노력을 소비해왔다.

물론, 이들 이외에도 중요한 트레이드 오프 고려 사항은 많이 있지만, 상기 리스트는 현재 발명의 일부 관점에 관한 기본 원리를 준다. 이러한 고려의 결과에 의해 마이크로프로세서 디자이너는 보다 낮은 전압에서 동작하는 디자인을 제조해왔다. 초기 디자인은 5V에서 동작했으며; 이는 3.3, 3.0, 2.7, 2.3으로 감소되었고, 기입시에 주된 디자인은 2.0V에서 동작한다. 또한, 계속 감소되면, 미래의 디자인은 1.8, 1.5, 1.3, 1.0, 및 1V 미만의 약 0.4V 정도로 낮아져도 동작될 것이다.

한편, 열 제거의 발달에 의해, 점점 높아지는 열 손실 레벨에서 프로세서가 실행되도록 기대된다. 초기의 칩은 1와트 정도를 손실했고; 현재 디자인은 30와트 레벨에서 동작하며, 미래의 열 제거 디자인은 프로세서에 의해 발생되는 전력을 100와트만큼 손실할 수 있다. 손실되는 전력은 동작 전압의 제곱에 비례하기 때문에, 열을 제거하는 능력이 향상되어도, 낮은 동작 전압에서 실행되려는 경향은 남아있다.

이 모든 것은 기본적인 고려 사항: 고속 칩이 금전적인 가치가 있는 것에 의해 행해진다. 따라서, 디자이너는 배열할 때 어떻게든 반드시 속도를 증가시키려 하며, 이는 칩의 소형화, 저전압, 및 파워 상승을 유도한다. 전력은 전류의 전압배이드

로, 전압이 강하됨에 따라, 전류는 주어진 전력에 대해 증가한다. 만약 동시에 열 제거의 향상과 동시에 전력이 더 높아지면, 전류는 더 증가한다. 이는, 전류가 매우 빠르게 상승함을 의미한다. 초기 칩은 전원 전류 중 아주 일부의 A를 사용했고, 현재의 디자인은 15-50A까지 사용하며, 미래의 디자인은 100A 이상을 사용할 수 있다.

상기 프로세서의 속도가 증가함에 따라, 전원 역학에 대한 요구도 증가한다. 프로세서는 아이들링 때문에 거의 전류를 인출(draw)할 수 없으며, 그 후, 프로세서가 갑자기 빠른 연산을 개시하도록 야기하는 일이 발생할 수 있다(메모리 소자로부터의 한 조작의 키 데이터 또는 외부 사건으로부터의 신호의 도달 등). 이는 프로세서에 의해 인출되는 전류에 급격한 변화를 생성할 수 있고, 이는 심각한 전기적 결과를 갖는다.

인덕턴스는 자계의 에너지 저장의 치수이다. 모든 전류-운반 컨덕터는 자계의 전류와 연관되어 있고, 이는 에너지 저장을 나타낸다. 자계에 저장된 에너지가 자계의 제곱의 부피 적분의 절반인 것은 상기 분야의 종사자에 의해 잘 알려져 있다. 상기 자계가 컨덕터의 전류에 선형적으로 연관되어 있기 때문에, 컨덕터를 운반하는 전류에 의해 저장되는 에너지는 전류의 제곱의 절반에 비례하며, 그 비례 상수를 컨덕터의 "인덕턴스"라 칭한다. 상기 시스템에 저장된 에너지는 전기 전류의 소스에 의해 공급되고, 주어진 전원에 대해 에너지가 공급될 수 있는 비율에는 한계가 있으며, 이는 저장된 에너지가 시간이 경과한 후에 다시 회복되어야 함을 의미한다. 따라서, 에너지 저장 메카니즘의 존재는, 전류가 회복될 수 있기 전에, 일정 비율로 에너지가 생성되어 자계에서 측정되어야 함에 따라, 당연히 회로의 속도를 떨어뜨린다.

유효한 전압, 인덕턴스 및 컨덕터의 전류의 변화율은, 상기 분야의 당업자에 의해 잘 알려진 다음 식에 의해 관련된다.

$$V = L * \partial I / \partial t,$$

여기서,  $L$ 은 컨덕터의 인덕턴스이고,  $\partial I / \partial t$ 는 컨덕터의 전류의 변화율이다. 이 식은, 전력 시스템상의 부하에 주어진 전류 변화를 생성하기 위해 요구되는 전압이 그 변화의 시간 스케일이 감소됨에 따라 증가하고, 또한 그 부하로의 어떤 접속의 인덕턴스가 증가됨에 따라 증가함을 나타낸다. 마이크로프로세서의 속도가 증가됨에 따라, 시간 스케일은 감소되고, 유효한 전압이 감소됨에 따라, 이 식은 비례하여 강화되는 인덕턴스를 요구한다.

통상, 반도체 장치를 파워-온할 때, 장치로의 접속의 인덕턴스를 고려할 필요가 없지만, 현대 전자부품, 특히 마이크로프로세서에 의하면, 이러한 고려가 접속의 인덕턴스를 낮추도록 하는데 많은 주의를 강요한다. 상기 분야의 전류 상태에서, 예컨대 마이크로프로세서는 약 2V에서 동작하며, 약 7% 또는 140mV의 전원선상의 전압 과도 현상을 허용할 수 있다. 이 동일한 마이크로프로세서는, 전원 전류가 적어도 나노초당 1/3 또는 거의 일A의 비율, 또는  $3 * 10^8$  또는  $10^9$  A/세컨드의 비율로 각각 변화하도록 요구할 수 있다. 상기 식은, 약 140피코hen리( $1.4 * 10^{-10}$ H) 및 1/2 나노hen리( $5 * 10^{-10}$ H)의 인덕턴스가 전류 상승의 2 비율로 140mV의 전압을 강하시킴을 나타낸다. 상관 관계에 이 숫자를 넣기 위해, 자유 공간에서 1인치 길이의 와이어의 인덕턴스는 약 20나노hen리, 또는 20,000피코hen리이다. 상기 접속의 인덕턴스는 과잉 접속을 병렬로 함으로써 감소될 수 있으며, 약 1 센티미터 길이의 컨덕터에 의해 140피코hen리의 인덕턴스에 의한 접속을 생성하기 위해서는 20개의 병렬 컨덕터가 요구되며, 예컨대 1/2 나노hen리의 인덕턴스에 의한 접속은 거의 100개의 병렬 컨덕터를 요구한다.

상기 논의는, 저전압의 소스가 마이크로프로세서, 또는 일반적인 특수한 구성 요소의 액티브 부분에 물리적으로 가까워야 함을 나타내며, 역으로 이는 물리적으로 작아야 함을 나타낸다. 컨덕터의 전류가 상승하도록 요구되는 지연 기간 동안, 커패시터가 에너지를 공급하기 위해 사용된다고 가정하면, 커패시터로의 접속의 고유 인덕턴스는 현재 엄격하게 이 접근을 제한한다. 따라서, 시스템 디자이너는, 프로세서의 전원이 전류 드로우의 빠른 변화하에서 적절하게 안정되는 것을 보증하기 위해, 전원을 프로세서에 매우 가까이 위치시켜야 하는 것에 직면한다. 이러한 요구는, 전압이 더 강하되고 또한 전류가 증가함에 따라, 점점 엄격해지며, 그 이유는 전자는 허용 가능한 과도한 사이즈를 감소시키고, 후자는 전류 변화의 퍼텐셜 비율을 증가시키기 때문이다. 두 팩터 모두는 접속의 허용 가능한 인덕턴스를 감소시킨다. 이는 디자이너에게 낮은 인덕턴스 접속을 갖는 보다 작은 커패시터의 사용을 강요할 수 있고, 커패시터가 작을수록 에너지를 적게 저장하기 때문에, 이는 상기 전력 시스템을 높은 주파수로 구동하며, 이는 비용을 증가시키고 효율성을 떨어뜨린다.

상기 언급은 컴퓨터에서 실제적인 중앙 마이크로프로세서에 한정되지 않는다. 메모리 매니지먼트 회로, 그래픽 디스플레이 장치, 고속 입출력 회로 및 다른 보조 회로 등의, 현대 컴퓨터의 다른 소자는 거의 중앙 처리 소자만큼 빠르게 속도가 증가되고 있고, 동일한 고려사항이 적용된다.

컴퓨터를 포함한 많은 현대 전자부품 회로는 스위치모드 전력 변환 시스템에 의해 파워-온된다. 이러한 시스템은 유틸리티 라인으로부터의 인커밍 파워를 1개 이상의 스위치의 동작에 의해 전자 회로에 의해 요구되는 전압 및 전류로 변환시킨

다. 데스크탑 퍼스널 컴퓨터 등의, 저전력 사업 및 소비자 전자부품에서, 인커밍 전력은 교류 전압, 일반적으로 미국에는 115V 및 나머지 세계 대부분에는 220V로서 공급된다. 교류 주파수는 위치에 따라, 50 또는 60헤르츠이다. 이러한 상용 전원은 저전압 정상 전류(직류) 또는 DC로 변환되어야 하고, 전자 회로에 대한 전력으로서 사용되기 위해 몇 페센트로 레귤레이트되어야 한다. 이러한 변환을 행하는 장치를 "파워 서플라이"라고 칭한다. 단순 변압기, 정류기, 및 선형 레귤레이터를 사용하여 레귤레이트된 DC 전원에 의해 저전압을 생성하는 것은 가능한 반면, 이러한 유닛은 무겁고, 부피가 크고, 비효율적이다. 이러한 애플리케이션에서는, 무게 및 사이즈를 감소시키는 것이 바람직하며, 이러한 접근은 이 이유에 대해서만 부적절하다. 또한, 선형 레귤레이터의 비효율성도 허용될 수 없다. 효율성은 출력 대 입력의 비율로서 정의되며, 낮은 효율성은 유닛을 저온상태로 유지하기 위해 주위로 전환되어야 하는 열이 유닛에서 비롯되었음을 의미한다. 효율성이 낮을수록, 열은 더 전환되어야 하고, 이것이 교류 접근을 찾아야 하는 이유 그 자체이다.

이러한 이유 때문에, 실제로 모든 현대 전자부품 회로는 스위치모드 변환 시스템에 의해 파워-온된다. 이러한 시스템은 전형적으로 다음과 같이 동작한다. 인커밍 상용 전원은 우선 정류기에 의해, 레귤레이트되지 않은 직류로 변환된다. 그 후, 상기 정류된 DC는 전자 스위치에 의해, 전형적으로 수백 킬로헤르츠의 고주파수로 변환된다. 그 후, 이 고주파수 전력은 적당한 변압기에 의해 적절한 전압 레벨로 변환되고; 이 변압기는 또한 상용 전원으로부터, 안정성의 이유 때문에 요구되는 절연을 제공한다. 상기 결과의 분리된 고주파 전력은, 그 후 다시 정류되고, 전자부품에 위한 사용을 위해 정상 직류로 여과된다. 출력 전압의 레귤레이션은 대개 전자 스위치의 도통 시간의 제어에 의해 실현된다. 상기 결과의 파워 변환 유닛은, 변압기 및 출력 필터의 사이즈 및 중량이 기본적인 상용 전원 주파수 이상의 주파수의 증가에 비례하여 감소되기 때문에, 초기 접근에 비해 작고 무게가 가볍다. 이 모든 것은 종래의 기술에 잘 나타나 있다.

복합적인 전자 시스템에서는, 다양한 전압이 요구될 수 있다. 예컨대, 컴퓨터 시스템에서, 주변 장치(디스크 드라이브 등)는 + 12V를 요구할 수 있고, 일부 논리 회로는 + 5V를 요구할 수 있고, 입력/출력 회로는 또한 -12V를 요구할 수 있고, 메모리 인터페이스 및 일반적인 논리는 + 3.3V를 요구할 수 있으며, 중앙 마이크로프로세서는 2V를 요구할 수 있다. 표준은, 중앙 전원(상용 전원에 직접 접속되어 있는 장치)이 ± 12 및 + 5V를 전달하고, 상기 낮은 전압은 전압 레귤레이션 모듈이라 칭해지는 부가 회로, 또는 저전압을 요구하는 회로에 가까운 VRM에 의해 + 5V 공급원으로부터 전달되도록 개발되어 왔다. 이 부가 회로는, AC 파워의 기간의 제어를 통해 전압을 수정하고, 다시 저전압 DC로 재정류함으로써, + 5V 전원을 고주파 AC 전원으로 다시 변환한다.

상기 결과의 전체 시스템은, 스위치모드 기술의 사용에도 불구하고, 복잡하고, 매우 비효율적이다. 전형적인 200와트 컴퓨터 시스템에서, 유틸리티 라인의 초기 정류에서는 4와트, 전자 스위치에서는 8와트, 변압기에서는 2.5와트, 출력 정류 및 필터링에서는 20와트, 중앙 전원 및 전자 부품 보드 사이의 접속에서는 4와트가 손실된다. 따라서, 고전압 전자 부하에 대한 변환 프로세스에서는 38.5와트가 손실된다. 실질적인 추가 손실이 저전압 변환 프로세스에서 지속될 수 있다. 마이크로프로세서에 대해 10A의 + 5V를 25A의 + 2V로 변환할 수 있는 전형적인 50와트 전압 레귤레이션 모듈은, 그 자체가 AC 변환 및 변압기에서는 각각 약 1와트 정도, 최종 정류 및 필터링에서는 약 10와트 정도의 손실을 가질 수 있다. 다른 전압 레귤레이션 모듈은 전체 시스템에 대해, 사용된 전력의 1/3 정도를 손실하는 큰 손실을 가질 수 있다. 일부 특수한 비효율적 접근은, 입력 전력 회로가 실제적인 최종 회로에 의해 요구되는 전력을 두 배 이용하도록 요구하고, 실제 동작 회로에 의해 이론적으로 요구되는 것에 따라, 2배의 열이 전자부품에서 소비되도록 요구함으로써(이는 편에 의해 제거되어야 함), 50% 정도의 낮은 효율을 나타낼 수 있다.

이 시스템은 여러 해 동안 발전했고, 많은 현재 사용에 대해 최적화되지 않았지만, 산업의 관성 때문에, 그리고 중앙 전원 유닛에 의해 발생되는 전압 및 전류상의 산업 표준을 유지하는 상기 지각된 이점 때문에 지속된다.

마이크로프로세서 산업의 현재 경향을 분석하면, 현재 시스템이 미래에 적합하지 않는 것이 명백하게 나타낸다. 이러한 경향은 코어 마이크로프로세서 등의 임계 소자의 전류 드로우가 끊임없이 증가해왔고, 미래에도 계속 그렇게 될 것이라는 것을 나타낸다. 반면, 동작 전압은, 이에 의해 절대항의 전원 전압의 허용 가능한 허용 오차를 강하시키면서, 끊임없이 감소해왔다. 최종적으로, 프로세서 전류의 변화율 - 전류 회전율은 가까운 미래에 대한 실질적인 추가 증가 예측에 의해 매우 빠르게 증가하고 있다. 이러한 팩터 전체는 현재 기술에 대해 완화되어, 미래에 채용되는 새로운 접근을 요구한다. 현재의 파워-온 및 다른 기술은 마이크로프로세서의 하나의 부가적인 세대에 비해 좀더 지속되지 않는 것이 신뢰할 수 있게 평가되어 왔고, 디자이너가 그 다음에 뒤따르는 세대에서 현재 연구하기 때문에, 이러한 디자이너는 현재 이용 가능한 기술에 의해 파워-온 할 수 없는 마이크로프로세서의 개발 프로세스 중이라고 말할 수 있다.

종래의 기술의 다른 문제점은 사각파 전자 변환 기술의 사용이다. 펄스폭 변조에 대한 PWM으로서 알려진 이러한 기술은 가파른 상승 구간을 갖는 스위치 전압 파형을 생성한다. 이러한 구간은 적합한 동작에 의해 간접하며, 인접한 회로에 도통되거나 방사될 수 있는 고주파수 전력 구성요소를 생성한다. 이러한 고주파수 전력 구성요소는 또한 적합한 동작에 의해 간접하면서, 라디오 또는 텔레비전 수상기 등의 다른 전자 장치에도 도통되거나 방사될 수 있다. 이러한 구성요소의 존재

는 고주파수 전력 구성요소로부터 다른 회로를 보호하기 위한 전력 시스템의 패키지, 및 그 입력 및 출력 리드상에서 전원 패키지로부터 이러한 구성요소의 도통을 방지하기 위한 비싸고 복잡한 필터의 인스톨레이션에 주의 깊은 설계를 요구한다. 그 후 필요한 것은, 작고 고효율의 전압 레귤레이션 모듈이 전력 사용의 포인트에 가까이 위치하도록 하는 전력 변환 시스템이며, 이는 일반적으로 빠르고, 효율이 좋고, 적어도 대체하는 종래의 기술만큼 비용이 낮다.

### 발명의 상세한 설명

따라서, 본 발명의 목적은 종래의 기술에 의해 실현될 수 있는 것에 비해, 낮은 인덕턴스 접속에 의해 에너지를 저장하는 수단을 제공하는 것이다. 또한, 전자 부하에 매우 가까이 위치시킬 필요 없는 저전압 및 고전류에서의 에너지의 소스를 제공하는 것이 본 발명의 다른 목적이다. 유사하게, 전류 드로우의 높은 변화율의 존재시에도 상기 파워-온 된 부하를 교차하는 전압을 유지할 수 있는 저전압의 소스를 제공하는 것이 본 발명의 또 다른 목적이다.

또한, 현재 기술을 사용하여 실현될 수 있는 것에 비해, 보다 높은 효율로 유효 배전에 대해 고주파수 교대 전력으로 상용 전원을 변환하는 수단을 제공하는 것이 본 발명의 목적이다. 또한, 고주파수 AC 파워를, 현재 기술을 사용하여 실현될 수 있는 것에 비해, 보다 높은 효율로, 현재 및 미래 전자부품에 의해 요구되는 낮은 DC 전압 및 높은 DC 전류로 변환하는 수단을 제공하는 것이 목적이다. 또한, 넓은 범위의 부하 상태 이상의 효율을 유지하는 것이 본 발명의 다른 목적이다.

또한, 본 발명의 목적은 종래의 기술에 비해, 실질적으로 작은 고주파수 전력의 소스를 제공하는 것이다. 유사하게, 소스가 전자 부하에 매우 가까이 위치되도록 하는 종래의 기술에 비해, 실질적으로 작은 대전류, 저전압의 소스를 제공하는 것이 목적이다.

또한, 매우 짧은 기간에 대해서도, 전원의 출력 전압의 인접한 제어를 제공하는 것이 본 발명의 목적이다. 즉, 파워-온 또는 이러한 넓은 대역폭을 필요로 하지 않고 부하의 변화에 작은 단기 응답을 갖는 전원을 제공하는 일을 완화하는 것이 목적이다. 따라서, 부하의 변화에 좀더 단기의 응답에 의한 시스템을 제공하는 것이 목적이다.

또한, 종래의 기술에 의해 요구되는 것에 비해, 보다 적은 에너지를 저장하는 전력 변환 시스템을 제공하는 것이 본 발명의 목적이다.

또한, 종래의 기술에 비해, 낮은 비용으로 생성될 수 있는 전력 변환 시스템을 제공하는 것이 본 발명의 목적이다.

또한, 사각과 전자 변환 기술의 사용에 의해 연관된 문제를 제기하는 것이 목적이다. 또한, 전력 시스템의 전류의 상승률 및 전압의 하강률을 감소시킴으로써, 전력 시스템, 및 파워-온된 전자부품 및 상기 파워-온된 전자부품 부근의 다른 장치 사이에서 가능한 간섭을 감소시키는 것이 본 발명의 목적이다. 유사하게, 전력 변환 회로에서 매끄럽게 변화하는 파형을 사용하는 전력을 제공하는 것이 목적이다.

또한, 상수 주파수, 또는 다양한 주파수를 수용하는 다른 실시예를 통해 동작하는, 전술한 목적이 만족되는 전력을 제공하는 것이 본 발명의 일 실시예의 목적이다.

본 발명의 다른 기본적인 관점은 변압기 누설 인덕턴스의 확정적인 사용에 대한 퍼텐셜이다. 이는 DC 출력 전압 요구가 낮아짐에 따라 필요해질 수 있다.

본 발명의 다른 이점은 전원의 그 본질을 포함하는 것이다. 이러한 소자 중 일부 또는 전체를 내장함으로써, 전력을 멀리 제공할 수 있다. 출력 커패시턴스가 마이크로프로세서 편상에서 필요한 바이패스 커패시터로만 구성되도록 함으로써, 마이크로프로세서 어셈블리를 공급하는 회로는 유도성 출력을 반드시 가질 수 있다.

함께 또는 별개로 취해지는 다양한 형태는, 증가되는 전력 변환 주파수가 다음 세대 저전압 요구에 대해 높은  $di/dt$  요구를 만족시기 위해 낮은 저장 에너지 접근을 제공하도록 할 수 있게 개시되어 있다. 따라서, 다른 목적은 회로를 제공하는 것, 및 저전압, 고전류 및 높은  $di/dt$  요구에 의한 전자부품에 전력을 제공하고, 실질적으로 높은 전력 변환 주파수를 제공하고, 변압기 누설 인덕턴스 및 스위칭 장치 커패시턴스의 합리적인 양을 가능케 하는 회로를 제공하고, 동기 정류기(SR)가 장치를 교차하여 항상 0V에 의해 스위칭됨으로써 고주파수 동작을 가능케 하는 회로 또는 방법을 제공하고, SR로의 제어 신호가 비손실 패턴에서 동작함으로써 HF 동작을 가능케 하는 회로 또는 방법을 제공하고, HF 동작을 통해 출력 커패시턴스의 감소된 사이즈를 제공하는 방법을 포함한다.

따라서, 일 실시예에서, 본 발명은, 전기 접속 주위의 자계의 감소 및 그에 저장된 자기 에너지를 통해, 빠른 응답 저장 및 중간의 파워-온을 생성함으로써, 에너지를 좀더 저장할 수 있고, 전력이 공급된 전자부품으로부터 물리적으로 멀리 위치 할 수 있는 에너지 저장 시스템으로 향한다. 자계의 감소 및 그 결과로 인덕턴스의 감소는 전자부품이 높은 속도에서 동작하게 하고, 증가된 에너지 저장은 파워 공급 시스템이 낮은 속도에서 동작하게 한다. 파워 공급 시스템 주파수의 이러한 감소는 고주파 파워 시스템을 사용하여 얻어질 수 있는 것에 비해, 비용을 낮게 할 수 있다.

유사하게, 다른 실시예의 본 발명은, 고주파 AC 파워를 부하 부근의 포인트로 배전하고, 파워 소비 시점에서 AC로부터 DC로 단일 변환을 행함으로써, 종래의 기술 중 많은 소자를 제거하는 전력 변환 시스템으로 향한다. 특히, 본 발명은 양호한 레귤레이션 및 과도 응답에 의해, AC 대 DC 변환, 및 고전압 AC 파워의 매우 낮은 DC 전압으로의 변환에 관한 문제점의 해결을 나타낸다.

종래의 기술 접근에서 많은 잉여 소자를 제거하면, 전력 손실 요소를 제거함으로써 효율성이 증가되고, 시스템으로부터 제거된 소자의 비용을 제거함으로써 비용도 감소된다. 또한, 높은 주파수 스위칭 손실이 매우 중요해지고 있고, 모든 다른 손실과 동일하거나 또한 이를 초과할 수 있기 때문에, 주파수의 감소는 파워 공급 시스템의 효율을 증가시킨다. 본 발명은, 에너지 저장 소자 및 상기 전력이 공급된 전자부품 사이의 컨덕터 주위의 자계의 양을 줄이는 메카니즘을 통해 길이에 제한이 없는, 에너지 저장 소자에 대해 낮은 인덕턴스 접속을 제공함으로써 이러한 목적 대부분을 실행한다.

또 다른 실시예에서, 본 발명은 매끄럽게 변화하거나 또는 정현파형의 고주파를 전송하며, 이는 주어진 주파수에 대해 상대적으로 전압 변화율이 낮고, 사각파 또는 사다리꼴 파형 배전 등의 교대 AC 접근에 비해 매우 낮음을 나타낸다. 종래의 기술에서 대개 행해졌던 DC 전압보다 정현파 커브의 AC 전압 배전은 중앙 전력 유닛을 단순화하고, 전압 레귤레이션 모듈을 매우 단순하게 함으로써, 비용을 줄이고 효율을 증가시킨다. 또한, 이러한 접근은 전력 유닛 및 인접한 회로 사이의 간섭을 감소시키고, 설계를 단순하게 하고, 사용 전원선을 따라 도통된 간섭을 방지하기 위해 사용된 라인 필터의 비용을 감소시킨다. 또한, 낮은 DC 전압(예컨대, 5V)의 배전은, 중간 전압 교대 배전 레벨(예컨대, 30 Vrms)의 사용에 비교하면, 배전선 및 커넥터에 상대적으로 높은 손실을 야기하지만, 그럼에도 불구하고 터치하기에 안전하다.

## 실시예

본 발명의 기본 컨셉은 다양한 방법으로 구체화될 수 있다. 이 컨셉은 장치와 함께 또는 이를 실행하는 프로세스 또는 방법을 포함한다. 또한, 일부 특수한 회로가 개시되어 있지만, 이는 임의의 방법을 실행할 뿐만 아니라 많은 방식으로 다양화될 수 있음을 이해해야 한다. 중요한 것은, 상기 전체에 대해, 이러한 단면 전체가 이 명세서에 의해 포함되는 것을 이해해야 하는 것이다.

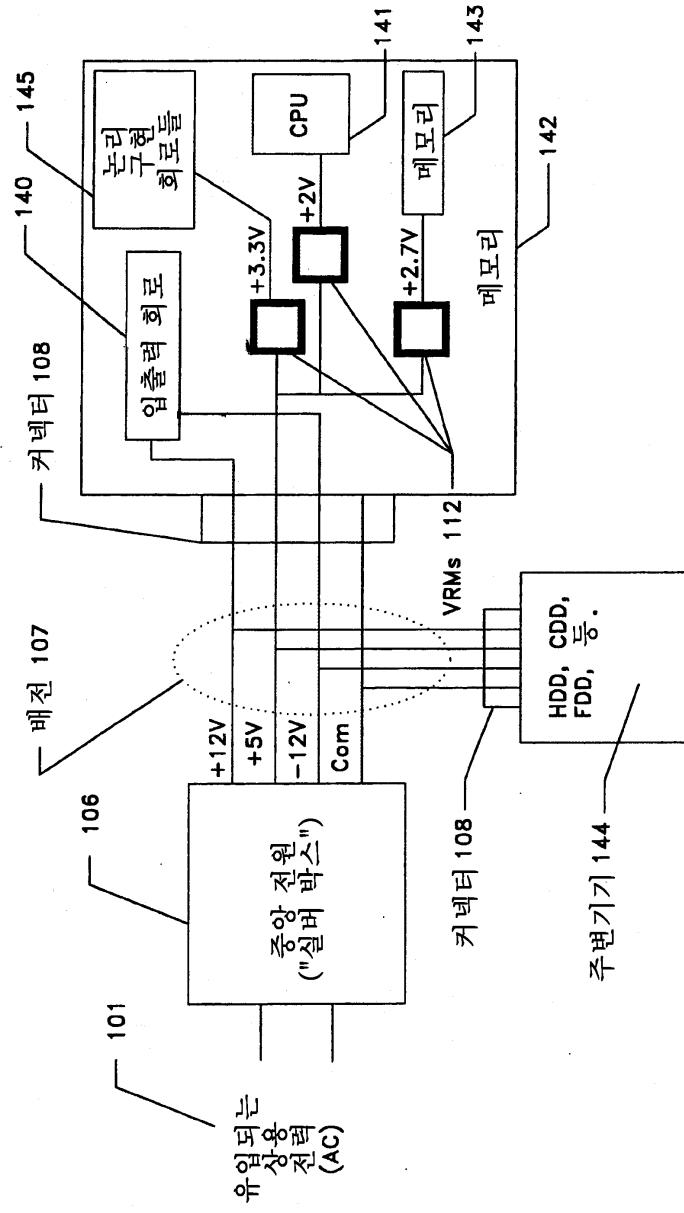

종래의 기술에서, 중앙 전원은 전자부품에 의한 사용에 대해 다양한 표준전압을 제공한다. 도1a를 참조하면, 전형적으로 50 또는 60 주기로 교대하는 110 또는 220V 공칭 AC 파워의 상용 전원(101)은 전원(106)에 의해 표준 DC 전압, 대개  $\pm 12$  및  $\pm 5V$ 로 변환된다. 이 전압은 플라잉(flying) 리드상의 전원으로부터 얻어지며, 이는 하나 이상의 커넥터(108)에서 종료되는, 일종의 배전 시스템(107)을 형성한다. 이러한 표준 전압은 입력/출력 회로(140), 및 하드디스크, 플로피 디스크 및 콤팩트디스크 드라이브 등의 주변장치(144) 중 대부분에 전력을 공급하는데 직접적으로 유용하다. 중앙 처리 유닛(CPU) 칩(141)의 기술이 발달됨에 따라, 상기에서 논의된 바와 같이, 이러한 칩의 동작 전압은 점점 더 높아지는 동작 속도에 대한 탐구에서 끊임없이 감소되고 있다. 이 프로세서 속도의 증가는 최후에 CPU에 대한 지시 및 데이터를 유지하기 위해 사용된 다이나믹 랜덤 액세스 메모리(DRAM)의 속도 증가를 요구했고, 그 결과로서, 이러한 DRAM 칩의 동작 전압도 감소되었다. 또한, 논리 중 어떤 것도 입력/출력 기능 및 특히 CPU로의 데이터의 흐름을 다루기 위해 요구되지 않으며, 메모리 및 외부 장치는 CPU 칩상에 존재한다. 하우스키핑 기능(클록 발생 등), 인터럽트 요구 처리 등과 함께, 이러한 매진트 기능은, 논리 구현 회로(145)로서 도1a에 도시한 "칩 세트"에 의해 처리될 수 있다. 이러한 회로는 또한 속도가 끊임 없이 증가되어 왔고, 이에 대응하여 낮은 동작 전압을 요구해왔다.

따라서, 표준 전압은 적절한 파워 CPU(141), 메모리(143), 및 매니지먼트 회로(145)에는 너무 높다. 이는 도1a에 도시한 바와 같이 모두 상이한 전압을 요구하며, 도시한 실제 전압은 오직 예이다. 이 상이한 전압은 개별적인 전압 레귤레이션 모듈(112)(VRM)에 의해 각각 생성될 수 있으며, 이는 전원(106)에 의해 공급되는 전압을 상기 전력이 공급된 회로에 의해 요구되는 전압으로 감소시킬 수 있다.

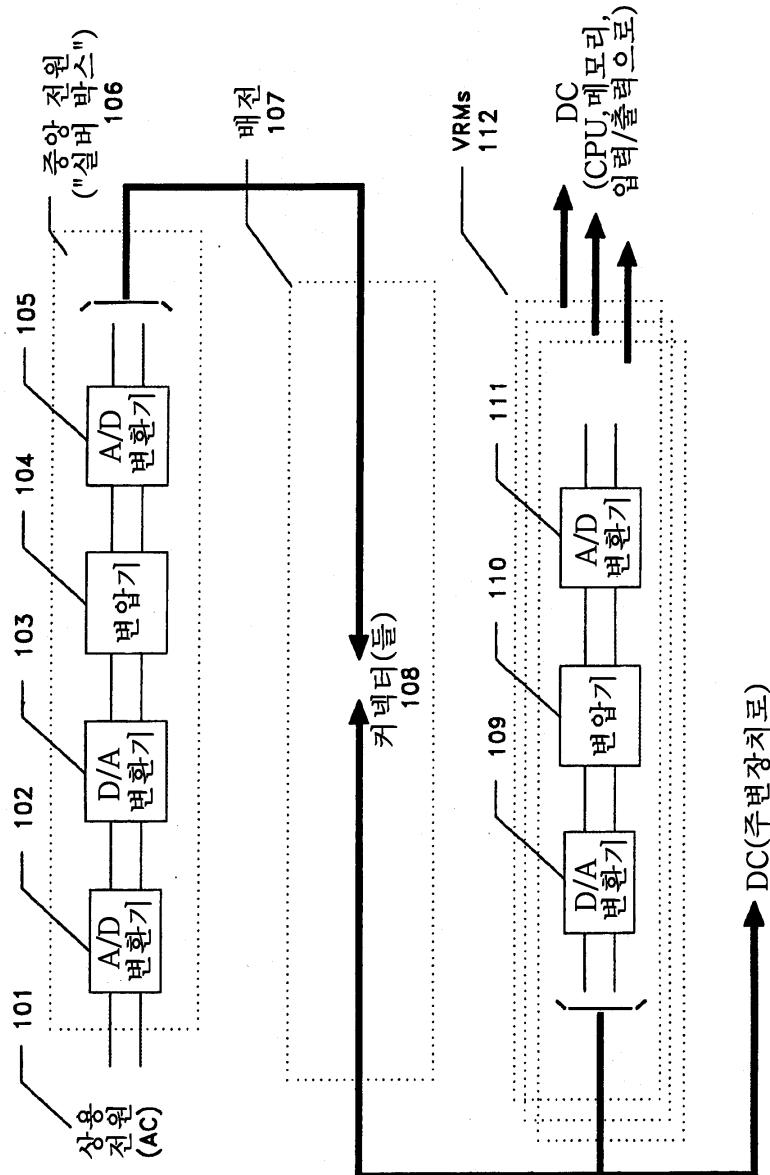

이상의 모든 관점으로부터, CPU(141) 등의 회로 부하에 전력을 전송하는 종래의 기술 프로세스는 전원(106) 내부의 파워 처리, 배전 시스템(107) 및 커넥터(108), 및 VRM 유닛(112) 내부의 파워 처리 전부를 포함한다. 이러한 이상의 모든 처리가 도1b에 도시되어 있다. 또한, "실버 박스"라 칭하는 중앙 전원(106)은 처리 소자(102,103,104,10)에 의해 스위치모드

기술을 사용한다. 또한, 상기 전압 레귤레이션 모듈(VRM)은 스위치모드 기술을 사용한다. 상기에 제공된 논의는 양 구성 요소에 모두 적용됨을 이해해야 한다. 따라서, 하나의 정황에서 논의되었던 다양한 형태가 잠재적으로 다른 것에 적용될 수 있음을 이해해야 한다. 상용 전원(101)은 실버 박스에 들어가고, 정류기 유닛 또는 AC/DC 변환기(102)에 의해 레귤레이트되지 않은 DC 파워로 변환된다. 그 후, 상기 결과의 DC 파워는 인버터 유닛(103)(또는, DC/AC 컨버터라 칭함)에 의해 고주파수에서 교류 전원으로 다시 변환된다. 고주파수 AC는 상용 전원(101)에 갈바닉 전기 접속되어, 상용 전원(101)의 전압 레벨에 있다. 안전을 고려하면, 상용 전원(101)으로부터 절연을 요구하며, 상기 요구되는 출력 전압이 상용 전원(101)에 비해 매우 낮으면, 전압 감소 또한 필요하다. 이러한 기능은 모두 변압기(104)에 의해 실행된다. 상기 결과의 절연되고 저전압인 AC는, 그 후, 배전용 배선(107) 및 커넥터(108)에 의해 회로 부하에 배전된 정류기 및 필터 유닛(105)에 의해, 직류 또는 다직류 전력 출력(들)으로 정류된다. 전술한 바와 같이, 특수한 표준 전압 ±12 및 +5V는 VRM 유닛(112)에 의해, CPU(141), 메모리(143) 및 구현 논리(145)에 대해 낮은 전압으로 변환되어야 한다. 전원 유닛(106)으로부터의 표준 DC 전압(보통 +5V)은 DC/AC 컨버터(109)에 의해 다시 교류 파워로 변환되고, 변압기(110)에 의해 저전압으로 변압되고, AC/DC 유닛(111)에 의해 적절한 저전압으로 다시 정류된다.

회로 부하로의 상기 전달된 전력의 전압이 감소함에 따라, 전류는 증가하고, CPU(141)의 속도가 증가됨에 따라, 또한 전력 시스템은 점점 커지는 전류의 변화율을 다룰 수 있어야 한다. 상기에 논의된 바와 같이, 이는 회로 부하에 가까운 전원을 요구하며, CPU 유닛(141)(및 다른 저전압 회로)에 대해서는 VRM(112)이다. 인접한 기간의 설계에 대해서는, 전류 변화율이 용량성 에너지 저장에 의해 다뤄질 수 있고, 더 낮은 전압 및 더 높은 전류의 미래 설계에 대해서는, VRM 유닛(112)이 회로 부하에 가까이 위치될 수 있도록 매우 작게 제조되어야 하고, 또한 많은 양의 에너지 저장이 요구되지 않도록 매우 높은 주파수에서 동작해야 한다. 낮은 에너지 저장에 대한 요구는, 큰 저장 소자에 대한 물리적 공간이 없고, 높은 고유 임피던스에 대해 허용이 되지 않는다는 2가지 사실에 근거한다. 따라서, VRM(112)의 주파수가 증가되어야 한다는 요구가 나타난다.

또한, 도1b는 적어도 2개의 제거될 수 있는 잉여 요소를 나타낸다. 배전용 직류 전원은 정류기 및 필터(105)를 요구하고, 낮은 레벨로 전압을 강하시키기 위한 필요는 인버터(109)에 의해 DC를 교류 전원으로의 재변환을 요구한다. 이 중 하나는 명백하게 불필요하다.

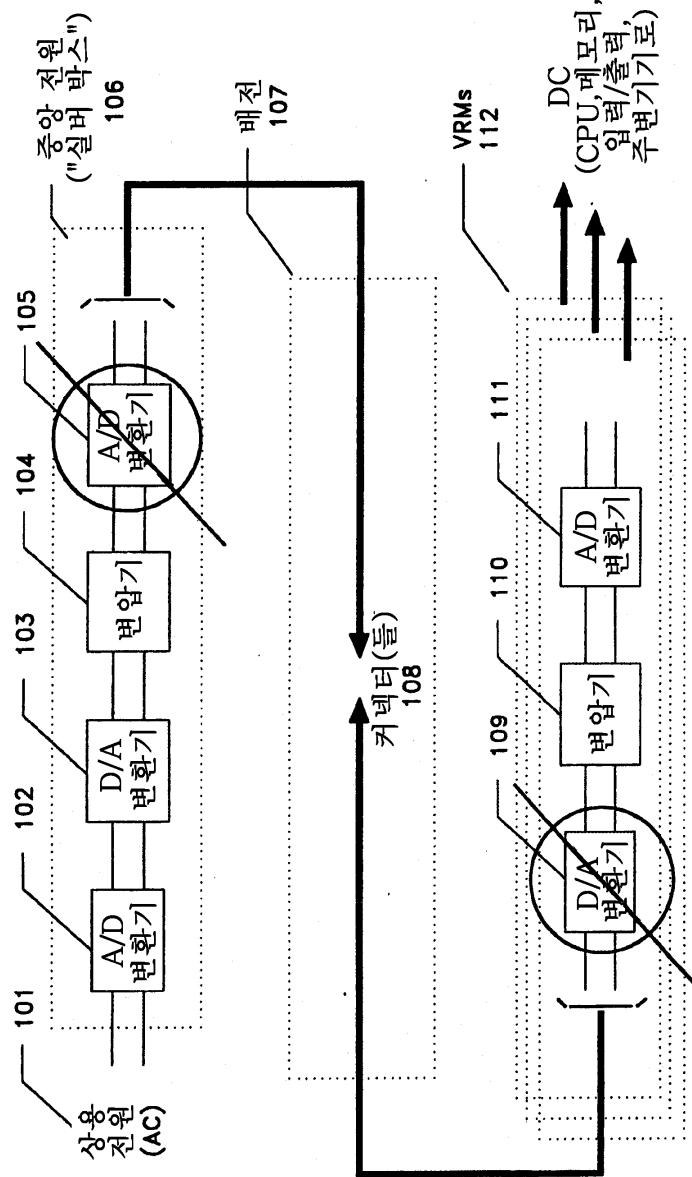

이는 소자(105,109)를 제거하고, 직류 전원 대신 교류 전원을 전송하기 위해 선택함으로써, 비용 감소의 가능성을 연다. 물론, AC의 활용은 소망의 혼성 시스템뿐만 아니라, 현재의 전통적인 DC 리드에 의해 구성될 수도 있다. 그러나, 활용에 되돌아가면, 전술한 바와 같이, 인버터(109)의 주파수는 증가되어 왔고, 계속해서 증가될 것이며, 이는 상기 감소된 시스템에서, 인버터(103)의 주파수가 시스템의 미래의 요구를 충족시키기 위해 적절한 레벨로 증가해야 하는 것을 요구한다. 도1c는 이러한 과정 소자를 나타낸다.

원칙적으로, 변압기(104,110) 사이에는 다른 불필요한 것이 존재하지만, 배전 시스템(107)에 절연된 파워를 제공하기 위한 소망은 변압기(104)의 사용을 요구하고, 상이한 부하에 대해 상이한 전압에 대한 요구는 또한 변압기(110)를 사용하기 위해 다양한 VRM을 요구할 수도 있다. 이러한 소자들이 적절한 위치에 놓여 있다고 가정하면, 그 후, 고주파 AC 배전을 사용하면 도1d에 도시한 바와 같이 시스템을 생성한다. 따라서, 일 실시예는 특히 단순화된 VRM으로 향하고 있다. 이러한 구성은 또한 파워 요소의 위치가 전기적으로 멀리 위치하게 한다(예컨대, 리드 인더턴스가 종래의 기술을 사용하여 다르게 작동하기 시작하는 위치).

도1d에서, 중앙 전원(147)은 AC/DC 컨버터(146)에 의해 상용 전원(101)을 DC 파워로 변환한다. 그 후, DC 파워는 DC/AC 컨버터(113)에 의해 고주파 정현파 커브 파워로 변환된다. 상기 정현파 커브 파워(또는, 이상적인 인버터 등에 비해 적은 양에 의해서도 생성될 수 있는, "실질적으로" 또는 "대략" 정현파 커브 파워)는 파워의 사용 위치에 배전되며, 여기서 고주파수 VRM(118)은 CPU(141), 입력/출력 회로(140), 논리 매니지먼트 회로(145) 및 메모리(143) 등의 회로 부하에 대해 사인곡선 파워를 저전압, 고전류 파워로 변환한다. 이러한 접근에서, VRM은 상기 저전압 회로에 대해서 뿐만 아니라, 주변 장치(144)에 대해서도 요구되며, 그 이유는 이러한 유닛에 대한 DC 파워(+12V 등) 요구가 중앙 전원(106)에 의해 공급되지 않기 때문이다(단, 중앙 전원(106)은 이러한 접근에서 사인곡선 고주파(AC)만을 공급할 수 있다). 따라서, 고주파 변압기(114)는 갈바닉 전기 절연을 제공할 수 있고, 일정한 전압의 사인곡선 DC/AC 컨버터(113)로부터의 전압을 접근하기에 안전하다고 생각되는 레벨로 변환할 수 있다.

전체 부하에 일정한 전류를 제공하는 배전 시스템을 구성할 수 있고, 이와 달리 이러한 부하에 일정한 전압을 제공할 수 있다. 다양한 전압을 요구하는 컴퓨터 시스템 및 다른 복합 전자 시스템의 구조는 후의 접근에 좀더 적합하다. 즉, 배전된 AC 전압의 크기는 어떤 출력 부하 변동, 심지어 마이크로세컨드 시간의 스케일에 대해서도 거의 상수에 가깝게 유지되는 것이 바람직하다. 따라서, 다양한 부하, 즉 종래 기술의 구성에 공급되는 파워에 변동을 야기하는 레벨에서 변화하는 부하를 수용할 수 있다. 또한, 전자파 장해(EMI)를 감소시키기 위해, 배전된 AC 전압의 전체 고조파 왜곡(total harmonic

distortion)(THD)을 낮게 유지하는 것이 중요할 수도 있다. 그러나, 본 발명은 일정한 전류를 제공하기 위해 수정될 수도 있음을 주의해야 한다. 즉, 당업자들은 쉽게 이해할 수 있듯이, 일정한 전류 애플리케이션의 사용에 대해, 일정한 전류가 공칭 회로에서 단락 회로로 변하는 부하에 전달되도록 상기 회로를 수정할 수 있다.

컨버터(113)는 부하와는 별개로, 로우 THD에 의해 일정한 출력 전압을 제공하도록 설계될 수 있다. 여기에 나타낸 일부 실시예는 컨버터(146)로부터 일정한 입력 DC 전압에 의해 공급되는 것에 의존한다. 또한, 대신 컨버터(113) 내부의 피드백에 의해 이 일정한 배전 전압을 생성하는 것이 가능하며, 그 후 이는 컨버터(146)로부터 일정한 입력 전압을 요구하지 않는다. 후의 접근 - 피드백을 통해 일정한 전압을 생성 - 은 피드백 시스템이 어떤 출력 부하 변동, 심지어 나노초 시간 스케일에 대해서도 출력 전압을 거의 일정하게 유지하도록 높은 밴드폭(고속)을 갖는 것을 요구한다. 이 피드백 접근은 실현하기에 어렵고 비용이 높을 수 있으며, 본 발명은 피드백 없이, 회로의 고유 동작에 의해 컨버터(113)로부터 일정한 전압을 실현하도록 하고 있다. 이는, 적어도 나노초당 약 0.2 A, 나노초당 약 0.5A, 나노초당 약 1A, 나노초당 약 3A, 나노초당 약 10A, 심지어 적어도 나노초당 약 30A 이상의 빠른 에너지 수요를 갖는 시스템의 필요를 만족시킬 수 있기 때문에, 중요할 수 있다. 또한,

- "나이퀴스트 주파수" 시간 이하(예컨대, 나이퀴스트 속도, 즉 사건의 샘플링 또는 전송이 시스템의 피드백-타입에 대해 발생할 수 있는 이론적인 최대 속도),

- 나이퀴스트 주파수 시간의 약 2 $\frac{1}{2}$ 배 이하,

- 나이퀴스트 주파수 시간의 약 5배 이하,

- 나이퀴스트 주파수 시간의 약 10배 이하,

- 상기 교류 전원 출력시간의 약 2배 이하,

- 상기 교류 전원 출력시간의 약 4배 이하,

- 약 200 나노초 이하,

- 약 500 나노초 이하,

- 약 1000 나노초 이하, 및

- 약 2000 나노초 이하 이내에서, 빠르게 상태의 변화에 반응할 수 있기 때문에, 중요할 수 있다.

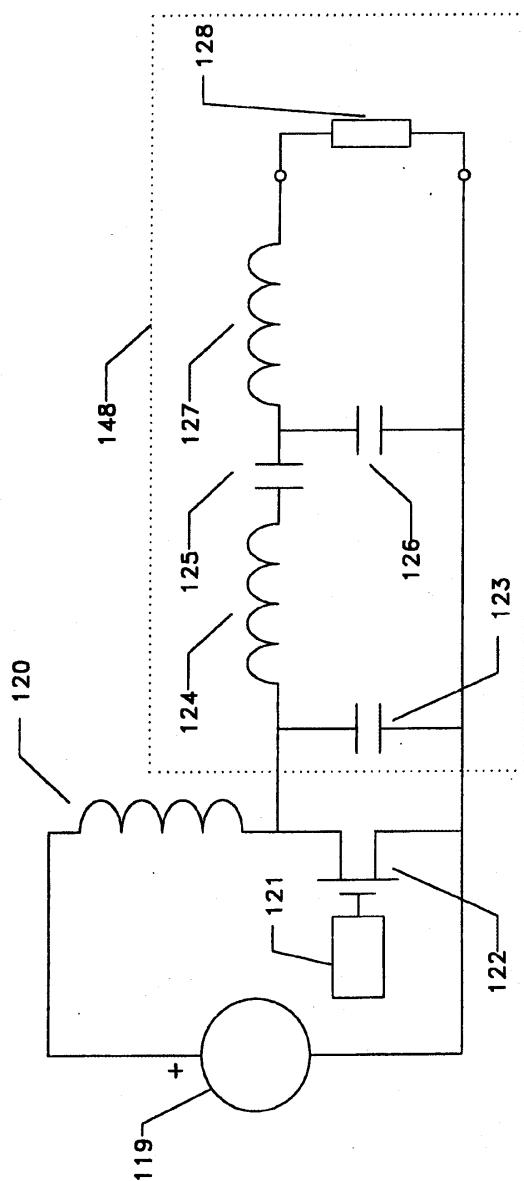

도1e는 컨버터(113)의 기능을 실행하는 일정한 전압의 고주파수 전원의 일 실시예를 도시한다. 여기서, DC 파워 소스(119)는 컨버터(146)로부터 일정한 전압을 나타내는 회로이고, 부하(128)는 배전 시스템(115)(커넥터(18) 및 배전 시스템(115)의 영향 포함)에 접속되어 있는 부하의 모임을 나타낸다. 소스(119)로부터의 전압은 인덕터(120)에 의해 일정한 전류로 변환되고, 스위치가 ON 일 때, 스위치에 의해 방향을 돌리거나, 또는 스위치가 OFF 일 때, 스위치(122)와 병렬인 소자를 포함하는, 네트워크(148)에 흘러들어 가게 한다. 따라서, 상기 네트워크는 응답 네트워크, 즉 스위치가 변화된 후에 작용하는 것으로서 작용한다. 스위치(122)를 교차하는 전압은, 스위치(122)가 ON 일 때는 대략 0이고, 스위치(122)가 OFF 일 때는 네트워크(148)의 응답에 의존한다. 이 응답 과정, 또는 "스위치 전압 과정"은 부하(128)를 교차하는 전압을 형성하기 위해 네트워크(148)에 의해 전환된다. 부하(128)의 컨덕턴스의 값에 관계없이, 적어도 부하(128)에 대한 컨덕턴스의 공칭 범위 내에서, 스위치 전압이 스위치(122)가 ON일 때의 시간 간격의 시작에서 0이 되도록, 소자(123,124,125,126,127)의 값을 선택하는 것은 가능하다고 판명되었다. 이는 다음 방식으로 실행될 수 있다. 부하(128)의 컨덕턴스가 매우 작으면(경부하), 인덕턴스(127)내에 거의 전류가 흐르지 않고, 그 값은 스위치(122)를 교차하는 과정에 크게 영향을 미치지 않는다. 그 후, 소자(123,124,125,126)의 값은, 스위치(122)가 도통을 개시하는 순간에, 스위치(122)를 교차하는 과정이 거의 0이 되도록, 또는 소망의 고정된 값이 되도록 선택될 수 있다. 이를 실행하는 방법론에 대한 명백한 설명이 US 특허 3,919,656 및 5,187,580에 개시되어 있다. 일단 이것이 실행되면, 부하(128)의 컨덕턴스는 최대 공칭 값, 및 그 ON 기간의 시작에서 스위치(122)를 교차하는 전압치를 제1 단계에서 선택된 값으로 되돌리기 위해 선택되는 인덕터(127)의 값으로 변화될 수 있다. 이 알고리즘은 상기 정의된 공칭 범위내에서, 스위치(122)의 ON 기간의 시작에서의 스위치 전압 과정의 값이 부하(128)의 컨덕턴스 값과 거의 관계가 없는 회로가 된다. 또한, 스위치 전압 과정의 형상이 부하(128)의 컨덕턴스의 범위 이상에서 최소한으로 변화하는 회로가 된다. 소자(123,124, 125, 126,127)에 의해 형성된 네트워크의 중요한 기능은 부하(128)를 교차하는 사인 과정을 형성하는 것이다. 이는 선형 패시브 네트워크, 즉 비액티브 소자(스티어링 다이오드, 일반적

인 다이오드, 다른 액티브 소자 등에 한정되지 않은 것을 제외하고 포함)에 의한 네트워크 또는 일부 타입의 피드백 소자(상태를 감지하고, 그 후 결과의 지연된 결정-타입의 결과로서 그 상태에 응답하는 소자)가 없는 네트워크이기 때문에, 스위치 전압 파형의 형상이 어떤 실질적인 방식으로 변화하지 않고, 특히 스위치 전압 파형의 기본적인 주파수 구성요소(동작 주파수의 파형의 푸리에 구성요소)가 실질적으로 변화하지 않으면, 이 회로에 대해, 부하(128)를 교차하는 정현파 커브 전압의 값은 실질적으로 변화하지 않는다. 따라서, 이러한 방법으로 소자(123, 124, 125, 126, 127)의 값을 선택하면, 부하(128)의 컨덕턴스의 값과 관계없이, 부하(128)를 교차하는 안정되고, 일정하고, 고주파수이며, 단순한 정현파 커브 전압이 되어, 따라서, 배전 시스템에 일정한 전압을 제공하는 목적을 실현하게 된다. 단, 일정한 출력 전압을 생성하는 이 네트워크의 동작은 매우 빠르다; 그 전체 공칭 범위 이상의 부하(128)의 컨덕턴스의 급격한 변화는 동작의 일부 사이클에서 수정될 수 있다. 이는 전형적인 피드백 접근이 동일한 수정을 할 수 있는 것에 비해 보다 빠르며, 빠른 작용 네트워크, 즉 시스템의 피드백 타입에서 상기 존재하는 지연을 겪지 않는 것을 제공하기 위해 다뤄진다.

본 발명의 특징은 공칭 부하에서 개방회로까지 또는 공칭 부하에서 단락 회로까지의 전체 부하 범위에 걸쳐 효율이 높다는 것이다. (당업자들이 이해하고 있는 것과 같이, 서로 반대되는 것을 얻을 수 있는 하나의 방법은, AC 배전 시스템을 1/4 파장만큼 변경하는 것이다. 이는 상기 일정한 고정 스위치 파형의 결과에 의해 발생한다. 전압 파형은 변하지만 부하 범위에 걸쳐서는 거의 변하지 않기 때문에, 회로에서의 스위칭 손실은 부하 변경에 의해 영향을 받지 않는다. 또한, 본 발명의 모든 이점은 동작 주파수를 변경하지 않고 얻어질 수 있다. 따라서, 적어도 약 80%, 적어도 약 85%, 적어도 약 90%, 적어도 약 95%, 적어도 약 98% 및 심지어 적어도 약 99% 효율 이상의 고효율을 얻을 수 있다.

고속으로 변화할 수 있는, 부하에 걸리는 정전압 정현파 출력(또는 반드시 부하에 "걸리지" 않고, 보다 일반적으로 부하가 비트의 직접 및 간접 응답을 포함하여 응답하는)을 제공하고, 단일 또는 다수의 스위치와 간단한 회로를 사용하고, 정 주파수에서 동작하는 반면, 전체 부하 범위에 걸쳐 고효율을 유지하는, 이와 같은 회로는 전력 변환의 분야에 있어서의 본 발명의 특징이다.

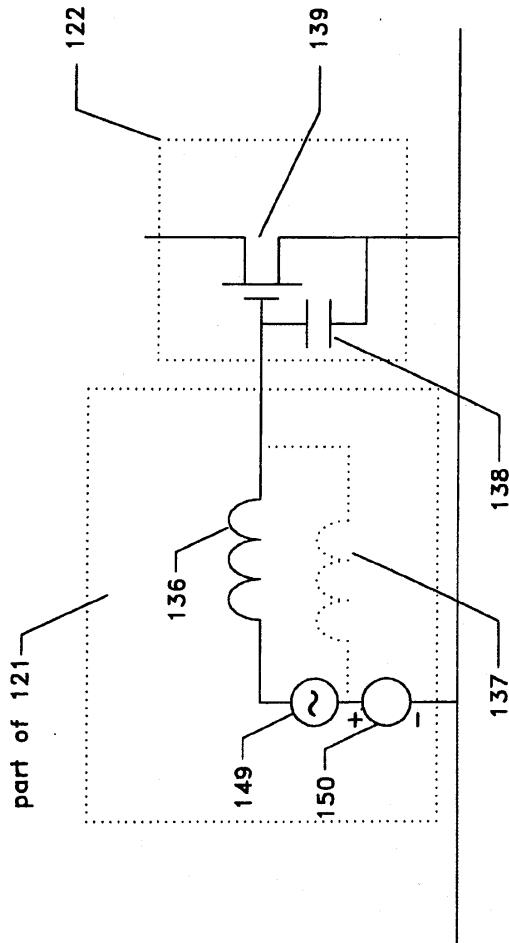

본 발명의 다른 특징은, 스위치(122)를 구동하는 방법이다. 앞서 지적한 바와 같이, 상기 적용에 있어서 효율은 중요하기 때문에, 스위치(122)를 구동하는 데 사용되는 회로를 포함하고 어디에서도 에너지를 낭비하지 않는 것이 바람직하다. 전계 효과 트랜지스터(FET) 등의 고주파 스위치의 특징은 입력 커패시턴스가 매우 크다는 것이다. 게이트단의 전압을 구형파로 변화시키는 회로는 스위치(122)용 게이트 임계 전압 이상의 전압 웰에 상기 커패시턴스를 우선 충전시키고, FET를 ON시켜, 그 공정에서 커패시턴스에 에너지를 축적해야 한다. 그 후, 스위치(22)용 게이트 임계 전압 이하의 전압 웰에 상기 커패시턴스를 방전해야 하고, 그 공정에서 게이트 커패시턴스에 저장된 에너지를 흡수한다. 상기 공정에서의 전력 손실은 동작 주파수를 곱한 게이트 커패시턴스에 저장된 에너지이며, 이는 상당한 수일 수 있다. 본 발명에서, 스위치(122)의 게이트 커패시턴스를 바람직하게 이용하여 게이트 또는 커패시턴스에 회로부를 정합함으로써 상기 손실을 피할 수 있다. 즉, 스위치(122)가 ON인 기간동안 게이트 커패시턴스에 저장된 에너지는, 본 발명에 있어서, 스위치(122)가 OFF인 기간동안 시스템의 다른 소자에 저장되기 때문에, 다음 ON 기간동안 임계 전압 이상으로 게이트를 회복시키기 위해 다음 사이클에 이용된다. 이는 게이트 커패시턴스(또는 시스템의 유효 커패시턴스)를 직렬 또는 병렬 인덕터와 "공진"시킴으로써 달성될 수 있다. 전체 시스템은 출력 주파수 및 스위치의 출력 커패시턴스와 정합하도록 동조된다. 도1g를 참조하여, FET 스위치(122)는 별도로 나타낸 바와 같이, 분명한 게이트 커패시턴스(138)를 갖는 내부 스위치 장치(139)로서 도시되고 있다. 본 발명에 의하면, 게이트 구동 회로(121)는 직렬로 접속된 인덕터(136)(또는 점선으로 다르게 접속한 것과 같이 평행으로 접속된 인덕터(137))를 포함한다. 상기 인덕터는, 인덕터(136)(137)의 리액턴스가 동작 주파수에서 커패시터(138)의 리액턴스와 동일하도록 선택된다. 이 때, 게이트 시스템의 에너지는 게이트 커패시터(138)에서 인덕터(136)(137)까지 전송되며, 각 사이클을 다시 반복하기 때문에, 인덕터 및 게이트 레지스턴스에서의 불가피한 손실을 각 사이클마다 재생시킬 필요가 있다.

이와 같은 시스템에서, 게이트 전압은 실질적으로 정현파이다. 시스템의 듀티 사이클(즉, 스위치(122)가 ON인 총 기간의 일부)이 실제로 스위치(122)의 임계 전압 이상인 정현파 주기의 일부에 의해 결정되는 것은 당업자들에게 명확하다. 또한, 스위치(122)의 듀티 사이클은, 정현파 신호의 진폭에 의해 제어될 수 있고, 이와 같은 접근은 듀티 사이클의 유용한 범위에 제한을 두게 되며, 바람직한 정류 회수(즉, 스위치가 ON에서 OFF 상태로 천이하는 총 기간중의 일부)보다 긴 결과를 가져올 수 있다. 이는 스위치(122)의 손실을 증가시킬 수 있어 시스템의 효율성을 감소시킨다. 이 때문에, 스위치(122)에 대한 구동 파형은 본 발명에서 AC부(149) 및 DC부(150)로 나누어질 수 있고, 스위치(122)의 구동 파형의 AC 및 DC 성분의 상대적인 진폭을 변화시킴으로써 스위치(122)의 듀티 사이클의 변화를 제어할 수 있다.

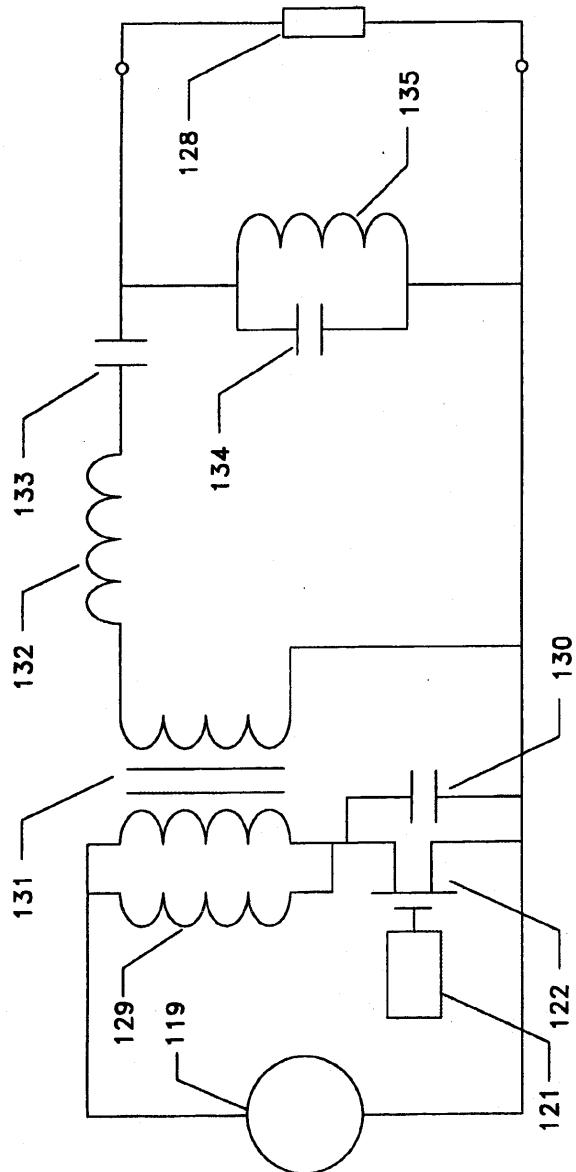

정전압, 고주파 전원 발생에 대한 다른 접근을 도1f에 도시한다. 이하, DC 전원(119)은 컨버터(146)로부터의 정전압을 나타낸 회로이고, 부하(128)는 배전 시스템(115)(컨버터(108) 및 배전 시스템(115)의 영향을 포함)에 접속된 부하들의 집합을 나타낸다. 스위치(122)는 소스(119)와 병렬로, 인덕터(129)와 직렬로 배치된다. 인덕터(129)에 걸리는 전압은 변압기(131)에 의해 변압되고 소자(132, 133, 134, 135)를 포함하는 네트워크에 걸린다. 상기 네트워크는 배전 시스템(컨버터(108)와

배전 시스템의 효과를 포함)(115)에 접속된 부하들의 집합을 대표하는, 부하(128)에 걸리는 출력 전압을 생성한다. 회로 소자들의 값이 적절히 선택되면, 상기 출력 전압은, 이러한 컨덕턴스의 명목상의 범위 내에서, 부하(128)의 컨덕턴스의 값에 무관할 것이다. 상기 독립성을 위해, 일례로서, 변압기(131)의 자화 인덕턴스와 병렬의 인덕터(129)의 리액턴스를, 동작 주파수에서의 스위치(122)의 보조 출력 커패시턴스와 평행한 커패시터(130)의 리액턴스와 동일하게 하고, 변압기(131)의 누설 인덕턴스와 직렬인 인덕터(132)의 리액턴스를, 동작 주파수에서의 커패시터(133)의 리액턴스와 동일하게 하며, 인덕터(134)의 리액턴스를 동작 주파수에서의 커패시터(35)의 리액턴스와 동일하게 하도록 소자들의 값을 선택하는 것은 충분하다. 이와 같이 회로 소자들의 값을 선택하는 것에 의해, 부하(128)의 컨덕턴스값에 관계없이 부하(128)에 걸리는 안정하고 일정하며 고주파인 순수 정현파 전압을 얻을 수 있기 때문에, 배전 시스템에 정전압을 제공하는 목적을 실현할 수 있다.

최소 부하 컨덕턴스가 0에 가깝지 않으면, 인덕터(134) 및 커패시터(135)에 의해 형성된 병렬 공진 회로에 대한 필요성이 감소한다. 즉, 소자들(134,135)로 구성된 네트워크는 부하(128)가 제거되거나 매우 낮은 값으로 감소하면 출력 파형을 정현파로 유지하도록 발생기에 최소 부하를 제공하는 기능을 갖는다. 본 발명이 적용되는 경우에 낮은 값으로 부하가 변경되지 않거나, 광 부하에 낮은 THD가 필요하지 않으면, 소자(134,135)들을 포함하는 네트워크가 불필요하게 될 수 있다. 또한, 소자(134,135)들을 포함하는 네트워크는, 최고 효율이 요구되지 않는다면, 인덕터 또는 커패시터의 단일 소자로 줄여들 수 있다.

일반적으로, 변압기(131)의 자화 인덕턴스를 바람직하게 이용함으로써 인덕터(129)도 불필요하게 될 수 있다. 이와 유사하게, 일반적으로, 변압기(131)의 누설 인덕턴스를 바람직하게 이용함으로써 인덕터(132)가 불필요하게 될 수 있다. 이는, 당업자들에게 공지된 바와 같이 변압기(131)의 구조를 변경함으로써 실현될 수 있다.

상기한 바와 같이, 고효율을 달성하기 위해, 스위치(122)의 게이트 커패시턴스를 바람직하게 이용하는 것이 중요하고, 도1g를 참조한 모든 설명은 도1f의 실시예에도 적용된다.

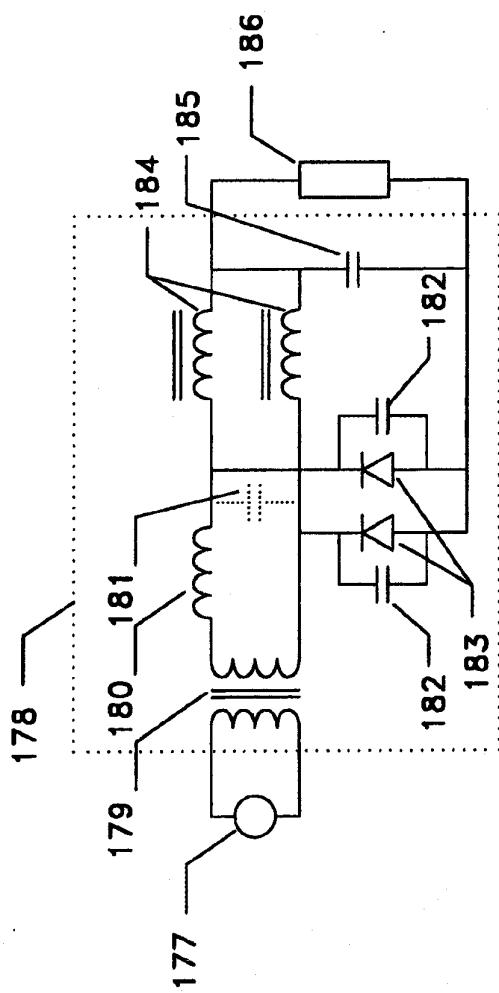

도1d를 참조하여 상기한 바와 같이, AC/DC 소자(146)와 함께 동작하는 컨버터(113)는 부하에 관계없이 낮은 THD에서 일정한 고주파 AC 출력 전압을 제공하도록 고안되어 있다. VRM(118)은 전원(147)으로부터의 상기 고주파 AC 전원을 전원이 공급되는 회로부(145,141,143)에 의해 사용되는 저전압 대전류 DC 파워로 변환해야 하는 것은 VRM(118)이다. 도1h는 본 발명에 의한 상기 변환을 달성하기 위해 VRM의 일 실시예 중 정류부에 대한 일 실시예를 나타낸다. 전원(147)으로부터 나오는 입력 AC 전원은 또한 정류 프로세스 전에 그 안정성을 향상시키도록 더욱 프로세스될 수 있고, 상기 부가된 프로세싱은 도1d에 도시되지 않는다. 상기 프로세싱의 결과는 도1h의 점선 박스에 나타낸 정류회로(178)로의 안정하게 조정된 AC 입력(177)이다.

정류회로(178)는 1차 및 2차 권선 사이의 불완전한 결합에 의해 발생되는 누설 인덕턴스를 실제로 나타내는 변압기(179)를 포함하고 있다. 상기 누설 인덕턴스는 일반적으로 변압기의 1차 및 2차 권선과 직렬의 인덕턴스로서 표시된다. 도1h에서, 누설 인덕턴스는 인덕터(180)로 표시되기 때문에, 회로의 실제 부품이 아니라 간단히 실제 변압기(179) 일부의 회로로 표시될 수 있다. 당업자들에게는 자명한 바와 같이, 변압기(179)의 내추럴 누설 인덕턴스가 원하는 것보다 작으면, 2차(또는 1차) 권선과 직렬로 부가적인 인덕턴스를 부가하여 내추럴 값을 증가시켜야 한다. 본 발명의 목적을 위해, 인덕터(180)는 변압기(179)의 내추럴 누설 인덕턴스와 다른 목적으로 부가된 부가적인 별개의 인덕턴스의 총합으로 고려된다.

다이오드(83)는 변압기(179)의 AC 출력을 정류하고, 필터 인덕턴스(184) 및 필터 커패시터(185)는 마이크로프로세서 또는 다른 전기적 부하(186)에 의해 소비되는 정상 DC 출력을 생성한다. 낮은 출력 전압에 있어서, 다이오드(183)에 걸리는 전압 강하는 상기 출력 전압에 비해 매우 크기 때문에 효율이 떨어진다. 그 결과, 다이오드(183)는 전계 효과 트랜지스터(FET) 스위치에 의해 적절히 대체될 수 있고, 전압 강하가 매우 낮게 제조될 수 있다. 이 경우, FET 장치는 그 도통 기간을 결정하기 위해 구동 신호를 필요로 한다. 이를 행하는 회로는 도1h에는 도시되지 않는다.

출력 전압이 강하함에 따라 발생하는 두 번째 문제는 변압기(179)의 인트린직 누설 인덕턴스이다. 상기 인덕턴스는, 다른 회로의 인덕턴스와 함께, 인덕터(180)로서 표시되며, 전체 회로의 출력 임피던스를 증가시키는 직렬 임피던스로서 작용한다. 즉, 인덕터(180)의 리액턴스와 부하 임피던스(136) 사이의 내추럴 전압 분배가 있기 때문에, 출력 전압이 부하(186)의 저항에 변함에도 불구하고 고정되어 있다면 보상용 입력 전압이 증가되어야 한다. 상기 전압 분배는 출력전압이 부하(186)의 저항에 크게 작용하게 하며, 이는 회로의 출력 임피던스가 부하 저항(186)에 비해 작지 않다는 것을 설명하는 또 다른 방식이다.

도1h에 도시된 다이오드(183)는, 그 다이오드의 전압이 그 캐소드에 비해 양일 때마다 이상적으로 도통하고, 상기 전압이 역극성일 때는 도통하지 않는다. 이것은 소위 제로 전압 스위칭, 즉 ZVS이다. 그 이유는, 도통 상태에서 비도통 상태로 바

끼는 스위칭점 즉, 천이가 파형의 제로 전압점에서 발생하기 때문이다. ZVS에서 FET 장치를 동작시키면, 상기 장치가 그 출력 커패시턴스로부터의 에너지, 즉 스위치와 평행한 커패시터(182)에 저장된 에너지를 방전할 필요가 없어, 손실이 줄어들기 때문에 바람직하다. 부하(186)를 흐르는 출력 전류가 증가함에 따라, ZVS를 생성하는 스위치의 타이밍이 변해야 하고, FET 구동 회로부를 복잡하게 할 수 있다. 그러나, 다음 도면들의 설명에서, 스위치들은 ZVS 조건에서 동작한다는 것, 또는 실제 다이오드가 사용된다는 것을 추정할 수 있다.

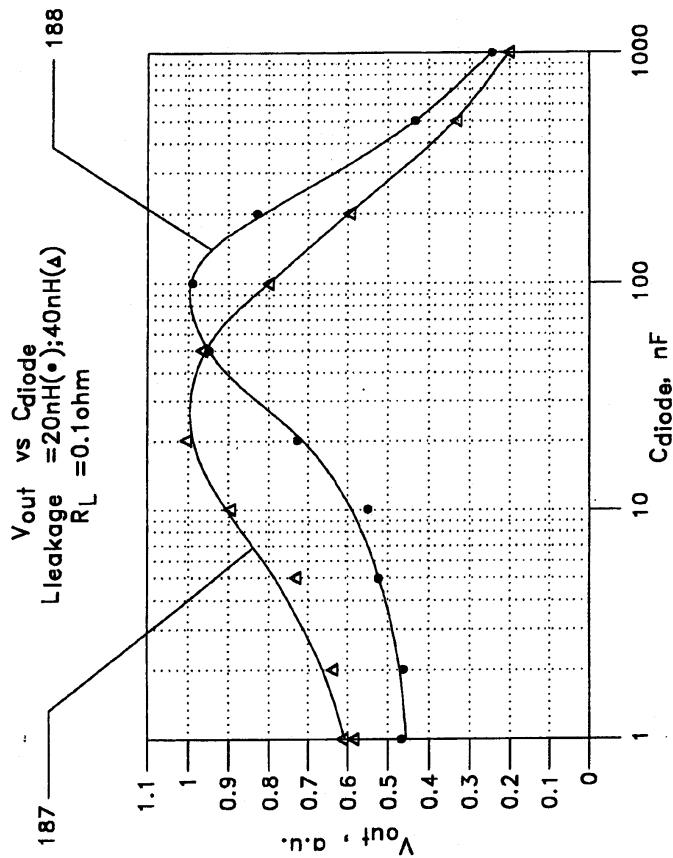

도1i는 다이오드(183)와 병렬로 배치된 커패시턴스(182) 값의 변화에 따라 출력 전압이 변하는 모양을 나타낸다. 상기 곡선은 3.39 MHz의 동작 주파수에 대해 그려지고 있다. 도1i에서 알 수 있는 바와 같이, 커패시턴스(182)의 값이 증가함에 따라, 출력 전압(즉, 부하 저항에 걸리는 전압)(186)은 증가하기 시작하지만, 커패시턴스(182)의 값이 계속 증가하면, 부하 저항(186)에 걸리는 전압은 다시 하강하기 시작한다. 따라서, 최고 전압 전송 기능을 갖는 커패시턴스의 최적치가 존재한다. 도1i에서는, 2개의 커브가 도시되며, 커브(187)는 인덕턴스(180)의 값이 40nH일 때이고, 커브(188)는 인덕턴스(180)의 값이 20nH일 때이다. 커브(187)는 출력전압의 피크가 커패시턴스(182)의 값이 약 27 nF일 때 발생하고, 커브(188)는 커패시턴스의 값이 약 86nF일 때 피크가 발생하는 것을 보여준다. 상기 2개의 커브가 별개의 2개의 팩터인 인덕터(180)의 값에 대한 것이기 때문에, 커패시턴스(182) 및 인덕터(180)의 값이 공진조건을 만족하는 경우와 같이 별개의 팩터(86/27>3)가 아니다. 이는, 최대 출력 조건이 발생기(177)로부터 나오는 입력 전원의 주파수에서의 공진 조건과 동일하지 않다는 것을 의미한다. 상기 2개의 커패시터(180)는 변압기(179)의 1차 권선 및 인덕터(180)와 병렬로 배치되는 하나의 커패시터(181)로 대체될 수 있다. 다이오드(183)의 전류가 이 경우에는 동일하지 않더라도 결과가 동일하다.

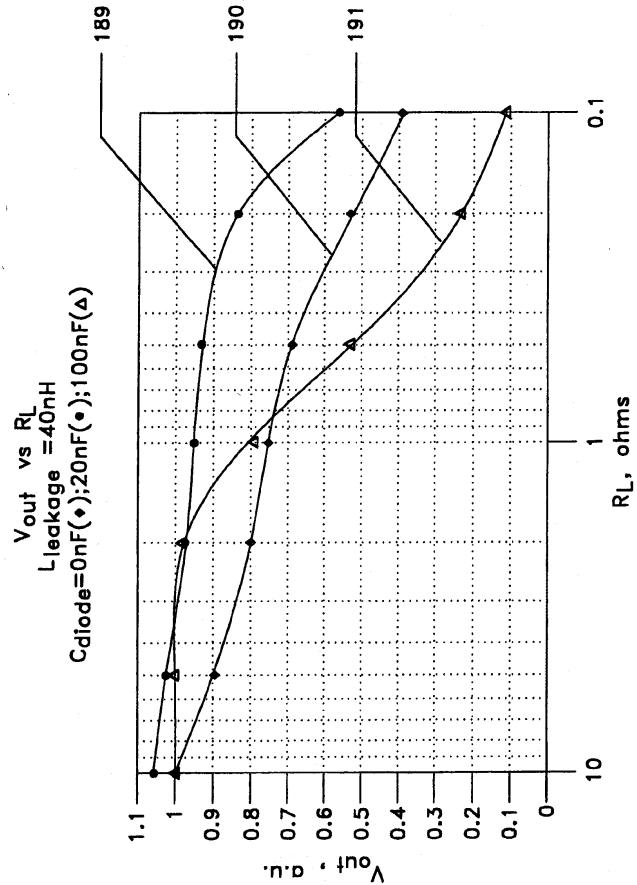

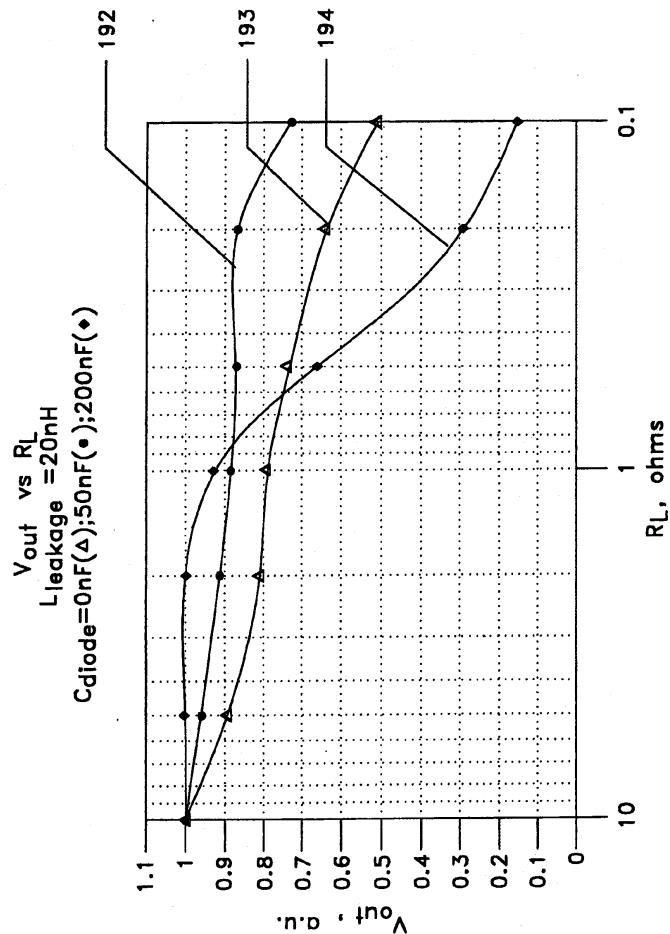

도1j 및 도1k는 부하 저항(186)의 기능으로서 부하 저항(186)에 걸리는 전압을 나타낸다. 상기 커브의 기울기는 회로(178)의 출력 임피던스의 측정치이다. 즉, 기울기가 0이면, 출력 임피던스는 0이고, 회로는 피드백이 없는 "내추럴 레귤레이션"을 나타낸다. 도1j의 커브(189)와 도1k의 커브(192)는, 부하 저항(186)에 걸리는 전압의 피크치와 동일한 커패시턴스(182)의 값에 대해서는, 피드백 없이 거의 0의 기울기가 얻어지는 것을 보여준다. 즉, 인덕턴스(180)에 대해 커패시턴스(182)의 값을 적절히 선택하기 위해, 부하 저항(186)에 걸리는 전압은 부하저항(186)의 실제 값에 비교적 무관하게 되고, 출력은 "내추럴 레귤레이션"된다. 피드백이 없는 내추럴 조정의 이점은, 레퍼런스와 비교하여 출력전압의 변화를 인식하고, 회로 내부의 파라미터를 변경하기 위해 피드백 시스템을 기다릴 필요가 없게 되는 것이다. 상기 조건하에서, 출력 전압은 안정한 피드백 시스템에 비해 짧은 동작 주파수의 1 또는 2 사이클 내에서 일정하게 유지된다.

이와 같이, 부하 저항의 급격한 변화의 조건하에서도 피드백 없이 광범위한 부하 저항에 대해 안정한 출력전압을 생성하는 시스템에 대해 설명했다. 도면에 도시된 출력의 변화를 허용하는 시스템에 있어서는, 피드백이 필요하지 않다. 부하가 변하는 조건하에서 출력 전압을 엄격히 제어할 필요가 있는 시스템에 있어서는, 피드백이 부가될 수 있다. 본 발명에 의해, 피드백 시스템의 일부를 동작시킬 필요성이 감소하기 때문에, 사용되는 피드백 회로를 보다 간단하고 고속으로 저렴하게 할 수 있다.

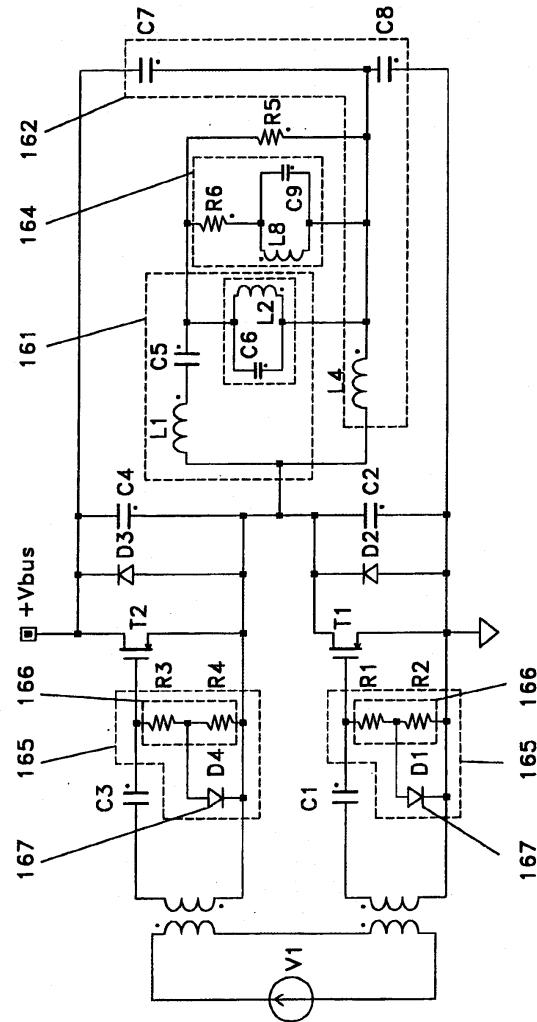

상기한 바와 같이, 본 발명의 목적을 실현하기 위해, 각종 방법으로 회로를 구체화할 수 있다. 일반적으로 예컨대, 회로 설계의 다른 예로서 도11을 참조하면, 회로를 이해할 수 있다. 상기 회로는 보다 일반적으로 진술된 각종 소자들의 조합을 가질 수 있다. 우선, 상기 회로는 일정한 출력전압소자(161)와 같은 일정한 출력 소자를 가질 수 있다, 상기 구성에 있어서, 일정한 출력 소자는 가변 부하로부터 발생할 수 있는 변경에 관계없이 몇 개의 출력 파라미터를 일정하는 유지를 한다. 당업자들이라면, 유지되는 파라미터들이 각종 파라미터들로부터 선택될 수 있고, 다음과 같은 파라미터들을 포함하고 있지만 이에 한정되지 않는다는 것을 용이하게 이해할 수 있을 것이다:

- 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐 거의 일정한 스위치 전압 출력,

- 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐 거의 일정한 부하 전압 출력,

- 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐 거의 일정한 스위치 전압 푸리에 변환,

- 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐 거의 일정한 스위치 전압 출력 파형,

- 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐 거의 일정한 스위치 전압 천이 최종점, 및

- 상기 각각의 교환 및 조합들.

도시된 구성에 있어서, 상기 일정한 출력 전압소자(161)는 기본적인 동작 주파수에서의 직렬 공진에 동조될 수 있는 인덕터 L1 및 커패시터 C5, 기본적인 동작 주파수에서의 병렬 공진에 동조될 수 있는 인덕터 L2 및 커패시터 C6, 및 하프 브리

지 구성에 공통인 저 AC 임피던스와 전원이 공급될 부하를 나타내는 R5에 하프 전원(half supply)을 형성하도록 배치된 커패시터 C7 및 C8을 갖는다. 물론, 상기 일반적인 원리로부터 당업자들은 용이하게 이해할 수 있는 바와 같이, 상기 기본적인 목적을 실현하도록 다른 디자인이 구성될 수 있다.

둘째, 상기 시스템은 일정한 직교절선 소자(162)와 같은 일정한 직교절선 소자를 포함할 수 있다. 상기 구성에 있어서, 일정한 직교절선 소자는 가변 부하로부터 발생할 수 있는 변화에 관계없이 거의 일정한 응답 파형(또는 파형의 푸리어 성분)을 유지하는 작용을 한다. 도시된 구성에서, 상기 일정한 직교절선 소자(162)에서는 하프 전원(커패시터 C7 및 C8로 도시됨)에 인덕터(L4)가 접속되어 있다. 상기 일정한 직교절선 소자(162)는, 스위치 T1 도통에서 스위치 T2 도통으로 천이(또는 반대)할 때 정전류를 제공한다. 여기서, 다이오드 D2 및 커패시터 C2가 스위치 T1의 부속 소자이고, 다이오드 D3 및 커패시터 C4가 스위치 T2의 부속 소자이다. 유지되고 있는 직교절선은 시간에 대한 전압의 연속 2계 도함수를 나타내는 직교절선으로 유지될 수 있다. 이하에 나타낸 바와 같이, 일정한 최종점을 실현하도록 설계될 수도 있다. 최종점은 0이 될 수도 있고 그렇지 않을 수도 있다. 예컨대, 최종점이 0이 되지 않도록 설계하는 것이 바람직할 수 있다. 이와 같은 설계는, 상기 가변 부하가 실제로 존재하는 모든 레벨에 걸쳐, OV 전압, 다이오드 ON 레벨보다 낮은 전압, 상기 스위치 DC 스위치 전원 전압의 약 5% 이하의 전압, 상기 스위치 DC 전원 전압의 약 10% 이하의 전압, 상기 스위치 DC 전원 전압의 약 20% 이하의 전압, 및 상기 스위치 DC 전원 전압의 약 50% 이하의 전압 등의 값을 포함한다. 그러나, 일정한 결과(직교절선, 최종점, 또는 이외의 것)는, 스위치가 ON되는 순간 또는 매우 중요할 수 있는 보디(BODY) 다이오드가 ON되지 않을 때의 전압이기 때문에 중요하다. 또한, 상기 일반적인 원리로부터, 당업자들이 용이하게 알 수 있는 바와 같이, 상기 기본적인 목적을 실현하도록 다른 설계를 구성할 수 있다. 이에 따라, 거의 부하에 무관하고 직교절선 고정응답을 제공하는 네트워크를 제공할 수 있다. 또한, 다수 스위치의 밸런스 커패시턴스 특성 등의 임의 부품의 비선형 전송 특성, 변압기의 비선형 전송 특성 등이, 최적의 결과를 위해 네트워크에 의해 바람직하게 이용될 수 있다.

셋째, 상기 회로는 에너지 유지회로(163) 등의 에너지 유지소자를 포함한다. 여기서, 상기 에너지 유지회로(163)는 가변 부하로부터 발생할 수 있는 변화에 관계없이 일정해야 하는 에너지를 유지하는 작용을 한다. 도시된 구성에 있어서, 상기 에너지 유지회로(163)는 인덕터 L2와 병렬로 구성된 커패시터 C6을 포함하며, 상기 인덕터와 커패시터는 R5로 도시된 부하와 병렬이다. 상기 소자는 이미 언급된 부하의 고속 에너지 요구를 거의 모두 제공하도록 작용할 수 있다. 또한, 상기와 같이 기본적인 목적을 실현하기 위해 다른 설계가 구성될 수도 있다.

넷째, 상기 회로는 도시된 안정화소자(164) 등의 몇 가지의 안정화소자를 포함할 수 있다. 상기 안정화소자(164)는 이하 레퍼런스에 포함된 미국 특허 제 5,747,935에 기재된 원리에 따라 기본 주파수에는 없는 에너지를 흡수하는 기능을 한다.

마지막으로, 상기 회로는 각 스위치에 도시된 바와 같은 직류 바이어스 변경소자(165) 등의 자동 바이어스 네트워크를 포함할 수 있다. 상기 구성에 있어서, 상기 네트워크는 다이오드(167) 등의 도통 제어소자를 갖는 분압기(166)를 포함할 수 있다. 여기서, 분압기(166)는 각각  $1K\Omega$  등의 높은 값을 있고, 동일한 것이 선택될 수 있는 2개의 저항 R1 및 R2를 사용한다. 상기 소자는 AC 구동 진폭에 비례하는 부 바이어스를 제공한다. 그 결과는 구동 진폭에 관계없는 도통 기간이다. 따라서, 어떤 스위치도 도통 상태가 아닌 경우 고정 불감시간(응답 시간)을 제공할 수 있다. 또한, 상기 일반적인 원리로부터, 상기 기본 목적을 실현하도록 다른 설계를 구성할 수 있다.

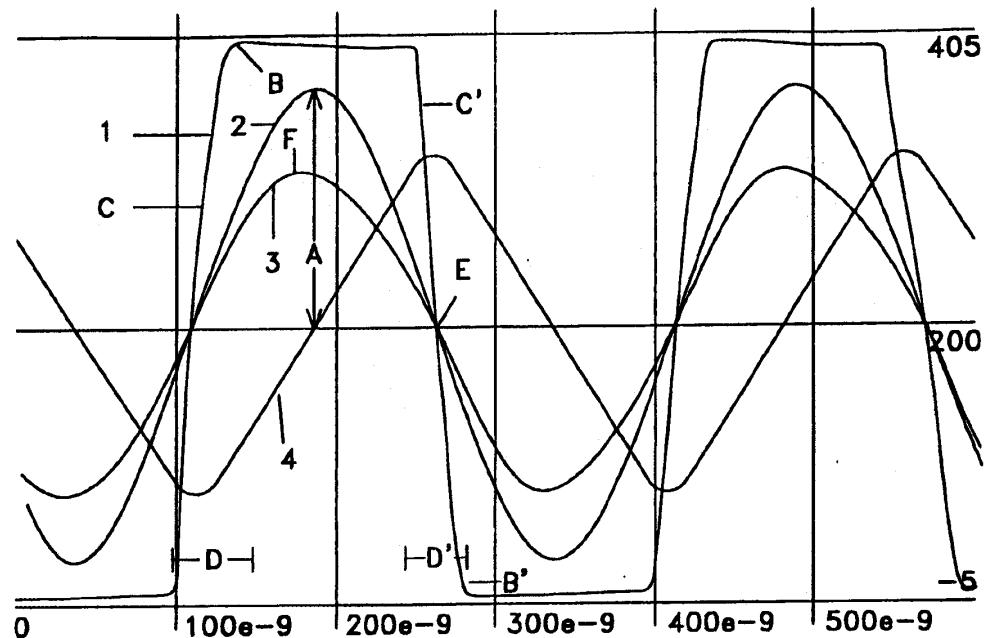

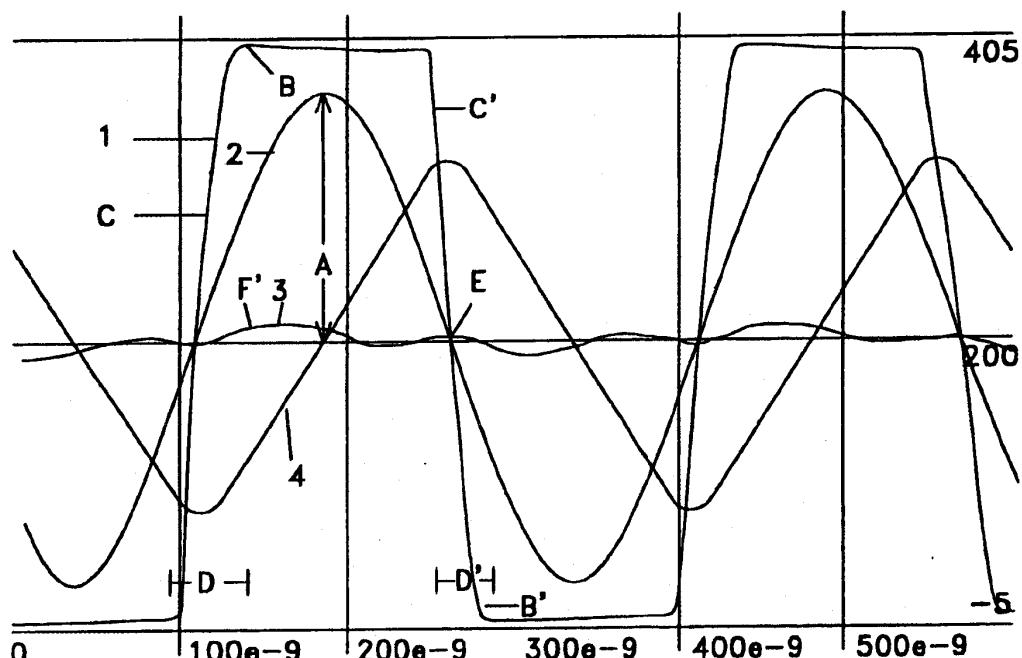

도1m 및 1n에 도시된 바와 같이, 본 발명에 의해 적절히 구성된 시스템이 상기 안정도 특징을 갖는 방법을 알 수 있다. 플롯 1-4는 다음과 같은 파형을 나타내고 있다.

1-스위치 T1과 T2 사이의 접합점에서의 전압;

2-부하 R5에 걸린 출력 전압;

3-L1에 흐르는 전류; 및

4-L4에 흐르는 전류.

상기 두 도면에 도시된 바와 같은 동일한 네트워크에 대한 고부하 및 저부하 상황을 비교함으로써, 여러가지의 결과를 알 수 있다. L1(F,F')에서 네트워크로 흐르는 전류로 도시된 바와 같이 심하게 변하는 전원 및 부하 전류가 존재하더라도, 상기 결과는, 일정한 출력전압(A), 일정한 최종점(B,B'), 일정한 직교절선(C,C'), 일정한 응답기간(D,D'), 제로 전압 스위치(B,B'), 및 천이시의 제로 부하전류의 발생(E)을 포함한다. 당업자들이 용이하게 이해할 수 있는 것과 같이 다른 특징들도 주목할 만하다.

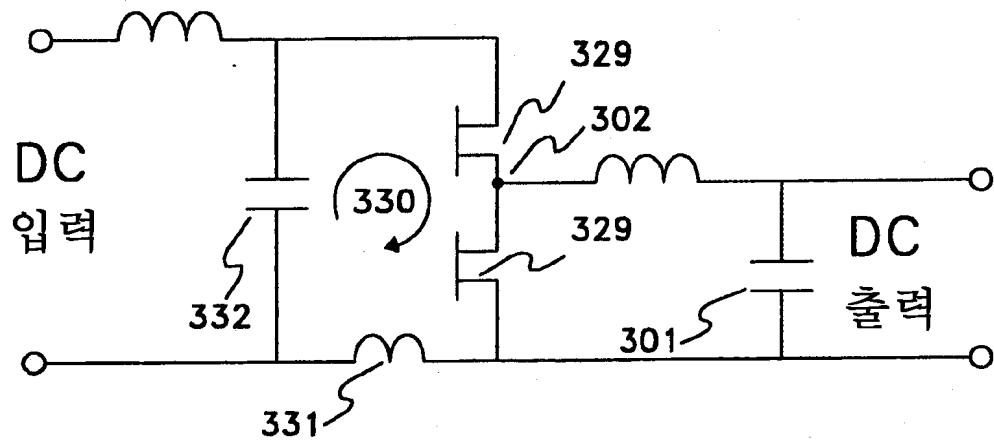

상기한 바와 같이, 벽(BUCK) 컨버터 토플로지(도3a에 도시한 바와 같은)는 현재 전원을 공급하는 마이크로 프로세서, 특히 전압 레귤레이션 모듈에 사용되고 있다. 2.5 V, 13 A가 필요하면, 300 kHz의 스위칭 주파수가 부적합하게 된다. 실제 스텝 부하 변경을 충족시키기 위해 3 mF의 출력 커패시턴스(301)가 필요하게 된다. 마이크로프로세서 전압 조건은 50 A에서 1.0 V로 내려가기 때문에, 종래기술의 토플로지는 더욱 적합하지 않게 된다. 2.5배의 전압 강하( 및 차동 전압 허용치의 부수적인 강하)와 4배의 전류의 증가에 의해, 30mF의 출력 커패시터가 필요한 스텝 응답을 유지할 필요가 있다. 그러나, 마이크로프로세서 접속부에 가깝게 이와 같은 큰 커패시터를 배치하는 것은 매우 어렵거나 불가능하다. 또한, 전압이 감소함에 따라 비용이 증가할 것이다. 다른 가능성은 주파수를 증가시키는 것이다. 도3b에 도시된 전압 파형(302)은 벽 컨버터에 있어서 일반적인 것이다. 그러나, 상기와 같은 구성에서 주파수가 증가하면, 상기 파형의 비공진 에지들은 FET 출력 커패시턴스의 정류와 같은 문제를 발생시키고, 스위칭 주파수를 약 1MHz 이상 증가시키지 못하게 한다. 적합한 전원을 제공하는 것이 매우 어려운 마이크로 프로세서와 다른 저전압 전자제품이 개발됨에 따라 이러한 상황은 급격히 심각해진다. 본 발명은, 필요하다면 더 높은 고주파와 전류를 허용한다. 또한 적어도 약 300kHz 이상, 적어도 약 500kHz 이상, 적어도 약 1MHz 이상, 적어도 약 3MHz 이상, 적어도 약 10MHz 이상, 및 적어도 약 30MHz 이상의 주파수를 허용하고, 본 발명은 약 15A 이상, 약 20A 이상, 약 50A 이상, 및 약 100A 이상의 전류를 처리하도록 구성될 수 있다.

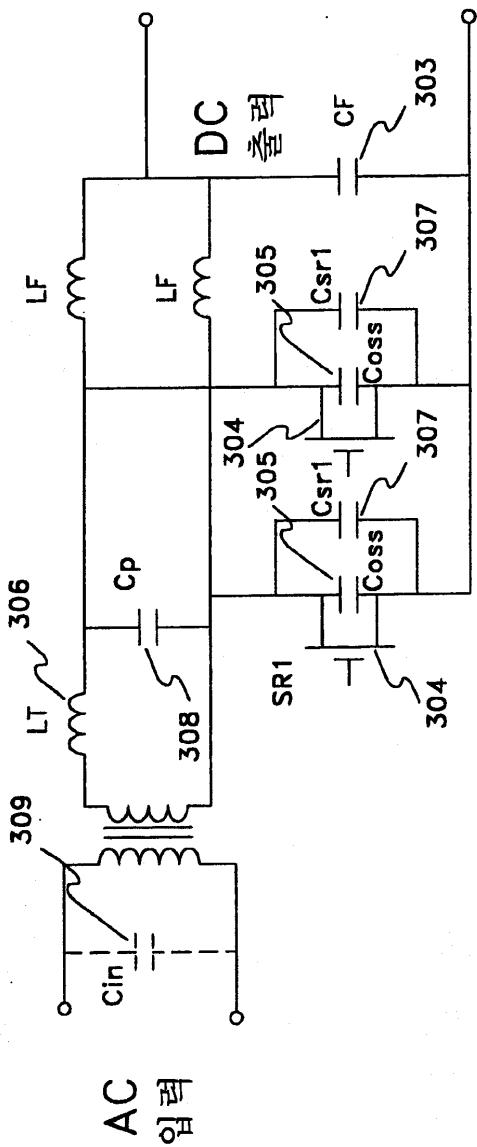

일 실시예에서, 본 발명의 일 양태는 기본적으로 DC를 DC로 변환하는 회로로부터, 변압기와 동기식 정류기를 사용하여 AC를 DC로 변환하는 회로로 바꾸는 것이다. 이 접근에서는 컨버터 입력에 분배되는 큰 전류가 제거될 수 있기 때문에 변압기가 유용하다. 따라서 대전류 2차 권선은 부하에 물리적으로 가깝게 배치될 수 있다. 이를 실현하기 위한 회로가 도3c에 도시되어 있다. 본 발명이 개시되는 것에 의해, 에너지 변환 주파수가 실제로 증가할 수 있기 때문에, 출력 커패시턴스(303)를 작은 값으로 유지하고 마이크로 프로세서 내부 접속 등의 주어진 부하에 인접하게 배치되게 할 수 있다. 사실, 보다 높은 변환 주파수를 실현할 수 있는 것에 의해 출력 커패시턴스를 실제로 감소시킬 수 있다. 1.0V, 50A가 필요한 경우에는, 필요한 부하에 따라, 본 발명의 출력 커패시턴스(303)를  $500\mu F$  또는 그 이하로 할 수 있다. 실제로, 본 발명에 의하면, 약 10mF 이하, 약 3mF 이하1, 약 1mF 이하, 약 0.5mF 이하, 및 심지어 약 0.3mF 이하인 효율적인 커패시턴스(설계된 회로에 사용하면 상당한 효과를 발생시킴)를 포함하는 네트워크를 제공하도록 설계할 수 있다.

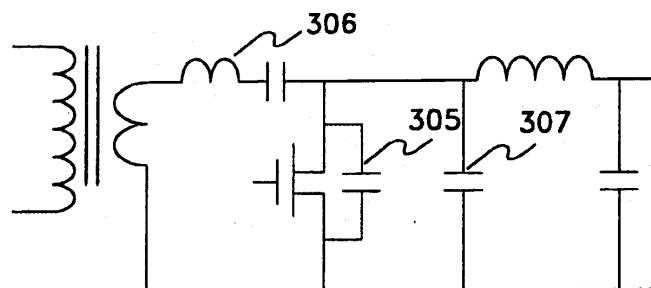

여러 요소들을 각각 또는 동시에 내장함으로써 이와 같은 효과적인 개선이 이루어질 수 있다. 본 발명의 주 목적은 주파수와 관련된 제한을 제거하는 것이다. 결과적으로 커패시터의 무리한 전압 정류를 제거하는 것이 중요할 수 있다. 사용되는 동기식 정류기(SR)(304) 장치는 드레인-소스 커패시턴스(305)가 부가된 전계 효과 트랜지스터(FET)이다. 상기 SR은 제로 전압이 걸릴 때 도통 상태로 항상 정류된다.

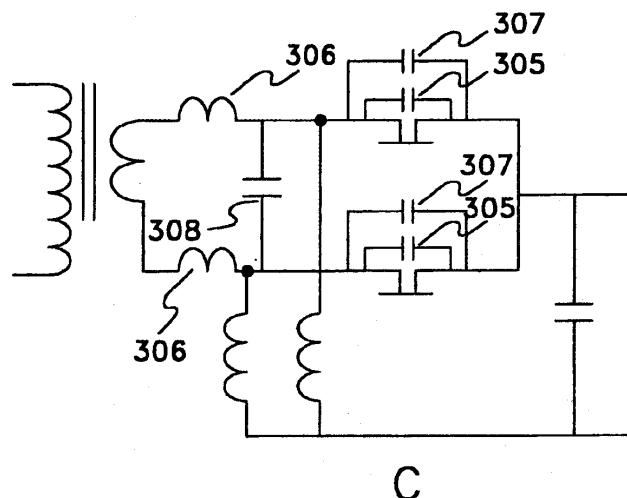

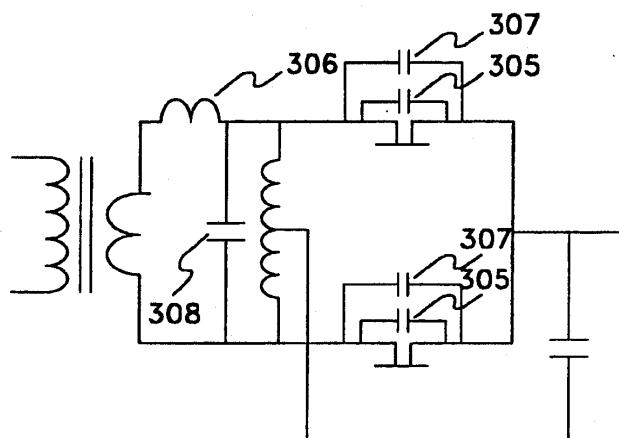

도3c는 저전압 대전류 전원의 정류부에 대한 바람직한 실시예를 나타낸다. 상기 소자 LT(306)(총 직렬 인덕턴스)는 변압기 누설 인덕턴스와 변압기와 직렬인 다른 인덕턴스의 총합으로 정의된다(1차 권선의 인덕턴스는 2차 권선의 인덕턴스의 간단한 비율이다). 소자 CT(총 병렬 커패시턴스)는 SR에 부가된 커패시턴스(305)(Coss), 각 SR의 외부 병렬 커패시턴스(307)(Csr) 및 변압기의 2차 권선과 병렬인 커패시턴스(308)(Cp)의 총합으로 정의된다.

상기 회로를 최적화하도록 고려되는 다수의 파라미터가 있다. 전원이 공급되는 부하의  $di/dt$ 가 높을 가능성이 있거나, 상기 부하 전류가 계단 함수이면 다음 파라미터들이 고려될 수 있다.

#### 동작의 기본 주파수

변압기 권수비

LT

CT

SR의 도통각(CA)

SR의 위상 지연(PD)

출력 인덕턴스 LF와 출력 커패시턴스 CF는 중요하지만 본 발명의 적절한 동작에 직접적으로 영향을 주지 않는다.

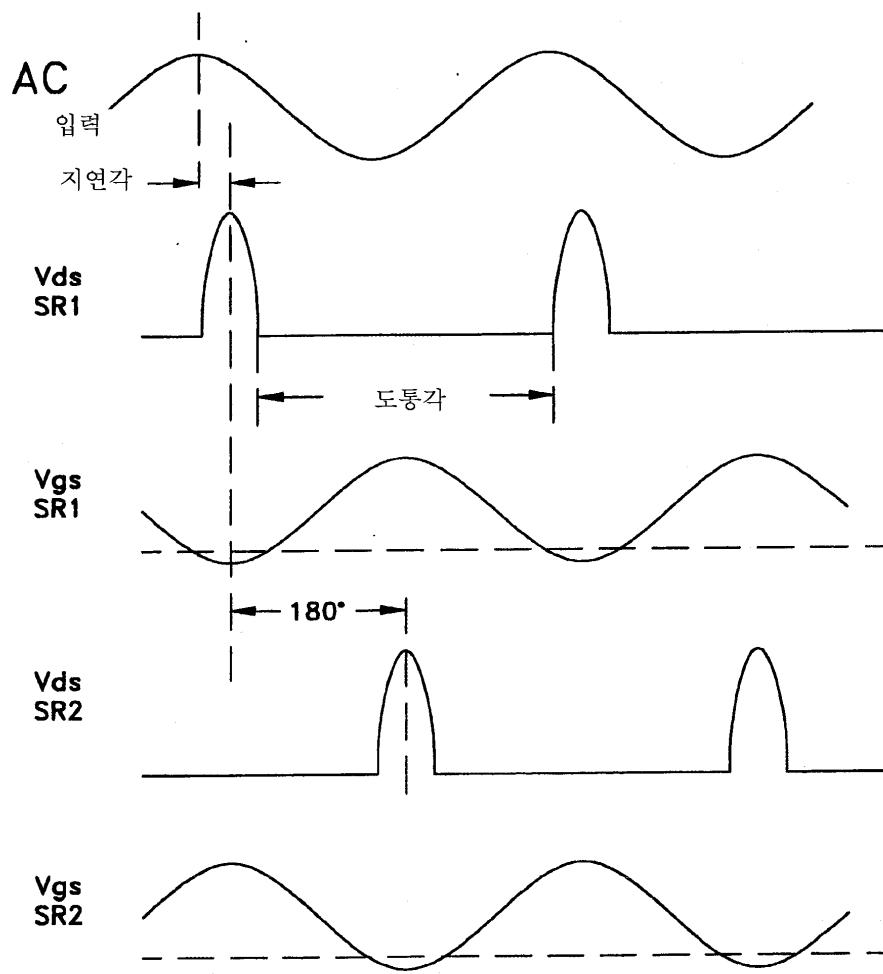

도통각과 효율성 사이의 기본적인 관계도 잠재적인 것으로 고려된다. 종래기술에서는, SR의 도통각은 변압기의 2차 권선에 단락을 막기 위해 180도(즉, SR 도통이 겹치지 않음) 이하가 되도록 주의깊게 선택된다. 주파수를 보다 낮게 가정하는

것에 의해 이와 같은 오해가 발생한다. 본 발명에 의하면, 180도 이상의 도통각은 허용될 뿐만 아니라 동작의 기본적인 이점을 제공하고 있다. 300도 이상의 범위에서의 도통각은 확실히 증명되었다. LT, CT, 위상각(PA) 및 도통각(CA)을 적절히 선택하는 것에 의해, 도3d에 도시된 SR(304)의 드레인 파형을 실현할 수 있다. 상기 조건에 의해, 출력 전압에 대한 SR의 제곱근(RMS) 전류의 비가 낮게 실현된다. 1.3:1보나 낮은 비를 실현할 수 있다.

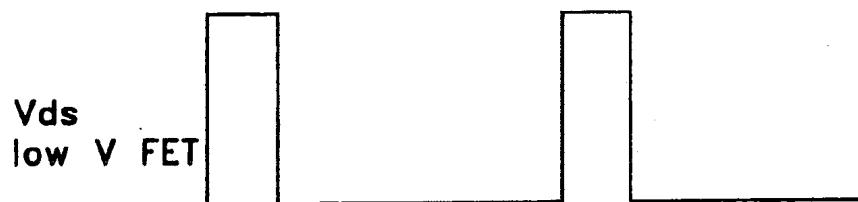

일반적인 비교와 같이, 종래 기술로부터 도3d의 파형은 도3b와 비교될 수 있다. 두 파형은 낮은 듀티 사이클 양상을 공유하지만 도3d에서는 SR의 스위칭이 제로 V에서 발생하며 이상적으로 손실이 없다.

#### 누설 인덕턴스 및 중첩 도통각:

변압기 누설 인덕턴스는 저전압, 대전류, 고주파 전원에 대한 기본 제한 요소이다. 이는 변압기와 직렬인 인덕턴스를 포함하며, 원래 변환 주파수를 제한하고 있다.

다른 기술에서는, 누설 인덕턴스는 각종 방식으로 처리되고 있다. DC-DC 변환에 대한 슈렉트, 리 및 바우만에 의한 3진의 특허가 모두 누설 인덕턴스 처리 방법을 포함하고 있기 때문에 다루어질 것이다. 슈렉트 등, 미국 특허 제4,788,634호에서, 누설 인덕턴스는 최소화되도록 조정된다. 상기 특허에는: "일방향 도통소자 및 제어 가능한 스위치 모두가 제로 전압 스위칭 천이를 갖도록, 상기 누설 인덕턴스의 크기를 공진 인덕터(이 경우에는 변압기의 1차 권선 인덕턴스)에 비해 극히 작은 값으로 제한하는 것이 바람직하다"라고 기재되어 있다. 리 등, 미국 특허 제4,785,387호 및 바우만 등 미국 특허 제4,605,999호에서, 변압기 누설 인덕턴스는 기본 주파수에서보다 약간 높은 주파수에서 공진하는 회로에 사용된다. 상기 회로의 목적은 정류기 뿐만 아니라 1차 권선 스위치에 대해 제로 전압 스위칭을 실현하는 것이다. 그러나, 본 발명은 기본 주파수에서 공진하지 않는 방식으로 누설 인덕턴스를 사용한다.

본 발명의 일 양태는 보다 큰 누설 인덕턴스에 대해서도 가능한 회로 토폴로지 및 동작 클래스이다. 이는, SR에서 높은 도통각을 선택하는 것에 의해 실현될 수 있다. 사실상, 일부 적용에 있어서 300도보다 더 높은 도통각이 유용하다는 것을 보여주고 있다. 출력 전압에 대한 요구가 감소하고 전류에 대한 요구가 증가하기 때문에, 이러한 변화에 의해 도통각이 높아지게 된다. 바람직한 조건들 중 하나가 동기식 정류기용 제로 전압 스위칭(ZVS)이면 상기 높은 도통각, 총 인덕턴스 및 총 커패시턴스의 설정은, 동시에 행해진다. 이에 의해 높은 주파수에서의 동작, 또는 높은 누설 인덕턴스에서 동작하는 주어진 주파수에서의 동작을 가능하게 한다. 고주파 동작 및/또는 높은 리크 인덕턴스 허용치의 조합이 상기 설계의 기본적인 이점이며, 마이크로프로세서 전원에 대한 요구를 충족시키기는 것이 보다 어렵게 되기 때문에 아마도 필요한 이점이 될 것이다.

총 커패시턴스에 대한 하나의 부가적인 특징 - 변압기(308)와 병렬로 또는 SR(307)와 병렬로 커패시터가 배치되는 위치의 선택은, SR을 통한 전류 파형을 변화시키지만 전압 파형에는 크게 영향을 주지 않는다. 변압기와 병렬로 배치되는 커패시터는 전류 파형을 보다 사각 파형처럼 만드는 데 비해 커패시터가 SR과 병렬로 배치되면 반 정현파이다. 이 차이는 당업자들이라면 용이하게 이해할 수 있는 것으로서 중요한 결과를 가질 수 있다.

#### SR에서의 고전압:

정류 회로 설계에서 관찰되는 일반적인 원리는, 정류 장치에 인가되는 역전압 스트레스를 최소화하는 것이다. 필터 입력의 타입에 따라, 역전압의 피크는 보통은 출력 전압보다 1.4배 또는 특수한 환경에서는 DC 출력 전압의 2배 높은 DC 출력 전압과 동일한 범위내에 있다.

높은 도통각에 의한 한가지 결과는 정류 장치에 걸리는 상당히 높은 전압이다. 예컨대 개시되어 있는 회로값들 중에, 출력 전압은 1.8V인 반면 정류 장치의 전압은 15V이다. 당업자들은 잘 이해하고 있는 바와 같이 상기 타입의 회로 성능은 여러 가지 이유로 좋지 않다. 이것이 이와 같이 유용한 회로가 지금까지 개시되지 않은 이유이다.

그러나, 비도통 상태 동안 SR에 걸리는 부수적인 고전압에 의한 높은 도통각은, 도통 상태 동안 SR을 흐르는 RMS 전류가 낮은 이점이 있고, 큰 변압기 누설 인덕턴스를 가능하게 하는 조건이 된다. 상기 회로는 저전압, 대전류 조건에 적합하다. 또한, 상기 회로는 높은 동작 주파수와 출력 커패시턴스에 저장된 낮은 에너지의 결과로서  $di/dt$ 가 높은 조건을 갖는 부하에 매우 적합하다. 상기 회로가 더 높은 전압이 되면 SR에 대한 요구가 곤란해진다. 상기 회로는 고전압을 증명하였기 때문에 SR에 대한 조건은 문제되지 않는다. 현재 제조 기술에 의해 SR 오프 상태 전압을 약 20V 이하로 억제시키는 것은 거의 이득이 없다는 것을 알 수 있다.

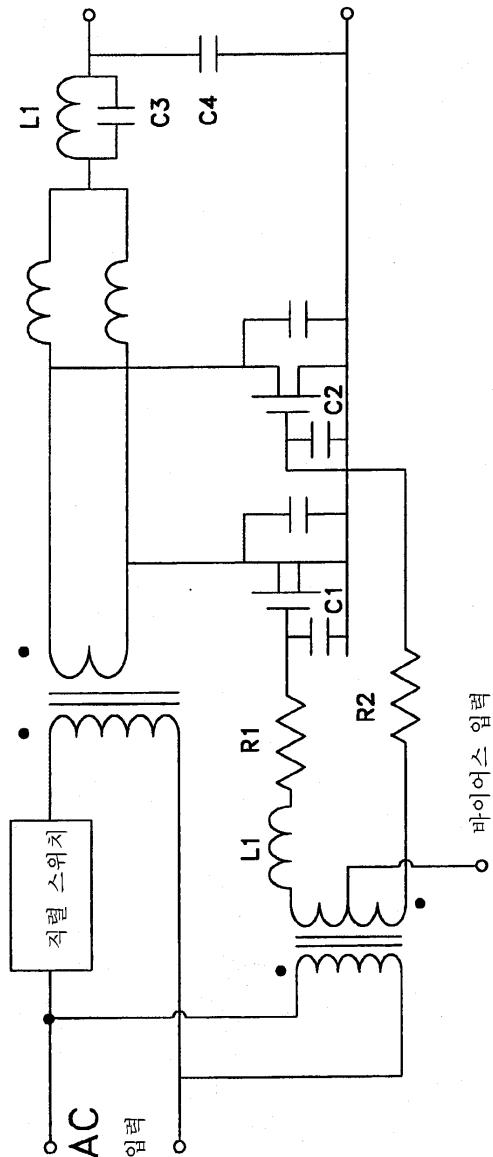

#### 케이트 구동:

도3e에 도시되어 있는 다음 회로는, AC 입력으로부터 전원을 얻고 단지 수동 소자들만을 사용하는 게이트 구동 회로이다. SR의 게이트 구동은 또한 거의 손실이 없다. 이에 의해 비용이 감소하고 성능이 향상된다. 또한 고주파 동작에 중요하다.

또한, 각종 부하 조건하에서 레귤레이션을 제공하거나 효율성을 증가시키도록 DC 또는 저주파 바이어스를 부가하는 것이 가능하다. 도3e에 BIAS INPUT으로 나타낸 점은 제어 입력에 대한 주입점의 예이다. 상기 입력에서의 전압을 변화시키면 상기 DELAY ANGLE에는 영향을 주지 않으면서 SR의 도통각으로 변화시키는 영향을 준다(도3d).

SR의 도통을 위한 정확한 위상각은 게이트 구동에 의해 결정된다. 도3d를 참조하면, 도3e의 소자 L1, R1,2, 및 C1,2와 같은 것을 사용하여 DELAY ANGLE로 참조된 각을 얻을 수 있다. 상기 인덕턴스 L1은 게이트 구동 변압기 누설 인덕턴스를 포함한다.

상기 원리를 구체화시키는 게이트 구동의 각종 변경이 있을 수 있다. 이는 게이트 구동이 DC 전원으로부터 나오고 타이밍 회로 및 스위칭 장치들을 포함하고 있는 종래 기술과 대조될 수 있다.

SR의 레귤레이션:

SR 도통각(CA)을 변화시켜 출력 전압을 제어 및/또는 레귤레이트하는 것도 가능하다. 점선으로 도시된 커페시터 Cin(309)이 삽입된 도3c에 대해 고려해 본다.

상기 제어된 출력 회로의 값들을 선택하기 위해, 우선 CA가 SR에 대해 360도 회전된 경우를 본다. 이 경우 결과가 제로 DC 출력으로 된다. Cin(309)의 임피던스는 기본 주파수에서 병렬 공진 회로를 형성하는 LT(권수비)를 제곱하여 1차 권선으로 변압됨)의 값에 맞추어져야 한다. 이상적인 조건에서 손실이 없는 병렬 공진 회로에 의해 AC 입력이 로드되는 것을 알 수 있다.

상기와 같이 충분한 부하 조건이 만족될 때까지 360도에서 아래쪽으로 CA가 연속적으로 존재한다. 적절히 선택된 회로 파라미터에 의해, 전체 레귤레이션 범위에 걸쳐 ZVS 스위칭이 유지될 수 있다. ZVS에 중요한 필요조건은 도통 시간과 AC 입력 사이의 일정한 위상 관계를 제공하는 것이다. 1차 분석에 있어서, 유일하게 필요한 제어 입력은 도3e에 도시된 것이다.

파라메트릭 레귤레이션(parametric regulation):

출력의 레귤레이션 또는 제어를 제공하는 또 다른 방법은 출력 전압을 변경하기 위해 바렉터 회로 또는 포화가능한 인덕터 등의 파라메트릭 소자들을 사용하는 것이다. 이는 주어진 소자들에 대한 감도를 최대화하는 회로를 동조시키고 결과적으로 그것을 변화시키는 것을 포함할 수 있다. 이와 같은 종류의 설계에 있어서 다른 접근은 전원 특성을 갖는 기본 전송 기능으로 시작하는 것이다. 이에 따라 하나 이상의 가변 소자들에 있어서 작은 변화에 의해서도, 출력이 일정하게 유지될 수 있다.

몇 가지 부하 조건에 있어서, 상기 제어 방법은 가장 간단하고 비용이 효율적일 수 있다. 높은 di/dt 조건을 갖지 않는 특정 부하에서 또는 필요한 전압이 매우 낮지 않다면, 파라메트릭 레귤레이션은 이상적일 수 있다.

상기 제어방법은 부하를 변경하는 응답시간이 나쁘고 입력 레귤레이션이 나쁜 단점을 갖는다. 또 다른 단점은 소자 허용치에 대해 현재 증가된 감도이다. 도3d에서는, CA가 매우 크다는 것을 알 수 있다. 일반적으로, 적정 CA는 더 낮은 출력 전압에 대해 증가한다. 파라메트릭 레귤레이션을 사용하는 경우의 결과는, 출력 전압의 증가된 감도를 실제 회로 값들로 처리하기가 매우 어렵게 될 수 있다는 것이다. 부품 감도를 처리할 수 없게 되면, 정류용 회로의 정류부를 최적화하고 임피던스가 더 높은 변압기의 1차 권선측을 레귤레이트 또는 제어하는 것이 바람직하다. 레이아웃 및 부품 값들은 1차 권선에서 보다 처리가능할 수 있다. 선형 가변 커페시터, 선형 가변 인덕터, 또는 심지어 선형 가변 저항(알 수 있는 바와 같이, 저항은 손실이 생길 수 있기 때문에 바람직한 소자가 아니다) 등의 내추럴 선형 부품들도 사용될 수 있다.

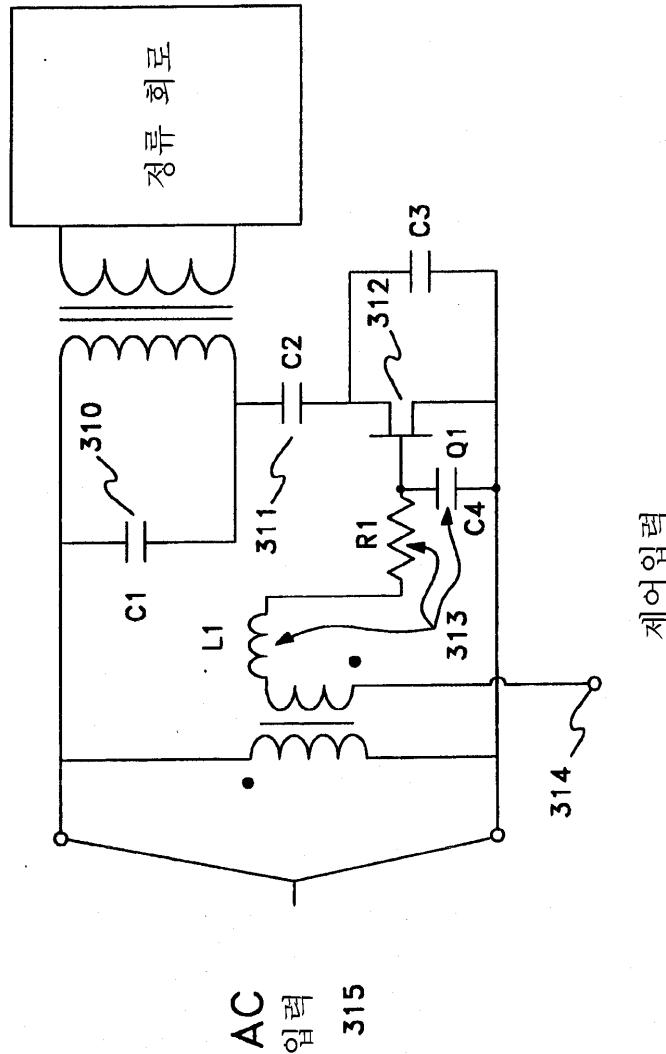

1차 권선측의 레귤레이션(싱글 엔디드 스위치(single ended switch)를 포함):

도3f는 변압기의 1차 권선측에 있는 간략화된 직렬 스위치를 나타낸다. 상기 회로 설계는 변압기 입력의 AC 전압을, DC 출력 전압을 레귤레이트하는 가능한 방법으로서 사용될 수 있다. 예컨대, C1(310)은 정류 회로의 잔류 유도성 부품들로 공진될 수 있다. C2(311)는 기본 주파수에서 저 임피던스일 수 있다. Q1(312)의 드라이브 사이클은 상기 정류 회로에 입력되는

AC 전압을 변경하도록 제어될 수 있다. 위상 지연(313)(L1,R1,C4)은, 최초 도통시 Q1(312)에 걸리는 전압이 거의 0이 되도록 선택될 수 있다. 또한, Q1의 게이트 구동은 상기한 동기식 정류기용 게이트 구동 방식과 유사하게 설정될 수 있다. AC 입력(315)은 저전압으로 변압되어 지연회로(313)를 통해 게이트에 공급되는 전원으로서 사용될 수 있다. 이와 직렬로 구동 회로가 제어입력(314)으로 될 수 있다. 상기 두 전압을 합하여 도통각을 0에서 360도까지 변화시킬 수 있다.

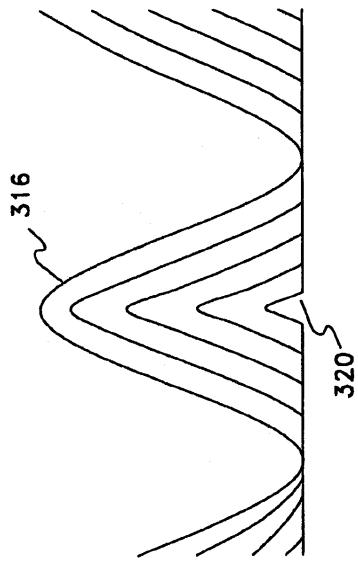

상기 도통각은 제어 입력에 의해 설정될 수 있고, 위상 관계는 AC 입력(315)으로부터 얻어질 수 있다. 적절히 선택된 회로 소자 및 지연 시간에 의해, Q1(312)에 걸리는 전압이 0일 때 Q1(312)은 도통 상태로 항상 정류될 수 있다. 따라서 정류회로의 AC 전압은 손실없는 조건을 유지하면서 거의 0에서 최대까지 변화될 수 있다. 도3g는 제어 입력의 함수로서 Q1(312)에 걸리는 전압(FET 스위치용의  $V_{ds}$ ) 파형의 집합을 나타낸다. 부호 316의 파형은 도통 시간을 단축시키는 저 바이어스에 의해 발생한다. 상기 조건은 최소 출력을 제공한다. 320으로 참조된 파형은 고 바이어스 입력에 의해 발생하고 큰 도통각에 대응하며 최대 출력을 제공한다. 모든 파라미터들이 동시에 최적화되는 것도 가능하다.

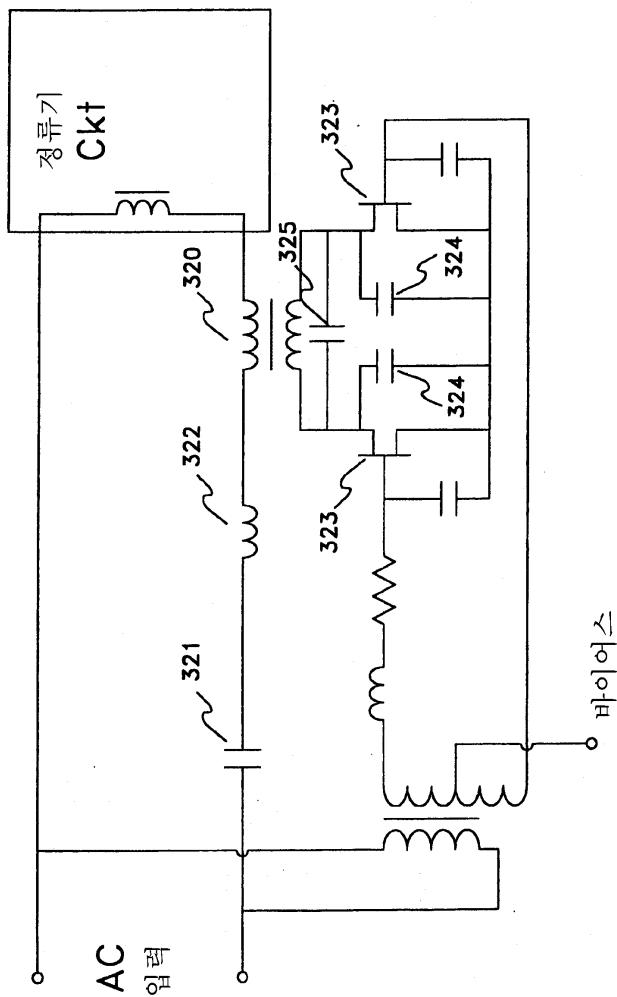

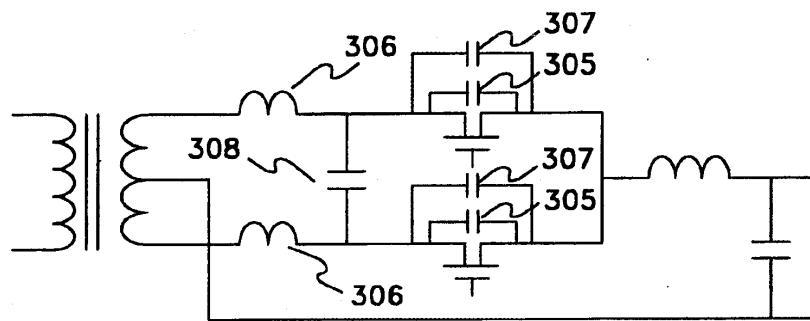

### 1차 권선측의 레귤레이션(2중 스위치 포함)

도3h 및 3l은 변압기의 1차 권선측의 레귤레이션을 제공하는 다른 구성을 나타낸다. 상기 회로는, 위상이 180도 어긋나게 동작하는 2개의 스위치(323)를 사용할 수 있다. 상기 스위치들은 커패시터(321)와 직렬 변압기(320)의 누설 인덕턴스(322) 사이의 직렬 공진에 의해 움직이도록 동작할 수 있다. 이것은 두 스위치가 모두 단혀 있을 때 발생한다. 이는 1차 인덕턴스를 중단시키고 단지 상기한 직렬 공진만을 남긴다. 상기 조건은 정류회로에 최대 AC 전압을 인가할 수 있다.

두번째 조건은 두 스위치가 완전히 열려 있을 때 발생할 수 있다. 상기 조건 동안, 커패시터(324)(스위치 보조 커패시턴스를 포함하고 있음)는 직렬 스위치 변압기와 직렬일 수 있다. 또한 변압기(325) 양단에 걸려 있는 커패시터 또는 그 두 개의 조합을 사용하는 것도 가능하다. 상기 총 커패시턴스는 변압기의 자화 인덕턴스와 동조될 수 있다. 이는 주 변압기의 1차 권선과 직렬로 병렬 공진 회로를 생성할 수 있고, 정류회로에 최소 AC 전압을 인가할 수 있다.

### 내추럴 레귤레이션:

총 인덕턴스, 총 커패시턴스 및 출력 필터 인덕턴스의 임의의 값이 정확하게 선택되면 새로운 현상이 발생할 수 있다. DC 출력 전압이 비교적 부하 전류에 무관하게 남아있을 수 있다. 이는 가변 소자들이나 피드백 없이 발생할 수 있다.

예:

모든 회로의 파라메트릭 값들을 선택하는 것은 긴 작업일 수 있다. 다음 예는 1,8 V에서 동작하고 20 A가 필요한 마이크로프로세서에 전원을 공급하기 위해 최적화된 일반적인 목적의 정류기이다. 도3c의 회로를 사용하여 다음 파라메트릭 값을 사용할 수 있다.

$$\text{주파수} = 3.3\text{MHz}$$

$$\text{권수비} = 5:1$$

$$\text{입력 전압} = 30 \text{ VAC}$$

$$LT = 30\text{nH}$$

$$CT = 10\text{nF}$$

$$Cin = 2 \text{ nF}$$

$$L1 \& L2 = 100 \text{ nF}$$

$$Co = 500\mu\text{F}$$

$$SR1 \& SR2 = 3 \text{ ea. FDS6880}$$

$$\text{도통각} = 266\text{도}$$

지연각 = 24도

도3e는 SR 게이트 구동의 일 실시예를 나타내며, AC 입력으로부터 나오는 정현파 신호와 제어 신호의 합을 포함하고 있다. 또한, AC 입력으로부터 나오는 신호는 고효율을 위해 최적 지연을 가질 수 있다. 상기 회로는 게이트 변압기 누설 인덕턴스 및 AC 입력으로부터 고조파를 필터링하는 게이트 커패시턴스를 이용하여 정확한 AC 전압을 생성할 수 있다. 또한 상기 회로는 R1,2, C1,2의 조합(부가의 게이트/소스 커패시턴스를 포함함), 및 인덕터 L1을 사용하여 지연을 생성하는 것을 보여준다.

출력 트랩:

도5에도 중요한 필터 소자가 도시되어 있다. C3 및 L1은 기본 주파수의 2배에서 병렬 회로 공진을 형성할 수 있다. 상기 병렬 트랩은 다음과 같은 이점을 제공할 수 있다:

- 1) 가장 큰 리플 성분만을 목표로 한다

- 2) 거의 에너지를 저장하지 않고 고속 루프 제어를 행한다

- 3) 출력 커패시터와의 접속부의 AC 전류 성분을 급격하게 감소시킨다.

상기 회로가 마이크로 프로세서에 전원을 공급하면, 상기 C4는 마이크로 프로세서에 인덕턴스를 최소화하기 위해 정밀하게 배치될 수 있다. 이 경우, 병렬 트랩은 나머지 회로에서 Cout까지의 접속부에 있어서의 "핫 리드(hot leads)"를 최소화 할 수 있다.

토폴로지 변경:

도3ia,3ib,3ic,3id는 개시되어 있는 본 발명을 구현하기 위해 사용될 수 있는 각종 토폴로지를 나타낸다.

총 인덕턴스 및 총 커패시턴스의 위치가 각각 도시되어 있다. 도ia는 싱글 엔디드 버전을 나타내고 있다. 이는 저비용을 위한 바람직한 토폴로지일 수 있다. 도3ib는 중앙 텁을 갖는 변압기의 영향을 나타내고 있다. 상기 회로는 유용할 수 있지만 변압기의 2차 권선을 충분히 이용하지 않을 수 있다. 또한, 저전압을 위해, 2차 권선이 중앙 텁을 보다 구현하기 어렵게 할 수 있는 단지 1회의 권수를 갖도록 할 필요가 있다. 도3ic는 SR 및 필터 인덕터의 반전을 도시하고 있다. 상기 회로는 이미 설명된 것과 거의 동일할 수 있다. 또한, 게이트 구동은 구동 회로를 보다 복잡하게 만드는 공통 소스점(도시하지 않음)과 관계가 없을 수 있다. 도3id는 중앙에 텁이 있는 2차 권선 대신에 중앙에 텁이 있는 코일을 도시하고 있다. 자기의 실현에 의해 상기 회로가 주목을 받을 수 있다. 이를 개시하는 목적을 잘 적용하고 있다.

상기 예는 가능한 많은 설계들 중 일부만을 나타내고 있다. 상기 변경들로부터, 개시되어 있는 아이디어들을 구체화하고 있는 다른 회로들이 설계될 수 있다는 것을 자명하다.

3차 고조파 트랩:

상기한 회로 설계들로부터 알 수 있는 바와 같이, 짹수 고조파 또는 홀수 고조파가 존재하거나 상이한 방향에 영향을 미칠 수 있다. 짹수 고조파(즉, 2차, 4차 등)는 전방 방향에 영향을 미칠 수 있고, 홀수 고조파(즉, 3차, 5차)는 후방 방향에 영향을 미칠 수 있다. 각각은 어드레스될 수 있다. 물론, 이와 같은 고조파(즉, 2차 또는 3차) 중 최고차가 최초의 관심이 될 수 있다. 상기 설명에서, 전방과 관계있는 홀수차 고조파(즉, 2차 고조파)도 역시 어드레스된다. 후방과 관계있는 짹수차 고조파(즉, 3차 고조파)도 역시 어드레스된다. 3차 고조파에 있어서, 3차 고조파에 동조된 인덕터와 커패시터의 직렬 접속은 주 VRM 변압기의 1차 권선과 병렬로 배치될 수 있다. 개시되어 있는 바람직한 실시예는 입력 전압을 실제 3차 고조파의 정보로 이용할 수 있다. 회로의 입력에 트랩을 설치함으로써 고조파의 정보는 트랩을 흐를 수 있고 회로에 전원을 공급하는 배전상에 나타나지 않을 수 있다. 당업자들은 용이하게 실행할 수 있는 바와 같이, 간단한 동조를 행함으로써 다른 고조파들을 어드레스할 수 있다.

보다 중요하게, 정류기의 효율은 3차 고조파 트랩을 부가하여 향상될 수 있다. 출력 회로는 도통각이 큰 SR과 특히 비선형이다(도3d 참조).

상기 회로로부터의 DC 출력 전압(도3d 및 도3j)은 SR에 결리는 전압의 합(인덕터에 결리는 평균 전압은 0이다)과 동일할 수 있다. 상기 파형의 왜곡은 DC 출력 전압을 감소시켜 결과적으로 효율을 감소시킨다. 3차 고조파 트랩은 SR 전압 파형의 내추럴 피크를 유지할 수 있다.

3차 고조파 트랩의 또 다른 가능한 이점은 다수의 SR 회로들이 공통 AC 소스로부터 입력되는 시스템의 안정성이 증가된다는 것이다. 국부의 3차 고조파 트랩은, SR 회로들이 배전 경로를 따라 흐르는 3차 고조파 전류에 의해 상호작용하는 것을 방지할 수 있다.

즉, 3차 고조파 트랩이 없는 경우 SR 비도통 시간시 음의 임피던스가 존재할 수 있다. 이는 전체적인 시스템 불안정에 있어서 명백해질 수 있다. 각각의 SR 회로의 입력에서 3차 고조파 트랩의 존재는 고차원 전류 요구를 국소적으로 만족시킬 수 있으며 시스템 안정을 가져올 수 있다.

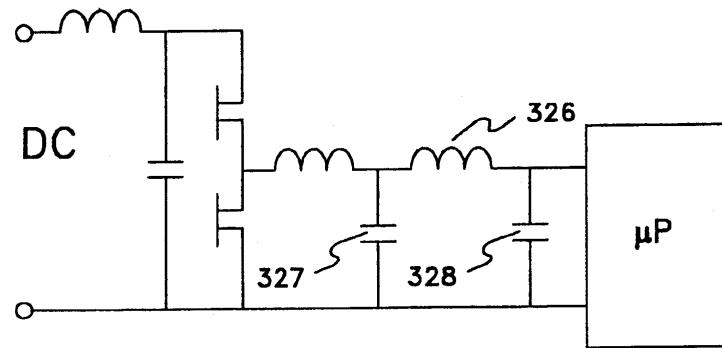

#### 원격 전원:

마이크로프로세서와 같은 장치는 저전압, 고전류를 요구할 수 있으며, 높은 전류 변화율( $di/dt$ ) 요구사항을 나타낸다. 도3j의 회로에서, 존재할 수 있는 1가지 문제는 상호 인덕턴스(326)에 의해 야기되는 전류 변화율( $di/dt$ )이다. 흔히 사용되는 상기 회로에서, 바이패스 커패시터(328)(별렬의 많은 소규모 커패시터로 구성될 수 있음)는 마이크로프로세서 전원 편 근처에 위치될 수 있다. 흔히 벌크 커패시터(327)로 호칭되는 보다 큰 커패시터는 짧은 거리를 두고 위치될 수 있다. 커패시터(327,328)간의 짧은 거리는 인덕터(326)를 형성할 수 있다. 상기 인덕터(326)는 마이크로프로세서가 전원으로부터 인출할 수 있는 최대 전류 변화율( $di/dt$ )을 제한 할 수 있다. 이는 바이패스 커패시터가 작거나(이는 흔한 경우이다) 또는 기본적인 전원 변환 주파수가 너무 작은(이 또한 흔한 경우이다) 경우 특히 옳은 진술일 수 있다. 상기 바이패스 커패시터(328)는 요구되는 전압으로 충전된 상태로 유지될 수 없다. 전원 공급 커패시터(327)가 이상적이거나 또는 커패시터(327)가 이상적인 전압원으로 대체되는 경우에도, 전류 변화율( $di/dt$ ) 극한은 상호 인덕턴스(326)의 결과로서 존재할 수 있다.

본 발명의 회로에서, 상기 문제는 극복될 수 있다. 도3c를 참조하면, 상기 방법 및 회로에 의해 전원 변환 주파수는 마이크로프로세서 전원 편에 인접하여 위치될 수 있는 마이크로프로세서 바이패스 커패시터로서 사용될 수 있을 정도로 출력 커패시턴스가 충분히 작아질 수 있는 지점까지 증가될 수 있다; 따라서 상기 출력은 실질적으로 비용량형이 될 수 있다. 따라서, 특정 부품용 DC 전원전압은 부품 자체와는 전기적으로 원격인 상태로 배치될 수 있다. 이러한 배치로서 관련된 특정 부품에 바로 인접한 VRM을 제공해야 하는 필요성을 회피할 수 있다. 중요하게도, 본 발명에 있어서 DC전압은 이제 부품의 능동부(마이크로프로세서 자체 등)로부터 약 1/2인치보다 큰 거리에서 공급될 수 있다. 상기 부품의 능동부(즉, 배선 또는 커넥터 등과 같이 전원을 단순히 전송하기만 하지 않고 일부 소정의 기능을 달성하기 위해 전원을 소모하는 부위)를 고려함으로써, 원격으로 배치되는 것으로 인한 진정한 전기적 효과는 충분히 이해될 수 있다. 상기 설계에 의해 훨씬 먼 거리에 전원을 배치시킬 수 있다. 이는 능동부로부터 약 1/2인치보다 큰 거리를 포함할 뿐만 아니라 능동부로부터 약 1인치보다 큰 거리 및 심지어는 능동부로부터 약 2인치보다 큰 거리를 포함할 수 있다.

#### 노이즈 없는 전원:

전압이 강하하고, 전류가 증가하며, 전류 변화율( $di/dt$ ) 조건이 증가하는 전원 공급장치 산업분야에서 직면하는 문제점들 중 하나는 노이즈이다. 도3a의 회로는 3가지 원인에 의한 노이즈이다.

우선, 스위칭 FET(329)는 가파른 전압 파면으로 강제적으로 정류될 수 있다. 이는 노이즈를 주변 구성으로 유도하고 방출시킬 수 있다. 도3b의 전압 파형을 도3d의 전압 파형과 비교하면 그 차이를 알 수 있다.

둘째, 도3a에 도시된 입력 회로는 전류를 접지 경로로 도입할 수 있다. FET(329)가 스위칭될 때, 입력 커패시터(332), 상호 인덕턴스(331) 및 FET(329)를 통해 큰 전류가 루프(330)를 통해 흐를 수 있다. 상기 루프(330) 주위의 전류 변화율( $di/dt$ )은 출력 전압에 가해질 수 있는 전압이 인덕터(331)를 통해 형성될 수 있도록 한다.

셋째, 도3a에 도시된 바와 같은 회로의 출력은 DC 출력 전압이 감소될 때 본질적으로 노이즈가 발생될 수 있다. DC 출력 전압은 도3b에 도시된 점2에서의 전압의 평균치이다. 전압 레귤레이션 방법은 때때로 더빙된 펄스 폭 변조이다. 저출력 전압에 대해 펄스 폭은 제어하기 어려운 지점까지 낮아진다. 이는 펄스 폭의 변동이 총 펄스 폭의 대부분을 차지하기 때문이다. 이로 인해 출력전압의 떨림 현상, 즉 노이즈가 발생한다.

여기에 개시되고 있는 회로는 제로 전압 스위칭(ZVS)을 사용할 수 있으며 정류회로에서 매끄러운 전압 파형을 가질 수 있다. 도3b(종래기술)에 대한 전압 파형을 도3d와 비교해 보자. 본 발명의 파형은 노이즈가 적어짐이 명백하다. 둘째로, 바람직한 일 실시예에서, 레귤레이션은 주로 변압기에서 발생할 수 있다. 상기 회로는 또한 ZVS이며 DC 출력 전압으로부터 분리된다. 상기 복합적인 요인들에 의해 본 접근방법은 차세대 저전압 장치에 훨씬 더 적합할 수 있다.

추가적인 예:

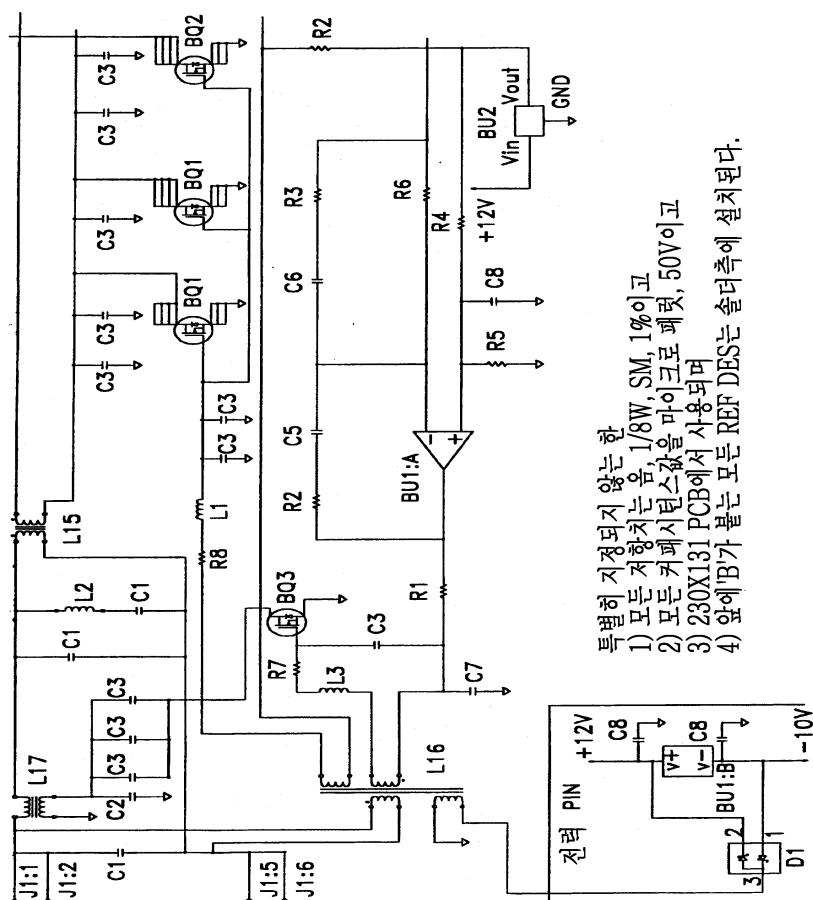

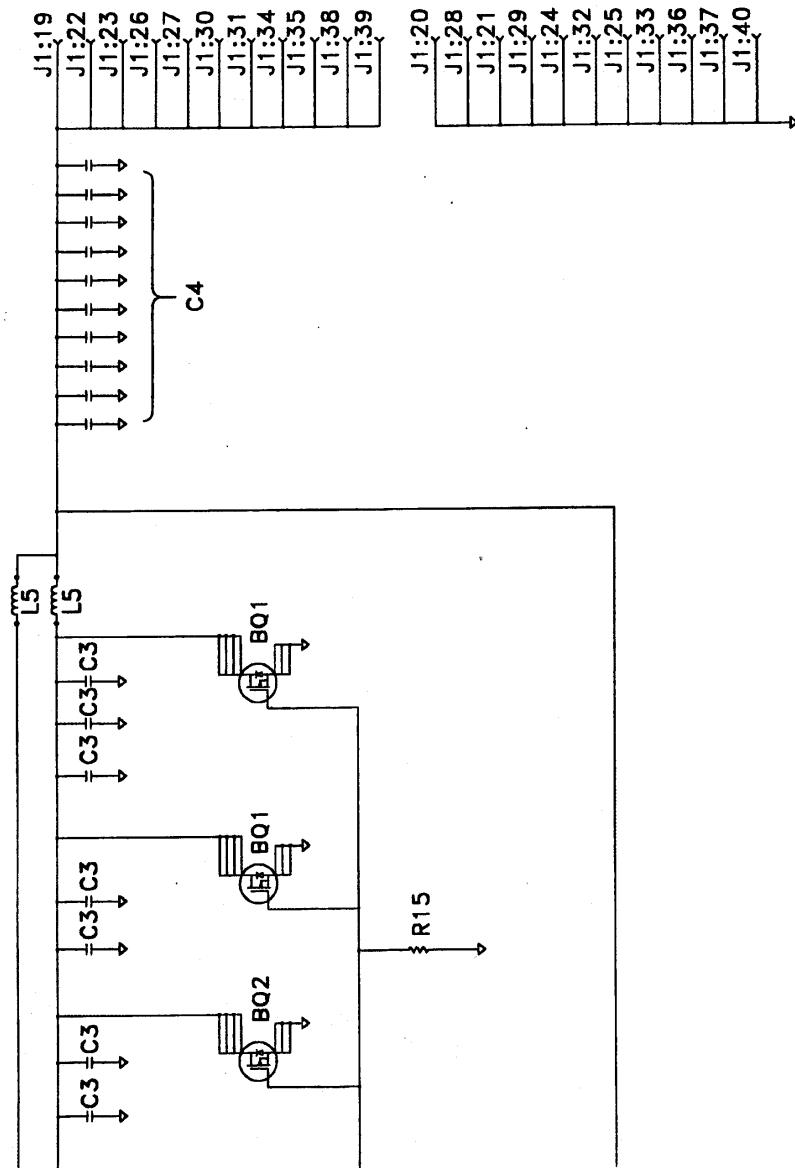

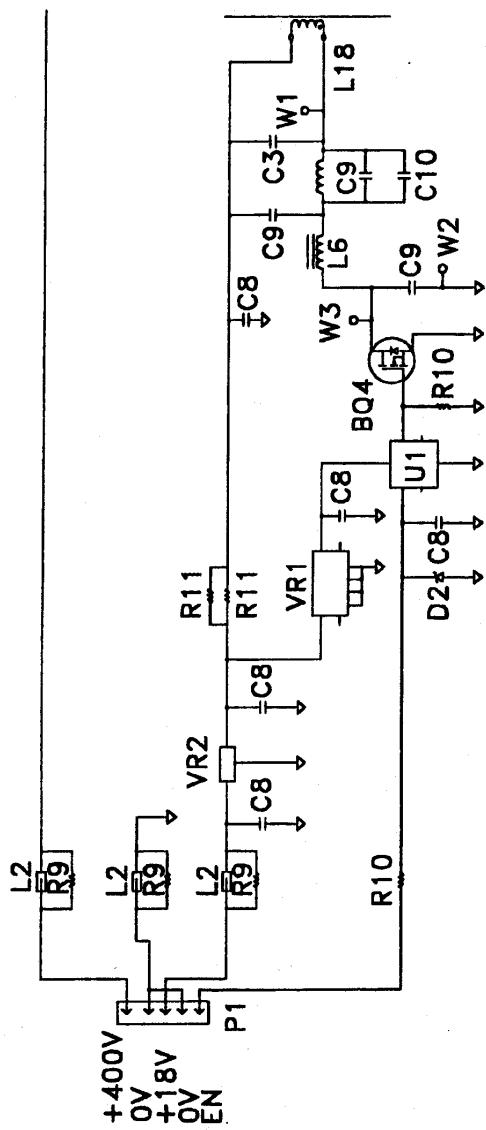

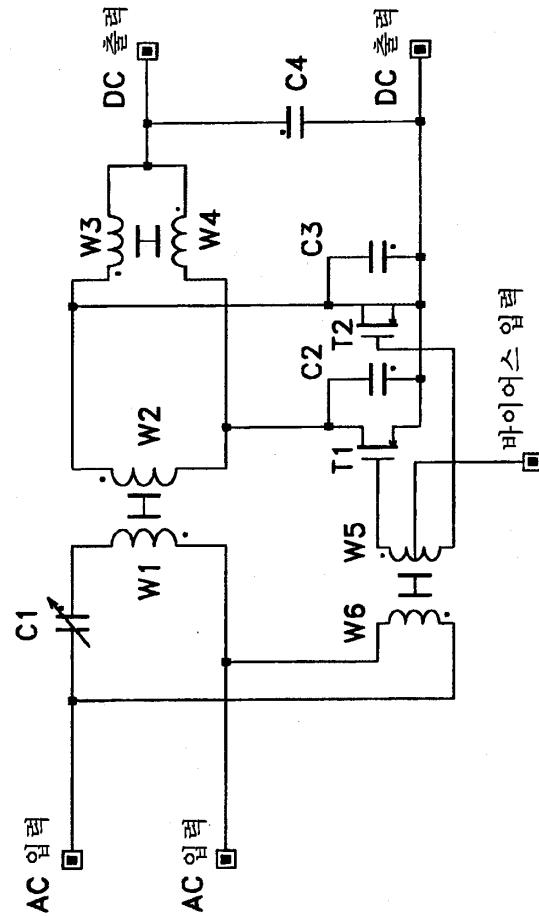

도3k 및 3l은 정류부, 게이트 드라이브, 자체 유도 DC전원과 함께 있는 직렬 스위치(들) 및 상기 조정용 직렬 스위치에 대한 출력으로부터의 피드백을 포함할 수 있는 완전한 AC-DC 전원 변환기에 대한 구성도를 도시한다. 이들 구성도는 개시된 많은 것을 구현할 수 있으며 높은 전류 변화율( $di/dt$ )을 요구하는 부하에 적합한 완벽하게 동작하는 1.8볼트, 20암페어 DC전원을 도시한다. 이들은 3.39 MHz주파수의 30볼트 RMS에서 AC입력 버스로부터 동작할 수 있다. 끝으로, 도3m은 바람직한 일 실시예에서 구성될 수 있는 "실버 박스(silver box)"의 다소 중요한 전체부의 전위 구도를 도시한다.

1차측(가변 커패시터와 병행함)에서의 레귤레이션:

변압기의 1차측에서의 직렬 스위치와 커패시터간의 차이는 커패시터가 손실이 없는 소자를 제공할 수 있다는 점이다. 또한 상기 커패시터는 선형 소자가 될 수 있다. 도3n에 도시된 실시예를 참조하면, 가변 커패시터(C1)는 주변압기의 1차 AC 에너지원과 1차 권선간의 위상차를 발생시킬 수 있다. 상기 1차측 레귤레이터의 구성에서 레귤레이션 메카니즘은 단일 및 2중 스위치에 대해 전술한 것과는 다르다. 레귤레이션 과정에는 자화 인덕턴스의 공명이 관련되지 않는다. 상기 토플로지에 대한 레귤레이션의 주 요소들은 게이트 구동 위상각 및 SR입력 임피던스와 직렬 커패시터 임피던스의 결합을 포함할 수 있다. 직렬 커패시터 값, 변압기(들)의 누설 인덕턴스 및 상기 SR의 원래 또는 보조 커패시턴스들의 특정 조합은 다음과 같은 많은 장점들을 제공할 수 있다:

- 1) 상기 회로는 변압기의 자화 인덕턴스에 상대적으로 민감하지 않을 수 있다(예컨대, 변압기에 사용되는 물질의 투자율의 안정성은 매우 부적절할 수 있다);

- 2) 상기 SR의 게이트 드라이브에 대한 위상 지연 회로는 더 이상 요구되지 않는다(예컨대, 도3e에 도시된 소자(L1,R1,R2,C1,C2)들은 배제될 수 있다);

- 3) 가변 부하 상황에서, 가변 부하 조건(예컨대, 출력 전류 변화)하에서 상기 SR 게이트 구동 전압은 소정의 부하 상태에 가장 효율적인 수치로 자동적으로 조정될 수 있다. 예컨대, 상기 회로의 실제적인 구현 중 하나에서 10% 전류부하에서의 효율은 전체 부하에서 보다 단지 15% 작다;

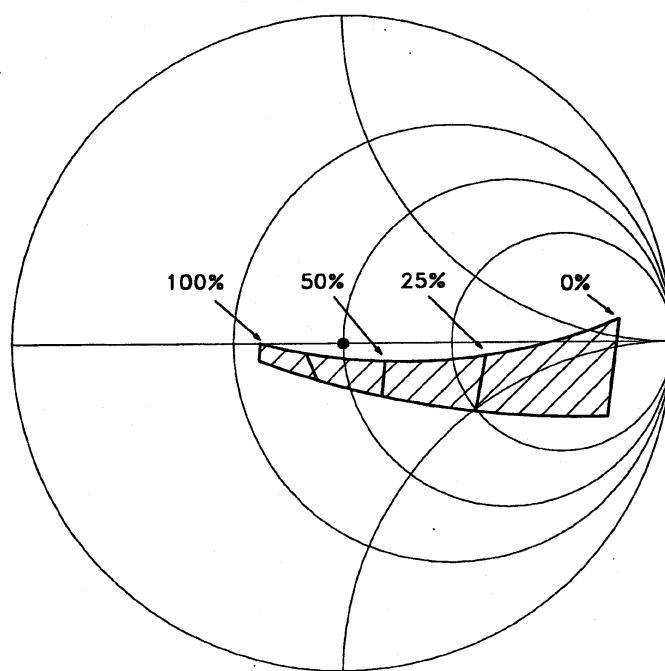

- 4) 회로의 리액티브 부분은 다른 부하상태하에서 일정해질 수 있으며 회로의 입력에 평행 인덕터를 부가함으로써 0(직렬 등가 R-X 회로)으로 될 수 있다. 즉, 회로의 입력 임피던스는 전 범위의 부하상태에 대해 리액티브 성분이 거의 없는 상태를 유지할 수 있다. 이는 다양한 부하 조건에 대해 도3o에 도시된다. 상기 특징은 대부분의 AC 발생기가 실질적으로 저항성인 부하에서만 효율적으로 동작할 수 있으므로 1차 에너지원으로서 중요하다. 상기 특징은 1차 전원용으로 보다 덜 복잡한 AC발생기를 사용할 수 있도록 해준다;

- 5) 내추럴 레귤레이션(natural regulation) 현상이 나타날 수 있다. 이는 직렬 커패시터가 전범위의 부하 레귤레이션을 달성하는데 요구되는 범위의 제한을 가져온다. 예컨대, 1실시예에서, 필요한 직렬 커패시터 값의 범위는 단지 주 값의 ±25%이다. 상기 목적을 달성하기 위해 간단한 바랙터(varactor) 소자가 사용될 수 있다.

1차권선측에서의 레귤레이션(가변 커패시터와 등가인 스위치와 병행함):

요구되는 커패시턴스의 제한된 범위의 결과로 ZVS 스위치는 변압기의 1차 권선측에 등가인 아날로그로서 사용될 수 있다. 스위치에 해당하는 일 실시예의 구성은 도3h에 대해 전술한 것과 유사할 수 있다. 상기 회로는 도3l로부터 알 수 있는 바와 같이 180도의 위상차로 동작할 수 있는 2개의 스위치를 사용할 수 있다. 상기 회로는 변압기에 있어서 SR과 전기적으로 고립될 수 있다. 안정한 누설 인덕턴스를 가질 필요가 있는 많은 경우를 제외하고는 변압기에 특별히 요구되는 것은 없다. 상기 누설 인덕턴스 값은 또한 회로 설계시 고려될 수 있으며 필요한 경우 보상될 수 있다. 자화 인덕턴스와 누설 인덕턴스 어느 것도 공명회로의 일부가 될 필요는 없다. 또한 변압기에 대한 철심 투자율의 안정성에 특별한 요구사항도 없다. 적절히 선택된 회로 파라미터들로서 선형 가변 커패시터에 대한 ZVS 스위칭 및 등가물은 또한 전체 레귤레이션 범위

에 걸쳐 유지될 수 있다. 유효 커페시턴스 값의 제어는 FET 게이트에 대한 콘트롤 DC바이어스 전압에 의해 설정될 수 있다. 전술한 직렬 스위치 실시예와는 달리, 절연 변압기 양단의 파형은 전체 레귤레이션 범위에 걸쳐 실질적으로 정현파가 될 수 있으며 그 진폭은 다른 부하 조건하에서만 변할 수 있다.

#### 출력 변압기:

본 발명의 또 다른 잠재적으로 독립적인 특징은 도3n에 도시된다. 이는 SR용 출력 필터 소자에 대한 다른 옵션을 도시한다. 도3c에 도시된 Lf와 같은 2개의 출력 인덕터 대신, 1:1 비율의 1개 변압기만이 사용될 수 있다. 보다 일반적으로, 출력 변압기는 단지 일정 방식으로 결합되는 2개의 출력 인덕턴스(도3n에서 W3 및 W4)가 될 수 있다. 자기 결합(magnetic coupling) 또는 변압기를 사용함으로써, 다음과 같은 장점들이 실현될 수 있다:

- 1) 2개 대신 1개의 자기 요소만이 사용될 수 있다;

- 2) 자기 소자를 통한 기본 주파수 AC전류는 갑자기 감소될 수 있으며, 또한 발산되는 AC자계를 감소시킨다;

- 3) 변압기의 누설 인덕턴스는 SR의 출력에 대한 필터링 소자로서 사용될 수 있다. 또한, 제1 접근방법에서의 누설 인덕턴스는 철심의 투자율에 의존하지 않을 수 있으며 따라서 자화 물질 안정성에 대한 필수적인 요구사항은 없다;

- 4) 2개의 반쪽 SR로부터의 출력 DC전류는 변압기를 통해 역방향으로 흐를 수 있으며 서로 상쇄되어 변압기 철심에서의 결과적인 DC자계는 거의 0이 될 수 있다. 그 결과 철심에서의 자계 포화는 있을 수 없으며 소량의 자화 물질이 폐로 구성(토로이드)으로 사용될 수 있다.

본 특허에 포함된 논의는 기본적인 설명으로 제공되는 것이다. 독자는 구체적인 논의가 가능한 모든 실시예를 명시적으로 설명할 수는 없으며, 따라서 많은 대안들이 내재함을 알아야 한다. 또한 본 발명의 일반적인 특징을 충분히 설명할 수도 없으며 각각의 특징 또는 소자가 보다 광범위한 기능 또는 많은 다른 또는 등가의 소자들을 실제로 어떻게 나타내는지를 명시적으로 나타낼 수는 없다. 본 발명의 본질에서 벗어남이 없이 많은 변경이 행해질 수 있다. 이러한 모든 변경은 본 명세서에 내재적으로 포함된다. 본 발명이 장치 중심의 용어로 기술되는 곳에서, 상기 장치 각각의 소자는 일 기능을 함축적으로 행한다. 장치 청구항들은 기술된 많은 실시예들에 포함되지만, 최초의 방법 청구항만이 제공된다. 제시된 장치 청구항을 뒤따르는 추가적인 방법 청구항들뿐만 아니라 본 발명 및 각각의 소자가 행하는 다양한 기능을 제시하는 부가적인 방법 및/또는 장치가 포함될 수 있다. 제법에 의한 물건 청구항 등 또한 상기 시스템을 통해 완성된 임의의 결과에 부가될 수 있다. 설명, 용어 또는 제시된 구체적인 청구항 어느 것도 본 특허 명세서의 범위 또는 궁극적으로 가능한 적용범위를 제한하지 않음을 이해하는 것이 중요하다. 기타 전자 부품뿐만 아니라 컴퓨터 시스템에 대한 적용범위가 제시될 수 있으며 최초로 제시된 것 또는 개시된 명칭에 관계없이 본 출원에 의해 포함되는 것으로 이해되어야 한다. 이 모든 것은 방법 청구항에 대해서도 특히 주목되어야 한다. 장치에 관한 청구항이 매우 상세히 포함되었지만, 절차상의 편의를 위해 방법에 관한 최초의 청구항만이 포함되었다. 당연히, 장치에 중점을 둔 상세한 설명과 청구항은 방법 및 장치 청구항 모두의 전범위를 지원하기에 충분한 것으로 이해되어야 한다. 부가적인 방법 청구항들은 전술한 세부사항들을 명시적으로 청구범위에 기재하기에 적합할 때 추후에 부가될 수 있다. 따라서, 본 명세서는 방법 청구항의 모든 범위를 포함하는 것으로 해석되어야 하며, 장치 관련사항에 제시된 것들과 유사한 청구항 및 종속 청구항을 포함하지만 이에 한정되지는 않는다. 또한 개시되었지만 청구항에 기재되지 않은 실시예들에 대한 다른 청구항들 또한 부가될 수 있다.

또한, 여기에 기술된 원리들을 사용하면 다양한 구성을 형성할 수 있으며, 전술한 바와 같이, 다양한 설계 변경이 가능하다. 또한, 본 발명 및 청구항들의 각 구성요소는 다양한 방식으로 완성되거나 독립적으로 제공될 수 있다. 본 명세서는 각각의 상기 변경 및 임의 또는 모든 구성요소 또는 응용들의 다양한 조합 및 순열을 포함하는 것으로 이해되어야 한다. 특히, 본 명세서가 발명의 구성요소들을 언급할 때 각 구성요소의 용어는 그 기능 또는 결과가 동일하기만 하면 등가의 장치 용어 또는 방법 용어로 표현될 수 있다. 그러한 등가의, 광범위한 또는 보다 일반적인 용어는 각각의 구성요소 또는 작용에 관한 서술에 포함되는 것으로 이해되어야 한다. 상기 용어는 본 발명이 지향하는 내재적으로 광범위한 적용범위를 명백히 하기 위해 요구되는 경우 대체될 수 있다. 일례로서, 모든 작용은 그 작용을 받아들이는 수단으로서 또는 그 작용을 일으키는 구성요소로서 표현될 수 있음을 이해하여야 한다. 마찬가지로, 개시된 각각의 물리적인 구성요소는 그 물리적인 구성요소가 이용하는 작용의 개시를 포함하는 것으로 이해되어야 한다. 예컨대, "스위치"의 개시는 명시적으로 표현되었는지의 여부를 불문하고 "스위칭" 작용의 개시를 포함하는 것으로 이해되어야 하며, 역으로 "스위칭"의 작용만 개시되어 있다면, 그러한 개시는 "스위치" 또는 "스위칭 수단"의 개시를 포함하는 것으로 이해되어야 한다. 이러한 변경 및 대체 용어들은 그 기본적인 개념 및 이해가 본질적이고 다양한 분야에서 다양한 방식으로 적용될 수 있으므로 본 발명에 특히 적합한 기술로서 명시적으로 포함되는 것으로 이해되어야 한다.

또한, 출원서로 채워진 임의의 참조문헌 목록에 제시된 모든 참조문헌뿐만 아니라 본 특허를 위해 출원서에 언급된 참조문헌들은 이에 참조문헌으로서 합체되지만, 이러한 진술이 출원인에 의해 행해진 것으로 명시적으로 고려되지 않는 한도에 있어서 상기 진술은 본 발명의 특허와는 합치되지 않는 것으로 고려될 수 있다.

끝으로, 문맥상 달리 해석되지 않는 한, "포함한다(comprise)"("comprises" 또는 "comprising"과 같이 변형될 수 있음)라는 용어는 언급된 구성요소 또는 단계, 또는 구성요소들 또는 단계들의 그룹을 포함하지만 임의의 다른 구성요소 또는 단계, 또는 구성요소들 또는 단계들의 그룹을 배제하지는 않음을 암시하는 것으로 이해되어야 한다. 또한, 모든 구성요소 또는 응용들의 다양한 조합 및 순열이 생성되고 제공될 수 있다. 구체적인 응용에 있어서 성능을 최적화하기 위한 모든 것이 행해질 수 있다.

## 도면의 간단한 설명

도1a는 종래의 기술 중 종래의 컴퓨터 파워 전달 시스템을 도시한다.

도1b는 종래의 기술의 컴퓨터 파워 운반 시스템의 세부 설명이다.

도1c는 본 발명에 의해 제거될 수 있는 종래의 기술의 컴퓨터 파워 운반 시스템의 일부를 도시한다.

도1d는 본 발명의 일 실시예에 따른 컴퓨터 파워 운반 시스템을 도시한다.

도1e는 본 발명의 파워 변환 소자의 실시예를 도시한다.

도1f는 본 발명의 파워 변환 소자의 다른 실시예를 도시한다.

도1g는 본 발명에 스위치 드라이브의 세부 사항을 도시한다.

도1h는 본 발명의 정류기 회로를 도시한다.

도1i는 일 실시예에서 커패시턴스 값의 변화에 의한 출력 전압의 변화를 도시한다.

도1j 및 도1k는 부하 저항의 함수로서 부하 저항을 교차하는 2개의 전압 변동을 도시한다.

도1l은 2개의 스위치 구성 및 다양한 일반적인 소자에 의한 다른 실시예이다.

도1m 및 도1n은 2개의 상이한 부하, 하이 및 로우 각각에 대해 다양한 위치에서의 전압 파형의 도면이다.

도3a는 종래의 기술의 전통적인 벽(BUCK) 컨버터이다.

도3b는 도3a에 도시한 벽 컨버터의 중점의 파형을 도시한다.

도3c는 본 발명에 따른 변압기 및 정류기 일부의 구성을 도시한다.

도3d는 도3c에 도시한 회로의 다양한 위치에서 존재할 수 있는 전압 파형을 도시한다.

도3e는 본 발명에 따른 SR에 대한 하나의 게이트 드라이브 구성을 도시한다.

도3f는 단일 스위칭 설계에 의한 1차측상의 전압 제어에 대한 회로를 도시한다.

도3g는 FET를 교차하는 제어 입력 전압의 기능으로서 소스 전압으로의 드레인의 균을 도시한다.

도3h는 듀얼 스위칭 설계에 의한 1차측상의 전압 제어에 대한 회로를 도시한다.

도3ia, 도3ib, 도3ic 및 도3id는 본 발명에 따른 다양한 동기 정류 회로를 도시한다.

도3j는 종래의 기술의 마이크로프로세서 시스템에 적용된 벌크 커패시터 및 바이패스 커패시터 구성을 도시한다.

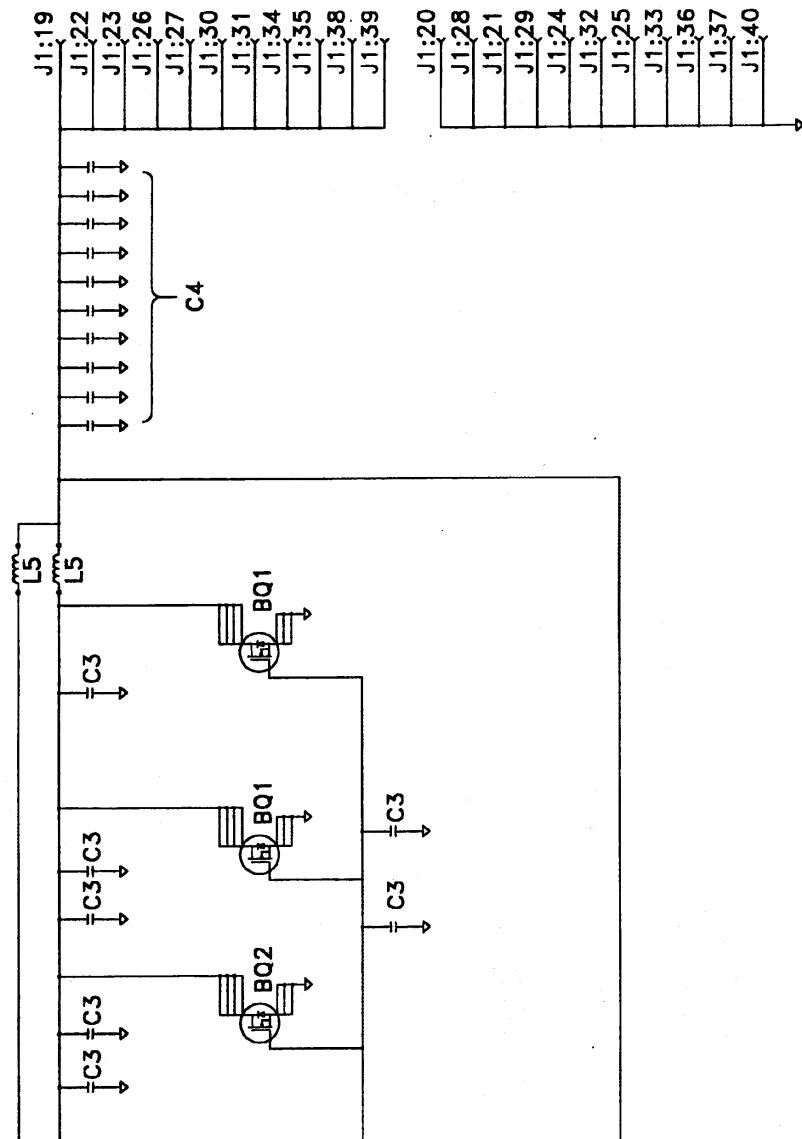

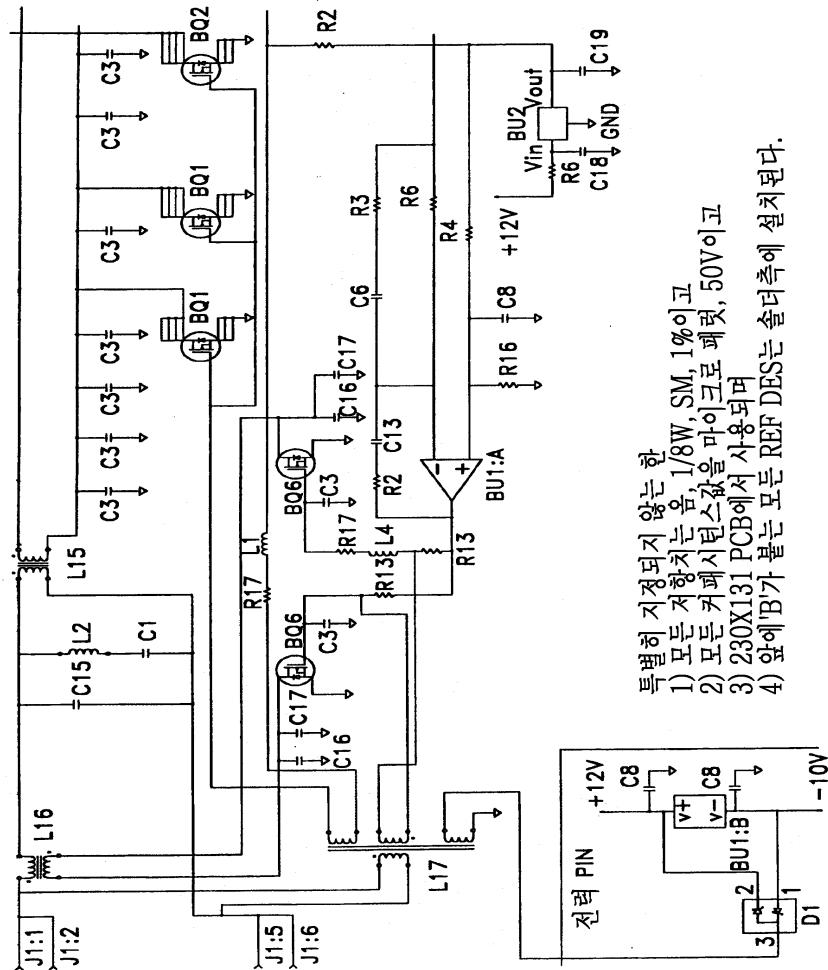

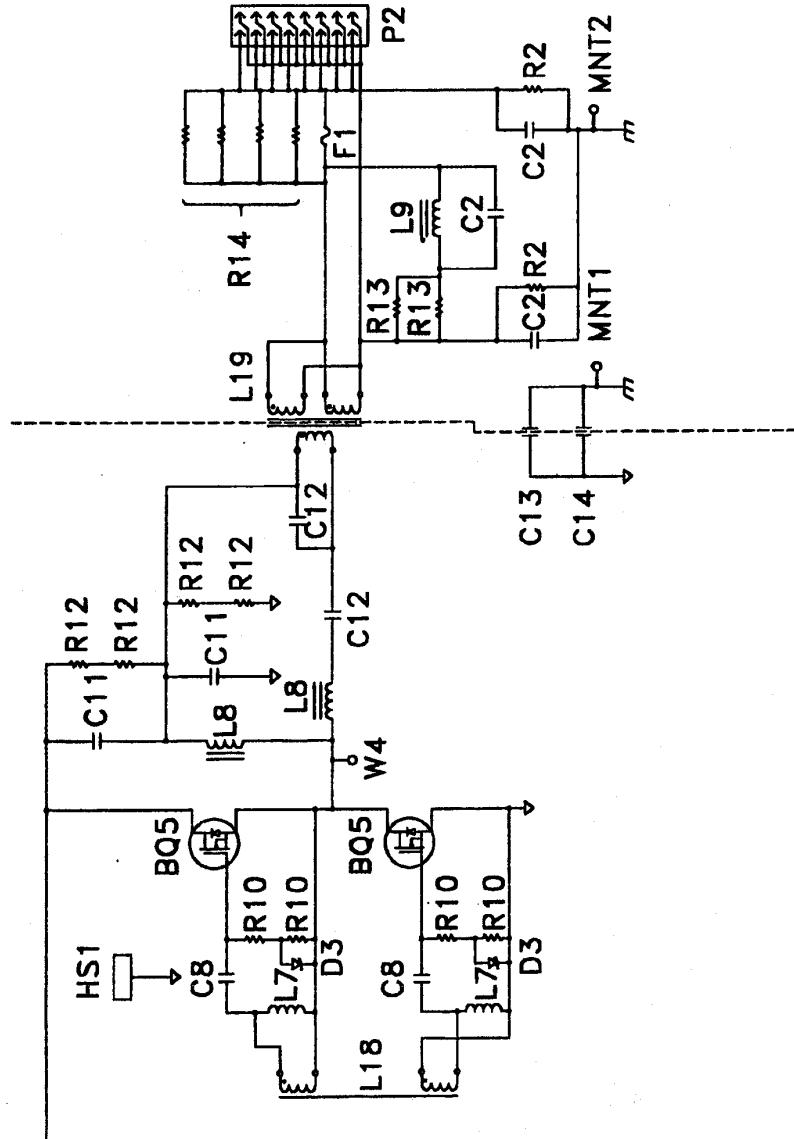

도3k는 단일 스위치 제어 소자를 사용하는 본 발명 중 전반적으로 바람직한 실시예를 도시한다.

도3l은 듀얼 스위치 제어 소자를 사용하는 본 발명 중 전반적으로 바람직한 실시예를 도시한다.

도3m은 설계 관점의 중요한 관점 중 전반적으로 바람직한 실시예를 도시한다.

도3n은 1차측 래글레이션에 대해 다양한 커패시터를 사용하는 전압 래글레이션 모듈 설계 중 다른 바람직한 실시예를 도시한다.

도3o는 본 발명의 일 설계에 대해 VRM 입력 임피던스 대부하 전류 퍼센트의 범위를 도시하는 스미스 차트이다.

**도면**

도면1a

도면1b

도면1c

도면1d

도면1e

도면1f

도면1g

도면1h

도면1i

도면1j

도면1k

도면11

도면1m

300 와트 출력

도면1n

30 와트 출력

도면3a

(종래기술)

도면3b

(종래기술)

도면3c

도면3d

도면3e

도면3f

도면3g

직렬스위스

FET Q1에

서리 Vds

도면3h

도면3ia

도면3ib

도면3ic

C

도면3id

도면3j

도면3ka

도면3kb

도면3kc

## 커패시터

|    |        |      |

|----|--------|------|

| C1 | 470PF  | 100V |

| C2 | 1000PF | 100V |

| C3 | 2200PF |      |

| C4 | 22PF   | 10V  |

| C5 | 100PF  | 100V |

| C6 | 4700PF | 100V |

| C7 | 5600PF | 100V |

| C8 | 0.1    |      |

## 저항

|    |                |

|----|----------------|

| R1 | 124            |

| R2 | 10K            |

| R3 | 49.9           |

| R4 | 3.24K          |

| R5 | 1.82K          |

| R6 | 499            |

| R7 | 5.6 1/2W 5% SM |

| R8 | 0.1 1/2W SM    |

## 인덕터

|    |          |

|----|----------|

| L1 | 330NH    |

| L2 | No Value |

| L3 | 150NH    |

| L5 | 100NH    |

## 보조

|       |        |

|-------|--------|

| BU1:A | AD825  |

| BU1:B | AD825  |

| BU2   | AD1585 |

## 변압기

|     |       |    |

|-----|-------|----|

| L15 | TRANS | L2 |

| L16 | TRANS | L4 |

| L17 | TRANS | L6 |

D1 HSMS2802

## 트랜지스터

|     |           |

|-----|-----------|

| BQ1 | OPEN      |

| BQ2 | M14420T   |

| BQ3 | Q1 NOTEST |

도면31a

도면3lb

## 도면3lc

## 커패시터

|     |        |      |     |           |

|-----|--------|------|-----|-----------|

| C1  | 470PF  | 100V | R2  | 10K       |

| C3  | 2200PF |      | R3  | 49.9      |

| C4  | 22PF   | 10V  | R4  | 3.24K     |

| C6  | 4700PF | 100V | R6  | 499       |

| C8  | 0.1PF  |      | R13 | 100       |

| C15 | 1500PF | 50V  | R15 | 24.9K     |

| C16 | 2700PF | 100V | R16 | 1.82K     |

| C17 | 680PF  | 100V | R17 | OPEN 1/2W |

| C18 | 4.7uF  |      |     |           |

| C19 | 1uF    |      |     |           |

## 저항

## 인덕터

|    |          |

|----|----------|

| L1 | 330NH    |

| L2 | No Value |

| L4 | OPEN     |

| L5 | 100NH    |

## 보조

|       |          |

|-------|----------|

| BU1:A | AD825    |

| BU1:B | AD825    |

| BU2   | AD1585   |

| D1    | HSMS2802 |

## 변압기

|     |       |    |

|-----|-------|----|

| L15 | TRANS | L2 |

| L16 | TRANS | L4 |

| L17 | TRANS | L6 |

## 트랜지스터

|     |               |

|-----|---------------|

| BQ1 | OPEN          |

| BQ2 | M14420T       |

| BQ6 | RFD16NO06LESM |

도면3ma

- 특별한 지정되지 않는 한

1) 모든 저항치는  $1/8W$ ,  $SM$ ,  $1\%$ 이고

2) 모든 커넥션은 스트립으로 페킷,  $50V$ 이고

3) 2305684 PCB에서 사용되며

4) 앞에 'B'가 붙는 모든 REF DES는 솔더축에 설치된다.

도면3mb

도면3mc

## 커패시터

|     |        |

|-----|--------|

| C2  | 1000PF |

| C3  | 2200PF |

| C8  | 0.1PF  |

| C9  | 220PF  |

| C10 | 150PF  |

| C11 | 0.1PF  |

| C12 | 270PF  |

| C13 | OPEN   |

| C14 | 2200PF |

|     | 250VAC |

## 저항

|     |      |

|-----|------|

| R2  | 10K  |

| R9  | OPEN |

| R10 | 1K   |

| R11 | 10   |