## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2003/0123271 A1 **Iwata**

Jul. 3, 2003 (43) Pub. Date:

## (54) MAGNETIC RANDOM ACCESS MEMORY

Inventor: Yoshihisa Iwata, Yokohama-shi (JP)

Correspondence Address: OBLON, SPIVAK, MCCLELLAND, MAIER & NEUSTADT, P.C. 1940 DUKE STREET ALEXANDRIA, VA 22314 (US)

(21) Appl. No.: 10/162,605

Filed: Jun. 6, 2002

(30)Foreign Application Priority Data

(JP) ...... 2001-390549

### Publication Classification

(51) Int. Cl.<sup>7</sup> ...... G11C 5/06

## ABSTRACT

A read block is formed from a plurality of TMR elements stacked in the vertical direction. One terminal of each TMR element in the read block is connected to a source line through a read select switch. The source line extends in the Y-direction and is connected to a ground point through a column select switch. The other terminal of each TMR element is independently connected to a corresponding one of read/write bit lines. Each read/write bit line extends in the Y-direction and is connected to a read circuit through the column select switch.

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

FIG.8

FIG.9

FIG. 10

FIG. 11

FIG. 12

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 24

FIG. 25

F I G. 27

FIG. 28

FIG. 30

FIG. 32

FIG. 33

FIG. 34

FIG. 35

FIG. 39

FIG. 40

FIG. 41

FIG. 44

FIG. 46

FIG. 47

FIG. 48

FIG. 49

FIG. 50

FIG. 51

FIG. 52

FIG. 53

FIG. 56

FIG. 58

FIG. 60

FIG. 61

FIG. 62

FIG. 63

FIG. 64

FIG. 65

FIG. 66

FIG. 68

FIG. 73

FIG. 74

FIG. 75

FIG. 78

FIG. 80

FIG. 81

FIG. 83

FIG. 84

FIG. 86

FIG. 88

FIG. 90

FIG. 91

FIG. 96

FIG. 97

FIG. 98

FIG. 99

FIG. 100

FIG. 101

FIG. 102

FIG. 103

FIG. 104

FIG. 105

FIG. 107

FIG. 108

FIG. 109

FIG. 110

FIG. 111

FIG. 112

FIG. 113

FIG. 114

FIG. 115

FIG. 116

#### MAGNETIC RANDOM ACCESS MEMORY

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is based upon and claims the benefit of priority from the prior Japanese Patent Application No. 2001-390549, filed Dec. 21, 2001, the entire contents of which are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a magnetic random access memory (MRAM) which stores "1"- and "0"-data using a magnetoresistive effect.

[0004] 2. Description of the Related Art

[0005] In recent years, many memories which store data by new principles have been proposed. One of them is a magnetic random access memory which stores "1"- and "0"-data using a tunneling magnetoresistive (to be referred to as TMR hereinafter) effect.

[0006] As a proposal for a magnetic random access memory, for example, Roy Scheuerlein et al, "A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell", ISSCC2000 Technical Digest, p. 128 is known.

[0007] A magnetic random access memory stores "1"- and "0"-data using TMR elements. As the basic structure of a TMR element, an insulating layer (tunneling barrier) is sandwiched between two magnetic layers (ferromagnetic layers).

[0008] Data stored in the TMR element is determined on the basis of whether the magnetizing states of the two magnetic layers are parallel or anti-parallel. "Parallel" means that the two magnetic layers have the same magnetizing direction. "Anti-parallel" means that the two magnetic layers have opposite magnetizing directions.

[0009] Normally, one (fixed layer) of the two magnetic layers has an anti-ferromagnetic layer. The anti-ferromagnetic layer serves as a member for fixing the magnetizing direction of the fixed layer. In fact, data ("1" or "0") stored in the TMR element is determined by the magnetizing direction of the other (free layer) of the two magnetic layers.

[0010] When the magnetizing states in the TMR element are parallel, the resistance of the insulating layer (tunneling barrier) sandwiched between the two magnetic layers of the TMR element is minimized. For example, this state is defined as a "1"-state. When the magnetizing states in the TMR element are anti-parallel, the resistance of the insulating layer (tunneling barrier) sandwiched between the two magnetic layers of the TMR element is maximized. For example, this state is defined as a "0"-state.

[0011] Currently, various kinds of cell array structures have been examined for a magnetic random access memory from the viewpoint of increasing the memory capacity or stabilizing write/read operation.

[0012] For example, currently, a cell array structure in which one memory cell is formed from one MOS transistor and one TMR element (or an MTJ (Magnetic Tunnel Junc-

tion) element) is known. Additionally, a magnetic random access memory which has such a cell array structure and stores 1-bit data using two memory cell arrays so as to realize stable read operation is also known.

[0013] However, in these magnetic random access memories, it is difficult to increase the memory capacity. This is because one MOS transistor corresponds to one TMR element in these cell array structures.

### BRIEF SUMMARY OF THE INVENTION

[0014] According to an aspect of the present invention, there is provided a magnetic random access memory comprising: a plurality of memory cells which are stacked at a plurality of stages to store data using a magnetoresistive effect; a read select switch commonly connected to one terminal of each of the plurality of memory cells; and a plurality of bit lines arranged in correspondence with the plurality of memory cells and extending in a first direction, wherein each of the plurality of memory cells has the other terminal independently connected to one of the plurality of bit lines.

[0015] According to an aspect of the present invention, there is provided a read method-of a magnetic random access memory, the magnetic random access memory having a read block formed from a plurality of memory cells which store data using a magnetoresistive effect, and a plurality of sense amplifiers arranged in correspondence with the plurality of memory cells, comprising: simultaneously and independently supplying a read current to the plurality of memory cells; detecting data of the plurality of memory cells by the plurality of sense amplifiers on the basis of the read current; and simultaneously outputting data of the plurality of sense amplifiers.

[0016] According to an aspect of the present invention, there is provided a manufacturing method of a magnetic random access memory, comprising: forming a read select switch on a surface region of a semiconductor substrate; forming a first write word line extending in a first direction on the read select switch; forming a first MTJ element right above the first write word line; forming, right above the first MTJ element, a first read/write bit line which is in contact with the first MTJ element and extends in a second direction perpendicular to the first direction; forming a second write word line extending in the first direction right above the first write word line; forming a second MTJ element right above the second write word line; and forming, right above the second MTJ element, a second read/write bit line which is in contact with the second MTJ element and extends in the second direction.

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

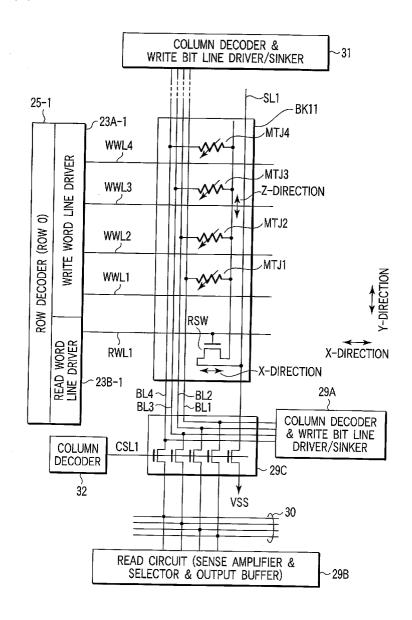

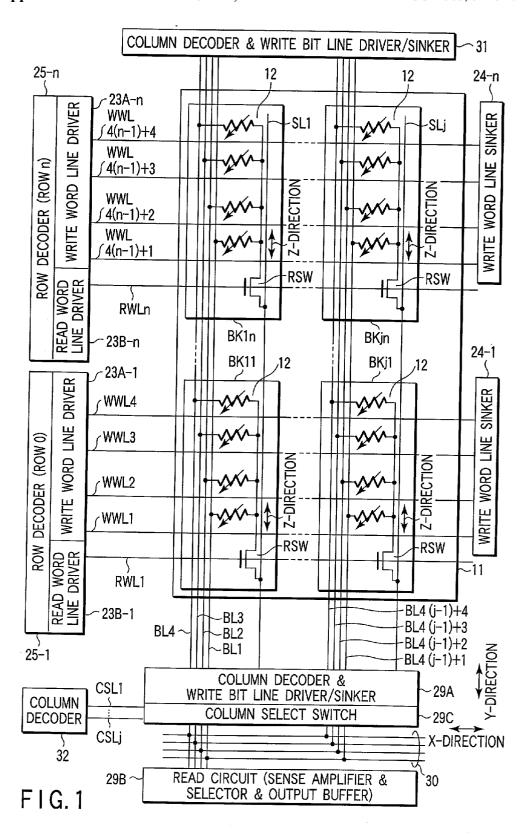

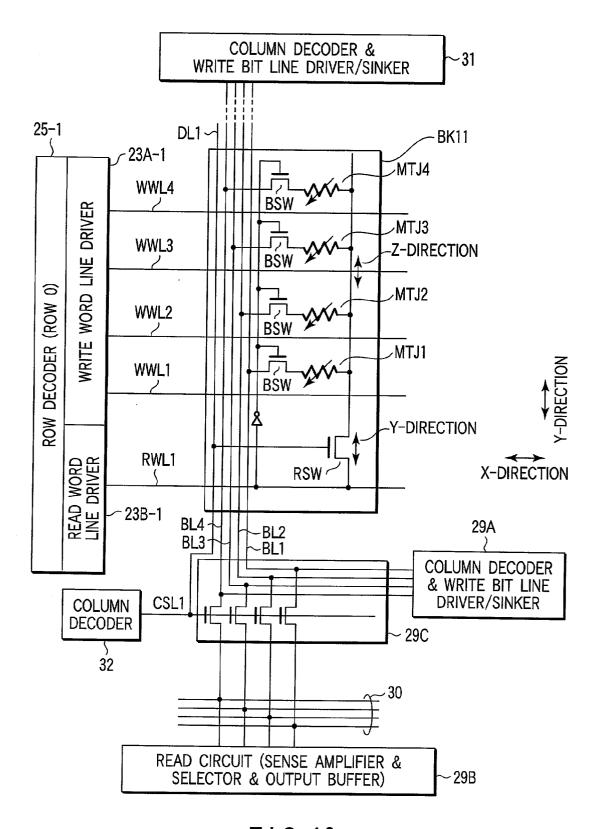

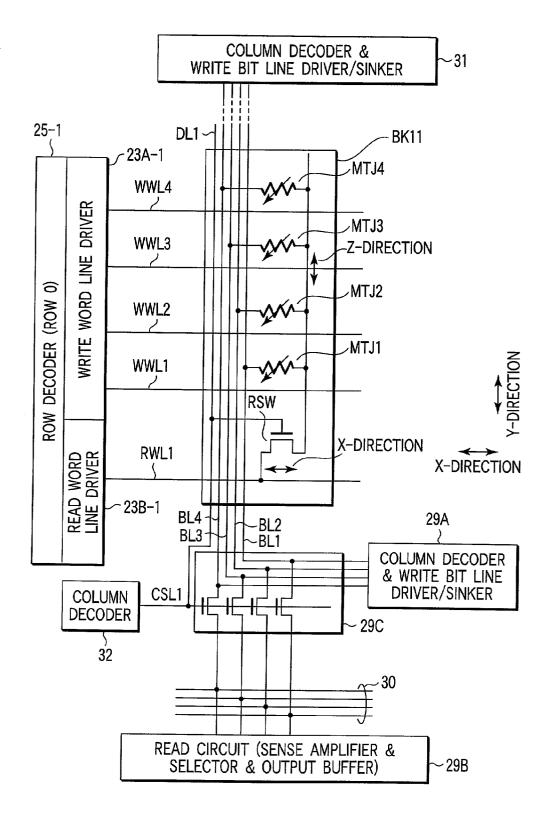

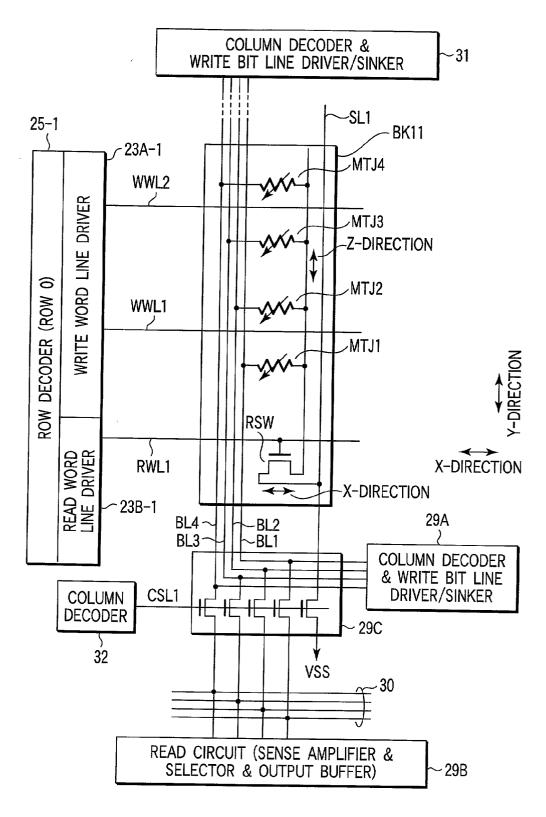

[0017] FIG. 1 is a circuit diagram related to a magnetic random access memory of Structural Example 1 of the present invention;

[0018] FIG. 2 is a circuit diagram related to the magnetic random access memory of Structural Example 1 of the present invention;

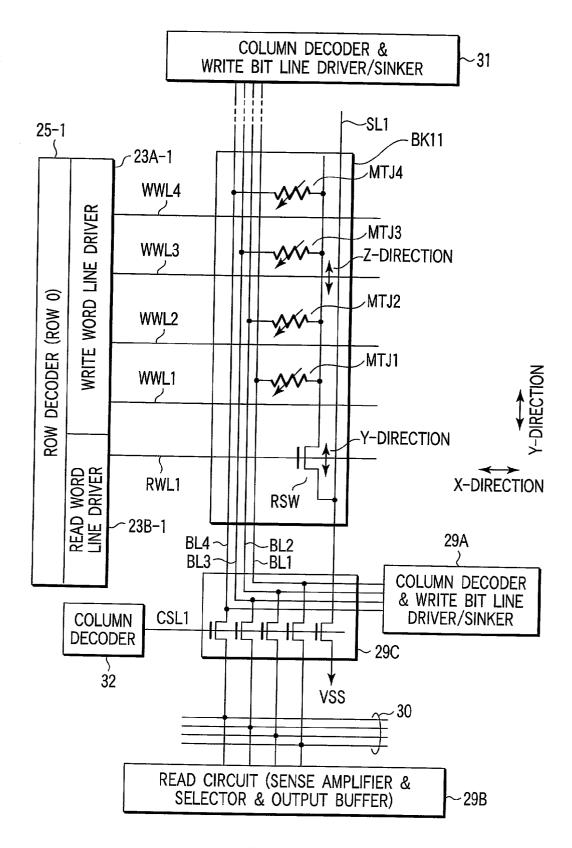

[0019] FIG. 3 is a circuit diagram related to a modification to the magnetic random access memory of Structural Example 1 of the present invention;

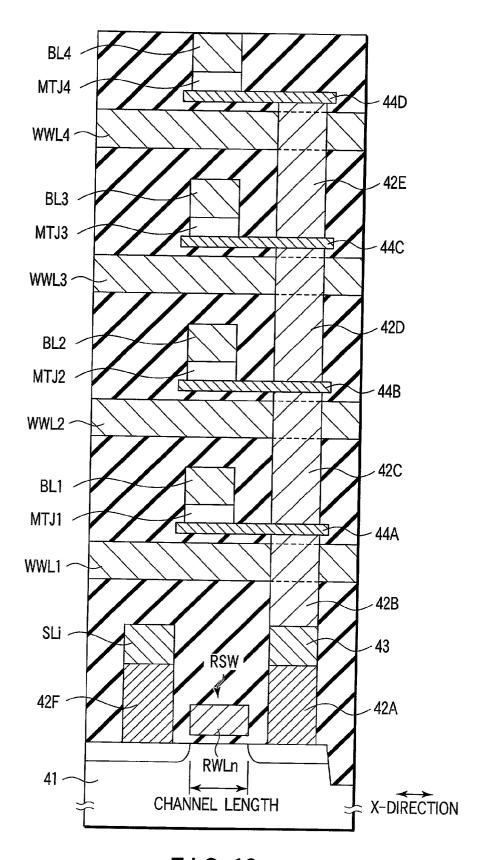

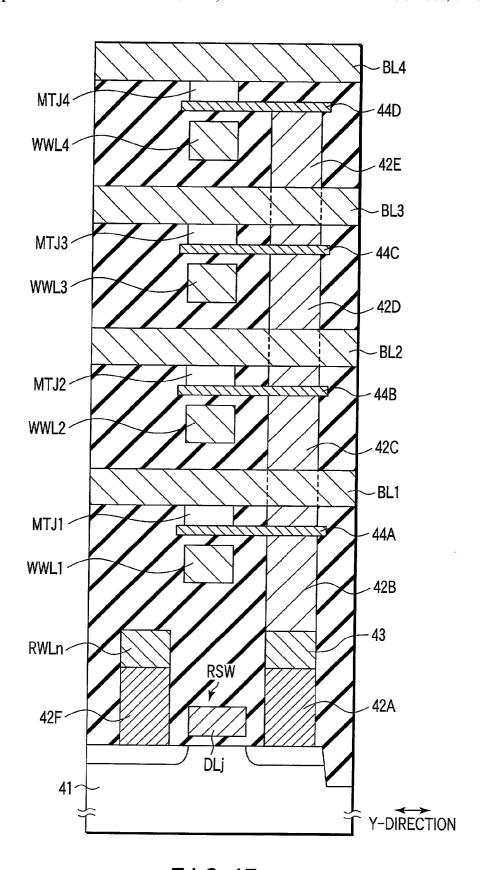

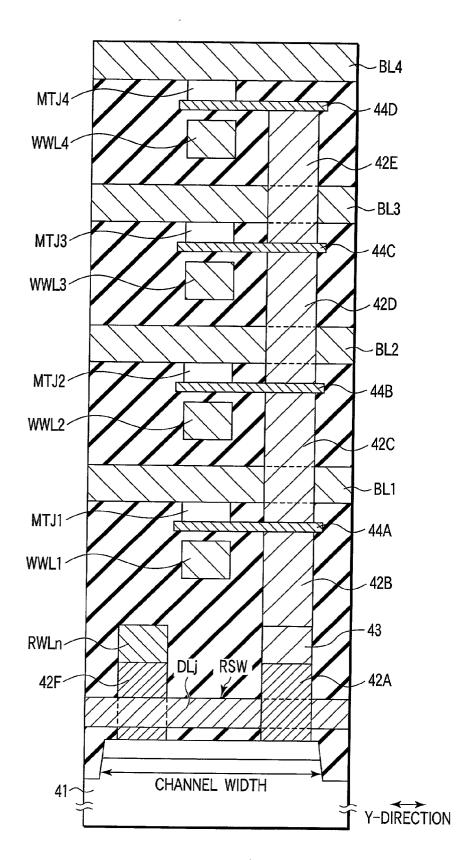

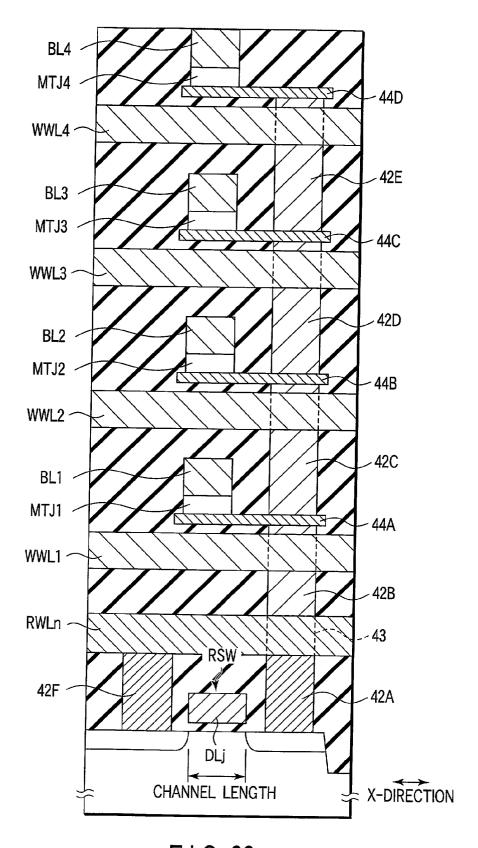

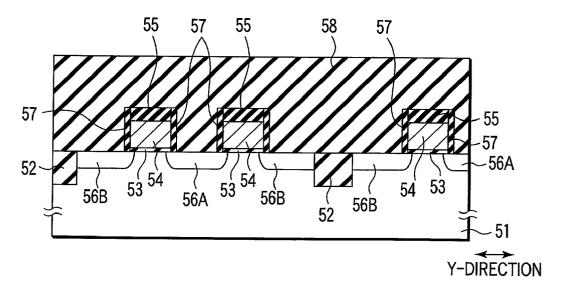

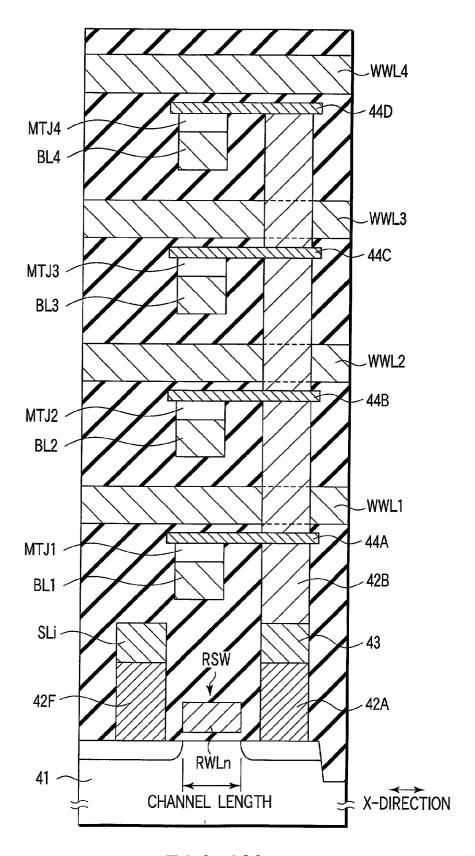

[0020] FIG. 4 is a sectional view related to the magnetic random access memory of Structural Example 1 of the present invention;

[0021] FIG. 5 is a sectional view related to the magnetic random access memory of Structural Example 1 of the present invention;

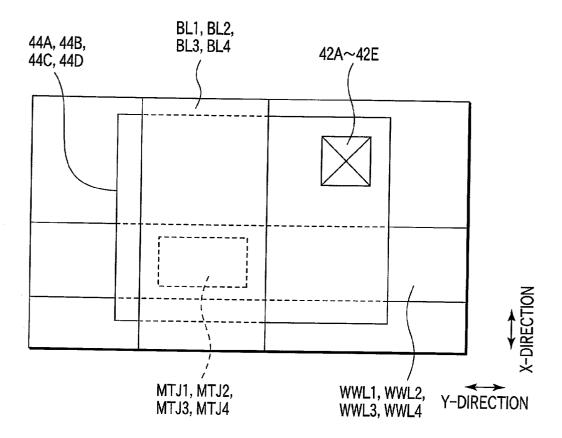

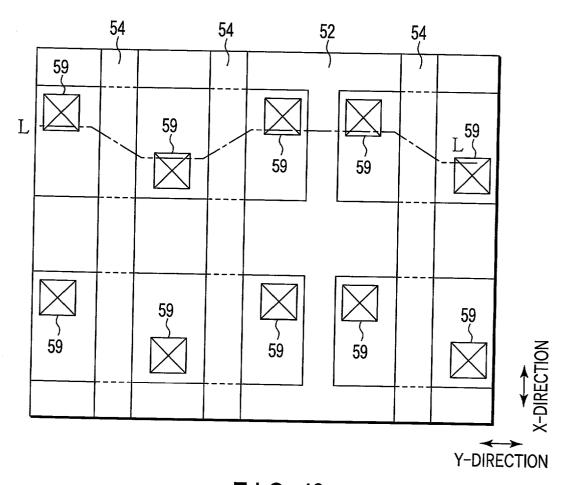

[0022] FIG. 6 is a plan view showing a TMR element of Structural Example 1 and the layout near the TMR element;

[0023] FIG. 7 is a sectional view showing a structural example of the TMR element;

[0024] FIG. 8 is a sectional view showing a structural example of the TMR element;

[0025] FIG. 9 is a sectional view showing a structural example of the TMR element;

[0026] FIG. 10 is a circuit diagram related to a magnetic random access memory of Structural Example 2 of the present invention;

[0027] FIG. 11 is a sectional view related to the magnetic random access memory of Structural Example 2 of the present invention;

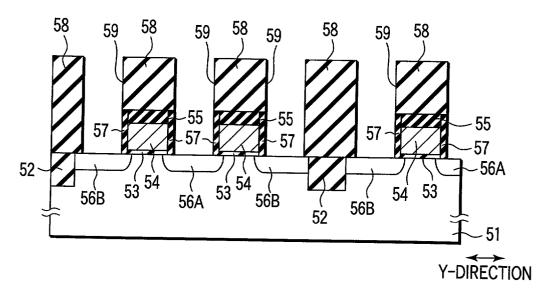

[0028] FIG. 12 is a sectional view related to the magnetic random access memory of Structural Example 2 of the present invention;

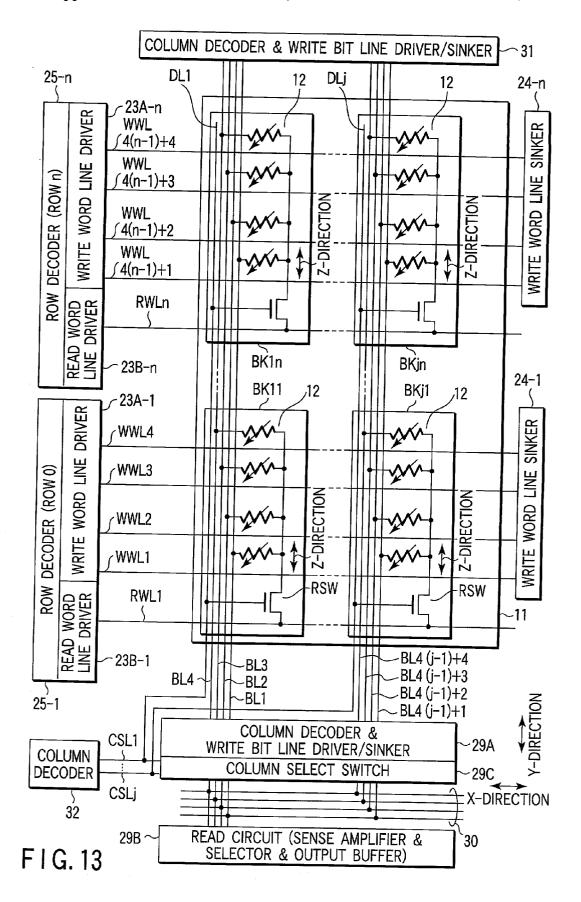

[0029] FIG. 13 is a circuit diagram related to a magnetic random access memory of Structural Example 3 of the present invention;

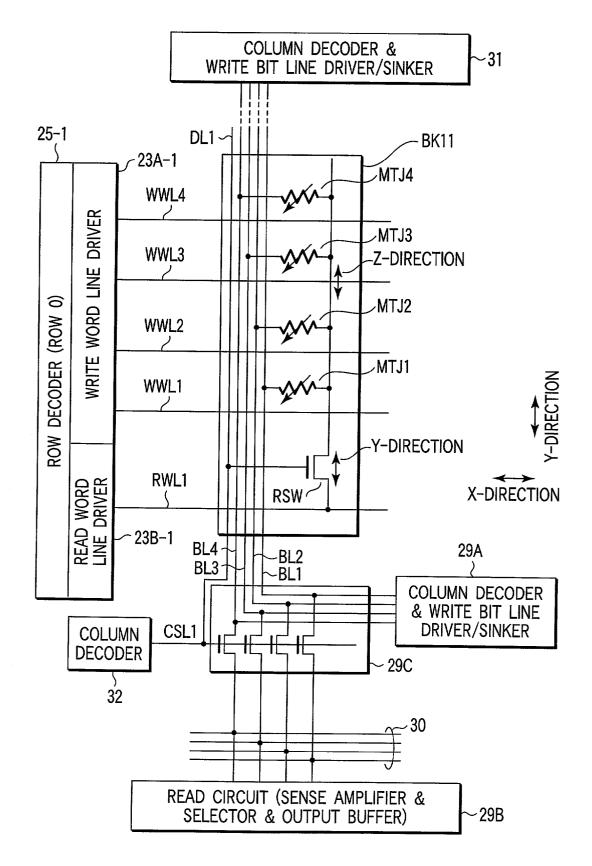

[0030] FIG. 14 is a circuit diagram related to the magnetic random access memory of Structural Example 3 of the present invention;

[0031] FIG. 15 is a circuit diagram related to a modification to the magnetic random access memory of Structural Example 3 of the present invention;

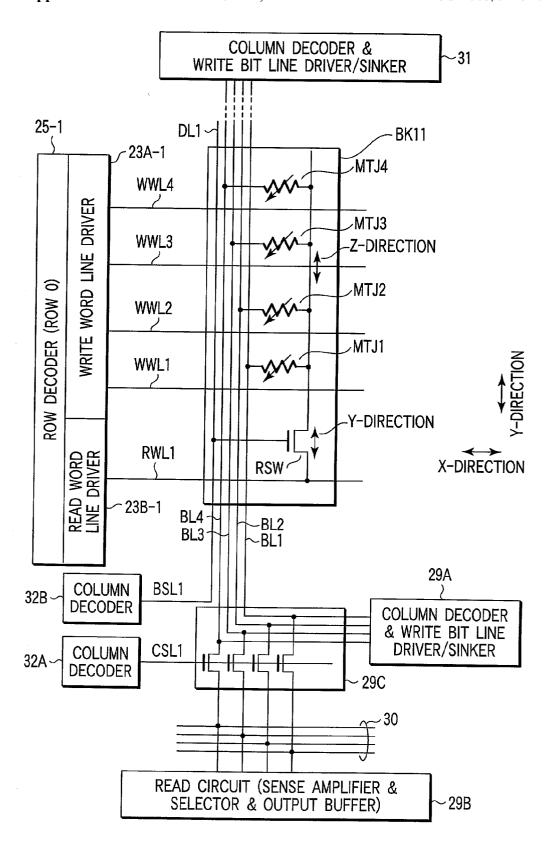

[0032] FIG. 16 is a circuit diagram related to a modification to the magnetic random access memory of Structural Example 3 of the present invention;

[0033] FIG. 17 is a sectional view related to the magnetic random access memory of Structural Example 3 of the present invention;

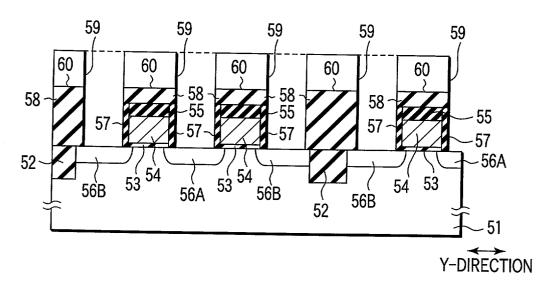

[0034] FIG. 18 is a sectional view related to the magnetic random access memory of Structural Example 3 of the present invention;

[0035] FIG. 19 is a plan view showing a TMR element of Structural Example 3 and the layout near the TMR element;

[0036] FIG. 20 is a circuit diagram related to a magnetic random access memory of Structural Example 4 of the present invention;

[0037] FIG. 21 is a sectional view related to the magnetic random access memory of Structural Example 4 of the present invention;

[0038] FIG. 22 is a sectional view related to the magnetic random access memory of Structural Example 4 of the present invention;

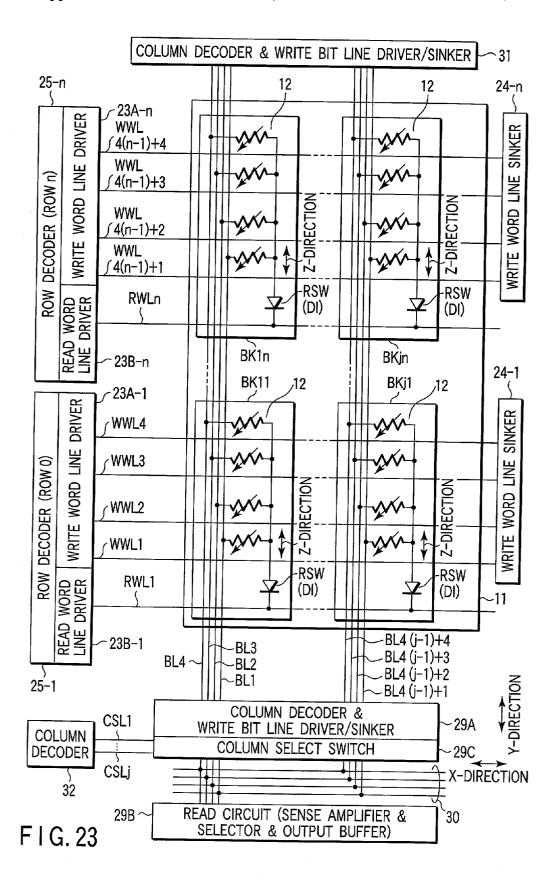

[0039] FIG. 23 is a circuit diagram related to a magnetic random access memory of Structural Example 5 of the present invention;

[0040] FIG. 24 is a sectional view related to the magnetic random access memory of Structural Example 5 of the present invention;

[0041] FIG. 25 is a sectional view related to the magnetic random access memory of Structural Example 5 of the present invention;

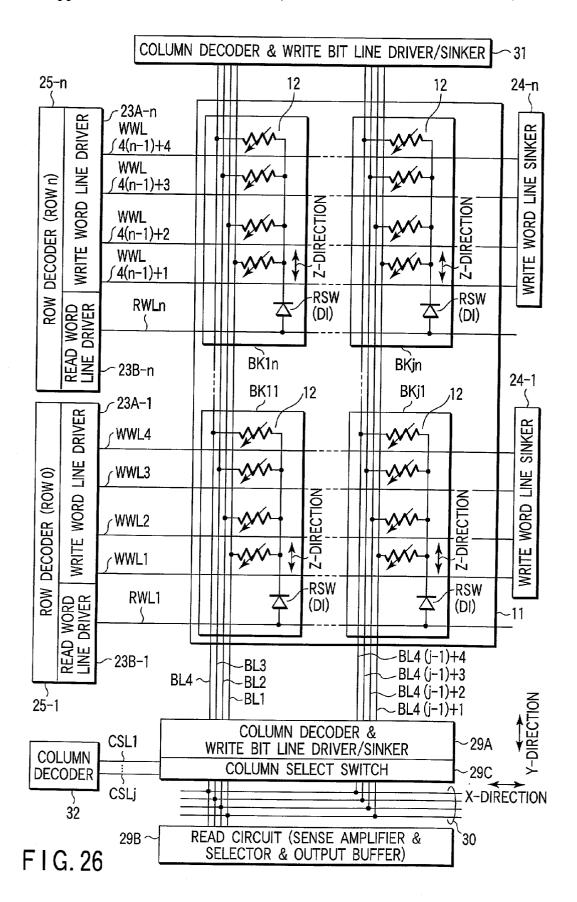

[0042] FIG. 26 is a circuit diagram related to a magnetic random access memory of Structural Example 6 of the present invention;

[0043] FIG. 27 is a sectional view related to the magnetic random access memory of Structural Example 6 of the present invention;

[0044] FIG. 28 is a sectional view related to the magnetic random access memory of Structural Example 6 of the present invention;

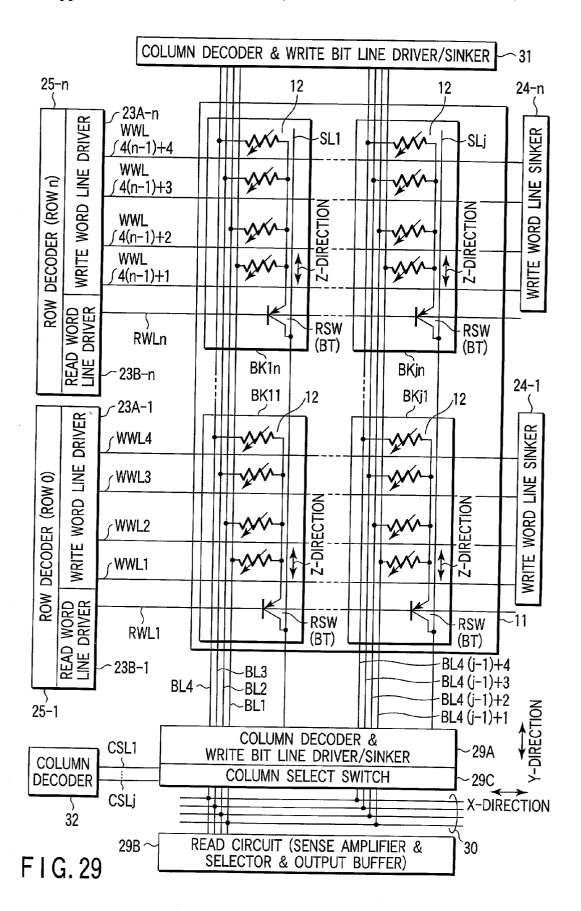

[0045] FIG. 29 is a circuit diagram related to a magnetic random access memory of Structural Example 7 of the present invention;

[0046] FIG. 30 is a sectional view related to the magnetic random access memory of Structural Example 7 of the present invention;

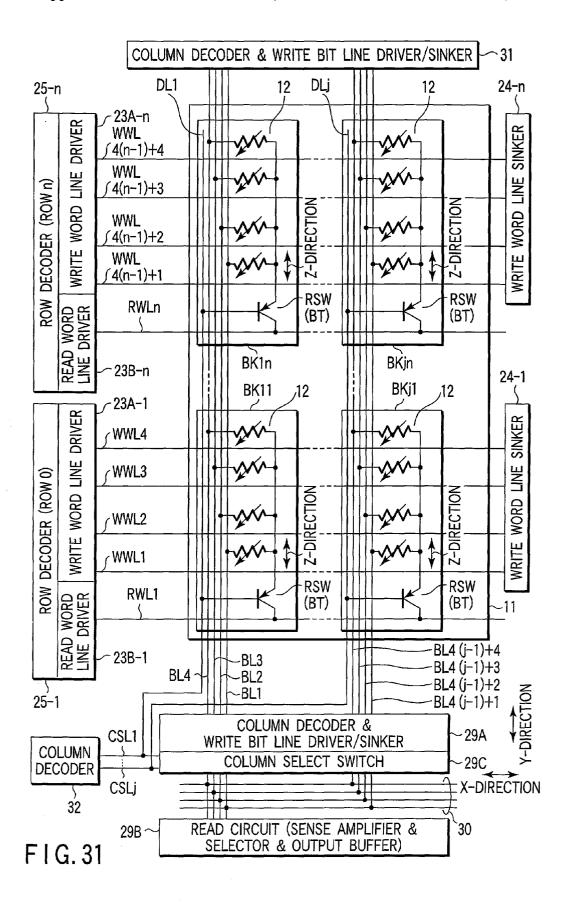

[0047] FIG. 31 is a circuit diagram related to a magnetic random access memory of Structural Example 8 of the present invention;

[0048] FIG. 32 is a sectional view related to the magnetic random access memory of Structural Example 8 of the present invention;

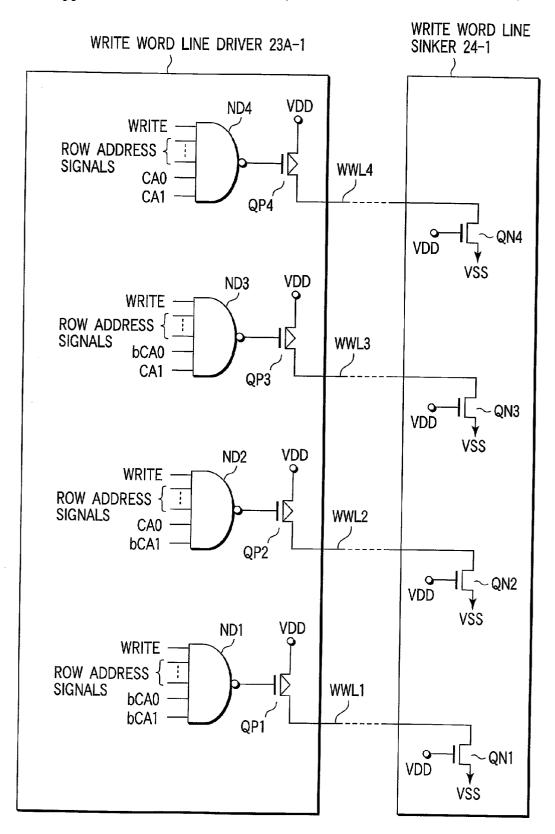

[0049] FIG. 33 is a view showing a circuit example of the write word line driver/sinker;

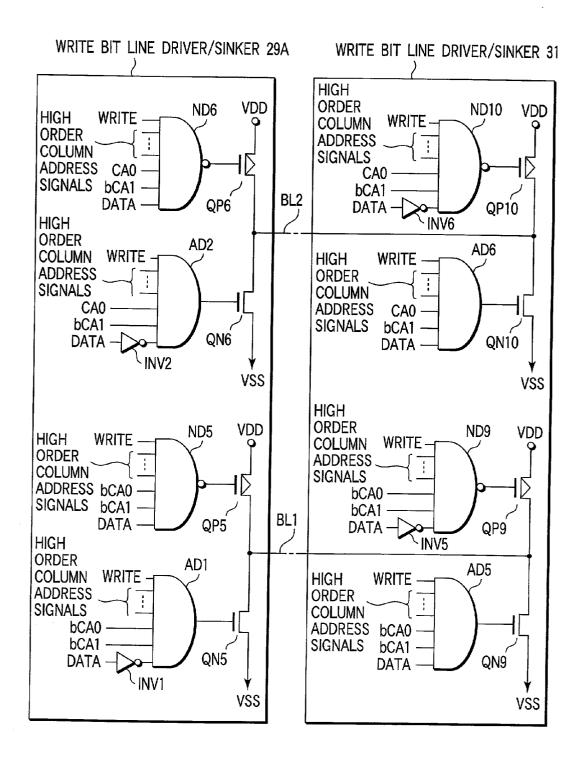

[0050] FIG. 34 is a view showing a circuit example of the write bit line driver/sinker;

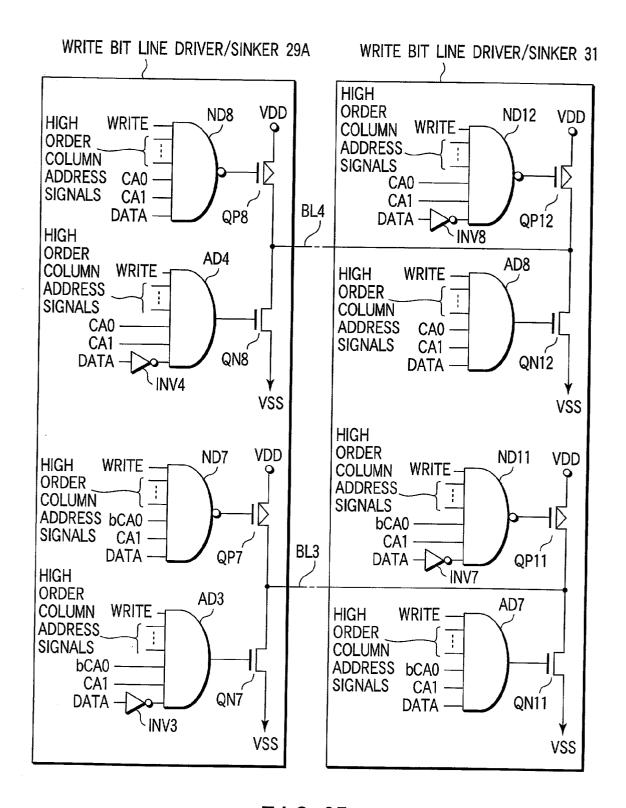

[0051] FIG. 35 is a view showing a circuit example of the write bit line driver/sinker;

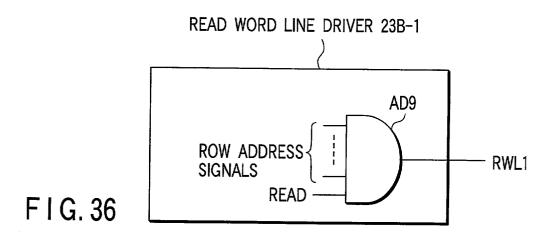

[0052] FIG. 36 is a view showing a circuit example of the read word line driver;

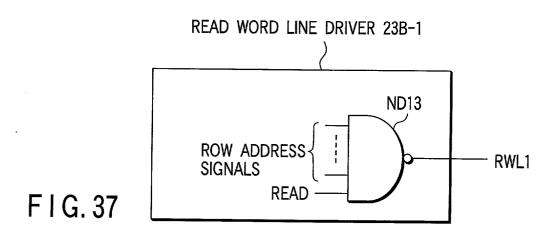

[0053] FIG. 37 is a view showing a circuit example of the read word line driver;

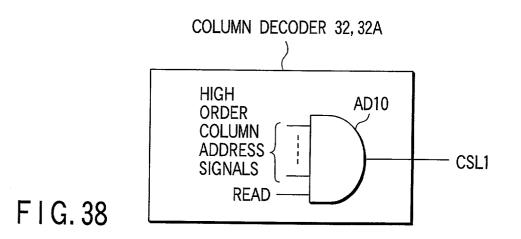

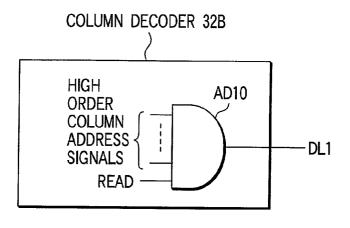

[0054] FIG. 38 is a view showing a circuit example of the column decoder;

[0055] FIG. 39 is a view showing a circuit example of the column decoder;

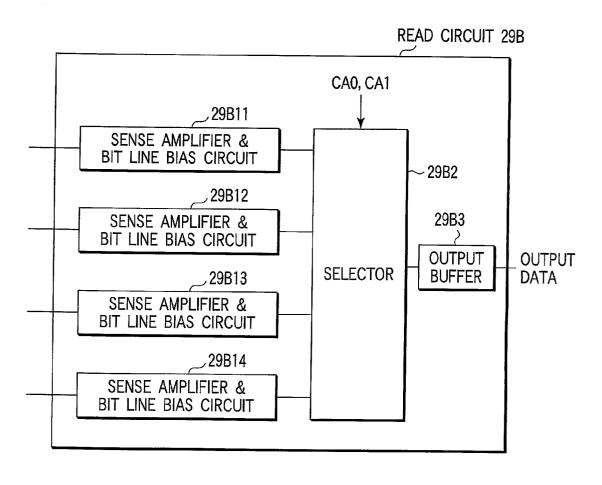

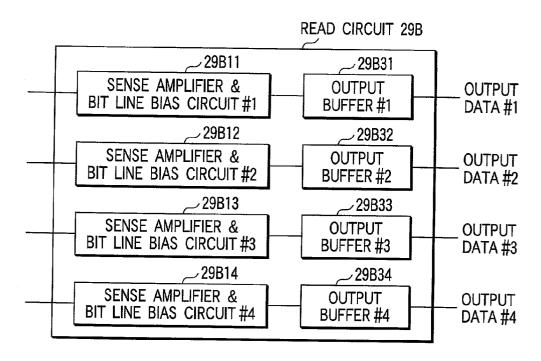

[0056] FIG. 40 is a block diagram of a circuit example of the read circuit;

[0057] FIG. 41 is a block diagram of a circuit example of the read circuit;

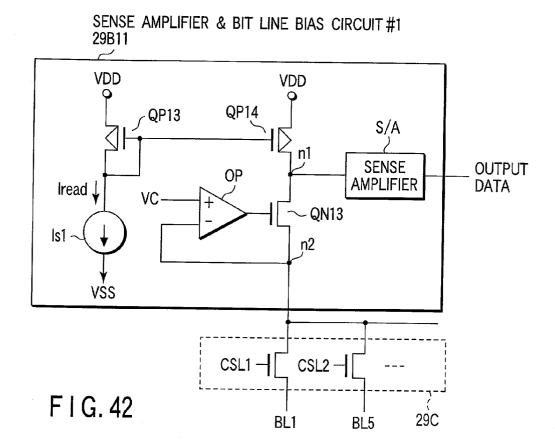

[0058] FIG. 42 is a view showing a circuit example of the sense amplifier & bias circuit;

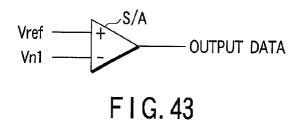

[0059] FIG. 43 is a view showing a circuit example of the sense amplifier;

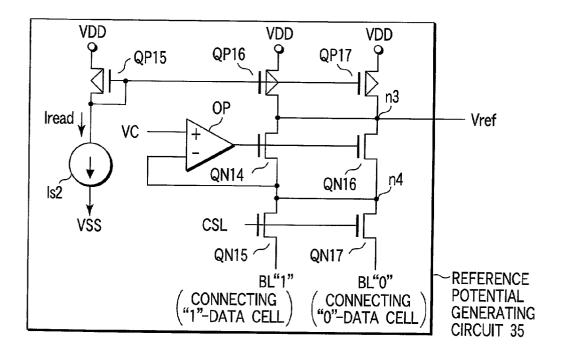

[0060] FIG. 44 is a view showing a circuit example of the reference potential generating circuit;

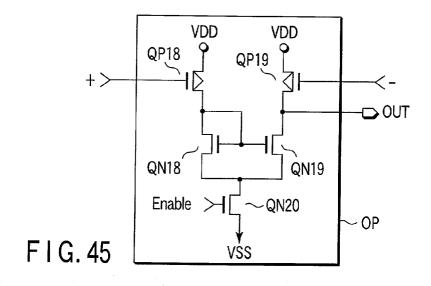

[0061] FIG. 45 is a view showing a circuit example of an differential amplifier, the OP in FIGS. 42 and 44 and the S/A in FIG. 43;

[0062] FIG. 46 is a view showing a device structure to which the manufacturing method of the present invention is applied;

[0063] FIG. 47 is a sectional view showing one step of the manufacturing method of the present invention;

[0064] FIG. 48 is a sectional view showing one step of the manufacturing method of the present invention;

[0065] FIG. 49 is a plan view showing one step of the manufacturing method of the present invention;

[0066] FIG. 50 is a sectional view taken along a line L-L in FIG. 49;

[0067] FIG. 51 is a sectional view showing one step of the manufacturing method of the present invention;

[0068] FIG. 52 is a sectional view showing one step of the manufacturing method of the present invention;

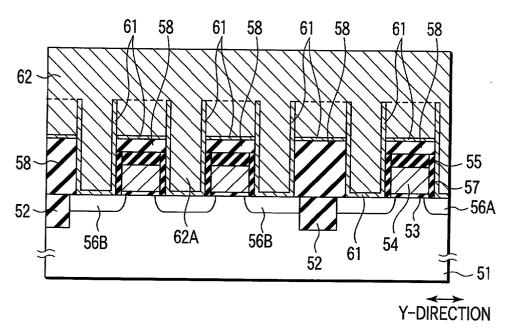

[0069] FIG. 53 is a sectional view showing one step of the manufacturing method of the present invention;

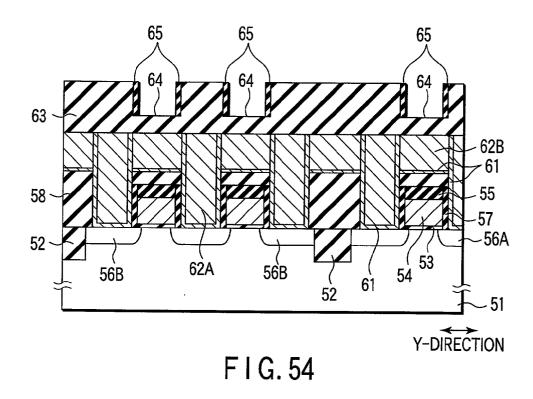

[0070] FIG. 54 is a sectional view showing one step of the manufacturing method of the present invention;

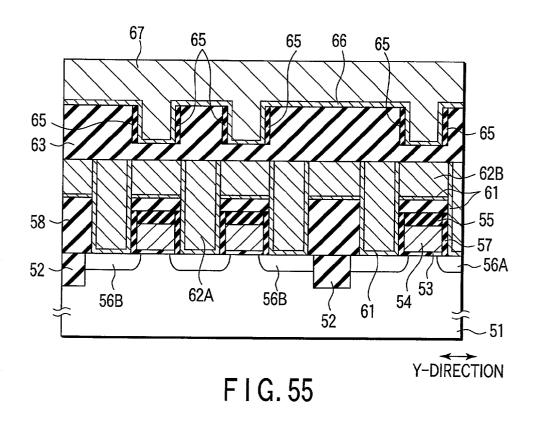

[0071] FIG. 55 is a sectional view showing one step of the manufacturing method of the present invention;

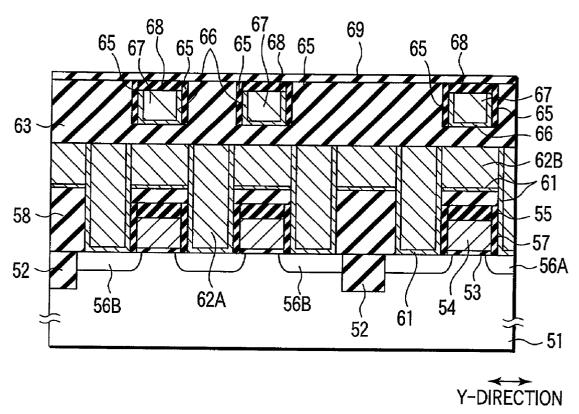

[0072] FIG. 56 is a sectional view showing one step of the manufacturing method of the present invention;

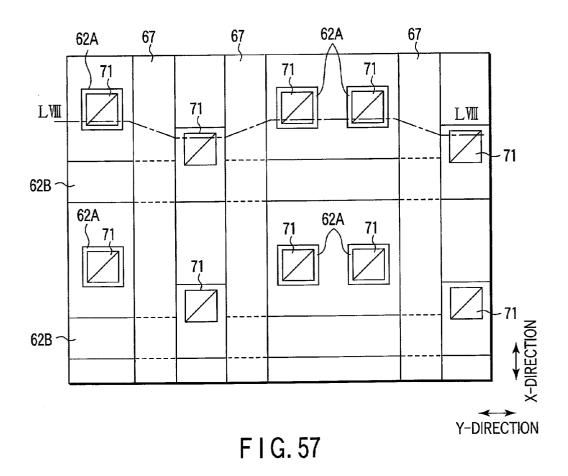

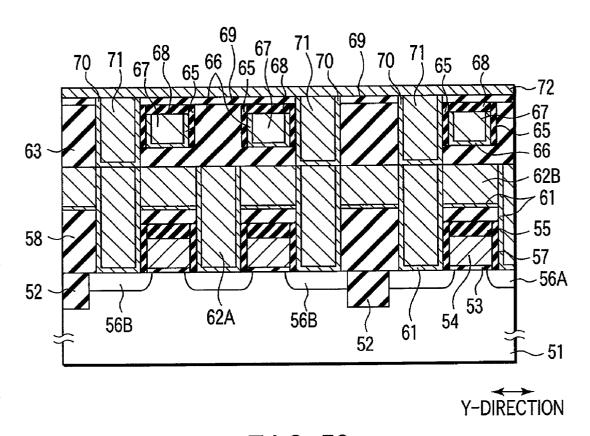

[0073] FIG. 57 is a plan view showing one step of the manufacturing method of the present invention;

[0074] FIG. 58 is a sectional view taken along a line LVIII-LVIII in FIG. 57;

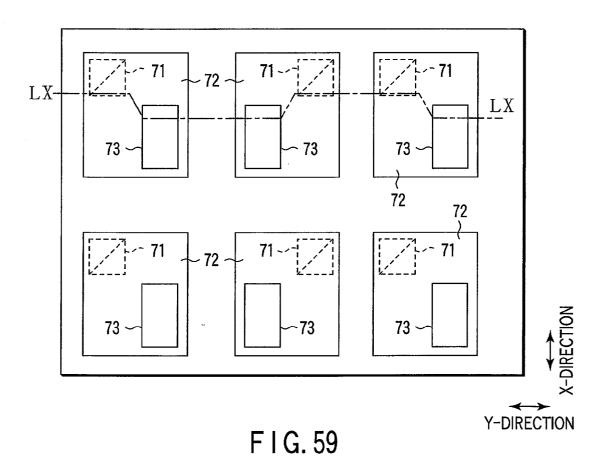

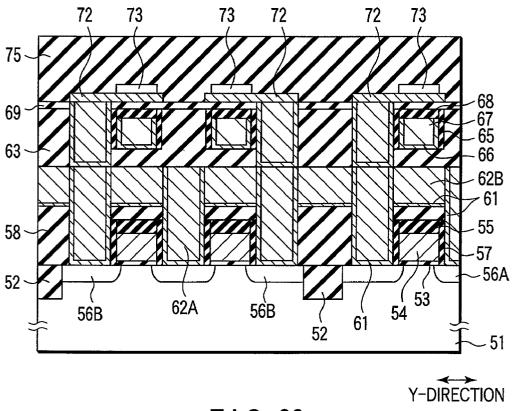

[0075] FIG. 59 is a plan view showing one step of the manufacturing method of the present invention;

[0076] FIG. 60 is a sectional view taken along a line LX-LX in FIG. 59;

[0077] FIG. 61 is a sectional view showing one step of the manufacturing method of the present invention;

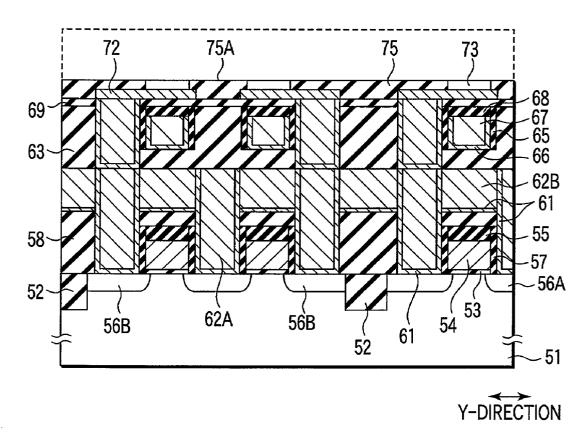

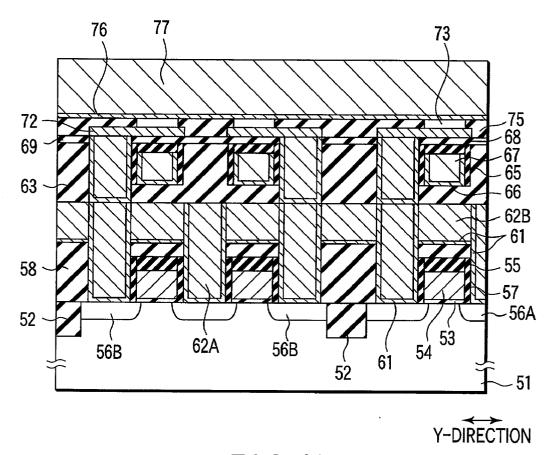

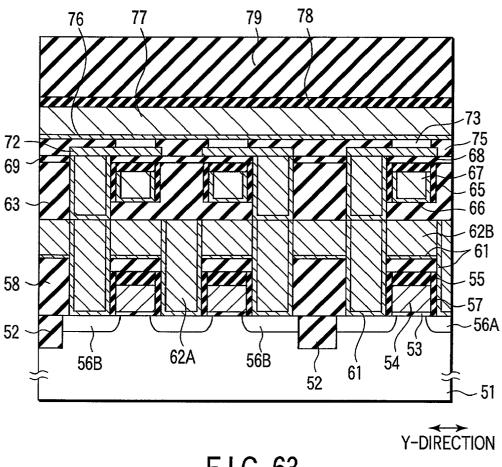

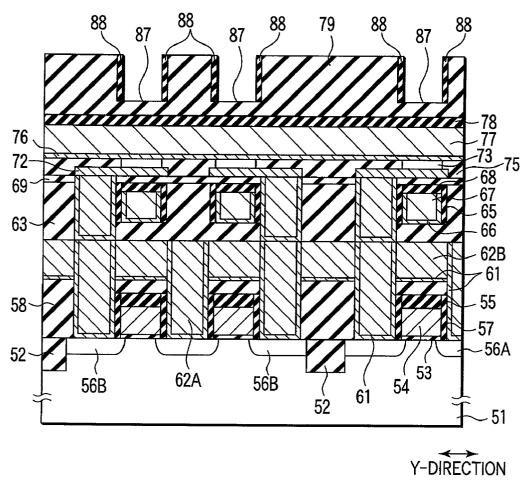

[0078] FIG. 62 is a sectional view showing one step of the manufacturing method of the present invention;

[0079] FIG. 63 is a sectional view showing one step of the manufacturing method of the present invention;

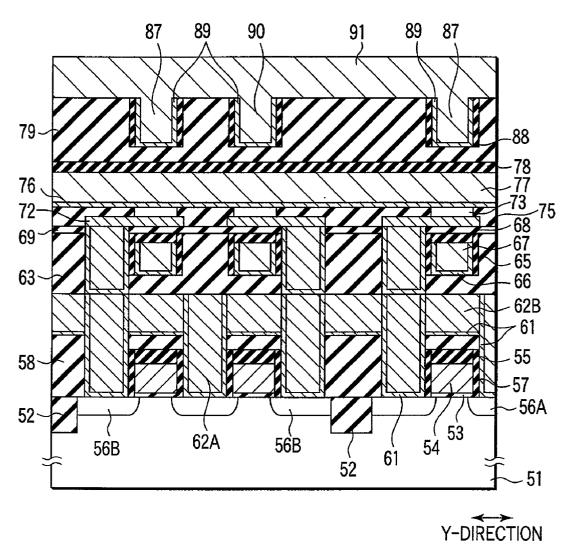

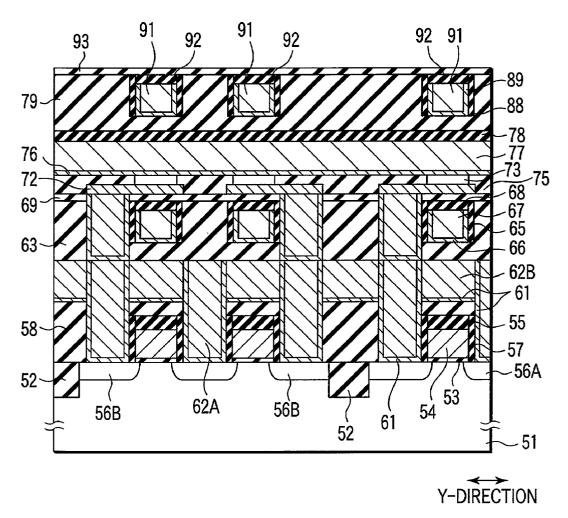

[0080] FIG. 64 is a sectional view showing one step of the manufacturing method of the present invention;

[0081] FIG. 65 is a sectional view showing one step of the manufacturing method of the present invention;

[0082] FIG. 66 is a sectional view showing one step of the manufacturing method of the present invention;

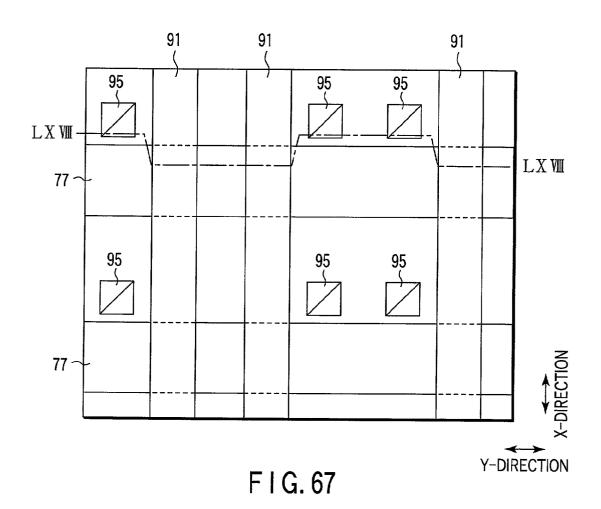

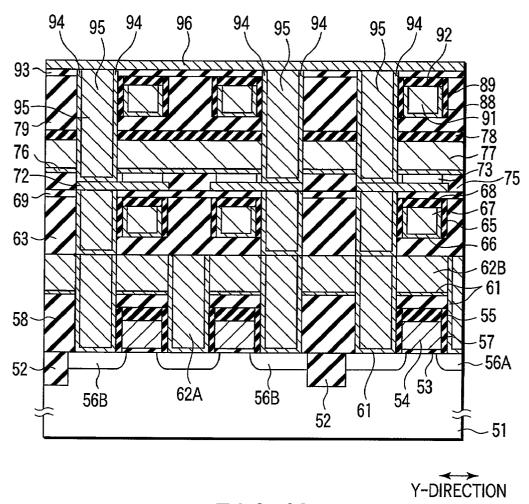

[0083] FIG. 67 is a plan view showing one step of the manufacturing method of the present invention;

[0084] FIG. 68 is a sectional view taken along a line LXVIII-LXVIII in FIG. 67;

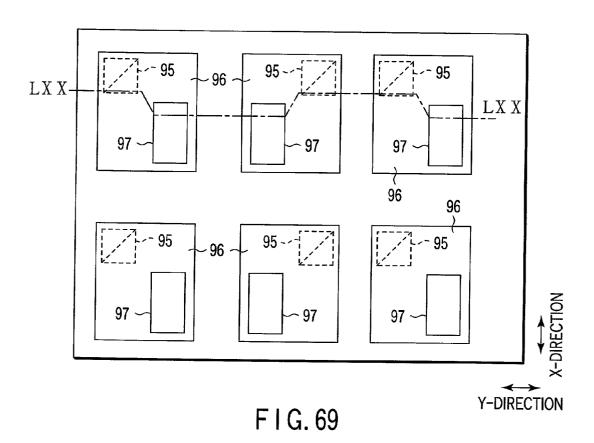

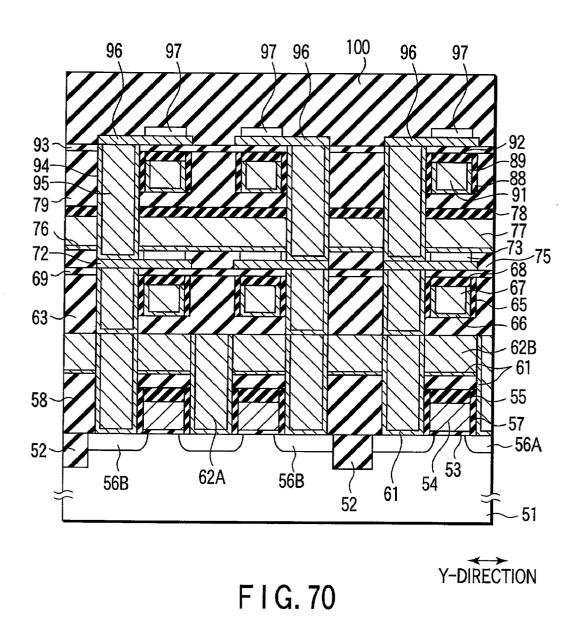

[0085] FIG. 69 is a plan view showing one step of the manufacturing method of the present invention;

[0086] FIG. 70 is a sectional view taken along a line LXX-LXX in FIG. 69;

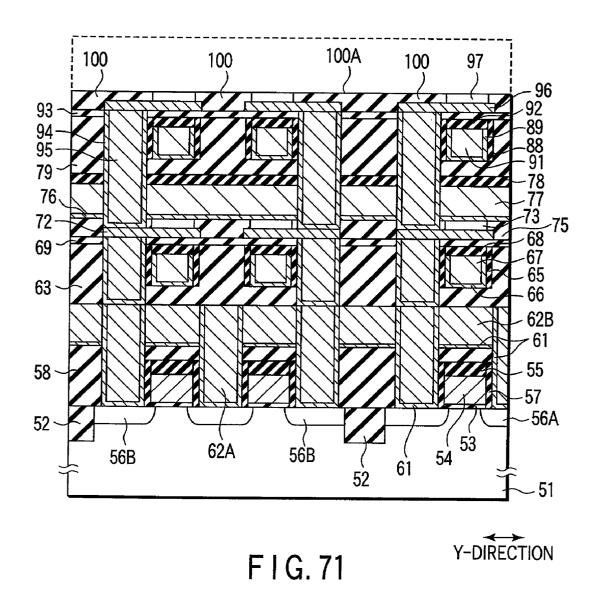

[0087] FIG. 71 is a sectional view showing one step of the manufacturing method of the present invention;

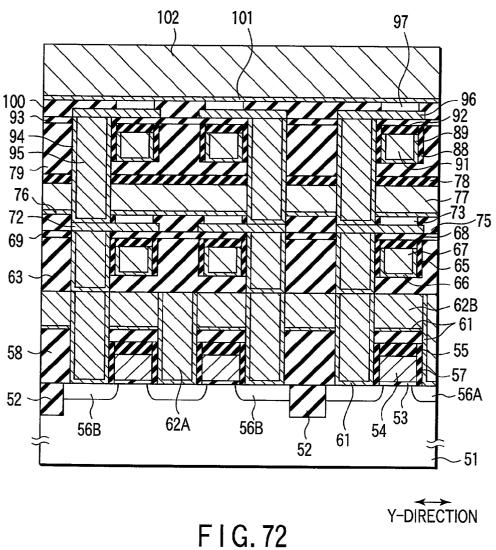

[0088] FIG. 72 is a sectional view showing one step of the manufacturing method of the present invention;

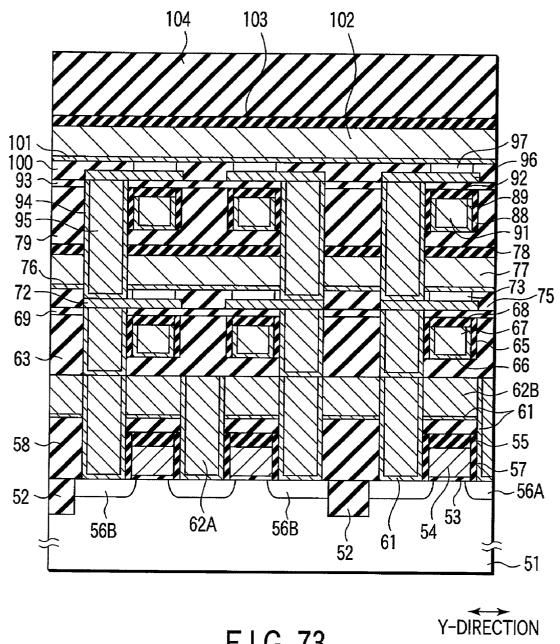

[0089] FIG. 73 is a sectional view showing one step of the manufacturing method of the present invention;

[0090] FIG. 74 is a sectional view showing one step of the manufacturing method of the present invention;

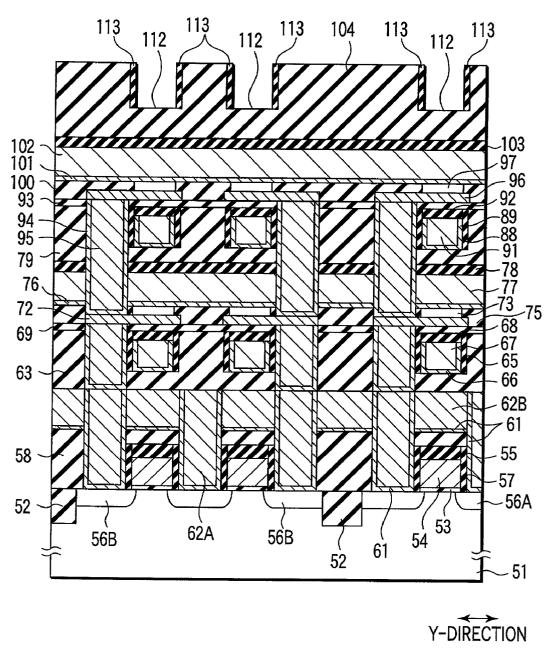

[0091] FIG. 75 is a sectional view showing one step of the manufacturing method of the present invention;

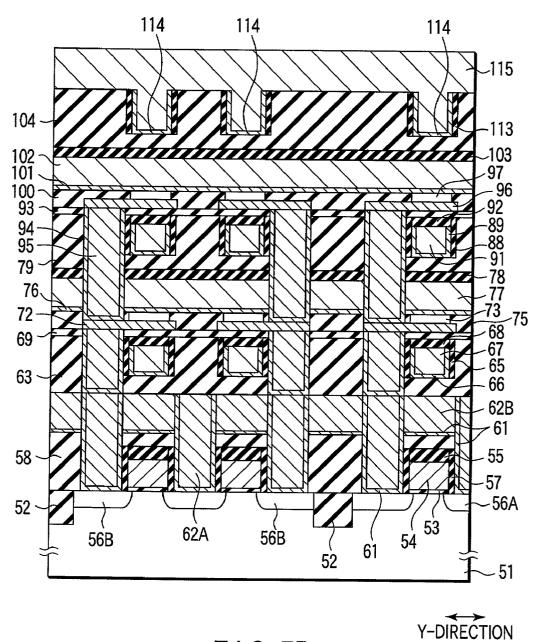

[0092] FIG. 76 is a sectional view showing one step of the manufacturing method of the present invention;

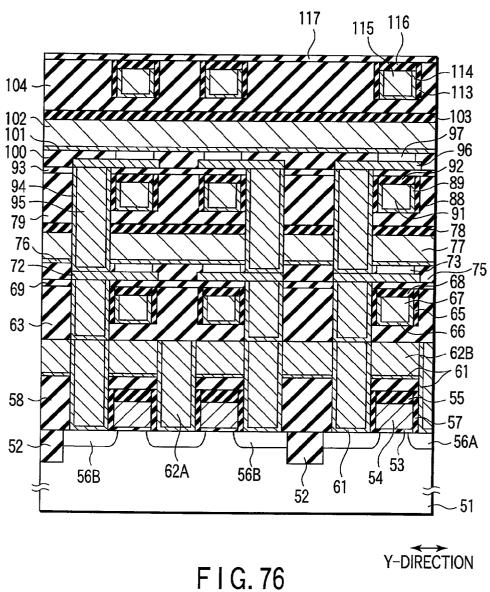

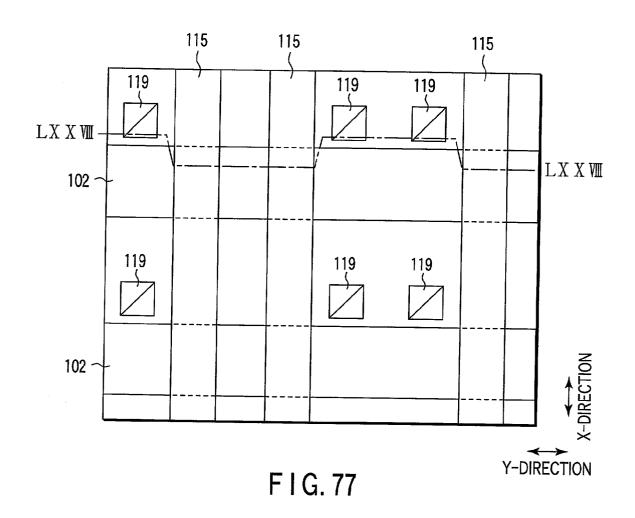

[0093] FIG. 77 is a plan view showing one step of the manufacturing method of the present invention;

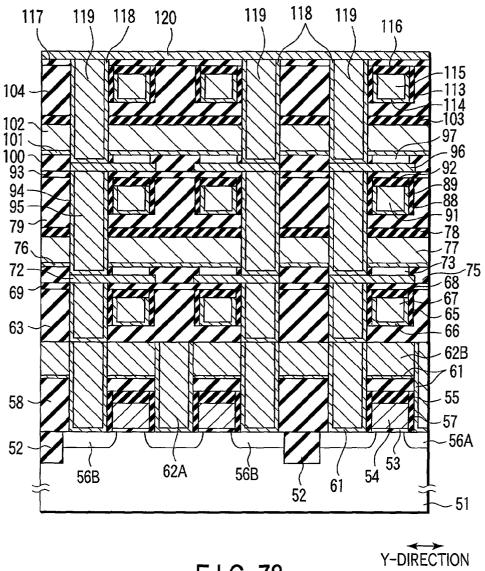

[0094] FIG. 78 is a sectional view taken along a line LXXVIII-LXXVIII in FIG. 77;

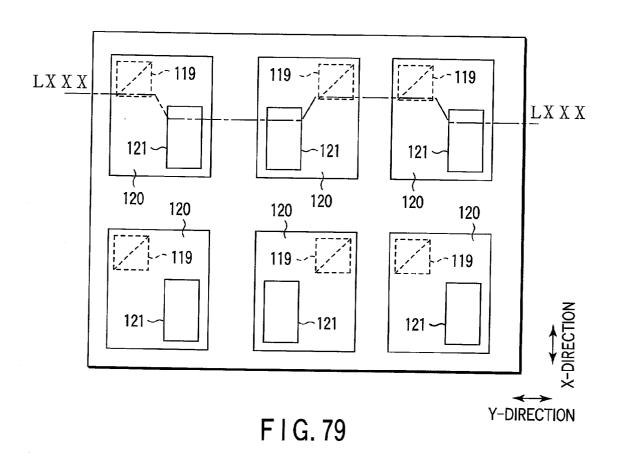

[0095] FIG. 79 is a plan view showing one step of the manufacturing method of the present invention;

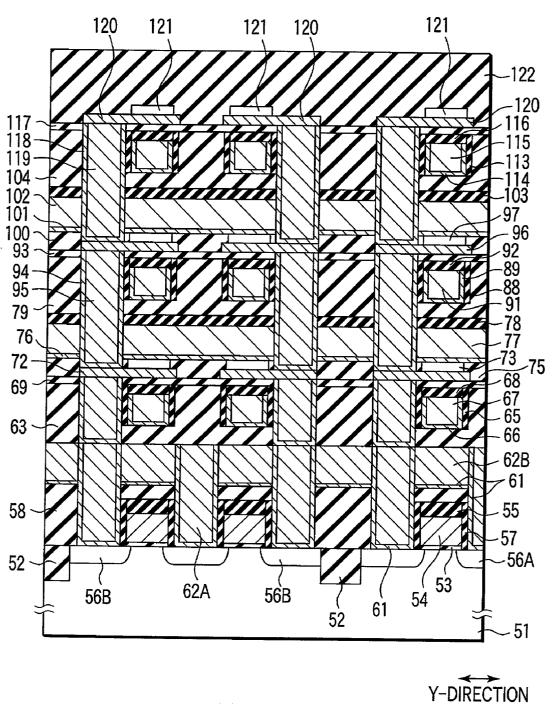

[0096] FIG. 80 is a sectional view taken along a line LXXX-LXXX in FIG. 79;

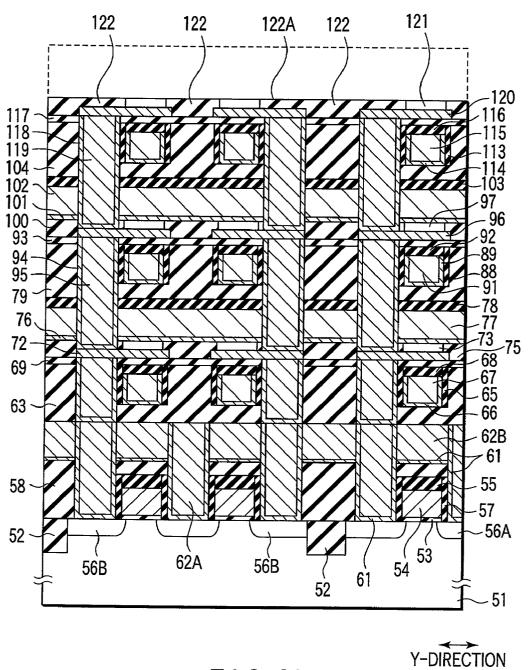

[0097] FIG. 81 is a sectional view showing one step of the manufacturing method of the present invention;

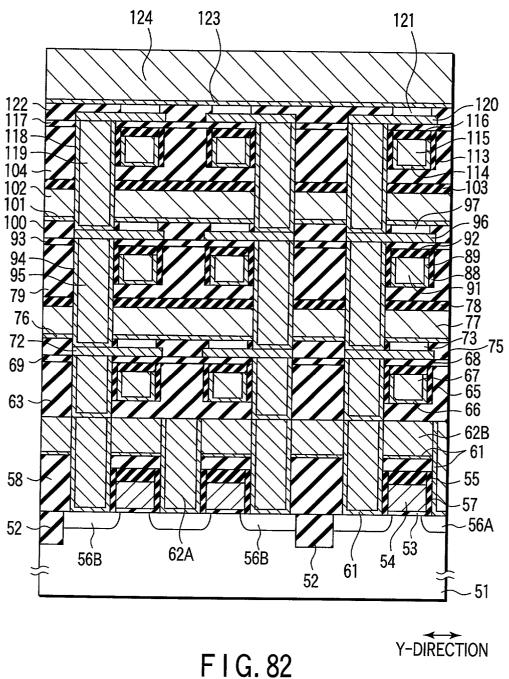

[0098] FIG. 82 is a sectional view showing one step of the manufacturing method of the present invention;

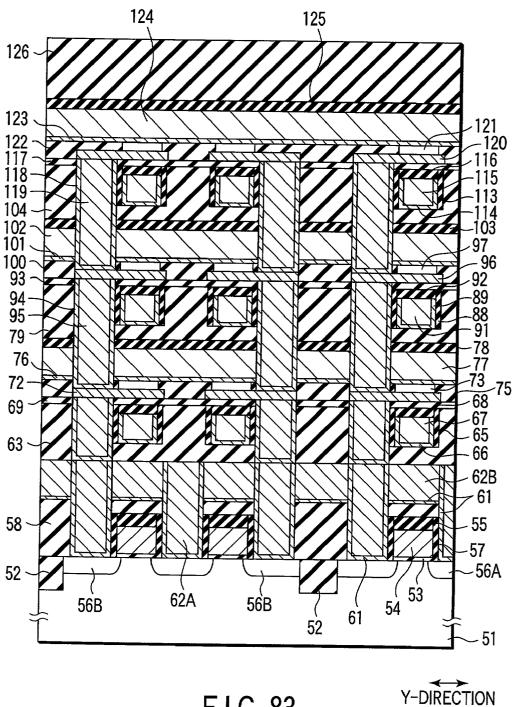

[0099] FIG. 83 is a sectional view showing one step of the manufacturing method of the present invention;

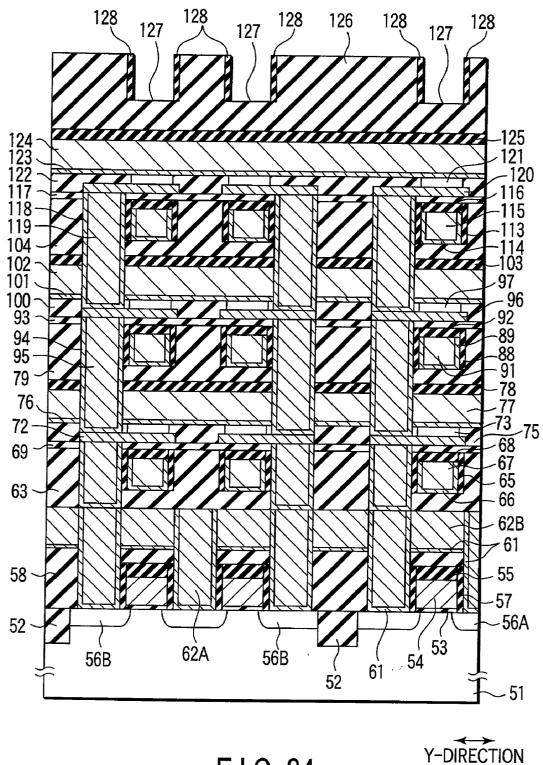

[0100] FIG. 84 is a sectional view showing one step of the manufacturing method of the present invention;

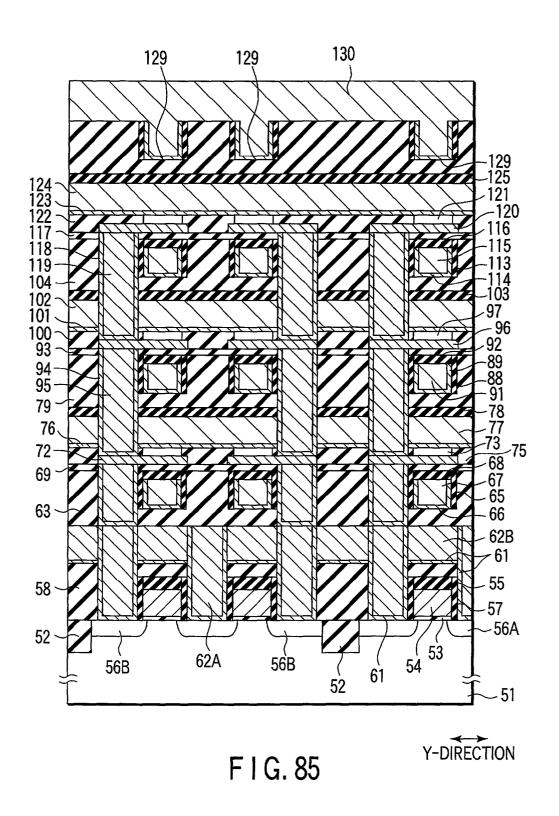

[0101] FIG. 85 is a sectional view showing one step of the manufacturing method of the present invention;

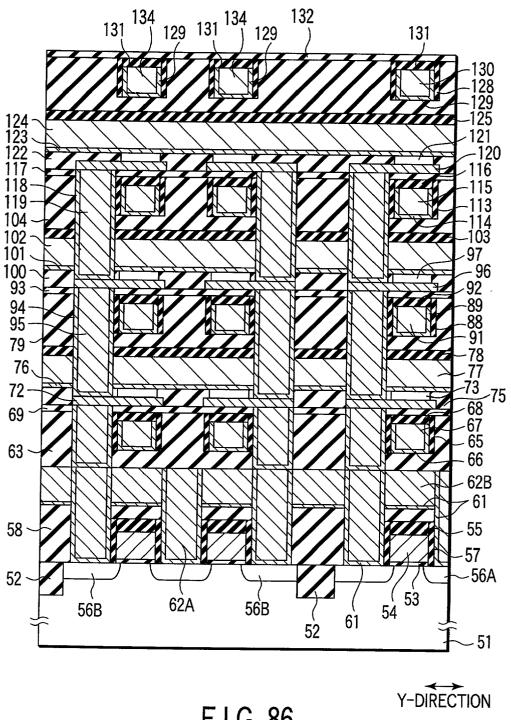

[0102] FIG. 86 is a sectional view showing one step of the manufacturing method of the present invention;

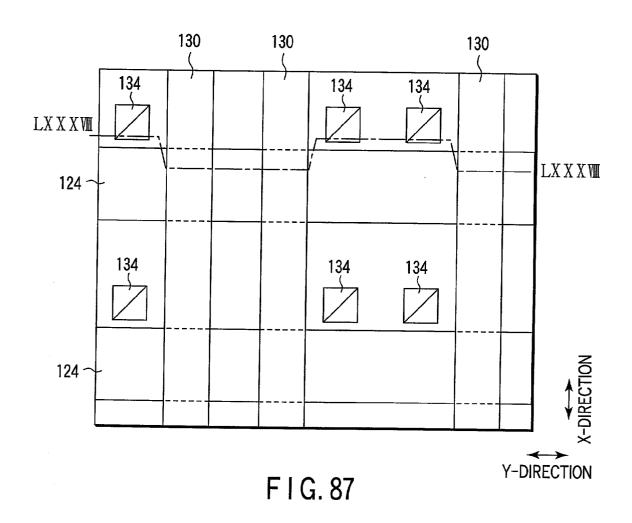

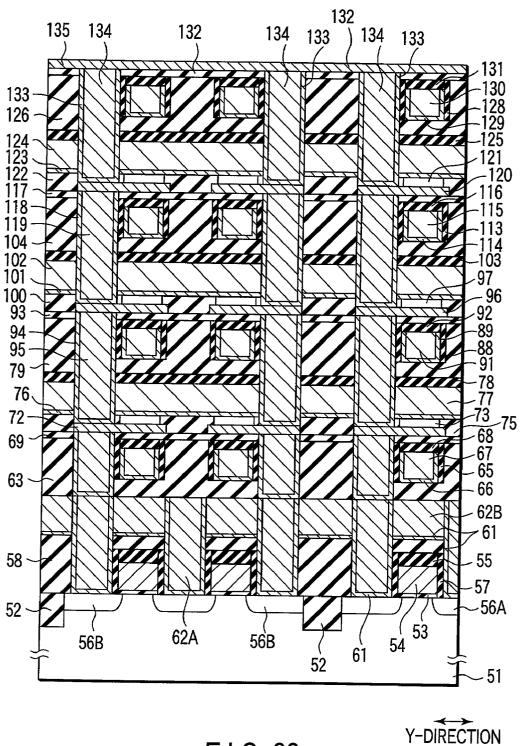

[0103] FIG. 87 is a plan view showing one step of the manufacturing method of the present invention;

[0104] FIG. 88 is a sectional view taken along a line LXXXVIII-LXXXVIII in FIG. 87;

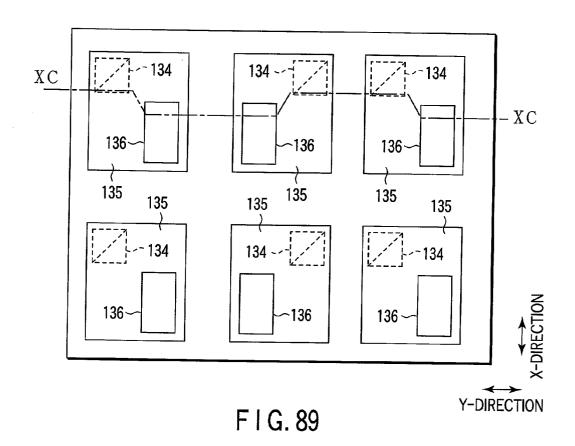

[0105] FIG. 89 is a plan view showing one step of the manufacturing method of the present invention;

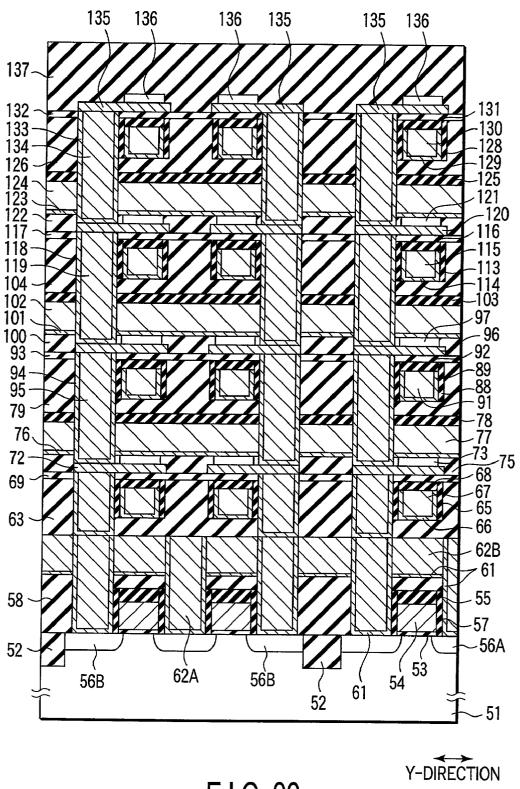

[0106] FIG. 90 is a sectional view taken along a line XL-XL in FIG. 90;

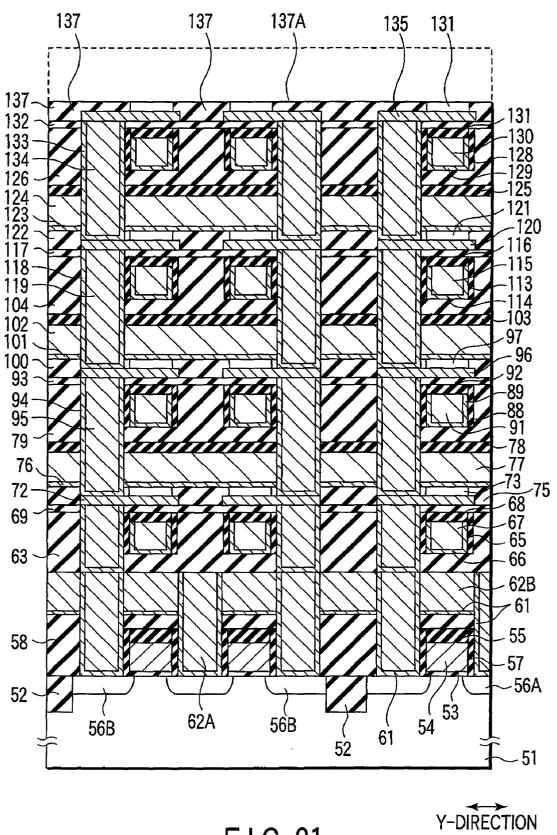

[0107] FIG. 91 is a sectional view showing one step of the manufacturing method of the present invention;

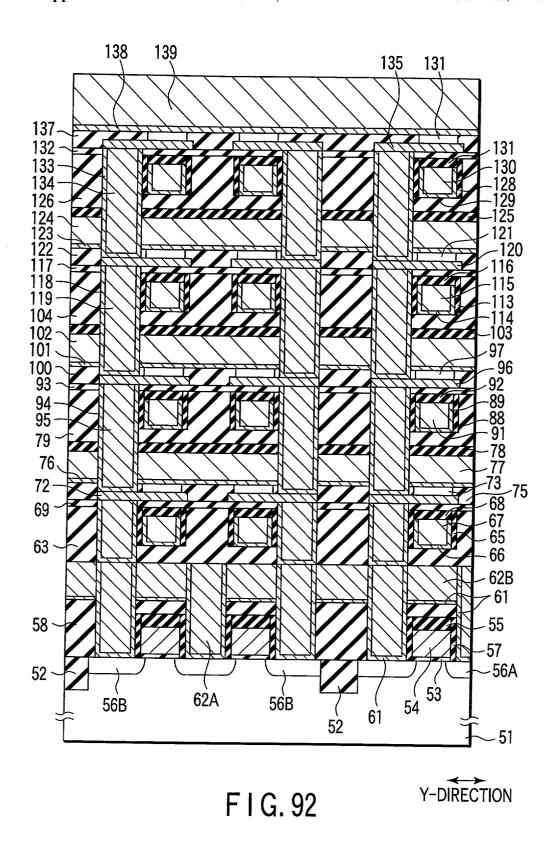

[0108] FIG. 92 is a sectional view showing one step of the manufacturing method of the present invention;

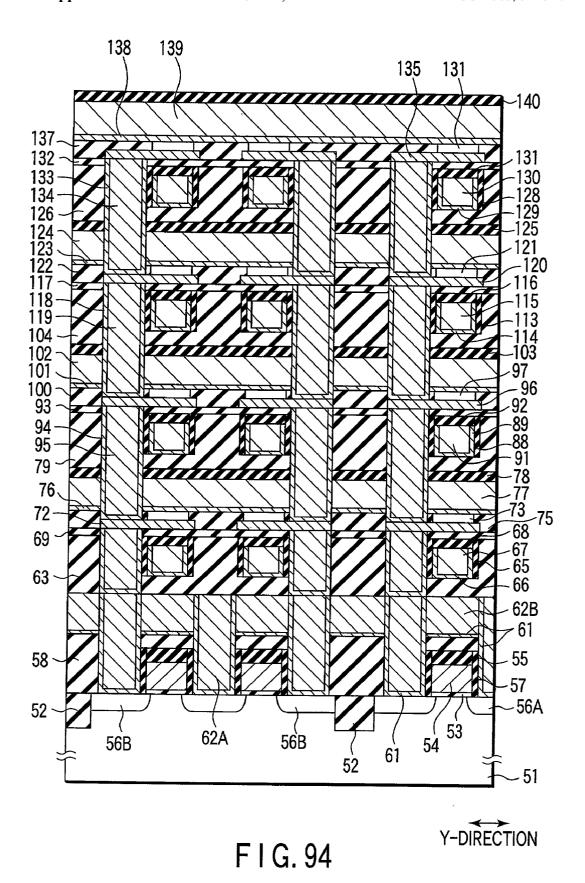

[0109] FIG. 93 is a plan view showing one step of the manufacturing method of the present invention;

[0110] FIG. 94 is a sectional view taken along a line XCIV-XCIV in FIG. 93;

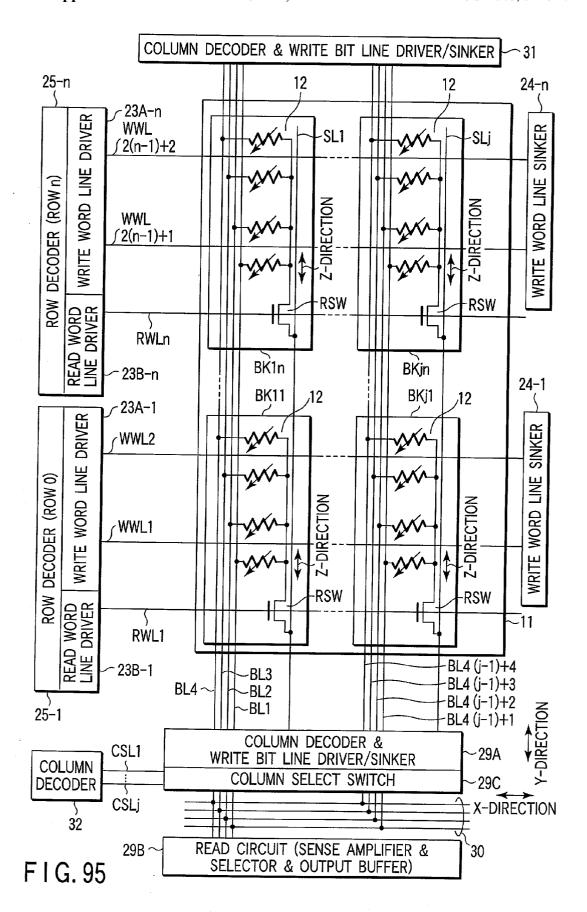

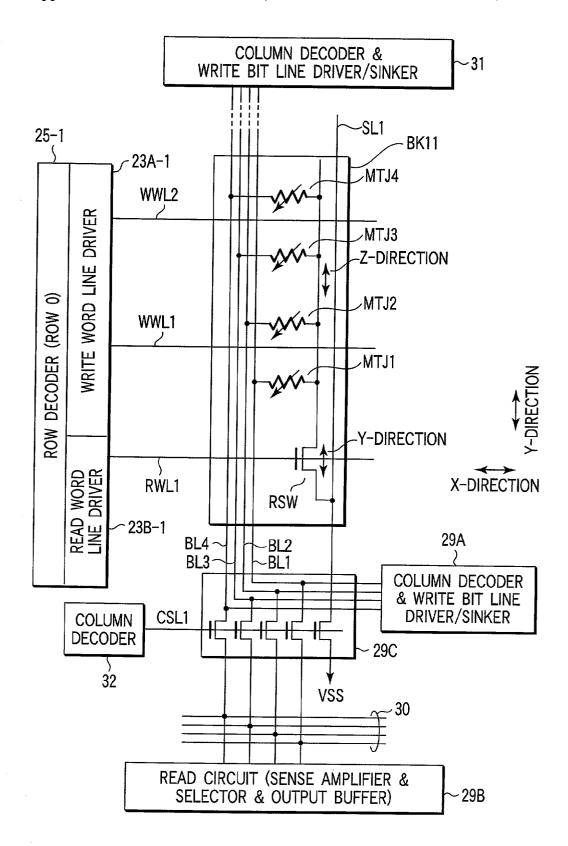

[0111] FIG. 95 is a circuit diagram showing a modification to Structural Example 1;

[0112] FIG. 96 is a circuit diagram showing a modification to Structural Example 1;

[0113] FIG. 97 is a sectional view showing a modification to Structural Example 1;

[0114] FIG. 98 is a sectional view showing a modification to Structural Example 1;

[0115] FIG. 99 is a sectional view showing a modification to Structural Example 1;

[0116] FIG. 100 is a sectional view showing a modification to Structural Example 1;

[0117] FIG. 101 is a circuit diagram showing a modification to Structural Example 2;

[0118] FIG. 102 is a sectional view showing a modification to Structural Example 2;

[0119] FIG. 103 is a sectional view showing a modification to Structural Example 2;

[0120] FIG. 104 is a sectional view showing a modification to Structural Example 1;

[0121] FIG. 105 is a sectional view showing a modification to Structural Example 1;

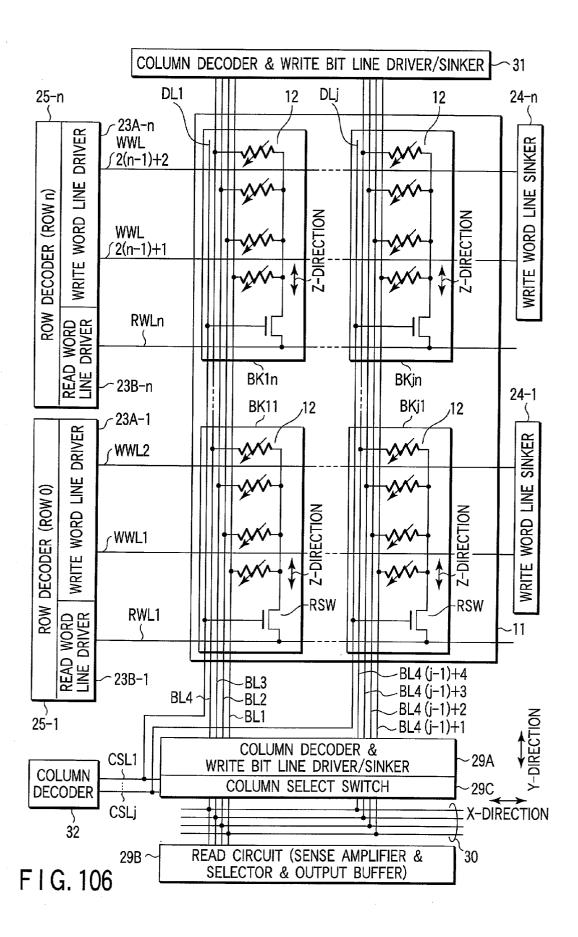

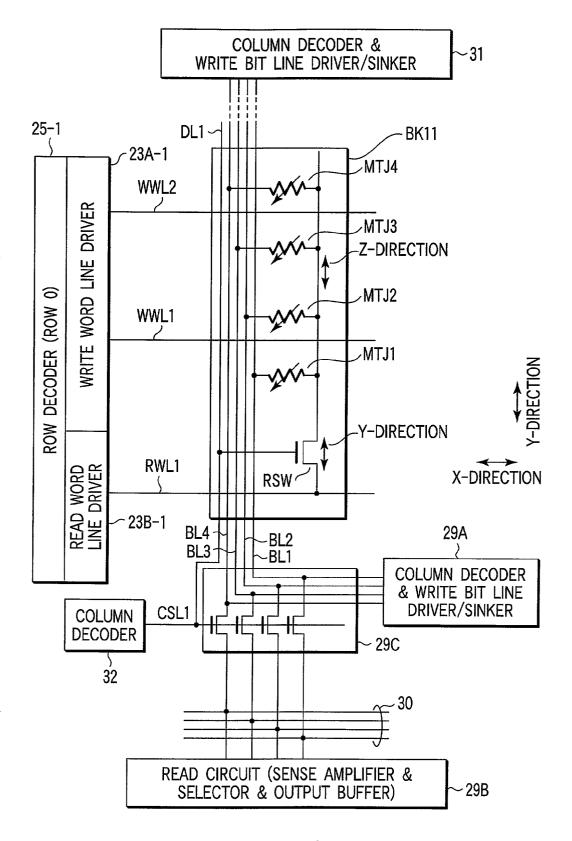

[0122] FIG. 106 is a circuit diagram showing a modification to Structural Example 3;

[0123] FIG. 107 is a circuit diagram showing a modification to Structural Example 3;

[0124] FIG. 108 is a sectional view showing a modification to Structural Example 3;

[0125] FIG. 109 is a sectional view showing a modification to Structural Example 3;

[0126] FIG. 110 is a sectional view showing a modification to Structural Example 3;

[0127] FIG. 111 is a sectional view showing a modification to Structural Example 3;

[0128] FIG. 112 is a circuit diagram showing a modification to Structural Example 4;

[0129] FIG. 113 is a sectional view showing a modification to Structural Example 4;

[0130] FIG. 114 is a sectional view showing a modification to Structural Example 4;

[0131] FIG. 115 is a sectional view showing a modification to Structural Example 4; and

[0132] FIG. 116 is a sectional view showing a modification to Structural Example 4.

# DETAILED DESCRIPTION OF THE INVENTION

[0133] A magnetic random access memory of an aspect of the present invention will be described below in detail with reference to the accompanying drawings.

[0134] 1. Cell Array Structure

[0135] First, a cell array structure of a magnetic random access memory of an aspect of the present invention will be described below in detail.

#### (1) STRUCTURAL EXAMPLE 1

[0136] In Structural Example 1, one read block is formed from four TMR elements. In this example, a case wherein the number of TMR elements in one read block is four will be described. However, the number of TMR elements in one read block is not limited to four and can be freely set.

[0137] (1) Circuit Structure

[0138] The circuit structure will be described first.

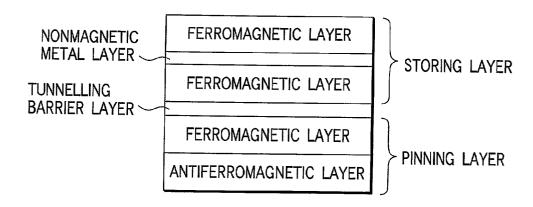

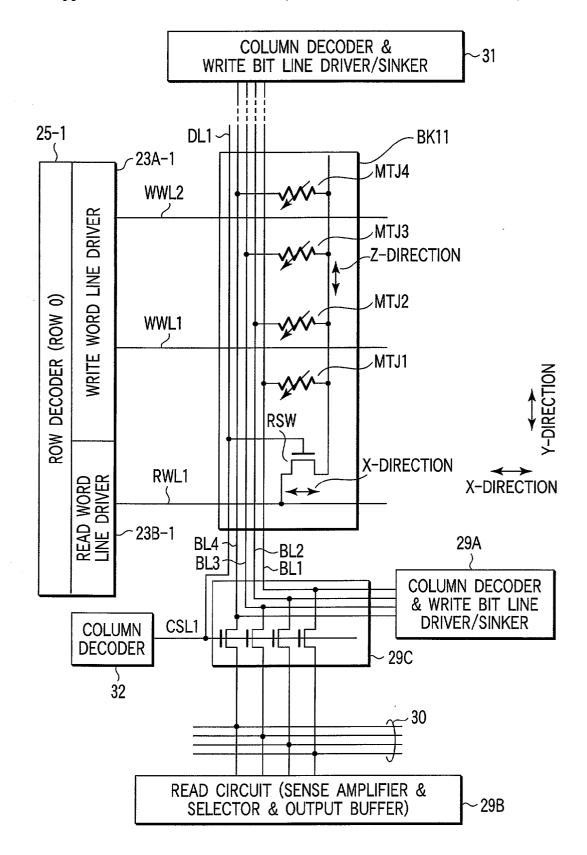

[0139] FIG. 1 shows main part of a magnetic random access memory as Structural Example 1 of the present invention. FIG. 2 shows an example of a column select switch shown in FIG. 1.

[0140] A memory cell array 11 has a plurality of TMR elements 12 arrayed in the X-, Y- and Z-directions. The Z-direction means a direction perpendicular to the X- and Y-directions, i.e., a direction perpendicular to the memory cell array plane.

[0141] In this example, the memory cell array 11 has a cell array structure formed from j TMR elements 12 arranged in the X-direction, n TMR elements 12 arranged in the Y-direction, and four TMR elements (MTJ1, MTJ2, MTJ3 and MTJ4) 12 stacked in the Z-direction.

[0142] In this example, the number of TMR elements 12 stacked in the Z-direction is four. However, the number of TMR elements is not particularly limited as long as the number is two or more.

[0143] The four TMR elements 12 stacked in the Z-direction construct one read block BKik (i=1, 2, ..., j, k=1, 2, ..., n). In fact, the four TMR elements 12 in the read block BKik overlap one another in the direction (Z-direction) perpendicular to the memory cell array plane.

[0144] In this example, one row is constructed by j read blocks BKik arranged in the X-direction. The memory cell array 11 has n rows. In addition, one column is constructed by n read blocks BKik arranged in the Y-direction. The memory cell array 11 has j columns.

[0145] One terminal of each of the four TMR elements 12 in the block BKik is commonly connected. The terminals are connected to a source line SLi (i=1, 2, ..., j) through a read select switch (block select switch or row select switch) RSW formed from, e.g., a MOS transistor. The source line SLi extends in the Y-direction. For example, one source line SLi is arranged in one column.

[0146] The source line SLi is connected to a ground point VSS through, e.g., a column select switch 29C formed from a MOS transistor.

[0147] In read operation, in the selected row, the read select switches RSW in the read blocks BKik are turned on. In the selected column, the column select switch 29C is turned on. For this reason, the potential of the source line SLi becomes the ground potential VSS. That is, a read current flows only to the TMR elements 12 in the read block BKik located at the intersection between the selected row and the selected column.

[0148] In the read mode, in an unselected column, the column select switch 29C is OFF. Hence, the other terminal of each TMR element 12 in the read blocks BKik in an unselected column is short-circuited.

[0149] In this case, if read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 in an unselected column have different potentials, they may influence the read operation. To prevent this, the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 in an unselected column are set at an equipotential level (e.g., ground potential).

[0150] In the read operation, the read select switches RSW in an unselected row are OFF. Hence, the other terminal of each TMR element 12 in the read blocks BKik in an unselected row is also short-circuited.

[0151] The short circuit between the TMR elements 12 in the read blocks BKik belonging to the selected column and unselected rows may influence the read operation of the TMR elements 12 in the selected read block BKik belonging to the selected row and column.

[0152] Hence, for example, as shown in FIG. 3, block select switches BSW each formed from a MOS transistor may be arranged in each read block BKik. The read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 may be electrically connected only to the TMR elements 12 in the selected read block BKik belonging to the selected row and column. In addition, the read current may be supplied only to these TMR elements.

[0153] The other terminal of each of the four TMR elements 12 in the read block BKik is independently connected to a corresponding one of the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4. Four read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 are arranged in one column in correspondence with four TMR elements 12 in one read block BKik.

[0154] The read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 extend in the Y-direction. One end of each read bit line is connected to a common data line 30 through the column select switch (MOS transistor) 29C. The common data line 30 is connected to a read circuit (including, e.g., a sense amplifier, selector, and output buffer) 29B.

[0155] A column select line signal CSLi (i=1, 2, ..., j) is input to the column select switch 29°C. A column decoder 32 outputs the column select line signal CSLi.

[0156] In this example, the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 also function as write bit lines.

[0157] That is, one end of each of the write/read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 is connected to a circuit block 29A including a column decoder and write bit line driver/sinker. The other end is connected to a circuit block 31 including a column decoder and write bit line driver/sinker.

[0158] In write operation, the circuit blocks 29A and 31 are set in an operative state. A write current flows to the write/read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 in accordance with write data in a direction toward the circuit block 29A or 31.

[0159] A plurality of (in this example, four) write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 that extend in the X-direction and are stacked in the Z-direction are arranged near the four TMR elements 12 of the read block BKik. Here, n indicates a row number  $(n=1, 2, \ldots)$

[0160] In this example, as for the write word lines extending in the X-direction, one write word line is arranged at one stage in one row. That is, one write word line corresponds to one TMR element in the selected read block BKik. In this case, the number of write word lines in one row extending in the X-direction is the same as the number of stages of the stacked TMR elements 12.

[0161] As shown in FIGS. 95 and 96, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films immediately under the TMR elements 12 or reducing the manufacturing cost.

[0162] The TMR element in the block and a detailed structure near it will be described in detail in the section about the device structure.

[0163] One end of each of the write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 is connected to a write word line driver 23A-n. The other end is connected to a write word line sinker 24-n.

[0164] The gate of the read select switch (MOS transistor) RSW is connected to a read word line RWLn (n=1, 2, ...) One read word line RWLn is arranged in one row, i.e., shared by the plurality of blocks BKik arranged in the X-direction.

[0165] For example, when one column has four blocks, the number of read word lines RWLn is four. Each read word line RWLn extends in the X-direction. One end of the read word line RWLn is connected to a read word line driver 23B-n.

[0166] When one read block BKik has a circuit structure shown in FIG. 3, the read word line RWLn is also connected to the gates of the block select switches BSW (MOS transistors).

[0167] That is, when the circuit structure shown in FIG. 3 is employed, only the read select switches RSW and block select switches BSW in the blocks BKik on the selected row, i.e., the row for which the potential of the read word line RWLn is at "H" level, are turned on.

[0168] In the write operation, a row decoder 25-n selects one of the plurality of rows on the basis of row address signals. The write word line driver 23A-n supplies write currents to the write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 in the selected row. The write currents are absorbed by the write word line sinker 24-n.

[0169] In the read operation, the row decoder 25-n selects one of the plurality of rows on the basis of row address signals. The read word line driver 23B-n supplies a read voltage (="H") to the read word line RWLn in the selected

[0170] In the magnetic random access memory of the present invention, one column is constructed by a plurality of read blocks. A plurality of TMR elements in each read block are connected to different read bit lines, respectively. Hence, data of the plurality of TMR elements in the read block can be read at once by one read step.

[0171] The plurality of TMR elements in each read block are stacked to form a plurality of stages on a semiconductor substrate. Each read bit line also functions as a write bit line.

That is, since no interconnection that functions only as a write bit line need be formed in the cell array, the cell array structure can be simplified.

[0172] In each read block, the read select switch RSW and block select switches (FIG. 3) are arranged. A column select switch is connected between a source line and the ground point. In the read operation, the TMR elements in an unselected read block do not influence the read operation. Hence, the read operation stabilizes.

[0173] ② Device Structure

[0174] The device structure will be described next.

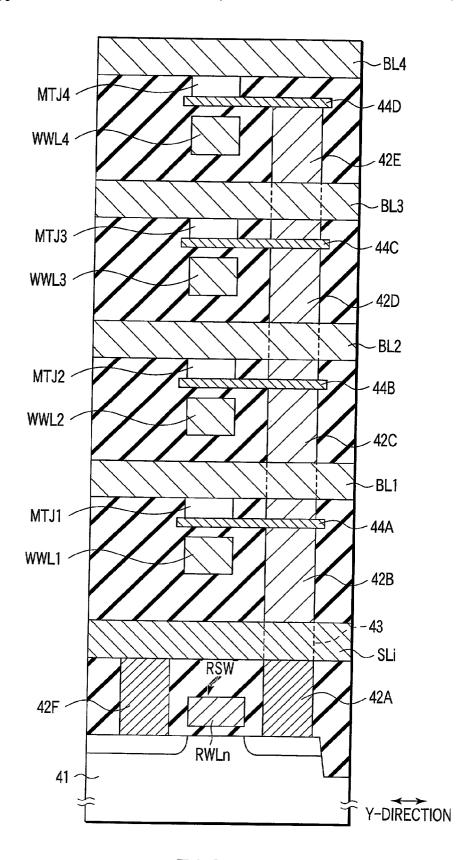

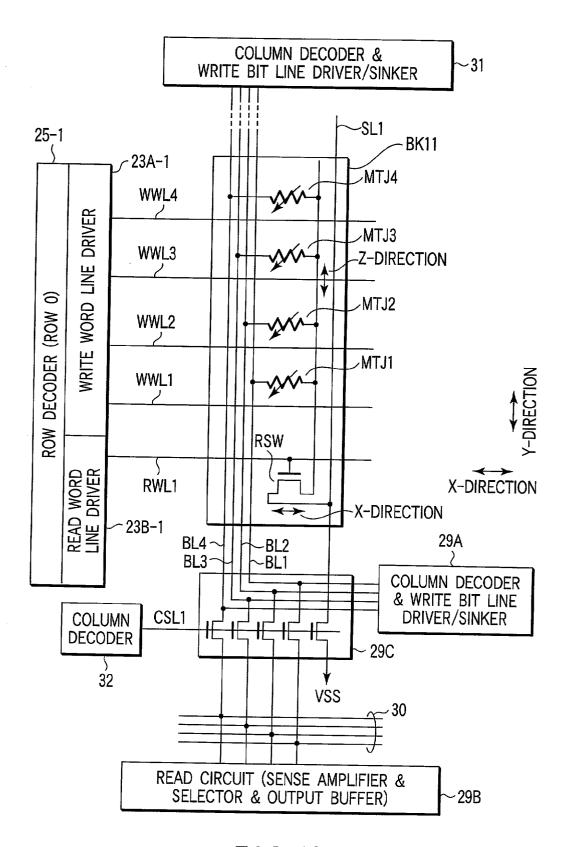

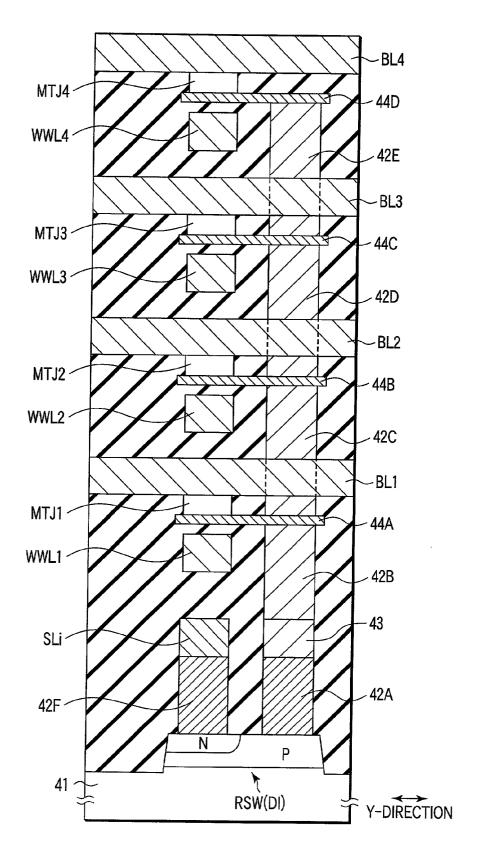

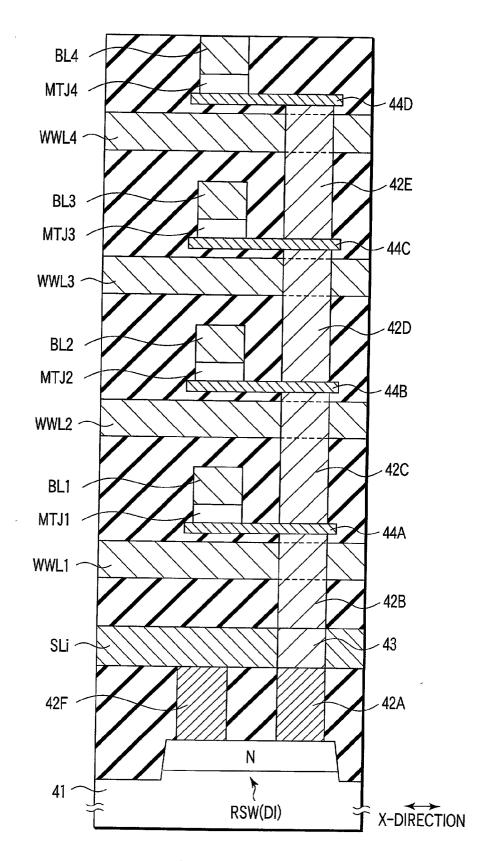

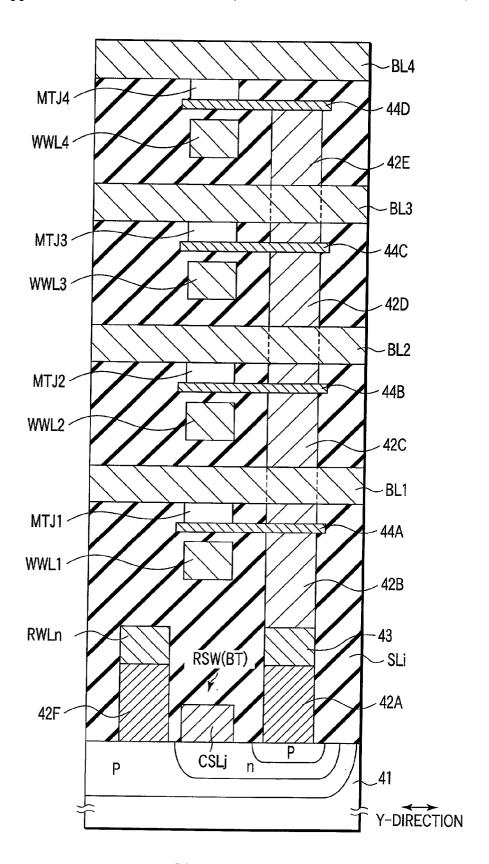

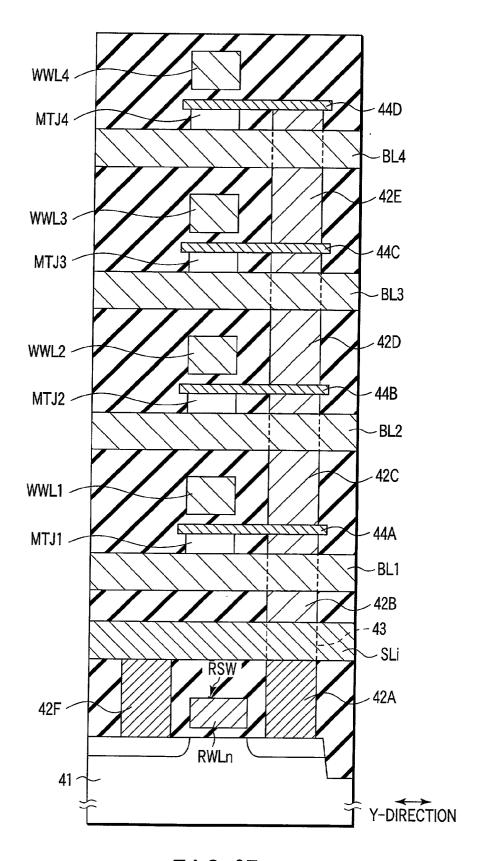

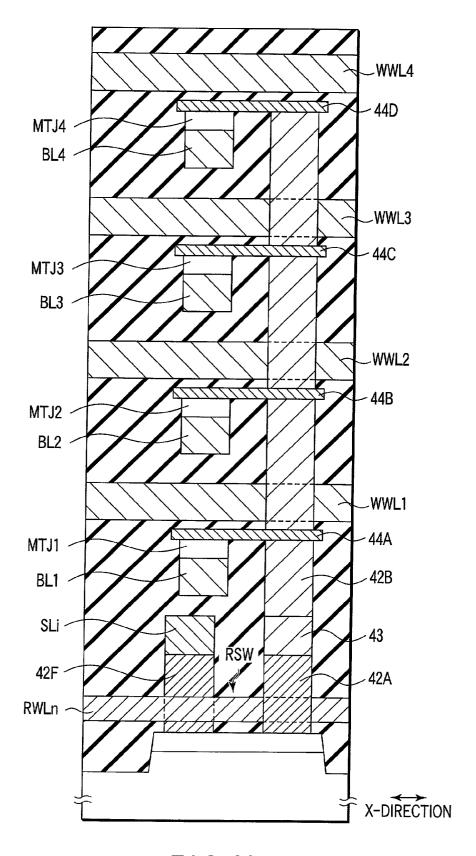

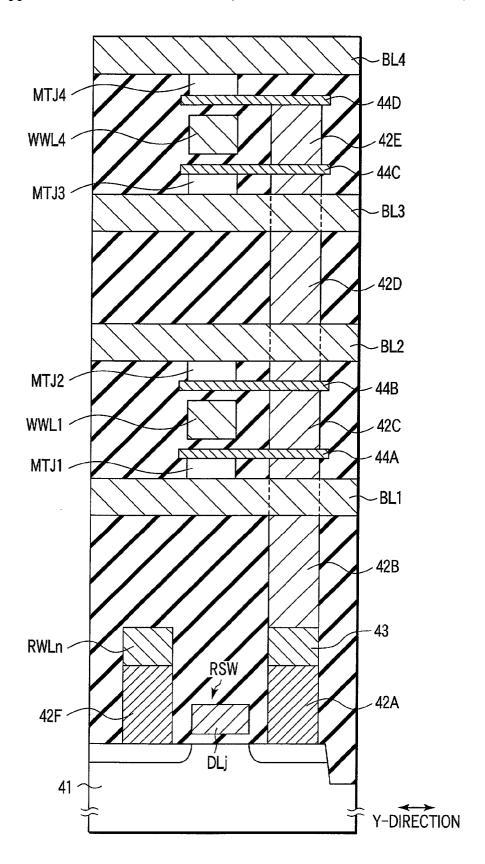

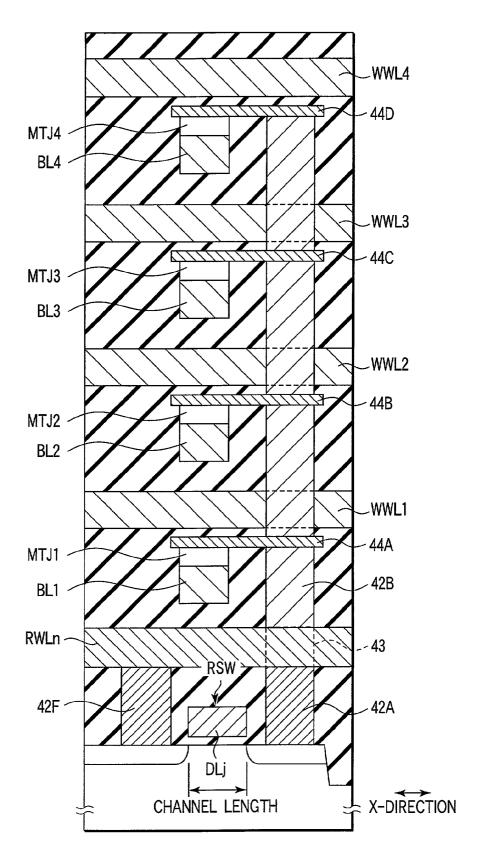

[0175] FIGS. 4 and 5 show the device structure of one block of the magnetic random access memory as Structural Example 1 of the present invention.

[0176] FIG. 4 shows the Y-direction section of one block of the magnetic random access memory. FIG. 5 shows the X-direction section of one block of the magnetic random access memory. The same reference numerals as in FIGS. 1 to 3 denote the same elements in FIGS. 4 and 5 to show the correspondence between the elements.

[0177] The read select switch (MOS transistor) RSW is arranged on the surface region of a semiconductor substrate 41. The source of the read select switch RSW is connected to the source line SLi through a contact plug 42F. The source line SLi extends straight, e.g., in the Y-direction and is connected to the ground supply through a column select switch arranged at the peripheral portion of the memory cell array region.

[0178] The gate of the read select switch (MOS transistor) RSW serves as the read word line RWLn. The read word line RWLn extends in the X-direction. The four TMR elements (MTJ (Magnetic Tunnel Junction) elements) MTJ1, MTJ2, MTJ3 and MTJ4 are stacked at a plurality of stages on the read select switch RSW.

[0179] One end (in this example, the lower end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is connected to a corresponding one of lower electrodes 44A, 44B, 44C and 44D. Contact plugs 42A, 42B, 42C, 42D and 42E and intermediate layer 43 electrically connect the lower electrodes 44A, 44B, 44C and 44D to each other and also electrically connect them to the drain of the read select switch RSW.

[0180] The other end (in this example, the upper end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is electrically connected to a corresponding one of read/write bit lines BL1, BL2, BL3 and BL4. The read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction.

[0181] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are independently connected to the read/write bit lines BL1, BL2, BL3 and BL4, respectively. That is, four read/write bit lines BL1, BL2, BL3 and BL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0182] Write word lines WWL1, WWL2, WWL3 and WWL4 are arranged immediately under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 and near them. The write word lines WWL1, WWL2, WWL3 and WWL4 extend in the X-direction.

[0183] In this example, four write word lines WWL1, WWL2, WWL3 and WWL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0184] In this example, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction are arranged on the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction are arranged below the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0185] However, the positional relationship of the read/write bit lines BL1, BL2, BL3 and BL4 and write word lines WWL1, WWL2, WWL3 and WWL4 with respect to the TMR elements is not limited to this.

[0186] For example, as shown in FIGS. 97 and 98, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction may be arranged under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction may be arranged above the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0187] As shown in FIGS. 99 and 100, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films right under the TMR elements 12 or reducing the manufacturing cost.

[0188] According to such a device structure, the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are connected to the different read/write bit lines BL1, BL2, BL3 and BL4, respectively. Hence, data of the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block can be read at once by one read step.

[0189] The plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are stacked at a plurality of stages on the semiconductor substrate 41. In addition, only the read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. For this reason, even when the number of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is increased, the cell array structure is not complicated.

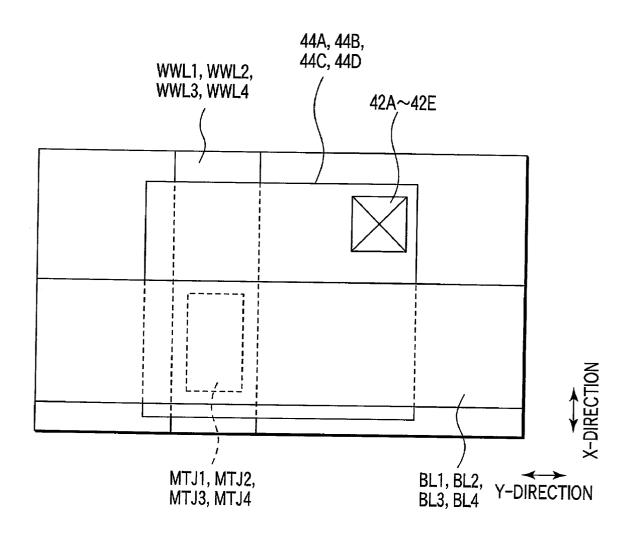

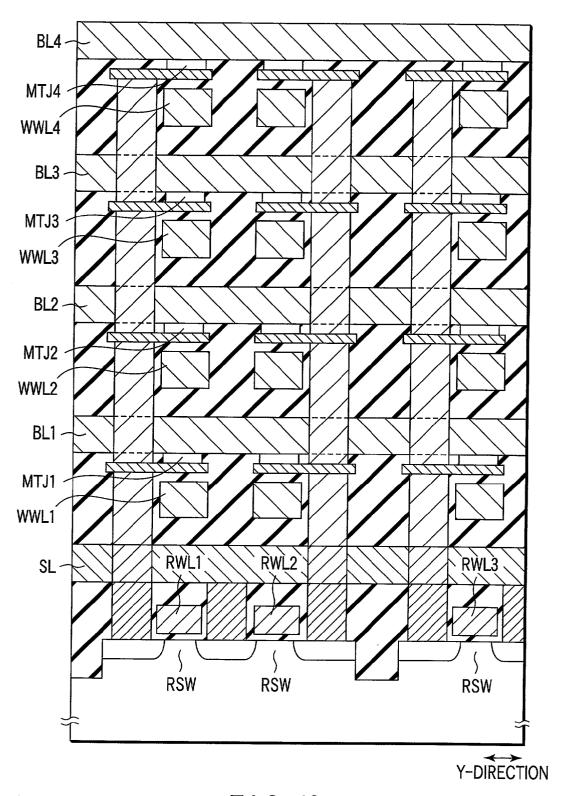

[0190] FIG. 6 shows the positional relationship between the TMR elements and the write word lines and read/write bit lines in the device structure shown in FIGS. 4 and 5.

[0191] In the device structure shown in FIGS. 4 and 5, the lower electrodes 44A, 44B, 44C and 44D, write word lines WWL1, WWL2, WWL3 and WWL4, and read/write bit lines BL1, BL2, BL3 and BL4 are arranged at the respective stages of the plurality of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0192] The layouts of, e.g., the stages of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are set to be identical.

[0193] Each of the lower electrodes 44A, 44B, 44C and 44D has, e.g., a rectangular pattern. They have contact regions corresponding to the contact plugs 42A to 42E at partial portions. The lower electrodes 44A, 44B, 44C and 44D have the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 at the remaining portions.

[0194] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are arranged at the intersections between the write word lines WWL1, WWL2, WWL3 and WWL4 and the read/write bit lines BL1, BL2, BL3 and BL4.

[0195] (3) Structural Example of TMR Element

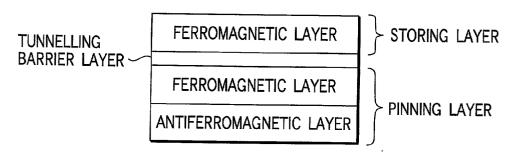

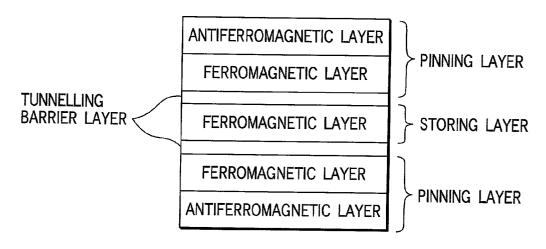

[0196] FIGS. 7 to 9 show structural examples of the TMR element.

[0197] The TMR element shown in FIG. 7 has the most basic structure having two ferromagnetic layers and a tunneling barrier layer sandwiched between these layers.

[0198] An anti-ferromagnetic layer for fixing the magnetizing direction is added to a fixed layer (pinning layer) of the two ferromagnetic layers, in which the magnetizing direction is fixed. The magnetizing direction in a free layer (storing layer) of the two ferromagnetic layers, in which the magnetizing direction can be freely changed, is determined by a synthesized magnetic field formed by a write word line and write bit line.

[0199] The TMR element shown in FIG. 8 has two tunneling barrier layers in it to make the bias voltage higher than in the TMR element shown in FIG. 7.

[0200] The TMR element shown in FIG. 8 can be regarded to have a structure (double junction structure) in which two TMR elements shown in FIG. 7 are connected in series

[0201] In this example, the TMR element has three ferromagnetic layers. Tunneling barrier layers are inserted between the ferromagnetic layers. Antiferromagnetic layers are added to the two ferromagnetic layers (pinning layers) at two ends. The middle layer in the three ferromagnetic layers serves as a free layer (storing layer) in which the magnetizing direction can be freely changed.

[0202] The TMR element shown in FIG. 9 can easily close lines of magnetic force in the ferromagnetic layer serving as a storing layer, as compared to the TMR element shown in FIG. 7.

[0203] For the TMR element of this example, it can be regarded that the storing layer of the TMR element shown in FIG. 7 is replaced with a storing layer formed from two ferromagnetic layers and a nonmagnetic metal layer (e.g., an aluminum layer) sandwiched between those layers.

[0204] When the storing layer of the TMR element has a three-layered structure made of two ferromagnetic layers and a nonmagnetic metal layer sandwiched between these layers, lines of magnetic force in the two ferromagnetic layers of the storing layer readily close. That is, since any anti-magnetic field component in the two ferromagnetic layers of the storing layer can be prevented, the MR ratio can be improved.

[0205] The structural examples of the TMR element have been described above. In the present invention (circuit structure, device structure, read operation mechanism, read circuit, and manufacturing method), the structure of the TMR element is not particularly limited. The above-described three structural examples are mere representative examples of the TMR element structure.

## (2) STRUCTURAL EXAMPLE 2

[0206] Structural Example 2 is a modification to Structural Example 1. A characteristic feature of Structural Example 2, which is different from Structural Example 1, is the direction of a read select switch. That is, in Structural Example 2, the read select switch of Structural Example 1 is rotated by 90°.

[0207] (1) Circuit Structure

[0208] The circuit structure will be described first.

[0209] FIG. 10 shows main part of a magnetic random access memory as Structural Example 2 of the present invention. The circuit diagram of FIG. 10 corresponds to that of FIG. 2. The outline of the memory cell array and its peripheral portion in Structural Example 2 is the same as in FIG. 1.

[0210] One terminal of each of four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in a block BK11 is connected to a source line SL1 through a read select switch (block select switch or row select switch) RSW formed from, e.g., a MOS transistor.

[0211] The line that connects the source and drain of the read select switch RSW is parallel to the X-direction. That is, the channel length of the read select switch RSW is the X-direction length of the channel of the read select switch RSW. The channel width is the Y-direction width of the channel of the read select switch RSW.

[0212] The gate of the read select switch RSW extends in the Y-direction and is connected, at a predetermined portion, to a read word line RWL1 that extends in the X-direction.

[0213] The source line SL1 extends in the Y-direction. For example, one source line is arranged in one column. The source line SL1 is connected to the ground supply through a column select switch 29C formed from, e.g., a MOS transistor.

[0214] Assume that the read block BK11 is selected in read operation. At this time, the read select switch RSW in the read block BK11 is turned on. In addition, the column select switch 29C is turned on. For this reason, the potential of the source line SL1 changes to the ground potential. That is, a read current flows to the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11.

[0215] The other terminal of each of the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11 is independently connected to a corresponding one of read bit lines BL1, BL2, BL3 and BL4. That is, four read bit lines BL1, BL2, BL3 and BL4 are arranged in correspondence with the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11.

[0216] The read bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. One end of each read bit line is connected to a common data line 30 through the column select switch (MOS transistor) 29C. The common data line 30 is connected to a read circuit (including, e.g., a sense amplifier, selector and output buffer) 29B.

[0217] A column select line signal CSL1 is input to the column select switch 29C. A column decoder 32 outputs the column select line signal CSL1.

[0218] In this example, the read bit lines BL1, BL2, BL3 and BL4 also function as write bit lines.

[0219] That is, one end of each of the read/write bit lines BL1, BL2, BL3 and BL4 is connected to a circuit block 29A including a column decoder and write bit line driver/sinker. The other end is connected to a circuit block 31 including a column decoder and write bit line driver/sinker.

[0220] In write operation, the circuit blocks 29A and 31 are set in an operative state. A write current flows to the read/write bit lines BL1, BL2, BL3 and BL4 in accordance with write data in a direction toward the circuit block 29A or 31.

[0221] A plurality of (in this example, four) write word lines WWL1, WWL2, WWL3 and WWL4 that extend in the X-direction and are stacked in the Z-direction are arranged near the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 of the read block BK11.

[0222] In this example, as for the write word lines extending in the X-direction, one write word line is arranged at one stage in one row. That is, one write word line corresponds to one TMR element in the read block BK11. In this case, the number of write word lines in one row extending in the X-direction is the same as the number of stages of the stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0223] As shown in FIG. 101, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films immediately under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 or reducing the manufacturing cost.

[0224] One end of each of the write word lines WWL1, WWL2, WWL3 and WWL4 is connected to a write word line driver 23A-n. The other end is connected to a write word line sinker 24-n.

[0225] The gate of the read select switch (MOS transistor) RSW is connected to the read word line RWL1. One read word line RWL1 is arranged in one row, i.e., shared by the plurality of blocks arranged in the X-direction.

[0226] In the write operation, a row decoder 25-1 selects one of the plurality of rows on the basis of row address signals. The write word line driver 23A-n supplies write currents to the write word lines WWL1, WWL2, WWL3 and WWL4 in the selected row. The write currents are absorbed by the write word line sinker.

[0227] In the read operation, the row decoder 25-1 selects one of the plurality of rows on the basis of row address signals. A read word line driver 23B-1 supplies a read voltage (="H") to the read word line RWL1 in the selected row.

[0228] In the magnetic random access memory of the present invention, one column is constructed by a plurality of read blocks. A plurality of TMR elements in each read block are connected to different read bit lines, respectively. Hence, data of the plurality of TMR elements in the read block can be read at once by one read step.

[0229] The plurality of TMR elements in each read block are stacked to form a plurality of stages on a semiconductor substrate. Each read bit line also functions as a write bit line. That is, since no interconnection that functions only as a write bit line need be formed in the cell array, the cell array structure can be simplified.

[0230] In each read block, the read select switch RSW is arranged. A column select switch is connected between a source line and the ground line. In the read operation, the TMR elements in an unselected read block rarely influence the read operation. Hence, the read operation stabilizes.

[0231] (2) Device Structure

[0232] The device structure will be described next.

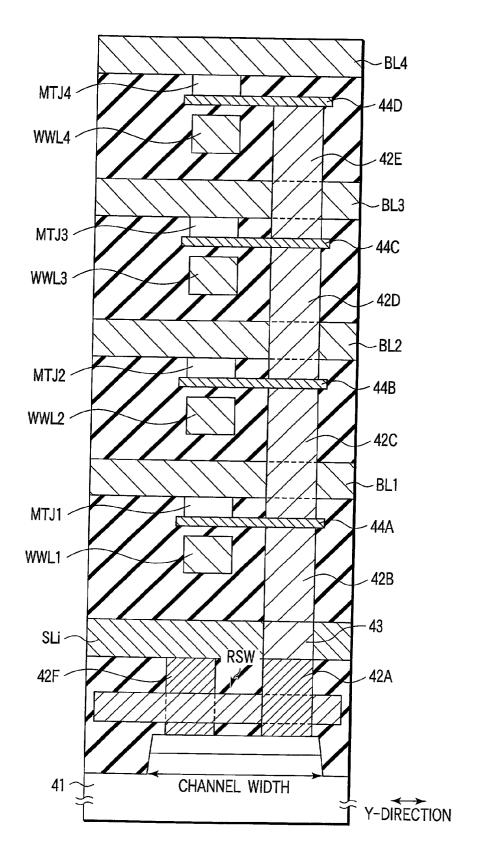

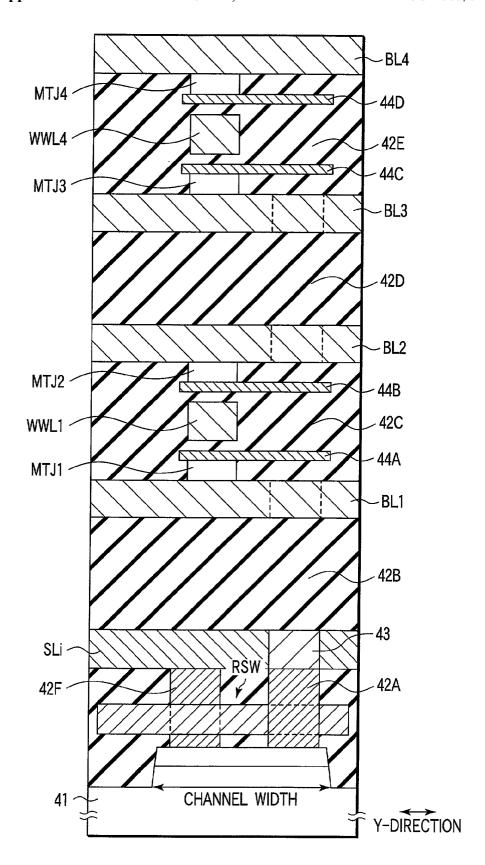

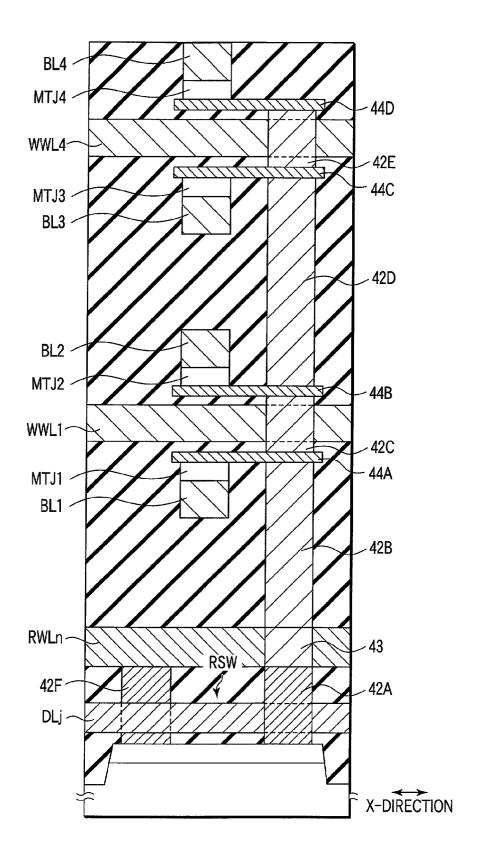

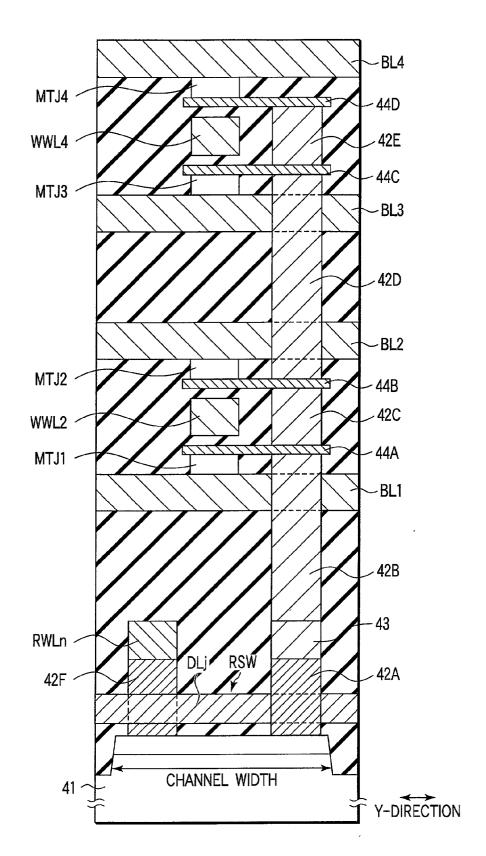

[0233] FIGS. 11 and 12 show the device structure of one block of the magnetic random access memory as Structural Example 2 of the present invention.

[0234] FIG. 11 shows the Y-direction section of one block of the magnetic random access memory. FIG. 12 shows the X-direction section of one block of the magnetic random access memory. The same reference numerals as in FIG. 9 denote the same elements in FIGS. 11 and 12 to show the correspondence between the elements.

[0235] The read select switch (MOS transistor) RSW is arranged on the surface region of a semiconductor substrate 41. The source of the read select switch RSW is connected to the source line SLi through a contact plug 42F. The source line SLi extends straight, e.g., in the Y-direction and is connected to the ground supply through a column select switch arranged at the peripheral portion of the memory cell array region.

[0236] The gate of the read select switch (MOS transistor) RSW serves as the read word line RWLn. The read word line RWLn extends in the X-direction. The four TMR elements (MTJ (Magnetic Tunnel Junction) elements) MTJ1, MTJ2, MTJ3 and MTJ4 are stacked at a plurality of stages on the read select switch RSW.

[0237] One end (in this example, the lower end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is connected to a corresponding one of lower electrodes 44A, 44B, 44C and 44D. Contact plugs 42A, 42B, 42C, 42D and 42E and intermediate layer 43 electrically connect the lower electrodes 44A, 44B, 44C and 44D to each other and also electrically connect them to the drain of the read select switch RSW.

[0238] The other end (in this example, the upper end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is electrically connected to a corresponding one of the read/write bit lines BL1, BL2, BL3 and BL4. The read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction.

[0239] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are independently connected to the read/write bit lines BL1, BL2, BL3 and BL4, respectively. That is, four read/write bit lines BL1, BL2, BL3 and BL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0240] The write word lines WWL1, WWL2, WWL3 and WWL4 are arranged right under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 and near them. The write word lines WWL1, WWL2, WWL3 and WWL4 extend in the X-direction

[0241] In this example, four write word lines WWL1, WWL2, WWL3 and WWL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0242] In this example, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction are arranged on the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction are arranged below the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0243] However, the positional relationship of the read/write bit lines BL1, BL2, BL3 and BL4 and write word lines WWL1, WWL2, WWL3 and WWL4 with respect to the TMR elements is not limited to this.

[0244] For example, as shown in FIGS. 102 and 103, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction may be arranged under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction may be arranged above the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0245] As shown in FIGS. 104 and 105, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films immediately under the TMR elements 12 or reducing the manufacturing cost.

[0246] According to such a device structure, the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are connected to the different read/write bit lines BL1, BL2, BL3 and BL4, respectively. Hence, data of the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block can be read at once by one read step.

[0247] The plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are stacked at a plurality of stages on the semiconductor substrate 41. In addition, only the read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. For this reason, even when the number of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is increased, the cell array structure is not complicated.

## (3) STRUCTURAL EXAMPLE 3

[0248] Structural Example 3 is a modification to Structural Example 1. A characteristic feature of Structural Example 3, which is different from Structural Example 1, is the interconnection connected to the gate and source of a read select switch

[0249] That is, in Structural Example 3, the gate of the read select switch is connected to a decode line, and its source is connected to a read word line. The read select switch in a read block is selected by column address signals.

[0250] (1) Circuit Structure

[0251] The circuit structure will be described first.

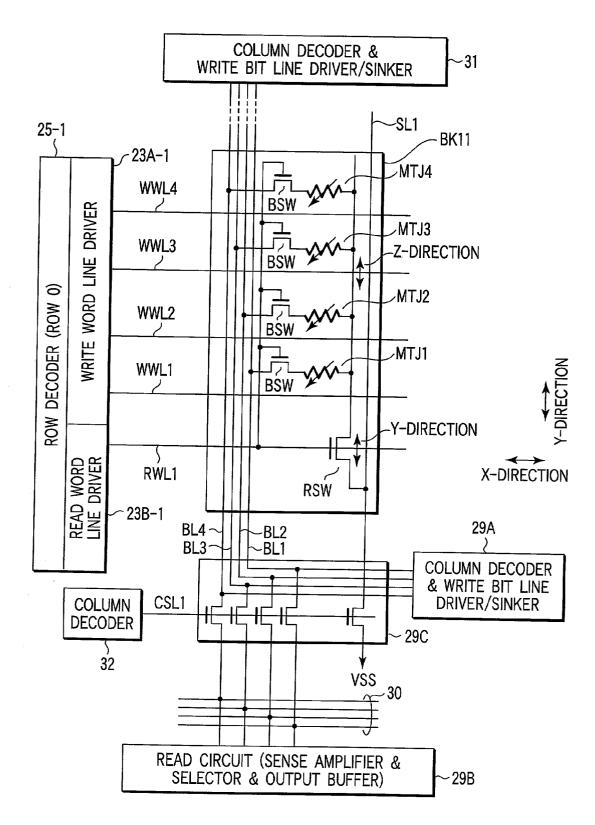

[0252] FIG. 13 shows main part of a magnetic random access memory as Structural Example 3 of the present invention. FIG. 14 shows an example of a column select switch shown in FIG. 13.

[0253] A memory cell array 11 has a plurality of TMR elements 12 arrayed in the X-, Y- and Z-directions. The Z-direction means a direction perpendicular to the X- and Y-directions, i.e., a direction perpendicular to the memory cell array plane.

[0254] The memory cell array 11 has a cell array structure formed from j TMR elements 12 arranged in the X-direction, n TMR elements 12 arranged in the Y-direction, and four TMR elements 12 stacked in the Z-direction. The number of TMR elements 12 stacked in the Z-direction is four. However, the number of TMR elements is not particularly limited as long as the number is two or more.

[0255] The four TMR elements 12 stacked in the Z-direction construct one read block BKik (i=1, 2, ..., j, k=1, 2, ..., n). In fact, the four TMR elements 12 in the read block BKik overlap one another in the direction (Z-direction) perpendicular to the memory cell array plane.

[0256] In this example, one row is constructed by j read blocks BKik arranged in the X-direction. The memory cell array 11 has n rows. In addition, one column is constructed by n read blocks BKik arranged in the Y-direction. The memory cell array 11 has j columns.

[0257] One terminal of each of the four TMR elements 12 in the block BKik is connected to a read word line RWLn (n=1, 2, . . . ) through a read select switch (block select switch or row select switch) RSW formed from, e.g., a MOS transistor. The read word line RWLn extends in the X-direction. For example, one read word line RWLn is arranged in one row.

[0258] The gate of the read select switch RSW is connected to a decode line DLi (i=1, 2, . . . ) The decode line DLi extends in the Y-direction. For example, one decode line is arranged in one column. One end of the decode line DLi is connected to a column decoder 32.

[0259] In this example, the decode line DLi is connected to the column decoder 32. That is, a column select switch and read select switches in read blocks, which are present on a single column, execute the same operation.

[0260] For example, when the column decoder 32 sets a column select signal CSL1 at "H" level, the column select switch of the column to which the read blocks BK11, ..., BK1n belong is turned on. At the same time, the read select switches RSW in the read blocks BK11, ..., BK1n are turned on.

[0261] In this example, both a column select switch 29C and the read select switch RSW in the read block BKik are controlled using a column select signal CSLi (i=1, 2, ...) output from the column decoder 32.

[0262] Instead, for example, as shown in FIG. 15, the column select switch 29C and the read select switch RSW in the read block BKik may be controlled by different signals.

[0263] That is, in the example shown in FIG. 15, the column select switch 29C is controlled by the column select signal CSL1 output from a column decoder 32A. The read select switch RSW in the read block BK11 is controlled by a block select signal BSL1 output from a column decoder 32B.

[0264] The column decoders 32A and 32B have identical structures, as will be described in the section about the read circuit.

[0265] In read operation, in the selected row, the potential of the read word line RWLn changes to "L" level. In the selected column, the read select switches RSW in the read blocks BKik are turned on, as described above.

[0266] Hence, a read current flows only to the TMR elements 12 in the read block BKik located at the intersection between the selected row and the selected column.

[0267] In the read mode, in an unselected column, the read select switches RSW in the read blocks BKik are OFF.

Hence, the other terminal of each TMR element 12 in the read blocks BKik in an unselected column is short-circuited.

[0268] In this case, if read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 in an unselected column have different potentials, they may influence the read operation. To prevent this, the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 in an unselected column are set at an equipotential level (e.g., ground potential).

[0269] In the read operation, in the selected column and unselected rows, for example, the read word lines RWLn are set in the floating state (fixed potential; it may be the same potential as that of the selected bit line). In this case, in the selected column and unselected rows, since the read select switches RSW in the read blocks BKik are ON, the other terminal of each TMR element 12 in the blocks BKik is short-circuited.

[0270] The short circuit between the TMR elements 12 in the read blocks BKik belonging to the selected column and unselected rows may influence the read operation of the TMR elements 12 in the selected read block BKik belonging to the selected row and column.

[0271] Hence, for example, as shown in FIG. 16, block select switches BSW each formed from a MOS transistor may be arranged in each read block BKik. The read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 may be electrically connected only to the TMR elements 12 in the selected read block BKik belonging to the selected row and column. In addition, the read current may be supplied only to these TMR elements.

[0272] The other terminal of each of the four TMR elements 12 in the read block BKik is independently connected to a corresponding one of the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4. Four read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 are arranged in one column in correspondence with four TMR elements 12 in one read block BKik.

[0273] The read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 extend in the Y-direction. One end of each read bit line is connected to a common data line 30 through the column select switch (MOS transistor) 29C. The common data line 30 is connected to a read circuit (including, e.g., a sense amplifier, selector and output buffer) 29B.

[0274] A column select line signal CSLi (i=1, 2, ..., j) is input to the column select switch 29°C. The column decoder 32 outputs the column select line signal CSLi.

[0275] In this example, the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 also function as write bit lines.

[0276] That is, one end of each of the write/read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 is connected to a circuit block 29A including a column decoder and write bit line driver/sinker. The other end is connected to a circuit block 31 including a column decoder and write bit line driver/sinker.

[0277] In write operation, the circuit blocks 29A and 31 are set in an operative state. A write current flows to the write/read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3

and BL4(j-1)+4 in accordance with write data in a direction toward the circuit block 29A or 31.

[0278] A plurality of (in this example, four) write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 that extend in the X-direction and are stacked in the Z-direction are arranged near the four TMR elements 12 of the read block BKik. Here, n indicates a row number (n=1, 2, ...)

[0279] In this example, as for the write word lines extending in the X-direction, one write word line is arranged at one stage in one row. That is, one write word line corresponds to one TMR element in the selected read block BKik. In this case, the number of write word lines in one row extending in the X-direction is the same as the number of stages of the stacked TMR elements 12.

[0280] As shown in FIGS. 106 and 107, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films right under the TMR elements 12 or reducing the manufacturing cost.

[0281] The TMR element in the block and a detailed structure near it will be described in detail in the section about the device structure.

[0282] One end of each of the write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 is connected to a write word line driver 23A-n. The other end is connected to a write word line sinker 24-n.

[0283] The source of the read select switch (MOS transistor) RSW is connected to the read word line RWLn (n=1, 2, ...) One read word line RWLn is arranged in one row, i.e., shared by the plurality of blocks BKik arranged in the X-direction.

[0284] When one read block BKik has a circuit structure shown in FIG. 16, the read word line RWLn is also connected to the gates of the block select switches BSW (MOS transistors) through, e.g., an inverter.

[0285] That is, when the circuit structure shown in FIG. 16 is employed, the block select switches BSW in the blocks BKik on the selected row, i.e., the row for which the potential of the read word line RWLn is at "L" level, are turned on.

[0286] The potential of the read word line RWLn of the selected row changes to "L" level. In addition, the read select switches RSW in the read blocks BKik of the selected column are turned on. For this reason, the read bit lines BL4(j-1)+1, BL4(j-1)+2, BL4(j-1)+3 and BL4(j-1)+4 are electrically connected only to the TMR elements 12 in the selected read block BKik belonging to the selected row and column. In addition, the read current flows only to these TMR elements.

[0287] In the write operation, a row decoder 25-*n* selects one of the plurality of rows on the basis of row address signals. The write word line driver 23A-n supplies write currents to the write word lines WWL4(n-1)+1, WWL4(n-1)+2, WWL4(n-1)+3 and WWL4(n-1)+4 in the selected row. The write currents are absorbed by the write word line sinker 24-*n*.

[0288] In the read operation, the row decoder 25-*n* selects one of the plurality of rows on the basis of row address

signals. The read word line driver 23B-n supplies a read voltage (="L") to the read word line RWLn in the selected row.

[0289] In the magnetic random access memory of the present invention, one column is constructed by a plurality of read blocks. A plurality of TMR elements in each read block are connected to different read bit lines, respectively. Hence, data of the plurality of TMR elements in the read block can be read at once by one read step.

[0290] The plurality of TMR elements in each read block are stacked to form a plurality of stages on a semiconductor substrate. Each read bit line also functions as a write bit line. That is, since no interconnection that functions only as a write bit line need be formed in the cell array, the cell array structure can be simplified.

[0291] In each read block, the read select switch RSW and block select switches (FIG. 16) are arranged. The read select switch is controlled by the output signal from the column decoder. The block select switch is controlled by the output from the row decoder. Hence, in the read operation, the TMR elements in an unselected read block do not influence the read operation. For this reason, the read operation stabilizes.

[0292] ② Device Structure

[0293] The device structure will be described next.

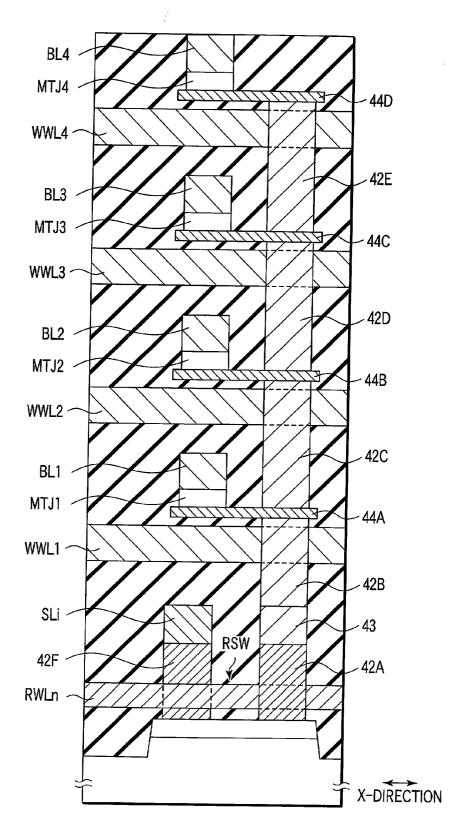

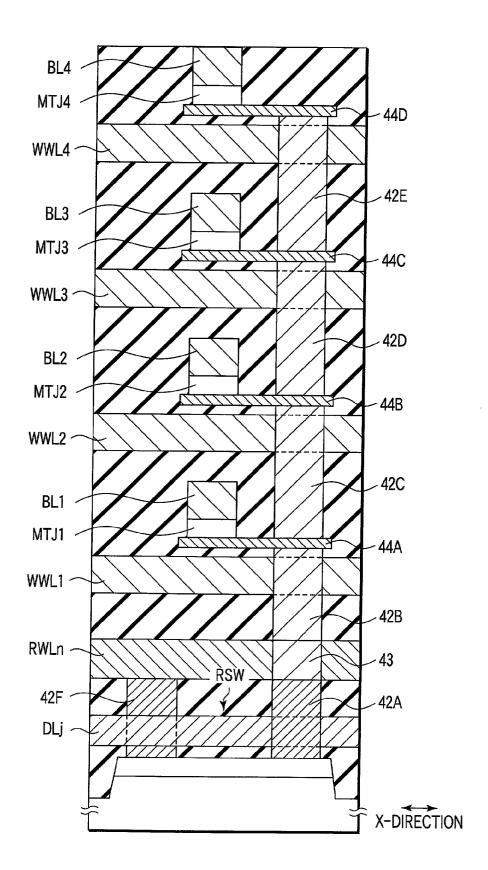

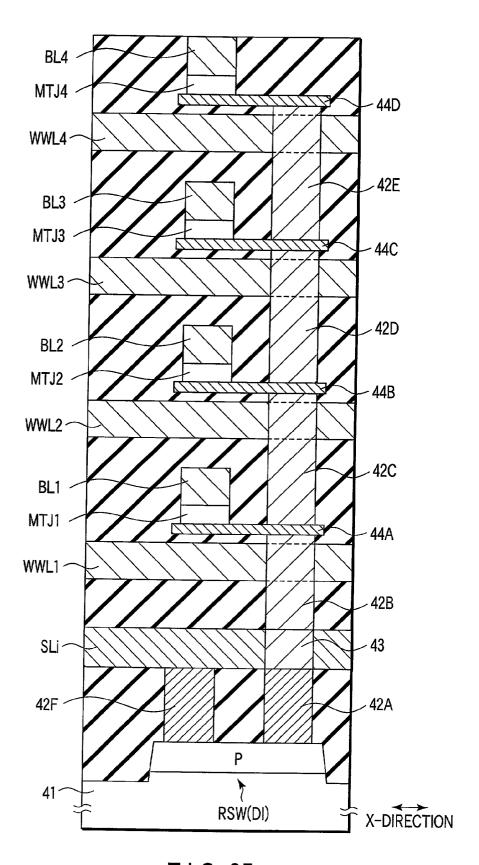

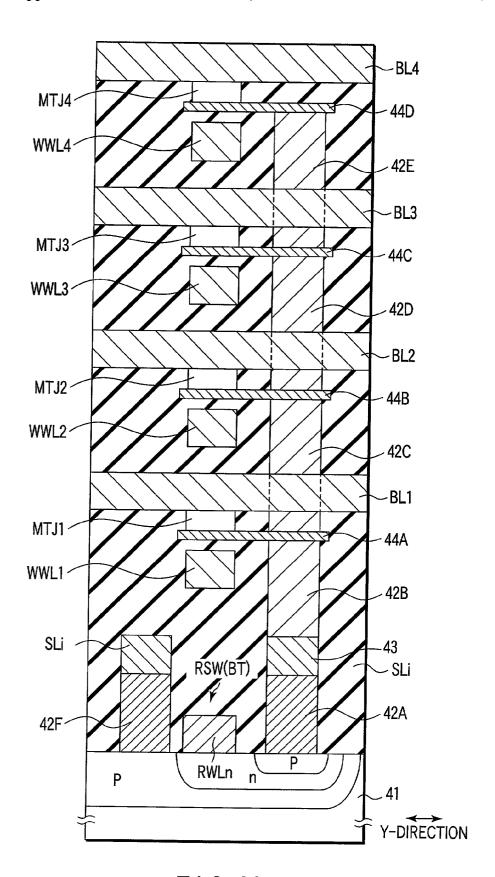

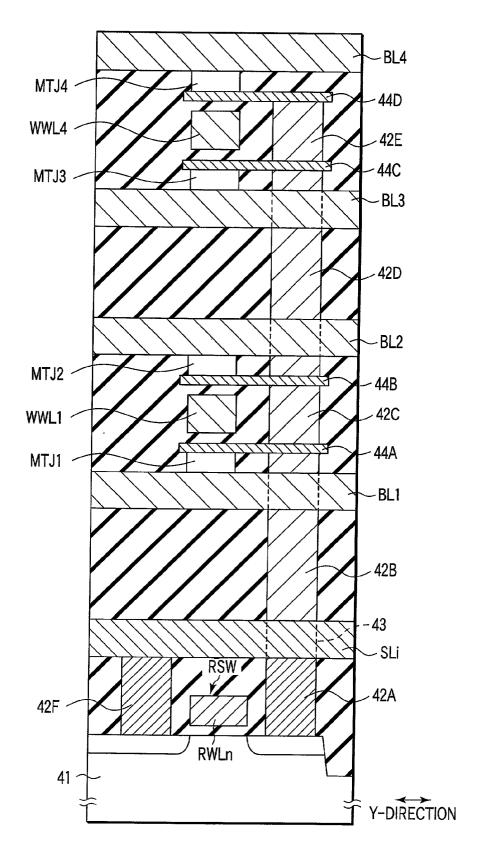

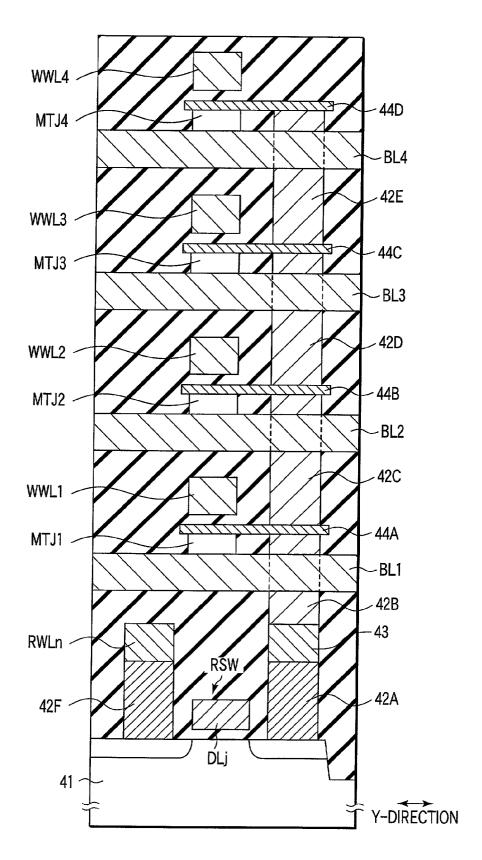

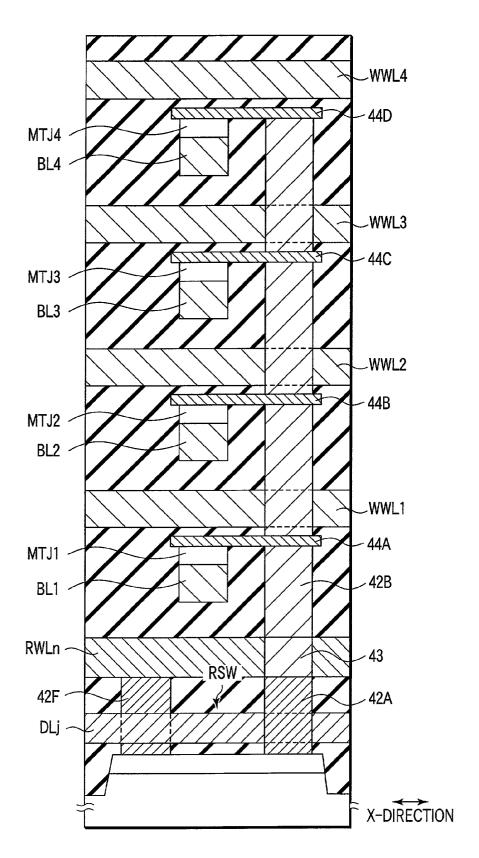

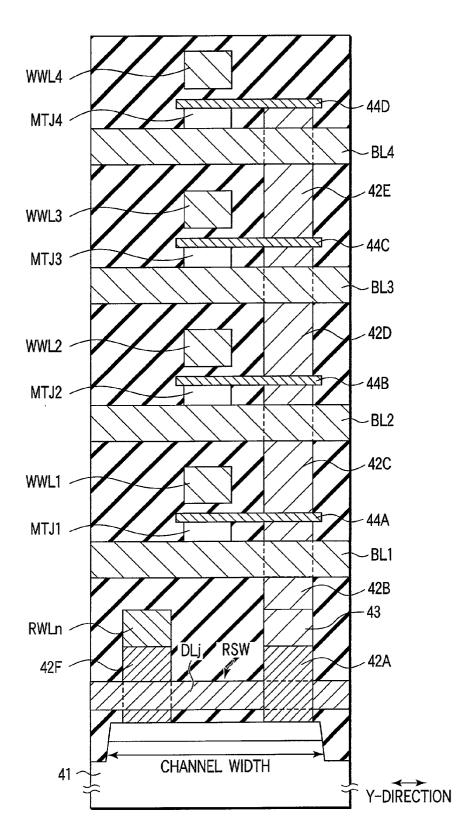

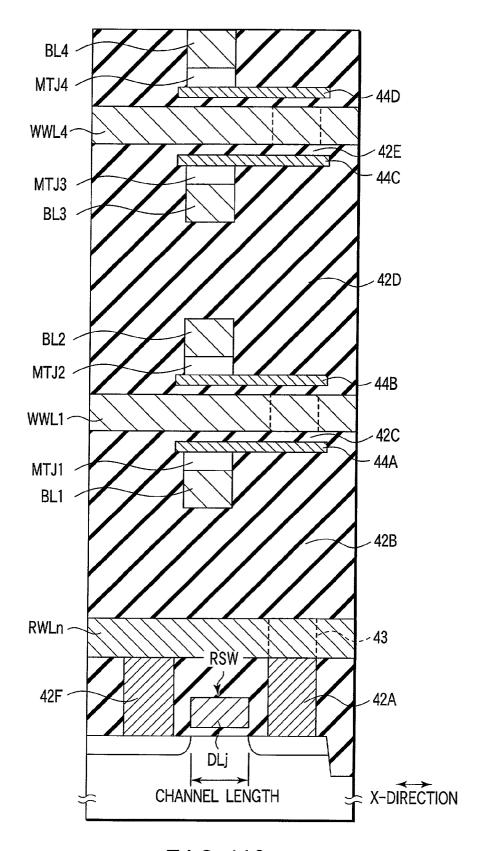

[0294] FIGS. 17 and 18 show the device structure of one block of the magnetic random access memory as Structural Example 3 of the present invention.

[0295] FIG. 17 shows the Y-direction section of one block of the magnetic random access memory. FIG. 18 shows the X-direction section of one block of the magnetic random access memory. The same reference numerals as in FIGS. 13 to 16 denote the same elements in FIGS. 17 and 18 to show the correspondence between the elements.

[0296] The read select switch (MOS transistor) RSW is arranged on the surface region of a semiconductor substrate 41. The source of the read select switch RSW is connected to the read word line RWLn through a contact plug 42F. The read word line RWLn extends straight, e.g., in the X-direction and is connected to the read word line driver arranged at the peripheral portion of the memory cell array region.

[0297] The gate of the read select switch (MOS transistor) RSW serves as a decode line DLj. The decode line DLj extends in the Y-direction at a portion other than the sections shown in FIGS. 17 and 18. The four TMR elements (MTJ (Magnetic Tunnel Junction) elements) MTJ1, MTJ2, MTJ3 and MTJ4 are stacked at a plurality of stages on the read select switch RSW.

[0298] One end (in this example, the lower end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is connected to a corresponding one of lower electrodes 44A, 44B, 44C and 44D. Contact plugs 42A, 42B, 42C, 42D and 42E and intermediate layer 43 electrically connect the lower electrodes 44A, 44B, 44C and 44D to each other and also electrically connect them to the drain of the read select switch RSW.

[0299] The other end (in this example, the upper end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is electrically connected to a corresponding one of read/

write bit lines BL1, BL2, BL3 and BL4. The read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction.

[0300] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are independently connected to the read/write bit lines BL1, BL2, BL3 and BL4, respectively. That is, four read/write bit lines BL1, BL2, BL3 and BL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0301] Write word lines WWL1, WWL2, WWL3 and WWL4 are arranged immediately under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 and near them. The write word lines WWL1, WWL2, WWL3 and WWL4 extend in the X-direction.

[0302] In this example, four write word lines WWL1, WWL2, WWL3 and WWL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0303] In this example, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction are arranged on the TMR elements. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction are arranged below the TMR elements. However, the positional relationship of the read/write bit lines BL1, BL2, BL3 and BL4 and write word lines WWL1, WWL2, WWL3 and WWL4 with respect to the TMR elements is not limited to this.

[0304] For example, as shown in FIGS. 108 and 109, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction may be arranged under the TMR elements.

[0305] The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction may be arranged above the TMR elements.

[0306] As shown in FIGS. 110 and 111, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films immediately under the TMR elements 12 or reducing the manufacturing cost. According to such a device structure, the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are connected to the different read/write bit lines BL1, BL2, BL3 and BL4, respectively. Hence, data of the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block can be read at once by one read step.

[0307] The plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are stacked at a plurality of stages on the semiconductor substrate 41. In addition, only the read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. For this reason, even when the number of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is increased, the cell array structure is not complicated.

[0308] FIG. 19 shows the positional relationship between the TMR elements and the write word lines and read/write bit lines in the device structure shown in FIGS. 17 and 18.

[0309] In the device structure shown in FIGS. 17 and 18, the lower electrodes 44A, 44B, 44C and 44D, write word lines WWL1, WWL2, WWL3 and WWL4, and read/write bit lines BL1, BL2, BL3 and BL4 are arranged at the respective stages of the plurality of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0310] The layouts of, e.g., the stages of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are set to be identical.

[0311] The lower electrodes 44A, 44B, 44C and 44D have, e.g., a rectangular pattern. They have contact regions corresponding to the contact plugs 42A to 42E at partial portions. The lower electrodes 44A, 44B, 44C and 44D have the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 at the remaining portions.

[0312] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are arranged at the intersections between the write word lines WWL1, WWL2, WWL3 and WWL4 and the read/write bit lines BL1, BL2, BL3 and BL4.

#### (4) STRUCTURAL EXAMPLE 4

[0313] Structural Example 4 is a modification to

[0314] Structural Example 3. A characteristic feature of Structural Example 4, which is different from Structural Example 3, is the direction of a read select switch. That is, in Structural Example 4, the read select switch of Structural Example 3 is rotated by 90°.

[0315] (1) Circuit Structure

[0316] The circuit structure will be described first.

[0317] FIG. 20 shows main part of a magnetic random access memory as Structural Example 4 of the present invention. The circuit diagram of FIG. 20 corresponds to that of FIG. 14. The outline of the memory cell array and its peripheral portion in Structural Example 4 is the same as in FIG. 13.

[0318] One terminal of each of four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in a block BK11 is connected to a read word line RWL1 through a read select switch (block select switch or row select switch) RSW formed from, e.g., a MOS transistor. The read word line RWL1 extends in the X-direction.

[0319] The line that connects the source and drain of the read select switch RSW is parallel to the X-direction. That is, the channel length of the read select switch RSW is the X-direction length of the channel of the read select switch RSW. The channel width is the Y-direction width of the channel of the read select switch RSW.

[0320] The gate of the read select switch RSW is connected to a decode line DL1. The decode line DL1 extends in the Y-direction. The decode line DL1 is connected to a column decoder 32. That is, the read select switch RSW is controlled by a decode signal CSL1 obtained by decoding a column address signal.

[0321] Assume that the read block BK11 is selected in read operation. At this time, since CSL1 changes to "H", the read select switch RSW in the read block BK11 is turned on. In addition, the read word line RWL1 changes to "L (ground potential VSS)". Furthermore, a column select switch 29C is turned on.

[0322] Hence, a read current flows to the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11.

[0323] The other terminal of each of the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11 is independently connected to a corresponding one of read bit lines BL1, BL2, BL3 and BL4. That is, four read bit

lines BL1, BL2, BL3 and BL4 are arranged in correspondence with the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block BK11.

[0324] The read bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. One end of each read bit line is connected to a common data line 30 through the column select switch (MOS transistor) 29C. The common data line 30 is connected to a read circuit (including, e.g., a sense amplifier, selector and output buffer) 29B.

[0325] A column select line signal CSL1 is input to the column select switch 29C. The column decoder 32 outputs the column select line signal CSL1.

[0326] In this example, the read bit lines BL1, BL2, BL3 and BL4 also function as write bit lines.

[0327] That is, one end of each of the read/write bit lines BL1, BL2, BL3 and BL4 is connected to a circuit block 29A including a column decoder and write bit line driver/sinker. The other end is connected to a circuit block 31 including a column decoder and write bit line driver/sinker.

[0328] In write operation, the circuit blocks 29A and 31 are set in an operative state. A write current flows to the read/write bit lines BL1, BL2, BL3 and BL4 in accordance with write data in a direction toward the circuit block 29A or 31.

[0329] A plurality of (in this example, four) write word lines WWL1, WWL2, WWL3 and WWL4 that extend in the X-direction and are stacked in the Z-direction are arranged near the four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 of the read block BK11.

[0330] In this example, as for the write word lines extending in the X-direction, one write word line is arranged at one stage in one row. That is, one write word line corresponds to one TMR element in the read block BK11. In this case, the number of write word lines in one row extending in the X-direction is the same as the number of stages of the stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0331] As shown in FIG. 112, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films right under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 or reducing the manufacturing cost.

[0332] One end of each of the write word lines WWL1, WWL2, WWL3 and WWL4 is connected to a write word line driver 23A-n. The other end is connected to a write word line sinker 24-n.

[0333] The gate of the read select switch (MOS transistor) RSW is connected to the read word line RWL1. One read word line RWL1 is arranged in one row, i.e., shared by the plurality of blocks arranged in the X-direction.

[0334] In the write operation, a row decoder 25-1 selects one of the plurality of rows on the basis of row address signals. The write word line driver 23A-n supplies write currents to the write word lines WWL1, WWL2, WWL3 and WWL4 in the selected row. The write currents are absorbed by the write word line sinker.

[0335] In the read operation, the row decoder 25-1 selects one of the plurality of rows on the basis of row address

signals. A read word line driver 23B-1 supplies a read voltage (=" $\mu$ L") to the read word line RWL1 in the selected row.

[0336] In the magnetic random access memory of the present invention, one column is constructed by a plurality of read blocks. A plurality of TMR elements in each read block are connected to different read bit lines, respectively. Hence, data of the plurality of TMR elements in the read block can be read at once by one read step.

[0337] The plurality of TMR elements in each read block are stacked to form a plurality of stages on a semiconductor substrate. Each read bit line also functions as a write bit line. That is, since no interconnection that functions only as a write bit line need be formed in the cell array, the cell array structure can be simplified.

[0338] In each read block, the read select switch RSW is arranged. The read select switch RSW is controlled by the decode signal CSL1 obtained by decoding a column address signal. The source of the read select switch RSW is connected to the read word line. Hence, the read operation can be stably done with the simple arrangement.

[0339] ② Device Structure

[0340] The device structure will be described next.

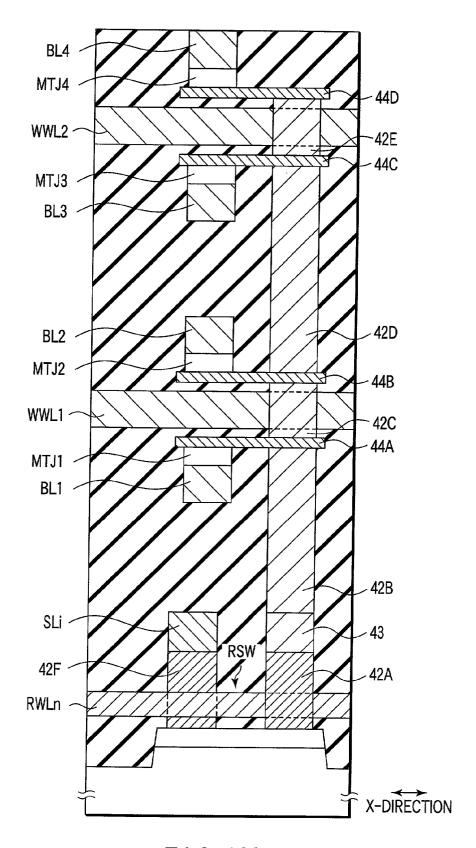

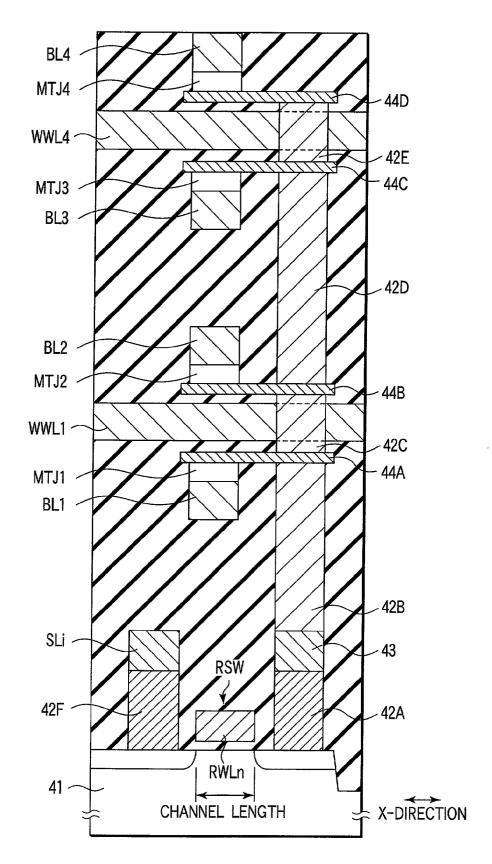

[0341] FIGS. 21 and 22 show the device structure of one block of the magnetic random access memory as Structural Example 4 of the present invention.

[0342] FIG. 21 shows the Y-direction section of one block of the magnetic random access memory. FIG. 22 shows the X-direction section of one block of the magnetic random access memory. The same reference numerals as in FIG. 20 denote the same elements in FIGS. 21 and 22 to show the correspondence between the elements.

[0343] The read select switch (MOS transistor) RSW is arranged on the surface region of a semiconductor substrate 41. The source of the read select switch RSW is connected to the read word line RWLn through a contact plug 42F. The read word line RWLn extends, e.g., in the X-direction and is connected to the read word line driver arranged at the peripheral portion of the memory cell array region.

[0344] The gate of the read select switch (MOS transistor) RSW serves as a decode line DLj. The decode line DLj extends in the Y-direction. The decode line DLj is connected to the column decoder arranged at the peripheral portion of the memory cell array region. The four TMR elements (MTJ (Magnetic Tunnel Junction) elements) MTJ1, MTJ2, MTJ3 and MTJ4 are stacked at a plurality of stages on the read select switch RSW.

[0345] One end (in this example, the lower end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is connected to a corresponding one of lower electrodes 44A, 44B, 44C and 44D. Contact plugs 42A, 42B, 42C, 42D and 42E and intermediate layer 43 electrically connect the lower electrodes 44A, 44B, 44C and 44D to each other and also electrically connect them to the drain of the read select switch RSW.

[0346] The other end (in this example, the upper end) of each of the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is electrically connected to a corresponding one of the

read/write bit lines BL1, BL2, BL3 and BL4. The read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction.

[0347] The TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 are independently connected to the read/write bit lines BL1, BL2, BL3 and BL4, respectively. That is, four read/write bit lines BL1, BL2, BL3 and BL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0348] The write word lines WWL1, WWL2, WWL3 and WWL4 are arranged immediately under the TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 and near them. The write word lines WWL1, WWL2, WWL3 and WWL4 extend in the X-direction.

[0349] In this example, four write word lines WWL1, WWL2, WWL3 and WWL4 are arranged in correspondence with four TMR elements MTJ1, MTJ2, MTJ3 and MTJ4.

[0350] In this example, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction are arranged on the TMR elements. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction are arranged below the TMR elements.

[0351] However, the positional relationship of the read/write bit lines BL1, BL2, BL3 and BL4 and write word lines WWL1, WWL2, WWL3 and WWL4 with respect to the TMR elements is not limited to this.

[0352] For example, as shown in FIGS. 113 and 114, the read/write bit lines BL1, BL2, BL3 and BL4 extending in the Y-direction may be arranged under the TMR elements. The write word lines WWL1, WWL2, WWL3 and WWL4 extending in the X-direction may be arranged above the TMR elements.

[0353] As shown in FIGS. 115 and 116, one write word line may be shared by a plurality of TMR elements (an upper TMR element and lower TMR element) in consideration of planarizing insulating films right under the TMR elements 12 or reducing the manufacturing cost.

[0354] According to such a device structure, the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are connected to the different read/write bit lines BL1, BL2, BL3 and BL4, respectively. Hence, data of the plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block can be read at once by one read step.

[0355] The plurality of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in the read block are stacked at a plurality of stages on the semiconductor substrate 41. In addition, only the read/write bit lines BL1, BL2, BL3 and BL4 extend in the Y-direction. For this reason, even when the number of stacked TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 is increased, the cell array structure is not complicated.

# (5) STRUCTURAL EXAMPLES 5, 6, 7 And 8

#### (1) STRUCTURAL EXAMPLE 5

[0356] Structural Example 5 is a modification to Structural Examples 1, 2, 3 and 4.

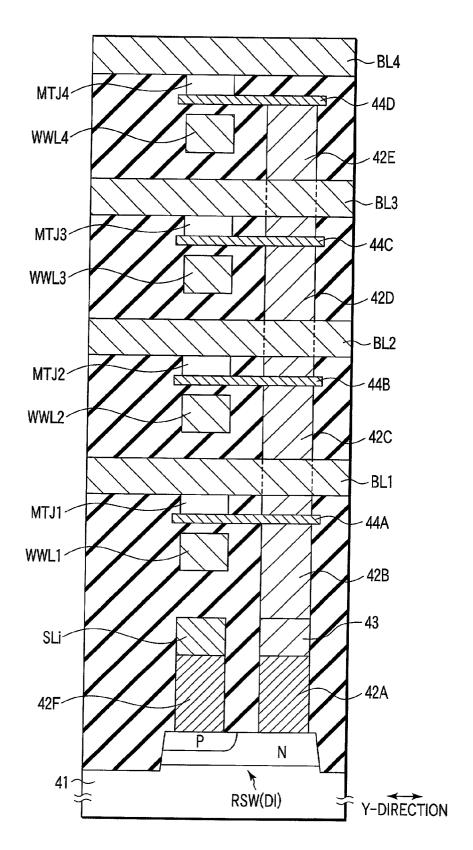

[0357] FIGS. 23, 24 and 25 show Structural Example 5.

[0358] The circuit diagram of FIG. 23 corresponds to that of FIG. 1 or 13. The sectional view of the device structure

shown in FIG. 24 corresponds to that in FIGS. 4, 11, 17 and 21. The sectional view of the device structure shown in FIG. 25 corresponds to that in FIGS. 5, 12, 18 and 22.

[0359] Structural Example 5 is different from Structural Examples 1, 2, 3 and 4 in the element that implements the read select switch.

[0360] In Structural Examples 1, 2, 3 and 4, the read select switch is formed from a MOS transistor. In Structural Example 5, however, the read select switch is formed from a diode DI.

[0361] The anode of the diode DI is connected to one terminal of each of TMR elements MTJ1, MTJ2, MTJ3 and MTJ4 in a read block BKik. The cathode of the diode DI is connected to a read word line RWLn (n=1, 2, ...)