(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-203484

(P2008-203484A)

(43) 公開日 平成20年9月4日(2008.9.4)

(51) Int.Cl.

G09F 9/00 (2006.01)

G02F 1/1345 (2006.01)

F 1

G09F 9/00

G02F 1/1345

テーマコード(参考)

2H092

5G435

審査請求 未請求 請求項の数 8 O L (全 14 頁)

(21) 出願番号

(22) 出願日特願2007-38909 (P2007-38909)

平成19年2月20日 (2007.2.20)

(71) 出願人 304053854

エプソンイメージングデバイス株式会社

長野県安曇野市豊科田沢6925

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 浅田 圭介

長野県安曇野市豊科田沢6925 エプソ

ンイメージングデバイス株式会社内

F ターム(参考) 2H092 GA40 GA41 GA44 GA48 GA50

GA55 MA31 MA32 NA29 PA06

5G435 AA14 AA17 AA18 BB12 EE37

EE41 EE42 EE44 EE47 KK05

KK09 LL07

(54) 【発明の名称】電気光学装置、フレキシブル回路基板の実装構造体及び電子機器

## (57) 【要約】

【課題】フレキシブル回路基板及び基板の端子部のピッチ間隔が狭い場合であっても隣接する端子間の短絡を防

止しつつ、電気的な接続が確実に行われる電気光学装置

、フレキシブル回路基板の実装構造体及び電子機器を提

供する。

【解決手段】フレキシブル回路基板が電気的に接続され

た基板を含む電気光学装置であって、基板は第1の端子

部を備え、フレキシブル回路基板は第2の端子部を備え

、第1の端子部又は第2の端子部のいずれか一方がスタ

ットドバンプであるとともに、第1の端子部及び第2の端

子部が電気的に接続された状態でフレキシブル回路基板

と基板とが絶縁性接着剤で固定される。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

フレキシブル回路基板が電気的に接続された基板を含む電気光学装置において、前記基板は第1の端子部を備え、前記フレキシブル回路基板は第2の端子部を備え、前記第1の端子部又は前記第2の端子部の少なくともいずれか一方がスタッドバンプであるとともに、前記第1の端子部及び前記第2の端子部が電気的に接続された状態で前記フレキシブル回路基板と前記基板とが絶縁性接着剤で固定されたことを特徴とする電気光学装置。

**【請求項 2】**

前記スタッドバンプが千鳥状に配置されることを特徴とする請求項1に記載の電気光学装置。 10

**【請求項 3】**

前記第1の端子部又は前記第2の端子部の少なくともいずれか一方が、前記基板から前記フレキシブル回路基板が導出される方向に配列された複数の前記スタッドバンプを備え、当該複数のスタッドバンプと他方の端子部とが複数箇所で電気的に接続されることを特徴とする請求項1又は2に記載の電気光学装置。

**【請求項 4】**

前記第1の端子部が前記基板の端辺に沿って配置されることを特徴とする請求項1～3のいずれか一項に記載の電気光学装置。

**【請求項 5】**

前記絶縁性接着剤が絶縁性接着フィルム、絶縁性接着ペースト又はアンダーフィルのいずれかであることを特徴とする請求項1～4のいずれか一項に記載の電気光学装置。 20

**【請求項 6】**

前記基板上に半導体素子が異方性導電接着剤を用いて実装されているとともに、前記絶縁性接着剤が光硬化性接着剤であることを特徴とする請求項1～5のいずれか一項に記載の電気光学装置。

**【請求項 7】**

基板上にフレキシブル回路基板が実装されたフレキシブル回路基板の実装構造体において、

前記基板は第1の端子部を備え、前記フレキシブル回路基板は第2の端子部を備え、

前記第1の端子部又は前記第2の端子部の少なくともいずれか一方がスタッドバンプであるとともに、前記第1の端子部及び前記第2の端子部が電気的に接続された状態で前記フレキシブル回路基板と前記基板とが絶縁性接着剤で固定されたことを特徴とするフレキシブル回路基板の実装構造体。 30

**【請求項 8】**

請求項1～6のうちのいずれか一項に記載された電気光学装置を備えた電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電気光学装置、フレキシブル回路基板の実装構造体及び電子機器に関する。特に、フレキシブル回路基板が電気的に接続された電気光学装置用基板を備えた電気光学装置、フレキシブル回路基板の実装構造体及びそのような電気光学装置を備えた電子機器に関する。 40

**【背景技術】****【0002】**

従来、画像を表示する電気光学装置の一態様として、液晶装置やエレクトロルミネッセンス(EL)装置などが知られている。例えば、液晶装置は、電極の対向領域からなる画素を複数形成し、これらの複数の画素に印加する電圧を選択的にオン、オフさせることによって、所定の画素の液晶材料を通過する光を変調させ、絵や文字等の画像を表示させる装置である。このような液晶装置において、装置を小型化したり装置に様々な機能を付加

10

20

30

40

50

したりする等の目的から、液晶パネルや光源を駆動するための回路基板として、配線パターンが形成されたフレキシブル回路基板を、液晶パネルを構成する基板に対して接続して構成されたものがある。

#### 【0003】

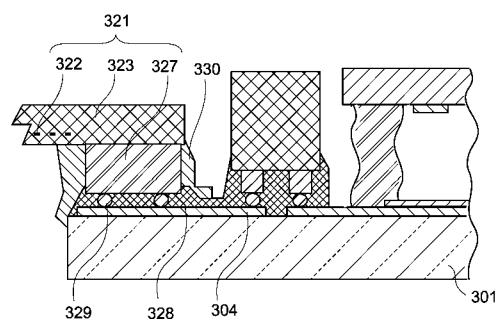

このフレキシブル回路基板を基板に対して接続する方法として、異方性導電接着剤を用いた実装方法がある。例えば、図13に示すように、導電粒子329が絶縁性の接着剤328中に混合された異方性導電フィルム(ACF)330を用いて、液晶パネルを構成するガラス基板301の取り出し電極(Outer Lead)304とフレキシブル回路基板321の接続電極327とを電気的に接続するOLB(Outer Lead Bonding)実装方法が知られている(例えば、特許文献1参照。)。

10

#### 【0004】

【特許文献1】特開2006-235295号公報 (図2)

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

ところで、近年、液晶装置の小型化に伴い、取り出し電極(Outer Lead)のピッチ間隔が狭くなっている。今後、さらなる小型化が進むにつれて、上述のACFを用いた実装方法を採用できなくなるおそれがある。すなわち、隣接する取り出し電極(Outer Lead)間の距離が小さくなると、ACF中の導電粒子が少數連なった場合であっても、両電極間の短絡が生じるおそれがある。

20

#### 【0006】

そこで、本発明の発明者らは鋭意努力し、フレキシブル回路基板を基板に実装する実装方法において、フレキシブル回路基板側の端子又は基板側の端子の少なくともいずれか一方をスタッドバンプとし、フレキシブル回路基板と基板とを絶縁性接着剤で固定することにより、このような問題を解決できることを見出し、本発明を完成させたものである。

すなわち、本発明は、フレキシブル回路基板及び基板の端子部のピッチ間隔が狭い場合であっても隣接する端子間の短絡を防止しつつ、電気的な接続が確実に行われる電気光学装置及びフレキシブル回路基板の実装構造体を提供することを目的とする。また、本発明の別の目的は、そのような電気光学装置を備えた電子機器を提供することである。

30

#### 【課題を解決するための手段】

#### 【0007】

本発明によれば、フレキシブル回路基板が電気的に接続された基板を含む電気光学装置であって、基板は第1の端子部を備え、フレキシブル回路基板は第2の端子部を備え、第1の端子部又は第2の端子部の少なくともいずれか一方がスタッドバンプであるとともに、第1の端子部及び第2の端子部が電気的に接続された状態でフレキシブル回路基板と基板とが絶縁性接着剤で固定されたことを特徴とする電気光学装置が提供され、上述した問題を解決することができる。

すなわち、フレキシブル回路基板側及び基板側の端子部のいずれかをスタッドバンプとし、フレキシブル回路基板と基板とを絶縁性接着剤で固定することにより、端子部のピッチ間隔が狭い場合であっても、隣り合う端子部間での短絡を防止しつつ、電気的な接続状態を確保することができる。また、フレキシブル回路基板を接続する際に、スタッドバンプを用いた構成とすることにより、スタッドバンプの高さに多少のばらつきがある場合であっても、フレキシブル回路基板のフレキシブル性を利用して電気的な接続を確保することができる。したがって、基板あるいはフレキシブル回路基板の外形の小型化が容易になり、電気光学装置の外形を小型化したり、生産コストを低下させたりすることができる。

40

#### 【0008】

また、本発明の電気光学装置を構成するにあたり、スタッドバンプが千鳥状に配置されることが好ましい。

このように構成することにより、端子部のピッチ間隔を狭くする場合であっても隣り合う端子部間の距離を確保しやすくなり、短絡の発生をより低減させることができる。

50

**【0009】**

また、本発明の電気光学装置を構成するにあたり、第1の端子部又は第2の端子部の少なくともいずれか一方が基板からフレキシブル回路基板が導出される方向に配列された複数のスタッズバンプを備え、当該複数のスタッズバンプと他方の端子部とが複数箇所で電気的に接続されることが好ましい。

このように構成することにより、第1の端子部と第2の端子部との接続領域が狭くしつつ、両端子間の接続信頼性を向上させることができる。

**【0010】**

また、本発明の電気光学装置を構成するにあたり、第1の端子部が基板の端辺に沿って配置されることが好ましい。

このように構成することにより、端子部の大きさを小さくできる分、基板の外形を小型化することができる。

**【0011】**

また、本発明の電気光学装置を構成するにあたり、絶縁性接着剤が絶縁性接着フィルム、絶縁性接着ペースト又はアンダーフィルのいずれかであることが好ましい。

このように構成することにより、フレキシブル回路基板と基板とを位置合わせしつつ、容易に固定することができる。

**【0012】**

また、本発明の電気光学装置を構成するにあたり、基板上に半導体素子が異方性導電接着剤を用いて実装されているとともに、絶縁性接着剤が光硬化性接着剤であることが好ましい。

このように構成することにより、製造時においてフレキシブル回路基板の実装工程の際に、半導体素子が熱に晒されるおそれがなく、熱損傷を防ぐことができる。

**【0013】**

また、本発明の別の態様は、基板上にフレキシブル回路基板が実装されたフレキシブル回路基板の実装構造体であって、基板は第1の端子部を備え、フレキシブル回路基板は第2の端子部を備え、第1の端子部又は第2の端子部の少なくともいずれか一方がスタッズバンプであるとともに、第1の端子部及び第2の端子部が電気的に接続された状態でフレキシブル回路基板と基板とが絶縁性接着剤で固定されたことを特徴とするフレキシブル回路基板の実装構造体である。

すなわち、フレキシブル回路基板側及び基板側の端子部のいずれかをスタッズバンプとし、フレキシブル回路基板と基板とを絶縁性接着剤で固定することにより、端子部のピッチ間隔が狭い場合であっても、隣り合う端子部間での短絡を防止しつつ、電気的な接続状態を確保することができる。また、フレキシブル回路基板を接続する際に、スタッズバンプを用いた構成とすることにより、スタッズバンプの高さに多少のばらつきがある場合であっても、フレキシブル回路基板のフレキシブル性を利用して電気的な接続を確保することができる。したがって、基板あるいはフレキシブル回路基板の外形の小型化が容易になり、電気光学装置の外形が小型化され、生産コストが低下させられるフレキシブル回路基板の実装構造体とすることができる。

**【0014】**

また、本発明のさらに別の態様は、上述したいずれかの電気光学装置を備えた電子機器である。

すなわち、基板及びフレキシブル回路基板の端子部を狭ピッチ化する一方、電気的な接続が確実にされ、短絡が低減された電気光学装置を備えているために、動作不良の発生が少ない電子機器とすることができる。

**【発明を実施するための最良の形態】****【0015】**

以下、図面を参照して、本発明の電気光学装置、フレキシブル回路基板の実装構造体、及び電子機器に関する実施形態について具体的に説明する。ただし、かかる実施形態は、本発明の一態様を示すものであり、この発明を限定するものではなく、本発明の範囲内で

任意に変更することが可能である。

#### 【0016】

##### [第1の実施の形態]

本発明の第1の実施の形態は、フレキシブル回路基板が電気的に接続された基板を含む電気光学装置である。本実施形態の電気光学装置において、基板は第1の端子部を備え、フレキシブル回路基板は第2の端子部を備え、第1の端子部又は第2の端子部の少なくともいすれか一方がスタッドバンプであるとともに、第1の端子部及び第2の端子部が電気的に接続された状態でフレキシブル回路基板と基板とが絶縁性接着剤で固定されたことを特徴とする。

以下、図1～図11を適宜参照しながら、本発明の第1の実施の形態の電気光学装置としての液晶装置を例に採って説明する。なお、各図中において、同じ符号を付したもののは同一の部材を示しており、適宜説明を省略するとともに、それぞれの図中、一部の部材が適宜省略されている。

#### 【0017】

##### 1. 全体構造

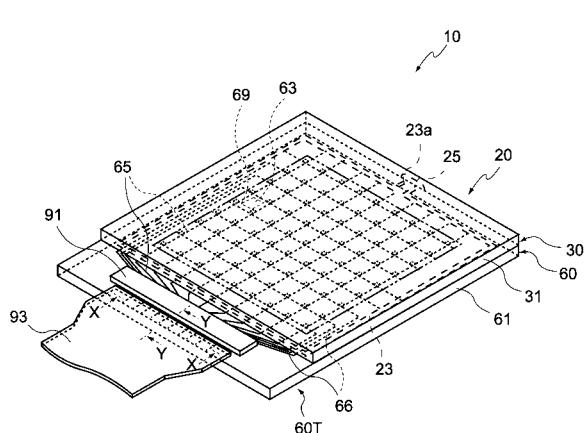

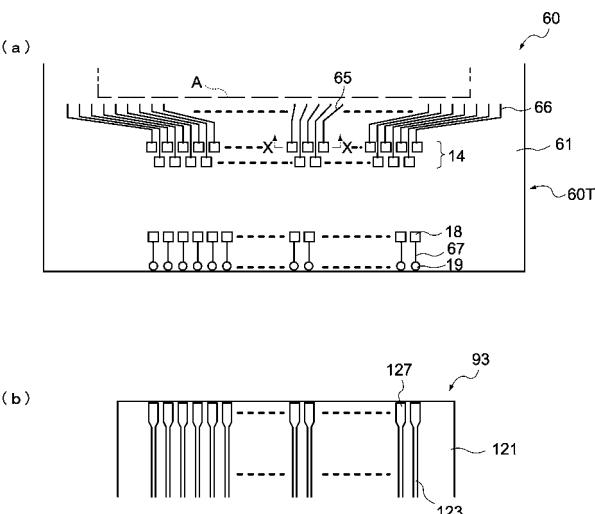

まず、図1を参照して本発明の第1の実施の形態に係る液晶装置10の全体構造について具体的に説明する。ここで、図1は本実施形態に係る液晶装置10の概略斜視図を示している。なお、図1中、上側の面が画像表示面となっている。

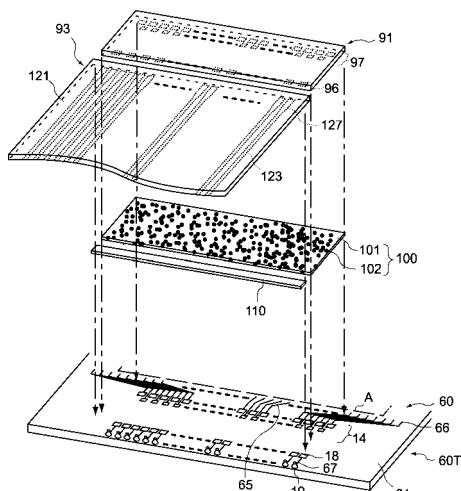

この図1に示すように、本実施形態の液晶装置10は、それぞれ電極を備えた二枚の基板30、60をシール材によって貼り合わせるとともにセル領域内に液晶材料が配置された液晶パネル20を備えている。また、液晶パネル20の背面側には照明装置(図示せず)が配置されている。

#### 【0018】

また、液晶パネル20を構成する素子基板60は、対向基板30の外形よりも外側に張り出してなる基板張出部60Tを有している。この基板張出部60Tにおける液晶材料を保持する面側には接続用端子(図示せず)が形成されるとともに、当該接続用端子に対して半導体素子91及びフレキシブル回路基板93が接続されている。このフレキシブル回路基板93には光源やコネクタ等の電子部品が実装されるようになっている。

#### 【0019】

##### 2. 液晶パネル

液晶パネル20としては、TFT素子(Thin Film Transistor)やTFD素子(Thin Film Diode)等のスイッチング素子を備えたアクティブマトリクス型の液晶パネル、あるいは、スイッチング素子を備えていないパッシブマトリクス型の液晶パネルが代表的なものである。このうち、TFT素子を備えたアクティブマトリクス型の液晶パネルの構成例について説明する。

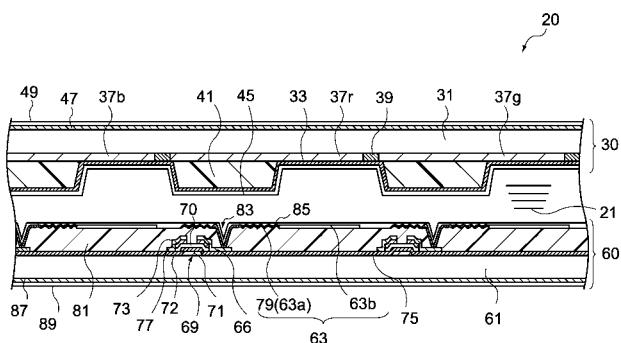

図2は、TFT素子を備えたアクティブマトリクス型の液晶パネル20の各画素領域の部分拡大断面図を示している。この図2に示すように、液晶パネル20は、スイッチング素子としてのTFT素子を備えた素子基板60と、当該素子基板60に対向し、カラーフィルタ37r、37g、37bを備えた対向基板30とを備えている。また、対向基板30の外側(図2の上側)表面には位相差フィルム47と偏光板49が配置されている。同様に、素子基板60の外側(図2の下側)表面にも位相差フィルム87と偏光板89が配置されている。そして、素子基板60の下方に上述した照明装置(図示せず)が配置されている。

#### 【0020】

この液晶パネル20において、対向基板30は、ガラス等の基板31を基体として、色相が異なる複数の着色層からなるカラーフィルタ37r、37g、37bと、そのカラーフィルタ37r、37g、37bの上に形成された対向電極33と、その対向電極33の上に形成された配向膜45とを備えている。また、カラーフィルタ37r、37g、37bと対向電極33との間には、反射領域及び透過領域それぞれのリターデーションを最適化するための透明樹脂層41を備えている。

10

20

30

40

50

ここで、対向電極 33 は ITO (インジウムスズ酸化物) 等によって対向基板 30 上の全域に形成された面状電極である。また、カラーフィルタは R (赤)、G (緑)、B (青) それぞれの色相を有する複数の着色層 37r、37g、37b からなり、対向する素子基板 60 側の画素電極 63 に対応する画素領域がそれぞれ所定の色相の光を呈するよう設けられている。そして、それぞれの画素領域の間隙に相当する領域に対応して遮光膜 39 が設けられている。

また、表面に設けられたポリイミド系の高分子樹脂からなる配向膜 45 には、配向処理としてのラビング処理が施されている。

#### 【0021】

また、対向基板 30 に対向する素子基板 60 は、ガラス等の基板 61 を基体として、スイッチング素子として機能するアクティブ素子としての TFT 素子 69 と、透明な絶縁膜 81 を挟んで TFT 素子 69 の上層に形成された画素電極 63 と、その画素電極 63 の上に形成された配向膜 85 とを備えている。

ここで、図 2 に示す画素電極 63 は、反射領域においては反射表示を行うための光反射膜 79 (63a) を兼ねて形成されるとともに、透過領域においては ITO などにより透明電極 63b として形成されている。この画素電極 63a としての光反射膜 79 は、例えば Al (アルミニウム)、Ag (銀) 等といった光反射性材料によって形成される。ただし、画素電極や光反射膜の構成は図 2 に示すような構成に限られるものではなく、画素電極全体を ITO 等を用いて形成するとともに、別の部材としてアルミニウム等を用いた反射膜を設けた構成とすることもできる。

そして、表面に設けられたポリイミド系の高分子樹脂からなる配向膜 85 には配向処理としてのラビング処理が施されている。

#### 【0022】

また、TFT 素子 69 は、素子基板 60 上に形成されたゲート電極 71 と、このゲート電極 71 の上で素子基板 60 の全域に形成されたゲート絶縁膜 72 と、このゲート絶縁膜 72 を挟んでゲート電極 71 の上方位置に形成された半導体層 70 と、その半導体層 70 の一方の側にコンタクト電極 77 を介して形成されたソース電極 73 と、さらに半導体層 70 の他方の側にコンタクト電極 77 を介して形成されたドレイン電極 66 とを有している。

また、ゲート電極 71 はゲートバス配線 (図示せず) から延びており、ソース電極 73 はソースバス配線 (図示せず) から延びている。また、ゲートバス配線は素子基板 60 の横方向に延びていて縦方向へ等間隔で平行に複数本形成されるとともに、ソースバス配線はゲート絶縁膜 72 を挟んでゲートバス配線と交差するように縦方向へ延びていて横方向へ等間隔で平行に複数本形成される。

かかるゲートバス配線は液晶駆動用半導体素子 (図示せず) に接続されて、例えば走査線として作用し、他方、ソースバス配線は他の駆動用半導体素子 (図示せず) に接続されて、例えば信号線として作用する。

また、画素電極 63 は、互いに交差するゲートバス配線とソースバス配線とによって区画される方形領域のうち TFT 素子 69 に対応する部分を除いた領域に形成されており、この画素電極 63 単位で画素領域が構成されている。

#### 【0023】

ここで、ゲートバス配線及びゲート電極は、例えばクロム、タンタル等によって形成することができる。また、ゲート絶縁膜は、例えば窒化シリコン (SiN<sub>x</sub>)、酸化シリコン (SiO<sub>x</sub>) 等によって形成される。また、半導体層は、例えばドープト a-Si、多結晶シリコン、CdSe 等によって形成することができる。さらに、コンタクト電極は、例えば a-Si 等によって形成することができ、ソース電極及びそれと一体をなすソースバス配線並びにドレイン電極は、例えばチタン、モリブデン、アルミニウム等によって形成することができる。

#### 【0024】

また、有機絶縁膜 81 は、ゲートバス配線、ソースバス配線及び TFT 素子を覆って素

10

20

30

40

50

子基板 6 0 上の全域に形成されている。但し、有機絶縁膜 8 1 のドレイン電極 6 6 に対応する部分にはコンタクトホール 8 3 が形成され、このコンタクトホール 8 3 の所で画素電極 6 3 と TFT 素子 6 9 のドレイン電極 6 6 との導通がなされている。

また、かかる有機絶縁膜 8 1 には、反射領域 R に対応する領域に、散乱形状として、山部と谷部との規則的な又は不規則的な繰り返しパターンから成る凹凸パターンを有する樹脂膜が形成されている。この結果、有機絶縁膜 8 1 の上に積層される光反射膜 7 9 ( 6 3 a ) も同様にして凹凸パターンから成る光反射パターンを有することになる。但し、この凹凸パターンは、透過領域 T には形成されていない。

#### 【 0 0 2 5 】

以上のような構造を有する液晶パネルでは、太陽光や室内照明光などの外光が、対向基板 3 0 側から液晶パネル 2 0 に入射するとともに、カラーフィルタ 3 7 や液晶材料 2 1 などを通過して光反射膜 7 9 に至り、そこで反射されて再度液晶材料 2 1 やカラーフィルタ 3 7 r 、 3 7 g 、 3 7 b などを通過して、液晶パネル 2 0 から外部へ出ることにより、反射表示が行われる。一方、照明装置が点灯され、照明装置から出射された光が液晶パネル 2 0 に入射するとともに、透光性の透明電極 6 3 b 部分を通過し、カラーフィルタ 3 7 r 、 3 7 g 、 3 7 b 、液晶材料 2 1 などを通過して液晶パネル 2 0 の外部へ出ることにより、透過表示が行われる。

そして、それぞれの画素領域から出射される光が混色されて視認されるに至り、様々な色の表示が表示領域全体としてカラー画像として認識される。

#### 【 0 0 2 6 】

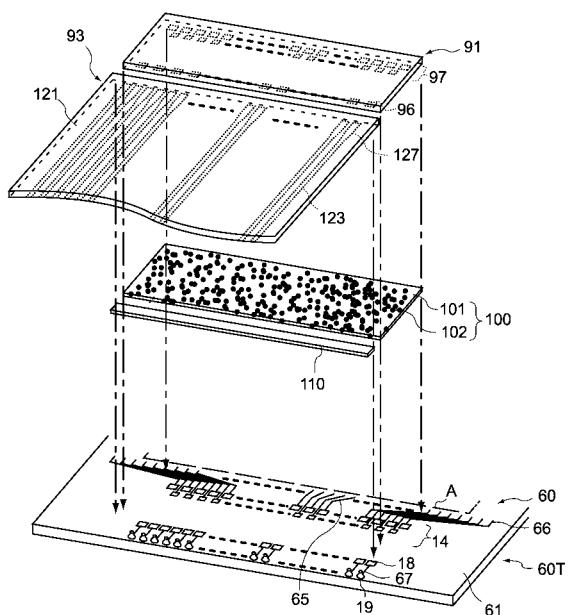

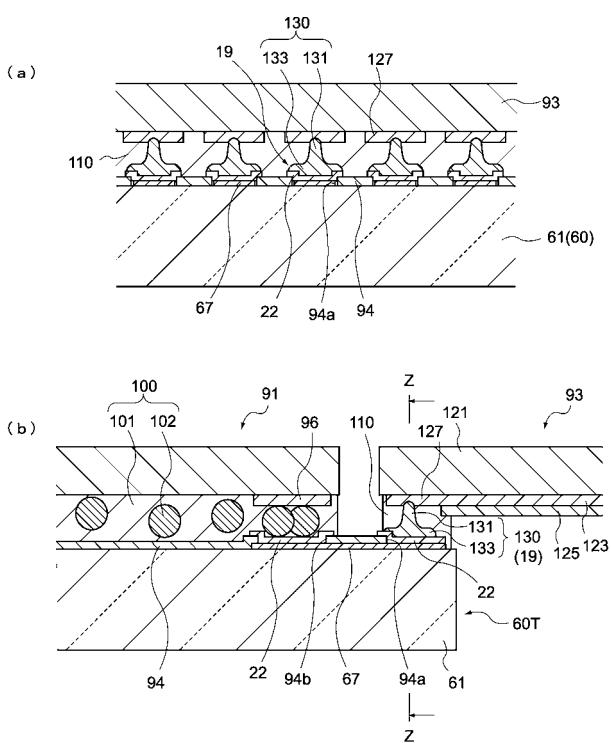

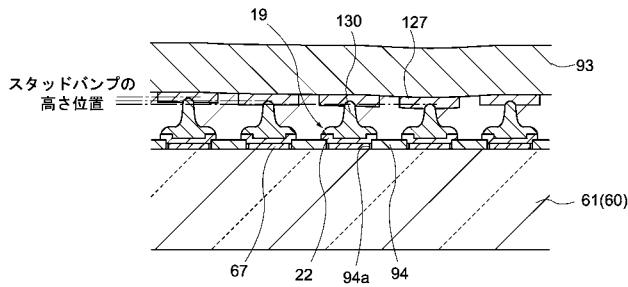

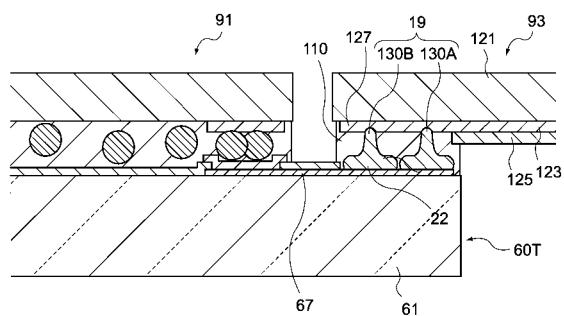

#### 3 . フレキシブル回路基板の実装構造体

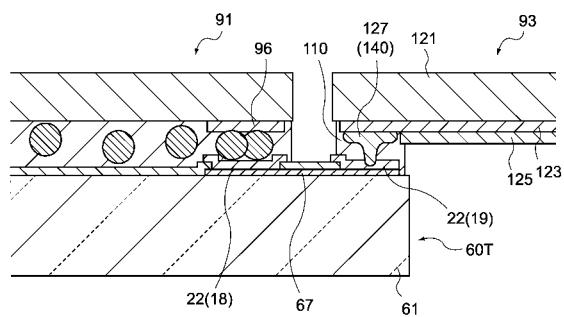

次に、液晶パネルを構成する素子基板に電気的に接続されたフレキシブル回路基板の実装構造体について詳細に説明する。図 3 ~ 図 5 はフレキシブル回路基板 9 3 の実装構造体を説明するための図である。図 3 ( a ) は、素子基板 6 0 の基板張出部 6 0 T をフレキシブル回路基板 9 3 の実装面側から見た平面図であり、図 3 ( b ) は、素子基板 6 0 に対して電気的に接続されるフレキシブル回路基板 9 3 の平面図である。また、図 4 は、素子基板 6 0 、フレキシブル回路基板 9 3 、半導体素子 9 1 、異方性導電フィルム ( A C F ) 1 0 0 、及び絶縁性接着フィルム ( 以下「 N C F 」と称する。 ) 1 1 0 とを分解して示した斜視図である。また、図 5 ( a ) ~ ( b ) はフレキシブル回路基板 9 3 の実装構造体の断面図であって、図 5 ( a ) は図 1 中の X X 断面 ( 図 5 ( b ) の Z Z 断面 ) を矢印方向に見た断面図を示し、図 5 ( b ) は図 1 中の Y Y 断面を矢印方向に見た断面図を示している。

#### 【 0 0 2 7 】

これらの図に示すように、フレキシブル回路基板 9 3 は、ポリイミド等からなる可撓性の基板 1 2 1 上に Cu 等からなる配線パターン 1 2 3 を備え、さらに、表面に絶縁膜 1 2 5 ( 図 5 ( b ) を参照 ) が形成されて構成されている。また、絶縁膜 1 2 5 における配線パターン 1 2 3 の端部に相当する箇所は露出され、素子基板 6 0 側の外部接続用端子部 1 9 と電気的に接続される電極端子 1 2 7 として構成されている。この電極端子 1 2 7 のピッチ間隔は、例えば、 C t o C で 4 0  $\mu$ m 以下とされ、素子基板 6 0 上のスタッドバンプ 1 3 0 からなる外部接続用端子部 1 9 の大きさ及び配置に対応して形成されている。

#### 【 0 0 2 8 】

また、半導体素子 9 1 は、素子基板 6 0 側の各端子部 1 4 、 1 8 とそれぞれ電気的に接続されるバンプ部 9 6 、 9 7 を備えている。これらの各バンプ部 9 6 、 9 7 は、ゲートバス配線 6 5 やソースバス配線 6 6 に対して信号を出力する出力側バンプ部 9 7 と、図示しない C P U からの駆動信号が入力される入力側バンプ部 9 6 を含むものである ( 図 3 ( a ) を参照 ) 。本実施形態に用いられる半導体素子 9 1 はガラス基板 6 1 上に A C F 1 0 0 を用いて実装されるものであり、すべてのバンプ部 9 6 、 9 7 によって A C F 1 0 0 に含まれる導電粒子 1 0 2 を押しつぶして互いの接触面積が確保されるように、すべてのバンプ部 9 6 、 9 7 の高さが等しくされている。これらのバンプ部 9 6 、 9 7 は金属層の表面に金メッキが施された、矩形状のバンプ部として構成されている。

#### 【 0 0 2 9 】

10

20

30

40

50

一方、素子基板 60 の基板張出部 60T には、表示領域 A 内のゲートバス配線 65 やソースバス配線 66 の一端側が延設されており、これらのゲートバス配線 65 等の端部に端子部 14 が形成されている。これらの端子部 14 は、半導体素子 91 の出力側バンプ部 97 が電気的に接続され、半導体素子 91 からの駆動信号が出力されるようになっている。また、端子部 14 よりも表示領域 A から離れる側には、半導体素子 91 の入力側バンプ部 96 が電気的に接続される端子部 18 と、フレキシブル回路基板 93 が電気的に接続される外部接続用端子部 19 とが形成されている。この端子部 18 と外部接続用端子部 19 とは接続配線 67 によって電気的に接続されている。

#### 【0030】

基板張出部 60T においては、ゲートバス配線 65 やソースバス配線 66 、接続配線 67 は絶縁膜 94 で被覆されるとともに、この絶縁膜 94 における上記各端子部 14 、 18 、 19 に相当する箇所には開口部 94a 、 94b が形成されている（図 5 を参照）。そして、絶縁膜 94 の開口部 94a には、ゲートバス配線 65 等を構成する金属材料が腐食しないように、耐腐食性のITOからなる導電膜 22 が形成されている。

#### 【0031】

ここで、本実施形態の液晶装置では、半導体素子 91 の実装には ACF100 が用いられており、半導体素子 91 のバンプ部 96 、 97 と素子基板 60 の端子部 14 、 18 とは導通粒子 102 を介して電気的に接続されるため、上記の導電膜 22 が各端子部 14 、 18 とされている。一方、フレキシブル回路基板 93 の実装には NCF110 が用いられており、フレキシブル回路基板 93 の電極端子 127 が電気的に接続される外部接続用端子部 19 として、上記導電膜 22 上にスタッダードバンプ 130 が形成されている。

#### 【0032】

スタッダードバンプは、ワイヤボンディング法により形成されるバンプであり、例えば、スタッダードバンプが形成されるべき位置に設けられた Au (金) などからなるパッドに対して、Au などの導電性材料からなるワイヤを押し当てて超音波をかけることによりワイヤとパッドとの界面で摩擦熱を発生させ、ワイヤの先端が溶融してパッドに溶着させた後、ワイヤを引きちぎることにより形成することができる。

#### 【0033】

このスタッダードバンプ 130 からなる外部接続用端子部 19 は、素子基板 60 の端辺に沿って配置されている。また、スタッダードバンプ 130 の平面形状は、例えば、直径が 15 ~ 20 μm の円形となっており、上述したフレキシブル回路基板 93 側の電極端子 127 に対応して、ピッチ間隔が CtoC で 40 μm 以下とされている。

なお、導電膜 22 を省略して、接続配線 67 上に直接スタッダードバンプ 130 を形成することもできる。

#### 【0034】

フレキシブル回路基板 93 の実装構造体において、素子基板 60 側の外部接続用端子 19 をスタッダードバンプ 130 とし、素子基板 60 とフレキシブル回路基板 93 とを NCF110 で接着することにより、電気的な接続信頼性を低下させることなく、また、素子基板 60 上の外部接続用端子部 19 及びフレキシブル回路基板 93 上の電極端子 127 のピッチ間隔を小さくした場合であっても、素子基板 60 側及びフレキシブル回路基板 93 側の隣接する端子部 19 、 127 間での短絡のおそれを少なくすることができる。

#### 【0035】

すなわち、ACF を用いた実装方法の場合には、ACF に含まれる導電粒子を介して素子基板上の外部接続用端子とフレキシブル回路基板上の電極端子とを電気的に接続するために、両端子部間に導電粒子が配置されるようにそれぞれの端子部の面積を確保する必要がある。また、導電粒子が連なることによる端子部間の短絡のおそれがあることから、端子部間のピッチ間隔を小さくすることにも限界がある。

一方、スタッダードバンプ及び NCF を利用したで実装方法あれば、導電粒子による短絡のおそれがなくなる上に、スタッダードバンプの突起部の位置によって電気的な接続点も決定するために、端子部の面積も相対的に小さくすることができる。したがって、隣接する端

10

20

30

40

50

子部間の短絡を低減しつつ、端子部間のピッチ間隔を小さくすることができる。

#### 【0036】

また、素子基板60側のスタッドバンプ130の突起部131は、フレキシブル回路基板93側の電極端子127に食い込んだ状態で固定されるため、電気的な接続信頼性が高められる。特に、本発明では一方の基板がフレキシブル回路基板93であることから、図6に示すように、スタッドバンプ130の突起部131の先端位置（スタッドバンプ130の高さ）にはらつきがある場合であっても、スタッドバンプ130の突起部131の先端位置に応じて撓ませることができるために、より確実に接続させることができる。

したがって、液晶装置あるいはフレキシブル回路基板の外形を小さくして、端子部のピッチ間隔を小さくした場合であっても、隣り合う端子部間での短絡を低減しつつ、接続信頼性を高めることができる。10

#### 【0037】

また、上述のように、スタッドバンプ130の平面積は、従来の端子部の面積に対して小さくすることができることから、本実施形態の液晶装置のようにスタッドバンプ130からなる外部接続用端子部19が基板61の端辺に沿って配置されている場合には、外部接続端子部19の配列方向と直交する方向の素子基板の長さも短くすることができる。

#### 【0038】

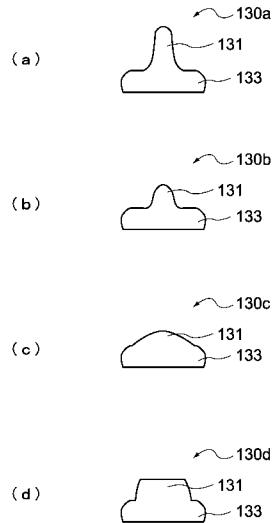

外部接続用端子部としてのスタッドバンプの形状は、例えば、図7(a)～(d)に示すように構成することができる。図7(a)は、台座部133の中央に比較的長い突起部131が形成されたスタッドバンプ130aの例であり、図7(b)は、台座部133の中央に比較的短い突起部131が形成されたスタッドバンプ130bの例であり、図7(c)は、台座部133上に梯型の凸部131が形成されたスタッドバンプ130cの例であり、図7(d)は、台座部133上にさらに台上の凸部131が形成されたスタッドバンプ130dの例である。20

これらの例示されたスタッドバンプは、公知の方法により形成することができる。

#### 【0039】

また、本実施形態の液晶装置では、フレキシブル回路基板93を素子基板60に固定するためのNCF110として、光硬化性の樹脂材料からなるNCF110が用いられている。したがって、製造時において、半導体素子91を実装した後にフレキシブル回路基板93を実装する際に、加熱による硬化作業を実施する必要がなくなり、半導体素子91が熱によってダメージを受けるおそれを低減することができる。30

なお、本実施形態では絶縁性接着剤としてNCF110を用いているが、これに限られるものではなく、絶縁性接着ペースト(NCP)や、フレキシブル回路基板と素子基板とを電気的に接続した状態でそれらの間に接着剤を流し込むアンダーフィル等であっても構わない。また、このような絶縁性接着剤を構成する樹脂の代表的なものとしては、エポキシ系やアクリル系の樹脂等が挙げられる。

#### 【0040】

##### 4. 変形例

本発明は、これまで説明した半導体素子の実装構造の構成に限られるものではなく、種々の変更が可能である。40

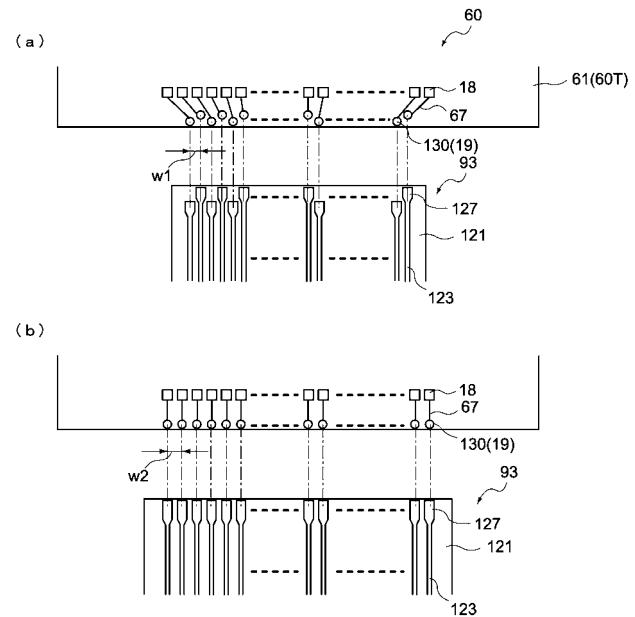

例えば、上述した構成例では、スタッドバンプからなる素子基板上の外部接続用端子部が、基板の端辺に沿って一列に配列されているが、図8(a)に示すように、スタッドバンプ130を千鳥状に配置させることもできる。この図8(a)の例では、隣接するスタッドバンプ130のピッチ間隔w1が、図8(b)に示す直線状に配列させた場合のピッチ間隔w2と比較して小さくされるとともに、スタッドバンプ130同士の間の間隙の大きさがスタッドバンプ130の幅よりも小さくなっている。したがって、このようにスタッドバンプ130を千鳥状に配置した場合には、端子部を短絡させることなく端子部間のピッチ間隔をさらに小さくすることができる。

#### 【0041】

また、図9に示すように、素子基板60からフレキシブル回路基板93が導出される方

向、すなわち、素子基板 60 の接続配線 67 やフレキシブル回路基板 93 の配線パターン 123 が延在する方向に複数のスタッドバンプ 130A、130B を形成し、フレキシブル回路基板 93 上の電極端子 127 に対して複数のスタッドバンプ 130A、130B を接触させて、電気的に接続することもできる。この図 9 の例では、フレキシブル回路基板 93 の一つの電極端子 127 に対して、素子基板 60 上の二つのスタッドバンプ 130A、130B が接触させられている。

このように、フレキシブル回路基板 93 側の電極端子 127 と素子基板 60 側の外部接続用端子 19 を複数箇所で電気的に接続することにより、接続信頼性をより高めることができる。また、上述のとおりスタッドバンプ 130A、130B の平面形状は比較的小さくできるとともに、共通する電極端子に接触する複数のスタッドバンプ 130A、130B はつながっていてもよいため、複数のスタッドバンプ 130A、130B を形成した場合であっても、基板 61 の外形が著しく大きくなることもない。

10

#### 【0042】

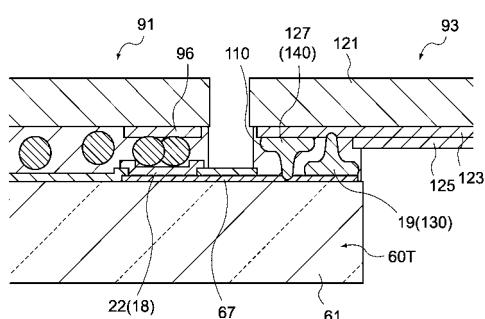

また、これまで説明した例では、素子基板上の外部接続用端子部がスタッドバンプとされ、フレキシブル回路基板上の端子部が電極端子とされていたが、図 10 に示すように、素子基板 60 上の外部接続用端子部 19 を、半導体素子 91 のバンプ部 96 が電気的に接続される端子部 18 と同様に導電膜 22 からなる端子部 19 とし、フレキシブル回路基板 93 側の端子部 127 をスタッドバンプ 140 とすることもできる。

さらには、図 11 に示すように、素子基板 60 上の接続配線 67 及びフレキシブル回路基板 93 上の配線パターン 123 それぞれの端部位置にスタッドバンプ 130、140 を形成し、互いのスタッドバンプ 130、140 の位置が重ならないように接続配線 67 及び配線パターン 123 の延在方向に沿ってずらされた状態で、それぞれのスタッドバンプ 130、140 を対向する接続配線 67 及び配線パターン 123 に接触させて固定することもできる。

20

#### 【0043】

##### [第 2 の実施の形態]

本発明に係る第 2 の実施の形態として、第 1 の実施の形態の液晶装置を備えた電子機器について具体的に説明する。

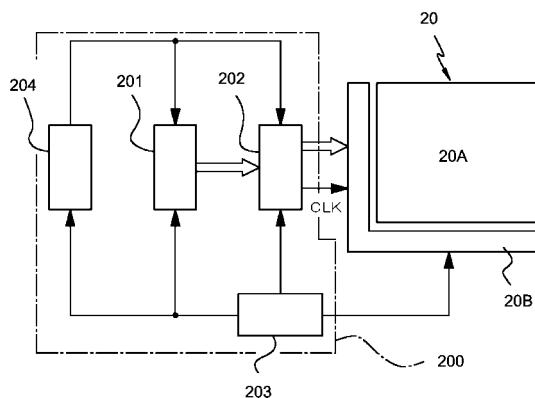

#### 【0044】

図 12 は、本実施形態の電子機器の全体構成を示す概略構成図である。この電子機器は、液晶装置に備えられた液晶パネル 20 と、これを制御するための制御手段 200 を有している。また、図 12 中では、液晶パネル 20 を、パネル構造体 20a と、半導体素子 (I C) 等で構成される駆動回路 20b と、に概念的に分けて描いてある。また、制御手段 200 は、表示情報出力源 201 と、表示処理回路 202 と、電源回路 203 と、タイミングジェネレータ 204 とを有することが好ましい。

30

また、表示情報出力源 201 は、ROM (Read Only Memory) や RAM (Random Access Memory) 等からなるメモリと、磁気記録ディスクや光記録ディスク等からなるストレージユニットと、デジタル画像信号を同調出力する同調回路とを備え、タイミングジェネレータ 204 によって生成された各種のクロック信号に基づいて、所定フォーマットの画像信号等の形で表示情報を表示処理回路 202 に供給するように構成されていることが好ましい。

40

#### 【0045】

また、表示処理回路 202 は、シリアル - パラレル変換回路、増幅・反転回路、ローテーション回路、ガンマ補正回路、クランプ回路等の周知の各種回路を備え、入力した表示情報の処理を実行して、その画像情報をクロック信号 CLK と共に駆動回路 20b へ供給することが好ましい。さらに、駆動回路 20b は、第 1 の電極駆動回路、第 2 の電極駆動回路及び検査回路を含むことが好ましい。また、電源回路 203 は、上述の各構成要素にそれぞれ所定の電圧を供給する機能を有している。

そして、本実施形態の電子機器であれば、所定の関係を満たすようにバンプ部の平面投影面積を異ならせた半導体素子の実装構造体を備えるために、半導体素子の導通不良の少

50

ない電子機器とすることができます。

【産業上の利用可能性】

【0046】

本発明によれば、所定の関係を満たすようにバンプ部の平面投影面積を異ならせた半導体素子の実装構造体を備えることにより、半導体素子の導通不良の少ない電気光学装置や電子機器を提供することができる。したがって、液晶装置やエレクトロルミネッセンス装置等の電気光学装置や電子機器、例えば、携帯電話機やパソコン用コンピュータ等をはじめとして、液晶テレビ、ビューファインダ型・モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電気泳動装置、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた電子機器、電子放出素子を備えた装置(FED:Field Emission DisplayやSCED:Surface-Conduction Electron-Emitter Display)などに幅広く適用することができる。10

【図面の簡単な説明】

【0047】

【図1】第1の実施の形態にかかる液晶装置の概略斜視図である。

【図2】第1の実施の形態にかかる液晶装置の画素領域部分の概略断面図である。

【図3】第1の実施の形態の液晶装置に用いられる素子基板及びフレキシブル回路基板の平面図である。

【図4】フレキシブル回路基板の実装構造体の構成を説明するための分解図である。

【図5】フレキシブル回路基板の実装構造体の構成を説明するための断面図である。20

【図6】スタッドバンプの高さが異なった状態を示す図である。

【図7】スタッドバンプの形状の例を示す図である。

【図8】スタッドバンプを千鳥状に配置した例を示す図である。

【図9】一つの電極端子に対して複数のスタッドバンプを形成した状態を示す図である。

【図10】フレキシブル回路基板側にスタッドバンプを形成した変形例を示す図である。

【図11】素子基板及びフレキシブル回路基板の双方にスタッドバンプを形成した変形例を示す図である。

【図12】第2の実施の形態の電子機器の概略構成を示すブロック図である。

【図13】従来のフレキシブル回路基板の実装構造体の構成を示す図である。

【符号の説明】

【0048】

10: 液晶装置(電気光学装置)、14:配線端子部、18:端子部、19:外部接続用端子部、20:液晶パネル、21:液晶材料、22:導電膜、23:シール材、26:半導体実装領域、30:カラーフィルタ基板、31:ガラス基板、33:面状電極(対向電極)、37:着色層、41:樹脂層、45:配向膜、60:素子基板(電気光学装置用基板)、60T:基板張出部、61:ガラス基板、63:画素電極、65:ゲートバス配線、66:ソースバス配線、67:接続配線、69:TFT素子、85:配向膜、91:半導体素子、93:フレキシブル回路基板、94:絶縁膜、94a:開口部、96:入力側バンプ部、97:出力側バンプ部、100:ACF(異方性導電フィルム)、101:接着剤、102:導電粒子、110:NCF(絶縁性接着フィルム)、121:可撓性基板、123:配線パターン、125:絶縁膜、127:電極端子、130・140:スタッドバンプ3040

【図1】

【 図 2 】

【 図 3 】

【図4】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】