(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6344264号

(P6344264)

(45) 発行日 平成30年6月20日(2018.6.20)

(24) 登録日 平成30年6月1日(2018.6.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/872 | (2006.01) | HO1L 29/86 | 301F |

| HO1L 29/47  | (2006.01) | HO1L 29/48 | F    |

| HO1L 21/28  | (2006.01) | HO1L 29/48 | D    |

| HO1L 29/41  | (2006.01) | HO1L 21/28 | 301B |

| HO1L 21/329 | (2006.01) | HO1L 21/28 | 301R |

請求項の数 17 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2015-37512 (P2015-37512)

(22) 出願日

平成27年2月27日(2015.2.27)

(65) 公開番号

特開2016-162786 (P2016-162786A)

(43) 公開日

平成28年9月5日(2016.9.5)

審査請求日

平成29年3月23日(2017.3.23)

(73) 特許権者 000241463

豊田合成株式会社

愛知県清須市春日長畑1番地

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(72) 発明者 長谷川 一也

愛知県清須市春日長畑1番地 豊田合成株式会社内

(72) 発明者 岡 徹

愛知県清須市春日長畑1番地 豊田合成株式会社内

(72) 発明者 田中 成明

愛知県清須市春日長畑1番地 豊田合成株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置であって、

上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する半導体層と、

前記周囲面から前記側面を通じて前記上面の上方にわたって形成された絶縁膜であって、前記上面の上方に形成され前記上面の端部より内側に開口部を画定する上面部と、前記側面に形成された側面部と、前記周囲面に形成された周囲部と、を有する絶縁膜と、

前記開口部の内側から、前記上面部、前記側面部および前記周囲部の上にわたって形成された電極と

を備え、

前記側面部は、前記周囲部より薄い膜厚から前記上面部に向かうにつれて更に膜厚が薄くなる部分を、有し、

前記上面部の膜厚は、前記開口部に向かうにつれて薄くなり、

前記電極は、前記上面にショットキー接合されたショットキー電極を含み、

前記絶縁膜の膜厚は、前記周囲部と前記側面部と前記上面部とのうち、前記周囲部が最も大きく、前記側面部が第2番目に大きく、前記上面部が最も小さい、半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置であって、

前記絶縁膜は、前記周囲面から前記側面を通じて前記上面にわたって形成され、

10

20

前記電極は、前記上面のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に形成された、半導体装置。

【請求項3】

請求項1または請求項2に記載の半導体装置であって、

前記電極は、第1の電極と、第2の電極とを含み、

前記第1の電極は、前記上面に形成され、

前記絶縁膜は、前記周囲面から前記側面を通じて前記第1の電極の上にわたって形成され、

前記第2の電極は、前記第1の電極のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に形成された、半導体装置。 10

【請求項4】

前記絶縁膜は、二酸化ケイ素( $\text{SiO}_2$ )、酸化アルミニウム( $\text{Al}_2\text{O}_3$ )、窒化ケイ素( $\text{Si}_3\text{N}_4$ )、酸窒化ケイ素( $\text{SiON}$ )および酸窒化アルミニウム( $\text{AlON}$ )の少なくとも1つから主に成る、請求項1から請求項3までのいずれか一項に記載の半導体装置。

【請求項5】

前記半導体層は、窒化ガリウム( $\text{GaN}$ )、窒化アルミニウムガリウム( $\text{AlGaN}$ )、窒化インジウムガリウム( $\text{InGaN}$ )、炭化ケイ素( $\text{SiC}$ )、ケイ素( $\text{Si}$ )およびヒ化ガリウム( $\text{GaAs}$ )の少なくとも1つから主に成る、請求項1から請求項4までのいずれか一項に記載の半導体装置。 20

【請求項6】

前記電極は、ニッケル( $\text{Ni}$ )、パラジウム( $\text{Pd}$ )、白金( $\text{Pt}$ )、金( $\text{Au}$ )、モリブデン( $\text{Mo}$ )およびイリジウム( $\text{Ir}$ )の少なくとも1つから主に成る、請求項1から請求項5までのいずれか一項に記載の半導体装置。

【請求項7】

半導体装置の製造方法であって、

上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面とを、半導体層に形成する工程と、

前記周囲面から前記側面を通じて前記上面の上方にわたって絶縁膜を形成する工程であって、前記上面の上方に形成され前記上面の端部より内側に開口部を画定する上面部と、前記側面に形成された側面部と、前記周囲面に形成された周囲部と、を有する絶縁膜を形成する工程と、 30

ウェットエッティングによって前記絶縁膜における前記開口部を形成する工程と、

前記開口部の内側から、前記上面部、前記側面部および前記周囲部の上にわたって電極を形成する工程と

を備え、

前記開口部を形成する工程は、

前記開口部に対応する部分にマスク開口部を有するマスクを、前記絶縁膜の部位のうち、前記上面部と、前記側面部と、前記周囲部との各部の上に形成する工程と、

前記マスクを形成した後、前記絶縁膜における前記マスク開口部から露出した部分をエッチャントに晒すことによって前記開口部を形成する際、前記絶縁膜と前記マスクとの間に前記エッチャントを入り込ませることによって、前記周囲部より薄い膜厚から前記上面部に向かうにつれて更に膜厚が薄くなる部分を、前記側面部に形成する工程と 40

を含み、

前記上面部の膜厚は、前記開口部に向かうにつれて薄くなり、

前記電極は、前記上面にショットキー接合されたショットキー電極を含む、半導体装置の製造方法。

【請求項8】

前記マスクを形成した後、前記絶縁膜における前記マスク開口部から露出した部分をエッチャントに晒すことによって前記開口部を形成する際、前記絶縁膜と前記マスクとの間 50

に前記エッチャントを入り込ませることによって、前記上面部の膜厚を前記開口部に向かうにつれて薄くする、請求項7に記載の半導体装置の製造方法。

【請求項 9】

請求項7または請求項8に記載の半導体装置の製造方法であって、

前記絶縁膜を形成する工程は、前記周囲面から前記側面を通じて前記上面にわたって前記絶縁膜を形成する工程であり、

前記電極を形成する工程は、前記上面のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に前記電極を形成する工程である、半導体装置の製造方法。

【請求項 10】

10

請求項7または請求項8に記載の半導体装置の製造方法であって、

更に、前記絶縁膜を形成する工程に先立って、前記電極とは異なる他の電極を前記上面に形成する工程を備え、

前記絶縁膜を形成する工程は、前記他の電極を形成した後、前記周囲面から前記側面を通じて前記他の電極の上にわたって前記絶縁膜を形成する工程であり、

前記電極を形成する工程は、前記他の電極のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に前記電極を形成する工程である、半導体装置の製造方法。

【請求項 11】

20

前記メサ構造および前記周囲面を形成する前の半導体層の表面に前記他の電極を形成した後、前記他の電極をマスクとして用いたドライエッチングにより前記半導体層を加工することによって、前記メサ構造および前記周囲面を形成する、請求項10に記載の半導体装置の製造方法。

【請求項 12】

前記マスクは、フォトレジストから成る、請求項7から請求項11までのいずれか一項に記載の半導体装置の製造方法。

【請求項 13】

前記エッチャントは、バッファードフッ酸である、請求項7から請求項12までのいずれか一項に記載の半導体装置の製造方法。

【請求項 14】

30

前記エッチャントにおけるフッ化アンモニウムに対するフッ化水素酸の質量比は、0.1以上1.0以下である、請求項13に記載の半導体装置の製造方法。

【請求項 15】

疎水化表面処理、エッチング処理、並びに、密着性向上剤を塗布する処理を、前記絶縁膜の表面に対して実施せずに、前記マスクを前記絶縁膜に形成する、請求項7から請求項14までのいずれか一項に記載の半導体装置の製造方法。

【請求項 16】

前記絶縁膜の最外層として窒化ケイ素(SiNx)から主になる層を形成する、請求項7から請求項15までのいずれか一項に記載の半導体装置の製造方法。

【請求項 17】

40

前記絶縁膜に対する前記マスクの形成に先立って、プラズマ処理を前記絶縁膜の表面に対して実施する、請求項7から請求項16までのいずれか一項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置(半導体デバイス、半導体素子)では、半導体層および電極の各端部の周辺

50

に発生する電界集中を緩和することによって逆方向リーク電流を抑制することが求められる。特に、パワーデバイスとして用いられる半導体装置では、高耐圧化を実現するために、電界集中の緩和による逆方向リーク電流の抑制が重要である。例えば、半導体装置の1つであるショットキーバリアダイオード (Schottky barrier diode: SBD) では、ショットキー接合の端部に発生する電界集中が問題となる。また、半導体装置の1つであるp-n接合ダイオードでは、p-n接合界面の端部に発生する電界集中が問題となる。

#### 【0003】

特許文献1には、ショットキーバリアダイオードとして、メサ構造を有する半導体層に対してフィールドプレート構造を有する電極を形成した半導体装置が開示されている。特許文献1の半導体装置によれば、半導体層のメサ構造および電極のフィールドプレート構造によって、半導体層と電極とのショットキー接合の端部に発生する電界集中を緩和できる。特許文献1の半導体装置では、絶縁膜の膜厚が薄いほど、ショットキー接合の端部に発生する電界集中を抑制できる。

#### 【0004】

特許文献2には、絶縁膜が既に形成されている製造途中の半導体装置に対して更に絶縁膜を形成することによって、電極端部の周辺における絶縁膜の膜厚を十分に確保する技術が開示されている。特許文献2の半導体装置では、電極端部の周辺における絶縁膜の絶縁破壊を防止できる。

#### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】特開平8-139341号公報

【特許文献2】特開2012-109368号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0006】

特許文献1の半導体装置では、絶縁膜の膜厚が薄くなりすぎた場合、電極端部の周辺における絶縁膜で絶縁破壊が発生する虞があるという問題があった。特許文献2の半導体装置では、電極端部の周辺における絶縁膜の膜厚を確保するために製造工程が煩雑となるという問題があった。そのため、半導体装置において、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーク電流の抑制とを両立できる技術が望まれていた。そのほか、半導体装置においては、低コスト化、微細化、製造の容易化、省資源化、使い勝手の向上、耐久性の向上などが望まれていた。

#### 【課題を解決するための手段】

##### 【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態として実現することが可能である。

本発明の一形態によれば、半導体装置が提供される。この半導体装置は、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する半導体層と；前記周囲面から前記側面を通じて前記上面の上方にわたって形成された絶縁膜であって、前記上面の上方に形成され前記上面の端部より内側に開口部を画定する上面部と、前記側面に形成された側面部と、前記周囲面に形成された周囲部と、を有する絶縁膜と；前記開口部の内側から、前記上面部、前記側面部および前記周囲部の上にわたって形成された電極と；を備え；前記側面部は、前記周囲部より薄い膜厚から前記上面部に向かうにつれて更に膜厚が薄くなる部分を、有し；前記上面部の膜厚は、前記開口部に向かうにつれて薄くなり；前記電極は、前記上面にショットキー接合されたショットキー電極を含み；前記絶縁膜の膜厚は、前記周囲部と前記側面部と前記上面部とのうち、前記周囲部が最も大きく、前記側面部が第2番目に大きく、前記上面部が最も小さい。

##### 【0008】

(1) 本発明の一形態によれば、半導体装置が提供される。この半導体装置は、上面と側面

10

20

30

40

50

面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する半導体層と；前記周囲面から前記側面を通じて前記上面の上方にわたって形成された絶縁膜であって、前記上面の上方に形成され前記上面の端部より内側に開口部を画定する上面部と、前記側面に形成された側面部と、前記周囲面に形成された周囲部と、を有する絶縁膜と；前記開口部の内側から、前記上面部、前記側面部および前記周囲部の上にわたって形成された電極とを備え、前記側面部は、前記周囲部より薄い膜厚から前記上面部に向かうにつれて更に膜厚が薄くなる部分を、有する。この形態によれば、絶縁膜の周囲部の膜厚によって電極端部の周辺における絶縁破壊を防止できるとともに、絶縁膜の側面部における薄肉化によって逆方向リーク電流を抑制できる。また、絶縁膜に開口部を形成する工程において側面部を薄肉化する製造方法を適用できる。これらのことから、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーク電流の抑制とを両立できる。

## 【0009】

(2) 上記形態の半導体装置において、前記上面部の膜厚は、前記開口部に向かうにつれて薄くなつてもよい。この形態によれば、絶縁膜の上面部における薄肉化によって逆方向リーク電流をいっそう抑制できる。

## 【0010】

(3) 上記形態の半導体装置において、前記絶縁膜は、前記周囲面から前記側面を通じて前記上面にわたって形成され、前記電極は、前記上面のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に形成されてもよい。この形態によれば、絶縁膜を形成した後に電極を形成する製造方法を適用できる。

## 【0011】

(4) 上記形態の半導体装置において、前記電極は、第1の電極と、第2の電極とを含み、前記第1の電極は、前記上面に形成され、前記絶縁膜は、前記周囲面から前記側面を通じて前記第1の電極の上にわたって形成され、前記第2の電極は、前記第1の電極のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に形成されてもよい。この形態によれば、絶縁膜を形成する前に第1の電極を半導体層の上に形成する製造方法を適用できる。

## 【0012】

(5) 上記形態の半導体装置において、前記電極は、前記上面にショットキー接合されたショットキー電極を含んでもよい。この形態によれば、ショットキー接合の端部に発生する電界集中を抑制できる。

## 【0013】

(6) 上記形態の半導体装置において、前記半導体層は、相互に隣接するp型半導体層およびn型半導体層を含み、前記電極は、前記上面にオーミック接合されたオーミック電極を含み、前記側面は、前記p型半導体層から前記n型半導体層にわたって形成されてもよい。この形態によれば、p-n接合界面の端部に発生する電界集中を抑制できる。

## 【0014】

(7) 上記形態の半導体装置において、前記絶縁膜は、二酸化ケイ素(SiO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、窒化ケイ素(Si<sub>3</sub>N<sub>4</sub>)、酸窒化ケイ素(SiON)および酸窒化アルミニウム(AlON)の少なくとも1つから主に成ってもよい。この形態によれば、絶縁破壊の防止と逆方向リーク電流の抑制とを十分に図ることができる。

## 【0015】

(8) 上記形態の半導体装置において、前記半導体層は、窒化ガリウム(GaN)、窒化アルミニウムガリウム(AlGaN)、窒化インジウムガリウム(InGaN)、炭化ケイ素(SiC)、ケイ素(Si)およびヒ化ガリウム(GaAs)の少なくとも1つから主に成ってもよい。この形態によれば、絶縁破壊の防止と逆方向リーク電流の抑制とを十分に図ることができる。

## 【0016】

(9) 上記形態の半導体装置において、前記電極は、ニッケル(Ni)、パラジウム(Pd)、白金(Plt)、金(Au)、モリブデン(Mo)およびイリジウム(Ir)の少な

10

20

30

40

50

くとも1つから主に成ってもよい。この形態によれば、絶縁破壊の防止と逆方向リーケ電流の抑制とを十分に図ることができる。

#### 【0017】

(10) 本発明の一形態によれば、半導体装置の製造方法が提供される。この製造方法は、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面とを、半導体層に形成する工程と；前記周囲面から前記側面を通じて前記上面の上方にわたって絶縁膜を形成する工程であって、前記上面の上方に形成され前記上面の端部より内側に開口部を画定する上面部と、前記側面に形成された側面部と、前記周囲面に形成された周囲部と、を有する絶縁膜を形成する工程と；ウェットエッチングによって前記絶縁膜における前記開口部を形成する工程と；前記開口部の内側から、前記上面部、前記側面部および前記周囲部の上にわたって電極を形成する工程とを備え、前記開口部を形成する工程は、前記開口部に対応する部分にマスク開口部を有するマスクを、前記絶縁膜の部位のうち、前記上面部と、前記側面部と、前記周囲部との各部の上に形成する工程と；前記マスクを形成した後、前記絶縁膜における前記マスク開口部から露出した部分をエッチャントに晒すことによって前記開口部を形成する際、前記絶縁膜と前記マスクとの間に前記エッチャントを入り込ませることによって、前記周囲部より薄い膜厚から前記上面部に向かうにつれて更に膜厚が薄くなる部分を、前記側面部に形成する工程とを含む。この形態によれば、絶縁膜に開口部を形成する工程において側面部を薄肉化できる。したがって、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーケ電流の抑制とを両立可能な半導体装置を製造できる。

10

20

#### 【0018】

(11) 上記形態の製造方法において、前記マスクを形成した後、前記絶縁膜における前記マスク開口部から露出した部分をエッチャントに晒すことによって前記開口部を形成する際、前記絶縁膜と前記マスクとの間に前記エッチャントを入り込ませることによって、前記上面部の膜厚を前記開口部に向かうにつれて薄くしてもよい。この形態によれば、絶縁膜に開口部を形成する工程において側面部の膜厚に加え上面の膜厚を加工できる。したがって、製造工程の煩雑化を回避しながら、逆方向リーケ電流をいっそう抑制可能な半導体装置を製造できる。

#### 【0019】

(12) 上記形態の製造方法において、前記絶縁膜を形成する工程は、前記周囲面から前記側面を通じて前記上面にわたって前記絶縁膜を形成する工程であり、前記電極を形成する工程は、前記上面のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に前記電極を形成する工程であってもよい。この形態によれば、絶縁膜を形成した後に電極を形成できる。

30

#### 【0020】

(13) 上記形態の製造方法において、更に、前記絶縁膜を形成する工程に先立って、前記電極とは異なる他の電極を前記上面に形成する工程を備え、前記絶縁膜を形成する工程は、前記他の電極を形成した後、前記周囲面から前記側面を通じて前記他の電極の上にわたって前記絶縁膜を形成する工程であり、前記電極を形成する工程は、前記他の電極のうち前記開口部から露出した部分から、前記上面部、前記側面部および前記周囲部の上にわたって一体的に前記電極を形成する工程であってもよい。この形態によれば、絶縁膜を形成する前に他の電極を半導体層の上に形成できる。

40

#### 【0021】

(14) 上記形態の製造方法において、前記メサ構造および前記周囲面を形成する前の半導体層の表面に前記他の電極を形成した後、前記他の電極をマスクとして用いたドライエッチングにより前記半導体層を加工することによって、前記メサ構造および前記周囲面を形成してもよい。この形態によれば、他の電極を利用した自己整合によって、メサ構造を形成するマスクを別途作製する必要がないため、製造コストを抑制できる。

#### 【0022】

(15) 上記形態の製造方法において、前記マスクは、フォトレジストから成ってもよい

50

。この形態によれば、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

【0023】

(16) 上記形態の製造方法において、前記エッチャントは、バッファードフッ酸であってもよい。この形態によれば、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

【0024】

(17) 上記形態の製造方法において、前記エッチャントにおけるフッ化アンモニウムに対するフッ化水素酸の質量比は、0.1以上10以下であってもよい。この形態によれば、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

10

【0025】

(18) 上記形態の製造方法において、疎水化表面処理、エッチング処理、並びに、密着性向上剤を塗布する処理を、前記絶縁膜の表面に対して実施せずに、前記マスクを前記絶縁膜に形成してもよい。この形態によれば、絶縁膜とマスクとの密着力を抑制できるため、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

【0026】

(19) 上記形態の製造方法において、前記絶縁膜の最外層として窒化ケイ素(SiN<sub>x</sub>)から主になる層を形成してもよい。この形態によれば、絶縁膜とマスクとの密着力を抑制できるため、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

20

【0027】

(20) 上記形態の製造方法において、前記絶縁膜に対する前記マスクの形成に先立って、プラズマ処理を前記絶縁膜の表面に対して実施してもよい。この形態によれば、絶縁膜とマスクとの密着力を抑制できるため、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

【0028】

本発明は、半導体装置およびその製造方法以外の種々の形態で実現することも可能であり、例えば、上記形態の半導体装置が組み込まれた電気機器、並びに、その半導体装置を製造する製造装置などの形態で実現できる。

30

【発明の効果】

【0029】

本願発明の半導体装置によれば、絶縁膜の周囲部の膜厚によって電極端部の周辺における絶縁破壊を防止できるとともに、絶縁膜の側面部における薄肉化によって逆方向リーケ電流を抑制できる。また、絶縁膜に開口部を形成する工程において側面部の膜厚を加工する製造方法を適用できる。これらのことから、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーケ電流の抑制とを両立できる。

【0030】

本願発明における半導体装置の製造方法によれば、絶縁膜に開口部を形成する工程において側面部の膜厚を加工できる。したがって、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーケ電流の抑制とを両立可能な半導体装置を製造できる。

40

【図面の簡単な説明】

【0031】

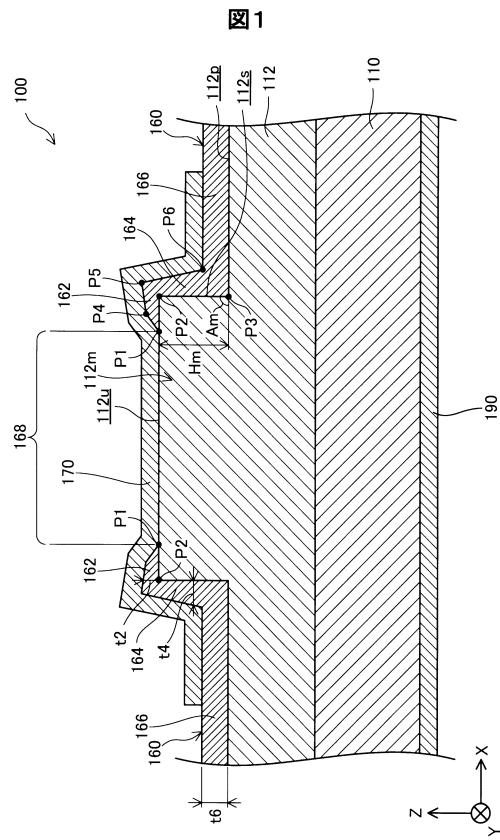

【図1】第1実施形態における半導体装置の構成を模式的に示す断面図である。

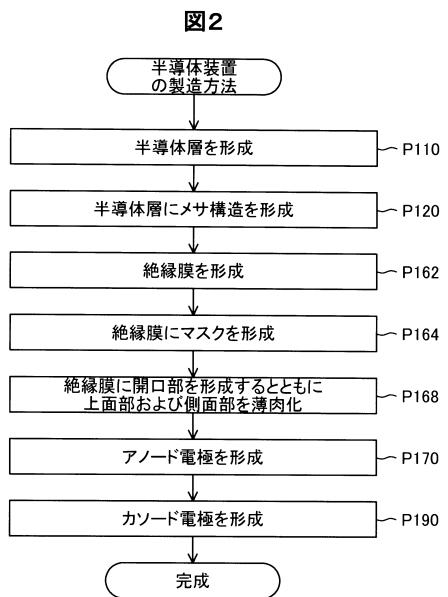

【図2】第1実施形態における半導体装置の製造方法を示す工程図である。

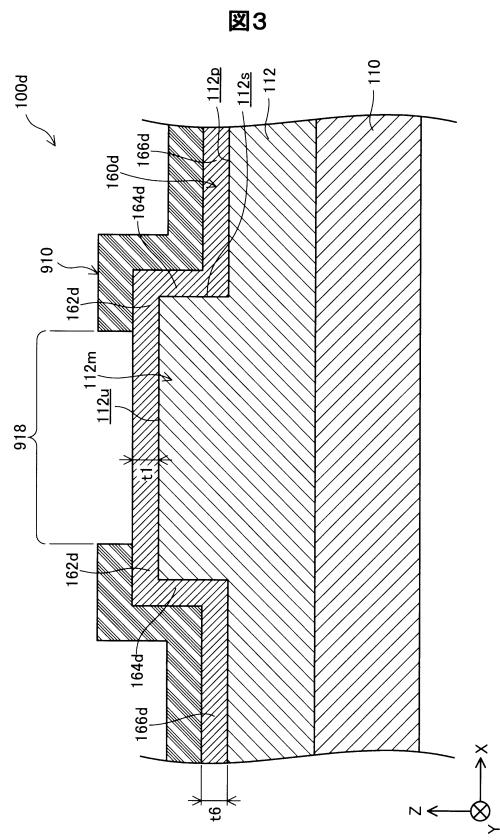

【図3】製造途中にある半導体装置を示す説明図である。

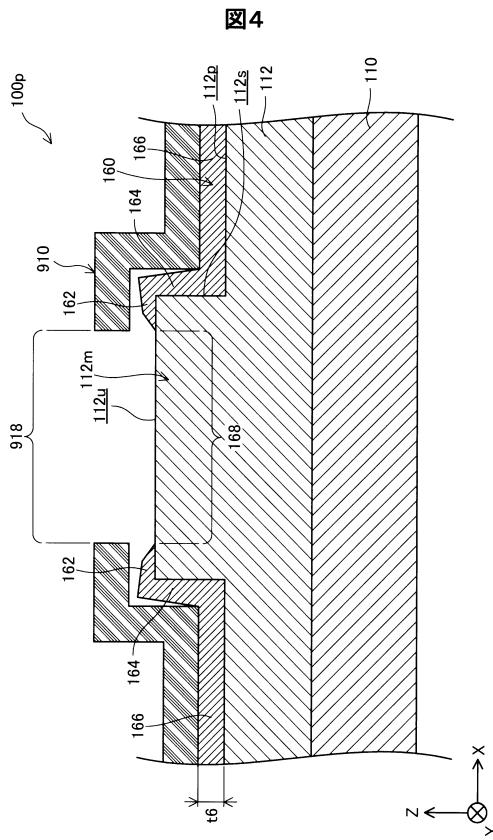

【図4】製造途中にある半導体装置を示す説明図である。

【図5】逆方向電流密度を評価した結果を示すグラフである。

【図6】第2実施形態における半導体装置の構成を模式的に示す断面図である。

【図7】第2実施形態における半導体装置の製造方法を示す工程図である。

【図8】第3実施形態における半導体装置の製造方法を示す工程図である。

50

【図9】第4実施形態における半導体装置の製造方法を示す工程図である。

【図10】第5実施形態における半導体装置の構成を模式的に示す断面図である。

【発明を実施するための形態】

【0032】

#### A. 第1実施形態

##### A-1. 半導体装置の構成

図1は、第1実施形態における半導体装置100の構成を模式的に示す断面図である。図1には、相互に直交するXYZ軸が図示されている。図1のXYZ軸のうち、X軸は、図1の紙面左から紙面右に向かう軸である。+X軸方向は、紙面右に向かう方向であり、-X軸方向は、紙面左に向かう方向である。図1のXYZ軸のうち、Y軸は、図1の紙面手前から紙面奥に向かう軸である。+Y軸方向は、紙面奥に向かう方向であり、-Y軸方向は、紙面手前に向かう方向である。図1のXYZ軸のうち、Z軸は、図1の紙面下から紙面上に向かう軸である。+Z軸方向は、紙面上に向かう方向であり、-Z軸方向は、紙面下に向かう方向である。図1のXYZ軸は、他の図のXYZ軸に対応する。

10

【0033】

本実施形態では、半導体装置100は、窒化ガリウム(GaN)を用いて形成されたGaN系の半導体装置である。本実施形態では、半導体装置100は、縦型ショットキーバリアダイオードである。本実施形態では、半導体装置100は、電力制御に用いられ、パワー・デバイスとも呼ばれる。半導体装置100は、基板110と、半導体層112と、絶縁膜160と、アノード電極170と、カソード電極190とを備える。

20

【0034】

半導体装置100の基板110は、X軸およびY軸に沿って広がる板状を成す半導体である。本実施形態では、基板110は、窒化ガリウム(GaN)から主に成る。本明細書の説明において、「窒化ガリウム(GaN)から主に成る」とは、モル分率において窒化ガリウム(GaN)を90%以上含有することを意味する。本実施形態では、基板110は、ケイ素(Si)をドナー元素として含有するn型半導体である。本実施形態では、基板110に含まれるケイ素(Si)濃度の平均値は、約 $1 \times 10^{18} \text{ cm}^{-3}$ である。

【0035】

半導体装置100の半導体層112は、基板110の+Z軸方向側に位置し、X軸およびY軸に沿って広がるn型半導体層である。本実施形態では、半導体層112は、窒化ガリウム(GaN)から主に成る。本実施形態では、半導体層112は、ケイ素(Si)をドナー元素として含有する。本実施形態では、半導体層112に含まれるケイ素(Si)濃度の平均値は、約 $1 \times 10^{16} \text{ cm}^{-3}$ である。本実施形態では、半導体層112は、有機金属気相成長法(MOCVD: Metal Organic Chemical Vapor Deposition)によって形成された半導体層である。

30

【0036】

半導体層112は、メサ構造112mと、周囲面112pとを有する。半導体層112のメサ構造112mは、上面112uと側面112sとを有する台地状を成す。本実施形態では、メサ構造112mは、周囲面112pより+Z軸方向に突出した構造である。半導体層112の周囲面112pは、メサ構造112mの周囲に広がる表面である。本実施形態では、メサ構造112mおよび周囲面112pは、ドライエッチングによって形成された構造である。本実施形態では、半導体層112の厚み(Z軸方向の長さ)は、メサ構造112mの部分において約10μm(マイクロメートル)である。

40

【0037】

半導体装置100において、基点P1は、上面112uにおける絶縁膜160の端部であり、本実施形態では、半導体層112とアノード電極170とのショットキー接合の端部である。半導体装置100において、基点P2は、上面112uの端部である。半導体装置100において、基点P3は、メサ構造112mと周囲面112pとの境界である。

【0038】

50

基点 P 1 における電界集中を抑制する観点から、メサ構造 112 m の高さ H m は、絶縁膜 160 の厚みより高いことが好ましい。加工性を確保する観点から、メサ構造 112 m の高さ H m は、5  $\mu$ m 以下であることが好ましい。基点 P 1 における電界集中を抑制する観点から、周囲面 112 p に対する側面 112 s の角度 A m は、10° 以上 90° 以下であることが好ましい。

【0039】

半導体装置 100 の絶縁膜 160 は、電気絶縁性を有する膜である。絶縁膜 160 は、周囲面 112 p から側面 112 s を通じて上面 112 u の上方にわたって形成されている。本実施形態では、絶縁膜 160 は、周囲面 112 p から側面 112 s を通じて上面 112 u にわたって形成されている。絶縁膜 160 は、上面部 162 と、側面部 164 と、周囲部 166 とを有する。 10

【0040】

絶縁膜 160 の上面部 162 は、上面 112 u の上方に形成された部位である。上面部 162 は、基点 P 2 より内側に開口部 168 を画定する。開口部 168 は、上面 112 u が露出するまで絶縁膜 160 の一部を上面 112 u の上からウェットエッチングによって除去した構造である。開口部 168 の端部は、基点 P 1 を形成する。

【0041】

上面部 162 の膜厚は、開口部 168 に向かうにつれて薄くなる。上面部 162 は、開口部 168 を形成するウェットエッチングのエッチャントをマスクとの間に入り込ませることによって薄肉化した構造である。絶縁膜 160 の基点 P 4 は、上面部 162 の +Z 軸方向側の表面部位のうち膜厚の変化率が変化する部位である。絶縁膜 160 の基点 P 5 は、絶縁膜 160 の部位のうち上面 112 u から +Z 軸方向に最も離れた部位である。本実施形態では、上面部 162 は、基点 P 1, P 2, P 4, P 5 に囲まれた部位である。 20

【0042】

絶縁膜 160 の側面部 164 は、側面 112 s に形成された部位である。側面部 164 は、周囲部 166 の膜厚 t6 より薄い膜厚 t4 から上面部 162 に向かうにつれて更に膜厚が薄くなる部分を有する。側面部 164 の膜厚 t4 は、上面部 162 の膜厚のうち基点 P 2 における膜厚 t2 より厚い。側面部 164 は、開口部 168 を形成するウェットエッチングのエッチャントをマスクとの間に入り込ませることによって薄肉化した構造である。絶縁膜 160 の基点 P 6 は、絶縁膜 160 の +Z 軸方向側の表面部位のうちメサ構造 112 m に沿って +Z 軸方向に立ち上がる起点である。本実施形態では、側面部 164 は、基点 P 2, P 3, P 5, P 6 に囲まれた部位である。 30

【0043】

絶縁膜 160 の周囲部 166 は、周囲面 112 p に形成された部位である。周囲部 166 の膜厚 t6 は、上面部 162 の膜厚のうち基点 P 2 における膜厚 t2 より厚い。

【0044】

本実施形態では、絶縁膜 160 は、原子層堆積法 (ALD : Atomic Layer Deposition) による厚さ 100 nm の酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) から主に成る層に、プラズマ化学気相成長法 (プラズマ CVD : Plasma Chemical Vapor Deposition) による厚さ 50 nm の二酸化ケイ素 (SiO<sub>2</sub>) から主に成る層を積層した膜である。 40

【0045】

半導体装置 100 のアノード電極 170 は、導電性材料から成り、半導体層 112 の上面 112 u にショットキー接合されたショットキー電極である。アノード電極 170 は、開口部 168 の内側から、上面部 162、側面部 164 および周囲部 166 の上にわたって形成されている。これによって、アノード電極 170 は、半導体層 112 との間に絶縁膜 160 を挟むフィールドプレート構造を形成する。本実施形態では、アノード電極 170 は、上面 112 u のうち開口部 168 から露出した部分から、上面部 162、側面部 164 および周囲部 166 の上にわたって一体的に形成されている。

【0046】

本実施形態では、アノード電極 170 は、電子ビーム蒸着法によって、半導体層 112 50

側から順に、厚さ約100nm(ナノメートル)のニッケル(Ni)から主に成る層と、厚さ約100nmのパラジウム(Pd)から主に成る層と、厚さ約20nmのモリブデン(Mo)から主に成る層とを積層した電極である。アノード電極170におけるニッケル(Ni)は、半導体層112の窒化ガリウム(GaN)とのショットキー接合を形成する。アノード電極170におけるパラジウム(Pd)は、ショットキー障壁高さを向上させる。アノード電極170におけるモリブデン(Mo)は、アノード電極170の上に他の電極(例えば、配線電極)が形成された場合にバリアメタルとして電極層間における電極材料の相互拡散を防止する。

#### 【0047】

半導体装置100のカソード電極190は、導電性材料から成り、基板110の-Z軸方向側にオーミック接合されたオーミック電極である。本実施形態では、カソード電極190は、スパッタ法によってチタン(Ti)から主に成る層にアルミニウム-ケイ素合金(AlSi)から成る層を積層した電極である。

#### 【0048】

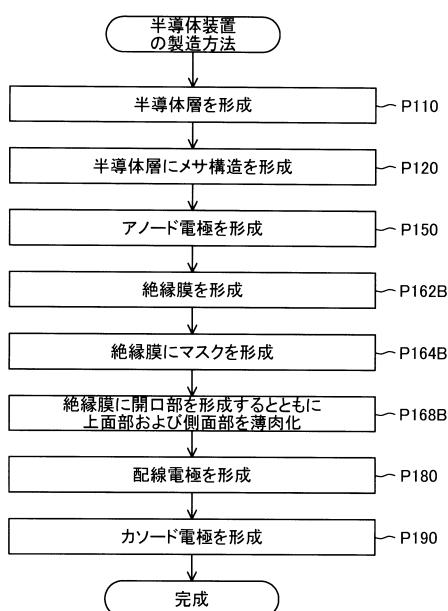

##### A-2. 半導体装置の製造方法

図2は、第1実施形態における半導体装置100の製造方法を示す工程図である。半導体装置100の製造者は、基板110の上に半導体層112をエピタキシャル成長によって形成する(工程P110)。本実施形態では、製造者は、有機金属気相成長法(MOCVD)を実現するMOCVD装置を用いたエピタキシャル成長によって、半導体層112を形成する。

10

20

#### 【0049】

半導体層112を形成した後(工程P110)、製造者は、半導体層112にメサ構造112mを形成する(工程P120)。本実施形態では、製造者は、半導体層112の表面のうちメサ構造112mとして残す部分にマスクを形成した後、塩素(Cl)系のドライエッティングによって半導体層112の一部を除去することによって、半導体層112にメサ構造112mおよび周囲面112pを形成する。その後、製造者は、半導体層112に形成したマスクを除去する。マスクは、二酸化ケイ素(SiO<sub>2</sub>)から主に成るマスクであってもよいし、フォトレジストから成るマスクであってもよい。

#### 【0050】

メサ構造112mを形成した後(工程P120)、製造者は、半導体層112の+Z軸方向側の表面に、絶縁膜160の元となる絶縁膜を形成する(工程P162)。本実施形態では、製造者は、原子層堆積法(ALD)によって酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)から主に成る層を形成した後、プラズマ化学気相成長法(Plasma CVD)によって二酸化ケイ素(SiO<sub>2</sub>)から主に成る層を積層することによって、絶縁膜160の元となる絶縁膜を形成する。

30

#### 【0051】

絶縁膜160の元となる絶縁膜を形成した後(工程P162)、製造者は、絶縁膜160の元となる絶縁膜をウェットエッティングによって加工することによって、絶縁膜160の開口部168を形成する(工程P164, P168)。

#### 【0052】

40

絶縁膜160の開口部168を形成する際、製造者は、絶縁膜160の元となる絶縁膜の上にマスクを形成する(工程P164)。本実施形態では、製造者は、フォトレジストから成るマスクを絶縁膜の上に形成する。

#### 【0053】

図3は、製造途中にある半導体装置100dを示す説明図である。半導体装置100dは、絶縁膜160の元となる絶縁膜160dの上にマスク910を形成することによって作製される。マスク910は、絶縁膜160dの部位のうち、上面112uに形成された上面部162dと、側面112sに形成された側面部164dと、周囲面112pに形成された周囲部166dとの各部の上に形成される。マスク910は、絶縁膜160の開口部168に対応する部分にマスク開口部918を有する。半導体装置100dにおいて、

50

上面部 162d の膜厚  $t_1$  は、周囲部 166d の膜厚  $t_6$  に等しい。

【0054】

本実施形態では、製造者は、疎水化表面処理、エッティング処理、並びに、密着性向上剤を塗布する処理を、絶縁膜 160d の表面に対して実施せずに、マスク 910 を絶縁膜 160d に形成する。これによって、絶縁膜 160d とマスク 910 との密着力を抑制できる。他の実施形態では、製造者は、絶縁膜 160d に対するマスク 910 の形成に先立つて、プラズマ処理を絶縁膜 160d の表面に対して実施してもよい。これによっても、絶縁膜 160d とマスク 910 との密着力を抑制できる。

【0055】

図 2 の説明に戻り、絶縁膜 160d の上にマスク 910 を形成した後（工程 P164）10、製造者は、絶縁膜 160d の上面部 162d に開口部 168 を形成するとともに、絶縁膜 160d の上面部 162d および側面部 164d を薄肉化する（工程 P168）。これによって、絶縁膜 160 が形成される。製造者は、絶縁膜 160d におけるマスク開口部 918 から露出した部分をエッチャントに晒すことによって、絶縁膜 160d の上面部 162d に開口部 168 を形成する。その際、製造者は、マスク開口部 918 側から絶縁膜 160d とマスク 910 との間にエッチャントを入り込ませることによって、上面部 162d および側面部 164d の各膜厚を薄くする。

【0056】

図 4 は、製造途中にある半導体装置 100p を示す説明図である。半導体装置 100p は、半導体装置 100d に対してウェットエッティングを実施することによって作製される20。本実施形態では、絶縁膜 160 における薄肉化される部位は、上面部 162 および側面部 164 の全域である。他の実施形態では、絶縁膜 160 における薄肉化される部位は、上面部 162 から側面部 164 の途中までの範囲であってもよいし、上面部 162 から周囲部 166 にわたる範囲であってもよい。

【0057】

本実施形態では、絶縁膜 160d を処理するエッチャントは、バッファードフッ酸（BFH）である。絶縁膜 160d とマスク 910 との間へエッチャントを入り込みやすくする観点から、エッチャントに使用するバッファードフッ酸において、フッ化アンモニウムに対するフッ化水素酸の質量比は、0.1 以上であることが好ましく、0.5 以上であることがさらに好ましく、1 以上であることがいっそう好ましい。絶縁膜 160d とマスク 910 との間へと過度にエッチャントが入り込むことを防止する観点から、エッチャントに使用するバッファードフッ酸において、フッ化アンモニウムに対するフッ化水素酸の質量比は、1.0 以下であることが好ましい。30

【0058】

図 2 の説明に戻り、絶縁膜 160 を形成した後（工程 P168）、製造者は、マスク 910 を除去した上で、アノード電極 170 を形成する（工程 P170）。本実施形態では、製造者は、リフトオフ法を用いた電子ビーム蒸着法によってアノード電極 170 を形成する。アノード電極 170 を形成する方法は、電子ビーム蒸着法に限らず、抵抗加熱蒸着法であってもよいし、スパッタ法であってもよい。他の実施形態では、製造者は、上面 112u および絶縁膜 160 の全面に電極を形成した後、その電極の一部を除去することによって、アノード電極 170 を形成してもよい。本実施形態では、製造者は、半導体層 112 側から順に、ニッケル（Ni）から主に成る層と、パラジウム（Pd）から主に成る層と、モリブデン（Mo）から主に成る層とを積層することによって、アノード電極 170 を形成する。40

【0059】

アノード電極 170 を形成した後（工程 P170）、製造者は、カソード電極 190 を形成する（工程 P190）。本実施形態では、製造者は、スパッタ法によってチタン（Ti）から主に成る層にアルミニウム - ケイ素合金（AlSi）から主に成る層を積層することによって、カソード電極 190 を形成する。

【0060】

50

これらの工程を経て、半導体装置 100 が完成する。他の実施形態では、製造者は、半導体層 112 を形成した後（工程 P110）であれば、カソード電極 190 を形成する工程（工程 P190）を、アノード電極 170 を形成する工程（工程 P170）に先立って実施してもよい。

#### 【0061】

##### A - 3 . 評価試験

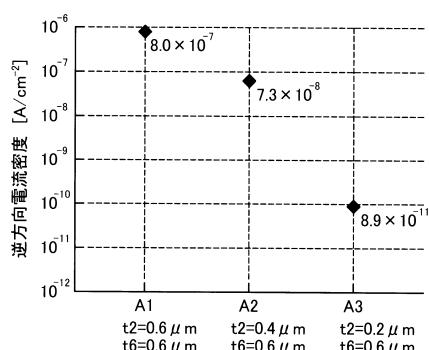

図 5 は、逆方向電流密度を評価した結果を示すグラフである。試験者は、3 つの試料 A1, A2, A3 について、シミュレーションによって逆方向電流密度を評価した。図 5 の逆方向電流密度は、各試料に対して 500V を印加した際に測定される逆方向電流密度を示す。

10

#### 【0062】

試料 A1 は、フッ化アンモニウムに対するフッ化水素酸の質量比が 0.1 未満であるバッファードフッ酸をエッチャントに用いて、絶縁膜 160 の開口部 168 を形成することによって、側面部 164 が薄肉化されていない点を除き、図 1 の半導体装置 100 と同様である。試料 A1 の絶縁膜 160 において、上面部 162 の膜厚  $t_2$  は 0.6 μm であり、周囲部 166 の膜厚  $t_6$  は 0.6 μm である。

#### 【0063】

試料 A2 は、フッ化アンモニウムに対するフッ化水素酸の質量比が試料 A3 より低いバッファードフッ酸をエッチャントに用いた半導体装置 100 である。試料 A2 の絶縁膜 160 において、上面部 162 の膜厚  $t_2$  は 0.4 μm であり、周囲部 166 の膜厚  $t_6$  は 0.6 μm である。

20

#### 【0064】

試料 A3 は、フッ化アンモニウムに対するフッ化水素酸の質量比が試料 A2 より高いバッファードフッ酸をエッチャントに用いた半導体装置 100 である。試料 A3 の絶縁膜 160 において、上面部 162 の膜厚  $t_2$  は 0.2 μm であり、周囲部 166 の膜厚  $t_6$  は 0.6 μm である。

#### 【0065】

図 5 の評価結果によれば、上面部 162 および側面部 164 における膜厚が薄いほど、逆方向電流密度を抑制できることが分かる。言い換えると、上面部 162 および側面部 164 における膜厚が薄いほど、逆方向リーキ電流を抑制できる。この結果は、上面部 162 および側面部 164 の薄肉化によって、ショットキー接合の端部である基点 P1 に発生する電界集中が緩和されることに起因する。

30

#### 【0066】

##### A - 4 . 効果

以上説明した第 1 実施形態によれば、絶縁膜 160 の周囲部 166 の膜厚  $t_6$  によってアノード電極 170 の端部の周辺における絶縁破壊を防止できるとともに、絶縁膜 160 の側面部 164 における薄肉化によって逆方向リーキ電流を抑制できる。また、絶縁膜 160 に開口部 168 を形成する工程 P168 において側面部 164 を薄肉化する製造方法を適用できる。これらのことから、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーキ電流の抑制とを両立できる。

40

#### 【0067】

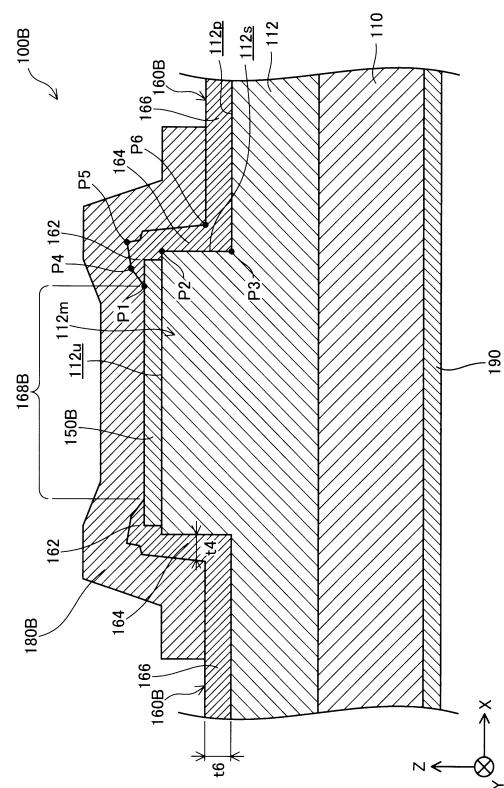

##### B . 第 2 実施形態

図 6 は、第 2 実施形態における半導体装置 100B の構成を模式的に示す断面図である。半導体装置 100B の構成は、絶縁膜 160 およびアノード電極 170 に代えて、アノード電極 150B と、絶縁膜 160B と、配線電極 180B とを備える点を除き、第 1 実施形態の半導体装置 100 と同様である。

#### 【0068】

半導体装置 100B のアノード電極 150B は、導電性材料から成り、半導体層 112 の上面 112u にショットキー接合されたショットキー電極である。アノード電極 150B は、上面 112u に形成された第 1 の電極である。本実施形態では、アノード電極 15

50

0 B は、電子ビーム蒸着法によって、半導体層 112 側から順に、厚さ約 100 nm のニッケル (Ni) から主に成る層と、厚さ約 100 nm のパラジウム (Pd) から主に成る層と、厚さ約 20 nm のモリブデン (Mo) から主に成る層とを積層した電極である。

【0069】

半導体装置 100 B の絶縁膜 160 B は、周囲面 112 p から側面 112 s を通じてアノード電極 150 B の上にわたって形成され、アノード電極 150 B の上に開口部 168 B を有する点を除き、第 1 実施形態の絶縁膜 160 と同様である。本実施形態では、絶縁膜 160 の側面部 164 は、基点 P5 の周辺に段差を有する。他の実施形態では、側面部 164 は、基点 P5 から基点 P6 にかけてなだらかであってもよい。

【0070】

半導体装置 100 B の配線電極 180 B は、アノード電極 150 B のうち開口部 168 B から露出した部分から、上面部 162、側面部 164 および周囲部 166 の上にわたって一体的に形成された第 2 の電極である。これによって、配線電極 180 B は、半導体層 112 との間に絶縁膜 160 B を挟むフィールドプレート構造を形成する。

【0071】

本実施形態では、配線電極 180 B は、スパッタ法によって、アノード電極 150 B および絶縁膜 160 B の側から順に、厚さ約 20 nm のチタン (Ti) から主に成る層と、厚さ約 200 nm の窒化チタン (TiN) から主に成る層と、厚さ約 20 nm のチタン (Ti) から主に成る層と、厚さ約 2000 nm のアルミニウム - ケイ素合金 (AlSi) から主に成る層とを積層した電極である。配線電極 180 におけるチタン (Ti) は、隣接する電極層および絶縁膜 160 との密着性を向上させる。配線電極 180 B における窒化チタン (TiN) は、バリアメタルとして電極層間における電極材料の相互拡散を防止する。配線電極 180 B におけるアルミニウム - ケイ素合金 (AlSi) は、配線電極 180 における電気抵抗を抑制する。

【0072】

図 7 は、第 2 実施形態における半導体装置 100 B の製造方法を示す工程図である。半導体装置 100 B の製造者は、第 1 実施形態と同様に半導体層 112 にメサ構造 112 m を形成した後 (工程 P120)、アノード電極 150 B を形成する (工程 P150)。本実施形態では、製造者は、リフトオフ法を用いた電子ビーム蒸着法によってアノード電極 150 B を形成する。アノード電極 150 B を形成する方法は、電子ビーム蒸着法に限らず、抵抗加熱蒸着法であってもよいし、スパッタ法であってもよい。他の実施形態では、製造者は、半導体層 112 の全面に電極を形成した後、その電極の一部を除去することによって、アノード電極 150 B を形成してもよい。本実施形態では、製造者は、半導体層 112 側から順に、ニッケル (Ni) から主に成る層と、パラジウム (Pd) から主に成る層と、モリブデン (Mo) から主に成る層とを積層することによって、アノード電極 150 B を形成する。

【0073】

アノード電極 150 B を形成した後 (工程 P150)、製造者は、半導体層 112 の + Z 軸方向側の表面およびアノード電極 150 B の表面に、絶縁膜 160 B の元となる絶縁膜を形成する (工程 P162B)。本実施形態では、製造者は、原子層堆積法 (ALD) によって酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) から主に成る層を形成した後、プラズマ化学気相成長法 (Plasma CVD) によって二酸化ケイ素 (SiO<sub>2</sub>) から主に成る層を積層することによって、絶縁膜 160 B の元となる絶縁膜を形成する。

【0074】

絶縁膜 160 B の元となる絶縁膜を形成した後 (工程 P162B)、製造者は、第 1 実施形態と同様に、絶縁膜 160 B の元となる絶縁膜をウェットエッティングによって加工することによって、絶縁膜 160 B の開口部 168 B を形成する (工程 P164B, P168B)。これによって、薄肉化された上面部 162 および側面部 164 を有する絶縁膜 160 B が形成される。

【0075】

10

20

30

40

50

絶縁膜 160 を形成した後（工程 P168B）、製造者は、配線電極 180B を形成する（工程 P180）。本実施形態では、製造者は、アノード電極 150B および絶縁膜 160B の側から順に、厚さ約 20nm のチタン（Ti）から主に成る層と、厚さ約 200nm の窒化チタン（TiN）から主に成る層と、厚さ約 2000nm のアルミニウム - ケイ素合金（AlSi）から主に成る層とを積層することによって、配線電極 180B を形成する。本実施形態では、製造者は、配線電極 180B の元となる電極をアノード電極 150B および絶縁膜 160B の全面にスパッタ法によって形成する。その後、製造者は、配線電極 180 として残す部分にマスク（フォトレジスト）を形成した後、塩素（Cl）系のドライエッチングによって電極の一部を除去することによって、配線電極 180B を形成する。その後、製造者は、配線電極 180B の上に形成されているマスクを除去する。10

#### 【0076】

配線電極 180B を形成した後（工程 P180）、製造者は、第 1 実施形態と同様にカソード電極 190 を形成する（工程 P190）。これらの工程を経て、半導体装置 100 が完成する。他の実施形態では、製造者は、半導体層 112 を形成した後（工程 P110）であれば、カソード電極 190 を形成する工程（工程 P190）を、配線電極 180B を形成する工程（工程 P180）に先立って実施してもよい。

#### 【0077】

以上説明した第 2 実施形態によれば、第 1 実施形態と同様に、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーク電流の抑制とを両立できる。20

#### 【0078】

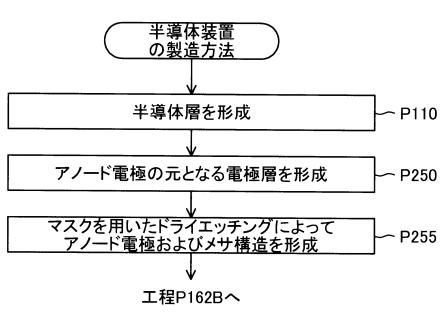

#### C. 第 3 実施形態

図 8 は、第 3 実施形態における半導体装置 100B の製造方法を示す工程図である。第 2 実施形態の半導体装置 100B は、その製造方法が異なる点を除き、第 2 実施形態と同様である。

#### 【0079】

第 2 実施形態と同様に半導体層 112 を形成した後（工程 P110）、製造者は、アノード電極 150B の元となる電極層を半導体層 112 の全面にわたって形成する（工程 P250）。本実施形態では、製造者は、電子ビーム蒸着法によって電極層を形成する。電極層を形成する方法は、電子ビーム蒸着法に限らず、抵抗加熱蒸着法であってもよいし、スパッタ法であってもよい。30

#### 【0080】

アノード電極 150B の元となる電極層を形成した後（工程 P250）、製造者は、マスクを用いたドライエッチングによって、アノード電極 150B およびメサ構造 112m を形成する（工程 P255）。本実施形態では、製造者は、メサ構造 112m に対応するマスク（フォトレジスト）を形成した後、塩素（Cl）系のドライエッチングによって半導体層 112 の一部および電極層の一部を除去することによって、アノード電極 150B およびメサ構造 112m を形成する。アノード電極 150B およびメサ構造 112m を形成した後（工程 P255）、製造者は、第 2 実施形態と同様に、絶縁膜 160B を形成し（工程 P162B, P164B, P168B）、それ以降の工程を実施する。40

#### 【0081】

以上説明した第 3 実施形態によれば、第 2 実施形態と同様に、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーク電流の抑制とを両立できる。また、アノード電極 150B の端部と上面 112u の端部との間の距離を抑制できるため、アノード電極 150B の端部における電解集中を効果的に抑制できる。

#### 【0082】

#### D. 第 4 実施形態

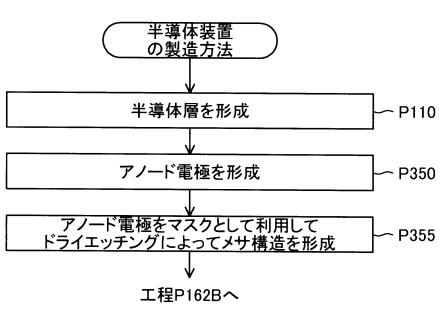

図 9 は、第 4 実施形態における半導体装置 100B の製造方法を示す工程図である。第 4 実施形態の半導体装置 100B は、その製造方法が異なる点を除き、第 2 実施形態と同様である。50

## 【0083】

第2実施形態と同様に半導体層112を形成した後（工程P110）、製造者は、半導体層112の上にアノード電極150Bを形成する（工程P350）。本実施形態では、製造者は、リフトオフ法を用いた電子ビーム蒸着法によってアノード電極150Bを形成する。アノード電極150Bを形成する方法は、電子ビーム蒸着法に限らず、抵抗加熱蒸着法であってもよいし、スパッタ法であってもよい。他の実施形態では、製造者は、半導体層112の全面に電極を形成した後、その電極の一部を除去することによって、アノード電極150Bを形成してもよい。

## 【0084】

アノード電極150Bを形成した後（工程P350）、製造者は、アノード電極150Bをマスクとして用いたドライエッチングによって、半導体層112にメサ構造112mを形成する（工程P355）。本実施形態では、製造者は、塩素（C1）系のドライエッチングによって半導体層112の一部を除去することによって、半導体層112にメサ構造112mを形成する。メサ構造112mを形成した後（工程P355）、製造者は、第2実施形態と同様に、絶縁膜160Bを形成し（工程P162B, P164B, P168B）、それ以降の工程を実施する。

## 【0085】

以上説明した第4実施形態によれば、第2実施形態と同様に、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーク電流の抑制とを両立できる。また、アノード電極150Bを利用した自己整合によって、メサ構造112mを形成するマスクを別途作製する必要がないため、製造コストを抑制できる。また、アノード電極150Bの端部と上面112uの端部との間の距離を抑制できるため、アノード電極150Bの端部における電解集中を効果的に抑制できる。

## 【0086】

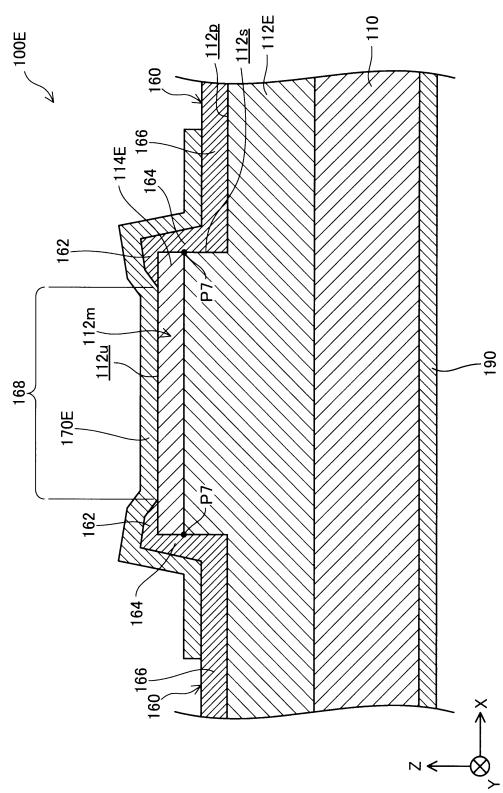

## E. 第5実施形態

図10は、第5実施形態における半導体装置100Eの構成を模式的に示す断面図である。本実施形態では、半導体装置100Eは、縦型pn接合ダイオードである。半導体装置100Eは、半導体層112およびアノード電極170に代えて、半導体層112Eと、半導体層114Eと、アノード電極170Eとを備える点を除き、第1実施形態の半導体装置100と同様である。

## 【0087】

半導体装置100Eの半導体層112Eは、基板110の+Z軸方向側に位置し、X軸およびY軸に沿って広がるn型半導体層である。半導体層112Eは、メサ構造112mの+Z軸方向側に半導体層114Eが積層されている点を除き、第1実施形態の半導体層112と同様である。

## 【0088】

半導体装置100Eの半導体層114Eは、メサ構造112mにおいて半導体層112Eの+Z軸方向側にX軸およびY軸に沿って広がるp型半導体層である。本実施形態では、半導体層114Eは、窒化ガリウム（GaN）から主に成る。本実施形態では、半導体層114Eは、マグネシウム（Mg）をアクセプタとして含有する。半導体装置100Eにおいて、基点P7は、半導体層112Eと半導体層114Eとのpn接合界面の端部であり、側面112sに位置する。

## 【0089】

半導体装置100Eのアノード電極170Eは、導電性材料から成り、半導体層114Eの上面112uにオーミック接合されたオーミック電極である。アノード電極170Eは、開口部168の内側から、上面部162、側面部164および周囲部166の上にわたって形成されている。これによって、アノード電極170Eは、半導体層112E, 114Eとの間に絶縁膜160を挟むフィールドプレート構造を形成する。本実施形態では、アノード電極170Eは、上面112uのうち開口部168から露出した部分から、上面部162、側面部164および周囲部166の上にわたって一体的に形成されている。

10

20

30

40

50

本実施形態では、アノード電極 170E は、半導体層 114E 側から順に、ニッケル (Ni) から主に成る層と、金 (Au) から主に成る層とを積層した電極である。

#### 【0090】

以上説明した第5実施形態によれば、上面部 162 および側面部 164 の薄肉化によって、pn接合界面の端部である基点 P7 に発生する電界集中を緩和できる。そのため、第1実施形態と同様に、製造工程の煩雑化を回避しながら、絶縁破壊の防止と逆方向リーケ電流の抑制とを両立できる。

#### 【0091】

##### F. 他の実施形態

本発明は、上述の実施形態や実施例、変形例に限られるものではなく、その趣旨を逸脱しない範囲において種々の構成で実現することができる。例えば、発明の概要の欄に記載した各形態中の技術的特徴に対応する実施形態、実施例、変形例中の技術的特徴は、上述の課題の一部または全部を解決するために、あるいは、上述の効果の一部または全部を達成するために、適宜、差し替えや、組み合わせを行うことが可能である。また、その技術的特徴が本明細書中に必須なものとして説明されていなければ、適宜、削除することが可能である。

10

#### 【0092】

本発明が適用される半導体装置は、上述の実施形態で説明した半導体装置に限らず、メサ構造にフィールドプレート構造を組み合わせた半導体装置であればよい。例えば、ショットキーバリアダイオードである第2実施形態の半導体装置 100B を、第5実施形態と同様に、pn接合ダイオードに適用してもよい。

20

#### 【0093】

上述の実施形態において、n型半導体層に含まれるドナー元素は、ケイ素 (Si) に限らず、ゲルマニウム (Ge)、酸素 (O) などであってもよい。上述の実施形態において、p型半導体層に含まれるアクセプタ元素は、マグネシウム (Mg) に限らず、亜鉛 (Zn)、炭素 (C) などであってもよい。

上述の実施形態において、基板の材質は、窒化ガリウム (GaN) に限らず、ケイ素 (Si)、サファイア (Al<sub>2</sub>O<sub>3</sub>) および炭化ケイ素 (SiC) などのいずれであってもよい。

#### 【0094】

30

上述の実施形態において、半導体層の材質は、窒化ガリウム (GaN) に限らず、ケイ素 (Si)、ゲルマニウム (Ge)、III-V 族化合物（例えば、窒化アルミニウムガリウム (AlGaN)、窒化インジウムガリウム (InGaN)、ヒ化ガリウム (GaAs)、リン化インジウム (InP) など）、炭化ケイ素 (SiC)、酸化ガリウム (Ga<sub>2</sub>O<sub>3</sub>)、ワイトバンドギャップ半導体（例えば、ダイヤモンド）などのいずれであってもよい。半導体層は、1つの半導体層であってもよいし、複数の半導体層であってもよい。

#### 【0095】

上述の実施形態において、ショットキー電極の材質は、ニッケル (Ni)、パラジウム (Pd)、白金 (Pt)、金 (Au)、モリブデン (Mo) およびイリジウム (Ir) の少なくとも1つであればよい。ショットキー電極は、1つの電極層であってもよいし、複数の電極層であってもよい。

40

#### 【0096】

上述の実施形態において、配線電極の材質は、アルミニウム (Al)、チタン (Ti)、モリブデン (Mo)、バナジウム (V)、タンタル (Ta)、金 (Au) および銅 (Cu) の少なくとも1つであればよい。これによって、電気抵抗を抑制しつつ絶縁膜との密着性を十分に確保できる。配線電極は、1つの電極層であってもよいし、複数の電極層であってもよい。例えば、配線電極は、アルミニウム (Al) から主に成る1つの電極層であってもよいし、アルミニウム - ケイ素合金 (AlSi) から主に成る1つの電極層であってもよい。配線電極は、ショットキー電極および絶縁膜の側から順に、チタン (Ti) から主に成る層と、窒化チタン (TiN) から主に成る層と、チタン (Ti) から主に成

50

る層と、アルミニウム(Al)から主に成る層とを積層した電極であってもよい。配線電極は、ショットキー電極および絶縁膜の側から順に、タンタル(Ta)から主に成る層と、銅(Cu)から主に成る層とを積層した電極であってもよい。配線電極は、ショットキー電極および絶縁膜の側から順に、窒化タンタル(TaN)から主に成る層と、銅(Cu)から主に成る層とを積層した電極であってもよい。

#### 【0097】

上述の実施形態において、絶縁膜の材質は、二酸化ケイ素(SiO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、窒化ケイ素(SiNx)、酸窒化ケイ素(SiON)、酸窒化ジルコニウム(ZrON)、酸窒化アルミニウム(AlON)、酸化ジルコニウム(ZrO<sub>2</sub>)および酸化ハフニウム(HfO)の少なくとも1つであればよい。これによって、逆方向リーキ電流を十分に抑制できる。絶縁膜は、1つの絶縁層であってもよいし、複数の絶縁層であってもよい。例えば、絶縁膜は、窒化ケイ素(SiNx)から主になる1つの絶縁層であってもよい。絶縁膜の最外層は、窒化ケイ素(SiNx)から主になる層であってもよい。これによって、二酸化ケイ素(SiO<sub>2</sub>)と比較して、絶縁膜とマスクとの密着力を抑制できるため、絶縁膜とマスクとの間にエッチャントを容易に入り込ませることができる。

10

#### 【符号の説明】

#### 【0098】

100, 100B, 100E, 100d, 100p ... 半導体装置

20

110 ... 基板

112 ... 半導体層

112E ... 半導体層

112m ... メサ構造

112p ... 周囲面

112s ... 側面

112u ... 上面

114E ... 半導体層

150B ... アノード電極

160, 160B, 160d ... 絶縁膜

30

162, 162d ... 上面部

164, 164d ... 側面部

166, 166d ... 周囲部

168, 168B ... 開口部

170, 170E ... アノード電極

180, 180B ... 配線電極

190 ... カソード電極

910 ... マスク

918 ... マスク開口部

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

## フロントページの続き

| (51)Int.Cl. |                  | F I     |               |

|-------------|------------------|---------|---------------|

| H 0 1 L     | 29/06 (2006.01)  | H 0 1 L | 29/44 Y       |

| H 0 1 L     | 29/861 (2006.01) | H 0 1 L | 29/48 E       |

| H 0 1 L     | 29/868 (2006.01) | H 0 1 L | 29/48 P       |

|             |                  | H 0 1 L | 29/48 M       |

|             |                  | H 0 1 L | 29/06 3 0 1 M |

|             |                  | H 0 1 L | 29/86 3 0 1 D |

|             |                  | H 0 1 L | 29/86 3 0 1 E |

|             |                  | H 0 1 L | 29/06 3 0 1 F |

|             |                  | H 0 1 L | 29/86 3 0 1 M |

|             |                  | H 0 1 L | 29/86 3 0 1 P |

|             |                  | H 0 1 L | 29/91 D       |

|             |                  | H 0 1 L | 29/91 F       |

審査官 正山 旭

(56)参考文献 特開2014-013886 (JP, A)

国際公開第2010/016388 (WO, A1)

特開2015-023073 (JP, A)

特開平08-139341 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 3 1 6

H 0 1 L 2 1 / 3 2 9

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 1 / 3 3 8

H 0 1 L 2 9 / 8 7 2

H 0 1 L 2 9 / 0 6

H 0 1 L 2 9 / 4 1 7

H 0 1 L 2 9 / 4 7

H 0 1 L 2 9 / 8 0

H 0 1 L 2 9 / 8 6 1