(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-238372

(P2012-238372A)

(43) 公開日 平成24年12月6日(2012.12.6)

| (51) Int.Cl.            | F 1          | テーマコード (参考)       |

|-------------------------|--------------|-------------------|

| G 11 C 15/04 (2006.01)  | G 11 C 15/04 | 6 O 1 R 5 F 0 8 3 |

| H 01 L 27/105 (2006.01) | H 01 L 27/10 | 4 4 1 5 F 1 1 O   |

| H 01 L 27/10 (2006.01)  | H 01 L 27/10 | 4 8 1             |

| H 01 L 29/786 (2006.01) | H 01 L 27/10 | 4 9 1             |

|                         | H 01 L 29/78 | 6 1 8 B           |

審査請求 未請求 請求項の数 6 O L (全 36 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2012-99368 (P2012-99368)   |

| (22) 出願日     | 平成24年4月25日 (2012. 4. 25)     |

| (31) 優先権主張番号 | 特願2011-101468 (P2011-101468) |

| (32) 優先日     | 平成23年4月28日 (2011. 4. 28)     |

| (33) 優先権主張国  | 日本国 (JP)                     |

|            |                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 出願人   | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地                                                                                                                                                                                                                 |

| (72) 発明者   | 高橋 康之<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                                                                                                                                                                                   |

| F ターム (参考) | 5F083 AD02 AD14 AD69 EP22 EP75<br>GA01 GA05 GA06 GA09 GA18<br>GA21 GA25 GA27 GA28 HA02<br>HA06 HA08 JA02 JA05 JA06<br>JA12 JA19 JA35 JA36 JA37<br>JA39 JA40 JA42 JA44 JA53<br>LA02 LA09 LA10 MA06 MA19<br>PR03 PR05 PR22 PR33 PR34<br>ZA12 ZA13 ZA14 ZA15 ZA23 |

|            | 最終頁に続く                                                                                                                                                                                                                                                         |

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参考回路を有し、参考回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1端子がピット線に電気的に接続され、ゲートがワード線に電気的に接続され、酸化物半導体を半導体層に有する第1のトランジスタと、第1電極が前記第1のトランジスタの第2端子に電気的に接続され、第2電極がデータ線に電気的に接続された容量素子とを、有するメモリ回路と、

ゲートが前記第1のトランジスタの第2端子及び前記容量素子の第1電極に電気的に接続された第2のトランジスタを有する参照回路と、を有する複数のメモリセルを有し、

前記複数のメモリセルが、前記ピット線が延設された方向及び前記ワード線が延設された方向に複数設けられ、

前記ワード線が延設された方向に隣接する前記メモリセル間では、前記第2のトランジスタの第1端子と第2端子とが電気的に直列接続されており、当該直列接続された前記第2のトランジスタには判定回路が電気的に接続される半導体記憶装置。

**【請求項 2】**

請求項1において、前記第2のトランジスタが単結晶シリコンを半導体層に有する半導体記憶装置。

**【請求項 3】**

請求項2において、前記第1のトランジスタと前記第2のトランジスタとが積層して設けられている半導体記憶装置。

**【請求項 4】**

請求項1において、前記第2のトランジスタが酸化物半導体を半導体層に有する半導体記憶装置。

**【請求項 5】**

請求項4において、前記第1のトランジスタの半導体層と前記第2のトランジスタの半導体層とが同じ層に設けられる半導体記憶装置。

**【請求項 6】**

請求項1乃至請求項5のいずれか一において、前記判定回路は前記直列接続された前記第2のトランジスタの導通状態または非導通状態に応じた電位の変動を検出する回路である半導体記憶装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

半導体記憶装置に関する。特に半導体記憶装置内の格納された検索したいデータを高速に探し出すことが可能な半導体記憶装置に関する。

**【背景技術】****【0002】**

連想メモリ( C A M : Content Addressable Memory )は、アドレスを指定して格納されたデータを読み出す半導体記憶装置とは異なり、格納されたデータと検索したいデータとを比較することで整合するデータのアドレスを取得し、高速な検索を可能にした半導体記憶装置である。

**【0003】**

C A Mとしては、特許文献1に記載のように揮発性の記憶装置を用いる構成がある。揮発性の記憶装置を用いるC A Mの構成では、電源電圧の供給が停止した時点で記憶されたデータが消失してしまう。特に電源電圧の供給を安定的に得ることが困難なモバイル機器において、電源電圧の供給が停止することに伴うデータの消失は、利便性に欠けるものである。

**【0004】**

そこで近年では、特許文献2に記載のように不揮発性の記憶装置を用いるC A Mの構成が提案されている。特許文献2の構成では、電源電圧の供給が停止した場合のデータの消失を防ぐために、相変化材料を用いた不揮発性の記憶装置をC A Mに用いる構成について開

10

20

30

40

50

示している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特表2004-525473号公報

【特許文献2】特表2008-545221号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、相変化材料を用いたメモリ回路を有する不揮発性の記憶装置をC A Mに用いる構成では、データの書き込み時において、相変化材料に電流を流して熱起因による相変化材料の構造の相変化を促す必要がある。

【0007】

電流を流すことによってデータの書き込みを行う不揮発性の記憶装置を有するC A Mは、複数のメモリセルに一斉に電流を流してデータの書き込みを行うことが難しい。また、データを書き込むための電流を生成する回路を新たに設ける必要がある。そのため、消費電力が増加するといった問題がある。

【0008】

また、電流を流すことによってデータの書き込みを行う不揮発性の記憶装置を有するC A Mは、繰り返しの書き込みに伴う劣化が問題となる。

【0009】

また、電流を流すことによってデータの書き込みを行う不揮発性の記憶装置を有するC A Mは、データの書き込み時に熱を生じさせる必要がある。そのためメモリ回路の高密度化を図ることが難しくなるといった問題がある。

【0010】

そこで本発明の一態様では、不揮発性の記憶装置を有するC A Mとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また本発明の一態様は、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また本発明の一態様は、メモリセルの高密度化が可能な不揮発性の記憶装置を提供することを課題の一とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索を可能にした半導体記憶装置である。

【0012】

本発明の一態様は、第1端子がビット線に電気的に接続され、ゲートがワード線に電気的に接続され、酸化物半導体を半導体層に有する第1のトランジスタと、第1電極が第1のトランジスタの第2端子に電気的に接続され、第2電極がデータ線に電気的に接続された容量素子とを、有するメモリ回路と、ゲートが第1のトランジスタの第2端子及び容量素子の第1電極に電気的に接続された第2のトランジスタを有する参照回路と、を有するメモリセルが、ビット線が延設された方向及びワード線が延設された方向に複数設けられ、ワード線が延設された方向に隣接するメモリセル間では、第2のトランジスタの第1端子と第2端子とが電気的に直列接続されており、当該直列接続された第2のトランジスタには判定回路が電気的に接続される半導体記憶装置である。

【0013】

本発明の一態様において、第2のトランジスタが単結晶シリコンを半導体層に有する半導体記憶装置が好ましい。

10

20

30

40

50

## 【0014】

本発明の一態様において、第1のトランジスタと第2のトランジスタとが積層して設けられている半導体記憶装置が好ましい。

## 【0015】

本発明の一態様において、第2のトランジスタが酸化物半導体を半導体層に有する半導体記憶装置が好ましい。

## 【0016】

本発明の一態様において、第1のトランジスタの半導体層と第2のトランジスタの半導体層とが同じ層に設けられる半導体記憶装置が好ましい。

## 【0017】

本発明の一態様において、判定回路は直列接続された第2のトランジスタの導通状態又は非導通状態に応じた電位の変動を検出するための回路である半導体記憶装置が好ましい。

## 【発明の効果】

## 【0018】

本発明の一態様により、不揮発性の記憶装置を有するCAMとする際に低消費電力化を図ることができる。また本発明の一態様により、データの書き込みを繰り返し行う際の劣化をなくすことができる。また本発明の一態様は、メモリセルの高密度化を図ることができる。

## 【図面の簡単な説明】

## 【0019】

【図1】半導体記憶装置の例を示す回路図。

【図2】半導体記憶装置の例を示す回路図。

【図3】半導体記憶装置の例を示す回路図。

【図4】半導体記憶装置の例を示す回路図およびタイミングチャート図。

【図5】半導体記憶装置の例を示す回路図。

【図6】半導体記憶装置の例を示す回路図。

【図7】半導体記憶装置を用いたCPUのブロック図。

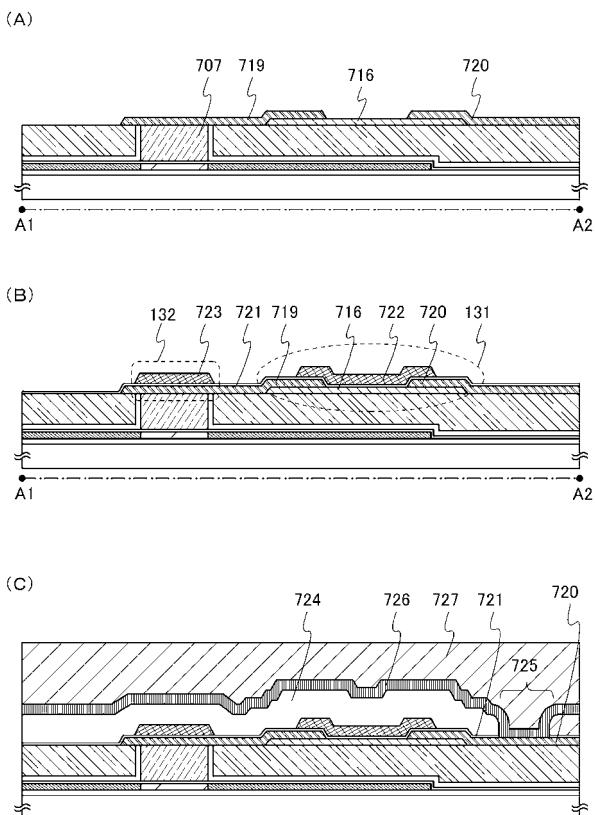

【図8】半導体記憶装置の作製工程を示す図。

【図9】半導体記憶装置の作製工程を示す図。

【図10】半導体記憶装置の作製工程を示す図。

【図11】半導体記憶装置の構成を示す断面図。

【図12】本発明の一態様に係る酸化物材料の構造を説明する図。

【図13】本発明の一態様に係る酸化物材料の構造を説明する図。

【図14】本発明の一態様に係る酸化物材料の構造を説明する図。

## 【発明を実施するための形態】

## 【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面において、同じものを指す符号は異なる図面間でも共通して用いる。

## 【0021】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、信号波形、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

## 【0022】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。

## 【0023】

なお本明細書においては、トランジスタのソース及びドレインとして機能する領域を、電

10

20

30

40

50

位の高低に応じて区別することなく、第1端子、第2端子と表記する場合がある。あるいは、それを第1の電極、第2の電極と表記する場合がある。あるいは、ソース領域、ドレイン領域と表記する場合がある。

#### 【0024】

なお明細書においては、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。具体的には、トランジスタをはじめとするスイッチング素子を介してAとBとが接続され、該スイッチング素子の導通によって、AとBとが概略同電位となる場合や、抵抗素子を介してAとBとが接続され、該抵抗素子の両端に発生する電位差が、AとBとを含む回路の動作に影響しない程度となっている場合など、回路動作を考えた場合、AとBとの間の部分と同じノードとして捉えて差し支えない状態である場合を表す。

#### 【0025】

##### (実施の形態1)

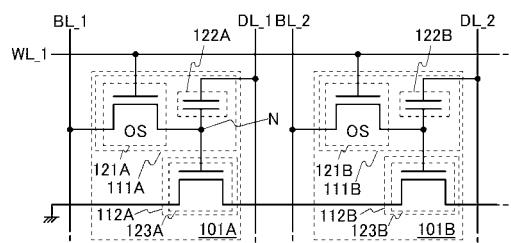

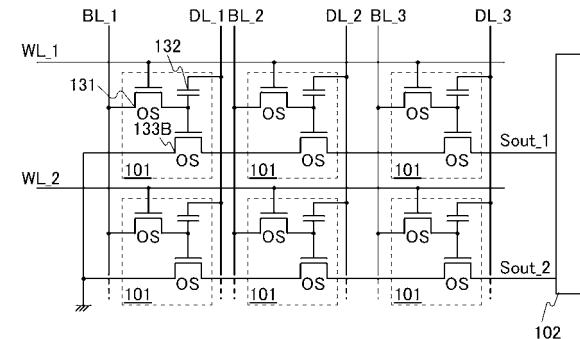

本実施の形態では、CAMとして動作可能な半導体記憶装置の構成について、図1を用いて説明する。

#### 【0026】

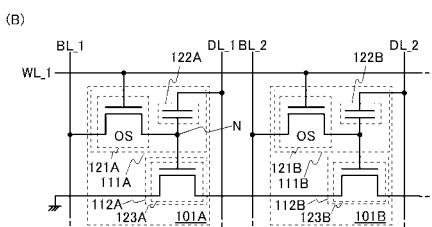

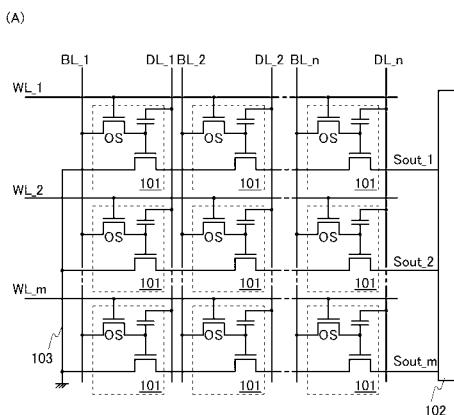

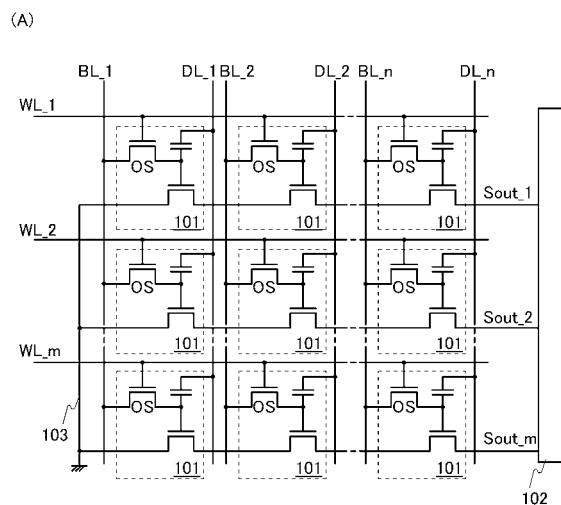

図1(A)はm行n列(m、nは自然数)のメモリセルを有する半導体記憶装置の回路図である。図1(A)に示す半導体記憶装置は、ビット線BL\_1乃至BL\_nと、ワード線WL\_1乃至WL\_mと、データ線DL\_1乃至DL\_nと、複数のメモリセル101と、判定回路102、を有する。

#### 【0027】

メモリセル101は、ビット線BL\_1乃至BL\_nのいずれか一、ワード線WL\_1乃至WL\_mのいずれか一、データ線DL\_1乃至DL\_nのいずれか一に接続されている。またメモリセル101は、行方向、すなわちワード線WL\_1乃至WL\_mが延設された方向に接続されており、一方の端部では出力信号線Sout\_1乃至Sout\_mが判定回路102に接続され、他方の端部では共通の電源線103(図1(A)ではGND線)に接続されている。

#### 【0028】

判定回路102は、ワード線WL\_1乃至WL\_mが延設された方向におけるメモリセルの導通状態又は非導通状態に応じて変化する、出力信号線Sout\_1乃至Sout\_mの電位を検出するための回路である。

#### 【0029】

図1(B)では、図1(A)のメモリセル101の構成を示す。なお図1(A)で示すようにメモリセル101は、ビット線が延設された方向(図1(A)で列方向)、及びワード線が延設された方向(図1(A)で行方向)にマトリクス状に設けられる。ここで図1(B)では図1(A)のメモリセル101のうち隣接するメモリセルの一例として、1行1列のメモリセルをメモリセル101A、1行2列のメモリセルをメモリセル101Bとして説明する。

#### 【0030】

図1(B)に示すメモリセル101Aは、第1のトランジスタ121A及び容量素子122Aを有するメモリ回路111Aと、第2のトランジスタ123Aを有する参照回路112Aとで構成される。

#### 【0031】

第1のトランジスタ121Aの第1端子はビット線BL\_1に接続されている。第1のトランジスタ121Aのゲートはワード線WL\_1に接続されている。容量素子122Aの第1電極は、第1のトランジスタ121Aの第2端子に接続されている。容量素子122Aの第2電極は、データ線DL\_1に接続されている。第2のトランジスタ123Aの第1端子は電源線103に接続されている。第2のトランジスタ123Aのゲートは第1のトランジスタ121Aの第2端子及び容量素子122Aの第1電極に接続されている。

## 【0032】

図1(B)に示すメモリセル101Bは、第1のトランジスタ121B及び容量素子122Bを有するメモリ回路111Bと、第2のトランジスタ123Bを有する参照回路112Bとで構成される。

## 【0033】

第1のトランジスタ121Bの第1端子はビット線BL\_2に接続されている。第1のトランジスタ121Bのゲートはワード線WL\_1に接続されている。容量素子122Bの第1電極は、第1のトランジスタ121Bの第2端子に接続されている。容量素子122Bの第2電極は、データ線DL\_2に接続されている。第2のトランジスタ123Bの第1端子は第2のトランジスタ123Aの第2端子に接続されている。第2のトランジスタ123Bのゲートは第1のトランジスタ121Bの第2端子及び容量素子122Bの第1電極に接続されている。10

## 【0034】

なお参照回路112A及び112Bは、ワード線が延設された方向において、隣り合う関係にあるメモリセルの中の第2のトランジスタ123Bの第1端子と第2のトランジスタ123Aの第2端子とが接続されるようにして直列接続される。すなわち、第2トランジスタ123Aの第2端子及び第2のトランジスタ123Bの第1端子を、ワード線が延設された方向で直列接続させ、且つ1列目となる第2のトランジスタ123Aの第1端子が電源線103に接続され、n列目となる第2のトランジスタ123Bの第2端子が出力信号線Sout\_1乃至Sout\_mの各配線を介して判定回路102に接続される。20

## 【0035】

従って参照回路である第2のトランジスタの導通状態により、出力信号線Sout\_1乃至Sout\_mと電源線103との間の導通状態が決まる。各列の第2のトランジスタが全て導通状態となることで、出力信号線Sout\_1乃至Sout\_mと電源線103とが導通状態となる。逆に各列の第2のトランジスタがいずれか一つでも非導通状態となることで、出力信号線Sout\_1乃至Sout\_mと電源線103とが非導通状態となる。

## 【0036】

参照回路における第2のトランジスタの導通状態を検出することにより、半導体記憶装置はメモリセルに格納されたデータと検索したいデータとを比較し、判定回路102で整合するデータのアドレスを取得し、高速な検索を可能にすることができる。30

## 【0037】

なお本実施の形態では、検索したいデータと一致する、メモリセルに格納されたデータを、当該メモリセルの参照回路における第2のトランジスタの導通状態又は非導通状態を検出することによって検索する。従って格納されたデータとしては、検索したいデータを入力した際に、参照回路における第2のトランジスタの導通状態又は非導通状態が変化するようなデータであることが好ましい。

## 【0038】

なお検索したいデータは、データ線DL\_1乃至DL\_nを介して各メモリセルに入力する。データ線DL\_1乃至DL\_nでは、検索したいデータに応じた電位の変動が行われる。当該電位の変動に応じて、メモリセル内の容量素子が容量結合により第2のトランジスタのゲートの電位を変動させる。そして第2のトランジスタの導通状態又は非導通状態を制御し、判定回路102で整合するデータのアドレスを取得することができる。40

## 【0039】

なお本実施の形態におけるメモリ回路111A、111Bの第1のトランジスタ121A、121Bには、オフ電流の小さいトランジスタを用いる。具体的には、高純度化された、バンドギャップが2.5eV以上の酸化物半導体、炭化シリコン又は窒化ガリウムなどを半導体層に用いたトランジスタとすればよい。前述の半導体層はバンドギャップが大きく、不純物準位が少ないため、キャリアの再結合が少なく、オフ電流が小さい。

## 【0040】

10

20

30

40

50

本実施の形態で説明する構成では第1のトランジスタの半導体層に、高純度化された、バンドギャップが2.5 eV以上の酸化物半導体を用いる構成とすることが好適である。ここで高純度化とは、酸化物半導体中の水素などの不純物が十分に除去されていること、又は、十分な酸素が供給されていることをいう。具体的には、例えば、酸化物半導体の水素濃度は $5 \times 10^{-9}$  atoms/cm<sup>3</sup>以下、望ましくは $5 \times 10^{-8}$  atoms/cm<sup>3</sup>以下、より望ましくは $5 \times 10^{-7}$  atoms/cm<sup>3</sup>以下とする。なお、上述の酸化物半導体中の水素濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)で測定したものである。

#### 【0041】

なお図1(A)、(B)での第1のトランジスタ121A、121Bは、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。なお図面において、第1のトランジスタ121A、121Bには酸化物半導体を有する半導体層にチャネルが形成されるトランジスタであることを示すために、OSの符号を付している。

10

#### 【0042】

このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体では、キャリア濃度が $1 \times 10^{12}$  atoms/cm<sup>3</sup>未満、望ましくは、 $1 \times 10^{11}$  atoms/cm<sup>3</sup>未満、より望ましくは $1.45 \times 10^{10}$  atoms/cm<sup>3</sup>未満となる。例えば、室温でのオフ電流(ここでは、単位チャネル幅(1 μm)あたりの値)は、100 zA/μm(1 zA(ゼプトアンペア)は $1 \times 10^{-21}$  A)以下、望ましくは、10 zA/μm以下となる。このように、i型化(真性化)又は実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性の第1のトランジスタとすることができます。

20

#### 【0043】

第1のトランジスタを極めて優れたオフ電流特性のトランジスタとした場合、非導通状態とした際に、ほぼ絶縁体とみなすことができる。従って第1のトランジスタをメモリ回路に用いることで、容量素子と第1のトランジスタが接続されたノード(図1(B)中のノードN)に保持された電位の低下を極めて小さいレベルに抑制できる。その結果、電源電圧の供給が停止した場合でも、ノードNの電位の変動を小さくでき、記憶されたデータの消失を防ぐことができる不揮発性のメモリ回路とすることができます。

30

#### 【0044】

なお保持されたデータの書き換えは、ワード線の電位を第1のトランジスタが導通状態となる電位にして、一斉にビット線の電位をノードNに与える。従ってデータの書き換えは、素子に直接電流を流してデータを保持させる構成ではなく、ビット線の電位を第1のトランジスタを介してノードNに与える構成とすることができます。そのため電流を流して複数のメモリセルの書き換えを行う構成と違って、複数のメモリセルにデータの書き換えを行っても大電流を流す必要がない。言い換えれば、複数のメモリセルの書き換えを一斉に行うことが可能である。

30

#### 【0045】

また本実施の形態の半導体記憶装置におけるメモリ回路は、電流によるデータの書き換えがないため、半導体記憶装置の周辺回路として、書き換え時に必要な電流を生成するための回路をなくすことができる。そのため、書き換えに必要な電流を生成するための回路がない分の消費電力を削減することが可能である。このため本発明の一態様により、不揮発性の記憶装置を有するCAMとする際に低消費電力化を図ることができる。

40

#### 【0046】

このように、本実施の形態の半導体記憶装置は、データの書き換えを、ノードでの電位の保持によって実現することができる。従って、本実施の形態の構成で示すメモリ回路の構成は、繰り返しデータの書き換えを行う構成とした際のメモリ素子の劣化を原理的になくすことができる。このため本発明の一態様により、電流を流すことでの書き込みを行っても、データの書き込みを繰り返し行う際の劣化をなくすことができる。

50

## 【0047】

また本実施の形態の半導体記憶装置は、メモリ回路にデータを書き込むために大きな電流を必要としない。そのため、電流が流れることによる発熱が小さく、メモリ回路を構成する素子に微細化及び積層化が可能なトランジスタ及び容量素子で構成することができる。よって、本発明の一態様は、メモリセルの高密度化を図ることができる。

## 【0048】

なお本実施の形態において第1のトランジスタは、nチャネル型トランジスタであるものとして説明したが、pチャネル型トランジスタを用いることもできる。ここで本実施の形態で説明する技術の本質は、オフ電流の小さい第1のトランジスタとする点にある。従つて、第1のトランジスタの半導体層に用いる材料については、酸化物半導体に限らず、オフ電流の小さいトランジスタとすることができます半導体であればよい。

10

## 【0049】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0050】

## (実施の形態2)

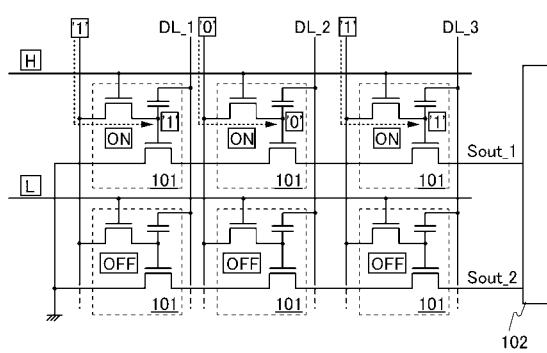

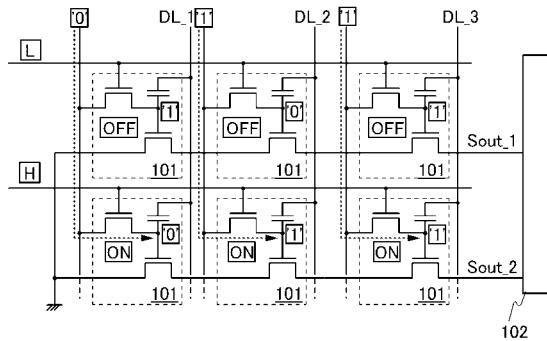

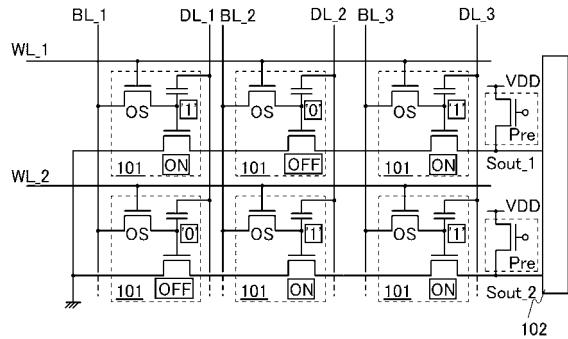

本実施の形態では、上記実施の形態1で説明した、CAMとして動作可能な半導体記憶装置の具体的な構成を示し、その構成及び動作の一例について図2乃至図5を用いて説明する。

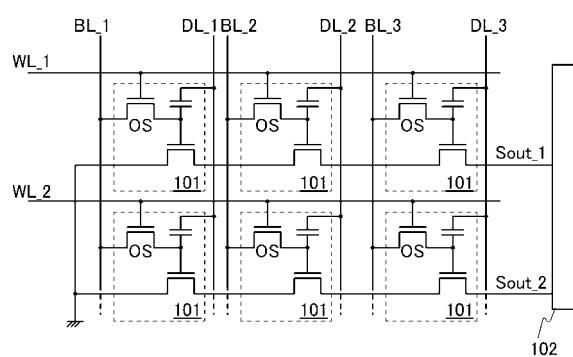

## 【0051】

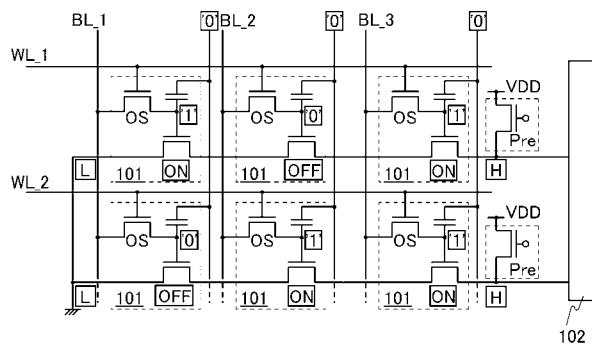

図2は図1(A)の一例として示す2行3列のメモリセルを有する半導体記憶装置の回路図である。図2に示す半導体記憶装置は、ビット線BL\_1乃至BL\_3と、ワード線WL\_1及びWL\_2と、データ線DL\_1乃至DL\_3と、2行3列のメモリセル101と、判定回路102、を有する。メモリセル101における各配線との接続、及びメモリセル内の回路構成については、図1(A)、(B)と同様である。

20

## 【0052】

次いで図3(A)、(B)では、図2の半導体記憶装置の各行にデータを書き込む際の動作について示す。なお各メモリセルのノードNに書き込むデータ'1'、又はデータ'0'は、電位の高低によって書き込まれる信号である。なお本実施の形態では、データ'1'がノードNに保持されることで第2のトランジスタを導通状態とすることができる電位である。また本実施の形態では、データ'0'がノードNに保持されることで第2のトランジスタを非導通状態とすることができる電位であるとして説明を行う。

30

## 【0053】

図3(A)では、1行1列目にデータ'1'、1行2列目にデータ'0'、1行3列目にデータ'1'を書き込む場合の動作について示したものである。データの書き換えは上記実施の形態1で説明したように、データを書き込む行に対応するワード線WL\_1の電位をHレベル(第1のトランジスタを導通状態とする電圧レベル)にして、1行一括してノードNにデータに相当する電位を書き込む(図3(A)中、点線矢印参照)。なおデータを書き込まない行に対応するワード線WL\_2の電位をLレベル(第1のトランジスタを非導通状態とする電圧レベル)にして、当該行のメモリセルのノードNにデータに相当する電位が書き込まれないようにする。

40

## 【0054】

次いで図3(B)では、2行1列目にデータ'0'、2行2列目にデータ'1'、2行3列目にデータ'1'を書き込む場合の動作について示したものである。データの書き換えは、データを書き込む行に対応するワード線WL\_2の電位をHレベルにして、一行一括してノードNにデータに相当する電位を書き込む(図3(B)中、点線矢印参照)。なおデータを書き込まない行に対応するワード線WL\_1の電位をLレベルにして、当該行のメモリセルのノードNにデータに相当する電位が書き込まれないようにする。ここで既にデータが書き込まれている1行目のメモリセルは、第1のトランジスタを非導通状態とすることで電源電圧の供給が停止してもデータの保持を可能とすることできる。

## 【0055】

50

図3(A)、(B)のようにして1行目のメモリセルにはワード線が延設された方向にデータ'101'が保存され、2行目のメモリセルにはワード線が延設された方向にデータ'011'が保存される。

#### 【0056】

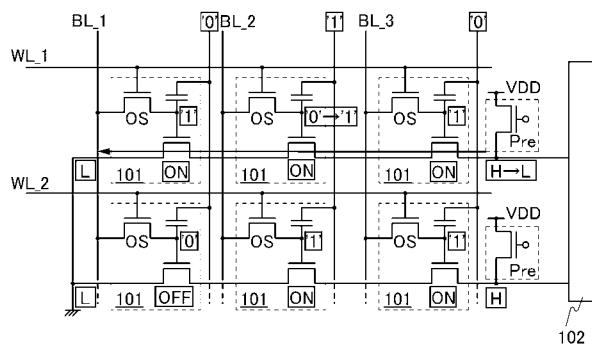

次いで参照回路における第2のトランジスタの導通状態を検出することにより、半導体記憶装置は格納されたデータと検索したいデータとを比較し、判定回路102で整合するデータのアドレスを取得する際の動作について回路図及びタイミングチャート図を用いて説明する。

#### 【0057】

なお以下では、図4(A)に示すように、図3(A)、(B)で2行3列のメモリセルに書き込んだデータを読み出す動作の一例について説明を行う。 10

#### 【0058】

また図4(A)では、図1(A)で図示していないプリチャージ回路Preを各出力信号線Sout\_1及びSout\_2に追加した構成について示している。プリチャージ回路Preは、データの読み出し動作の際、出力信号線Sout\_1及びSout\_2の電位を上昇させておくための回路である。プリチャージ回路Preの機能は、判定回路102で実現する構成としてもよい。

#### 【0059】

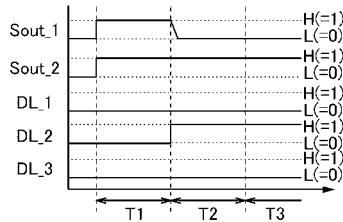

次いで図4(B)のタイミングチャート図について説明を行う。図4(B)のタイミングチャート図において、期間T1はプリチャージ期間、期間T2はデータ検索期間、期間T3はデータ出力期間である。 20

#### 【0060】

期間T1であるプリチャージ期間について説明する。データを読み出す前にプリチャージ回路Preにより出力信号線Sout\_1及びSout\_2の電位の電位を上昇させておく。このとき、データ線DL\_1乃至DL\_3は全てデータ'0'が入力されておくようになる。期間T1の各配線の信号の様子を図5(A)に示す。図5(A)に示すように参照回路の第2のトランジスタはワード線が延設された方向においていずれか一が非導通状態であり、電源線103と出力信号線Sout\_1又はSout\_2との間で電流は流れない。 30

#### 【0061】

次いで期間T2であるデータ検索期間について説明を行う。なお本実施の形態の説明では検索したいデータが'101'である場合について説明する。

#### 【0062】

データ'101'を検索する場合、1列目のデータ線DL\_1にデータ'0'、2列目のデータ線DL\_2にデータ'1'、3列目のデータ線DL\_3にデータ'0'を入力する。すなわち検索するデータとは反転した電位のデータをデータ線より入力する。するとデータ線よりデータ'1'を入力したメモリセルでは、メモリ回路内の容量素子を介してノードNの電位が容量結合により上昇し、参照回路である第2のトランジスタが導通状態となる。なお期間T2の前から第2のトランジスタが導通状態の場合、メモリ回路内の容量素子を介してノードNの電位が容量結合により上昇しても、導通状態に変化はない。期間T2の各配線の信号の様子を図5(B)に示す。 40

#### 【0063】

上述したようにデータ線の電位を変化させることで参照回路である第2のトランジスタの導通状態が変化する。検索したいデータ'101'がもともと書き込まれた1行目のメモリセルでは、データ線の電位の変化により、ワード線WL\_1が延設された方向の第2のトランジスタが全て導通状態となる。従って導通状態となった出力信号線Sout\_1と電源線103との間で電位差が生じることで電流が流れ(図5(B)中、実線矢印参照)、期間T1で上昇させておいた電位が下降する。

#### 【0064】

一方で検索したいデータ'101'がもともと書き込まれていない2行目のメモリセルで 50

は、データ線の電位の変化によりトランジスタの導通状態が変化しても、ワード線 W L \_ 2 が延設された方向の第 2 のトランジスタが全て導通状態とはならない。従って出力信号線 S o u t \_ 2 の電位が変化しない。

**【 0 0 6 5 】**

すなわち検索したいデータがある場合、データ線より検索したいデータの反転した電位を入力し、出力信号線と電源線との間の導通状態を検出することで、検索したいデータのアドレスを特定することができる。

**【 0 0 6 6 】**

次いでデータ出力期間 T 3 では、期間 T 2 での出力信号線の電位をラッチ回路等で保持しておき、導通状態となった出力信号線に対応するデータが格納されたメモリセルのアドレスを、判定回路 1 0 2 から外部回路に出力する。なお判定回路 1 0 2 としては、デマルチプレクサ回路等を用いて出力される信号のアドレスを検出する構成とすればよい。

10

**【 0 0 6 7 】**

以上説明したように、メモリセルに書き込まれたデータは、データ線の電位を変動させることで、高速に検索することができる。

**【 0 0 6 8 】**

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

**【 0 0 6 9 】**

( 実施の形態 3 )

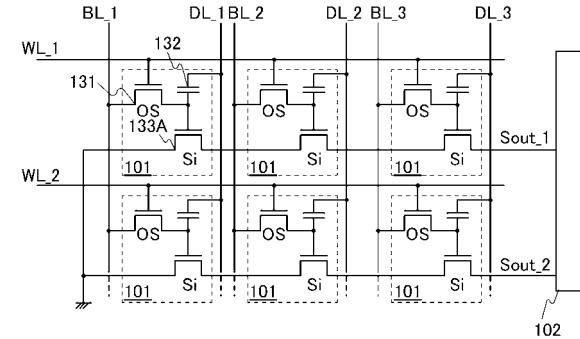

本実施の形態では、実施の形態 1 で示した参照回路における第 2 のトランジスタの構成について複数の形態を例示する。

20

**【 0 0 7 0 】**

第 2 のトランジスタは、上記実施の形態で説明したように導通状態又は非導通状態を検出することにより、高速なデータの検索を可能にするものである。従って第 2 のトランジスタの半導体層は、第 1 のトランジスタの半導体層と異なり、様々な材料を用いることが可能である。

**【 0 0 7 1 】**

例えば図 6 ( A ) は図 1 ( A ) と同様にメモリセルの構成を表す回路図である。図 6 ( A ) では第 1 のトランジスタ 1 3 1 、容量素子 1 3 2 、第 2 のトランジスタ 1 3 3 A を示している。第 2 のトランジスタ 1 3 3 A の半導体層にはシリコンを用いる構成とすることが可能である。

30

**【 0 0 7 2 】**

なお半導体層に用いるシリコンとしては、微結晶シリコン、多結晶シリコン、単結晶シリコン等を用いることが可能である。なお図 6 ( A ) で第 2 のトランジスタ 1 3 3 A はシリコンを有する半導体層にチャネルが形成されるトランジスタであることを示すために、S i の符号を付している。

30

**【 0 0 7 3 】**

また本発明の一態様は、シリコンで半導体層が形成された第 2 のトランジスタ 1 3 3 A と酸化物半導体層で半導体層が形成された第 1 のトランジスタ 1 3 1 を積層して形成することで、メモリセルの高密度化を図ることができる。

40

**【 0 0 7 4 】**

また別の構成として図 6 ( B ) は図 1 ( A ) と同様にメモリセルの構成を表す回路図である。図 6 ( B ) では第 1 のトランジスタ 1 3 1 、容量素子 1 3 2 、第 2 のトランジスタ 1 3 3 B を示している。第 2 のトランジスタ 1 3 3 B の半導体層には酸化物半導体を用いる構成とすることが可能である。

**【 0 0 7 5 】**

なお図 6 ( B ) で第 2 のトランジスタ 1 3 3 B は酸化物半導体を有する半導体層にチャネルが形成されるトランジスタであることを示すために、第 1 のトランジスタ 1 3 1 と同様に O S の符号を付している。

**【 0 0 7 6 】**

50

また本発明の一態様は、酸化物半導体で半導体層が形成された第2のトランジスタ133Bと酸化物半導体層で半導体層が形成された第1のトランジスタ131を積層して形成することで、メモリセルの高密度化を図ることができる。また図6(B)の構成では、第1のトランジスタ131と第2のトランジスタ133Bと同じ作製工程で作製することで製造コストの低減を図ることができる。

#### 【0077】

以上説明したように、第2のトランジスタの構成については、様々な形態を取ることが可能である。

#### 【0078】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

10

#### 【0079】

##### (実施の形態4)

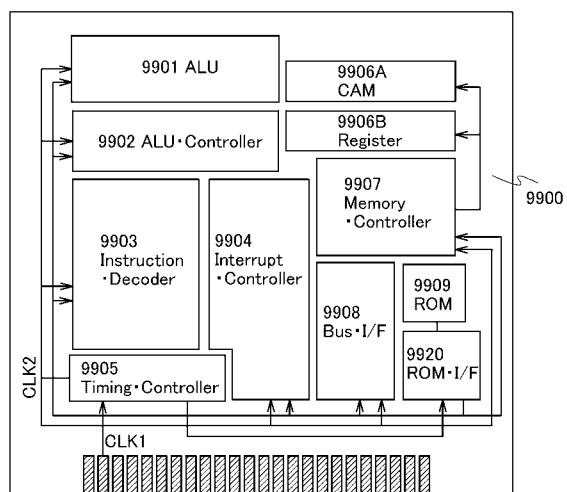

本実施の形態では、本発明の一態様に係る半導体記憶装置であるCAMを適用可能なCPUの構成について説明する。

#### 【0080】

図7に、本実施の形態のCPUの構成を示す。図7に示すCPUは、基板9900上に、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Timing・Controller9905、CAM9906A、Register9906B、Memory・Controller9907、Bus・I/F9908、書き換え可能なROM9909、ROM・I/F9920と、を主に有している。なお、ALUはArithmetic logic unitであり、Bus・I/Fはバスインターフェースであり、ROM・I/FはROMインターフェースであり、CAMはContent Addressable Memoryである。ROM9909及びROM・I/F9920は、別チップに設けても良い。勿論、図7に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

20

#### 【0081】

Bus・I/F9908を介してCPUに入力された命令は、Instruction・Decoder9903に入力され、デコードされた後、ALU・Controller9902、Interrupt・Controller9904、Memory・Controller9907、Timing・Controller9905に入力される。

30

#### 【0082】

ALU・Controller9902、Interrupt・Controller9904、Memory・Controller9907、Timing・Controller9905は、デコードされた命令に基づき、各種制御を行なう。具体的にALU・Controller9902は、ALU9901の動作を制御するための信号を生成する。また、Interrupt・Controller9904は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。Memory・Controller9907は、CAM9906A及びRegister9906Bのアドレスを生成し、CPUの状態に応じてCAM9906A、Register9906Bの読み出しや書き込みを行なう。

40

#### 【0083】

またTiming・Controller9905は、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Memory・Controller9907の動作のタイミングを制御する信号を生成する。例えばTiming・Controller9905は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に入力する。

50

## 【0084】

本実施の形態のC P UではC A M 9 9 0 6 Aに上記実施の形態で示した構成を有する半導体記憶装置が設けられている。Memory・Controller 9 9 0 7は、A L U 9 9 0 1からの指示に従い、C A M 9 9 0 6 Aである半導体記憶装置においてデータ信号の保持を行う。

## 【0085】

なお一時的にC P Uの動作を停止し、電源電圧の供給を停止した場合においてもデータ信号を保持することが可能であり、消費電力の低減を行うことができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、C P Uを停止することができ、それにより消費電力を低減することができる。10

## 【0086】

本実施の形態では、C P Uを例に挙げて説明したが、本発明の信号処理装置はC P Uに限らず、マイクロプロセッサ、画像処理回路、D S P (D i g i t a l S i g n a l Processor)、F P G A (F i e l d P r o g r a m m a b l e G a t e A r r a y)等のL S Iにも応用可能である。

## 【0087】

本実施の形態は、上記実施の形態と組み合わせて実施することが可能である。

## 【0088】

## (実施の形態5)

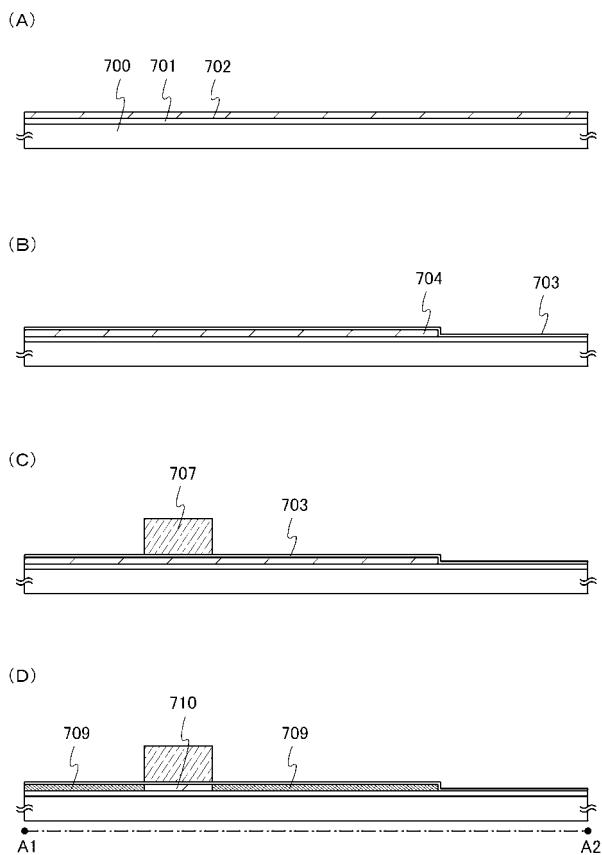

図6(A)に示した、チャネルがシリコンに形成される場合における第2のトランジスタ133Aと、チャネルが酸化物半導体層に形成される第1のトランジスタ131と、容量素子132とを例に挙げて、半導体記憶装置の作製方法について説明する。20

## 【0089】

図8(A)に示すように、基板700上に絶縁膜701と、単結晶の半導体基板から分離された半導体膜702と、を形成する。

## 【0090】

基板700として使用することができる素材に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板700には、フュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730以上の中を用いると良い。30

## 【0091】

また、本実施の形態では、半導体膜702が単結晶のシリコンである場合を例に挙げて、以下、第2のトランジスタ133Aの作製方法について説明する。なお、具体的な単結晶の半導体膜702の作製方法の一例について、簡単に説明する。まず、単結晶の半導体基板であるボンド基板に、電界で加速されたイオンでなるイオンビームを注入し、ボンド基板の表面から一定の深さの領域に、結晶構造が乱されることで局的に脆化された脆化層を形成する。脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。そして、ボンド基板と、絶縁膜701が形成された基板700とを、間に当該絶縁膜701が挟まるように貼り合わせる。貼り合わせは、ボンド基板と基板700とを重ね合わせた後、ボンド基板と基板700の一部に、 $1 \text{ N} / \text{cm}^2$ 以上 $500 \text{ N} / \text{cm}^2$ 以下、好ましくは $11 \text{ N} / \text{cm}^2$ 以上 $20 \text{ N} / \text{cm}^2$ 以下程度の圧力を加える。圧力を加えると、その部分からボンド基板と絶縁膜701とが接合を開始し、最終的には密着した面全体に接合があつぶ。次いで、加熱処理を行うことで、脆化層に存在する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、脆化層においてボンド基板の一部である単結晶半導体膜が、ボンド基板から分離する。上記加熱処理の温度は、基板700の歪み点を越えない温度とする。そして、上記単結晶半導体膜をエッチング等により所望の形状に加工することで、半導体膜702を形成することができる。4050

## 【0092】

半導体膜702には、閾値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型の導電性を付与する不純物元素、若しくはリン、砒素などのn型の導電性を付与する不純物元素を添加しても良い。閾値電圧を制御するための不純物元素の添加は、パターニングする前の半導体膜に対して行っても良いし、パターニング後に形成された半導体膜702に対して行っても良い。また、閾値電圧を制御するための不純物元素の添加を、ボンド基板に対して行っても良い。若しくは、不純物元素の添加を、閾値電圧を大まかに調整するためにボンド基板に対して行った上で、閾値電圧を微調整するために、パターニング前の半導体膜に対して、又はパターニングにより形成された半導体膜702に対してても良い。

10

## 【0093】

なお、本実施の形態では、単結晶の半導体膜を用いる例について説明しているが、本発明はこの構成に限定されない。例えば、絶縁膜701上に気相成長法を用いて形成された多結晶、微結晶、非晶質の半導体膜を用いても良いし、上記半導体膜を公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。あるいは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950程度の高温アニール法を組み合わせた結晶化法を用いても良い。

20

## 【0094】

次に、図8(B)に示すように、半導体膜702を用いて半導体層704を形成する。そして、半導体層704上にゲート絶縁膜703を形成する。

## 【0095】

ゲート絶縁膜703は、一例としては、プラズマCVD法又はスパッタ法などを用い、酸化珪素、窒化酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウム又は酸化タンタル、酸化イットリウム、ハフニウムシリケート( $HfSi_xO_y$ ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$ ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムアルミネート( $HfAl_xO_y$ ( $x > 0$ 、 $y > 0$ ))等を含む膜を、単層で、又は積層させることで、形成することができる。

30

## 【0096】

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質を意味する。

## 【0097】

ゲート絶縁膜703の厚さは、例えば、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。本実施の形態では、プラズマCVD法を用いて、酸化珪素を含む単層の絶縁膜を、ゲート絶縁膜703として用いる。

## 【0098】

次いで、図8(C)に示すように、ゲート電極707を形成する。

40

## 【0099】

ゲート電極707は、導電膜を形成した後、該導電膜を所定の形状に加工(パターニング)することで、形成することができる。上記導電膜の形成にはCVD法、スパッタ法、蒸着法、スピノコート法等を用いることができる。また、導電膜は、タンタル(Ta)、タンクステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等を用いることができる。上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。又は、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。

## 【0100】

50

なお、本実施の形態ではゲート電極 707 を単層の導電膜で形成しているが、本実施の形態はこの構成に限定されない。ゲート電極 707 は積層された複数の導電膜で形成されても良い。

#### 【0101】

2つの導電膜の組み合わせとして、1層目に窒化タンタル又はタンタルを、2層目にタングステンを用いることができる。上記例の他に、窒化タングステンとタングステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合わせとして、例えば、n型の導電性を付与する不純物元素がドーピングされた珪素とニッケルシリサイド、n型の導電性を付与する不純物元素がドーピングされた珪素とタングステンシリサイド等も用いることができる。

10

#### 【0102】

3つの導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

#### 【0103】

また、ゲート電極 707 に酸化インジウム、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、又は酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

20

#### 【0104】

なお、マスクを用いずに、液滴吐出法を用いて選択的にゲート電極 707 を形成しても良い。液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出又は噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

#### 【0105】

また、ゲート電極 707 は、導電膜を形成後、ICP (Inductively Coupled Plasma) エッチング法を用い、エッチング条件（コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等）を適宜調節することにより、所望のテーパー形状を有するようエッチングすることができる。また、テーパー形状は、マスクの形状によっても角度等を制御することができる。なお、エッチング用ガスとしては、塩素、塩化硼素、塩化珪素若しくは四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄若しくは弗化窒素などのフッ素系ガス又は酸素を適宜用いることができる。

30

#### 【0106】

次に、図8(D)に示すように、ゲート電極 707 をマスクとして一導電性を付与する不純物元素を半導体層 704 に添加することで、ゲート電極 707 と重なるチャネル形成領域 710 と、チャネル形成領域 710 を間に挟む一対の不純物領域 709 とが、半導体層 704 に形成される。

#### 【0107】

本実施の形態では、半導体層 704 に p型を付与する不純物元素（例えばボロン）を添加する場合を例に挙げる。

40

#### 【0108】

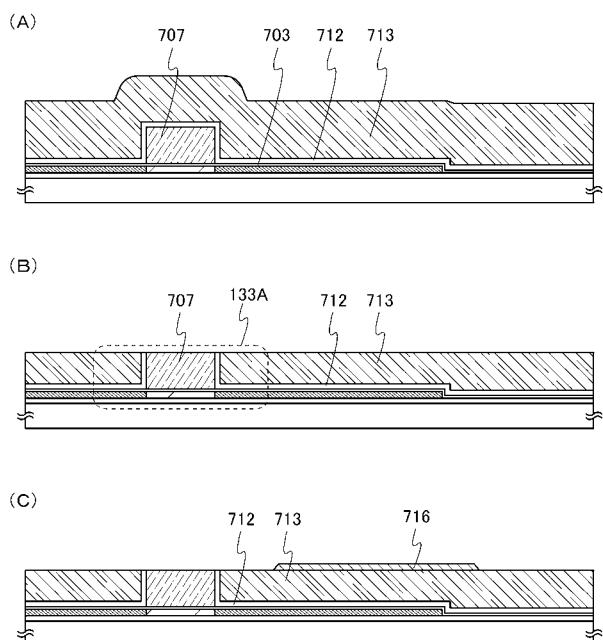

次いで、図9(A)に示すように、ゲート絶縁膜 703、ゲート電極 707 を覆うように、絶縁膜 712、絶縁膜 713 を形成する。具体的に、絶縁膜 712、絶縁膜 713 は、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。特に、絶縁膜 712、絶縁膜 713 に誘電率の低い(10w-k)材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁膜 712、絶縁膜 713 に、上記材料を用いた多孔性の絶縁膜を適用しても良い。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。

50

## 【0109】

本実施の形態では、絶縁膜712として酸化窒化珪素、絶縁膜713として窒化酸化珪素を用いる場合を例に挙げる。また、本実施の形態では、ゲート電極707上に絶縁膜712、絶縁膜713を形成している場合を例示しているが、本発明はゲート電極707上に絶縁膜を1層だけ形成しても良いし、3層以上の複数の絶縁膜を積層するように形成していくても良い。

## 【0110】

次いで、図9(B)に示すように、絶縁膜713にCMP(化学的機械研磨)処理やエッチング処理を行うことにより、ゲート電極707の表面を露出させる。なお、後に形成される第1のトランジスタ131の特性を向上させるために、絶縁膜713の表面は可能な限り平坦にしておくことが好ましい。

10

## 【0111】

以上の工程により、第2のトランジスタ133Aを形成することができる。

## 【0112】

次いで、第1のトランジスタ131の作製方法について説明する。まず、図9(C)に示すように、絶縁膜713上に酸化物半導体層716を形成する。

20

## 【0113】

酸化物半導体層716は、絶縁膜713上に形成した酸化物半導体膜を所望の形状に加工することで、形成することができる。上記酸化物半導体膜の膜厚は、2nm以上200nm以下、好ましくは3nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

20

## 【0114】

スパッタ法を用いて酸化物半導体層716を作製する場合には、成膜処理室内に存在する水、水素を極力低減しておく。具体的には、成膜前に成膜処理室内を加熱する、成膜処理室内に導入されるガス中の水及び/又は水素濃度を低減する、及び成膜処理室から排気されるガスの逆流を防止するなどを行うことが好適である。

30

## 【0115】

また、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁膜713の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

30

## 【0116】

酸化物半導体膜には、上述したような、四元系の金属酸化物であるIn-Sn-Ga-Zn系酸化物や、三元系の金属酸化物であるIn-Ga-Zn系酸化物、In-Sn-Zn系酸化物、In-Al-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物や、二元系の金属酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物や、酸化インジウム、酸化錫、酸化亜鉛などを用いることができる。

40

## 【0117】

なおIn-Sn-Zn系酸化物半導体を用いる場合、トランジスタの移動度を高くすることができます。またIn-Sn-Zn系酸化物半導体を用いる場合、トランジスタのしきい値電圧を安定して制御することが可能である。なおIn-Sn-Zn系酸化物半導体を用いる場合、用いるターゲットの組成比は、原子数比で、In:Sn:Zn = 1:2:2、

50

I n : S n : Z n = 2 : 1 : 3、I n : S n : Z n = 1 : 1 : 1などとすればよい。

【0118】

本実施の形態では、I n (インジウム)、G a (ガリウム)、及びZ n (亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚30nmのI n - G a - Z n系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、各金属の組成比がI n : G a : Z n = 1 : 1 : 0.5、I n : G a : Z n = 1 : 1 : 1、又はI n : G a : Z n = 1 : 1 : 2であるターゲットを用いることができる。また、I n、G a、及びZ nを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

10

【0119】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコードトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

20

【0120】

成膜条件の一例としては、基板とターゲットとの間との距離を100mm、圧力0.6Pa、直流(DC)電源電力0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

30

【0121】

また、スパッタリング装置の処理室のリーケートを $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3/\text{s}$ 以下とすることで、スパッタ法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として上述した吸着型の真空ポンプを用いることで、排気系からのアルカリ金属、水素原子、水素分子、水、水酸基、又は水素化物等の不純物の逆流を低減することができる。

【0122】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、又は水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

40

【0123】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜712及び絶縁膜713までが形成された基板700を予備加熱し、基板700に吸着した水分又は水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400

以下、好ましくは150以上300以下である。また、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。また、この予備加熱は、後に行われるゲート絶縁膜721の成膜前に、導電膜719、導電膜720まで形成した基板700にも同様に行ってもよい。

【0124】

なお、酸化物半導体層716を形成するためのエッチングは、ドライエッチングでもウ

50

エットエッティングでもよく、両方を用いてもよい。ドライエッティングに用いるエッティングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、三塩化硼素（BCl<sub>3</sub>）、四塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（CF<sub>4</sub>）、六弗化硫黄（SF<sub>6</sub>）、三弗化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）など）、臭化水素（HBr）、酸素（O<sub>2</sub>）、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。

## 【0125】

ドライエッティング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッティング法を用いることができる。所望の形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。10

## 【0126】

ウェットエッティングに用いるエッティング液として、磷酸と酢酸と硝酸を混ぜた溶液、クエン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO-07N（関東化学社製）を用いる。

## 【0127】

酸化物半導体層716を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。20

## 【0128】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層716及び絶縁膜712及び絶縁膜713の表面に付着しているレジスト残渣などを除去することが好ましい。

## 【0129】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分又は水素（水酸基を含む）が多量に含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分又は水素などの不純物を低減（脱水化または脱水素化）するために、酸化物半導体層716に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア（CRDS（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20ppm（露点換算で-55）以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）雰囲気下で、酸化物半導体層716に加熱処理を施す。30

## 【0130】

酸化物半導体層716に加熱処理を施すことで、酸化物半導体層716中の水分又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化又は脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。40

## 【0131】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

## 【0132】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧50

水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0133】

加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N (99.9999%) 以上、好ましくは7 N (99.99999%) 以上、(即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下) とすることが好ましい。

10

【0134】

なお、酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている（神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol. 44、pp. 621-633.）。しかし、このような指摘は適切でない。アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちNaは、酸化物半導体層に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散してNa<sup>+</sup>となる。また、Naは、酸化物半導体層内において、酸化物半導体を構成する金属と酸素の結合を分断する、あるいは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの特性の劣化が起こり、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタの特性の劣化と、特性のばらつきは、酸化物半導体層中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体層中の水素濃度が $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{17}$  atoms/cm<sup>3</sup>以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、二次イオン質量分析法によるNa濃度の測定値は、 $5 \times 10^{16}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下、cm<sup>3</sup>以下、更に好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするとよい。同様に、Li濃度の測定値は、 $5 \times 10^{15}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするとよい。同様に、K濃度の測定値は、 $5 \times 10^{15}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするとよい。

20

【0135】

以上の工程により、酸化物半導体層716中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、バンドギャップの広い酸化物半導体層を形成することができる。このため、大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。上記加熱処理は、酸化物半導体層の成膜以降であれば、いつでも行うことができる。

30

【0136】

なお、酸化物半導体層は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

40

【0137】

好ましくは、酸化物半導体膜は、C A A C - O S (C Axis Aligned Crystalline Oxide Semiconductor) 膜とする。

【0138】

C A A C - O S 膜は、完全な単結晶ではなく、完全な非晶質でもない。C A A C - O S 膜は、非晶質相に結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100 nm未満の立方体内に収まる大きさであること

50

が多い。また、透過型電子顕微鏡（TEM：Transmission Electron Microscope）による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

#### 【0139】

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

10

#### 【0140】

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

20

#### 【0141】

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

#### 【0142】

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

30

#### 【0143】

なおCAAC-OS膜は、スパッタ法によっても作製することができる。スパッタ法によってCAAC-OS膜を得るには、酸化物半導体の堆積初期段階において六方晶の結晶が形成されるようにすることと、当該結晶を種として結晶が成長されるようにすることが肝要である。そのためには、ターゲットと基板の距離を広くとり（例えば、150mm～200mm程度）、基板加熱温度を100～500、好適には200～400、さらに好適には250～300にすると好ましい。

#### 【0144】

また、CAAC-OS膜をスパッタ法を用いて成膜する場合には、雰囲気中の酸素ガス比が高い方が好ましい。例えば、アルゴン及び酸素の混合ガス雰囲気中でスパッタ法を行う場合には、酸素ガス比を30%以上とすることが好ましく、40%以上とすることがより好ましい。雰囲気中からの酸素の補充によって、CAAC-OS膜の結晶化が促進されるからである。

40

#### 【0145】

また、スパッタ法を用いてCAAC-OS膜を成膜する場合には、CAAC-OS膜が成膜される基板を150以上に加熱しておくことが好ましく、170以上に加熱しておくことがより好ましい。基板温度の上昇に伴って、CAAC-OS膜の結晶化が促進されるからである。

#### 【0146】

また、CAAC-OS膜に対して、窒素雰囲気中又は真空中において熱処理を行った後には、酸素雰囲気中又は酸素と他のガスとの混合雰囲気中において熱処理を行うことが好ま

50

しい。先の熱処理で生じる酸素欠損を後の熱処理における雰囲気中からの酸素供給によって復元することができるからである。

#### 【0147】

また、C AAC - OS 膜が成膜される膜表面（被成膜面）は平坦であることが好ましい。C AAC - OS 膜は、当該被成膜面に概略垂直となる c 軸を有するため、当該被成膜面に存在する凹凸は、C AAC - OS 膜における結晶粒界の発生を誘発することになるからである。よって、C AAC - OS 膜が成膜される前に当該被成膜表面に対して化学機械研磨（Chemical Mechanical Polishing : CMP）などの平坦化処理を行うことが好ましい。また、当該被成膜面の平均ラフネスは、0.5 nm 以下であることが好ましく、0.3 nm 以下であることがより好ましい。

10

#### 【0148】

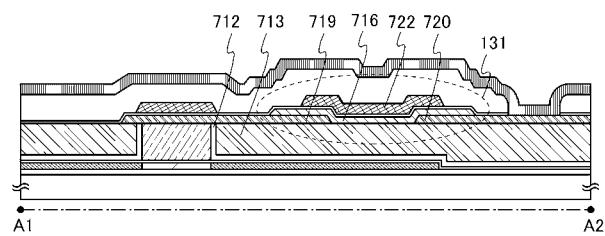

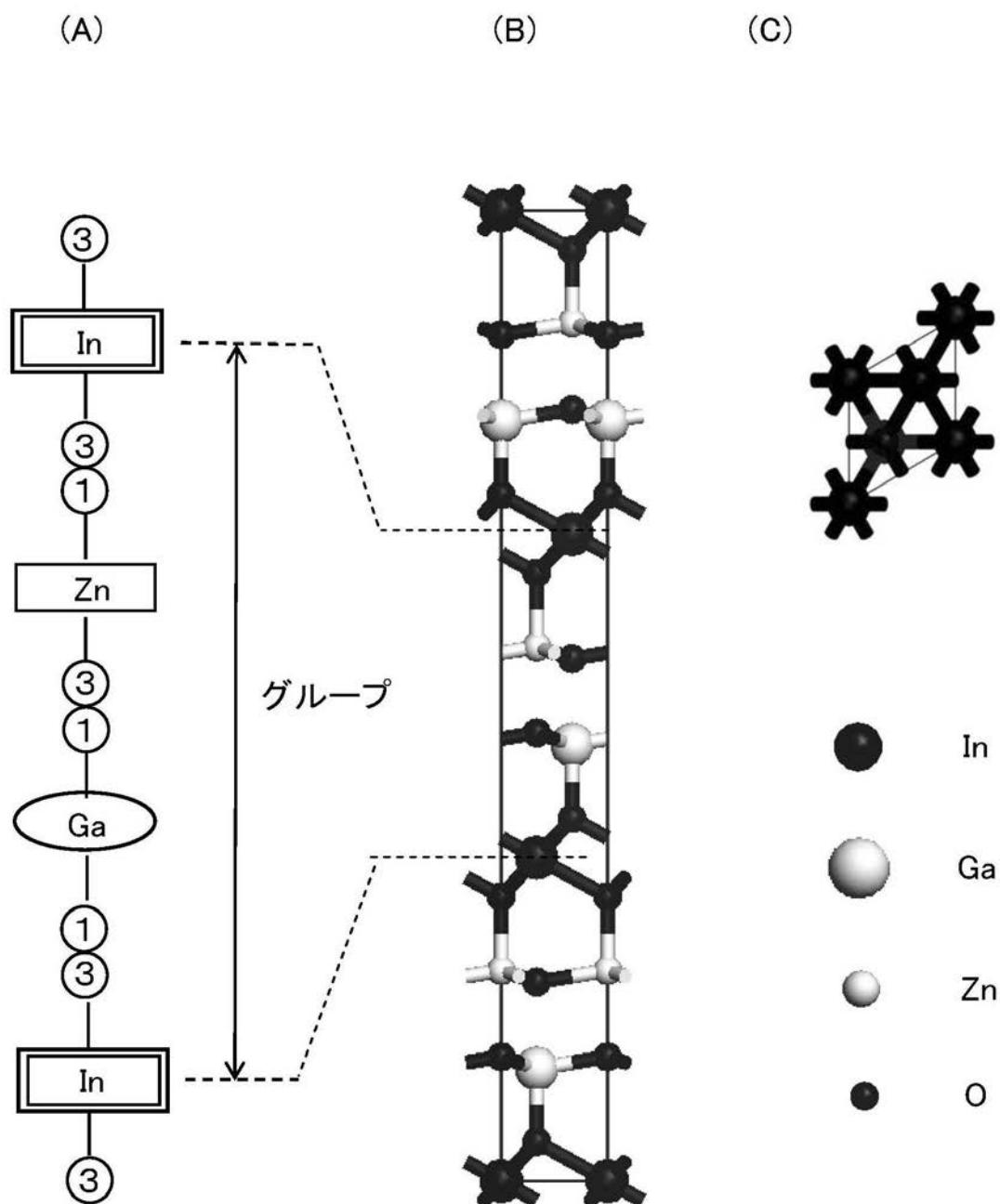

ここで、C AAC - OS 膜について図 12 乃至図 14 を用いて詳細に説明する。なお、特に断りがない限り、図 12 乃至図 14 は上方向を c 軸方向とし、c 軸方向と直交する面を a b 面とする。なお、単に上半分、下半分という場合、a b 面を境にした場合の上半分、下半分をいう。また、図 12 において、丸で囲まれた O は 4 配位の O を示し、二重丸で囲まれた O は 3 配位の O を示す。

#### 【0149】

図 12 (A) に、1 個の 6 配位の In と、In に近接の 6 個の 4 配位の酸素原子（以下 4 配位の O）と、を有する構造を示す。In が 1 個に対して、近接の酸素原子のみ示した構造を、ここではサブユニットと呼ぶ。図 12 (A) の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図 12 (A) の上半分及び下半分にはそれぞれ 3 個ずつ 4 配位の O がある。図 12 (A) に示すサブユニットは電荷が 0 である。

20

#### 【0150】

図 12 (B) に、1 個の 5 配位の Ga と、Ga に近接の 3 個の 3 配位の酸素原子（以下 3 配位の O）と、Ga に近接の 2 個の 4 配位の O と、を有する構造を示す。3 配位の O は、いずれも a b 面に存在する。図 12 (B) の上半分及び下半分にはそれぞれ 1 個ずつ 4 配位の O がある。また、In も 5 配位をとるため、図 12 (B) に示す構造をとりうる。図 12 (B) に示すサブユニットは電荷が 0 である。

#### 【0151】

図 12 (C) に、1 個の 4 配位の Zn と、Zn に近接の 4 個の 4 配位の O と、による構造を示す。図 12 (C) の上半分には 1 個の 4 配位の O があり、下半分には 3 個の 4 配位の O がある。図 12 (C) に示すサブユニットは電荷が 0 である。

30

#### 【0152】

図 12 (D) に、1 個の 6 配位の Sn と、Sn に近接の 6 個の 4 配位の O と、を有する構造を示す。図 12 (D) の上半分には 3 個の 4 配位の O があり、下半分には 3 個の 4 配位の O がある。図 12 (D) に示すサブユニットは電荷が +1 となる。

#### 【0153】

図 12 (E) に、2 個の Zn を含むサブユニットを示す。図 12 (E) の上半分には 1 個の 4 配位の O があり、下半分には 1 個の 4 配位の O がある。図 12 (E) に示すサブユニットは電荷が -1 となる。

40

#### 【0154】

ここでは、サブユニットのいくつかの集合体を 1 グループと呼び、複数のグループの集合体を 1 ユニットと呼ぶ。

#### 【0155】

ここで、これらのサブユニット同士結合する規則について説明する。6 配位の In の上半分の 3 個の O は、下方向にそれぞれ 3 個の近接 In を有し、下半分の 3 個の O は、上方向にそれぞれ 3 個の近接 In を有する。5 配位の Ga の上半分の 1 個の O は、下方向に 1 個の近接 Ga を有し、下半分の 1 個の O は、上方向に 1 個の近接 Ga を有する。4 配位の Zn の上半分の 1 個の O は、下方向に 1 個の近接 Zn を有し、下半分の 3 個の O は、上方向にそれぞれ 3 個の近接 Zn を有する。この様に、金属原子の上方向の 4 配位の O の数と、

50

そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種のサブユニット同士は結合することができる。例えば、6配位の金属原子(I<sub>n</sub>またはS<sub>n</sub>)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、4配位の金属原子(Zn)のいずれかと結合することになる。

#### 【0156】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるようにサブユニット同士が結合して1グループを構成する。

#### 【0157】

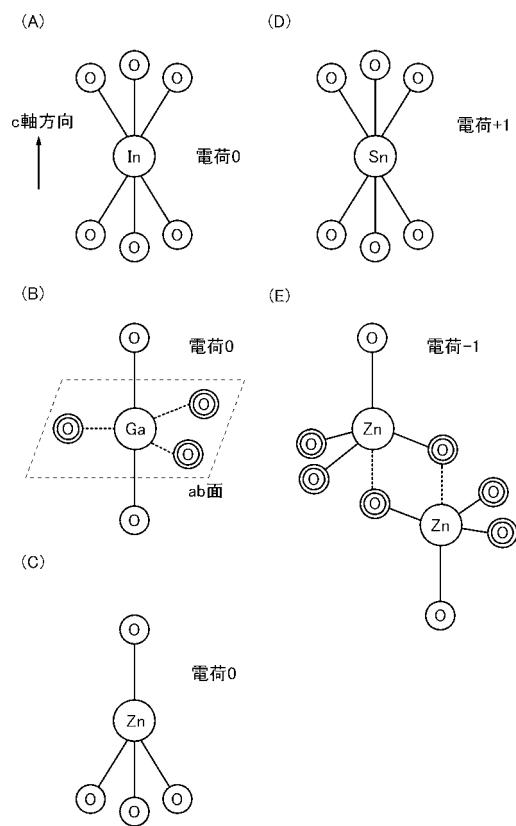

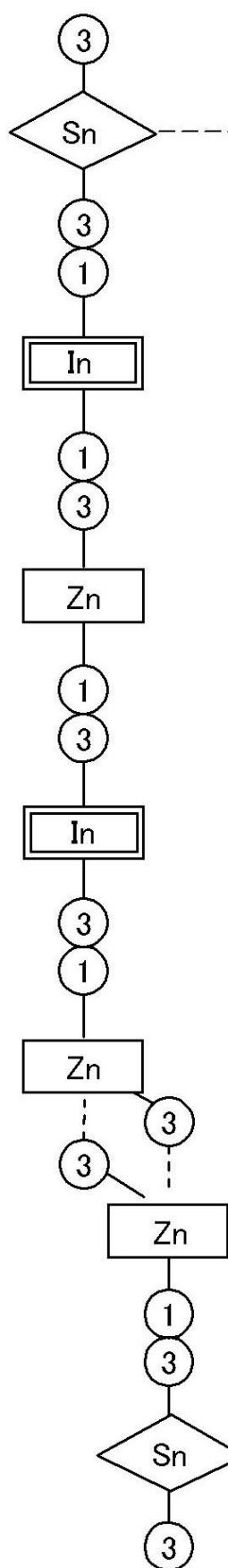

図13(A)に、In-Sn-Zn-O系の層構造を構成する1グループのモデル図を示す。図13(B)に、3つのグループで構成されるユニットを示す。なお、図13(C)は、図13(B)の層構造をc軸方向から観察した場合の原子配列を示す。

#### 【0158】

図13(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Sn原子の上半分及び下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図13(A)において、In原子の上半分及び下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図13(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZn原子と、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZn原子とを示している。

#### 【0159】

図13(A)において、In-Sn-Zn-O系の層構造を構成するグループは、上から順に4配位のOが3個ずつ上半分及び下半分にあるSn原子が、4配位のOが1個ずつ上半分及び下半分にあるIn原子と結合し、そのIn原子が、上半分に3個の4配位のOがあるZn原子と結合し、そのZn原子の下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分及び下半分にあるIn原子と結合し、そのIn原子が、上半分に1個の4配位のOがあるZn2個からなるサブユニットと結合し、このサブユニットの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分及び下半分にあるSn原子と結合している構成である。このグループを複数結合してユニットを構成する。

#### 【0160】

ここで、3配位のO及び4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含むサブユニットは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図12(E)に示すように、2個のZnを含むサブユニットが挙げられる。例えば、Snを含むサブユニットが1個に対し、2個のZnを含むサブユニットが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができます。

#### 【0161】

具体的には、図13(B)に示したユニットが繰り返されることで、In-Sn-Zn-O系の結晶(In<sub>2</sub>SnZn<sub>3</sub>O<sub>8</sub>)を得ることができる。なお、得られるIn-Sn-Zn-O系の層構造は、In<sub>2</sub>SnZn<sub>2</sub>O<sub>7</sub>(ZnO)<sub>m</sub>(mは0または自然数。)とする組成式で表すことができる。

#### 【0162】

また、このほかにも、四元系金属の酸化物であるIn-Sn-Ga-Zn-O系酸化物や、三元系金属の酸化物であるIn-Ga-Zn-O系酸化物(IGZOとも表記する。)

10

20

30

40

50

、In-Al-Zn-O系酸化物、Sn-Ga-Zn-O系酸化物、Al-Ga-Zn-O系酸化物、Sn-Al-Zn-O系酸化物や、二元系金属の酸化物であるIn-Zn-O系酸化物、Sn-Zn-O系酸化物、Al-Zn-O系酸化物、Zn-Mg-O系酸化物、Sn-Mg-O系酸化物、In-Mg-O系酸化物や、In-Ga-O系の材料などを用いた場合も同様である。

#### 【0163】

例えば、図14(A)に、In-Ga-Zn-O系の層構造を構成する1グループのモデル図を示す。

#### 【0164】

図14(A)において、In-Ga-Zn-O系の層構造を構成するグループは、上から順に4配位のOが3個ずつ上半分及び下半分にあるIn原子が、4配位のOが1個上半分にあるZn原子と結合し、そのZn原子の下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分及び下半分にあるGa原子と結合し、そのGa原子の下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分及び下半分にあるIn原子と結合している構成である。このグループを複数結合してユニットを構成する。

#### 【0165】

図14(B)に3つのグループで構成されるユニットを示す。なお、図14(C)は、図14(B)の層構造をc軸方向から観察した場合の原子配列を示している。

#### 【0166】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、Zn及びGaのいずれかを含むサブユニットは、電荷が0となる。そのため、これらのサブユニットの組み合わせであればグループの合計の電荷は常に0となる。

#### 【0167】

また、In-Ga-Zn-O系の層構造を構成するグループは、図14(A)に示したグループに限定されず、In、Ga、Znの配列が異なるグループを組み合わせたユニットを取りうる。

#### 【0168】

次いで、図10(A)に示すように、ゲート電極707と接し、なおかつ酸化物半導体層716とも接する導電膜719と、酸化物半導体層716とも接する導電膜720とを形成する。導電膜719及び導電膜720は、ソース電極又はドレイン電極として機能する。

#### 【0169】

具体的に、導電膜719及び導電膜720は、ゲート電極707及び絶縁膜713上を覆うようにスパッタ法や真空蒸着法で導電膜を形成した後、該導電膜を所定の形状に加工(パターニング)することで、形成することができる。

#### 【0170】

導電膜719及び導電膜720となる導電膜は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側若しくは上側にクロム、タンタル、チタン、モリブデン、タングステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウム又は銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム、イットリウム等を用いることができる。

#### 【0171】

また、導電膜719及び導電膜720となる導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、更にその上にチタン膜を成膜する3層構造などが挙げられる。また、Cu-M

10

20

30

40

50

g - Al 合金、Mo - Ti 合金、Ti、Mo、は、酸化膜との密着性が高い。よって、下層に Cu - Mg - Al 合金、Mo - Ti 合金、Ti、あるいは Mo で構成される導電膜、上層に Cu で構成される導電膜を積層し、上記積層された導電膜を導電膜 719 及び導電膜 720 に用いることで、酸化膜である絶縁膜と、導電膜 719 及び導電膜 720 との密着性を高めることができる。

#### 【0172】

また、導電膜 719 及び導電膜 720 となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、酸化インジウム酸化亜鉛、又は前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

10

#### 【0173】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### 【0174】

なお、導電膜のエッチングの際に、酸化物半導体層 716 がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、酸化物半導体層 716 の露出した部分が一部エッチングされることで、溝部（凹部）が形成されることもある。

#### 【0175】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液（アンモニア過水）を用いて、選択的に導電膜をウェットエッチングすることができる。具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と水とを、体積比 5 : 2 : 2 で混合したアンモニア過水を用いる。あるいは、塩素（Cl<sub>2</sub>）、塩化硼素（BCl<sub>3</sub>）などを含むガスを用いて、導電膜をドライエッチングしても良い。

20

#### 【0176】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことで更に形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

30

#### 【0177】

また、酸化物半導体層 716 と、ソース電極又はドレイン電極として機能する導電膜 719 及び導電膜 720との間に、ソース領域及びドレイン領域として機能する酸化物導電膜を設けるようにしても良い。酸化物導電膜の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを適用することができる。

40

#### 【0178】

例えば、酸化物導電膜を形成する場合、酸化物導電膜を形成するためのパターニングと、導電膜 719 及び導電膜 720 を形成するためのパターニングとを一括で行うようにしても良い。

#### 【0179】

ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、酸化物半導体層 716 と導電膜 719 及び導電膜 720 の間の抵抗を下げる所以で、トランジスタの高速動作を実現させることができる。また、ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、トランジスタの耐圧を高めることができる。

#### 【0180】

50

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行うようにしても良い。このプラズマ処理によって露出している酸化物半導体層の表面に付着した水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### 【0181】

なお、プラズマ処理を行った後、図10(B)に示すように、導電膜719及び導電膜720と、酸化物半導体層716とを覆うように、ゲート絶縁膜721を形成する。そして、ゲート絶縁膜721上において、酸化物半導体層716と重なる位置にゲート電極722を形成し、導電膜719と重なる位置に導電膜723を形成する。

#### 【0182】

ゲート絶縁膜721は、ゲート絶縁膜703と同様の材料、同様の積層構造を用いて形成することが可能である。なお、ゲート絶縁膜721は、水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。ゲート絶縁膜721に水素が含まれると、その水素が酸化物半導体層716へ侵入し、又は水素が酸化物半導体層716中の酸素を引き抜き、酸化物半導体層716が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。よって、ゲート絶縁膜721はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記ゲート絶縁膜721には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いることができる。複数の積層された絶縁膜を用いる場合、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体層716に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、導電膜719及び導電膜720及び酸化物半導体層716と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体層716内、ゲート絶縁膜721内、あるいは、酸化物半導体層716と他の絶縁膜の界面とその近傍に、水分又は水素などの不純物が入り込むのを防ぐことができる。また、酸化物半導体層716に接するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体層716に接するのを防ぐことができる。

#### 【0183】

本実施の形態では、スパッタ法で形成された膜厚200nmの酸化珪素膜上に、スパッタ法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、ゲート絶縁膜721を形成する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。

#### 【0184】

なお、ゲート絶縁膜721を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、又は希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。本実施の形態では、例えば、窒素雰囲気下で250、1時間の加熱処理を行う。あるいは、導電膜719及び導電膜720を形成する前に、水分又は水素を低減させるための酸化物半導体層に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含むゲート絶縁膜721が設けられた後に、加熱処理が施されることによって、酸化物半導体層716に対して行った先の加熱処理により、酸化物半導体層716に酸素欠損が発生していたとしても、ゲート絶縁膜721から酸化物半導体層716に酸素が供与される。そして、酸化物半導体層716に酸素が供与されることで、酸化物半導体層716において、ドナーとなる酸素欠損を低減し、化学量論的組成比を満たすことが可能である。酸化物半導体層716には、化学量論的組成比を超える量の酸素が含まれていることが好ましい。その結果、酸化物半導体層716をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性的向上を実現することができる。この加熱処理を行うタイミングは、ゲート絶縁膜721

10

20

30

40

50

の形成後であれば特に限定されず、他の工程、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理と兼ねることで、工程数を増やすことなく、酸化物半導体層716をi型に近づけることができる。

#### 【0185】

また、酸素雰囲気下で酸化物半導体層716に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体層716中においてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100以上350未満、好ましくは150以上250未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。10

#### 【0186】

あるいは、イオン注入法又はイオンドーピング法などを用いて、酸化物半導体層716に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45GHzのマイクロ波でプラズマ化した酸素を酸化物半導体層716に添加すれば良い。

#### 【0187】

また、ゲート電極722及び導電膜723は、ゲート絶縁膜721上に導電膜を形成した後、該導電膜をパターニングすることで形成することができる。ゲート電極722及び導電膜723は、ゲート電極707、或いは導電膜719及び導電膜720と同様の材料を用いて形成することが可能である。20

#### 【0188】

ゲート電極722及び導電膜723の膜厚は、10nm~400nm、好ましくは100nm~200nmとする。本実施の形態では、タンゲステンターゲットを用いたスパッタ法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極722及び導電膜723を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0189】

以上の工程により、第1のトランジスタ131が形成される。30

#### 【0190】

なお、ゲート絶縁膜721を間に挟んで導電膜719と導電膜723とが重なる部分が、容量素子132に相当する。

#### 【0191】

また、第1のトランジスタ131はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、デュアルゲート構造またはマルチゲート構造のトランジスタも形成することができる。

#### 【0192】

なお、酸化物半導体層716に接する絶縁膜(本実施の形態においては、ゲート絶縁膜721が該当する。)は、第13族元素及び酸素を含む絶縁材料を用いるようにしても良い。酸化物半導体材料には第13族元素を含むものが多く、第13族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体層に接する絶縁膜に用いることで、酸化物半導体層との界面の状態を良好に保つことができる。40

#### 【0193】

第13族元素を含む絶縁材料とは、絶縁材料に一又は複数の第13族元素を含むことを意味する。第13族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)50

がアルミニウムの含有量（原子%）以上のものを示す。

【0194】

例えば、ガリウムを含有する酸化物半導体層に接して絶縁膜を形成する場合に、絶縁膜に酸化ガリウムを含む材料を用いることで酸化物半導体層と絶縁膜の界面特性を良好に保つことができる。例えば、酸化物半導体層と酸化ガリウムを含む絶縁膜とを接して設けることにより、酸化物半導体層と絶縁膜の界面における水素のパイルアップを低減することができる。なお、絶縁膜に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁膜を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層への水の侵入防止という点においても好ましい。

10

【0195】

また、酸化物半導体層716に接する絶縁膜は、酸素雰囲気下による熱処理や、酸素ドープなどにより、絶縁材料を化学量論的組成比より酸素が多い状態とすることが好ましい。酸素ドープとは、酸素をバルクに添加することをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。また、酸素ドープは、イオン注入法又はイオンドーピング法を用いて行ってもよい。

20

【0196】

例えば、酸化物半導体層716に接する絶縁膜として酸化ガリウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムの組成を $Ga_2O_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができる。

【0197】

また、酸化物半導体層716に接する絶縁膜として酸化アルミニウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化アルミニウムの組成を $Al_2O_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができる。

【0198】

また、酸化物半導体層716に接する絶縁膜として酸化ガリウムアルミニウム（酸化アルミニウムガリウム）を用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムアルミニウム（酸化アルミニウムガリウム）の組成を $Ga_xAl_{2-x}O_{3+}$  ( $0 < X < 2 , 0 < X < 1$ ) とすることができる。

30

【0199】

酸素ドープ処理を行うことにより、化学量論的組成比より酸素が多い領域を有する絶縁膜を形成することができる。このような領域を備える絶縁膜と酸化物半導体層が接することにより、絶縁膜中の過剰な酸素が酸化物半導体層に供給され、酸化物半導体層中、又は酸化物半導体層と絶縁膜の界面における酸素欠陥を低減し、酸化物半導体層をi型化又はi型に限りなく近くすることができる。

【0200】

絶縁膜中の過剰な酸素が酸化物半導体層に供給されることで酸素欠陥が低減された酸化物半導体層は、水素濃度が十分に低減されて高純度化され、且つ十分な酸素の供給により酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層とすることができます。そのため、キャリア濃度が極めて小さい酸化物半導体層とすることができます、オフ電流が著しく低いトランジスタとすることができます。このようなオフ電流が著しく低いトランジスタを、上記実施の形態の第1のトランジスタに適用することで、非導通状態とした際に、ほぼ絶縁体とみなすことができる。従って第1のトランジスタをメモリ回路に用いることで、容量素子と第1のトランジスタが接続されたノードに保持された電位の低下を極めて小さいレベルに抑制できる。その結果、電源電圧の供給が停止した場合でも、ノードNの電位の変動を小さくでき、記憶されたデータの消失を防ぐことができる不揮発性のメモリ回路とすることができます。

40

【0201】

50

なお、化学量論的組成比より酸素が多い領域を有する絶縁膜は、酸化物半導体層716に接する絶縁膜のうち、上層に位置する絶縁膜又は下層に位置する絶縁膜のうち、どちらか一方のみに用いても良いが、両方の絶縁膜に用いる方が好ましい。化学量論的組成比より酸素が多い領域を有する絶縁膜を、酸化物半導体層716に接する絶縁膜の、上層及び下層に位置する絶縁膜に用い、酸化物半導体層716を挟む構成として、上記効果をより高めることができる。

#### 【0202】

また、酸化物半導体層716の上層又は下層に用いる絶縁膜は、上層と下層で同じ構成元素を有する絶縁膜としても良いし、異なる構成元素を有する絶縁膜としても良い。例えば、上層と下層とも、組成が $Ga_2O_x$ ( $X = 3 + , 0 < X < 1$ )の酸化ガリウムとしても良いし、上層と下層の一方を組成が $Ga_2O_x$ ( $X = 3 + , 0 < X < 1$ )の酸化ガリウムとし、他方を組成が $Al_2O_x$ ( $X = 3 + , 0 < X < 1$ )の酸化アルミニウムとしても良い。10

#### 【0203】

また、酸化物半導体層716に接する絶縁膜は、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良い。例えば、酸化物半導体層716の上層に組成が $Ga_2O_x$ ( $X = 3 + , 0 < X < 1$ )の酸化ガリウムを形成し、その上に組成が $Ga_xAl_{2-x}O_{3+}$ ( $0 < X < 2 , 0 < X < 1$ )の酸化ガリウムアルミニウム(酸化アルミニウムガリウム)を形成してもよい。なお、酸化物半導体層716の下層を、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良いし、酸化物半導体層716の上層及び下層の両方を、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良い。20

#### 【0204】

次に、図10(C)に示すように、ゲート絶縁膜721、ゲート電極722を覆うように、絶縁膜724を形成する。絶縁膜724は、PVD法やCVD法などを用いて形成することができる。また、酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化ガリウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。なお、絶縁膜724には、誘電率の低い材料や、誘電率の低い構造(多孔性の構造など)を用いることが望ましい。絶縁膜724の誘電率を低くすることにより、配線や電極などの間に生じる寄生容量を低減し、動作の高速化を図ることができるためである。なお、本実施の形態では、絶縁膜724を単層構造としているが、本発明の一態様はこれに限定されず、2層以上の積層構造としても良い。30

#### 【0205】

次に、ゲート絶縁膜721、絶縁膜724に開口部725を形成し、導電膜720の一部を露出させる。その後、絶縁膜724上に、上記開口部725において導電膜720と接する配線726を形成する。

#### 【0206】

配線726は、PVD法や、CVD法を用いて導電膜を形成した後、当該導電膜をパターニングすることによって形成される。また、導電膜の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、又はこれらを複数組み合わせた材料を用いてもよい。40

#### 【0207】

より具体的には、例えば、絶縁膜724の開口を含む領域にPVD法によりチタン膜を薄く(5nm程度)形成した後に、開口部725に埋め込むようにアルミニウム膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、被形成面の酸化膜(自然酸化膜など)を還元し、下部電極など(ここでは導電膜720)との接触抵抗を低減させる機能を有する。また、アルミニウム膜のヒロックを防止することができる。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により

10

20

30

40

50

銅膜を形成してもよい。

【0208】

ここで、導電膜720と配線726とを接続させる場合について説明する。この場合、導電膜720を形成した後、ゲート絶縁膜721及び絶縁膜724において開口部を形成し、配線726を形成することになる。

【0209】

次に、配線726を覆うように絶縁膜727を形成する。上述した一連の工程により、半導体記憶装置を作製することができる。

【0210】

なお、上記作製方法では、ソース電極及びドレイン電極として機能する導電膜719及び導電膜720が、酸化物半導体層716の後に形成されている。よって、図10(B)に示すように、上記作製方法によって得られる第1のトランジスタ131は、導電膜719及び導電膜720が、酸化物半導体層716の上に形成されている。しかし、第1のトランジスタ131は、ソース電極及びドレイン電極として機能する導電膜が、酸化物半導体層716の下、すなわち、酸化物半導体層716と絶縁膜712及び絶縁膜713の間に設けられていても良い。

【0211】

図11に、ソース電極及びドレイン電極として機能する導電膜719及び導電膜720が、酸化物半導体層716と絶縁膜712及び絶縁膜713の間に設けられている場合の、第1のトランジスタ131の断面図を示す。図11に示す第1のトランジスタ131は、絶縁膜713を形成した後に導電膜719及び導電膜720の形成を行い、次いで酸化物半導体層716の形成を行うことで、得ることができる。

【0212】

ところで、不揮発性の半導体記憶装置に用いる記憶素子として磁気トンネル接合素子(MTJ素子)が知られている。MTJ素子は、絶縁膜を介して上下に配置している膜中のスピンの向きが平行であれば低抵抗状態、反平行であれば高抵抗状態となることで情報を記憶する素子である。従って、本実施の形態で示す酸化物半導体を用いた半導体記憶装置とは原理が全く異なっている。表1はMTJ素子と、本実施の形態に係る半導体記憶装置との対比を示す。

【0213】

【表1】

|             | スピントロニクス(MTJ素子)                                                    | OS/Si                                     |

|-------------|--------------------------------------------------------------------|-------------------------------------------|

| 1) 耐熱性      | キュリー温度                                                             | プロセス温度500°C<br>(信頼性150°C)                 |

| 2) 駆動方式     | 電流駆動                                                               | 電圧駆動                                      |

| 3) 書き込み原理   | 磁性体膜の磁化の向きを変える                                                     | FETのオン/オフ                                 |

| 4) Si LSI   | バイポーラLSI向き<br>(バイポーラは高集積化には不向きなため、高集積化回路ではMOSの方が好ましい。ただし、Wが大きくなる。) | MOSLSI向き                                  |

| 5) オーバーヘッド  | 大きい<br>(ジュール熱が大きいため)                                               | 2~3桁以上小さい<br>(寄生容量の充放電)                   |

| 6) 不揮発性     | スピノンを利用                                                            | オフ電流が小さいことを利用                             |

| 7) 電荷保持可能回数 | 無制限                                                                | 無制限                                       |

| 8) 3D化      | 難(できても二層まで)                                                        | 容易(何層でも可)                                 |

| 10) 材料      | 磁性を有する希土類                                                          | OS材料                                      |

| 11) 素子コスト   | 高い                                                                 | 低い<br>(OSを構成する材料によっては(Inなど)、多少コスト高の可能性有り) |

| 12) 磁界耐性    | 弱い                                                                 | 強い                                        |

【0214】

MTJ素子は磁性材料を使用するためキュリー温度以上にすると磁性が失われてしまうと

10

20

30

40

50

いう欠点がある。また、MTJ素子は電流駆動であるため、シリコンのバイポーラデバイスと相性が良いが、バイポーラデバイスは集積化に不向きである。そして、MTJ素子は書き込み電流が微少とはいえメモリの大容量化によって消費電力が増大してしまうといった問題がある。

#### 【0215】

原理的にMTJ素子は磁界耐性に弱く強磁界にさらされるとスピノの向きが狂いやすい。また、MTJ素子に用いる磁性体のナノスケール化によって生じる磁化揺らぎを制御する必要がある。

#### 【0216】

さらに、MTJ素子は希土類元素を使用するため、金属汚染を嫌うシリコン半導体のプロセスに組み入れるには相当の注意を要する。MTJ素子はビット当たりの材料コストから見ても高価であると考えられる。

#### 【0217】

一方、本実施の形態で示す酸化物半導体を用いた半導体記憶装置は、チャネルを形成する半導体材料が金属酸化物であること以外は、素子構造や動作原理がシリコンMOSFETと同様である。また、酸化物半導体を用いた半導体記憶装置は磁界の影響を受けず、ソフトエラーも生じ得ないといった特質を有する。このことからシリコン集積回路と非常に整合性が良いといえる。

#### 【0218】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【符号の説明】

#### 【0219】

|      |          |    |

|------|----------|----|

| 100  | 半導体記憶装置  | 10 |

| 101  | メモリセル    |    |

| 102  | 判定回路     |    |

| 103  | 電源線      |    |

| 131  | トランジスタ   |    |

| 132  | 容量素子     |    |

| 700  | 基板       |    |

| 701  | 絶縁膜      | 30 |

| 702  | 半導体膜     |    |

| 703  | ゲート絶縁膜   |    |

| 704  | 半導体層     |    |

| 707  | ゲート電極    |    |

| 709  | 不純物領域    |    |

| 710  | チャネル形成領域 |    |

| 712  | 絶縁膜      |    |

| 713  | 絶縁膜      |    |

| 716  | 酸化物半導体層  |    |

| 719  | 導電膜      | 40 |

| 720  | 導電膜      |    |

| 721  | ゲート絶縁膜   |    |

| 722  | ゲート電極    |    |

| 723  | 導電膜      |    |

| 724  | 絶縁膜      |    |

| 725  | 開口部      |    |

| 726  | 配線       |    |

| 727  | 絶縁膜      |    |

| 101A | メモリセル    |    |

| 101B | メモリセル    | 50 |

|           |                      |    |

|-----------|----------------------|----|

| 1 1 1 A   | メモリ回路                |    |

| 1 1 1 B   | メモリ回路                |    |

| 1 1 2 A   | 参照回路                 |    |

| 1 1 2 B   | 参照回路                 |    |

| 1 2 1 A   | トランジスタ               |    |

| 1 2 1 B   | トランジスタ               |    |

| 1 2 2 A   | 容量素子                 |    |

| 1 2 2 B   | 容量素子                 |    |

| 1 2 3 A   | トランジスタ               |    |

| 1 2 3 B   | トランジスタ               | 10 |

| 1 3 3 A   | トランジスタ               |    |

| 1 3 3 B   | トランジスタ               |    |

| 9 9 0 0   | 基板                   |    |

| 9 9 0 1   | ALU                  |    |

| 9 9 0 2   | ALU・Controller       |    |

| 9 9 0 3   | Instruction・Decoder  |    |

| 9 9 0 4   | Interrupt・Controller |    |

| 9 9 0 5   | Timing・Controller    |    |

| 9 9 0 6 A | CAM                  |    |

| 9 9 0 6 B | Register             | 20 |

| 9 9 0 7   | Memory・Controller    |    |

| 9 9 0 8   | Bus・I/F              |    |

| 9 9 0 9   | ROM                  |    |

| 9 9 2 0   | ROM・I/F              |    |

【図1】

【図2】

(B)

【図3】

(A)

(B)

【図4】

(A)

(B)

【図5】

(A) T1

(B) T2

【図6】

(A)

(B)

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図13】

(A)

(B)

(C)

- In

- Sn

- Zn

- O

【図 14】

---

フロントページの続き

(51) Int.CI.

F I

テーマコード(参考)

H 0 1 L 29/78 6 1 3 B

H 0 1 L 29/78 6 1 3 Z

F ターム(参考) 5F110 AA01 AA04 AA09 AA14 BB05 BB08 BB11 CC01 CC02 DD01

DD02 DD03 DD05 DD07 DD15 EE01 EE02 EE03 EE04 EE05

EE06 EE07 EE09 EE14 EE15 EE23 EE27 EE42 EE43 EE44

EE45 FF01 FF02 FF03 FF04 FF05 FF06 FF09 FF28 FF30

FF36 GG01 GG02 GG06 GG07 GG12 GG13 GG14 GG15 GG16

GG17 GG25 GG32 GG34 GG35 GG43 GG57 GG58 HJ01 HK01

HK02 HK03 HK04 HK06 HK07 HK21 HK41 HK42 HL01 HL02

HL03 HL04 HL06 HL11 HL22 HL23 NN03 NN22 NN23 NN24

NN28 NN34 NN35 NN40 NN72 NN78 PP01 PP02 PP03 PP10

PP34 QQ06 QQ11 QQ16 QQ19