(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 699 26 382 T2 2006.04.27

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 114 537 B1

(21) Deutsches Aktenzeichen: 699 26 382.4

(86) PCT-Aktenzeichen: PCT/SE99/01693

(96) Europäisches Aktenzeichen: 99 969 864.0

(87) PCT-Veröffentlichungs-Nr.: WO 00/19654

(86) PCT-Anmeldetag: 24.09.1999

(87) Veröffentlichungstag

der PCT-Anmeldung: 06.04.2000

(97) Erstveröffentlichung durch das EPA: 11.07.2001

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 27.07.2005

(47) Veröffentlichungstag im Patentblatt: 27.04.2006

(51) Int Cl.<sup>8</sup>: H04L 5/06 (2006.01)

H03H 17/02 (2006.01)

(30) Unionspriorität:

163298 30.09.1998 US

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

(73) Patentinhaber:

Telefonaktiebolaget LM Ericsson (publ),

Stockholm, SE

(84) Benannte Vertragsstaaten:

DE, GB, IT

(72) Erfinder:

HELLBERG, Richard, S-141 47 Huddinge, SE

(54) Bezeichnung: VERÄNDERTER ALGORITHMUS ZUR SCHNELLEN FALTUNG NIEDRIGERER KOMPLEXITÄT

UND HÖHERER FLEXIBILITÄT

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft generell ein Funkkommunikationssystem, genauer betrifft sie die Nutzung eines modifizierten schnellen Faltungsalgorithmus in Kanalisierern und Entkanalisierern eines Funkkommunikationssystems.

**[0002]** In Funkbasisstationsanwendungen in zellbasierten, Land-Mobile-Radio-, Satelliten-, WLAN-(Wireless Local Area Network) und anderen Kommunikationssystemen werden Empfangs- und Sendekanäle gleichzeitig bedient. Zukünftig werden mobile Datenendgerät wie beispielsweise mobile Telefone weiterhin diese Möglichkeit beibehalten. Derartige Systeme beinhalten digitale Kanalisierungs- und De-Kanalierungsstrukturen in ihren entsprechenden Empfängern und Sendern. Kanalisierung und De-Kanalierung kann als das Filtern, die Dezimierung/Interpolation und die Frequenzumwandlung des empfangenen oder gesendeten Signals definiert werden.

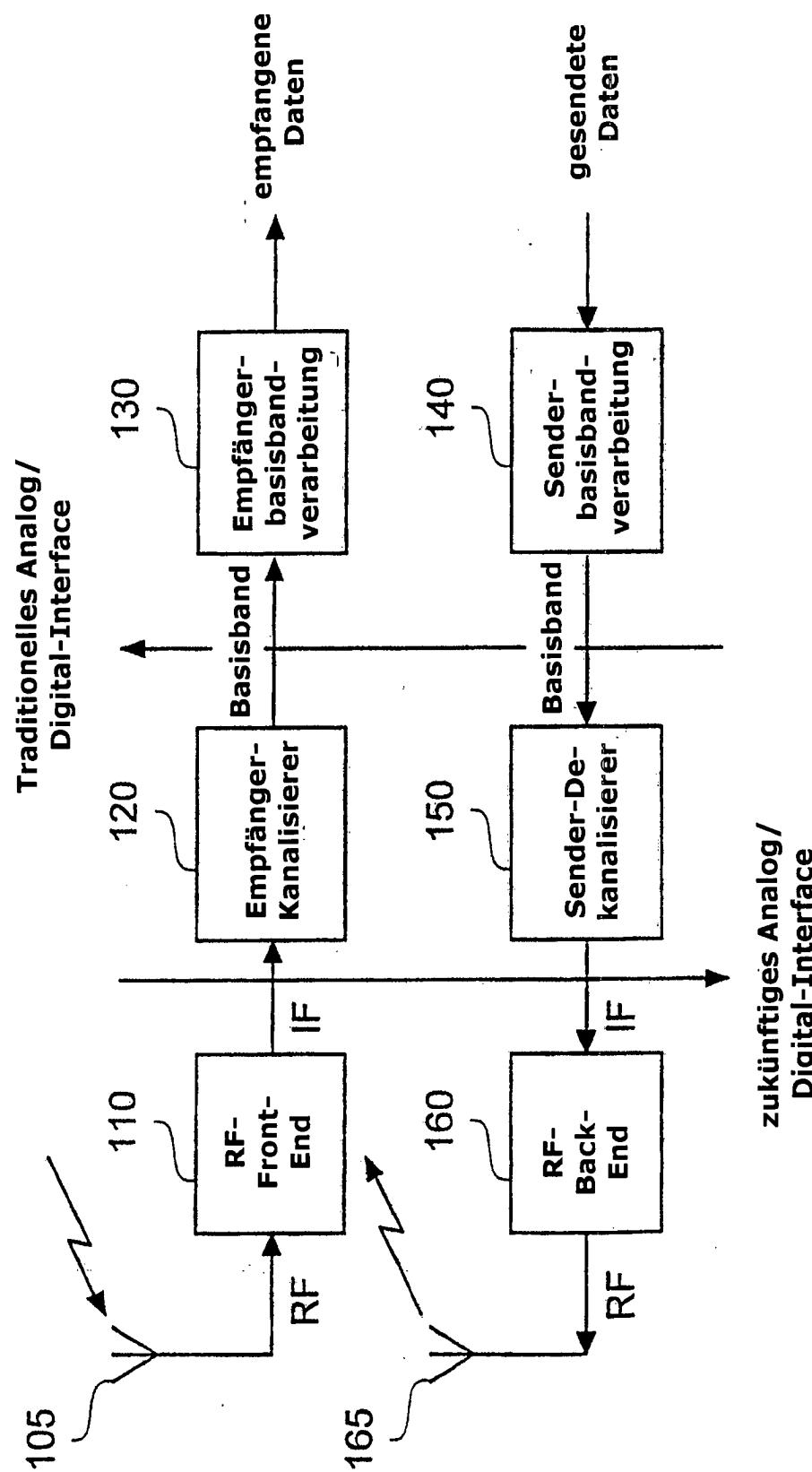

**[0003]** Die traditionelle Empfängerarchitektur ist in [Fig. 1](#) dargestellt. In [Fig. 1](#) wird ein Funkfrequenzsignal (RF = Radio Frequency) von der Antenne **105** empfangen und dann durch ein RF-Frontend **110** auf eine Zwischenfrequenz (IF = Intermediate Frequency) umgesetzt. Das RF-Frontend besteht aus Komponenten wie gering rauschende Verstärker (LNAs = Low Noise Amplifier), Filter und Mischer. Der gewünschte Kanal wird dann durch den Empfängerkanalisierer **120** extrahiert. Der analoge Kanalisierer besteht auch aus gering rauschenden Verstärkern (LNA), Mischern und Filtern.

**[0004]** Der gewünschte Kanal wird dann im Basisband durch die Empfängerbasisbandverarbeitungseinheit **130** verarbeitet, um den empfangenen, digitalen Datenstrom zu produzieren. Heute enthält die Basisbandverarbeitung Analog-zu-Digital-Umwandlung (AD-Wandlung), digitale Filterung, Dezimierung, Ausgleichung, Demodulation, Kanal-Dekodierung, Entschränkung (de-interleaving), Daten-Dekodierung, Zeitextraktion, usw..

**[0005]** Die traditionelle Senderarchitektur in [Fig. 1](#) ist das Gegenstück der Empfängerarchitektur. Die zu sendenden Daten werden zuerst durch die Senderbasisbandverarbeitungseinheit **140** verarbeitet, welche Datenkodierung, Verschränkung (interleaving), Kanalkodierung, Modulation, Interpolationsfilterung, Digital-zu-Analog-Umwandlung (DA-Wandlung) usw. enthält. Der Basisbandkanal wird dann in eine Zwischenfrequenz über den Sender-De-Kanalierer **150** umgewandelt. Der Sender-Analog-De-Kanalierer **150** besteht aus Filtern, Mischern und Verstärkern geringer Leistung. Das Zwischenfrequenzsignal wird dann zu einem Funksignal umgewandelt und durch das RF-Frontend **160**, welches aus Mischern, Filtern und

einem Hochleistungsverstärker besteht, umgewandelt. Schließlich wird das Signal über die Antenne **165** abgestrahlt.

**[0006]** [Fig. 1](#) stellt die traditionelle Architektur eines Einkanalempfängers und -senders eines mobilen Datenendgerätes (z.B. ein Mobiltelefon) dar. Im Falle der Basisstation werden Mehrfachkanäle in ähnlicher Weise verarbeitet. Auf der Empfängerseite wird der Pfad an einem Punkt auf gesplittet, um mehrere Pfade für jeden zu verarbeitenden Kanal zu bilden. Auf der Senderseite werden die Kanäle individuell verarbeitet und dann an einem Punkt gemischt, um ein Mehrkanalsignal zu bilden. Der Punkt der Aufspaltung und der Mischung variiert, und deshalb wurde eine Vielzahl von Basisstationsempfänger- und -senderarchitekturen entworfen. Wichtiger ist aber, dass das analoge und digitale Interface derzeit irgendwo zwischen dem Kanalisierer und den Basisbandverarbeitungsblöcken liegt.

**[0007]** Der analoge Kanalisierer/De-Kanalierer ist komplex zu entwerfen und herzustellen und deshalb teuer. Um einen billigeren und leichter herzustellenden Kanalisierer/De-Kanalierer bereitzustellen, wird das zukünftige Analog- und Digital-Interface stattdessen irgendwo zwischen dem RF-Frontend- und Kanalisiererblöcken liegen. Zukünftige Funkempfänger- und Senderstrukturen dieser Art haben vielfältige Namen inklusive Mehrkanalradio, Breitband-Digital-Tuner, Breitband-Radio oder Software-Radio, und sie alle erfordern einen digitalen Kanalisierer/De-Kanalierer.

**[0008]** Effiziente digitale Kanalisierer/De-Kanalierer-Strukturen, welche Filterung, Dezimierung/Interpolation und Frequenzumwandlungen ausführen, sind wichtig in Bezug auf die Leistungsaufnahme und den Platzbedarf auf einer Pro-Kanal-Basis. Eines der Hauptziele dieser Strukturen ist es, so viele Kanäle wie möglich in einem einzigen integrierten Schaltkreis (IC) zu integrieren.

**[0009]** Eine Transceiver-Vorrichtung, welche einen Breitband-FFT-Kanalierer und einen inversen FFT-Mischer für ein Multikanalkommunikationsnetzwerk verwenden, wurde am 9. Juli 1996 in US-A-5,535,240 (Carney et al.) veröffentlicht. Die Transceiver-Vorrichtung enthält einen Empfängerbereich, welcher einen Breitband-Diskrete-Fourier-Transformation-Kanalierer (DFT = discrete Fourier Transformation) zur Verarbeitung von mehreren Kanälen von digitalisierten, empfangenen Kanälen und einen Senderbereich, welcher einen Breitband-Inverse-DFT-Mischer zur Verarbeitung von mehreren digitalisierten Sendekanalsignalen enthält.

**[0010]** Ein effizientes und flexibles Kanalisierungsverfahren wird in der Druckschrift US 6.611.855 mit dem Titel "Flexible and efficient Channelizer Arch-

titectre", die am 26. August 2003 veröffentlicht wurde, vorgestellt. Das darin vorgestellte Verfahren basiert auf einem Faltungsalgorithmus zu effizienten Implementierung von Filtern, wobei die Abhängigkeit zwischen Multiplikationen im Frequenz(Fourier)-Bereich und der Faltung im Zeitbereich genutzt wird.

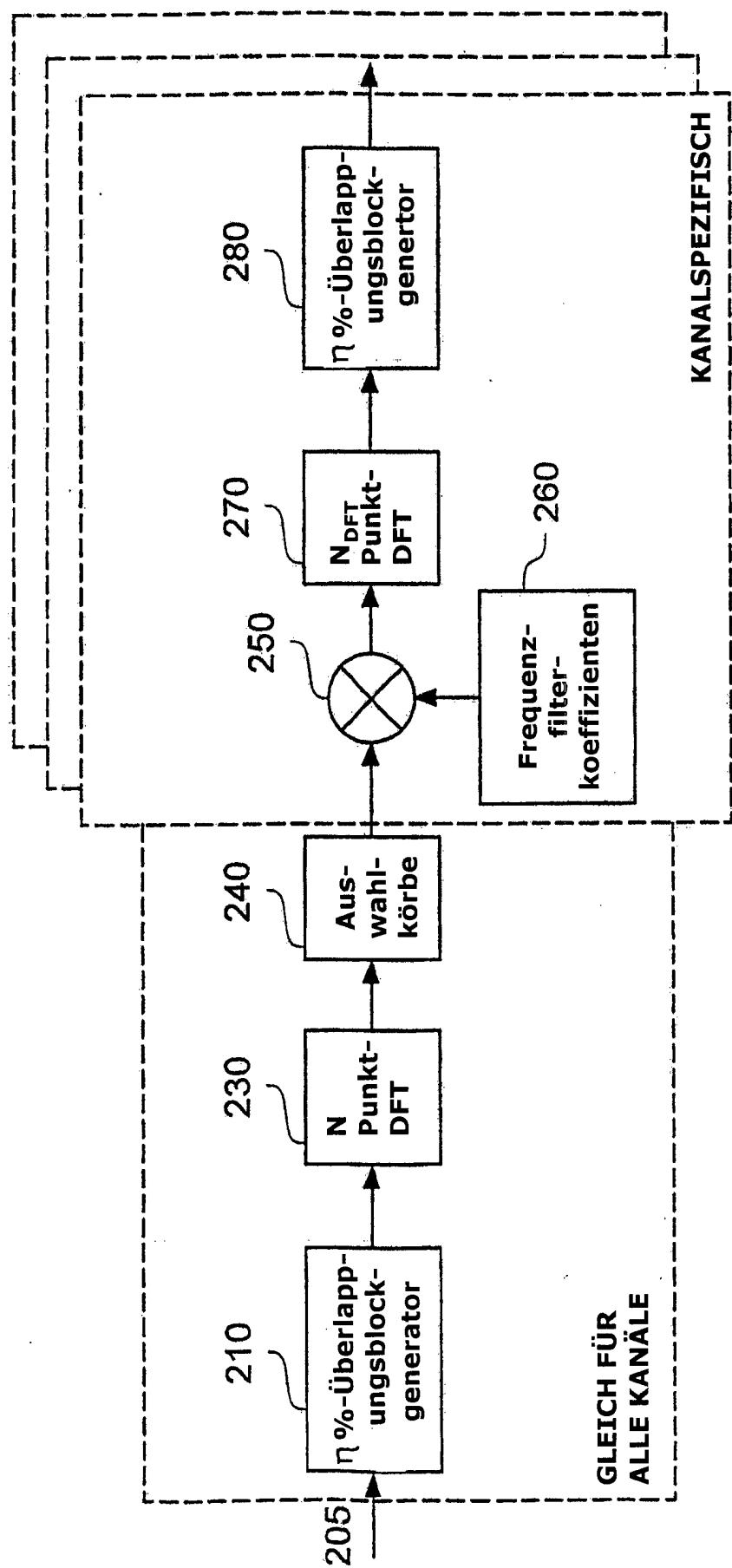

**[0011]** [Fig. 2A](#) und [Fig. 2B](#) stellen einen modifizierten schnellen Faltungsalgorhythmus, der entsprechend auf einen Kanalisierer und einen De-Kanalisiere angewandt wird, dar. In [Fig. 2A](#) wird ein Eingangssignal **205** an den Kanalisierer gelegt. Das Eingangssignal **205** ist ein Datenstrom, der von einer vorherigen Verarbeitung wie einer AD-Wandlung kommt.

**[0012]** Der Datenstrom **205** wird zuerst von einem  $\eta\%$ -Überlappungsblockgenerator **210** verarbeitet. Der Prozess basiert auf dem Wert der prozentualen Überlappung, der Größe der Diskreten-Fourier-Transformation (DFT) und der Art der Überlappung, namentlich überlappend/addierend oder überlappend/gesichert, wie es unten diskutiert wird. Im Falle des Überlappens und Addierens wird der Datenstrom in nicht überlappende Bereiche der Länge  $N_{DFT} \cdot (1 - \eta)$  zerhackt und mit  $N_{DFT} \cdot \eta$  Nullen umhüllt, um einen vollständigen Block zu bilden. Im Falle des Überlappens und Sicherns werden die Daten in Blöcke der Länge  $N_{DFT}$  zerhackt, welche eine Überlappung, die durch eine Länge  $N_{DFT} \cdot \eta$  gegeben ist, mit dem vorherigen Block aufweist.

**[0013]** Die resultierenden Blöcke werden dann in den DFT-Algorithmus geschickt. Der DFT-Algorithmus wird in Block **230** komplettiert. Als Ergebnis der Pipeline-FFT-Verarbeitung ist der Ausgang der FFT nicht in der richtigen Reihenfolge. Deshalb muss dies der Korbauswahl- und Extraktionsblock **240** durch Neuordnung der Ausgangssequenz und ausschließlichen Auswahl der benötigten Körbe kompensieren. Die Anzahl der benötigten Körbe hängt von der Anzahl der Filterkoeffizienten **260** ab.

**[0014]** Die ausgewählten Körbe werden mit den Filterfrequenzkoeffizienten **260** im Multiplizierer **250** multipliziert. Eine inverse, diskrete Fourier-Transformation (inverse-DFT oder IDFT) **270** wird dann auf dem Ergebnis der vorherigen Multiplikation komplettiert.

**[0015]** Der Ausgang der IDFT wird dann in den  $\eta\%$ -Überlappungsblockmischer **280** gegeben. Der Kombinationsarbeitsschritt hängt von der prozentualen Überlappung der Blöcke und davon, ob ein Überlappen/Sichern oder eine Überlappen/Addition angewendet wird, ab. Sowohl bei „Überlappen und Addieren“ als auch bei „Überlappen und Sichern“ überlappen die Blöcke mit den vorherigen Blöcken auf einer Länge gleich  $N_{IDFT} \cdot \eta$ . Beim „Überlappen und Addieren“ wird der Überlappungsanteil des Blocks zu

dem entsprechenden Überlappungsblockanteil des vorherigen Blockes hinzugefügt, während beim „Überlappen und Sichern“ der überlappende Anteil des Blockes einfach gelöscht wird. Sowohl für „Überlappen und Addieren“ als auch für „Überlappen und Sichern“ wird keine Operation auf dem nicht überlappenden Anteil des Blockes ausgeführt.

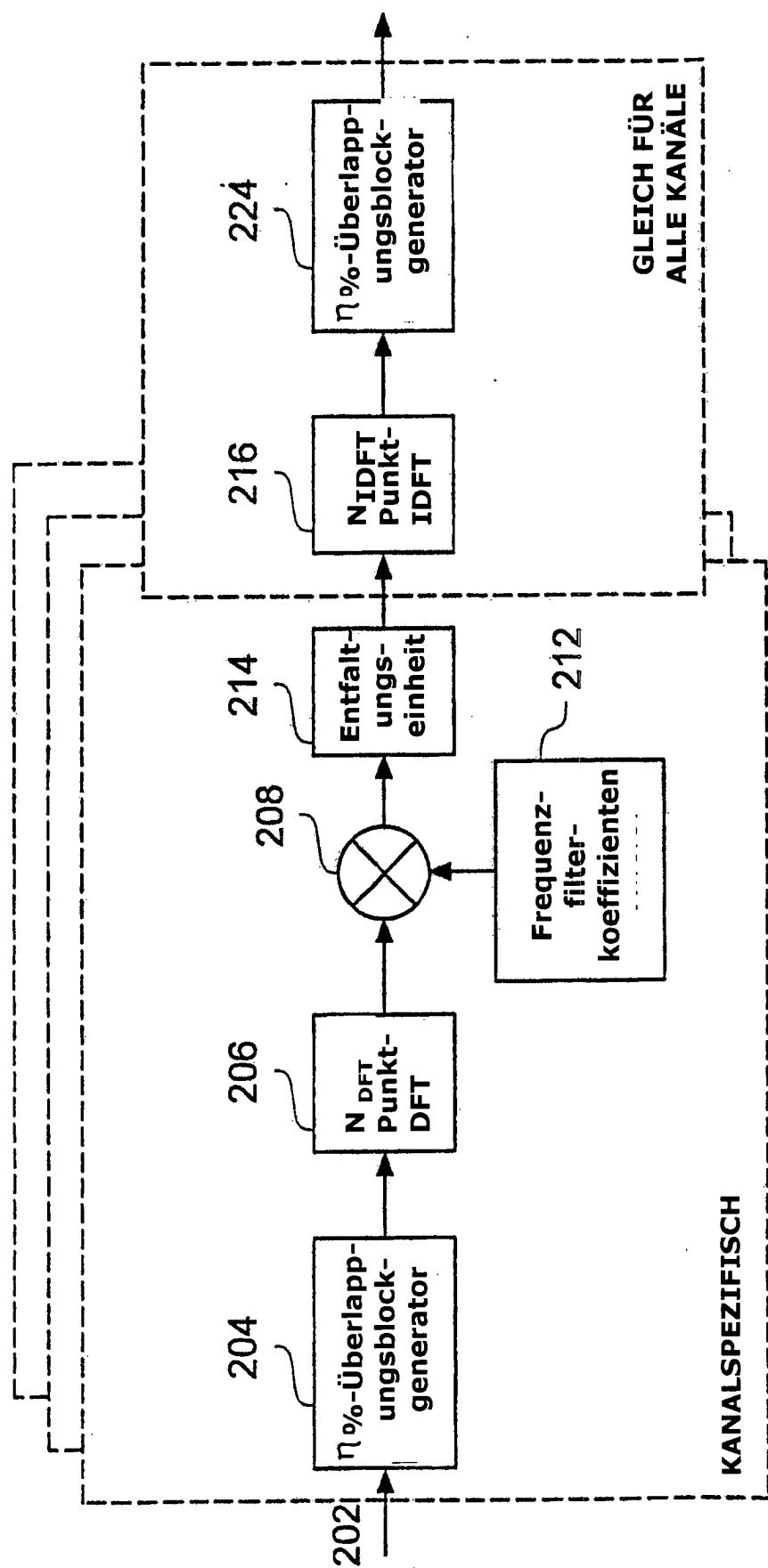

**[0016]** [Fig. 2B](#) stellt den auf den De-Kanalisiere angewendeten, modifizierten, schnellen Faltungsalgorhythmus dar. Das Eingangssignal ist ein Strom von Daten **202** aus einem vorherigen Prozess wie einer AD-Wandlerverarbeitung. Im Gegensatz zu [Fig. 2A](#) ist der Eingangsdatenstrom für einen Kanal spezifisch und nicht für eine Stromkombination, die mehrere Kanäle vereint.

**[0017]** Der Datenstrom **202** wird zuerst durch einen  $\eta\%$ -Überlappungsblockgenerator verarbeitet. Der Prozess basiert weitgehend auf dem Wert der prozentualen Überlappung, der Größe der DFT und der Art der Überlappung, die Überlappung/Addieren oder Überlappung/Sichern ist. Im Falle des „Überlappen und Addieren“ wird der Datenstrom in nicht überlappende Bereiche der Länge  $N_{DFT} \cdot (1 - \eta)$  zerhackt und in  $N_{DFT} \cdot \eta$  Nullen eingebettet, um einen einzigen Block zu bilden. Im Fall von „Überlappen und Sichern“ werden die Daten in Blöcke eine Länge von  $N_{DFT}$  zerhackt, welche eine Überlappung mit dem vorherigen Block, welche durch die Länge  $N_{DFT} \cdot \eta$  gegeben ist, aufweisen.

**[0018]** Die diskrete Fourier-Transformation (DFT) wird dann auf dem Ergebnis des vorherigen Arbeitsschrittes komplettiert. Dem Fachmann ist bekannt, dass die DFT **206** alternativ als eine FFT implementiert sein könnte. Im Gegensatz zum Empfänger der [Fig. 2A](#) ist die DFT-Struktur (**206**) schmal und die IDFT-Struktur (**216**) breit – im Gegenteil zum Empfängers.

**[0019]** Der Block wird dann durch die Multiplizierer **208** mit den Filterfrequenzkoeffizienten **212** multipliziert. Die Frequenzfilterkoeffizienten **212** sind äquivalent zur DFT der Impulsantworten.

**[0020]** Die Ergebnisse der Multiplikation werden dann als Eingangskorbblock **214** für die inverse, diskrete Fourier-Transformation (IDFT) **216** genutzt, und der IDFT-Algorithmus wird dann komplettiert. Der Ausgang des IDFT-Algorithmus wird durch den  $\eta\%$ -Überlappungsblockmischer **224** verarbeitet.

**[0021]** Die Blöcke werden in dem Blockmischer **224**, in Abhängigkeit von ihrer prozentualen Überlappung und davon abhängig, ob eine Überlappung/Sicherung oder Überlappung/Addition verwendet wird, gemischt. Sowohl für Überlappen/Addieren als auch für Überlappen/Sichern überlappen die Blöcke mit dem vorherigen Block auf einer Länge von  $N_{IDFT} \cdot \eta$ . Beim

Überlappen/Addieren wird der überlappende Anteil des Blockes zu dem entsprechenden Überlappungsanteil des vorherigen Blockes hinzugefügt, während beim Überlappen/Sichern der Überlappungsanteil des Blockes einfach gelöscht wird. Sowohl beim Überlappen/Addieren als auch beim Überlappen/Sichern werden keine Arbeitsschritte auf den nicht überlappenden Bereichen ausgeführt.

**[0022]** Die Druckschrift US-6,266,687B1 mit Namen "Flexibility Enhancements to the Modified Fast Convolution Algorithm", die am 24. Juli 2001 veröffentlicht wurde, detailliert die Schritte der Komponenten der [Fig. 2A](#) und [Fig. 2B](#) weiter.

**[0023]** Bei dem modifizierten schnellen Faltungsalgorithmus, wie er in Kanalisiern nach dem Stand der Technik genutzt wird, ist die Anzahl der Punkte in der IDFT (berechnet nach IFFT) eine Zweierpotenz. Die gleiche oder eine etwas geringere Anzahl von Frequenzkoeffizienten wird bei dem Frequenzbereichsfilter genutzt.

**[0024]** Ein Problem bei Systemen nach dem Stand der Technik ist es, dass die maximale Anzahl der Frequenzkomponenten begrenzt ist (auf die Anzahl der Frequenzkomponenten in der IDFT/DFT), wenn eine IDFT/DFT-Größe festgelegt wird, und deshalb auch die ultimative Filterzurückweisung begrenzt ist. Das heißt, dass entweder die erforderliche Zurückweisung nicht erreicht werden kann, oder dass es notwendig wird, eine doppelt so große IDFT/DFT zu wählen, um zu den Frequenzkomponenten zu passen. Die Anzahl der Arbeitsschritte kann deshalb durch eine kleine Erhöhung in der Filterzurückweisung drastisch anwachsen. Kurz gesagt, sind in Lösungen nach dem Stand der Technik die unterschiedlichen Systemparameter (das heißt Filterbandbreite, DFT/IDFT-Größe und Abtastrate) sehr eng miteinander verknüpft.

**[0025]** In dem kanalspezifischen Anteil von auf dem modifizierten, schnellen Faltungsalgorithmus basierenden Kanalisiern benötigen die schmale IDFT in einem Empfänger und die schmale DFT in einem Sender viele Arbeitsschritte bei ihren Berechnungen. Dieses begrenzt sowohl wegen des Leistungsverbrauches und als auch wegen der begrenzten Anzahl von Verarbeitungselementen, die auf dem gleichen Chip integrierbar sind, die Anzahl der Kanäle, die kanalisiert/de-kanalisiert werden können. Wenn ein festverdrahteter, kanalspezifischer Anteil genutzt wird, bleibt der Leistungsverbrauch der Hauptbegrenzungsfaktor. Wenn eine flexible Architektur, die auf einem programmierbaren Prozessor basiert, gewünscht ist, kann die Anzahl der Arbeitsschritte – sogar triviale als auch wenig Energie verbrauchende – die Anzahl der handhabbaren Kanäle begrenzen. Deshalb gibt es einen starken Anreiz, die Anzahl der Arbeitsschritte in dem Kanal-spezifischen Anteil des

modifizierten, schnellen Faltungsalgorithmus zu reduzieren.

### Zusammenfassung

**[0026]** Die vorliegende Erfindung versucht den oben beschriebenen, modifizierten, schnellen Faltungsalgorithmus zu verbessern, um die Flexibilität des Algorithmus zu erhöhen. In einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung wird eine Faltungseinheit als eine Vorverarbeitungsstufe vor der IDFT in dem Empfänger eingeführt. Die Faltungseinheit fügt äußere Frequenzkomponenten zu inneren Frequenzkomponenten in dem Frequenzbereich hinzu, um einen reduzierten Satz von Frequenzkomponenten zu erzeugen.

**[0027]** In einem alternativen Ausführungsbeispiel wird eine Entfaltungseinheit als Nachverarbeitungsstufe nach der DFT in dem Sender eingeführt. Die Entfaltungseinheit expandiert den Satz des Frequenzkomponentensatzes durch Addition übersetzter Originalkomponenten außerhalb des Originalsatzes.

**[0028]** Der Faltungs- und Entfaltungsprozess erhöht die Flexibilität des modifizierten, schnellen Faltungsalgorithmus durch die Reduktion der Anzahl der Verarbeitungsschritte pro Sekunde, die für den kanalspezifischen Anteil des Algorithmus ausgeführt werden müssen. Darüber hinaus können mehr Kanäle durch einen einzigen Chip behandelt werden, weil die Anzahl der Verarbeitungsschritte pro Kanal abnimmt.

### Kurze Beschreibung der Zeichnungen

**[0029]** Die obigen Ziele und Funktionen der vorliegenden Erfindung werden durch die folgende Beschreibung der bevorzugten Ausführungsbeispiele und mit Blick auf die begleitenden Zeichnungen besser ersichtlich. Dabei bedeuten:

**[0030]** [Fig. 1](#) stellt einen konventionellen Sender und Empfänger dar;

**[0031]** [Fig. 2A](#) stellt den auf einen Kanalisiere angewendeten modifizierten, schnellen Faltungsalgorithmus dar;

**[0032]** [Fig. 2B](#) stellt den auf einen De-Kanalisiere angewendeten modifizierten, schnellen Faltungsalgorithmus dar;

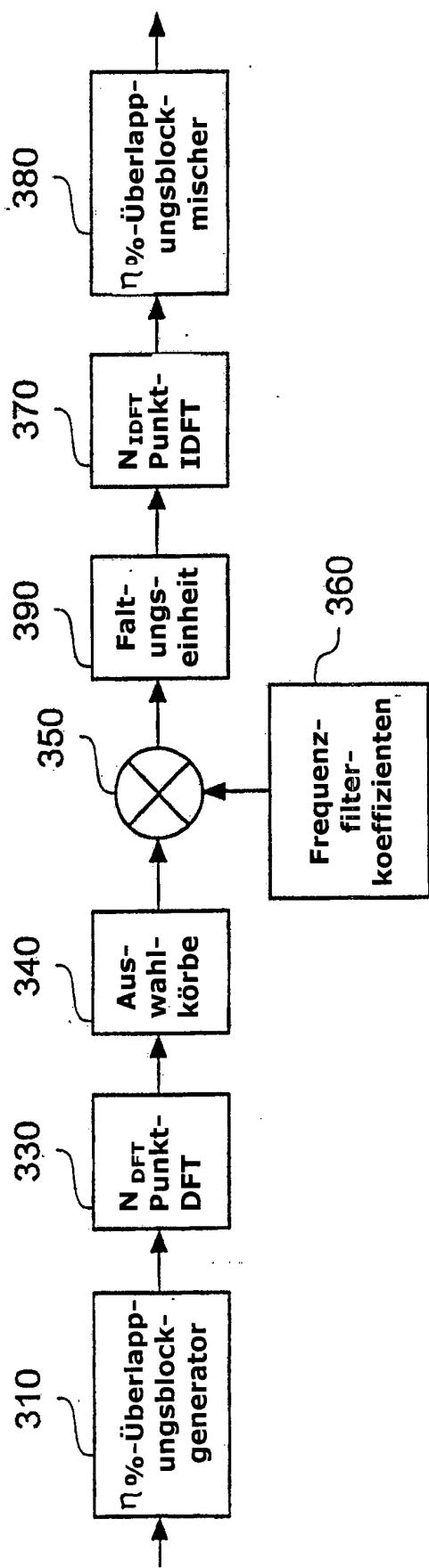

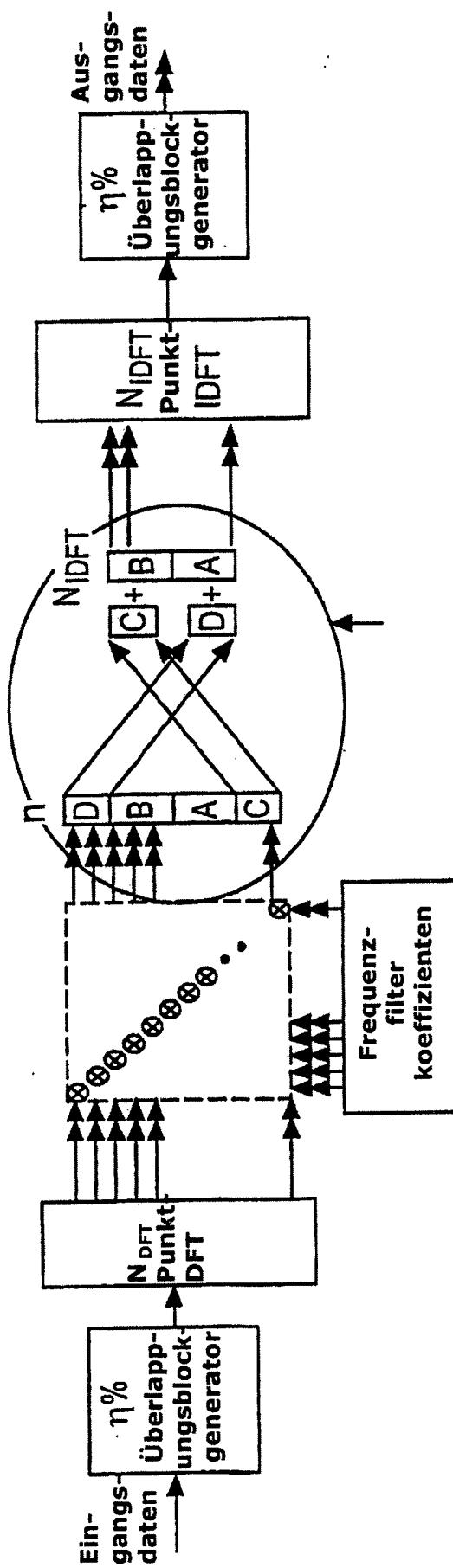

**[0033]** [Fig. 3](#) stellt den auf einen Kanalisiere angewandten modifizierten, schnellen Faltungsalgorithmus entsprechend einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung dar;

**[0034]** [Fig. 4](#) stellt den Faltungsprozess entsprechend einem Ausführungsbeispiel der vorliegenden

Erfindung dar;

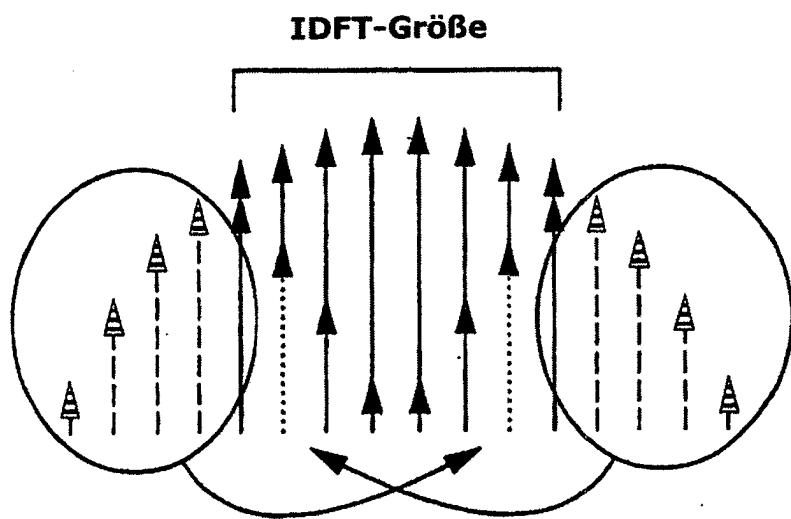

[0035] [Fig. 5](#) stellt die Platzierung des Faltungsprozesses in dem modifizierten, schnellen Faltungsalgorithmus entsprechend der vorliegenden Erfindung dar;

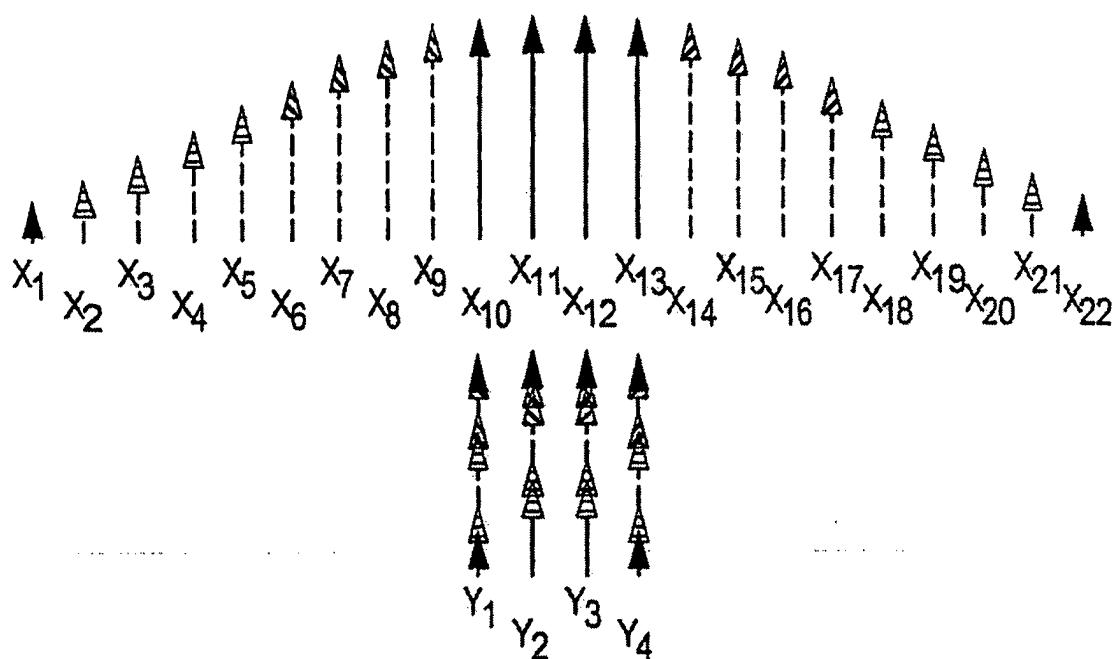

[0036] [Fig. 6](#) stellt einen Faltungsprozess höherer Ordnung entsprechend einem Ausführungsbeispiel der vorliegenden Erfindung dar;

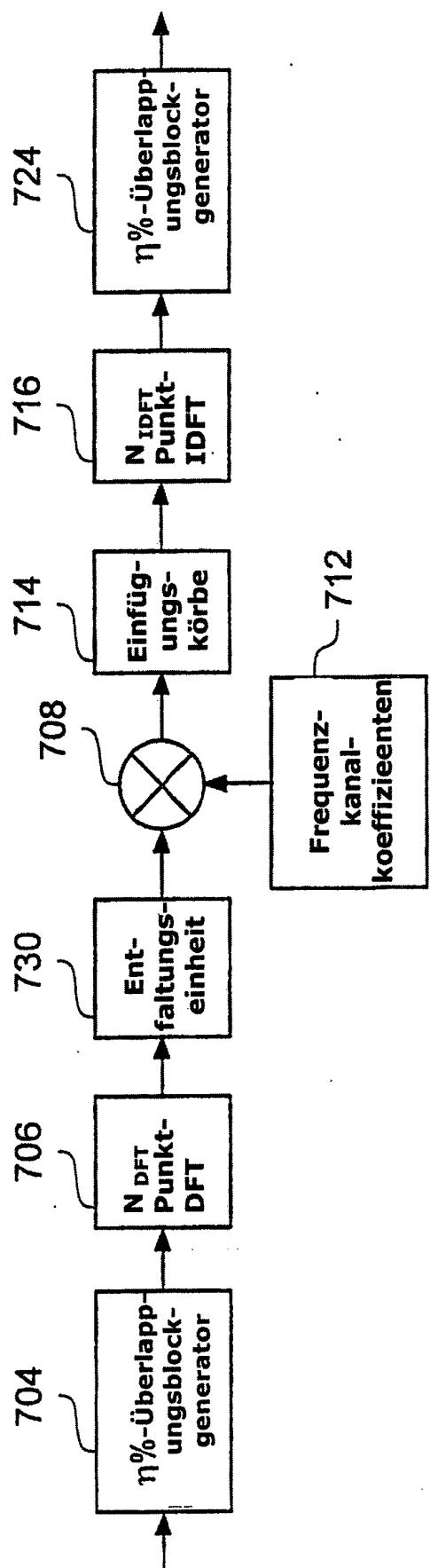

[0037] [Fig. 7](#) stellt den auf einen De-Kanalisierer angewendeten modifizierten, schnellen Faltungsalgorithmus entsprechend einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung dar;

[0038] [Fig. 8](#) stellt den Entfaltungsprozess entsprechend einem Ausführungsbeispiel der vorliegenden Erfindung dar;

[0039] [Fig. 9](#) stellt die Platzierung des Entfaltungsprozesses in dem modifizierten, schnellen Faltungsalgorithmus entsprechend der vorliegenden Erfindung dar; und

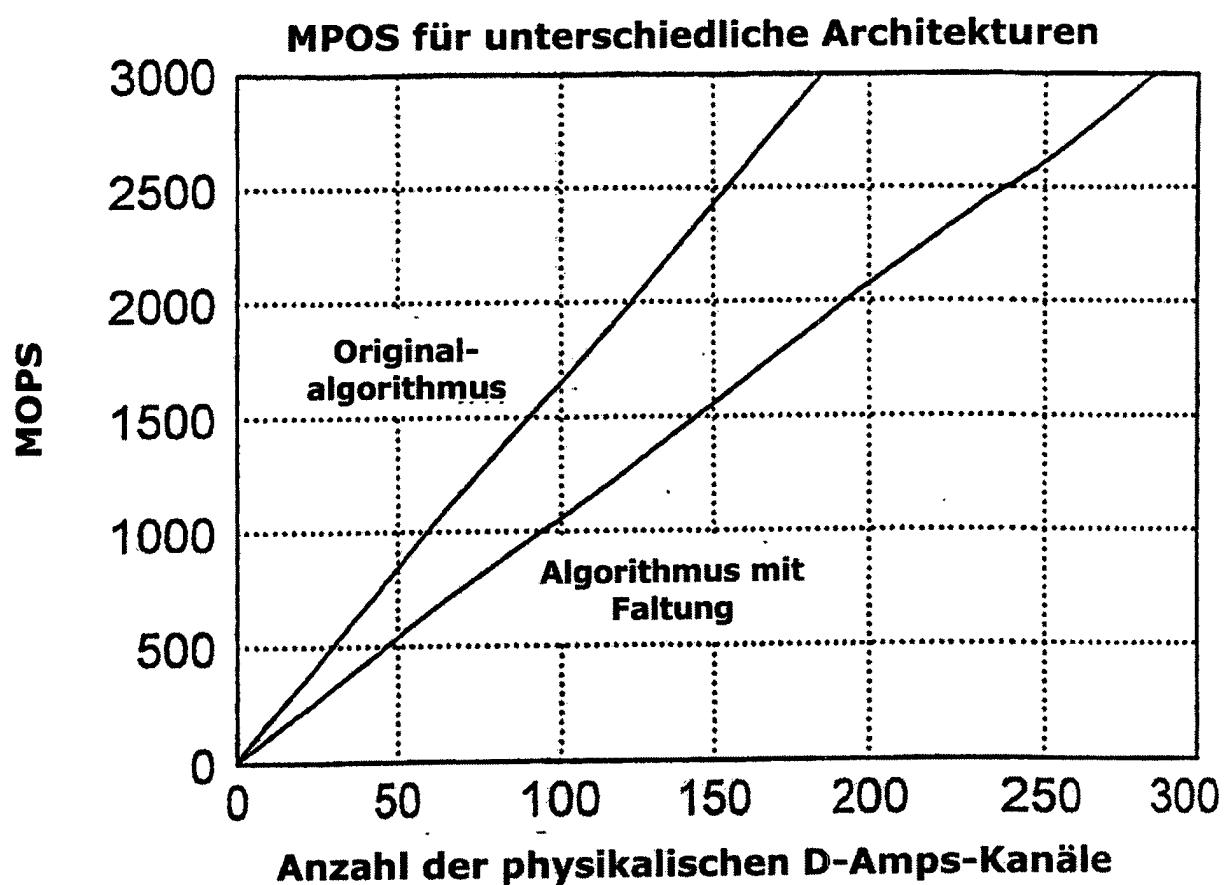

[0040] [Fig. 10](#) stellt einen Vergleich der Leistung eines modifizierten schnellen Faltungsalgorithmus nach dem Stand der Technik mit dem modifizierten, schnellen Faltungsalgorithmus der vorliegenden Erfindung dar.

#### Detaillierte Beschreibung

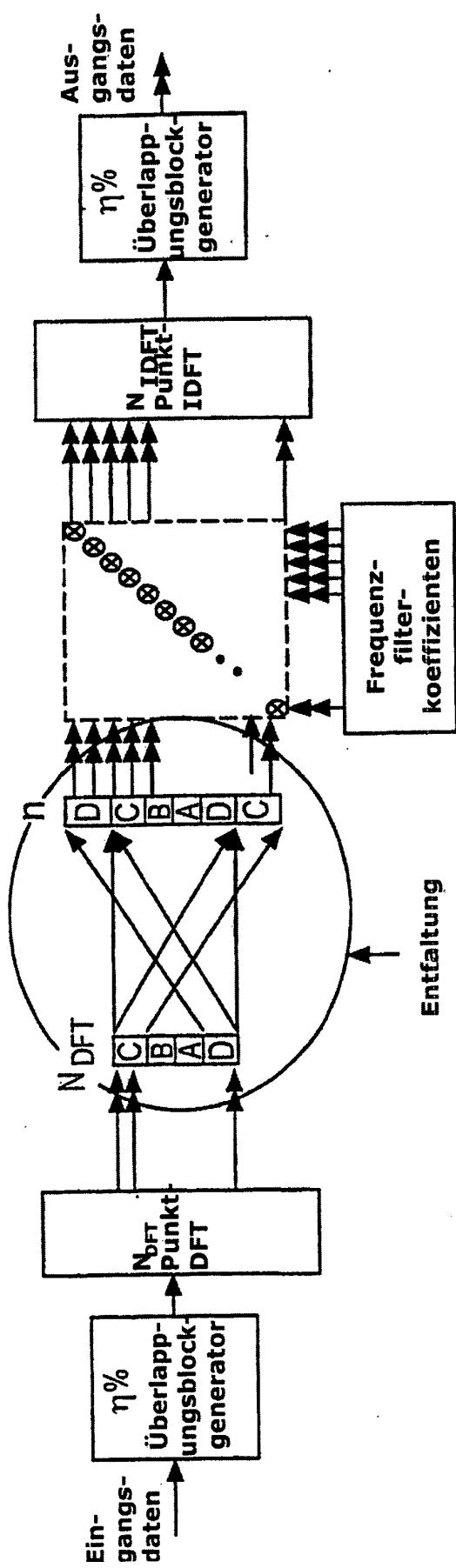

[0041] [Fig. 3](#) stellt den auf einen Kanalisierer angewendeten modifizierten, schnellen Faltungsalgorithmus entsprechend einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung dar. Ähnlich der Beschreibung der [Fig. 2A](#) enthält der auf den Kanalisierer angewandte, modifizierte, schnelle Faltungsalgorithmus der in [Fig. 3](#) dargestellten, vorliegenden Erfindung einen  $\eta$ -% Überlappungsblockgenerator **310**, eine große  $N_{DFT}$ -Punkt-DFT, einen Auswahlkorbblock **340**, einen Multiplizierer **350** zur Multiplikation der Auswahlkörbe mit Frequenzfilterkoeffizienten **360**, eine kleine  $N_{IDFT}$ -Punkt-IDFT **370** und einen  $\eta$ -% Überlappungsblockmischer, der in einer ähnlichen wie die oben beschriebenen Art arbeitet. Darüber hinaus enthält das System entsprechend dem vorliegenden Ausführungsbeispiel eine Faltungseinheit **390**, die den erfinderischen Faltungsprozess ausführt.

[0042] Die Faltungseinheit **390** addiert ausgewählte Frequenzkomponenten zu anderen Frequenzkomponenten; dieses wird in folgendem "Faltung" im Frequenzbereich genannt. Frequenzfaltung ist der Prozess des Addierens von äußeren Frequenzkomponenten zu den verbleibenden, inneren Frequenzkomponenten.

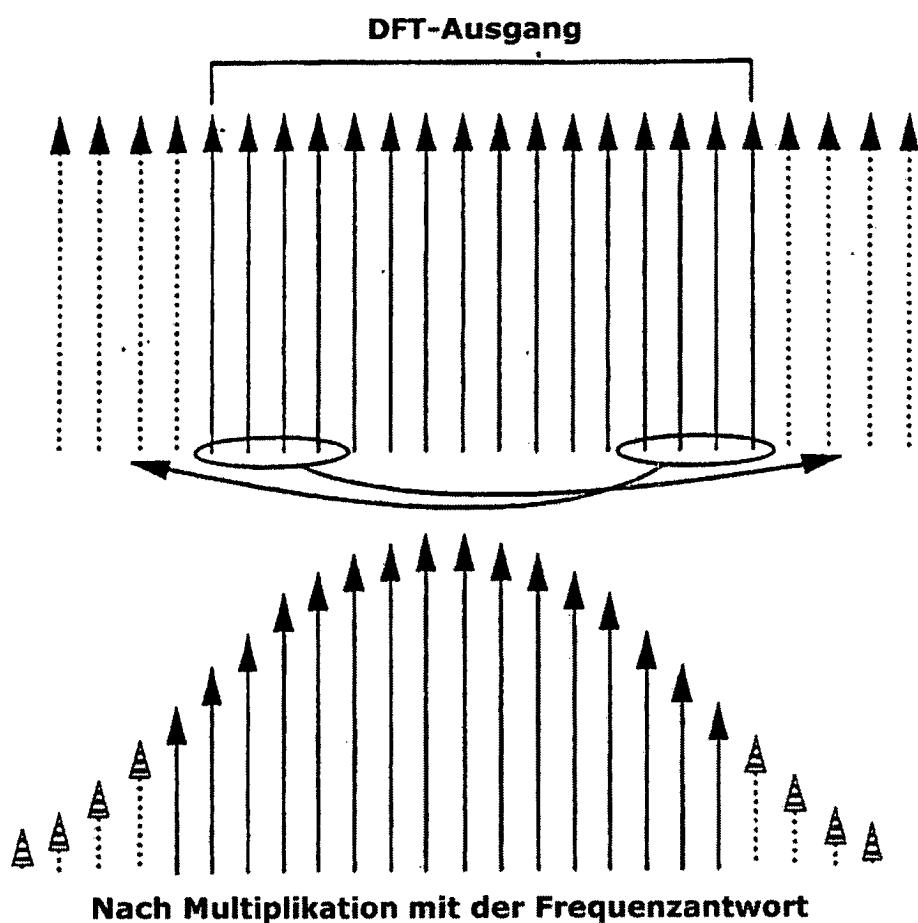

[0043] [Fig. 4](#) stellt den Faltungsprozess dar. In [Fig. 4](#) werden 16 Frequenzkomponenten in acht Frequenzkomponenten durch Addieren der äußeren 4 Komponenten auf der linken Seite zu den inneren 4 Komponenten auf der rechten Seite und durch Addieren der äußeren 4 Komponenten auf der rechten Seite zu den inneren 4 Komponenten auf der linken Seite gefaltet. Der Fachmann erkennt, dass die Faltung in der komplexen Ebene ablaufen wird, weil das Signal ein komplexes, imaginäre und reale Anteile enthaltendes Signal ist, und deshalb die rechten, äußeren Frequenzkomponenten um  $-90^\circ$  verschoben werden, wenn sie gefaltet werden, und in den in [Fig. 4](#) ausgewiesenen Bereichen landen werden.

[0044] Als Ergebnis des Faltungsprozesses sind die ursprünglichen 16 Frequenzkomponenten auf 8 Frequenzkomponenten reduziert. Der Faltungsprozess der vorliegenden Erfindung resultiert in einem reduzierten Satz von Frequenzkomponenten, der mit einer kleineren IDFT **370** verarbeitet werden kann, als es sonst der Fall wäre. Die Bildung des in [Fig. 4](#) dargestellten 8-Punktesatzes kann einfach geschrieben werden als

$$Y_{0-3} = X_{4-7} \cdot X_{12-15}$$

$$Y_{4-7} = X_{8-11} \cdot X_{0-3}$$

[0045] [Fig. 5](#) stellt die Platzierung des Faltungsprozesses innerhalb des in [Fig. 3](#) vorgestellten, modifizierten, schnellen Faltungsalgorithmus dar. Der Faltungsprozess wird ausgeführt, nachdem die Körbe mit den Frequenzfilterkoeffizienten modifiziert wurden, und bevor die Daten der IDFT zugeführt werden. Wie man [Fig. 5](#) selbstverständlich entnimmt, sind die exemplarischen 4 Frequenzkomponenten der Multiplizierergebnisse mit D, B, A und C gekennzeichnet. Die Faltungseinheit faltet die äußeren Frequenzkomponenten D und C auf die inneren Komponenten A und B, um so die Anzahl der Frequenzkomponenten, die durch die IDFT verarbeitet werden müssen, zu reduzieren.

[0046] Entsprechend einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung kann die Faltung im Frequenzbereich auf höhere Ordnungen ausgedehnt werden. Das heißt, dass die Frequenzkomponenten mehr als einmal nach innen gefaltet und addiert werden können, wie es in [Fig. 6](#) dargestellt ist. Das bedeutet, dass drei oder mehrere Komponenten zur Bildung einer inneren Komponente für die IDFT zusammenaddiert werden. Wie in [Fig. 6](#) dargestellt, werden 22 Frequenzkomponenten – gekennzeichnet mit  $X_1-X_{22}$  – mit dem Faltungsprozess der vorliegenden Erfindung in Frequenzkomponenten  $Y_1-Y_4$  gefaltet. Dieser Faltungsprozess würde es einer 4-Punkt-DFT erlauben, die 22 Frequenzkomponenten in einem einzigen Verarbeitungsschritt zu verarbeiten.

**[0047]** Faltungen höherer Ordnung sind besonders nützlich, wenn die Filterzurückweisung weit entfernt von der Trägerfrequenz sehr hoch sein muss, während die Anforderungen in der Nähe der Trägerfrequenz relativ lasch sind. Eine generelle Formel für Faltungen höherer Ordnung ist unten angegeben. Für die äußeren Frequenzkomponenten  $Y_k$  in einem zu verarbeitenden Satz in einer N-Punkt-IDFT lautet der

$$Y_k = \sum_{n=-N_{kl}}^{N_{ku}} X_{C_0+k+N\times n} \Big|_{0 \leq k < N}$$

wobei  $C_0$  die Anzahl der Zentrumsfrequenzpunkte in den Eingangsdaten und  $N_{ku}$  und  $N_{kl}$  die Anzahl der Frequenzkomponenten ist, die zu dem Ausgangskorb mit Index  $k$  addiert werden, die entsprechend von über oder unter  $C_0$  herrühren.

**[0048]** [Fig. 7](#) stellt den auf einen De-Kanalisiere angewendeten, modifizierten, schnellen Faltungsalgorithmus entsprechend einem exemplarischen Ausführungsbeispiel der vorliegenden Erfindung dar. Ähnlich der oben vorgestellten Beschreibung und mit Hinblick auf [Fig. 2B](#) enthält der auf den De-Kanalisiere angewandte, modifizierte, schnelle Faltungsalgorithmus der vorliegenden, in [Fig. 7](#) vorgestellten Erfindung einen  $\eta\%$ -Überlappungsblockgenerator **704**, eine schmale  $N_{DFT}$ -Punkt-DFT **706**, einen Multiplizierer **708** zur Multiplikation der Körbe mit Frequenzfilterkoeffizienten **712**, einen Einführungskorbblock **714**, eine größere  $N_{IDFT}$ -Punkt-IDFT **716** und einen  $\eta\%$ -Überlappungsblockmischer **724**, der in ähnlicher Weise wie der vorangehend Beschriebene arbeitet. Darüber hinaus enthält das System entsprechend des vorliegenden Ausführungsbeispiels eine Entfaltungseinheit **730**, welche den erfinderischen Entfaltungsprozess ausführt.

**[0049]** Die Entfaltungseinheit **730** expandiert den Satz der Frequenzkomponentenausgänge der DFT **706** durch Addieren übersetzter Originalkomponenten außerhalb des Originalsatzes. Das Konzept der Entfaltung ist in [Fig. 8](#) dargestellt. In [Fig. 8](#) wird ein 24-Punkte-Satz aus 16 Frequenzkomponenten, die von einer 16-Punkte-DFT kommen, gebildet. Wie dargestellt werden die vier am weitesten links stehenden Frequenzkomponenten des Originalsatzes zu den rechten der am weitesten rechts stehenden Frequenzkomponenten des Originalsatzes hinzuaddiert, und die 4 am weitesten rechts stehenden Frequenzkomponenten des Originalsatzes werden zu den linken der am weitesten links stehenden Frequenzkomponenten des Originalsatzes hinzuaddiert. Im Ergebnis wird eine neue 24-Punkte-Frequenzantwort erzeugt. Diese neue 24-Punkte-Frequenzantwort wird dann mit einer 24-Punkte-Frequenzantwort (das heißt, 24 Frequenzfilterkoeffizienten) ohne die Notwendigkeit, eine größere DFT-Bearbeitung ausführen

zu müssen, multipliziert.

**[0050]** Die Bildung des 24-Punkte-Satzes in [Fig. 8](#) kann geschrieben werden als

$$Y_{4-19} = X_{0-15}$$

$$Y_{0-3} = X_{12-15}$$

$$Y_{20-23} = X_{0-3},$$

wobei  $X_k$  die Eingangskomponenten bezeichnen und  $Y_k$  die Ausgangskomponenten bezeichnen.

**[0051]** [Fig. 9](#) stellt die Platzierung des Entfaltungsprozesses innerhalb des in [Fig. 7](#) dargestellten, modifizierten, schnellen Faltungsalgorithmus dar. Der Entfaltungsprozess wird nach dem DFT-Verarbeitungsschritt, und bevor die Daten mit den Frequenzfilterkoeffizienten multipliziert werden, ausgeführt. Wie man aus [Fig. 9](#) erkennt, sind die 4 Frequenzkomponenten der exemplarischen DFT-Ergebnisse mit C, B, A und D gekennzeichnet. Die Entfaltungseinheit addiert die Komponenten C und D außerhalb des Originalsatzes der Komponenten um einen Sechs-Komponentensatz (D, C, B, A, D und C) zum bilden.

**[0052]** Der Prozess der Entfaltung kann auch zu höheren Ordnungen erweitert werden, so dass die kleine Anzahl von DFT-Frequenzkomponenten, die der Frequenzantwortmultiplikation zugeführt werden, mehrmals benutzt werden.

**[0053]** Die allgemeine Formel zur Entfaltung inklusive der Entfaltung höhere Ordnung ist unten angegeben. Für die Ausgangsfrequenzkomponenten  $Y_{C_0+k+N\times n}$ , die durch die Entfaltung der Komponenten einer N-Punkt-DFT gebildet werden, lautet der Ausdruck

$$Y_{C_0+k+N\times n} = X_k \Big|_{\begin{array}{l} -N_{kl} \leq n \leq N_{ku} \\ 0 \leq k < N \end{array}}$$

wobei  $C_0$  die Anzahl der Zentrumsfrequenzpunkte in den Ausgangsdaten ist und  $N_{ku}$  und  $N_{kl}$  jeweils die Anzahl der Frequenzkomponenten ist, die aus den Eingangskomponenten mit Index  $k$  entsprechend oberhalb oder unterhalb von  $C_0$  eingefügt werden.

**[0054]** Wie oben dargestellt, ist es möglich, den DFT-Ausgang durch Ausführung einer Frequenzbereichsfaltung in einem Empfänger mit einer Filterantwort multipliziert zu erhalten, die breit genug ist, um Breitband-Aliasing zu verhindern, und das Ergebnis dieser Verarbeitung in die kleinstmögliche IDFT ohne die Einführung von Aliasing von dem nächsten, benachbarten Kanal gefaltet zu bekommen. Wenn man das Konzept der Frequenzbereichsentfaltung in ei-

nem Sender nutzt, ist es möglich, einen DFT-Ausgang zu erhalten, welcher kleiner ist als die Filterantwort, um diesen dann vor der Multiplikation mit der Frequenzantwort auf die notwendige Breite zu expandieren.

**[0055]** Frequenzbereichsfaltung und -entfaltung erhöhen die Flexibilität durch Entfernen von Restriktionen in den Frequenzbereichsfaltern und auch durch die Entkopplung der Filteranforderungen von den DFT/IDFT-Länge. Faltung/Entfaltung kann genutzt werden, um korrekte Abtastraten zu erhalten, die von Veränderungen in Filterbandbreiten oder Stoppbandunterdrückung unabhängig sind.

**[0056]** Faltung und Entfaltung reduziert die Anzahl der Verarbeitungsschritte pro Sekunde, die für die kanalspezifischen Anteile in dem modifizierten, schnellen Faltungsalgorithmus ausgeführt werden müssen, in dem Frequenzbereich signifikant. Sie reduzieren auch die Speicheranforderungen. Weil die Anzahl der Verarbeitungsschritte pro Kanal abnimmt, können mehr Kanäle von dem gleichen Chip behandelt werden. Im Ergebnis wird eine prozessorbasierte Architektur einfacher möglich.

**[0057]** Die vorliegende Erfindung ist auf alle Arten von schnellen Faltungsalgorithmen anwendbar, bei denen eine Änderung der Abtastrate vorkommt und insbesondere dort, wo es sehr starke Stoppbandanforderungen gibt. Die relative, durch die vorliegende Erfindung gegebene Reduktion der Anzahl der Verarbeitungsschritte hängt teilweise von der Gesamtanzahl der Verarbeitungsschritte, die für die DFT/IDFT notwendig sind, ab. Durch Reduktion der IDFT-Größe von 32 auf 16 Punkte wird die Anzahl der notwendigen Multiplikationsschritte von 88 auf 24 reduziert, wenn die IDFT durch eine IFFT mit der Basiszahl 2 durchgeführt wird. Diese Reduktion um den Faktor 3,7 Mal reflektiert einen entsprechenden Rückgang in der Leistungsaufnahme. Die Anzahl der arithmetischen Operationen (Additionen plus Multiplikationen) geht von 496 auf 176 zurück – ein 2,8-facher Rückgang.

**[0058]** Fig. 10 stellt einen Vergleich der Berechnungskomplexität in Millionen Verarbeitungsschritten pro Sekunde (ohne die Speicheroperationen) zwischen einem Algorithmus nach dem Stand der Technik und dem Faltungsalgorithmus der vorliegenden Erfindung dar. Der Vergleich wurde bei einer Abtastfrequenz von 66,44 MHz und einer gesamten Dezimierung von 512x durchgeführt. Man erkennt aus der Figur, dass der Faltungsalgorithmus der vorliegenden Erfindung eine größere Anzahl von zu verarbeitenden Kanälen als ein Algorithmus nach dem Stand der Technik erlaubt.

**[0059]** Das Vorangegangene hat die Prinzipien, bevorzugten Ausführungsbeispiele und Betriebsarten

der vorliegenden Erfindung beschrieben. Trotzdem sollte die Erfindung nicht auf die bestimmten, oben diskutierten Ausführungsbeispiele beschränkt ausgelegt werden. Deshalb sollten die oben beschriebenen Ausführungsbeispiele als Illustration und nicht einschränkend angesehen werden, und es ist selbstverständlich, dass Varianten dieser Ausführungsbeispiele von einem Fachmann ausgeführt werden können, ohne über den Umfang der vorliegenden Erfindung, wie er durch die folgenden Ansprüche definiert ist, hinauszugehen.

## Patentansprüche

1. System zur Verbesserung eines modifizierten schnellen Faltungsalgorithmus, der auf einem Kanalisierer Anwendung findet,

mit einem  $\eta\%$ -Überlappungsblockgenerator (310) (overlap block generator) zur Konvertierung eines empfangenen Datenstromes in Blöcke;

Mitteln (330) zur Ausführung einer  $N_{DFT}$ -Punkt-Diskreten-Fourier-Transformation (DFT) auf die Blöcke, um Frequenzkomponenten zu bilden;

Mitteln (340) zur Auswahl von Frequenzkomponenten;

einem Multiplizier (350) zur Multiplikation der Frequenzkomponenten mit Frequenzfilterkoeffizienten;

Mitteln (390) zur Faltung der multiplizierten Frequenzkomponenten in eine kleinere Anzahl von Frequenzkomponenten, wobei die Mittel (390) zur Faltung äußere Frequenzkomponenten zu inneren Frequenzkomponenten addiert, um die kleinere Anzahl von Komponenten zu erhalten;

Mitteln (370) zur Ausführung einer  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation (IDFT) auf gefaltete Frequenzkomponenten zur Bildung gefilterter Datenblöcke; und

einem  $\eta\%$ -Überlappungsblockmischer (380) (overlap block combiner), dem die Ausgänge der Mittel (370) zur Ausführung einer  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation (IDFT) zugeleitet werden, um die gefilterten Datenblöcke in einen kontinuierlichen Datenstrom zu konvertieren.

2. System nach Anspruch 1, bei dem die Mittel zur Faltung zwischen dem Multiplizierer und den Mitteln zur Ausführung der  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation angeordnet sind.

3. System nach Anspruch 1, wobei die Mittel zur Faltung eine Faltung höherer Ordnung ausführen, bei der drei oder mehr Frequenzkomponenten zur Bildung einer Eingangskomponente für die IDFT addiert werden.

4. Verfahren zur Verbesserung eines modifizierten schnellen Faltungsalgorithmus, der auf einem Kanalisierer Anwendung findet, mit den Schritten Konvertierung eines empfangenen Datenstromes in Blöcke durch einen  $\eta\%$ -Überlappungsblockgenerator

(310);

Verarbeitung der Datenblöcke mit einer  $N_{DFT}$ -Punkt-Diskreten-Fourier-Transformation (DFT) (330) zur Bildung von Frequenzkomponenten;

Auswahl (340) von Frequenzkomponenten;

Multiplikation (350) der ausgewählten Frequenzkomponenten mit Frequenzfilterkoeffizienten (360);

Faltung der multiplizierten Frequenzkomponenten in eine kleinere Anzahl von Frequenzkomponenten, wobei der Faltungsschritt einen Schritt zur Addition von äußeren Frequenzkomponenten zu inneren Frequenzkomponenten enthält, um die kleinere Anzahl an Komponenten zu bilden;

Ausführung einer  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation (IDFT) (370) auf die gefalteten Frequenzkomponenten zur Bildung gefilterter Datenblöcke; und

Mischen der gefilterten Datenblöcke in einen kontinuierlichen Datenstrom durch einen  $\eta\%$ -Überlappungsblockmischer (380).

5. Verfahren nach Anspruch 4, bei dem der Schritt des Faltens ein Schritt einer Faltung höherer Ordnung ist, bei der drei oder vier Frequenzkomponenten zur Bildung einer Eingangskomponente der IDFT addiert werden.

6. System zur Verbesserung eines modifizierten schnellen Faltungsalgorithmus, der auf einem Entkanalisierten Anwendung findet, mit einem  $\eta\%$ -Überlappungsblockgenerator (704) zur Konvertierung eines Datenstromes in Blöcke;

Mitteln (706) zur Ausführung einer  $N_{DFT}$ -Punkt-Diskreten-Fourier-Transformation auf die Blöcke zur Bildung eines ursprünglichen Satzes von Frequenzkomponenten;

Mitteln (730) zur Entfaltung des ursprünglichen Satzes von Frequenzkomponenten zur Bildung einer größeren Anzahl von Frequenzkomponenten, wobei die Mittel zur Entfaltung eine kleinere Anzahl von Frequenzkomponenten auf eine größere Anzahl von Frequenzkomponenten durch Addition der ursprünglichen Komponenten außerhalb des Originalsatzes erweitert;

einem Multiplizierer (708) zur Multiplikation der größeren Anzahl von Frequenzkomponenten mit Frequenzfilterkoeffizienten (712);

Mitteln (714) zum Einfügen der multiplizierten Frequenzkomponenten in eine  $N_{IDFT}$ -Punkt-Inverse-Diskrete-Fourier-Transformation;

Mitteln (716) zur Ausführung der  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation auf die eingefügten Frequenzkomponenten zur Bildung von gefilterten Datenblöcken, und

einem  $\eta\%$ -Überlappungsblockmischer (724), welcher durch die Ausgaben der eingefügten Frequenzkomponenten zur Bildung gefilterter Datenblöcke gespeist wird, um die gefilterten Datenblöcke in einen kontinuierlichen Datenstrom zu konvertieren.

7. System nach Anspruch 6, bei dem die Mittel zur Entfaltung eine Entfaltung höherer Ordnung durchführen, bei der die größere Anzahl mehr als zweimal die kleinere Anzahl ist.

8. Verfahren zur Verbesserung eines modifizierten schnellen Faltungsalgorithmus, der auf einem Entkanalisierten Anwendung findet, mit den Schritten Konvertierung eines empfangenen Datenstromes in Blöcke durch einen  $\eta\%$ -Überlappungsblockgenerator (704);

Ausführung einer  $N_{DFT}$ -Punkt-Diskreten-Fourier-Transformation (DFT) (706) auf überlappende Datenblöcke zur Bildung eines ursprünglichen Satzes von Frequenzkomponenten;

Entfaltung des ursprünglichen Satzes von Frequenzkomponenten, um eine größere Anzahl von Frequenzkomponenten zu bilden, wobei der Schritt des Entfaltens eine kleinere Anzahl von Frequenzkomponenten auf eine größere Anzahl von Frequenzkomponenten durch Addition von ursprünglichen Komponenten außerhalb des Originalsatzes erweitert; Multiplikation (708) der größeren Anzahl der Frequenzkomponenten mit Frequenzfilterkoeffizienten (712);

Einfügen (714) der multiplizierten Frequenzkomponenten in eine  $N_{IDFT}$ -Punkt-Inverse-Diskrete-Fourier-Transformation (716);

Ausführen einer  $N_{IDFT}$ -Punkt-Inversen-Diskreten-Fourier-Transformation (716) auf die eingefügten Frequenzkomponenten zur Bildung gefilterter Datenblöcke; und

Mischen der Datenblöcke in einen kontinuierlichen Datenstrom durch einen  $\eta\%$ -Überlappungsblockgenerator (724).

9. Verfahren nach Anspruch 8, bei dem der Schritt der Entfaltung eine Entfaltung höherer Ordnung ist, bei der die größere Anzahl mehr als zweimal der kleineren Anzahl ist.

Es folgen 10 Blatt Zeichnungen

FIG. 1

FIG. 2A

FIG. 2B

FIG. 3

**FIG. 4**

**FIG. 6**

FIG. 5

FIG. 7

FIG. 8

FIG. 9

**FIG. 10**