**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>6</sup>

G11C 16/06

(11) 공개번호 특1998-0011502

(43) 공개일자 1998년04월30일

---

|            |                                                                                    |

|------------|------------------------------------------------------------------------------------|

| (21) 출원번호  | 특1997-0030562                                                                      |

| (22) 출원일자  | 1997년07월02일                                                                        |

| (30) 우선권주장 | 96-180859 1996년07월10일 일본(JP)                                                       |

| (71) 출원인   | 히다치세사쿠쇼 주식회사 가나이 츠토무<br>일본국 도쿄도 지요다구 간다 스루가다이 4-6 히다치초엘에스아이 엔지니어링<br>주식회사 스즈키 진이치로 |

| (72) 발명자   | 일본국 도쿄도 고다이라시 죠스이촌쵸 5-20-1<br>요시다 게이이치<br>일본국 도쿄도 오우메시 노가미 657-5-206<br>구보노 쇼지     |

| (74) 대리인   | 일본국 도쿄도 아키시마시 미호리쵸 5-5-7<br>백남기                                                    |

---

**심사청구 : 없음**

**(54) 불휘발성 반도체 기억장치 및 라이트방법**

**요약**

반도체 기억장치 또는 불휘발성 반도체 기억장치에 있어서의 다진(多值) 정보의 기억방식에 적용해서 특히 유효한 기술에 관한 것으로서, 워드선 디스터브에 의한 메모리셀의 임계값의 변동을 최소로 억제할 수 있는 불휘발성 반도체기억장치를 제공하기 위해, 플래시 메모리는 컨트롤게이트 및 플로팅게이트를 갖는 불휘발성 기억장치를 메모리셀에 사용하고 있고 1개의 트랜지스터로 메모리셀이 이루어지는 구성으로 하였다. 이렇게 하는 것에 의해, 워드선 디스터브에 의한 메모리셀의 임계값이 변동을 최소로 억제하는 것이 가능하게 됨과 동시에 라이트시의 피크전류와 평균소비전력을 저감할 수 있는 휘발성 반도체 기억장치를 실현할 수 있다는 효과가 얻어진다.

**대표도**

**도1**

**명세서**

**도면의 간단한 설명**

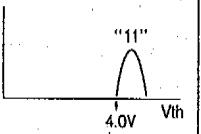

제1도는 본 발명에 관한 다진 플래시 메모리의 데이터 라이트방법의 개략을 도시한 설명도.

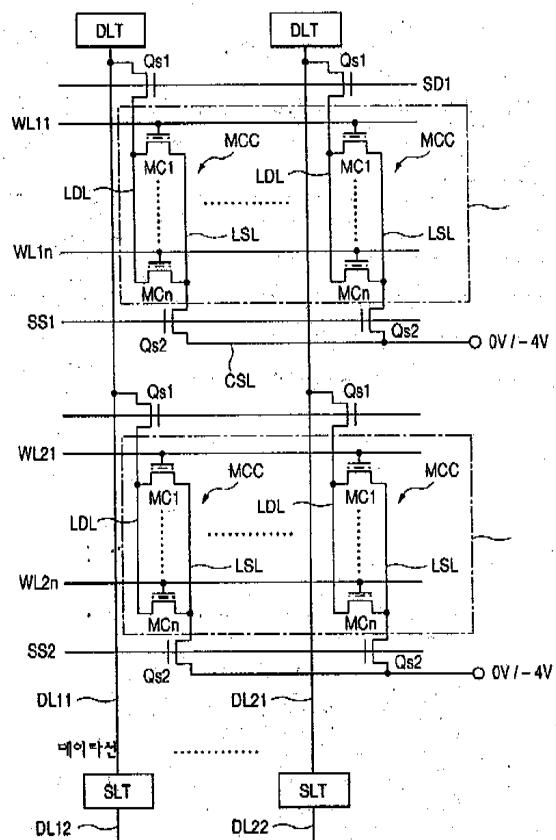

제2도는 본 발명에 관한 다진 플래시 메모리의 메모리 어레이의 구성예를 도시한 회로도.

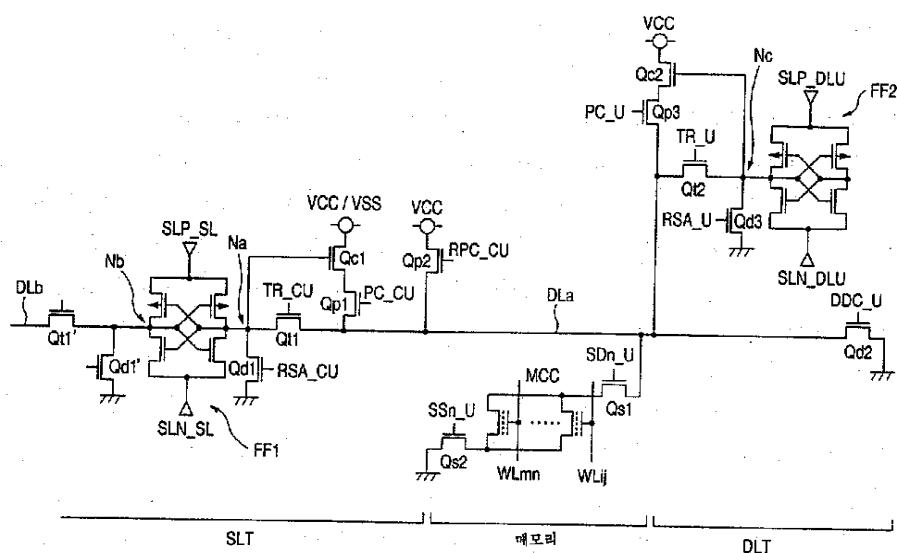

제3도는 센스 래치회로SLT 및 데이터 래치회DLT의 구체예를 도시한 회로도.

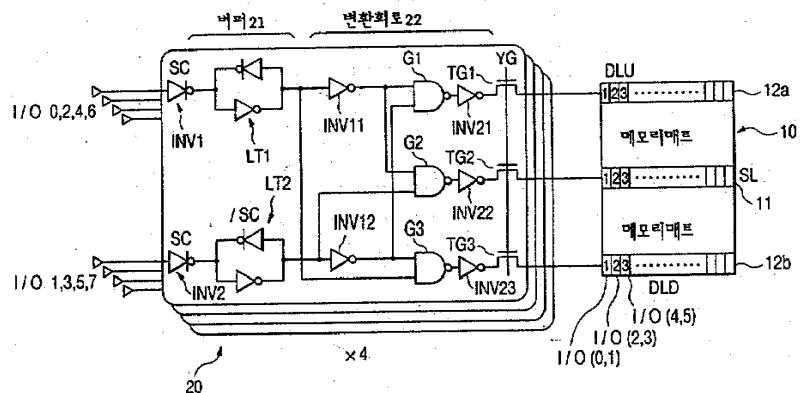

제4도는 본 발명에 관한 다진 플래시 메모리에 있어서의 2비트의 라이트 데이터를 4진의 데이터로 변환하는 데이터 변환회로의 1실시예를 도시한 논리회로도.

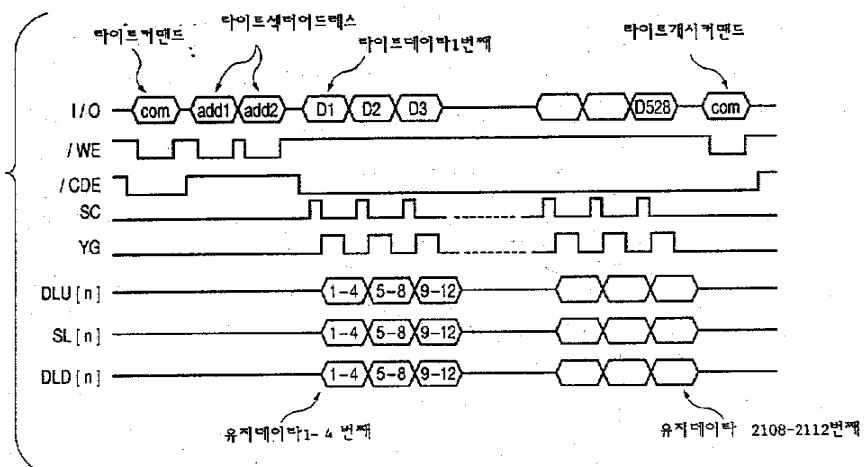

제5도는 실시예의 다진 플래시 메모리의 라이트시의 데이터 입력타이밍을 도시한 타이밍도.

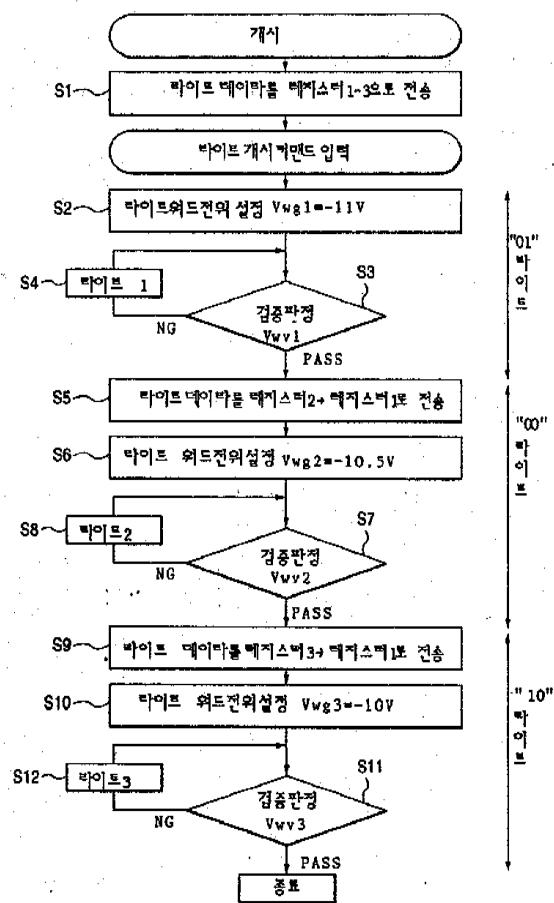

제6도는 실시예의 다진 플래시 메모리의 라이트 수순을 도시한 흐름도.

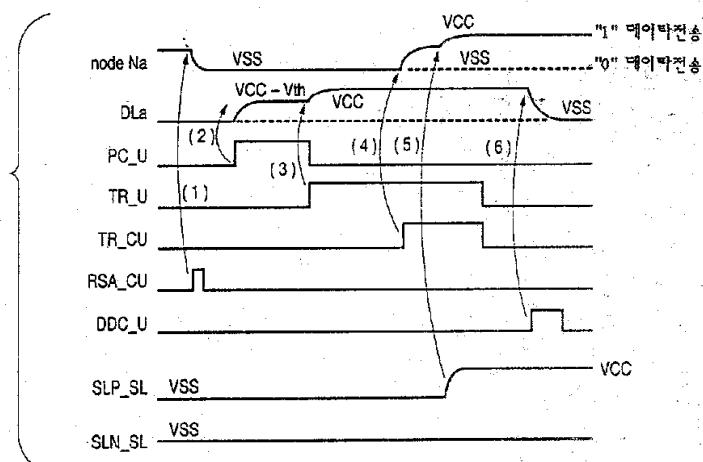

제7도는 데이터 래치회로DLT에서 센스 래치회로SLT의 데이터 전송시의 신호타이밍을 도시한 타이밍도.

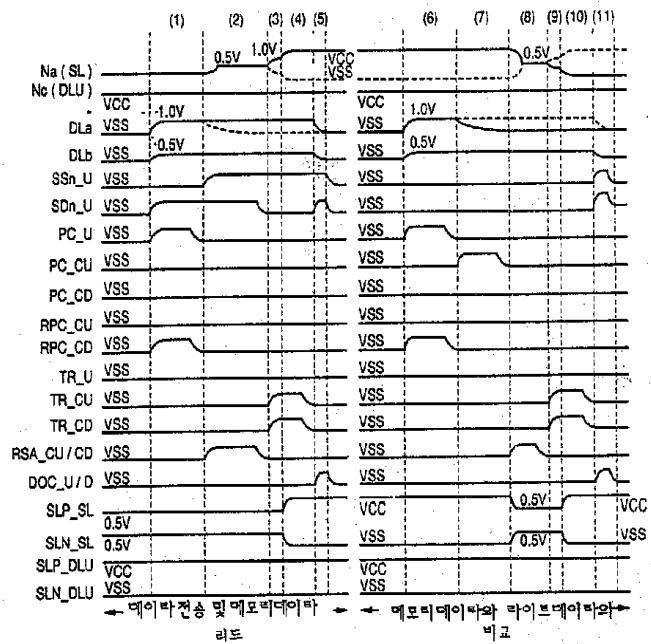

제8도는 불규칙 비트의 검출의 구체적 수순의 타이밍을 도시한 타이밍도.

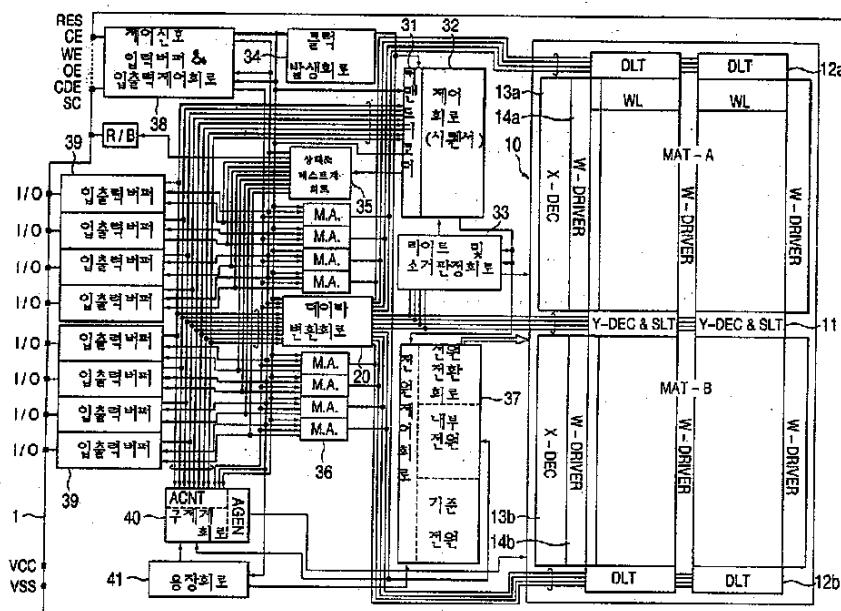

제9도는 본 발명에 관한 다진 플래시 메모리의 1실시예의 개략을 도시한 전체 블럭도.

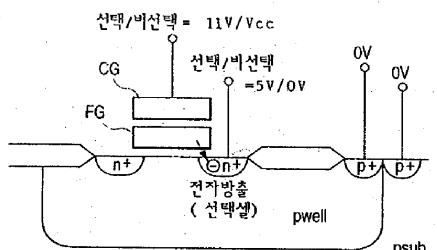

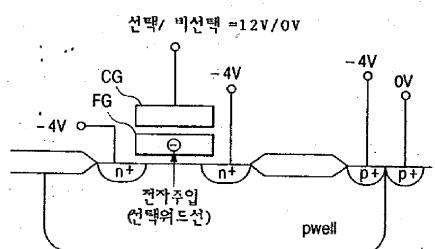

제10도는 실시예의 플래시 메모리에 사용되는 메모리셀의 구조 및 데이터라이트시의 전압상태를 도시한 모식도.

제11도는 실시예의 플래시 메모리에 사용되는 메모리셀의 소거시의 전압상태를 도시한 모식도.

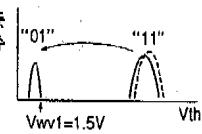

제12도는 선출원 발명에 관한 다진 플래시 메모리에 있어서의 데이터 라이트방법의 개략을 도시한 설명도.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은 반도체 기억장치 또는 불휘발성 반도체 기억장치에 있어서의 다진 정보의 기억방식에 적용해서 특히 유효한 기술에 관한 것으로서, 예를 들면 여러개의 기억정보를 전기적으로 일괄 소거할 수 있는 불휘발성 기억장치(이하, 간단히 플래시 메모리라고 한다)에 이용해서 유효한 기술에 관한 것이다.

플래시 메모리는 컨트롤게이트 및 플로팅게이트를 갖는 불휘발성 기억장치를 메모리셀에 사용하고 있고, 1개의 트랜지스터로 메모리셀을 구성할 수 있다.

이러한 플래시 메모리에 있어서는 라이트동작에서는 도10에 도시한 바와 같이 불휘발성 기억소자의 드레인영역을 예를 들면 5V(볼트)정도로 하고 컨트롤게이트CG가 접속된 워드선을 -11V정도로 하는 것에 의해, 터널전류에 의해 플로팅 게이트FG에서 전하를 인출해서 임계값 전압을 낮은 상태(논리 0)로 한다. 소거동작에서는 도11에 도시하는 바와 같이 웰영역, 드레인영역, 소오스영역을 -4V정도로 하고, 컨트롤케이트CG를 12V와 같은 고전압으로 해서 터널전류를 발생시켜 플로팅게이트FG에 부전하를 주입해서 임계값을 높은 상태(논리 1)로 한다.

이것에 의해 1개의 메모리셀에 1비트의 데이터를 기억시키도록 하고 있다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 기억용량을 증대시키기 위해 1메모리셀중에 2비트 이상의 데이터를 기억시키는 소위 「다진」 메모리의 개념이 제안되어 있다. 이 다진 메모리에 관한 발명으로서는 PCT/JP95/02260등이 있다.

상기 선출원의 다진 메모리에 있어서는 3단계의 라이트를 도12에 도시한 바와 같이, 소거레벨(임계값 약 5V)을 기점으로 해서 소거레벨에 가까운 임계값의 메모리셀로의 라이트부터 개시해서 순차 임계값이면 메모리셀로의 라이트를 실행하도록 하고 있었다. 이것은 다진 데이터의 라이트 시간을 짧게 하기 위함이다. 그러나, 플래시 메모리에서는 라이트 동작에 있어서 선택된 메모리셀과 공통 워드선에 결합되는 비선택의 메모리셀의 컨트롤게이트에도 높은 전압이 인가된다. 따라서 비선택의 메모리셀은 약한 라이트(디스터브 : disturbed)상태로 되고, 임계값 전압이 변동해서 기억데이터가 변화해 버릴 우려가 있다는 것이 알려져 있다. 이것을 워드선 디스터브라고 한다.

또한, 본 발명자들은 상기 워드선 디스터브에 의한 임계값의 변동은 소거레벨과 먼 임계값의 메모리셀보다 임계값이 가까운 메모리셀 쪽이 영향을 받기 쉽다는 특징이 있다는 것을 발견하였다. 이것은 메모리칩을 제조했을 때의 초기 임계값이 소거레벨보다 훨씬 낮고, 메모리셀은 디스터브가 걸리면 상기 초기 임계값으로 되돌아 가려는 성질이 있기 때문이라 고려된다.

그러나, 상기 선출원의 라이트방식에서는 소거레벨에 가까운 임계값의 메모리셀에서 임계값이 먼 메모리셀로 순차 라이트를 실행하도록 하고 있었으므로, 워드선 디스터브에 의한 임계값의 변동이 크다는 문제점이 있다는 것이 명확하게 되었다. 즉, 종래의 라이트방식에서는 도12에 도시한 바와 같이 소거레벨과 가장 먼 임계값(1.5V보다 낮은 임계값)의 메모리셀(데이터 1)을 고려하면, 이 메모리셀에는 한번도 워드선 디스터브가 걸리지 않는데 반해, 디스터브의 영향을 가장 받기 쉬운 소거레벨에 가장 가까운 임계값(약 3.2V)의 메모리셀(데이터 10)에는 평균 2회의 워드선 디스터브가 걸리게 된다는 문제가 있다.

또, 상기 선출원의 라이트방식에서는 제1단계의 라이트시에 임계값을 어긋나게 하고자 하는 모든 메모리셀에 대해서 라이트펄스를 인가하기 때문에, 라이트시 피크전류가 증대함과 동시에 평균소비전력도 많아진다는 문제가 있다는 것이 명확하게 되었다.

본 발명의 목적은 워드선 디스터브에 의한 메모리셀의 임계값의 변동을 최소로 억제할 수 있는 다진 기억형 불휘발성 반도체 기억장치를 제공하는 것이다.

본 발명의 다른 목적은 라이트시의 피크전류와 평균소비전력을 저감할 수 있는 불휘발성 반도체 기억장치를 제공하는 것이다.

본 발명의 상기 및 그 밖의 목적과 새로운 특징은 본 명세서의 기술 및 첨부도면에서 명확하게 될 것이다.

#### 발명의 구성 및 작용

본원에 있어서 개시되는 발명 중 대표적인 것의 개요를 간단히 설명하면 다음과 같다.

즉, 여러개의 임계값을 설정해서 1개의 메모리셀에 다진의 정보를 기억시키도록 한 불휘발성 반도체 기억장치에 있어서, 소거레벨에서 먼 임계값의 메모리셀로의 라이트부터 개시해서 순차 임계값이 가까운 메모리셀로의 라이트, 바꿔 말하면 소거레벨에서 라이트상태로서 가장 낮은 임계값 전압의 메모리셀로부터 라이트를 개시해서 순차 임계값 전압을 높게 하는 메모리셀로의 라이트를 실행하도록 한 것이다.

이것에 의해, 워드선 디스터브의 영향을 가장 받기 쉬운 소거레벨에 가까운 임계값의 메모리셀에 대해서 가해지는 워드선 디스터브의 회수를 감소시킬 수 있고 워드선 디스터브에 의한 임계값의 변동을 최소로 억제할 수 있다.

또, 상기 수단에 의해 1회의 라이트에 의해 프리차지하지 않으면 안되는 데이터선수와 라이트개시부터 종료할 때까지의 프리차지하지 않으면 안되는 데이터선의 총수를 종래 방식에 비해 적게 해서 라이트시의

피크전류와 평균소비전력을 저감할 수 있다.

### 실시예

이하, 본 발명을 1개의 메모리셀에 4진을 기억할 수 있는 플래시 메모리에 적용한 경우에 대해서 그 실시예를 도면을 사용해서 설명한다.

도 1은 본 실시예의 플래시 메모리의 데이터 라이트순서를 도시한 도면이다. 본 실시예에서는 라이트에 앞서 모든 메모리셀은 소거레벨의 임계값영역(임계값 4V이상, 기억데이터11)으로 한다. 다음에 도 1에 도시한 바와 같이, 소거레벨에서 가장 먼(낮은) 임계값영역(0V보다 높고 1.4V이하)의 메모리셀(기억데이터1)로의 라이트를 실행한다. 그 후, 소거레벨에서 두 번째로 먼(낮은) 임계값영역(1.6V이상 약 2.4V이하)의 메모리셀(기억데이터0)로의 라이트를 실행하고, 마지막으로 소거레벨에 가장 가깝고 라이트상태로서는 가장 높은 임계값 영역(2.6V이상 3.2V이하)의 메모리셀(기억데이터10)로의 라이트를 실행한다.

이것에 의해, 가장 워드선 디스터브의 영향을 받기 어려운 소거레벨에서 가장 먼 임계값 영역의 메모리셀(기억데이터1)에 대해서 가해지는 워드선 디스터브의 횟수는 2회로 되지만, 가장 워드선 디스터브의 영향을 받기 쉬운 소거레벨에 가장 가까운 임계값영역의 메모리셀(기억데이터10)에 대해서 가해지는 워드선 디스터브의 횟수는 0회로 감소시킬 수 있고, 도 12에 도시한 소거레벨에 가까운 측에서 라이트를 실행하는 방법에 비해서 워드선 디스터브에 의한 임계값의 변동을 작게 억제할 수 있다.

도 2에는 후술하는 도 9에 도시된 메모리 어레이(10)의 구체예를 도시한다. 이 실시예의 메모리 어레이(10)은 2개의 매트로 구성되어 있고, 도 2에는 그중 한쪽(상측)의 메모리매트의 구체예가 도시되어 있다. 동일 도면에 도시한 바와 같이 각 메모리매트는 구체예가 도시되어 있다. 동일 도면에 도시한 바와 같이 각 메모리매트는 열방향으로 배열되고 각각 소오스 및 드레인이 공통 접속된 병렬형태의 n개의 메모리셀(플로팅게이트를 갖는 MOSFET)MC1~MCn으로 이루어지는 메모리열 MCC가 행방향(워드선 WL방향) 및 열방향(데이터선 DL방향)으로 각각 여려개 배치되어 있다. 각 메모리열 MCC는 n개의 메모리셀MC1~MCn의 드레인 및 소오스가 각각 공통의 확산층에 의해 형성된 로컬드레인선 LDL 및 공통의 확산층에 의해 형성된 로컬소오스선LSL에 접속된다. 로컬드레인선LDL은 스위치 MOSFET Qs1을 거쳐서, 예를 들면 알루미늄과 같은 금속배선으로 이루어지는 데이터선DL에, 또 로컬소오스선LSL은 스위치 MOSFET Qs2를 거쳐서 역시 알루미늄과 같은 금속배선으로 이루어지는 공통소오스선CSL에 접지전위 또는 부전압이 공급되는 구성으로 되어 있다.

상기 여러개의 메모리열MCC 중 워드선방향으로 배치되어 있는 것은 반도체 기판상의 동일한 웰영역 WELL 내에 형성하고, 데이터 소거시에는 그 웰영역 WELL에 -4V와 같은 부전압을 인가하고, 웰영역을 공통으로 하는 워드선에 12V와 같은 전압을 인가하는 것에 의해 일괄 소거가 가능하게 되어 있다. 또한, 데이터 소거시에는 웰영역을 공통으로 하는 모든 스위치MOSFET Qs1, Qs2가 온상태로 되어 각 메모리셀의 소오스 및 드레인에 -4V의 부전압이 인가되도록 구성되어 있다.

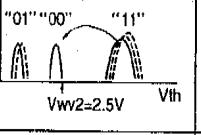

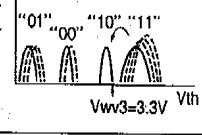

한편, 데이터 라이트시에는 선택되는 메모리셀이 접속된 워드선에 -11V와 같이 부전압이 인가됨과 동시에, 선택되는 메모리셀에 대응한 데이터선DL이 5V와 같은 전위로 되고 또한 선택메모리셀이 접속된 로컬드레인선LDL상의 스위치 MOSFET Qs1이 온상태로 되고 드레인에 5V가 인가된다. 단, 이때 로컬소오스선LSL상의 스위치 MOSFET Qs2는 오프상태로 되어 있다. 또, 데이터 리드시에는 선택되는 메모리 셀이 접속된 워드선에 1.5V, 2.5V, 3.3V와 같은 전압이 인가됨과 동시에, 선택되는 메모리셀에 대응한 데이터선DL이 1V와 같은 전위로 프리차지되고, 또한 선택메모리셀이 접속된 로컬드레인선LDL상의 스위치MOSFET Qs1이 온상태로 된다. 그리고, 이 때 로컬소오스선LSL상의 스위치 MOSFET Qs2는 온상태로 되고 접지전위 0V가 인가된다.

상기 데이터선DL의 한쪽끝(메모리 어레이의 중앙측)에는 리드시에 데이터선의 레벨을 검출함과 동시에 라이트시에 라이트 데이터로 따른 전위를 인가하는 센스 래치회로SLT가 각각 접속되고, 데이터선DL이 다른 쪽끝에는 라이트 데이터 및 리드 데이터를 유지하는 데이터 래치회로DLT가 각각 접속되어 있다.

이 실시예의 메모리 어레이에는 2개의 매트로 구성되어 있으므로, 센스 래치회로SLT의 반대측 즉 도면의 하측에도 상기와 마찬가지의 메모리매트가 배치되어 있고, 그 메모리 어레이내의 각 데이터선DL이 대응하는 센스 래치회로SLT의 다른쪽의 입출력단자에 접속되어 있다.

도 3에는 상기 센스 래치회로SLT 및 데이터 래치회로DLT의 구체적 회로예를 도시한다. 회로는 센스래치회로를 사이에 두고 대칭이므로, 한쪽의 메모리매트내의 1개의 데이터선에 대해서만 도시함과 동시에 편의상 데이터선에 접속되어 있는 메모리열 중 1개의 메모리열MCC만 도시했지만, 실제로는 여러개의 메모리열MCC가 접속되는 것이다. 도시한 바와 같이, 센스 래치회로SLT는 P채널 MOSFET와 N채널 MOSFET로 이루어지는 2개의 CMOS인버터의 입출력단자가 교차결합된 플립플롭회로 FF1를 구비하고 있다. 그리고, 상기 센스 래치회로SLT의 한쪽의 입출력노드Na에 한쪽의 메모리매트내의 데이터선DLa가 데이터 전송 MOSFET Qt1을 거쳐서 접속되어 있다. 또, 센스 래치회로SLT의 다른쪽의 입출력노드Nb에는 다른쪽의 메모리매트내의 데이터선DLb가 데이터 전송 MOSFET Qt1를 거쳐서 접속되어 있다.

또, 상기 센스 래치회로SLT의 입출력노드Na, Nb에는 각각 디스차지용 MOSFET Qd1, Qd1'접속되고, 데이터선DLa의 다른쪽끝에도 디스차지용 MOSFET Qd2가 접속되어 있다. 또, 각 데이터선DL에는 디스차지용MOSFET Qp1, Qp2가 접속되고, 이 중 Qp1은 MOSFET Qc1을 거쳐서 전압전압Vcc 또는 접지전압Vss가 공급되는 단자에 접속되어 있다. 또한, 이 센스 래치회로SLT의 입출력노드, Na, Nb에는 도시하지 않은 공통입출력선을 거쳐서 후술하는 데이터 변환회로에서 라이트 데이터가 입력가능하게 되어 있다.

한편, 상기 데이터 래치회로DLT는 센스 래치회로SLT와 마찬가지로 P채널MOSFET와 N채널 MOSFET로 이루어지는 2개의 CMOS인버터의 입출력단자가 교차결합된 플립플롭회로FF2를 구비하고 있다. 그리고, 상기 데이터 래치회로DLT의 한쪽의 입출력노드Nc에 메모리매트내의 데이터선DLa가 데이터 전송 MOSFET Qt2를 거쳐서 접속되어 있다. 또, 데이터 래치회로DLT의 입출력노드Nc에는 디스차지용MOSFET Qd3이 접속되고, 데이터선DLa와 전원전압Vcc 사이에는 프리차지신호PC\_U 및 상기 입출력노드Nc의 전위에 딸 온, 오프되는 MOSFET Qc3 및 Qc2가 직렬형태로 접속되어 있다.

또, 데이터 래치회로SLT의 입출력노드Nc에는 도시하지 않은 공통입출력선을 거쳐서 후술하는 데이터 변환회로에서 라이트 데이터를 입력가능하게 되어 있다. 또, 도 3에는 도시되어 있지는 않지만 상기 센스래치회로SLT의 입출력노드 Nb에 접속된 데이터선DLb의 다른쪽끝에도 데이터 변환회로로부터의 라이트 데이터를 유지하는 플립플롭회로로 이루어지는 데이터 래치회로DLT가 배치되어 있다. 도 4는 외부에서 입력된 기억해야 할 데이터를 메모리셀에 기억되는 다진 데이터로 변환하는 변환회로(20) 및 이 변환회로(20)과 메모리 어레이(10)내의 센스 래치열(11) 및 데이터 래치열(11) 및 데이터 래치열(12a), (12b)와의 관계를 도시한 도면이다. 데이터 변환회로(20)은 입력버퍼부(21)과 데이터 변환부(22)로 이루어지고, 8비트의 데이터가 2비트씩 쌍으로서 병렬로 입력가능하게 되어 있다. 도 4에는 그 중 1조의 데이터 변환부(21)과 데이터 변환부(22)의 상세가 도시되어 있다. 이하, 그중 1조의 데이터 변환회로에 대해서 설명한다.

1조의 데이터 변환회로내의 입력버퍼부(21)은 2개의 클럭된 인버터 INV1, INV2 및 래치회로 LT1, LT2로 구성되고, 데이터 변환부(22)는 상기 각 조의 래치회로 LT1, LT2에 접속된 인버터 INV11, INV12, 이 2개의 인버터 INV11, INV12의 출력과상기 각 조의 래치회로 LT1, LT2의 출력을 입력신호로 하는 3개의 NAND 게이트회로 G1, G2, G3 이들 게이트회로의 출력을 반전하는 인버터 INV21, INV22, INV23 및 이들 인버터에 접속된 MOSFET로 이루어지는 전송게이트 TG1, TG2, TG3에 의해 구성되고, 입력된 2비트의 데이터를 3비트이 데이터로 변환하고 전체로서 3비트×4의 데이터를 출력한다.

표1에는 상기 데이터 변환회로(20)에 있어서의 데이터 변환예를 나타낸다.

[표 1]

| 라이트데이터 | I/O 0 | I/O 1 | DLU 「1」 | SL 「1」 | DLD 「1」 |

|--------|-------|-------|---------|--------|---------|

| 1      | 0     | 1     | 0       | 1      | 0       |

| 0      | 0     | 0     | 1       | 0      | 0       |

| 10     | 1     | 0     | 0       | 0      | 1       |

| 11     | 1     | 1     | 0       | 0      | 0       |

표1에 도시되어 있는 바와 같이, 라이트 데이터1은 3비트의 데이터10으로 변환되고, 라이트 데이터0은 3비트의 데이터100으로 변환되고, 라이트 데이터10은 3비트의 데이터 1로 변환되고, 라이트 데이터 11은 3비트의 데이터0으로 변환된다. 그리고, 변환 후 1에 상당하는 비트에 대응하는 메모리셀에만 라이트가 실행되고, 변환 후 0에 상당하는 비트에 대응하는 메모리셀에는 라이트가 실행되지 않게 된다.

상기 데이터 변환회로(20)에 처음으로 입력된 8비트의 라이트 데이터의 외부단자 I/O0, I/O1을 거쳐서 공급된 비트를 변환해서 얻어진 3비트의 데이터는 메모리 어레이(10)의 양끝(도면에서는 상부와 하부)에 배치되어 있는 데이터 래치열 (12a), (12b)와 메모리 어레이의 중앙에 배치되어 있는 센스 래치열(11)의 1번째의 래치회로(DLU1, SL1, DLD1)로 각각 전송되고 유지된다. 또, 외부단자I/O2, I/O3을 거쳐서 공급된 라이트 데이터의 비트를 변환해서 얻어진 3비트의 데이터는 메모리 어레이(10)의 양끝(도면에서는 상부와 하부)에 배치되어 있는 데이터 래치열(12a), (12b)와 메모리 어레이의 중앙에 배치되어 있는 센스 래치열(11)의 2번째의 래치회로(DLU2, SL2, DLD2)로 각각 전송되고 유지된다.

이하, 마찬가지로 외부단자 I/O4, I/O5를 거쳐서 공급된 라이트 데이터의 비트를 변환해서 얻어진 3비트의 데이터는 데이터 래치열 (12a), (12b)와 센스 래치열(11)의 3번째의 래치회로(DLU3, SL3, DLD3)로 각각 전송되고 유지된다. 외부단자 I/O6, I/O7을 거쳐서 공급된 라이트 데이터의 비트를 변환해서 얻어진 3비트의 데이터는 데이터 래치열 (12a), (12b)와 센스 래치열(11)의 4번째의 래치회로 각각 전송되고 유지된다. 다음에, 입력된 8비트의 라이트 데이터는 데이터 변환회로(20)에 의해 변환되어 데이터 래치회로(12a), (12b)와 센스 래치회로(11)의 5~8번째의 비트로 각각 전송되고 유지된다.

상기 동작을 반복해서 데이터 래치열(12a), (12b)와 센스 래치열(11)의 모든 래치회로에 데이터가 저장된 시점에서, 메모리 내부에 마련되어 있는 후술하는 제어회로가 라이트 시퀀스를 기동해서 처음으로 센스 래치열(11)에 유지되어 있는 데이터, 다음에 센스 래치열(12a)의 데이터, 그 후에 (12b)의 데이터 순으로 라이트를 실행한다. 또한, 제어회로는 외부의 CPU 등에서 입력되는 커맨드에 따라서 제어를 실행하도록 구성되어 있다.

도 5에는 데이터 라이트시의 타이밍이 도시되어 있다. 동일 도면에서 알 수 있는 바와 같이, 라이트시에는 지시하는 라이트 커맨드가 입력되고, 이어서 라이트되어야 할 메모리셀이 결합되는 워드선이 어드레스(섹터어드레스)add1, add2가 입력된다. 각각은 라이트 인에이블신호/WE의 하강과 동기해서 입력된다. 이때 커맨드와 어드레스의 식별은 동시에 입력되는 제어신호(커맨드 데이터 인에이블신호)/CDE에 의해 구별된다. 즉, /CDE가 로우레벨일 때는 커맨드 또는 데이터가 입력되어 있는 것을 의미하고, /CDE가 하이레벨일 때는 어드레스가 입력되어 있는 것을 의미한다. 어드레스 다음에 1섹터(1개의 워드선에 접속되어 있는 메모리셀)에 기록해야 할 처음의 8비트의 라이트 데이터D1이 입력되고, 클럭SC와 동기해서 상기 입력버퍼부(21)에 페치된다. 또, 데이터 변환회로(20)에 있어서의 데이터 변환 후에 게이트 제어신호 YG에 의해 상기 전송게이트TG1~TG3이 온으로 되어 3비트×4의 라이트 데이터가 데이터 래치열(12a), (12b)와 센스 래치열(11)로 순차 전송되고 유지된다. 그 후, 8비트단위로 입력되는 라이트 데이터D2,D3,...D528이 순차 데이터 변화되어 센스 래치열(11)과 데이터 래치열(12a), (12b)에 저장되어 간다. 1섹터분의 라이트 데이터의 전송이 종료하면 외부에서 라이트동작을 개시시키는 라이트 개시커맨드가 입력되어 페치되고 이 커맨드를 해독해서 상기 라이트 시퀀스를 실행하는 것에 의해 1섹터분의 데이터의 라이트가 동시에 실행된다.

메모리 어레이(10)에서는 상기 센스 래치열(11)과 데이터 래치열(12a), (12b)에 저장된 데이터가 “1”로 되어 있는 데이터선에 접속되어 있는 기억소자에 대해서 라이트동작 즉 라이트펄스의 인각가 실행되고 각 기억소자의 임계값이 도 1에 도시한 바와 같이 시프트되어 4진의 데이터를 1메모리셀에 라이트할 수 있다. 도 6에 라이트 제어수순을 도시한다.

도 6에 있어서 우선 라이트 커맨드, 라이트 섹터어드레스 및 라이트 데이터가 입력된 후 제1스텝S1(라이트 데이터를 래치1~3으로 전송)에서 상기 데이터 변환회로(20)에 의해 변환된 데이터가 센스 래치열(11)과 데이터 래치열(12a), (12b)로 데이터 전송되고, 제2스텝 S2 이후가 라이트개시 커맨드가 입력되는 것에 의해 개시되는 제어시컨스이다.

이 제어시컨스에서는 우선 처음으로 이미 페치되어 있는 라이트 어드레스를 디코드하는 것에 의해 선택된 워드선을 -11V와 같은 전위로 설정한다(스텝S2), 이것과 동시에 데이터선상의 전송MOSFET Qt1을 온시키고, 그 때 센스 래치열(11)에 유지되어 있는 데이터에 따라서 데이터가 “1”로 되어 있는 데이터선을 5V와 같은 전위로 설정해서 라이트를 실행시킨다. 다음에, 데이터선으로 1V와 같은 전위로 프리차지한 후 상기 선택워드선을 1.5V와 같은 전압으로 설정하고 검증리드를 실행한다. 이 때, 정상적으로 라이트가 종료한 메모리셀에서 센스래치열(11)에 리도된 데이터는 0으로 변화한다. 그래서, 센스 래치열(11)의 유지데이터가 모두 “0”으로 되어 있는지 아닌지를 판정한다(스텝S3), 그리고, 1개라도 “1”의 데이터가 남아 있는 경우에는 그 때 센스 래치열(11)에 유지되어 있는 데이터를 사용해서 라이트되어 있지 않은 메모리셀만 재차 라이트를 실행한다(스텝S4).

검증판정의 결과, 센스 래치열(11)의 데이터가 모두 0으로 된 경우에는 스텝S5로 진행해서 데이터 래치열(12a)에 유지되어 있는 데이터를 센스 래치열(11)로 전송한다. 그리고, 선택워드선을 이전회보다 약간 낮은 -10.5V와 같은 전위로 설정한다(스텝S6), 다음에, 센스 래치열(11)에 유지된 데이터에 따라서 라이트를 실행한 후 선택워드선을 2.5V와 같은 전압으로 설정하고 검증리드를 실행해서 센스 래치열(11)의 유지데이터가 모두 0으로 되어 있는지 아닌지를 판정한다(스텝S7). 그리고, 1개라도 1의 데이터가 남아 있는 경우에는 그 때 센스 래치열(11)에 유지되어 있는 데이터를 사용해서 라이트되어 있지 않은 메모리셀만 재차 라이트를 실행한다(스텝S8).

검증판정의 결과, 센스 래치열(11)의 데이터가 모두 0으로 된 경우에는 스텝S9로 진행해서 이번에는 데이터 래치열(12b)에 유지되어 있는 데이터를 센스 래치열(11)로 전송한다. 그리고, 선택워드선을 이전회보다 더 약간 낮은 -10V와 같은 전위로 설정한다(스텝S10). 다음에, 센스 래치열(11)에 유지된 데이터에 따라서 라이트를 실행한 후 선택워드선을 3.3V와 같은 전압으로 설정하고 검증리드를 실행해서 센스 래치열(11)의 유지데이터가 모두 0으로 되어 있는지 아닌지를 판정한다(스텝S11). 그리고, 1개라도 1의 데이터가 남아 있는 경우에는 그 때 센스 래치열(11)에 유지되어 있는 데이터를 사용해서 라이트되어 있지 않은 메모리셀만 재차 라이트를 실행한다(스텝S12).

이상의 수순에 의해, 소거레벨에서 메모리셀의 임계값은 라이트상태로서 가장 낮은 임계값영역으로 되고, 순차 임계값이 높은 메모리셀로의 라이트가 실행되어 라이트동작이 종료한다. 이것에 의해, 소거레벨에 가까운 임계값의 메모리셀(라이트상태로서 가장 높은 임계값영역에 있는 메모리셀)에 대해서 가해지는 워드선 디스터브의 회수를 감소시킬 수 있고, 워드선 디스터브에 의한 임계값의 변동을 최소로 억제할 수 있다. 또, 상기 실시예에서는 라이트 워드선 전압을 -11V, -10.5V, -10V와 같이 절대값을 서서히 작게 해가도록 하고 있으므로, 1회에 발생하는 디스터브의 양도 점차 작아져 임계값의 변동을 더욱 작게 할 수 있다. 단, 라이트 전압을 서서히 낮춰가는 대신에 라이트 펄스폭을 서서히 작게 해 가도록 해도 좋다. 또, 커맨드를 이용하지 않고 외부로부터의 제어신호에 따라서 어드레스, 데이터의 입력이나 데이터의 라이트 동작이 개시되어도 좋다.

다음에, 상기 스텝S5, S9에 있어서의 데이터 래치열(12a), (12b)에서 센스 래치열(11)로의 데이터전송의 구체적 방법을 도 3의 회로도 및 도 7의 타이밍도를 사용해서 설명한다.

[1] 우선 센스 래치회로SLT의 PMOS측의 전원전압을 Vss(접지전위)로 설정해서 센스 래치회로SLT를 비활성상태로 하고, 디스차지MOSFET Qd1의 게이트에 리세트펄스RSA\_CU를 인가해서 노드Na의 전하를 인출한다.

[2] 다음에, 데이터 래치회로DLT의 프리차지MOSFET Qp3의 게이트제어신호 PC\_U를 하이레벨로 해서 데이터 래치회로DLT의 유지데이터를 사용해서 데이터선DLa를 Vcc~Vth까지 프리차지시킨다.

[3] 데이터 래치회로DLT의 전송MOSFET Qt2의 게이트제어신호TR\_U를 하이레벨로 해서 데이터 래치회로DLT의 유지데이터를 사용해서 데이터선DLa를 또 Vcc까지 프리차지시킨다.

[4] 센스 래치회로SLT의 전송MOSFET Qt1의 게이트 제어신호TR\_CU를 하이레벨로 해서 데이터선DLa의 레벨을 노드Na로 전송한다.

[5] 센스 래치회로SLT의 PMOS측에 전원전압Vcc를 공급하고 센스 래치회로SLT를 활성상태로 해서 노드Na의 전위 즉 유지데이터를 확정시킨다.

[6] 다음에, 전송MOSFET Qt1의 게이트제어신호TR\_CU를 로우레벨로 해서 오프시킨 후, 데이터선DLa의 다른쪽끝의 디스차지MOSFET Qd2의 게이트제어신호DDC\_U를 하이레벨로 해서 데이터 래치회로DLa의 전위를 Vss까지 디스차지시킨다.

이상의 동작을 모든 데이터선에 대해서 동시에 실행하는 것에 의해, 데이터 래치열(12a), (12b)에서 센스 래치열(11)로의 데이터전송을 실행할 수 있다.

또, 상기 구성의 메모리 어레이에 있어서는 이하에 기술하는 방법에 의해 소위 불규칙비트의 검출이 가능하고, 본 실시예의 플래시 메모리에 있어서는 불규칙비트를 검출해서 그것을 보수하는 시컨스가 마련되어 있다. 여기에서, 불규칙비트라는 것은 그 원인은 명확하지 않지만 동일한 라이트펄스가 인가된 메모리셀 중에서 갑자기 임계값이 너무 낮아져 예상데이터의 라이트가 실행되어 버린 것을 가리킨다. 즉, 데이터0에 대응하는 임계값으로 되도록 라이트펄스를 인가하거나, 데이터10 대응하는 임계값으로 되도록 라이트펄스를 인가했음에도 불구하고, 임계값이 너무 낮아져 데이터1에 대응하는 임계값을 갖는 메모리셀이 발생하는 것이 경형적으로 알려져 있다.

그래서, 이 실시예에서는 데이터 “00” 및 데이터 “10”에 대응되는 메모리셀의 라이트를 실행할 때 그 라이트 데이터를 데이터 래치회로에 남겨두고 라이트 종료 후에 센스 래치회로에 데이터를 리드해서 데이터선상에서 비교를 실행하는 것에 의해 불규칙비트의 검출을 실행하도록 하고 있다. 그 구체적 수순을 도 3

및 도 8을 참조하면서 설명한다.

[1] 라이트 종료 후에 데이터 래치회로DLT에 유지되어 있는 라이트 데이터를 사용해서 데이터선 DLa를 선택적으로 1.0V와 같은 레벨로 프리차지한다. 즉, 데이터 “1”을 유지하고 있는 데이터 래치회로에 접속되어 있는 데이터선만을 프리차지한다. 또한, 이 때, 반대측 매트의 데이터선DLb는 0.5V로 프리차지한다.

[2] 라이트를 실행한 메모리셀이 접속되어 있는 워드선을 목표로 한 임계값보다 낮은 리드레벨로 설정해서 리드를 실행한다. 이 때, 정상적인 라이트가 실행된 메모리셀은 오프이므로 데이터선은 프리차지전위 까지이지만, 불규칙비트의 메모리셀은 온상태로 되므로 데이터선은 디스차지된다.

[3] 데이터선상의 전송MOSFET Qt1을 온해서 센스 래치회로SLT에 의해 데이터선의 레벨을 검출한다.

[4] 센스 래치회로SLT로 전원전압을 공급해서 검출한 데이터선 레벨을 증폭한다.

[5] 데이터선상의 디스차지용 MOSFET Qd2를 온해서 모든 데이터선을 디스차지한다.

[6] 데이터 래치회로DLT에 유지되어 있는 라이트 데이터를 사용해서 데이터선DLa를 재차 선택적으로 1.0V와 같은 레벨로 프리차지한다. 반대측 매트의 데이터선DLb는 0.5V로 프리차지한다.

[7] 센스 래치회로SLT에 유지되어 있는 데이터선을 사용해서 MOSFET Qc1을 선택적으로 온시킴과 동시에 전원단자를 Vss로 해서 데이터선DLa를 선택적으로 디스차지한다. 이 때, 데이터선상의 전송MOSFET Qt1은 오프상태이다. 이것에 의해, 정상적인 라이트가 이루어진 메모리셀이 접속된 데이터선은 디스차지되지만, 불규칙비트를 발생한 메모리셀이 접속된 데이터선은 디스차지되지 않는다.

[8] 센스 래치회로SLT의 전원전압을 차단하고 디스차지용MOSFET Qd1을 온해서 센스 래치회로 SLT를 리셋한다.

[9] 데이터선상의 전송MOSFET Qt1을 온해서 센스 래치회로SLT에 의해 데이터선의 레벨을 검출한다. 디스 차지용MOSFET Qd1은 오프시킨다.

[10] 센스 래치회로SLT로 전원전압을 공급해서 검출한 데이터선 레벨을 증폭한다.

이상의 수순에 의해 불규칙비트를 발생한 메모리셀이 접속된 센스 래치회로SLT에는 데이터 “1”이 유지된다. 따라서, 센스 래치회로SLT에 “1”이 남아있는지의 여부를 후술하는 라이트 소거판정회로(33)(도 9참조)에 의해 검출하는 것에 의해 불규칙비트가 발생했는지의 여부를 검출하고, 에러플래그를 세워서 외부로 알리거나 센스 래치회로SLT에 남은 데이터를 사용해서 불규칙비트를 소거상태로 하고 재차 라이트를 실행하는 것에 의해 데이터를 보수하도록 할 수 있다.

또한, 불규칙비트는 임계값이 너무 낮아지는 현상이므로 임계값이 가장 낮은 메모리셀이 관해서는 라이트에 의해 불규칙비트가 발생해도 리드시에 에러데이터로는 되지 않는다. 워드선에 가장 낮은 리드레벨(1.7V)가 인가되었을 때 정상적인 라이트가 실행된 메모리셀과 마찬가지로 온상태로 되기 때문이다. 가령 불규칙비트의 임계값이 0V이하로 된 경우에는 워드선을 0V로 한 상태로 센스래치회로를 활성화하면 그 메모리셀은 온상태로 되어 있기 때문에 리드 데이터가 “1”로 되므로, 라이트 데이터가 남아 있지 않아도 검출할 수 있다. 상기 실시예에 있어서는 임계값이 가장 낮은 메모리셀의 라이트를 처음에 실행하도록 하고 있으므로, 처음과 라이트에 사용한 라이트 데이터가 센스 래치회로에서 손실되어도 불규칙비트의 검출에 있어서는 아무런 지장이 없다.

다음에, 외부단자를 거쳐서 메모리셀의 데이터를 플래시 메모리의 외부로 출력하는 통상의 리드동작에 대해서 설명한다. 데이터의 리드는 워드선을 상승시켜서 상기 검증동작시와 같이 메모리셀의 컨트롤레이트의 전위를 3단계(각 임계값의 중간값)로 변화시키고, 또 데이터선DL을 거쳐서 선택 메모리셀의 드레인에 1V의 전압을 인가하고 또 로컬소오스선LSL을 접지점에 접속하는 것에 의해 실행한다. 임계값이 워드선의 레벨보다 낮은 메모리셀은 온상태로 되므로, 이 메모리셀이 접속된 데이터선은 접지전위로 디스차지된다. 한편, 임계값이 워드선의 레벨보다 높은 메모리셀은 오프상태로 되므로, 이 메모리셀이 접속된 데이터선은 1V의 상태로 된다. 이 전위를 센스 래치회로SLT 또는 데이터 래치회로 DLT에 의해 검출하는 것에 의해 1차 리드 데이터가 얻어진다.

보다 구체적으로는 리드동작이 개시되면 우선 선택워드선의 레벨을 3.5V로 해서 선택메모리에서 데이터를 리드하여 데이터 래치열(12a)에 유지시킨다.

다음에, 선택워드선의 레벨을 2.7V로 해서 선택메모리에서 데이터를 리드하여 데이터 래치열(12b)에 유지시킨다. 마지막으로, 선택워드선의 레벨을 1.7V로 해서 선택메모리셀에서 데이터를 리드하여 데이터 래치열(11)에 유지시킨다. 이와 같이 해서 워드선레벨을 3단계로 변화시키는 것에 의해, 동일 메모리셀에서 3종의 데이터가 순차 리드되어 데이터 래치열(12a), (12b)와 센스 래치열(11)에 유지되므로, 이를 리드된 데이터에 대해서 논리연산을 실시해서 역변환하는 것에 의해 라이트된 데이터와 동일한 리드 데이터를 2비트 단위로 복원할 수 있다.

표 2에는 메모리셀의 기억데이터와 각 래치회로의 1차 리드 데이터 및 역변환 후의 리드 데이터를 나타낸다.

[표 2]

| 메모리<br>데이터 | 1회 째 리드<br>Vwr=3. 5V | 2회 째 리드<br>Vwr=2. 7V | 3회 째 리드<br>Vwr=1. 7V | 리드데이터 |       |

|------------|----------------------|----------------------|----------------------|-------|-------|

|            |                      |                      |                      | I/O 0 | I/O 1 |

| 01         | 0                    | 0                    | 0                    | 0     | 1     |

| 00         | 0                    | 0                    | 1                    | 0     | 0     |

| 10         | 0                    | 1                    | 1                    | 1     | 0     |

| 11         | 1                    | 1                    | 1                    | 1     | 1     |

또한, 상기 역변환은 데이터 변환회로(20)내에 그와 같은 논리연산회로를 마련해서 실행해도 좋지만, 메모리 어레이(10)내의 데이터선을 사용해서 데이터 래치열(12a), (12b)와 센스 래치열(11)에 유지되어 있는 데이터끼리의 와이어드 논리(논립합 또는 배타적 논리합)를 취하는 것에 의해 실행할 수도 있다. 또, 리드동작은 리드를 명령하는 커맨드가 입력되는 것에 의해 실행된다. 도 9에는 상기 메모리 어레이(10), 데이터 변환회로(20) 및 제어회로와 메모리 주변회로를 동일 반도체침상에 구비한 다진 플래시 메모리(1) 전체의 구성예가 도시되어 있다.

본 실시예의 플래시 메모리는 특히 제한되지 않지만 외부의 CPU등에서 외부단자I/O를 거쳐서 인가되는 커맨드를 디코드하는 커맨드 디코더(31) 및 이 커맨드 디코더(31)의 디코드 결과에 따라서 상기 커맨드에 대응한 처리를 실행해야 할 메모리 내부의 각 회로에 대한 제어신호를 순차 형성해서 출력하는 제어회로(시컨서)(32)를 구비하고 있고, 커맨드가 인가되면 그것을 해독해서 자동적으로 대응하는 처리를 실행하도록 구성되어 있다. 상기 제어회로(32)는 예를 들면 마이크로프로그램방식의 CPU와 제어부와 마찬가지로, 커맨드(명령)를 실행하는 데 필요한 일련의 마이크로 명령군이 저장된 ROM(리드 온리 메모리)으로 이루어지고, 커맨드 디코더(31)이 커맨드에 대응한 마이크로 명령군의 선두 어드레스를 생성해서 제어회로(32)에 인가하는 것에 의해, 마이크로프로그램이 기동되도록 구성되어 있다.

도 9에 있어서 도 4와 동일 부호가 붙여져 있는 회로부분은 동일한 기능을 갖는 회로이다. 즉, (10)은 2개의 메모리매트MAT-A, MAT-B로 구성된 메모리 어레이, (20)은 외부에서 입력된 라이트 데이터를 2비트마다 4진 데이터로 변환하는 데이터 변환회로, (11)은 변환된 라이트 데이터나 리드 데이터를 유지하는 센스 래치열, (12a), (12b)는 데이터 래치열이다.

메모리 어레이(10)에는 각 메모리매트MAT-A, MAT-B에 대응해서 각각 어드레스신호를 디코드하고, 웨드선택을 하는 X계의 어드레스 디코더(13a), (13b)와 이 디코더(13a), (13b)의 디코드결과에 따라서 각 메모리매트내의 1개의 선택된 웨드선WL으로 후술하는 내부전압 발생회로(37)에서 발생, 공급된 소정전압을 공급하는 웨드선 드라이브회로(14a), (14b)가 마련되어 있다. 특히 제한되지는 않지만, 본 실시예의 메모리 어레이(10)에서는 상기 웨드선 드라이브회로가 각 메모리매트의 양측 및 중앙에 배치되어 있다. 도 2나 도 3에는 도시되지 있지 않지만, Y계의 어드레스 디코더회로 및 이 디코더에 의해 선택적으로 온, 오프되어 데이터 변환회로(20)로부터의 데이터를 대응하는 센스 래치로 전송시키는 컬럼스위치는 센스 래치열(11)과 일체적으로 구성되어 있다. 도 9에는 이 Y계 디코더회로와 컬럼스위치 및 센스 래치회로가 1개의 기능블록Y-DECSLT로 도시되어 있다.

본 실시예의 다진 플래시 메모리에는 상기 각 회로 이외에 라이트시나 소거시에 센스 래치열(11)의 데이터에 따라서 리드 또는 소거가 종료했는지를 판정하여 상기 제어회로(32)에 알려 라이트 시컨스 또는 소거 시컨스를 종료시키는 라이트 소거 판정회로(34), 내부의 동작에 필요한 타이밍클럭을 형성해서 메모리 내의 각 회로에 공급하는 클럭발생회로(34), 메모리 내부의 상태를 반영함과 동시에 외부에 대해서 외부에서 액세스가 가능한지의 여부를 나타내는 레디/비치신호R/B를 신호로 형성해서 출력하거나 내부회부를 테스트하는 기능을 구비한 상태 테스트회로(35), 메모리 어레이(10)에서 리드된 신호를 증폭하는 메인앰프회로(36), 전원단자를 거쳐서 전원전압Vcc(3.3V) 및 접지전위Vss가 공급되는 내부전압 발생회로(37), 외부에서 외부단자I/O를 거쳐서 입력되는 어드레스신호나 라이트 데이터신호 및 커맨드를 폐지해서 내부의 소정의 회로에 공급함과 동시에 리드 데이터신호를 외부로 출력하기 위한 입출력 버퍼회로(38), 외부에서 입력되는 제어신호를 폐지해서 제어회로(32) 이외에 내부의 소정의 회로에 공급하거나 상기 입출력 버퍼회로(38)를 제어하는 제어신호 입력버퍼입출력 제어회로(39), 어드레스 제어계회로(40) 및 메모리 어레이내에 불량비트가 있었던 경우에 예비메모리행과 치환하기 위한 용장회로(41)등이 마련되어 있다.

본 실시예의 플래시 메모리는 어드레스신호와 라이트 데이터신호 및 커맨드 입력에 의해 외부단자(핀)I/O를 공용하고 있다. 그 때문에, 입출력 버퍼회로(38)은 상기 제어신호 입력버퍼입출력 제어회로(39)로부터의 제어신호에 따라서 이들 입력신호를 구별해서 폐지하고 소정의 내부회로로 공급한다. 또, 상기 내부전압 발생회로(37)은 기판전위 등의 기준으로 되는 전압을 발생하는 기준전원 발생회로나 외부에서 공급되는 전원전압Vcc에 따라서 라이트전압, 소거전압, 리드전압, 검증전압 등 칩 내부에 필요로 되는 전압을 발생하는 차지펌프 등으로 이루어지는 내부전원 발생회로, 메모리의 동작상태에 따라서 이들 전압중에서 원하는 전압을 선택해서 메모리 어레이(10)으로 공급하는 전원전환회로 및 이들 회로를 제어하는 전원제어회로로 등으로 이루어진다.

상기 어드레스 제어계회로(40)은 외부에서 입력되는 어드레스신호를 폐지해서 카운트업하고 어드레스 카운터ACNT, 데이터 전송시에 Y어드레스를 자동적으로 갱신하거나 데이터 소거시 등에서 자동적으로 X어드

레스를 발생하는 어드레스 발생기AGEN 및 입력어드레스와 불량어드레스를 비교해서 등으로 이루어진다.

외부의 CPU 등에서 본 실시예의 플래시 메모리에 입력되는 제어신호로서는 예를 들면 리세트신호RES나 칩 선택신호CE, 라이트 제어신호WE, 출력 제어신호OE, 커맨드 또는 데이터 입력인지 어드레스 입력인지나 타내기 위한 커맨드 인에이블신호CDE 및 시스템클럭SC 등이 있다.

또한, 상기 실시예의 다진 플래시 메모리를 제어하는 외부의 장치로서는 어드레스 생성기능과 커맨드 생성기능을 구비하고 있으면 좋으므로, 범용 마이크로컴퓨터LSI를 사용할 수 있다.

이상 설명한 바와 같이 상기 실시예에 있어서는 여러개의 임계값을 설정해서 1개의 메모리셀에 다진의 정보를 기억시키도록 한 불휘발성 반도체 기억장치에 있어서, 소거레벨에서 먼 임계값(라이트 상태로서의 가장 낮은 임계값)의 메모리셀로의 라이트부터 개시해서 순차 임계값이 높은 메모리셀로의 라이트를 실행하도록 했으므로, 워드선 디스터브의 영향을 가장 받기 쉬운 소거레벨에 가까운 임계값의 메모리셀에 대해서 가해지는 워드선 디스터브의 회수를 감소시킬 수 있고, 워드선 디스터브에 의한 임계값의 변동을 최소로 억제할 수 있다는 효과가 있다.

또, 종래의 라이트방식에서는 제1단계의 라이트시에 임계값을 어긋나게 하고자 하는 모든 메모리셀에 대해서 라이트펄스를 인가하기 때문에, 라이트시의 피크전류가 증대함과 동시에 평균소비전력도 많아진다는 문제가 있었지만, 상기 실시예에서는 목표으로 하는 임계값이 다른 메모리셀마다 라이트펄스를 인가하면 좋으므로, 1회의 라이트에 의해 프리차지하지 않으면 안되는 데이터선수와 라이트 개시부터 종료할 때까지 프리차지하지 않으면 안되는 데이터선수와 라이트개시부터 종료할 때까지 프리차지하지 않으면 안되는 데이터선의 총수를 종래 방식에 비해 적게 해서 라이트시의 피크전류와 평균소비전력을 저감 할 수 있다는 효과가 있다.

또한, 상기 실시예에서는 라이트 워드선 전압을 목표 임계값에 따라서 그 절대값이 서서히 작아지도록 제어하고 있으므로, 1회에 발생하는 디스터브의 양도 점차 작아져 임계값의 변동을 더욱 작게 할 수 있다. 또한, 상기 실시예에서는 메모리 어레이가 2개의 매트로 구성되고, 2개의 매트 사이에는 각 매트내의 데이터선이 입출력단자에 접속되고, 상기 데이터 변환회로에 의해 변환된 3비트 데이터 중 1비트를 유지할 수 있는 센스 래치회로가 배치되고, 각 매트의 외측에는 각각 상기 데이터 변환된 3비트 데이터 중 다른 1비트를 각각 유지할 수 있는 데이터 래치회로가 배치되고, 데이터 래치회로와 센스 래치회로 사이에서 데이터선을 거쳐서 데이터 전송을 실행하도록 하고 있으므로, 데이터 변환회로측에 변환 후의 데이터를 유지하는 레지스터를 마련할 필요가 없음과 동시에 불규칙비트의 검출도 간단히 실행할 수 있게 된다는 효과가 있다.

이상 본 발명자에 의해 이루어진 발명을 실시예에 따라서 구체적으로 설명했지만, 본 발명은 상기 실시예에 한정되는 것은 아니고, 그 요지를 일탈하지 않는 범위에서 여러가지로 변경가능한 것은 물론이다. 예를 들면, 상기 실시예에서는 메모리셀의 임계값을 4단계로 설정해서 1개의 메모리셀에 4진의 데이터를 기억할 수 있도록 하고 있지만, 메모리셀의 임계값을 3단계 또는 5단계 이상으로 설정하도록 한 불휘발성 메모리에 적용하는 것도 가능하다.

또, 본 실시예에서는 2비트 데이터를 4진 데이터로 변환하는 방식의 1예로서 표 1에 나타내는 바와 같은 변환을 실행되고 있지만, 변화방식은 표 1에 나타내는 것에 한정되지 않고 결과로서 1로 되어 있는 비트의 위치가 다른 데이터가 얻어지는 것이면 좋다. 또, 데이터 역변환을 위한 연산도 표 2의 것에 한정되지 않고 원래의 2비트 데이터를 복원할 수 있는 것이면 어떠한 변환이라도 좋다.

또, 각 메모리셀에 대한 라이트방식도 실시예와 같이 일단 소거를 실행해서 임계값을 높게 한 후에 라이트펄스에 의해 임계값을 낮추는 방식에 한정되지 않고, 라이트펄스에 의해 임계값을 높게 하는 방식 등이라도 좋다. 또, 실시예에서는 데이터 “1”을 유지하는 센스 래치회로에 대응하는 메모리셀에 라이트를 실행해서 임계값을 변환시키고 있지만, 데이터 “0”을 유지하는 센스 래치회로에 대응하는 메모리셀에 라이트를 실행해서 임계값을 변화시키도록 해도 좋다.

또한, 상기 실시예에서는 메모리 어레이를 2개의 매트로 구성한 경우에 대해서 설명했지만, 본 발명은 그 것에 한정되지 않고 우수개의 매트로 분할인 경우는 물론 1개의 매트로 구성되어 있는 경우에도 적용할 수 있다. 메모리 어레이가 1개의 매트로 구성된 경우에는 예를 들면 데이터 변환회로에 의해 변환된 후의 데이터를 2회로 나누어 전송하는 등의 방식을 적용하면 좋다.

이상의 설명에서는 주로 본 발명자에 의해 이루어진 발명을 그 배경으로된 이용분야인 일괄소거형 플래시 메모리에 적용한 경우에 대해서 설명했지만, 본 발명은 그것에 한정되는 것은 아니고 FAMOS를 기억소자로 하는 불휘발성 기억장치의 일반 또는 여러개의 임계값을 갖는 메모리셀을 구비한 반도체장치에 널리 이용할 수 있다. 또, 임계값을 가장 낮은 상태로 하는 것을 소자라고 정의하고, 소거상태에서 임계값을 높게 하는 것을 라이트라고 정의하고 있는 NOR형 플래시 메모리가 있다. 다진의 NOR형 플래시 메모리에서 라이트의 워드선 디스터브의 영향을 저감하는 것을 고려한 경우, 데이터가 라이트는 소거상태의 가장 낮은 임계값에서 2번째로 낮은 임계값으로, 다음에 가장 낮은 임계값에서 3번째로 낮은 임계값과 같은 방식으로 높은 임계값으로 서서히 실행하는 것이 바람직하다.

### 발명의 효과

본 원에 있어서 개시되는 발명 중 대표적인 것에 의해 얻어지는 효과를 간단하게 설명하면 다음과 같다.

즉, 본 발명은 워드선 디스터브에 의한 메모리셀의 임계값의 변동을 최소로 억제하는 것이 가능함과 동시에 라이트시의 피크전류와 평균소비전력을 저감할 수 있는 불휘발성 반도체 기억장치를 실현할 수 있다.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음

### (57) 청구의 범위

**청구항 1**

컨트롤게이트 및 플로팅게이트를 각각 갖고 데이터를 임계값으로서 저장하는 여러개의 메모리셀을 포함하고, 각각의 메모리셀의 임계값은 소거상태로 되는 제1임계값영역 및 상기 제1임계값영역과는 다른 라이트상태로 되는 여러개의 임계값영역에서 1개로 되고, 소거상태에 메모리셀에 데이터를 라이트할 때 선택된 메모리셀은 상기 소거상태의 임계값영역에서 라이트상태로서 가장 낮은 제2 임계값영역으로 되고, 또 데이터를 라이트할 때 제1 임계값영역내의 메모리셀이 상기 제1 임계값영역에서 상기 제2 임계값영역보다 높은 제3 임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 2**

제1항에 있어서, 데이터를 라이트할 때, 선택된 메모리셀의 컨트롤게이트에 제1전압이 공급되는 것에 의해 메모리셀의 임계값은 제1임계값영역에서 제2임계값영역으로 되고, 선택된 메모리셀의 컨트롤게이트에 상기 제1전압과는 다른 제2전압이 공급되는 것에 의해 메모리셀의 임계값은 제1 임계값영역에서 제3 임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 3**

제2항에 있어서, 상기 여러개의 메모리셀의 각각은 2비트의 데이터를 저장하는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 4**

제3항에 있어서, 외부단자, 데이터 변환회로, 제1 데이터 래치, 제2 데이터 래치 및 제3 데이터 래치를 갖고, 상기 외부데이터단자에서 공급된 데이터는 상기 데이터 변환되고, 변환된 데이터는 대응하는 상기 제1 데이터 래치, 상기 제2 데이터 래치 및 상기 제3 데이터 래치에 저장하는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 5**

제4항에 있어서, 선택된 메모리셀의 임계값은 상기 제1 데이터 래치회로에 저장된 데이터에 의해 제1임계값영역에서 제2 임계값영역으로 되고, 상기 제2 데이터 래치회로에 저장된 데이터에 의해 제1 임계값영역에서 제3 임계값영역으로 되고, 상기 제3 데이터 래치회로에 저장된 데이터에 의해 제1 임계값영역에서 제4 임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 6**

제5항에 있어서, 상기 제1데이터 래치회로에 저장된 데이터에 의해 선택된 메모리셀의 임계값이 상기 제1 임계값영역에서 상기 제2 임계값영역으로 되고, 상기 제2 데이터 래치회로에 저장되어 있던 데이터는 상기 제1데이터 래치회로로 전송되고, 상기 제1데이터 래치회로에 저장된 데이터에 의해 선택된 메모리셀의 임계값이 상기 제1임계값영역에서 상기 제3임계값영역으로 되고, 상기 제3 데이터에 의해 선택된 메모리셀의 임계값은 상기 제1임계값영역에서 제4 임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 7**

제6항에 있어서, 라이트동작을 지지하는 1개의 커맨드가 입력되는 것에 의해, 상기 여러개의 메모리셀중에서 선택된 메모리셀의 임계값은 상기 제1 임계값영역에서 상기 제4임계값영역까지 변화되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 8**

제7항에 있어서, 입력된 커맨드를 디코더하는 커맨드 디코더 및 상기 커맨드 디코더의 디코드 결과에 따라서 제어신호를 발생하는 제어회로를 더 포함하는 것을 특징으로하는 반도체 불휘발성 기억장치.

**청구항 9**

제8항에 있어서, 상기 제어회로가 발생한 제어신호에 응답해서 선택된 메모리셀의 컨트롤게이트에 소정전압을 공급하는 전압발생회로를 더 포함하는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 10**

제9항에 있어서, 라이트동작을 지시하는 외부제어신호에 따라서 상기 여러개의 메모리셀중에서 선택된 메모리셀의 임계값은 상기 제1 임계값영역에서 상기 제4임계값영역까지 변환되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 11**

여러개의 워드선, 컨트롤게이트 및 플로팅게이트를 각각 갖고 2비트 데이터를 임계값으로 저장하며 컨트롤게이트를 거쳐서 상기 여러개의 워드선중의 대응하는 워드선에 각각 결합되는 여러개의 메모리셀, 외부단자, 상기 외부단자를 거쳐서 공급된 어드레스신호에 따라서 상기 여러개의 워드선에서 소정 워드선을 선택하는 워드선 디코더, 선택된 워드선에 소정전압을 공급하는 워드선 드라이버, 상기 워드선 드라이버에 상기 소정 전압을 공급하는 내부전압 발생회로 및 상기 외부단자를 거쳐서 공급된 데이터를 변화하는 데이터 변환회로를 포함하고, 라이트동작에 있어서 라이트가 선택된 메모리셀의 임계값은 소거상태로 되는 제1임계값영역에서 상기 데이터 변환회로에 의해 변환된 데이터에 따라서, 라이트상태로서 가장 낮은 제2 임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

**청구항 12**

제11항에 있어서, 데이터를 라이트할 때, 선택된 메모리셀의 컨트롤게이트에 제1전압이 공급되는 것에 의해 메모리셀의 임계값은 제1임계값영역에서 제2임계값영역으로 되고, 메모리셀의 컨트롤게이트에 상기 제1전압과는 다른 제2전압이 공급되는 것에 의해 메모리셀의 임계값은 제1임계값영역에서 제3임계값영역으로 되고, 메모리셀의 컨트롤게이트에 상기 제1및 제2전압과는 다른 제3전압이 공급되는 것에 의해 메모리셀의 임계값은 제1임계값영역에서 제4임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 13

제12항에 있어서, 상기 제1, 제2 및 제3 전압은 상기 내부전압 발생회로에서 발생되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 14

제13항에 있어서, 제1데이터 래치, 제2데이터 래치 및 제3데이터 래치를 갖고, 상기 데이터 변환회로에 의해 변환된 데이터는 대응하는 상기 제1데이터래치, 상기 제2데이터 래치 및 상기 제3데이터 래치에 저장되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 15

제14항에 있어서, 선택된 메모리셀의 임계값은 상기 제1데이터 래치회로에 저장된 데이터에 의해 제1임계값영역에서 제2임계값영역으로 되고, 상기 제2데이터 래치회로에 저장된 데이터에 의해 제1임계값영역에서 상기 제3임계값영역으로 되고, 상기 제3데이터 래치에 저장된 데이터 의해 제1임계값영역에서 제3임계값영역으로 되고, 상기 제3데이터 래치회로에 저장된 데이터에 의해 제1임계값영역에서 제4임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 16

제15항에 있어서, 상기 제1데이터 래치회로에 저장된 데이터에 의해 선택된 메모리셀의 임계값이 상기 제1임계값영역에서 상기 제2임계값영역으로 되고, 상기 제2 데이터래치회로에 저장되어 있던 데이터는 상기 제1 데이터 래치회로로 전송되고, 상기 제1 데이터 래치회로에, 저장된 데이터에 의해 선택된 메모리셀의 임계값이 상기 제1임계값영역에서 상기 제3임계값영역으로 되고, 상기 제3데이터 래치에 저장되어 있던 데이터는 상기 제1 데이터 래치회로로 전송되고, 상기 제1 데이터 래치회로에 저장된 데이터에, 의해 선택된 메모리셀의 임계값은 상기 제1임계값영역에서 제4임계값영역으로 되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 17

제16항에 있어서, 라이트동작을 지시하는 1개의 커맨드가 상기 외부단자를 거쳐서 입력되는 것에 의해, 상기 여러개의 메모리셀중에서 선택된 메모리셀의 임계값은 상기 제1임계값영역에서 상기 제4임계값영역까지 변화되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 18

제17항에 있어서, 입력된 커맨드를 디코드하는 커맨드 디코더 및 상기 커맨드 디코더의 디코드 결과에 따라서 제어신호를 발생하는 제어회로를 갖는 것을 특징으로 하는 반도체 불휘발성 기억장치.

#### 청구항 19

제18항에 있어서, 라이트동작을 지시하는 외부제어신호에 따라서 상기 여러개의 메모리셀중에서 선택된 메모리셀들의 임계값은 상기 제1임계값영역에서 상기 제4임계값영역까지 변화되는 것을 특징으로 하는 반도체 불휘발성 기억장치.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

#### 도면

## 도면1

|                           | 초기상태         |                                                                                   |            |            | 타이프1       |            |                                                                                   |            |            |            |

|---------------------------|--------------|-----------------------------------------------------------------------------------|------------|------------|------------|------------|-----------------------------------------------------------------------------------|------------|------------|------------|

| V <sub>th</sub><br>분포의 변화 | 도수           |  |            |            |            | 도수         |  |            |            |            |

| 메모리 바이어스 조건               | 0V           | b1<br>(11)                                                                        | b2<br>(11) | b3<br>(11) | b4<br>(11) | 5V         | b1<br>(01)                                                                        | b2<br>(11) | b3<br>(11) | b4<br>(11) |

| V <sub>wv1</sub>          | -11V         | (01)                                                                              | (00)       | (10)       | (11)       | (01)       | (00)                                                                              | (10)       | (11)       |            |

| 타이프1데이터                   | 01           | 00                                                                                | 10         | 11         | 01         | 00         | 10                                                                                | 11         |            |            |

| 메모리데이터                    | 11           | 11                                                                                | 11         | 11         | 01         | 11         | 11                                                                                | 11         |            |            |

| 디스터보                      | -            | -                                                                                 | -          | -          | 0          | 1          | 1                                                                                 | 1          |            |            |

|                           | 타이프2         |                                                                                   |            |            | 타이프3       |            |                                                                                   |            |            |            |

| V <sub>th</sub><br>분포의 변화 | 도수           |  |            |            |            | 도수         |  |            |            |            |

| 메모리 바이어스 조건               | 5V<br>-10.5V | b1<br>(01)                                                                        | b2<br>(00) | b3<br>(11) | b4<br>(11) | 5V<br>-10V | b1<br>(01)                                                                        | b2<br>(00) | b3<br>(10) | b4<br>(11) |

| V <sub>wv2</sub>          | -10.5V       | (01)                                                                              | (00)       | (10)       | (11)       | (01)       | (00)                                                                              | (10)       | (11)       |            |

| 타이프2데이터                   | 01           | 00                                                                                | 10         | 11         | 01         | 00         | 10                                                                                | 11         |            |            |

| 메모리데이터                    | 01           | 00                                                                                | 11         | 11         | 01         | 00         | 10                                                                                | 11         |            |            |

| 디스터보                      | 1            | 0                                                                                 | 2          | 2          | 2          | 1          | 0                                                                                 | 3          |            |            |

## 도면2

도면3

도면4

도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

하이트시의 인가전압의 1에

## 도면11

소거시의 인가전압의 1에

## 도면12

| 초기상태            |                                                                                                                                | 하이트 1                                                                                                                                                                     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{th}$ 분포의 변화 | 동수                                                                                                                             | 동수                                                                                                                                                                        |

|                 |                                                                                                                                |                                                                                                                                                                           |

| 비모피바이어스 조건      | $0V$<br><br>$b_1 (11) \quad b_2 (11) \quad b_3 (11) \quad b_4 (11)$<br>$(01) \quad (00) \quad (10) \quad (11)$                 | $5V \quad 5V \quad 5V \quad b_4$<br>$b_1 \quad b_2 \quad b_3 \quad (11)$<br>$-11V \quad (10) \quad (10) \quad (10) \quad (11)$<br>$(01) \quad (00) \quad (10) \quad (11)$ |

| 하이트 대의파         | 01 00 10 11                                                                                                                    | 01 00 10 11                                                                                                                                                               |

| 비모피 대의파         | 11 11 11 11                                                                                                                    | 10 10 10 11                                                                                                                                                               |

| 디스비트            | - - - -                                                                                                                        | 0 1 2 3                                                                                                                                                                   |

|                 | 하이트 2                                                                                                                          | 하이트 3                                                                                                                                                                     |

| $V_{th}$ 분포의 변화 | 동수                                                                                                                             | 동수                                                                                                                                                                        |

|                 |                                                                                                                                |                                                                                                                                                                           |

| 메모리 바이어스 조건     | $5V \quad 5V$<br>$b_1 (00) \quad b_2 (00) \quad b_3 (10) \quad b_4 (11)$<br>$-11V \quad (01) \quad (00) \quad (10) \quad (11)$ | $5V \quad b_1 \quad b_2 \quad b_3 \quad b_4$<br>$(01) \quad (00) \quad (10) \quad (11)$<br>$-11V \quad (01) \quad (00) \quad (10) \quad (11)$                             |

| 하이트 대의파         | 01 00 10 11                                                                                                                    | 01 00 10 11                                                                                                                                                               |

| 비모피 대의파         | 00 00 10 11                                                                                                                    | 01 00 10 11                                                                                                                                                               |

| 디스비트            | - 0 1 2                                                                                                                        | 0 1 2 3                                                                                                                                                                   |