(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6041500号

(P6041500)

(45) 発行日 平成28年12月7日(2016.12.7)

(24) 登録日 平成28年11月18日(2016.11.18)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO4N 5/378 (2011.01) | HO4N 5/335 780 |

| HO4N 5/374 (2011.01) | HO4N 5/335 740 |

| HO4N 5/347 (2011.01) | HO4N 5/335 470 |

| GO2B 7/34 (2006.01)  | GO2B 7/34      |

| GO3B 13/36 (2006.01) | GO3B 13/36     |

請求項の数 17 (全 24 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2012-45652 (P2012-45652)    |

| (22) 出願日  | 平成24年3月1日(2012.3.1)           |

| (65) 公開番号 | 特開2013-183279 (P2013-183279A) |

| (43) 公開日  | 平成25年9月12日(2013.9.12)         |

| 審査請求日     | 平成27年3月2日(2015.3.2)           |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 橋本 誠二<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| (72) 発明者  | 鈴木 建<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内     |

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、撮像装置の駆動方法、撮像システムの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が入射光に基づく信号電荷を生成する n 個 (n は 2 以上の自然数) の光電変換部を有する画素と、

複数のアナログデジタル変換部と、を有し、

前記複数のアナログデジタル変換部が、

前記 n 個の光電変換部が含む m 個 (m は n > m の関係式を満たす自然数) の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第 1 の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第 1 の期間に行う第 1 のアナログデジタル変換部と、

前記 n 個の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第 2 の光電変換信号をデジタル信号に変換する動作の少なくとも一部を前記第 1 の期間に行う第 2 のアナログデジタル変換部と、を有することを特徴とする撮像装置。

## 【請求項 2】

前記撮像装置はさらに複数の前記画素と加算回路を有し、

前記複数の画素の各々は前記加算回路に前記第 1 の光電変換信号と前記第 2 の光電変換信号を出力し、

前記加算回路は、

前記複数の画素の各々から出力された前記第 1 の光電変換信号同士を加算して前記第 1 のアナログデジタル変換部に出力し、前記複数の画素の各々から出力された前記第 2 の光電変換信号同士を加算して前記第 2 のアナログデジタル変換部に出力することを特徴とす

10

20

る請求項 1 に記載の撮像装置。

【請求項 3】

前記複数の画素のうちの第 1 の画素と第 2 の画素は、第 1 の色のカラーフィルタを有し、前記複数の画素のうちの第 3 の画素は、第 2 の色のカラーフィルタを有し、

前記加算回路が、前記第 1 の画素と前記第 2 の画素の各々の前記第 1 の光電変換信号同士及び前記第 2 の光電変換信号同士を加算することを特徴とする請求項 2 に記載の撮像装置。

【請求項 4】

前記撮像装置は増幅回路をさらに有し、

前記増幅回路は、前記第 1 の光電変換信号を増幅して前記第 1 のアナログデジタル変換部に出力し、前記第 2 の光電変換信号を増幅して前記第 2 のアナログデジタル変換部に出力することを特徴とする請求項 1 ~ 3 のいずれか 1 項 に記載の撮像装置。 10

【請求項 5】

前記撮像装置はさらに、複数の前記画素と複数の信号線と、を有し、前記複数の画素の各々は前記複数の信号線のうちの 1 つの信号線を介して、前記第 1 のアナログデジタル変換部と前記第 2 のアナログデジタル変換部に前記第 1 の光電変換信号と前記第 2 の光電変換信号とを出力し、前記 1 つの信号線に対し、前記第 1 のアナログデジタル変換部および前記第 2 のアナログデジタル変換部が電気的に接続されていることを特徴とする請求項 1 ~ 4 のいずれか 1 項 に記載の撮像装置。

【請求項 6】

前記第 1 のアナログデジタル変換部と前記第 2 のアナログデジタル変換部の各々は、

前記第 1 の光電変換信号と前記第 2 の光電変換信号の一方と、時間に依存して電位が変化する参照信号とを比較した結果に基づく比較結果信号を出力する比較器を有し、

前記第 1 の期間に、

前記第 1 のアナログデジタル変換部の有する前記比較器が、前記第 1 の光電変換信号と前記参照信号とを比較する動作の少なくとも一部と、

前記第 2 のアナログデジタル変換部の有する前記比較器が、前記第 2 の光電変換信号と前記参照信号とを比較する動作の少なくとも一部と、を行うことを特徴とする請求項 1 ~ 5 のいずれか 1 項 に記載の撮像装置。 20

【請求項 7】

前記第 2 のアナログデジタル変換部が、前記第 2 の光電変換信号をデジタル信号に変換する動作を行う全期間に、

前記第 1 のアナログデジタル変換部が、前記第 1 の光電変換信号をデジタル信号に変換する動作を行う全期間が含まれることを特徴とする請求項 1 ~ 6 のいずれか 1 項 に記載の撮像装置。 30

【請求項 8】

前記第 1 の アナログデジタル変換部の有する前記比較器 と前記第 2 の アナログデジタル変換部の有する前記比較器 とに共通の前記参照信号を供給し、前記第 1 の光電変換信号と前記共通の参照信号を比較する全期間と、前記第 2 の光電変換信号と前記共通の参照信号とを比較する全期間とが前記第 1 の期間であることを特徴とする請求項 6 に記載の撮像装置。 40

【請求項 9】

前記第 1 の アナログデジタル変換部の有する前記比較器 に供給される前記参照信号と前記第 2 の アナログデジタル変換部の有する前記比較器 に供給される前記参照信号との、時間に依存した電位の変化を開始するタイミングが異なることを特徴とする請求項 6 に記載の撮像装置。

【請求項 10】

前記撮像装置は、マイクロレンズをさらに有し、

前記マイクロレンズは、前記画素の前記 n 個の光電変換部に光を入射させることを特徴とする請求項 1 ~ 9 のいずれか 1 項 に記載の撮像装置。 50

## 【請求項 1 1】

請求項 1 ~ 10 のいずれか 1 項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と、

を有することを特徴とする撮像システム。

## 【請求項 1 2】

請求項 10 に記載の撮像装置と、前記撮像装置から信号が入力される信号処理部と、を

有する撮像システムであって、

前記複数の画素の前記第 1 の光電変換信号に基づくデジタル信号と前記第 2 の光電変換

信号に基づくデジタル信号とが前記撮像装置から前記信号処理部に出力され、

前記信号処理部は、

前記画素の出力した前記第 1 の光電変換信号と前記第 2 の光電変換信号のそれぞれに基

づくデジタル信号の差分である差分信号を得て、前記第 1 の光電変換信号に基づくデジタル

信号と前記差分信号とによって焦点検出を行い、

さらに、前記信号処理部は、前記撮像装置から出力された、前記複数の画素の前記第 2

の光電変換信号に基づくデジタル信号によって画像を形成することを特徴とする撮像シス

テム。

## 【請求項 1 3】

各々が入射光に基づく信号電荷を生成する n 個 ( n は 2 以上の自然数 ) の光電変換部を

有する画素と、

複数のアナログデジタル変換部と、を有する撮像装置の駆動方法であって、

前記複数のアナログデジタル変換部のうちの第 1 のアナログデジタル変換部は、

前記 n 個 に含まれる m 個 ( m は  $n > m$  の関係式を満たす自然数 ) の前記光電変換部が入

射光に基づいて生成する信号電荷に基づく第 1 の光電変換信号をデジタル信号に変換する

動作の少なくとも一部を第 1 の期間に行い、

前記複数のアナログデジタル変換部のうちの第 2 のアナログデジタル変換部は、

前記 n 個 の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第 2 の光電変

換信号をデジタル信号に変換する動作の少なくとも一部を前記第 1 の期間に行うことを行

うことを特徴とする撮像装置の駆動方法。

## 【請求項 1 4】

前記第 1 の光電変換信号を前記第 1 のアナログデジタル変換部に出力した後に、前記第

2 の光電変換信号を前記第 2 のアナログデジタル変換部に出力することを特徴とする請求

項 13 に記載の撮像装置の駆動方法。

## 【請求項 1 5】

前記撮像装置は、

前記第 1 の光電変換信号が前記第 1 のアナログデジタル変換部に出力され、前記第 2 の

光電変換信号が前記第 2 のアナログデジタル変換部に出力される第 1 の動作と、

前記第 1 の光電変換信号が前記複数のアナログデジタル変換部に出力されず、前記第 2

の光電変換信号を前記第 1 のアナログデジタル変換部と前記第 2 のアナログデジタル変換

部との少なくとも一方に出力する第 2 の動作とを実行可能であり、

前記第 1 の動作では、

前記第 1 のアナログデジタル変換部が前記第 1 の光電変換信号をデジタル信号に変換す

る動作の少なくとも一部を前記第 1 の期間に行い、

前記第 2 のアナログデジタル変換部が前記第 2 の光電変換信号をデジタル信号に変換す

る動作の少なくとも一部を前記第 1 の期間に行い、前記第 2 の動作では、前記第 2 の光

電変換信号が出力された、前記第 1 のアナログデジタル変換部と前記第 2 のアナログデジ

タル変換部との少なくとも一方が前記第 2 の光電変換信号をデジタル信号に変換する動作

を行うことを特徴とする請求項 13 または 14 に記載の撮像装置の駆動方法。

## 【請求項 1 6】

前記撮像装置はさらに複数の前記画素を有し、

前記複数の画素の各々は前記第 1 の光電変換信号と前記第 2 の光電変換信号を出力し、

10

20

30

40

50

前記複数の画素の各々から出力された前記第1の光電変換信号同士を加算して前記第1のアナログデジタル変換部に出力し、前記複数の画素の各々から出力された前記第2の光電変換信号同士を加算して前記第2のアナログデジタル変換部に出力することを特徴とする請求項1\_5に記載の撮像装置の駆動方法。

【請求項1\_7】

撮像システムの駆動方法であって、

前記撮像システムは、

撮像装置と、前記撮像装置から出力される信号の信号処理を行う信号処理部とを有し、前記撮像装置は、

各々が入射光に基づく信号電荷を生成するn個（nは2以上の自然数）の光電変換部を 10

、各々が有する複数の画素と、

複数のアナログデジタル変換部と、

マイクロレンズを複数有するレンズアレイと、を有し、

1つの前記マイクロレンズで集光された光が前記画素の有する前記n個の光電変換部に入射し、前記n個に含まれるm個（mはn>mの関係式を満たす自然数）の光電変換部が入射光に基づいて生成する信号電荷に基づく第1の光電変換信号と、

前記n個の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第2の光電変換信号と、がそれぞれ前記複数のアナログデジタル変換部に出力され、

前記複数のアナログデジタル変換部のうちの第1のアナログデジタル変換部は、

前記第1の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行い、 20

前記複数のアナログデジタル変換部のうちの第2のアナログデジタル変換部は、

前記第2の光電変換信号をデジタル信号に変換する動作の少なくとも一部を前記第1の期間に行い、

前記撮像装置は、前記複数の画素の各々の前記第1の光電変換信号に基づくデジタル信号と、前記複数の画素の各々の前記第2の光電変換信号に基づくデジタル信号とを前記信号処理部に出力し、

前記信号処理部は、同一の画素の出力した前記第1の光電変換信号と前記第2の光電変換信号とのそれぞれに基づくデジタル信号の差分である差分信号を得て、前記第1の光電変換信号に基づくデジタル信号と前記差分信号とによって焦点検出を行い、 30

さらに前記信号処理部は、前記複数の画素の各々の前記第2の光電変換信号に基づくデジタル信号によって画像を形成することを特徴とする撮像システムの駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の光電変換部を含む画素を複数有する撮像装置に関するものである。

【背景技術】

【0002】

近年、光電変換部を有する画素が配された撮像装置では、より高速な信号出力が求められている。 40

撮像装置の一例として、光電変換を行い、入射光に基づく信号を出力する画素と、画素が行列状に配された画素アレイの各列にA/D変換器を有する列並列型のアナログデジタル変換回路（以下、アナログデジタル変換回路をA/D（A n a l o g D i g i t a l C o n v e r t e r）、列並列型のA/Dを列A/Dと表記する）と、を有する撮像装置が知られている。列A/Dにおいては、各列の回路部が画素から出力されるアナログ信号（以下、画素から出力されるアナログ信号を画素信号と表記する）をデジタル信号に変換するアナログデジタル変換（以下、A/D変換と表記する）を行う。

一方、特許文献1には複数の光電変換部を2次元に配列したマイクロレンズアレイのマイクロレンズ毎に設けて、位相差検出方式の焦点検出を行う撮像装置が記載されている。さらに、複数の光電変換部の第1の光電変換部の信号電荷に基づく信号、第1の光電変換

10

20

30

40

50

部とは別の第2の光電変換部の信号電荷に基づく信号、第1の光電変換部と第2の光電変換部とを合わせた信号電荷に基づく信号を出力する形態が記載されている。

また、特許文献2には画素が行列状に配され、異なる行に配された画素が出力する信号を加算し、加算した信号を演算増幅器に出力する構成が記載されている。特許文献2には、画素の各列に演算増幅器が設けられた構成が記載されている。さらに特許文献2に記載の撮像装置では、ある列の演算増幅器と隣接する列の演算増幅器の非反転入力端子( - )とがスイッチを介して接続されている。これにより、隣接する列の画素の信号を加算して演算増幅器に出力することができる。

【先行技術文献】

【特許文献】

10

【0003】

【特許文献1】特開2001-83407号公報

【特許文献2】特開2002-320146号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の撮像装置では、画素から出力される少なくとも2つのアナログ信号を高速にデジタル信号に変換する検討がなされていなかった。

特許文献2には、複数列の画素のそれぞれから出力される少なくとも2つのアナログ信号を高速にデジタル信号に変換する検討が充分では無かった。

20

【課題を解決するための手段】

【0005】

本発明は上記の課題を鑑みて為されたものであり、一の態様は、各々が入射光に基づく信号電荷を生成するn個(nは2以上の自然数)の光電変換部を有する画素と、複数のアナログデジタル変換部と、を有し、前記複数のアナログデジタル変換部が、前記n個の光電変換部が含むm個(mはn>mの関係式を満たす自然数)の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第1の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行う第1のアナログデジタル変換部と、前記n個の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第2の光電変換信号をデジタル信号に変換する動作の少なくとも一部を前記第1の期間に行う第2のアナログデジタル変換部と、を有することを特徴とする撮像装置である。

30

【0006】

また、一の態様は、各々が入射光に基づく信号電荷を生成するn個(nは2以上の自然数)の光電変換部を有する画素と、複数のアナログデジタル変換部と、を有する撮像装置の駆動方法であって、前記複数のアナログデジタル変換部のうちの第1のアナログデジタル変換部は、前記n個に含まれるm個(mはn>mの関係式を満たす自然数)の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第1の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行い、前記複数のアナログデジタル変換部のうちの第2のアナログデジタル変換部は、前記n個の前記光電変換部が入射光に基づいて生成する信号電荷に基づく第2の光電変換信号をデジタル信号に変換する動作の少なくとも一部を前記第1の期間に行うことを特徴とする撮像装置の駆動方法である。

40

【0007】

また、一の態様は、撮像システムの駆動方法であって、前記撮像システムは、撮像装置と、前記撮像装置から出力される信号の信号処理を行う信号処理部とを有し、前記撮像装置は、各々が入射光に基づく信号電荷を生成するn個(nは2以上の自然数)の光電変換部を、各々が有する複数の画素と、複数のアナログデジタル変換部と、マイクロレンズを複数有するレンズアレイと、を有し、1つの前記マイクロレンズで集光された光が前記画素の有する前記n個の光電変換部に入射し、前記n個に含まれるm個(mはn>mの関係式を満たす自然数)の光電変換部が入射光に基づいて生成する信号電荷に基づく第1の光電変換信号と、前記n個の前記光電変換部が入射光に基づいて生成する信号電荷に基づく

50

第2の光電変換信号と、がそれぞれ前記複数のアナログデジタル変換部に出力され、前記複数のアナログデジタル変換部のうちの第1のアナログデジタル変換部は、前記第1の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行い、前記複数のアナログデジタル変換部のうちの第2のアナログデジタル変換部は、前記第2の光電変換信号をデジタル信号に変換する動作の少なくとも一部を前記第1の期間に行い、前記撮像装置は、前記複数の画素の各々の前記第1の光電変換信号に基づくデジタル信号と、前記複数の画素の各々の前記第2の光電変換信号に基づくデジタル信号とを前記信号処理部に出力し、前記信号処理部は、同一の画素の出力した前記第1の光電変換信号と前記第2の光電変換信号とのそれぞれに基づくデジタル信号の差分である差分信号を得て、前記第1の光電変換信号に基づくデジタル信号と前記差分信号とによって焦点検出を行い、さらに前記信号処理部は、前記複数の画素の各々の前記第2の光電変換信号に基づくデジタル信号によって画像を形成することを特徴とする撮像システムの駆動方法である。 10

【発明の効果】

【0008】

本発明により、画素から出力される少なくとも2つのアナログ信号を高速にデジタル信号に変換できる。

【図面の簡単な説明】

【0009】

【図1】撮像装置の俯瞰図と等価回路図

【図2】撮像装置の断面図

20

【図3】撮像装置の等価回路図

【図4】撮像装置の動作タイミング図

【図5】他の一例の撮像装置に関する動作タイミング図

【図6】他の一例の撮像装置の等価回路図

【図7】他の一例の撮像装置の動作タイミング図

【図8】他の一例の撮像装置のブロック図

【図9】他の一例の撮像装置の等価回路図

【図10】他の一例の撮像装置の動作タイミング図

【図11】撮像システムのブロック図

【発明を実施するための形態】

30

【0010】

[実施例1]

以下、図面を参照しながら本実施例の撮像装置について説明する。

【0011】

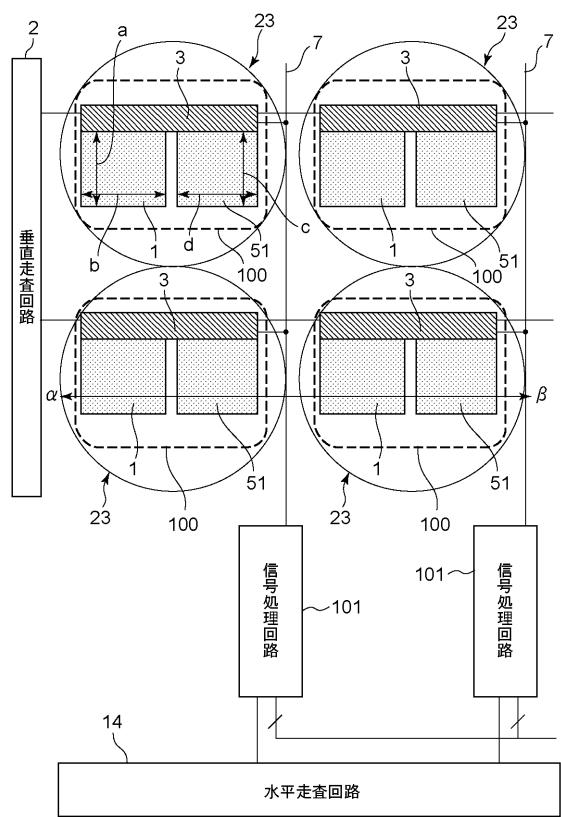

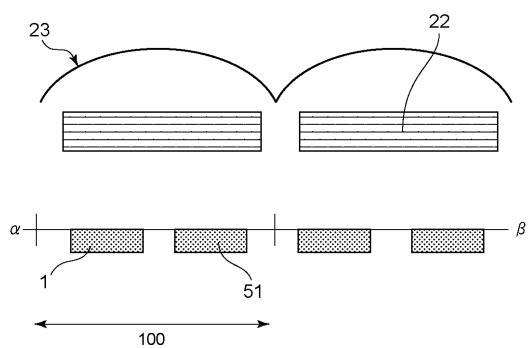

図1は本実施例に関する撮像装置の俯瞰図と、画素からの信号を読み出す回路構成を模式的に例示した図である。画素100は、第1の光電変換部である第1のフォトダイオード1、第2の光電変換部である第2のフォトダイオード51、フォトダイオード1、51に電気的に接続された画素内読み出し回路部3を有する。画素100は複数行、複数列に渡って配されている。即ち、画素100は行列状に配されている。この行列状に画素100が配された領域が画素部である。また、1つの画素100が有するフォトダイオード1とフォトダイオード51とをまとめて表す際は、受光部と表記する。入射光を受光部に導くための1つのマイクロレンズ23が、1つの受光部を覆うように配されている。つまり、1つのマイクロレンズは1つの受光部に対応して設けられており、対応する画素100の複数の光電変換部に入射光を導く。本実施例の撮像装置は、複数のマイクロレンズ23を有するマイクロレンズアレイを有する。フォトダイオードの面積は、例えばフォトダイオード1の面積は図1において示した  $a \times b$  で表される面積である。フォトダイオード51についても同様に、図1に示した  $c \times d$  で表される面積である。また、この  $a \times b$  で表される面積を有する面がフォトダイオード1の受光面である。同様に、 $c \times d$  で表される面積を有する面がフォトダイオード51の受光面である。 40

【0012】

50

画素 100 は、垂直走査回路 2 によって行ごとに順次走査される。垂直走査回路 2 が選択した行に属する画素 100 から、画素信号が垂直信号線 7 に出力される。垂直信号線 7 は、画素 100 から出力された画素信号を信号処理回路 101 に伝送する。信号処理回路 101 は画素 100 から出力される画素信号を処理する回路である。また、信号処理回路 101 は、画素 100 が output するアナログ信号をデジタル信号に変換するアナログデジタル変換部を含む。信号処理回路 101 は、水平走査回路 14 によって、列ごとに順次走査される。図 1 では、画素 100 におけるフォトダイオード 1、51 は、各列の信号処理回路 101 が並ぶ方向に沿って並んで配されている。即ち、画素 100 の内部には 2 列のフォトダイオード 1、51 が配されていると言え換えることができる。画素内信号読み出し回路 3 は、フォトダイオード 1、51 で生成した信号電荷に基づく信号を垂直信号線 7 に出力する。画素内信号読み出し回路 3 は後述する転送 MOS トランジスタ 20、50、リセット MOS トランジスタ 4、増幅 MOS トランジスタ 5、選択 MOS トランジスタ 6 を含んで構成される。

#### 【0013】

次に、図 2 に、図 1 で - の直線で示した部分の画素 100 の断面を示す。カラーフィルター 22 はマイクロレンズ 23 とフォトダイオード 1、51 との間に設けられている。

#### 【0014】

本実施例の撮像装置に設けられた画素は、位相差検出方式による焦点検出のための焦点検出用信号の基となる信号と、撮像のための信号である画像取得用信号の基となる信号を出力する。例えば、画素部のうちの、ライン状またはクロス状の位置にある複数の画素から焦点検出用信号の基となる信号が出力される。撮像装置は、画素から出力される焦点検出用信号の基となる信号と画像取得用信号の基となる信号を処理して焦点検出用信号、画像取得用信号を出力する。撮像装置から出力された焦点検出用信号に基づいて、2 つの光電変換部に対する入射光の位相差を検出することができる。この検出された位相差に基づいて焦点検出を行うことができる。

#### 【0015】

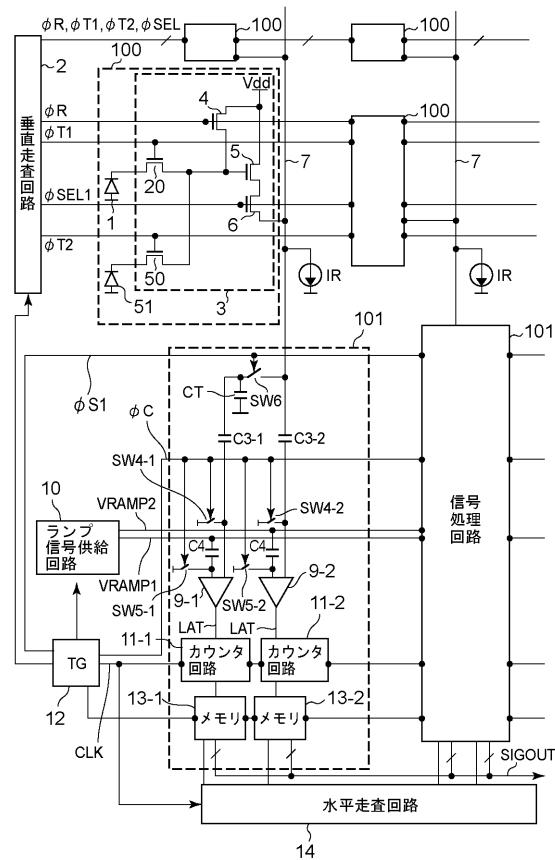

図 3 は本実施例の撮像装置のうち、2 行 2 列の画素 100 と、2 列の信号処理回路 101 を抜き出して模式的に表したブロック図である。

#### 【0016】

まず、画素 100 について説明する。

#### 【0017】

画素 100 は転送 MOS トランジスタ 20、50、リセット MOS トランジスタ 4、増幅 MOS トランジスタ 5、選択 MOS トランジスタ 6 を有している。フォトダイオード 1、51 では光が入射すると、光電変換により信号電荷が生じる。転送 MOS トランジスタ 20 はフォトダイオード 1 と増幅 MOS トランジスタ 5 の入力ノードに電気的に接続されている。また、転送 MOS トランジスタ 50 は、フォトダイオード 51 と増幅 MOS トランジスタ 5 の入力ノードに電気的に接続されている。転送 MOS トランジスタ 20 のゲートに、後述する垂直走査回路から供給される転送パルス T1 を High レベル（以降、H レベルと表記する。同様に、Low レベルを L レベルと表記する。）とすると、フォトダイオード 1 の信号電荷が増幅 MOS トランジスタ 5 の入力ノードに転送される。転送 MOS トランジスタ 50 のゲートに、同様に垂直走査回路 2 から供給される転送パルス T2 を H レベルとすると、フォトダイオード 51 の信号電荷が増幅 MOS トランジスタ 5 の入力ノードに伝送される。垂直走査回路 2 がリセット MOS トランジスタ 4 のゲートに供給するリセットパルス R を H レベルとすると、増幅 MOS トランジスタ 5 の入力ノードの電位がリセットされる。増幅 MOS トランジスタ 5 は選択 MOS トランジスタ 6 を介して垂直信号線 7 に電気的に接続されている。増幅 MOS トランジスタ 5 は、増幅 MOS トランジスタ 5 の入力ノードの信号電荷に基づいて、電気信号を出力する。選択 MOS トランジスタ 6 は選択パルス SEL1 が H レベルの時に増幅 MOS トランジスタ 5 から垂直信号線 7 への経路を導通させる。

10

20

30

40

50

## 【0018】

フォトダイオード1からの信号電荷が転送された増幅MOSトランジスタ5の入力ノードの電位に基づいて、垂直信号線7に出力される信号をA信号と表記する。また、フォトダイオード51からの信号電荷が転送された増幅MOSトランジスタ5の入力ノードの電位に基づいて、垂直信号線7に出力される信号をB信号と表記する。A信号およびB信号は焦点検出に用いられる焦点検出用信号の基となる信号である。A信号は画素100が出力する第1の光電変換信号である。また、転送パルスT1、T2を共にHレベルとするにより、フォトダイオード1、51のそれぞれに蓄積された信号電荷が増幅MOSトランジスタ5の入力ノードに転送される。この時の増幅MOSトランジスタ5の入力ノードの電位に基づいて垂直信号線7に出力される信号をA+B信号と表記する。A+B信号は、画像取得用信号の基となる信号であり、第2の光電変換信号である。本実施例では、B信号、すなわち、フォトダイオード51において光電変換を行って保持した信号電荷のみが増幅MOSトランジスタ5の入力ノードに転送されることで垂直信号線7に出力される信号については、画素100からの出力動作を行わない。B信号に相当する信号は、画像取得用信号と焦点検出用信号との差分処理を、後述するデジタル信号処理回路が行うことによって取得することができる。10

## 【0019】

本実施例では、相関二重サンプリング(以下、CDS(Correlated Double Sampling)と表記する。)を行うために、増幅MOSトランジスタ5の入力ノードの電位をリセットレベルにしたことによって増幅MOSトランジスタ5から選択MOSトランジスタ6を介して出力される信号であるN信号と、前述したA信号、A+B信号の3つの信号をサンプリングする。20

## 【0020】

本実施例における画素信号とは、画素100から出力されるN信号、A信号、A+B信号を含む、画素100から垂直信号線7に出力される信号の総称である。また、A信号、A+B信号は、入射した光によって受光部が生成した信号電荷に基づく光電変換信号である。また、N信号は画素100のノイズ成分を含むノイズ信号である。

## 【0021】

次に信号処理回路101について説明する。クランプ容量C3-1、C3-2はN信号を保持する容量である。容量CTは、スイッチSW6がオンの時に垂直信号線7に出力されている信号を保持する容量である。本実施例の場合ではA信号を保持する。30

## 【0022】

本実施例では画素100の1列に対し、比較器が比較器9-1、9-2の2つ設けられている形態である。比較器9-1、9-2には信号Vrefを含む信号が入力される。比較器9-1にはA+N信号からN信号が差し引かれ、信号Vrefを含むA+Vref信号が入力される。また、比較器9-2にはA+B+N信号からN信号が差し引かれ、信号Vrefを含むA+B+Vref信号が入力される。即ち、クランプ容量C3-1、C3-2を用いてCDSを行うことにより、A+N信号、A+B+N信号のそれぞれからN信号が差し引かれた信号が比較器9-1、9-2のそれぞれに与えられる。この比較器9-1、9-2にそれぞれ入力される信号を以下、A+Vref信号とA+B+Vref信号の信号Vrefを省略してA信号、A+B信号と表記する。比較器9-1はA信号と参照信号VRAMP1と、比較器9-2はA+B信号と参照信号VRAMP2とを比較する。参照信号VRAMP1、VRAMP2は参照信号供給回路10より各列に設けられた容量C4を介して比較器9-1、9-2に与えられる信号であり、時間に依存して電位が変化する信号である。比較器9-19-2の一の端子には、それぞれスイッチSW5-1、SW5-2を介して信号Vrefが与えられる。比較器9-1は、一の端子に与えられる、クランプ容量C3-1を介して画素100から入力される画素信号と、別の一の端子に与えられる参照信号VRAMP1との大小関係が逆転した時にラッチ信号LATをカウンタ回路11-1に出力する。また、比較器9-2は、一の端子に与えられる、クランプ容量C3-2を介して入力される画素信号と、別の一の端子に与えられる参照信号VRAMP40

2 参照信号との大小関係が逆転した時にラッチ信号 L A T をカウンタ回路 11 - 2 に出力する。この比較器 9 - 1、9 - 2 のそれぞれが出力するラッチ信号 L A T は、画素信号と参照信号とを比較した比較結果に基づく比較結果信号である。

【 0 0 2 3 】

カウンタ回路 11 - 1、11 - 2 は参照信号 V R A M P 1、V R A M P 2 が時間に依存した電位の変化を開始するのと同時に、タイミングジェネレータ（以下、T G と表記する）12 から与えられるクロックパルス信号 C L K のカウントを開始する。カウンタ回路 11 - 1、11 - 2 はクロックパルス信号 C L K をアップカウント、ダウンカウントするアップダウンカウンタを有している。カウンタ回路 11 - 1 は比較器 9 - 1 がラッチ信号 L A T を出力した時にクロックパルス信号 C L K のカウントを終了する。また、カウンタ回路 11 - 2 も同様に、比較器 9 - 2 がラッチ信号 L A T を出力した時にクロックパルス信号 C L K のカウントを終了する。このカウンタ回路 11 - 1、11 - 2 がクロックパルス信号をカウントした信号をカウント信号 C N T と表記する。

【 0 0 2 4 】

メモリ 13 - 1 はカウンタ回路 11 - 1 がクロックパルス信号 C L K をカウントしたカウント信号 C N T を保持する。また、メモリ 13 - 2 はカウンタ回路 11 - 2 がクロックパルス信号 C L K をカウントしたカウント信号 C N T を保持する。メモリ 13 - 1 が保持するカウント信号 C N T は A 信号に基づくデジタル信号である。このデジタル信号をデジタル A 信号と表記する。また、メモリ 13 - 2 が保持するカウント信号 C N T は A + B 信号に基づくデジタル信号である。このデジタル信号をデジタル A + B 信号と表記する。本実施例の第 1 のアナログデジタル変換部は、比較器 9 - 1、カウンタ回路 11 - 1、メモリ 13 - 1 を含む。また、本実施例の第 2 のアナログデジタル変換部は、比較器 9 - 2、カウンタ回路 11 - 2、メモリ 13 - 2 を含む。すなわち、信号処理回路 101 のそれぞれは複数のアナログデジタル変換部を有している。

【 0 0 2 5 】

水平走査回路 14 は T G 12 から与えられるクロックパルス信号 C L K に基づいて、各列のメモリ 13 を順次選択し、各列のメモリ 13 が保持したカウント信号 C N T の読み出しを行う。このメモリ 13 から出力されたカウント信号 C N T が撮像装置から出力される信号 S I G O U T である。

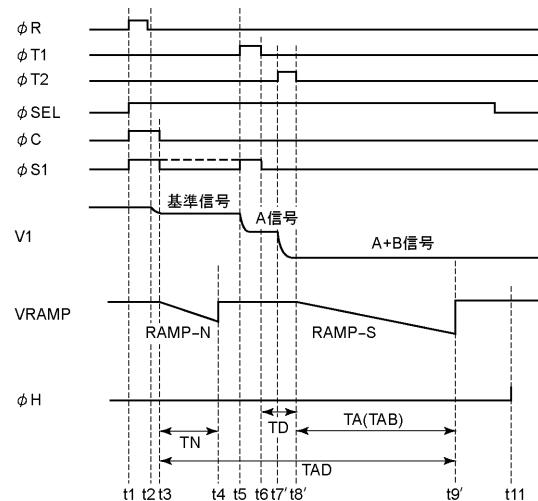

【 0 0 2 6 】

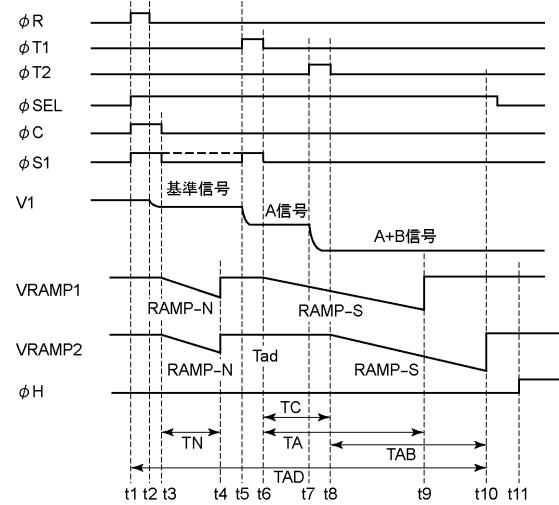

次に、図 4 を参照しながら、図 3 で例示した撮像装置の動作の一例について説明する。スイッチパルス S 1 はスイッチ S W 6 を制御するパルスであり、H レベルの時にスイッチ S W 6 は導通状態となる。信号処理回路リセットパルス C は、スイッチ S W 4 - 1、4 - 2、5 - 1、5 - 2 を制御するパルスである。信号処理回路リセットパルス C が H レベルの時にスイッチ S W 4 - 1、4 - 2、5 - 1、5 - 2 は導通状態となる。V 1 は垂直信号線 7 の電位を表している。

【 0 0 2 7 】

時刻 t 1 で画素リセットパルス R、選択パルス S E L、信号処理回路リセットパルス C、スイッチパルス S 1 をそれぞれ H レベルとする。そして、画素リセットパルス R を時刻 t 2 に L レベルとする。これにより、増幅 M O S ロジック 5 の入力ノードの電位がリセットされる。

【 0 0 2 8 】

時刻 t 3 において、信号処理回路リセットパルス C、スイッチパルス S 1 を L レベルとする。この時刻 t 3 において垂直信号線 7 に出力される信号が N 信号である。クランプ容量 C 3 - 1、C 3 - 2、容量 C T、容量 C 4 が時刻 t 3 の電位に基づく電荷を保持する。また、参照信号供給回路 10 は参照信号 V R A M P 1、V R A M P 2 の時間に依存した電位の変化を開始する。カウンタ回路 11 - 1、11 - 2 は、T G 12 から与えられるクロックパルス信号 C L K のカウントを開始する。この時、カウンタ回路 11 - 1、11 - 2 はダウンカウントを行う。比較器 9 - 1 は時刻 t 3 における電位に基づく電荷を保持したクランプ容量 C 3 - 1 を介して入力される信号と信号 V r e f とを含む基準信号と、

10

20

30

40

50

参照信号 V R A M P 1 とを比較する。また、比較器 9 - 2 は時刻 t 3 における電位に基づく電荷を保持したクランプ容量 C 3 - 2 を介して入力される信号と参照信号 V R A M P 2 とを比較する。比較器 9 - 1、9 - 2 のそれぞれは、比較する信号の大小関係が逆転した時にラッチ信号 L A T をそれぞれカウンタ回路 1 1 - 1、1 1 - 2 に出力する。

#### 【 0 0 2 9 】

時刻 t 4 に参照信号供給回路 1 0 は参照信号 V R A M P 1、V R A M P 2 の時間に依存した電位の変化を止める。この時刻 t 3 から時刻 t 4 の期間を N 変換期間 T N と表記する。また、時刻 t 3 から時刻 t 4 に行う動作を N 変換と表記する。

#### 【 0 0 3 0 】

時刻 t 5 において、転送パルス T 1、スイッチパルス S 1 を H レベルとする。これにより、垂直信号線 7 には画素 1 0 0 から A 信号が出力される。時刻 t 6 において、転送パルス T 1、スイッチパルス S 1 を L レベルとする。容量 C T は時刻 t 6 の時の垂直信号線 7 の電位の基づく電荷を保持する。すなわち画素 1 0 0 が出力した A 信号を保持する。

#### 【 0 0 3 1 】

比較器 9 - 1 には A 信号が供給されている。そして時刻 t 6 において、参照信号供給回路 1 0 は参照信号 V R A M P 1 の時間に依存した電位の変化を開始する。カウンタ回路 1 1 - 1 は、T G 1 2 から与えられるクロックパルス信号 C L K のカウントを開始する。この時、カウンタ回路 1 1 - 1 は先の N 変換時に保持したカウント信号値を出発値としてアップカウントを行う。比較器 9 - 1 は参照信号 V R A M P 1 と A 信号との大小関係が逆転した時にラッチ信号 L A T をカウンタ回路 1 1 - 1 に出力する。参照信号 V R A M P 1 の時間に依存した電位の変化は、参照信号 V R A M P 2 の時間に依存した電位の変化が開始する時刻 t 8 よりも後の時刻 t 9 に止める。この時刻 t 6 から時刻 t 9 の期間を A 変換期間 T A と表記する。比較器 9 - 1 は第 1 の比較器である。

#### 【 0 0 3 2 】

時刻 t 7 において転送パルス T 2 を H レベルとする。増幅 M O S トランジスタ 5 の入力ノードには先の時刻 t 6 の時の電位が保持されているため、垂直信号線 7 には A + B 信号が出力される。時刻 t 8 において、転送パルス T 2 を L レベルとする。

#### 【 0 0 3 3 】

比較器 9 - 2 には、A + B 信号が供給されている。そして時刻 t 8 において、参照信号供給回路 1 0 は参照信号 V R A M P 2 の時間に依存した電位の変化を開始する。カウンタ回路 1 1 - 2 は、T G 1 2 から与えられるクロックパルス信号 C L K のカウントを開始する。この時、カウンタ回路 1 1 - 2 は先の N 変換時に保持したカウント信号値を出発値としてアップカウントを行う。比較器 9 - 2 は参照信号 V R A M P 2 と A + B 信号との大小関係が逆転した時にラッチ信号 L A T をカウンタ回路 1 1 - 2 に出力する。

#### 【 0 0 3 4 】

時刻 t 1 0 において、参照信号 V R A M P 2 の時間に依存した電位の変化を止める。時刻 t 8 から時刻 t 1 0 の期間を A + B 変換期間 T A B と表記する。比較器 9 - 2 は第 2 の比較器である。

また時刻 t 1 から時刻 t 1 0 までの期間、すなわち画素 1 0 0 が画素信号を出力してからデジタル信号に変換するまでの期間を A D 変換期間 T A D と表記する。

#### 【 0 0 3 5 】

時刻 t 1 1 において、水平走査回路 1 4 は水平走査信号 H を H レベルとして、メモリ 1 3 - 1 が保持したデジタル N 信号、デジタル A 信号、メモリ 1 3 - 2 が保持したデジタル N 信号、デジタル A + B 信号をメモリ 1 3 - 1、1 3 - 2 のそれぞれから転送する。

#### 【 0 0 3 6 】

本実施例の撮像装置は、A 変換期間 T A の一部と A + B 変換期間 T A B の一部が重なっている。この A 変換期間 T A と A + B 変換期間 T A B とが重なっている期間が第 1 の期間である。即ち、第 1 の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第 1 の期間に行う第 1 のアナログデジタル変換部と、第 2 の光電変換信号をデジタル信号に

10

20

30

40

50

変換する動作の少なくとも一部を第1の期間に行う第2のアナログデジタル変換部を有している。また、A変換期間T<sub>A</sub>は第1の比較器が比較動作を行う第2の期間である。また、A+B変換期間T<sub>AB</sub>は第2の比較器が比較動作を行う第3の期間である。すなわち、第1の期間は、第2の期間と第3の期間とが重なる期間である。これにより、A変換期間T<sub>A</sub>とA+B変換期間T<sub>AB</sub>とに重なった期間が無い場合に比してA/D変換期間T<sub>AD</sub>を短くすることができる。

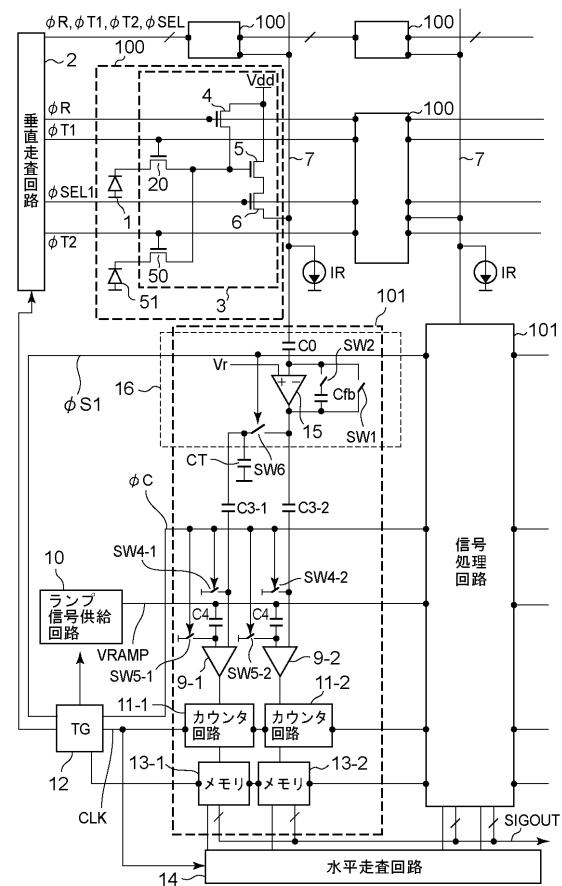

#### 【0037】

また、本実施例では、比較器9-1、9-2にそれぞれ別の参照信号VRAMP1、VRAMP2が供給される形態を説明した。しかし、比較器9-1、9-2に参照信号供給回路10から共通の参照信号VRAMPが供給される形態であっても良い。この形態の撮像装置の動作について例示したのが図5である。

10

#### 【0038】

図5の動作タイミングにおいて示した時刻t<sub>1</sub>から時刻t<sub>6</sub>のそれぞれの時刻における動作は、図3の動作タイミングにおいて示した時刻t<sub>1</sub>から時刻t<sub>6</sub>のそれぞれにおける動作と同様とすることができます。図5の動作タイミングにおいて示した時刻t<sub>7'</sub>において、転送パルスT<sub>2</sub>をHレベルとする。これにより、垂直信号線7にはA+B信号が出力される。時刻t<sub>8'</sub>において、転送パルスT<sub>2</sub>をLレベルとする。

#### 【0039】

時刻t<sub>8'</sub>において、参照信号供給回路10は参照信号VRAMPの時間に依存した電位の変化を開始する。カウンタ回路11-1、11-2は、TG12から与えられるクロックパルス信号CLKのカウントを開始する。この時、カウンタ回路11-1、11-2は先のN変換時に保持したカウント信号値を出発値としてアップカウントを行う。比較器9-1はA信号と参照信号VRAMPとを比較し、大小関係が逆転した時にラッチ信号LATをカウンタ回路11-1に出力する。また、比較器9-2はA+B信号と参照信号VRAMPとを比較し、大小関係が逆転した時にラッチ信号LATをカウンタ回路11-2に出力する。

20

#### 【0040】

時刻t<sub>9'</sub>において、参照信号供給回路10は参照信号VRAMPの時間に依存した電位の変化を止める。

30

#### 【0041】

図5で示した時刻t<sub>11</sub>における動作は図4で示した時刻t<sub>11</sub>における動作と同様とすることができます。

#### 【0042】

図4で示した動作タイミングではA変換期間T<sub>A</sub>の一部とA+B変換期間T<sub>AB</sub>の一部が重なっていた。図5で示した動作タイミングでは、A変換期間T<sub>A</sub>の全期間とA+B変換期間T<sub>AB</sub>の全期間とが重なっている形態である。この形態の第1の期間はA変換期間T<sub>A</sub>の全期間およびA+B変換期間T<sub>AB</sub>の全期間である。この形態では、A変換期間T<sub>A</sub>の始まりとA+B変換期間T<sub>AB</sub>の終わりまでの期間が図4の動作タイミングに対し図5の動作タイミングでは図4で示した期間TCの分短縮できる。この図4で示した期間TCは、A変換期間T<sub>A</sub>の始まりである時刻t<sub>6</sub>からA+B変換期間T<sub>AB</sub>の始まりである時刻t<sub>8</sub>までの期間である。一方で、図4ではA変換期間T<sub>A</sub>の始まりは時刻t<sub>6</sub>であったのに対し、図5で示した動作タイミングではA変換期間T<sub>A</sub>（A+B変換期間T<sub>AB</sub>でもある）、時刻t<sub>6</sub>よりも遅い時刻t<sub>8'</sub>である。即ち、図5で示した期間TDの分だけ、図5で示した動作タイミングでは図4で示した動作タイミングに対し、A変換期間T<sub>A</sub>の始まりが遅くなる。従って、図5で示した動作タイミングのA/D変換期間T<sub>AD</sub>は図4で示した動作タイミングのA/D変換期間T<sub>AD</sub>に対し、T期間TCと期間TDの差分であるTC-TDの期間分短縮することができる。

40

#### 【0043】

また、本実施例の撮像装置では、A信号を保持する容量として容量CTを有していたが

50

、容量 C T が設けられていない形態であってもよい。この形態では、時刻  $t_6$  のスイッチ SW 6 のオフ後もスイッチ SW 6 から比較器 9 - 1 の入力端子の電気的経路において時刻  $t_6$  における電位が保持されるため、比較器 9 - 1 の入力端子に A 信号が与えられる。よって、容量 C T が設けられていなくとも、実施することができる。ただし本実施例の撮像装置では、容量 C T を有することにより、スイッチ SW 6 のオン、オフ動作に伴ってスイッチ SW 6 から比較器 9 - 1 に至る電気的経路の電位が不安定になるのを抑制できる効果を有する。

#### 【 0 0 4 4 】

また、本実施例ではスイッチパルス S 1 が時刻  $t_3$  で L レベルとなった後、時刻  $t_4$  で H レベルとしていた。他の形態として、図 4、図 5 の動作タイミング図において破線で示した通り、時刻  $t_1$  で H レベルとした後、時刻  $t_3$  で L レベルにはせず、時刻  $t_6$  で L レベルとする形態であっても良い。

10

#### 【 0 0 4 5 】

また、本実施例では、画素 1 0 0 が 2 個の光電変換部の信号電荷に基づく光電変換信号である A + B 信号と、1 個の光電変換部に基づく光電変換信号である A 信号とを出力する形態を基に説明した。本実施例はこの形態に限定されるものではない。つまり、複数の画素の各々が有する  $m$  個 ( $m$  は自然数) の光電変換部で生成した信号電荷に基づく第 1 の光電変換信号を画素が output する。そして、この第 1 の光電変換信号を出力した複数の画素が、 $m$  個の光電変換部を含み、 $m$  個よりも多い  $n$  個 ( $n$  は自然数) の光電変換部に基づいた第 2 の光電変換信号をさらに出力する形態であれば好適に実施することができる。

20

#### 【 0 0 4 6 】

また、本実施例では、1 つの画素に対応して 1 つのマイクロレンズが設けられ、焦点検出を行うことのできる撮像装置を例に説明したが、本実施例はこの焦点検出を行うことのできる撮像装置に限られるものではない。つまり、フォトダイオード 1、フォトダイオード 5 1 に対して異なるマイクロレンズが配されている形態であっても好適に実施することができる。

#### 【 0 0 4 7 】

本実施例の画素 1 0 0 は、入射光を受け、入射光に基づいて信号電荷を生成するフォトダイオードを複数有し、複数のフォトダイオードの信号電荷に基づく光電変換信号を複数回出力する形態であれば良い。複数回出力される光電変換信号とは、本実施例において説明した構成においては A 信号、B 信号、A + B 信号である。さらに多くのフォトダイオードを有する画素 1 0 0 であれば、さらに多くの種類の光電変換信号が出力されうる。そして撮像装置は、画素 1 0 0 が output する複数の光電変換信号のうち第 1 の光電変換信号が第 1 の比較器に入力され、複数の光電変換信号のうち第 2 の光電変換信号が第 2 の比較器に入力される形態であれば良い。この形態において、第 1 の比較器が第 1 の光電変換信号と参照信号とを比較する少なくとも一部の動作と、第 2 の比較器が第 2 の光電変換信号と参照信号とを比較する少なくとも一部の動作とが第 1 の期間に行われれば良い。これにより、第 2 の期間と第 3 の期間とが全く重なっていない形態に比して、A D 変換期間 T A D を短縮できる効果を有する。

30

#### 【 0 0 4 8 】

また、本実施例では、時間に依存して電位が変化する参照信号と光電変換信号とを比較する、いわゆるランプ型の A D 変換を例に説明したが、本実施例は他の形式の A D 変換であっても好適に実施することができる。すなわち、第 1 のアナログデジタル変換部が第 1 の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第 1 の期間に行い、第 2 のアナログデジタル変換部が第 2 の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第 1 の期間に行う形態であれば良い。

40

#### 【 0 0 4 9 】

本実施例の撮像装置は、画素 1 0 0 が A + N 信号と A + B + N 信号を出力する第 1 のモードと、A + N 信号を出力せず、A + B + N 信号を出力する第 2 のモードで動作することができる。第 1 のモードでは、図 4 あるいは図 5 を参照しながら説明した動作タイミング

50

に基づいて動作させればよい。第2のモードでは、少なくとも比較器9-1, 9-2のいずれか一方がA+B信号のA/D変換を行えばよい。例えば、第1のモードでは焦点検出動作を行いながら画像を得る動作を行うため、動画撮影に好適である。また、第2のモードは静止画を撮影するのに好適である。

#### 【0050】

以上述べた通り、本実施例の撮像装置は、第2の期間の少なくとも一部と第3の期間の少なくとも一部が重なっている。これにより、第2の期間と第3の期間とに重なった期間が無い場合に比してA/D変換期間TADを短くすることができる効果を有する。

#### 【0051】

##### [実施例2]

10

以下、図面を参照しながら本実施例の撮像装置について、実施例1と異なる点を中心に説明する。

#### 【0052】

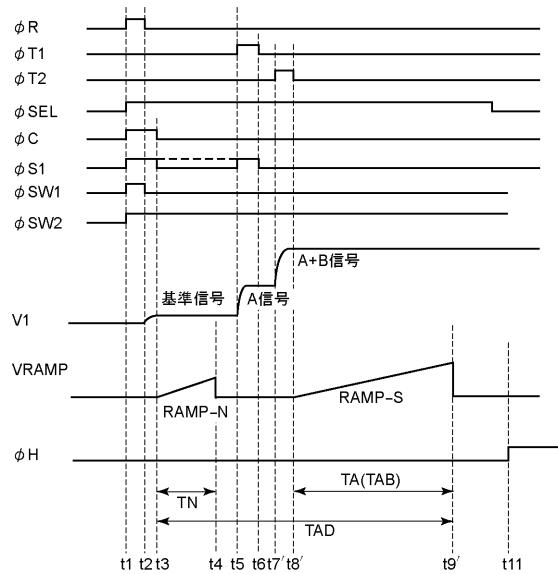

図6は本実施例の撮像装置の等価回路図の一例である。図6のそれぞれで例示した各部材は、図3と同じ機能を持つものについて図3と同じ符号を付して表している。

#### 【0053】

本実施例の撮像装置は、画素100が配された各列にオペアンプ15を含む反転増幅回路16を有する点で実施例1の撮像装置と異なる。反転増幅回路16は、オペアンプ15、帰還容量Cfb、クランプ容量C0、スイッチSW1、SW2を有している。オペアンプ15の反転入力端子には、クランプ容量C0を介して画素100が出力する画素信号が与えられる。オペアンプ15の非反転入力端子には、信号Vrが与えられる。オペアンプ15の帰還経路には帰還容量CfbとスイッチSW2とが設けられている。スイッチSW2がオンの時、帰還容量Cfbの容量値とクランプ容量C0の容量値との比による反転ゲインがオペアンプ15の出力端子に発生する。また、スイッチSW1をオンとしてオペアンプ15の出力端子と入力端子をショートさせることにより、帰還容量Cfbに保持された電荷がリセットされる。帰還容量Cfbは図6では1つとして示しているが、複数の容量がオペアンプ15の帰還経路に並列して設けられ、使用する帰還容量を複数の容量から選択できる構成であっても良い。オペアンプ15が出力した信号は、スイッチSW6がオンの時には容量CTに保持され、さらに比較器9-1の入力端子に出力される。また、オペアンプ15が出力した信号は、クランプ容量C3-2を介して比較器9-2に出力される。

20

#### 【0054】

次に図7を参照しながら、図6で例示した撮像装置の動作の一例について説明する。

#### 【0055】

図7に示したV1'はオペアンプ15の出力端子の電位を表している。本実施例では、画素信号が反転増幅回路16によって反転増幅されて比較器9-1、9-2に出力される。従って、本実施例の電位V1'は、実施例1の電位V1に対し、信号の極性が逆となる。同様に、参照信号VRAMPが時間に依存して電位が変化する方向についても実施例1とは逆の方向である。

30

#### 【0056】

時刻t1で、スイッチパルスSW1、SW2をHレベルとし、スイッチSW1、SW2を導通させる。

40

#### 【0057】

時刻t2において、リセットパルスR、スイッチパルスSW1をLレベルとする。スイッチパルスSW1をLレベルとすることで、画素100が出力するN信号が容量C0に保持される。これにより、オペアンプ15の出力端子にはオペアンプ15のオフセット成分を含む基準信号が出力される。

#### 【0058】

時刻t3に、信号処理回路リセットパルスCをLレベルとする。これにより、オペアンプ15のオフセット成分を含む基準信号がクランプ容量C3-1、C3-2のそれぞれ

50

に保持される。

【0059】

時刻  $t_3$  から時刻  $t_4$  の期間に比較器 9-1、9-2 はオペアンプ 15 からクランプ容量  $C_{3-1}$ 、 $C_{3-2}$  を介して入力された信号と参照信号  $V_{RAMP}$  との比較を行う。

【0060】

時刻  $t_8'$  から時刻  $t_9'$  の期間においても、比較器 9-1、9-2 はオペアンプ 15 からクランプ容量  $C_{3-1}$ 、 $C_{3-2}$  を介して入力された信号と参照信号  $V_{RAMP}$  との比較を行う。

【0061】

これらの点を除き、図 7 に例示した動作タイミングは実施例 1 で述べた図 5 の動作タイミングと同様とすることができる。 10

【0062】

本実施例のクランプ容量  $C_{3-1}$ 、 $C_{3-2}$  は、時刻  $t_3$  においてオペアンプ 15 のオフセット成分を含む基準信号を保持する。このオフセット成分を含む基準信号をクランプ容量  $C_{3-1}$ 、 $C_{3-2}$  が保持することにより、時刻  $t_6$ 、時刻  $t_8'$  に比較器 9-1、9-2 に与えられる信号は、基準信号を差し引いた信号とすることができます。よって、各列のオペアンプ 15 のオフセット成分のばらつきによって生じる画質の低下を低減することができる。

【0063】

また、N 変換を比較器 9-1、9-2 のそれぞれが行い、S 変換で得たデジタル信号から差し引くことで、比較器毎の動作のばらつきによって生じる画質の低下を低減することができる。 20

本実施例の撮像装置は実施例 1 で述べた撮像装置と同様に、A 変換期間  $T_A$  と  $A + B$  変換期間  $T_{AB}$  とが重なっている。これにより、A 変換期間  $T_A$  と  $A + B$  変換期間  $T_{AB}$  とに重なった期間が無い場合に比して A/D 変換期間  $T_{AD}$  を短くすることができる効果を有する。

【0064】

本実施例は、図 3 で例示した撮像装置のように、比較器 9-1、9-2 に参照信号  $V_{RAMP1}$ 、 $V_{RAMP2}$  が別々に与えられる形態であっても良い。この形態であっても、実施例 1 の図 4 に例示した動作タイミング図と同様にして動作させることができる。この形態では A 変換期間  $T_A$  の少なくとも一部と  $A + B$  変換期間  $T_{AB}$  の少なくとも一部が重なっている。これにより、A 変換期間  $T_A$  と  $A + B$  変換期間  $T_{AB}$  とに重なった期間が無い場合に比して A/D 変換期間  $T_{AD}$  を短くすることができる効果を有する。 30

【0065】

また、本実施例においてもスイッチパルス  $S_1$  は図 7 の動作タイミング図において破線で示した通り、時刻  $t_1$  で H レベルとした後、時刻  $t_3$  で L レベルにはせず、時刻  $t_6$  で L レベルとする形態であっても良い。

【0066】

[実施例 3]

以下、図面を参照しながら本実施例の撮像装置について実施例 2 と異なる点を中心に説明する。 40

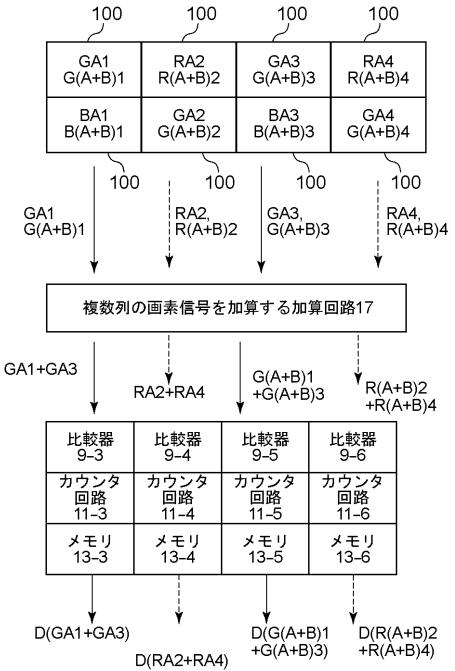

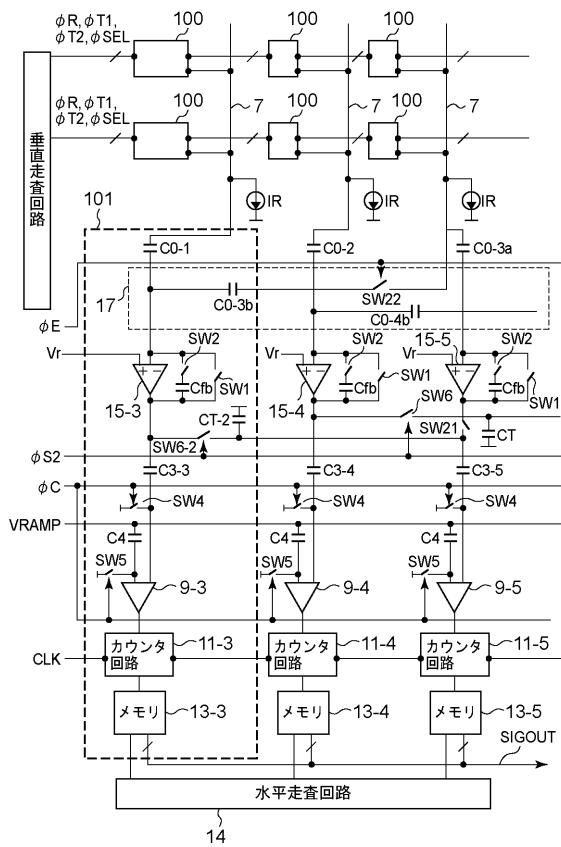

【0067】

図 8 は本実施例の撮像装置を模式的に表したブロック図である。図 8 は複数行複数列配された画素 100 のうち、2 行 4 列の画素 100 を抜き出して示すとともに、1 行目の画素 100 から画素信号が output される場合を示したものである。それぞれの画素 100 は実施例 1 で図 2 を参照しながら説明した通り、カラーフィルターを有している。カラーフィルターは赤 (R)、緑 (G)、青 (B) の三色である。この三色のカラーフィルターはベイア配列で配されている。図 8 では、画素 100 が output する画素信号についてカラーフィルターの色、出力する光電変換信号 (A 信号、 $A + B$  信号)、画素が配された列 (図 8 の左から数えた列) である。特に断りのない限り、本明細書において X 列目と記載した場合 50

には左から数えた列を指す。)を用いて表している。例えば、1行目1列目に配された画素100から出力されるA信号、A+B信号はそれぞれ、GA1、G(A+B)1として表記している。これは緑(G)のカラーフィルターを有する画素100が出力する、A信号もしくはA+B信号であって、図8で示した画素列の左から数えて1列目の画素100から出力される画素信号であることを示している。

#### 【0068】

1行目の画素100から加算回路17に画素信号が出力される。加算回路17は同色のカラーフィルターを有する複数の画素100のA信号同士とA+B信号同士を加算する。すなわち、複数の画素100の出力する第1の光電変換信号同士、第2の光電変換信号同士で加算する。同じ緑のカラーフィルターを有する画素100では、1列目と3列目の画素100のA信号同士、A+B信号同士を加算し、加算して得た2つの信号を別々の比較器に出力する。すなわち、信号GA1と信号GA3とを加算した信号GA1+GA3を比較器9-3に出力する。また、信号G(A+B)1と信号G(A+B)3とを加算した信号G(A+B)1+G(A+B)3を比較器9-5に出力する。比較器9-3に出力された信号GA1+GA3は実施例1の図5を参照しながら説明したAD変換動作によりデジタル信号に変換されてメモリ13-3から出力される。メモリ13-3から出力されるデジタル信号をD(GA1+GA3)と表記する。同様に、比較器9-5に入力された信号G(A+B)1+G(A+B)3はAD変換動作によりデジタル信号に変換されてメモリ13-5から出力される。このデジタル信号をD(G(A+B)1+G(A+B)3)と表記する。

10

#### 【0069】

これまで緑のカラーフィルターを有する1列目、3列目の画素100から出力された画素信号について述べた。赤のカラーフィルターを有する2列目、4列目の画素100から出力される画素信号についても同様にしてメモリ13-4からデジタル信号D(RA2+RA4)、メモリ13-6からデジタル信号D(R(A+B)2+R(A+B)4)がそれぞれ出力される。

20

#### 【0070】

図9は、図8のブロック図で模式的に示した撮像装置の詳細を示した等価回路図である。図9では図8で示した2行4列の画素100のうち、2行3列の画素100について示している。図9のそれぞれで例示した各部材は、図5と同じ機能を持つものについて図5と同じ符号を付して表している。

30

#### 【0071】

以下、実施例2の図6と異なる点を中心に1列目、3列目の画素100、信号処理回路101について説明する。2列目および不図示の4列目の画素100、信号処理回路101についてはそれぞれ、1列目、3列目の画素100、信号処理回路101と同様とすることができる。実施例1、2では画素100の1列に対し比較器が2つ配されている形態であったが、本実施例では画素100の1列に対し、比較器が1つ設けられている形態である。

#### 【0072】

1列目の画素100から出力される画素100はクランプ容量C0-1を介してオペアンプ15-3の反転入力端子に電気的に接続されている。また、3列目の画素100はスイッチSW22、クランプ容量C0-3bを介してオペアンプ15-3に電気的に接続されている。さらに、3列目の画素100はクランプ容量C0-3aを介してオペアンプ15-5に電気的に接続されている。ただし、本実施例の形態では、スイッチSW21をオフとし、比較器9-5にはオペアンプ15-5が出力する信号は供給されない場合を説明する。スイッチSW21の動作を制御する信号は、図示を省略した。

40

#### 【0073】

オペアンプ15-3から出力された信号は、クランプ容量C3-3を介して比較器9-3に与えられる。クランプ容量C3-3は実施例2の図6を参照しながら説明したクランプ容量C3-1と同様に動作する。また、スイッチSW6-2がオンの時には、オペアン

50

プ 15 - 3 から出力された信号はスイッチ SW 6 - 2 を介して容量 CT - 2 に保持されるとともに、クランプ容量 C 3 - 5 を介して比較器 9 - 5 に与えられる。

【0074】

例えば、1列目の画素 100 が出力した光電変換信号は第1のアナログデジタル変換部と第2のアナログデジタル変換部に与えられる。この第1のアナログデジタル変換部は、比較器 9 - 3、カウンタ回路 11 - 3、メモリ 13 - 3 を含む。また、第2のアナログデジタル変換部は、比較器 9 - 5、カウンタ回路 11 - 5、メモリ 13 - 5 を含む。

【0075】

次に図10を参照しながら、図9で例示した撮像装置の動作について、実施例2の図7と異なる点を中心に説明する。

10

【0076】

スイッチパルス E はスイッチ SW 2 2 を制御するパルスであり、H レベルの時にスイッチ SW 2 2 は導通状態となる。スイッチパルス S 2 はスイッチ SW 6 - 2 を制御するパルスであり、H レベルの時にスイッチ SW 6 - 2 は導通状態となる。

【0077】

時刻 t 1において、スイッチパルス E を H レベルとする。他の時刻 t 1 から時刻 t 1 1 までの動作は、実施例2で述べた図7における時刻 t 1 から時刻 t 1 1 までのそれぞれの動作と同様とすることができる。以下、オペアンプ 15 - 3、比較器 9 - 3、9 - 5 のそれぞれに入力される信号およびそれが出力する信号について述べる。

【0078】

時刻 t 1 で、スイッチパルス SW 1、SW 2 を H レベルとし、スイッチ SW 1 を導通させる。

20

【0079】

時刻 t 2 において、リセットパルス R、スイッチパルス SW 1 を L レベルとする。スイッチパルス SW 1 を L レベルとすることで、1列目の画素 100 が出力する N 信号 (GN 1) が容量 C 0 - 1 に保持される。また、3列目の画素 100 が出力する N 信号 (GN 3) が容量 C 0 - 3 b に保持される。これにより、オペアンプ 15 - 3 の出力端子にはオペアンプ 15 - 3 のオフセット成分を含む基準信号が出力される。

【0080】

時刻 t 3 において、信号処理回路リセットパルス C を L レベルとする。これにより、オペアンプ 15 - 3 のオフセット成分を含む基準信号が容量 C 3 - 3、C 3 - 5 のそれぞれに保持される。また、時刻 t 3 においてスイッチパルス S 2 を L レベルとする。容量 CT - 2 には、時刻 t 3 におけるオペアンプ 15 - 3 が output したオフセット成分を含む基準信号が保持される。

30

【0081】

時刻 t 3 から時刻 t 4 の期間に比較器 9 - 3、9 - 5 はオペアンプ 15 - 3 からクランプ容量 C 3 - 3、C 3 - 5 を介して入力された信号と参照信号 V R A M P との比較を行う。

【0082】

そして、参照信号供給回路 10 は参照信号 V R A M P の時間に依存した電位の変化を開始する。比較器 9 - 3、9 - 5 はそれぞれ、オペアンプ 15 - 3 が output する信号から基準信号が差し引かれた信号と参照信号 V R A M P との比較を行う。

40

【0083】

時刻 t 4 における動作は、実施例2で述べた図7における時刻 t 4 の動作と同様である。

【0084】

時刻 t 5 において、転送パルス T 1 とスイッチパルス S 2 を H レベルとする。これにより、画素 100 から信号 G A 1 と信号 G A 3 が垂直信号線 7 に出力される。スイッチ SW 2 2 はオンとなっているため、オペアンプ 15 - 3 には、信号 G A 1 と信号 G A 3 とを加算した信号 G A 1 + G A 3 から、クランプ容量 C 0 - 1、C 0 - 3 b に保持された信

50

号  $G_N 1 + G_N 3$  を差し引いた信号が与えられる。オペアンプ 15 - 3 から出力される信号は、スイッチ  $SW 6 - 2$  がオンであるため、容量  $CT - 2$ 、クランプ容量  $C3 - 5$  を介して比較器 9 - 5 に与えられる。

【0085】

時刻  $t_6$  において、転送パルス  $T_1$  とスイッチパルス  $S_2$  を L レベルとする。容量  $CT - 2$  に信号  $GA_1 + GA_3$  が保持される。

【0086】

時刻  $t_7'$  において、転送パルス  $T_2$  を H レベルとする。これにより、画素 100 から信号  $G(A + B)1$  と信号  $G(A + B)3$  が垂直信号線 7 に出力される。スイッチ  $SW 22$  はオンとなっているため、オペアンプ 15 - 3 には、信号  $G(A + B)1$  と信号  $G(A + B)3$  を加算した信号  $G(A + B)1 + G(A + B)3$  から、クランプ容量  $C0 - 1$ 、 $C0 - 3b$  に保持された信号  $G_N 1 + G_N 3$  を差し引いた信号が与えられる。オペアンプ 15 - 3 から出力される信号は、スイッチ  $SW 6 - 2$  はオフであるため、クランプ容量  $C3 - 3$  を介して比較器 9 - 3 に与えられる。

【0087】

時刻  $t_8'$  に転送パルス  $T_2$  を L レベルとする。そして、参照信号供給回路 10 は参照信号  $VRAMP$  の時間に依存した電位の変化を開始する。比較器 9 - 3 は、オペアンプ 15 - 3 からクランプ容量  $C3 - 3$  を介して出力された信号と参照信号  $VRAMP$  とを比較する。また、比較器 9 - 5 はオペアンプ 15 - 3 からクランプ容量  $C3 - 5$  を介して出力された信号と参照信号  $VRAMP$  とを比較する。

10

20

【0088】

時刻  $t_9'$  に参照信号供給回路 10 は参照信号  $VRAMP$  の時間に依存した電位の変化を終了する。メモリ 13 - 3 には、オペアンプ 15 - 3 からクランプ容量  $C3 - 3$  を介して比較器 9 - 3 に入力された信号に基づくデジタル信号が保持される。このデジタル信号は信号  $G(A + B)1 + G(A + B)3$  に基づくデジタル信号である。また、メモリ 13 - 5 には、オペアンプ 15 - 3 からクランプ容量  $C3 - 5$  を介して比較器 9 - 5 に入力された信号に基づくデジタル信号が保持される。このデジタル信号は信号  $GA_1 + GA_3$  に基づくデジタル信号である。

【0089】

これまで 1 列目と 3 列目の画素 100 に関する動作について述べた。2 列目と 4 列目の画素 100 についても、1 列目と 3 列目の画素 100 と同様の動作とすることができます。

30

【0090】

本実施例の撮像装置は実施例 2 で述べた撮像装置と同様に、A 変換期間  $TA$  と  $A + B$  変換期間  $TAB$  とが重なっている。これにより、A 変換期間  $TA$  と  $A + B$  変換期間  $TAB$  とに重なった期間が無い場合に比して A/D 変換期間  $TAD$  を短くすることができる効果を有する。

【0091】

本実施例は、図 3 で例示した撮像装置のように、比較器 9 - 3、9 - 5 に異なるランプ信号  $VRAMP 1$ 、 $VRAMP 2$  が別々に与えられる形態であっても良い。この形態であっても、実施例 1 の図 4 に例示した動作タイミング図と同様にして動作させることができる。この形態では A 変換期間  $TA$  の少なくとも一部と  $A + B$  変換期間  $TAB$  の少なくとも一部が重なっている。これにより、A 変換期間  $TA$  と  $A + B$  変換期間  $TAB$  とに重なった期間が無い場合に比して A/D 変換期間  $TAD$  を短くすることができる効果を有する。

40

また、N 変換を比較器 9 - 1、9 - 2 のそれぞれが行い、S 変換で得たデジタル信号から差し引くことで、比較器毎の動作のばらつきによって生じる画質の低下を低減することができる。

【0092】

また、本実施例においてもスイッチパルス  $S_2$  は図 7 の動作タイミング図において破線で示した通り、時刻  $t_1$  で H レベルとした後、時刻  $t_3$  で L レベルにはせず、時刻  $t_6$  で L レベルとする形態であっても良い。

50

## 【0093】

複数列の画素信号を加算する加算方式としては、アナログ信号で加算する方式とデジタル信号で加算する方式がある。本実施例はアナログ信号で加算する方式に関する。アナログ信号で加算する形態として、(1)複数の画素で増幅MOSトランジスタの入力ノードを共通に接続する形態、(2)画素が出力した信号を加算する形態がある。後者の形態の中でも、オペアンプの入力で加算する形態と比較器の入力で加算する形態がある。本実施例は、オペアンプの入力で加算する形態を基に説明した。本実施例ではアナログ信号で加算することにより、使用しないオペアンプ(本実施例においてはオペアンプ15-5)に對して供給する電流を低減する、あるいはゼロとすることで、撮像装置の消費電力を低減できる効果がある。比較器の入力で加算する加算回路を有する形態であっても、本実施例を好適に実施することができる。10

## 【0094】

また、本実施例では加算回路が、異なる信号線に出力された画素信号を加算する形態を説明した。他の形態として、画素100の1つの増幅MOSトランジスタ5の入力ノードに複数の画素100の光電変換部が接続されている形態であっても良い。これにより、複数の画素100の光電変換部が生成した信号電荷に基づく画素信号が出力される。この複数の画素100の光電変換部が生成した信号電荷に基づく信号は本実施例で述べたように、複数の画素100の各々が出力する画素信号を加算した信号に相当する。

## 【0095】

本実施例では加算回路が複数の画素100が出力する画素信号を加算する形態を基に説明した。本実施例の撮像装置は複数の画素100が出力する画素信号を加算せずに比較器9に与えるモードをさらに有していても良い。すなわち、それぞれの列に配された画素100の出力する画素信号が、比較器9のそれぞれに与えられるモードをさらに有していても良い。このような形態の一例として、図8の撮像装置では、1列目の画素が出力する画素信号は比較器9-3、2列目の画素が出力する画素信号は比較器9-4のそれぞれに出力される形態がある。別の一例として、1列目の画素が出力する画素信号は比較器9-5、2列目の画素が出力する画素信号は比較器9-6のそれぞれに出力される形態がある。すなわち撮像装置が、複数の画素が第1の光電変換信号であるA信号を第1のアナログデジタル変換部に、第2の光電変換信号であるA+B信号を第2のアナログデジタル変換部にそれぞれ出力する第1のモードと、複数の画素がA信号を出力せず、A+B信号を第1のアナログデジタル変換部と第2のアナログデジタル変換部との少なくとも一方に出力する第2のモードとで動作する形態であっても良い。第1のモードでは、第1のアナログデジタル変換部が第1の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行い、第2のアナログデジタル変換部が第2の光電変換信号をデジタル信号に変換する動作の少なくとも一部を第1の期間に行う。第2のモードでは、A+B信号が与えられた前記第1のアナログデジタル変換部と前記第2のアナログデジタル変換部との少なくとも一方がA+B信号をデジタル信号に変換する動作を行う。この形態であっても、第1のモードでA変換期間TAの少なくとも一部とA+B変換期間TABの少なくとも一部とが重なっていることにより、A変換期間TAとA+B変換期間TABとに重なった期間が無い場合に比してA/D変換期間TABを短くすることができる効果を有する。第1のモード、第2のモードを有することにより、例えば第1のモードでは焦点検出動作を行なうながらの動画撮影、第2のモードでは静止画撮影あるいは焦点検出動作を行わない動画撮影といったように、用途に応じてモードを使い分けることが可能である。3040

## 【0096】

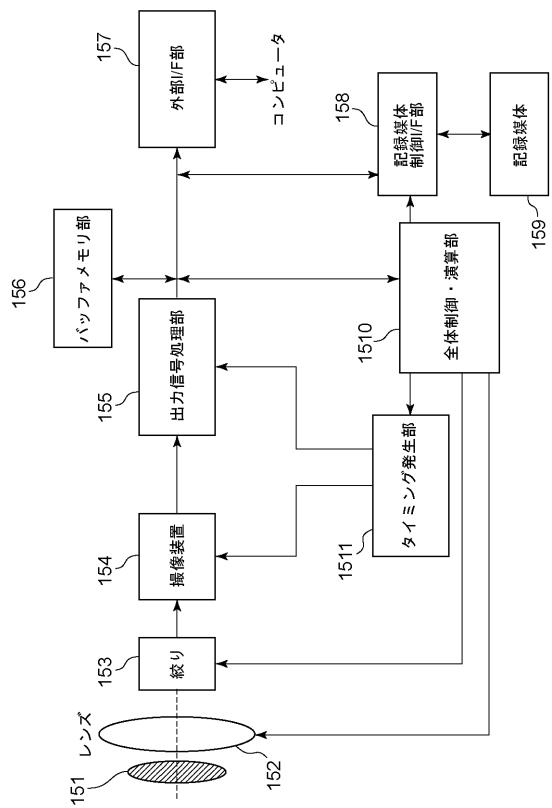

## [実施例4]

実施例1で述べた撮像装置を撮像システムに適用した場合の実施例について述べる。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図11に、撮像システムの例としてデジタルスチルカメラに撮像装置を適用した場合の模式図を示す。

## 【0097】

10

20

30

40

50

図11に例示した撮像システムは、レンズの保護のためのバリア151、被写体の光学像を撮像装置154に結像させるレンズ152、レンズ152を通過する光量を可変にするための絞り153を有する。レンズ152、絞り153は撮像装置154に光を集光する光学系である。また、図11に例示した撮像システムは撮像装置154より出力される出力信号の処理を行う出力信号処理部155を有する。

【0098】

出力信号処理部155はデジタル信号処理部を有し、撮像装置154から出力されるデジタルA信号、デジタルA+B信号のそれぞれからデジタルN信号を差し引く差分処理を行う。また、出力信号処理部155は同一画素のA+B信号とA信号とのそれぞれに基づく、デジタルA+B信号とデジタルA信号とを差し引いて差分信号を得る差分処理を行う。この差分信号がデジタルB信号である。また、出力信号処理部155はその他、必要に応じて各種の補正、圧縮を行って信号を出力する動作を行う。

10

【0099】

図11に例示した撮像システムはさらに、画像データを一時的に記憶する為のバッファメモリ部156、外部コンピュータ等と通信する為の外部インターフェース部157を有する。さらに撮像システムは、撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体159、記録媒体159に記録または読み出しを行うための記録媒体制御インターフェース部158を有する。さらに固体撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510、撮像装置154と出力信号処理部155に各種タイミング信号を出力するタイミング供給部1511を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置154と、撮像装置154から出力された出力信号を処理する出力信号処理部155とを有すればよい。

20

【0100】

出力信号処理部155が行う、デジタルA+B信号からデジタルA信号を差し引く処理は、同じ画素から出力された信号同士で行われる。すなわち、画素100が出力したA信号に基づく焦点検出用信号と焦点検出用信号を出力した画素100が出力したA+B信号に基づく画像取得用信号とで差分処理が行われる。これにより、画素100のB信号に基づく信号が得られ、この信号とA信号に基づく信号との信号値を比較することにより、位相差検出方式の焦点検出が行われる。また、出力信号処理部155は、画像取得用信号であるデジタルA+B信号からデジタルN信号を差し引いた信号によって画像の形成を行う。

30

【0101】

以上のように、本実施例の撮像システムは、撮像装置154を適用して焦点検出動作、撮像動作を行うことが可能である。

【符号の説明】

【0102】

- 1、51 フォトダイオード

- 2 垂直走査回路

- 3 画素内信号読み出し回路

- 4 リセットMOSトランジスタ

- 5 増幅MOSトランジスタ

- 6 選択MOSトランジスタ

- 7 垂直信号線

- C T 容量

- C3-1, C3-2, C4 クランプ容量

- 14 水平走査回路

- 9-1, 9-2 比較器

- 10 参照信号供給回路

- 11-1, 11-2 カウンタ回路

40

50

1 2 T G

1 3 - 1、1 3 - 2 メモリ

1 0 0 画素

1 0 1 信号処理回路

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 1 1】

---

フロントページの続き

(72)発明者 古林 篤

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2001-083407(JP, A)

特開2010-109893(JP, A)

特開2011-035689(JP, A)

特開2005-347932(JP, A)

特開2006-080937(JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |             |   |             |

|--------|-------------|---|-------------|

| H 04 N | 5 / 3 0     | - | 5 / 3 7 8   |

| H 04 N | 5 / 2 2 2   | - | 5 / 2 5 7   |

| H 04 N | 9 / 0 4     | - | 9 / 1 1     |

| H 01 L | 2 1 / 3 3 9 |   |             |

| H 01 L | 2 7 / 1 4   | - | 2 7 / 1 4 8 |

| H 01 L | 2 9 / 7 6 2 |   |             |

| G 02 B | 7 / 2 8     | - | 7 / 4 0     |

| G 03 B | 3 / 0 0     | - | 3 / 1 2     |

| G 03 B | 1 3 / 3 0   | - | 1 3 / 3 6   |

| G 03 B | 2 1 / 5 3   |   |             |