(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5111758号

(P5111758)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月19日(2012.10.19)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/786 | (2006.01)    |

| HO 1 L 29/423 | (2006.01)    |

| HO 1 L 29/49  | (2006.01)    |

| HO 1 L 29/41  | (2006.01)    |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/58 |

|               | HO 1 L 29/44 |

|               | 6 1 7 K      |

|               | 6 1 6 T      |

|               | 6 1 8 C      |

|               | G            |

|               | P            |

請求項の数 8 (全 16 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-364933 (P2005-364933)  |

| (22) 出願日  | 平成17年12月19日 (2005.12.19)      |

| (65) 公開番号 | 特開2007-173307 (P2007-173307A) |

| (43) 公開日  | 平成19年7月5日 (2007.7.5)          |

| 審査請求日     | 平成20年12月12日 (2008.12.12)      |

|           |                                                                              |

|-----------|------------------------------------------------------------------------------|

| (73) 特許権者 | 501426046<br>エルジー ディスプレイ カンパニー リ<br>ミテッド<br>大韓民国 ソウル、ヨンドゥンポーク、ヨ<br>ウィーテロ 128 |

| (74) 代理人  | 100094112<br>弁理士 岡部 譲                                                        |

| (74) 代理人  | 100064447<br>弁理士 岡部 正夫                                                       |

| (74) 代理人  | 100085176<br>弁理士 加藤 伸晃                                                       |

| (74) 代理人  | 100096943<br>弁理士 白井 伸一                                                       |

| (74) 代理人  | 100101498<br>弁理士 越智 隆夫                                                       |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に配置された円形状のゲート電極開口部を有するゲート電極と、

前記ゲート電極上にゲート絶縁膜を介して配置された半導体層と、

前記半導体層上に配置されたソース及びドレイン電極を含み、

前記ソース電極が前記ゲート電極開口部の中央に配置され、前記ドレイン電極が前記ソ

ース電極を囲むように同心円状に配置され、

前記同心円状に配置されたソース及びドレイン電極間にチャネル領域を有し、

前記ゲート電極開口部の外径は前記中央に配置されたソース電極の外径より小さく、か

つ前記ゲート電極開口部の外径が前記ソース又はドレイン電極の外径内に納まるように配

置されて、

前記半導体層は、前記ゲート電極開口部に対応する半導体層開口部を有することを特徴

とする薄膜トランジスタ。

## 【請求項 2】

前記ゲート電極開口部は前記ソース又はドレイン電極に対して同軸上に配置されること

を特徴とする請求項 1 に記載の薄膜トランジスタ。

## 【請求項 3】

前記薄膜トランジスタの実効 C g s 面積 S' が、150  $\mu\text{m}^2$  以下であり、

チャネル幅 W 対チャネル長 L 比 (W / L) が、4.5 以上であり、

実効 C g s 面積 S' への充電能力指標 F が、50 以下である

ことを特徴とする請求項 1 に記載の薄膜トランジスタ。

【請求項 4】

前記実効  $C_g s$  面積  $S'$  は  $\times ((\text{ソース電極外径 } D + L) / 2) \times ((D + L) / 2)$  -  $\times (\text{ゲート電極開口径 } d / 2) \times (d / 2)$  なる式より、前記チャネル幅  $W$  対チャネル長  $L$  比  $(W / L)$  は  $\times (D / L + 1)$  なる式より、及び前記実効  $C_g s$  面積  $S'$  への充電能力指標  $F$  は  $S' \div (W / L)$  なる式より算出される

ことを特徴とする請求項 3 に記載の薄膜トランジスタ。

【請求項 5】

表示セルがマトリクス状に配置された表示装置であって、前記表示セルが請求項 1 に記載の薄膜トランジスタを含む

10

ことを特徴とする表示装置。

【請求項 6】

基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

前記ゲート電極をマスクとして、前記基板底部から背面露光を行い、円形状の遮光膜を有するフォトマスクを介して、前記フォトレジスト上部より正面露光を行うことにより前記フォトレジストを感光させる工程、

20

前記背面及び正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

前記半導体層上にソース電極がゲート電極開口部の中央に配置され、ドレイン電極がソース電極を囲むように同心円状にソース及びドレイン電極を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法。

【請求項 7】

前記フォトマスクの遮光膜は、前記ゲート電極に形成された前記ゲート電極開口部に対して同軸上に配置される

ことを特徴とする請求項 6 に記載の薄膜トランジスタの製造方法。

30

【請求項 8】

基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

中央部に円形開口を有する遮光膜が形成されたフォトマスクを介して、前記フォトレジスト上部より正面露光を行い前記フォトレジストを感光させる工程、

前記正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

40

前記半導体層上にソース電極がゲート電極開口部の中央に配置され、ドレイン電極がソース電極を囲むように同心円状にソース及びドレイン電極を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ (TFT) に関し、特に、ソース・ドレイン電極を同心円状に形成することによりリーク電流や寄生TFTに起因するオフ電流の低減を実現すると同時に、ゲート電極に開口部を設けることによってゲート・ソース電極間容量とオン電流を最

50

適化した薄膜トランジスタに関する。

【背景技術】

【0002】

液晶表示装置（LCD）、電界放出ディスプレイ（FED）及びエレクトロルミネセンス（EL）ディスプレイに代表される平面表示装置は、CRTを使ったTVに比べて軽量、薄型、そして低消費電力という特徴を有する。この特徴を生かしてこれら平面表示装置は各種分野で利用されるようになっているし、更なる進展が期待されている。

【0003】

液晶表示装置においては、画素ごとにスイッチ素子が設けられ、そのスイッチ素子制御によりそれぞれの画素が駆動される。このスイッチ素子として、薄膜トランジスタが用いられている。

10

【0004】

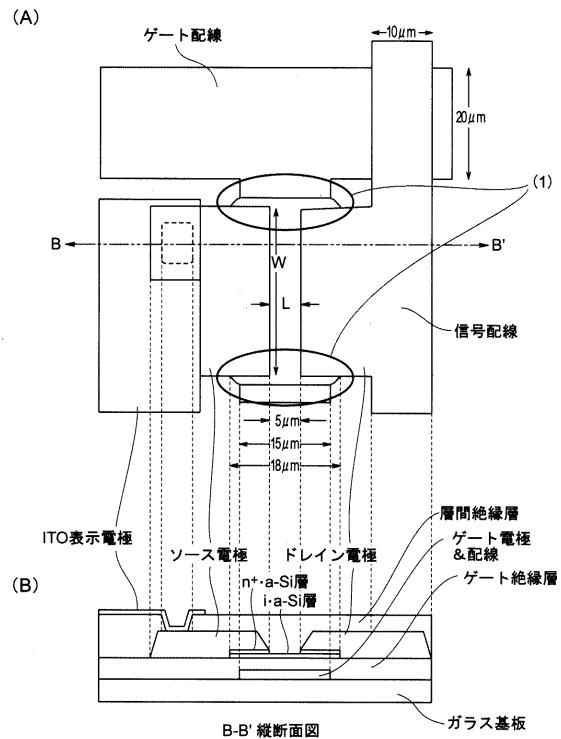

図1Aは、液晶表示装置に用いられる従来の非晶質シリコン半導体層を使った薄膜トランジスタの構成図、及び図1Bは、図1AのB-B'線に沿って切断された断面図を示す。このような従来の薄膜トランジスタにおいては、図1Aに示されるように、ソース・ドレイン電極からはみ出した「ゲート電極上の非晶質シリコン層端部（図中（1））」が必ず存在する。このような非晶質シリコン端部は精密な形状加工や清浄度制御が困難であり、これにより寄生TFTや汚染物質（例えば、レジスト残り、ドライエッチング残渣）付着による制御しがたいリーク電流が生じるという問題を有していた。このようなリーク電流は、素子ごとに増減し、リーク電流が大きいと、電荷の保持性能が悪くなり、画像にフリッカや残像が生じる。更に、画面内にリーク電流の大小ムラが生じると、画像に濃淡ムラが発生するという問題を有していた。

20

【0005】

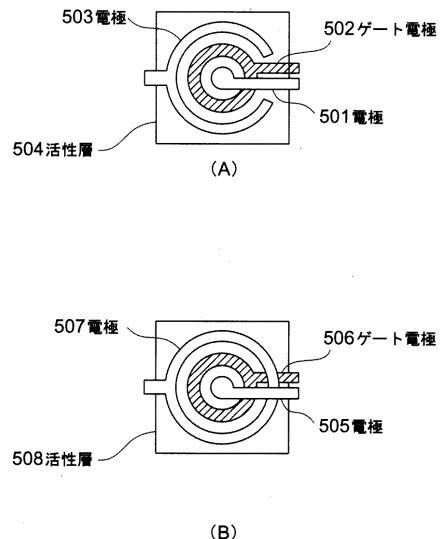

上記のようなリーク電流の問題に関しては、従来、薄膜トランジスタの電極構造を工夫してリーク電流の低減を図る種々の試みがなされている。例えば、特開2004-48036号公報は、リーク電流の少ない薄膜トランジスタを提案している。図2A及び2Bは、本公報における薄膜トランジスタの構成図である。これらの図に示されるように、半導体膜の活性層504には、TFTの電極が同心円状に配置されている。リング形状を有するゲート電極502, 506は、電極501, 505を囲むように配置されている。電極503, 507は、ゲート電極502, 506を囲むように形成されている。電極501, 505は、ゲート電極を構成する配線金属とは異なる層に配置され、電極501, 505と電極503, 507は、同一層に形成されている。電極501, 505と電極503, 507は、いずれか一方をソース電極とし、他方をドレイン電極とすることができます。このような構造によれば、上記従来技術において形成されるような非晶質シリコン層端部が生じない構造を形成することができ、その結果リーク電流の低減が図られている。

30

【0006】

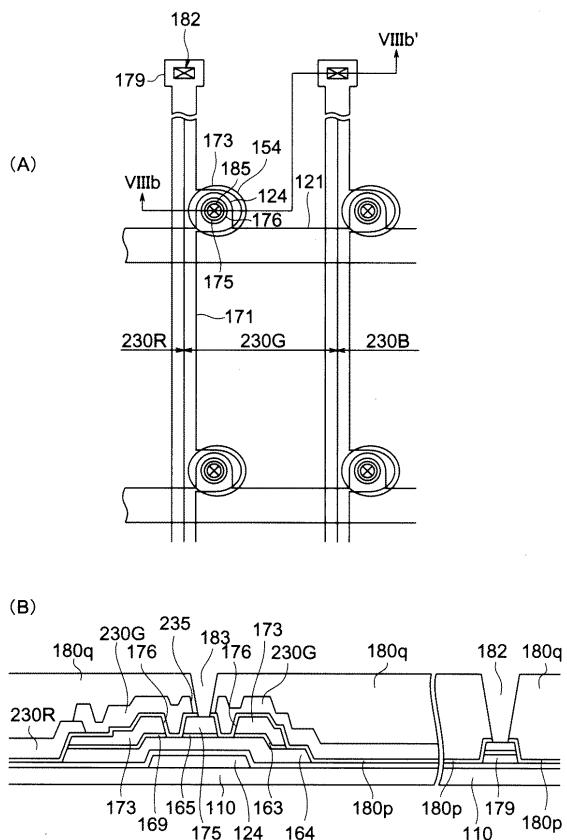

更に他の従来技術（韓国公開10-2005-0006340号公報）もまた、電極が同心円状に形成された薄膜トランジスタを提案している。図3Aは、表示パネル内に配置された本従来例の薄膜トランジスタの構成図を示す。図3Bは、図3Aのb-b'線に沿って切断された断面図を示す。基板110上にゲート電極124が配置され、その上にゲート絶縁層を介して真性非晶質シリコン（i・a-Si）層154が形成される。その上に円形の電極175が配置され、それを囲むように同一階層に電極176が配置される。電極175と電極176は、いずれか一方をソース電極とし、他方をドレイン電極とすることができます。このように、電極を円形に同心円状に形成することにより、i・a-Si層の端部を構造的になくすことができる。

40

【0007】

このように、従来技術においては非晶質シリコン層端部を形成しない構造を提案し、それによりリーク電流の低減が図られてきた。しかし、薄膜トランジスタには他に表示電極電位のレベルシフトの問題も存在する。レベルシフトはTFTのソース電極とゲート電極の重なりで形成される浮遊容量（以下「Cgs」という。）によって引き起こされる。レベル

50

シフト量はCgsに比例するが、フリッカや残像を視認できないレベルにするためにはCgsが小さいことが望ましく、また面内の分布が少ないと必须である。

上記従来技術では、リーク電流の低減が図られるとはいえ、表示電極電位のレベルシフトの問題についてはなんら提案や改善策が示されていない。したがって、レベルシフトの問題をリーク電流の低減と同時に解決する技術が望まれる。更に、大型液晶TVの本格的市場参入を実現するためにはHDTVに代表される画面の大型化＆高精細化が必須であり、これを実現するためにはTFTのオン電流を高めることが不可欠である。すなわちリーク電流の低減＆オン電流増大＆浮遊容量低減の3つを最適化することが必須になる。

【0008】

【特許文献1】特開2004-48036号公報

10

【特許文献2】韓国公開10-2005-0006340号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

そこで、本発明は、上記のようなリーク電流の低減を図ると同時に、表示電極電位のレベルシフトの問題を解決する。更に、薄膜トランジスタ画素回路における液晶駆動に適切なオン電流が供給できる薄膜トランジスタを提供する。

【課題を解決するための手段】

【0010】

本発明は、基板上に配置された円形状のゲート電極開口部を有するゲート電極と、

前記ゲート電極上にゲート絶縁膜を介して配置された半導体層と、

20

前記半導体層上に配置されたソース及びドレイン電極を含み、

前記ソース及びドレイン電極のいずれか一方が中央に配置され、他方がそれを囲むように同心円状に配置され、

前記同心円状に配置されたソース及びドレイン電極間にチャネル領域を有し、

前記ゲート電極開口部の外径は前記ソース又はドレイン電極の外径より小さく、かつ前記ゲート電極開口部の外径が前記ソース又はドレイン電極の外径内に納まるように配置されている

ことを特徴とする薄膜トランジスタである。

【0011】

30

本発明は、実効Cgs面積（以下「S'」という。）が、約150  $\mu\text{m}^2$  以下であり、

チャネル幅W対チャネル長L比（W/L）が、約4.5以上であり、

S'への充電能力指標Fが、約50以下である薄膜トランジスタである。

【0012】

S'は以下の式により算出される。

$$\text{式1 } S' = \times ((D+L)/2) \times ((D+L)/2) - \times (d/2) \times (d/2)$$

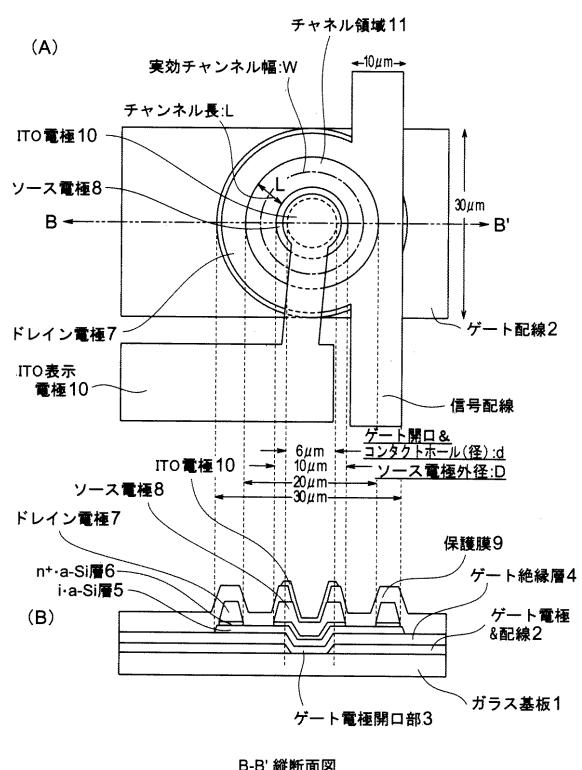

式中、DはTFTのソース電極外径、LはTFTのチャネル長、dはゲート電極開口径を意味する。（図4A 参照）

本発明では、D=d+4とした。4の意味は食刻工程の合せ精度、加工精度を勘案した数字であり、同心円の外径差2  $\mu\text{m}$ を意味する。

40

【0013】

発明者は、S'が約150  $\mu\text{m}^2$  を越えると表示電極電位のレベルシフトが生じ、画像にフリッカや残像問題が顕在化することを見出した。従って、本発明の薄膜トランジスタにおいては、S'が約150  $\mu\text{m}^2$  以下になるような数値が選択される。

【0014】

オン電流を定める指標としてW/Lの値を用いる。本発明の薄膜トランジスタにおいては、この値が約4.5以上となるような数値が選択される。W/Lは以下の式により算出される。

$$\text{式2 } W/L = \times (D/L+1)$$

【0015】

50

電極を同心円状に形成することにより、リーク電流の低減が達成されるとともに、Dを大きくすることによってオン電流も高めることも可能となる。しかし、オン電流を際限なく高めることはゲートとソース及びドレイン電極間のCgsを増やすことになり、レベルシフト量が問題レベルになってくる。本発明においては、ゲート電極に、基板の表面に達するゲート電極開口部を形成することにより、ゲート電極とソース又はドレイン電極の重なりを少なくすると共に、S'を小さくし、これによりゲート電極とソース及びドレイン電極間のCgsの低減を図り、結果としてレベルシフト量の低減を図ることができる。更に、本発明においては、ゲート電極上方に形成されたa-Si島に、前記ゲート電極開口部に対応する端部を有するa-Si島開口部を形成することにより、同様の効果を達成することができる。

10

## 【0016】

発明者は、S'への充電能力指標Fとして以下の式を定義する。

$$\text{式 3 } F = S' \div (W/L)$$

## 【0017】

この値は小さい方がよく、約50を超えるとS'に充電される電荷量がレベルシフト量に及ぼす影響が顕在化する。従って約50以下になるような数値を選択することにより、オン電流とレベルシフト量への影響問題を解消する。

## 【0018】

本発明は、上記式1乃至3により求められる数値のすべてが上記問題回避に必要な数値範囲に含まれるように選択される必要がある。得られた結果を表1に示す。

20

## 【0019】

## 【表1】

| $d; \mu m$ | $L; \mu m$ | 3           | 4           | 5           | 6           | 8           | 10          |

|------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0          | W/L        | 1 $\pi$     |

|            | S'         | 2.25 $\pi$  | 4 $\pi$     | 6.25 $\pi$  | 9 $\pi$     | 16 $\pi$    | 25 $\pi$    |

| 3          | W/L        | 2 $\pi$     | 1.75 $\pi$  | 1.6 $\pi$   | 1.5 $\pi$   | 1.375 $\pi$ | 1.3 $\pi$   |

|            | S'         | 9 $\pi$     | 12.25 $\pi$ | 16 $\pi$    | 20.25 $\pi$ | 30.25 $\pi$ | 42.25 $\pi$ |

| 5(1+3+1)   | W/L        | 2.67 $\pi$  | 2.25 $\pi$  | 2 $\pi$     | 1.83 $\pi$  | 1.625 $\pi$ | 1.5 $\pi$   |

|            | S'         | 13.75 $\pi$ | 18 $\pi$    | 22.75 $\pi$ | 28 $\pi$    | 40 $\pi$    | 54 $\pi$    |

| 8(2+4+2)   | W/L        | 3.66 $\pi$  | 3 $\pi$     | 2.6 $\pi$   | 2.33 $\pi$  | 2 $\pi$     | 1.8 $\pi$   |

|            | S'         | 26.25 $\pi$ | 32 $\pi$    | 38.25 $\pi$ | 45 $\pi$    | 60 $\pi$    | 77 $\pi$    |

| 10(2+6+2)  | W/L        | 4.33 $\pi$  | 3.5 $\pi$   | 3 $\pi$     | 2.66 $\pi$  | 2.25 $\pi$  | 2 $\pi$     |

|            | S'         | 33.25 $\pi$ | 40 $\pi$    | 47.25 $\pi$ | 55 $\pi$    | 72 $\pi$    | 91 $\pi$    |

| 12(2+8+2)  | W/L        | 5 $\pi$     | 4 $\pi$     | 3.4 $\pi$   | 3 $\pi$     | 2.5 $\pi$   | 2.2 $\pi$   |

|            | S'         | 40.25 $\pi$ | 48 $\pi$    | 56.25 $\pi$ | 65 $\pi$    | 84 $\pi$    | 105 $\pi$   |

| 14(2+10+2) | W/L        | 5.67 $\pi$  | 4.5 $\pi$   | 3.8 $\pi$   | 3.33 $\pi$  | 2.75 $\pi$  | 2.4 $\pi$   |

|            | S'         | 49.25 $\pi$ | 56 $\pi$    | 66.25 $\pi$ | 75 $\pi$    | 96 $\pi$    | 119 $\pi$   |

| 16(2+12+2) | W/L        | 6.33 $\pi$  | 5 $\pi$     | 4.2 $\pi$   | 3.66 $\pi$  | 3 $\pi$     | 2.6 $\pi$   |

|            | S'         | 54.25 $\pi$ | 64 $\pi$    | 74.25 $\pi$ | 85 $\pi$    | 109 $\pi$   | 133 $\pi$   |

| 18(2+14+2) | W/L        | 7 $\pi$     | 5.5 $\pi$   | 4.6 $\pi$   | 4 $\pi$     | 3.25 $\pi$  | 2.8 $\pi$   |

|            | S'         | 61.25 $\pi$ | 72 $\pi$    | 83.25 $\pi$ | 95 $\pi$    | 120 $\pi$   | 147 $\pi$   |

30

ここで、 $D = 0 \mu m$ は限界値を示すために挿入している。

## 【0020】

表1においては、縦欄にソース電極径D、横欄にチャネル長Lを定義し、W/L及びS'を算出した。表中斜線欄の値を示す設計寸法では、上記問題の内の一つ以上が回避できない例を示す。横線欄及び白地欄は本発明の目的を達成できる設計寸法から得られる数値範囲を示す。表中太枠で囲んだ範囲は、TFT液晶ディスプレイの画面の大小を問わず実用最適領

40

50

域である。尚、横線欄の数値を示す薄膜トランジスタは、パソコンやモニター等用の比較的小さな画面サイズの液晶表示装置に適しており、白地欄の数値を示す薄膜トランジスタは、液晶TV用の比較的大画面の液晶表示装置に適している。

**【0021】**

本発明は、表示セルがマトリクス状に配置された表示装置であって、前記表示セルが上記本発明の記載の薄膜トランジスタを

含むことを特徴とする表示装置である。

**【0022】**

本発明は、基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

前記ゲート電極をマスクとして、前記基板底部から背面露光を行い、円形状の遮光膜を有するフォトマスクを介して、前記フォトレジスト上部より正面露光を行うことにより前記フォトレジストを感光させる工程、

前記背面及び正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法である。

**【0023】**

本発明は、基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

中央部に円形開口を有する遮光膜が形成されたフォトマスクを介して、前記フォトレジスト上部より正面露光を行い前記フォトレジストを感光させる工程、

前記正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法である。

**【発明の効果】**

**【0024】**

上記したように、本発明の薄膜トランジスタを用いることにより、ゲート・ソース電極容量、並びにリーク電流の低減を図ると同時に、オン電流の増大とレベルシフト量の低減が併せて実現できる薄膜トランジスタが提供される。

**【発明を実施するための最良の形態】**

**【0025】**

本発明の薄膜トランジスタ、特にボトムゲート型薄膜トランジスタの実施例を、図面を参照しつつ説明する。尚、本発明は下記実施例に限定されるものではなく、本特許請求の範囲に規定された範囲において種々の修正及び変更を加えることは明らかである。

**【実施例1】**

**【0026】**

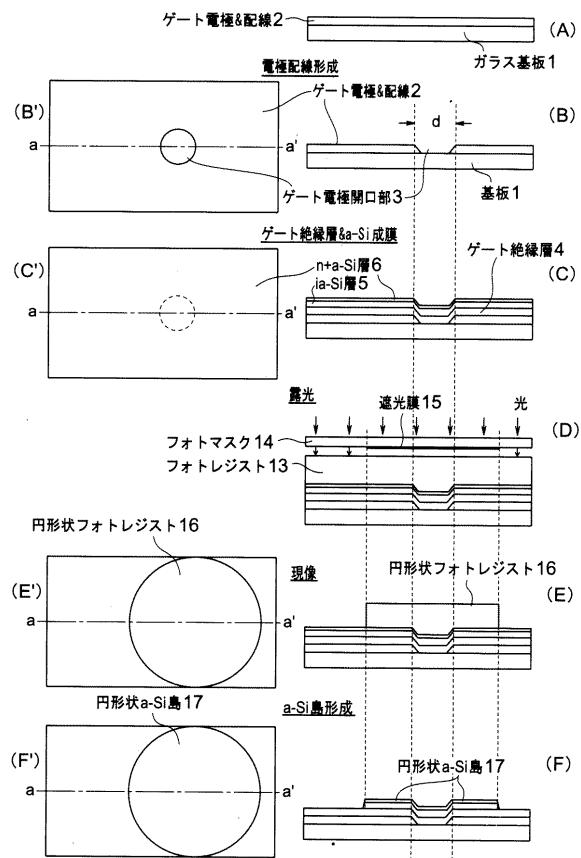

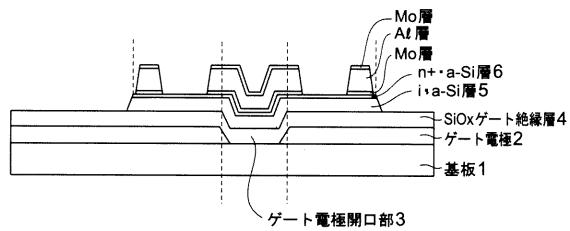

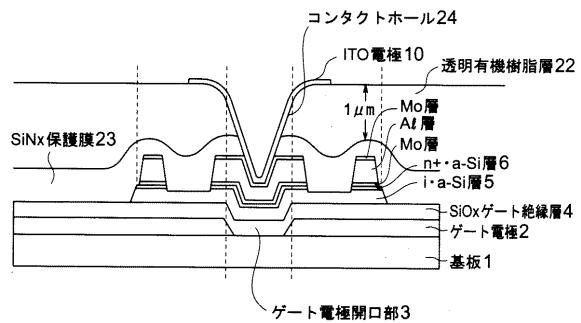

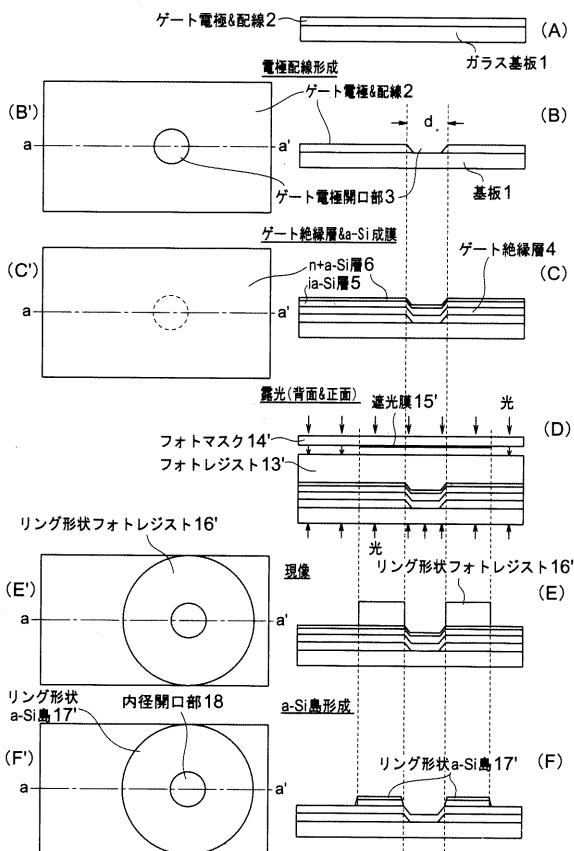

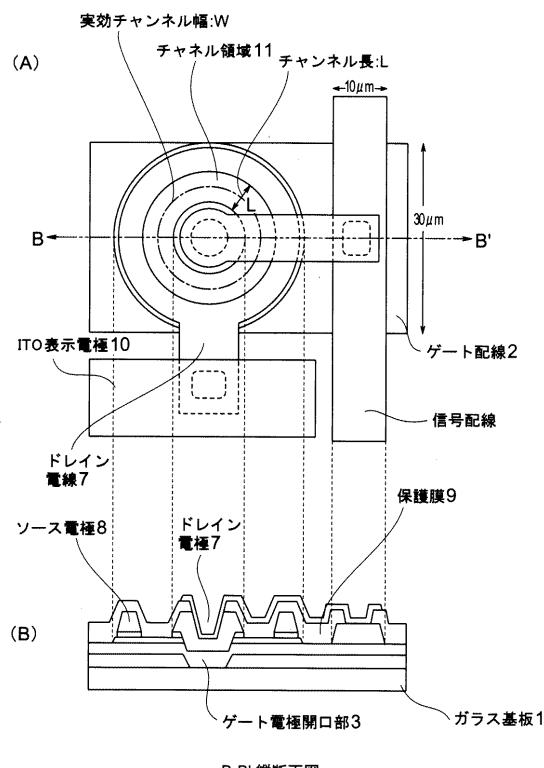

図4Aは、本発明の非晶質シリコン薄膜トランジスタの構成を示す上面図である。図4Bは、図4AのB-B'線に沿って切断された断面図である。図5A,A',B',C,D,D',E,E',F,F'は、図4B中、ガラス基板上にゲート電極、ゲート電極開口部、ゲート絶縁層、半導体層（本実施例においては、真性非晶質シリコン（i-a-Si:H）層、及びn<sup>+</sup>非晶質シリコン（n<sup>+</sup>-a-Si:H）層を含むa-Si島）の形成を示す工程図である。

10

20

30

40

50

## 【0027】

図5Aに示すように、ガラス基板1上にスパッタ成膜により200nm厚のMoWゲート電極・配線2を形成するための層を形成する。ここで、ガラス基板1は、透明なガラス基板の他、プラスチックやセラミクス等よりなる透明、あるいは不透明基板も使用することができる。

## 【0028】

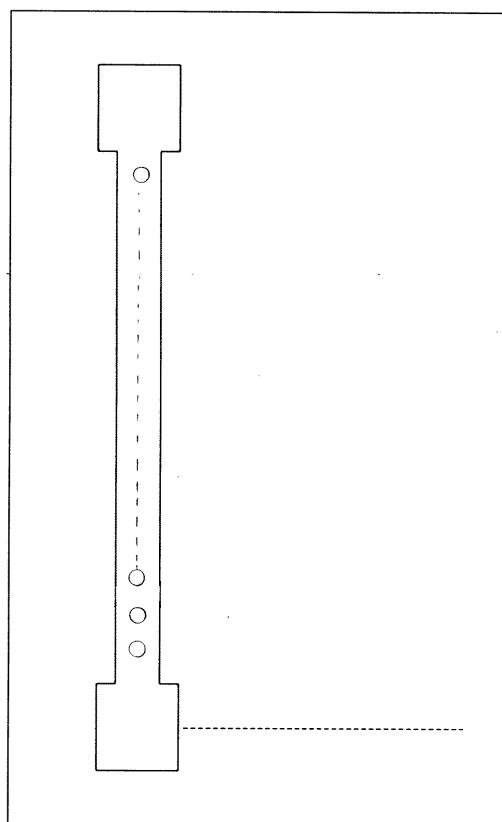

次に、形成された金属層は食刻工程を経て30μm幅のゲート電極・配線層2を電極形状に形成すると同時に、該ゲート電極・配線層2に6μm径のゲート電極開口部3を形成する。このように形成されたゲート電極・配線層2及びゲート電極開口部3を図5B、B'及び図6に示す。図6は、電極形状に形成された上記ゲート電極・配線層2及びゲート電極開口部3の配置を示す概略上面図である。MoWのエッティングは通常のケミカルドライエッティング技術を用いた。尚、ガラス基板1とゲート電極・配線層2の間には、適宜およそ200nm厚のSiO<sub>x</sub>層をプラズマ化学気相堆積(PE-CVD)法、以下プラズマCVD法と称す)により形成してもよい。

10

## 【0029】

次に、上記ゲート電極・配線層2から円形状a-Si島17形成までの工程を図5を参照しつつ説明する。

## 【0030】

上記エッティングの後、レジストを剥離し、ガラス基板1上に、上記ゲート電極・配線層2を覆うように250nm厚のゲート絶縁層4(SiO<sub>x</sub>)をプラズマCVD法により形成する。次いで、形成されたゲート絶縁層上にTFTのチャンネル用の180nm厚の真性非晶質シリコン(i・a-Si:H)層5、次いで連続的に50nm厚のオーミックコンタクト用のn<sup>+</sup>・a-Si:H層6をプラズマCVD法により形成する。このように形成された各層の構成を図5Cに示す。図5C'は、図5Cの上面図であり、図5Cは、図6C'のa-a'線に沿って切断した断面図である。

20

## 【0031】

次に、図5Dに示されるように、n<sup>+</sup>・a-Si:H層6上にフォトレジスト13を塗布する。次いで、図5Dに示されるように、円形状の遮光膜15が形成されたフォトマスク14を介して、UVにより正面露光を行う。ここで、遮光膜15は、その下部に位置するゲート配線開口部3に対して、同軸上に配置される。前記露光により感光された部分を現像除去し、図5E及びE'に示されるような、円形状フォトレジスト16を形成する。次いで、この円形状フォトレジスト16をマスクとして、露出したi・a-Si:H層5及びn<sup>+</sup>・a-Si:H層6を通常のケミカルドライエッティング技術を用いて除去し、図5F及びF'に示されるような直径30μmの円形状a-Si島17を形成する。

30

## 【0032】

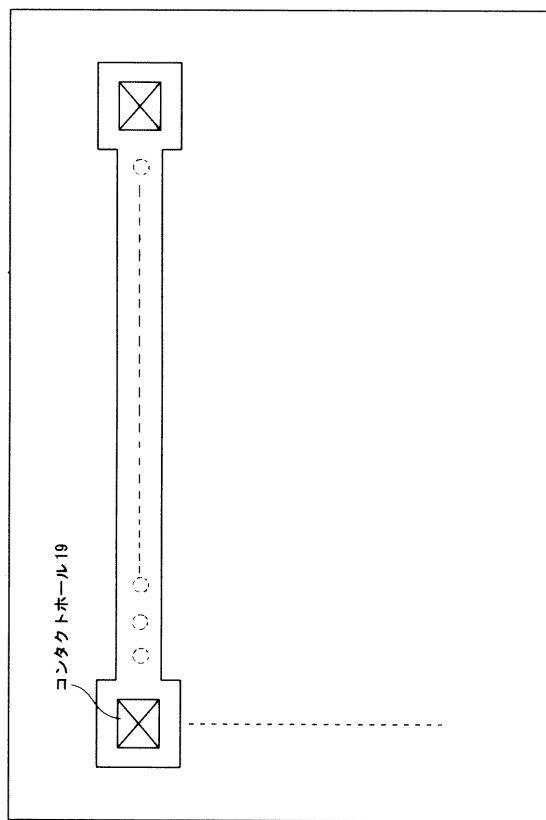

次に、ゲート電極配線の端子部にゲート電極駆動用ICとの接続のためのコンタクトホール19を食刻工程により形成する。図7は、形成されたコンタクトホール19の配置を示す概略上面図である。

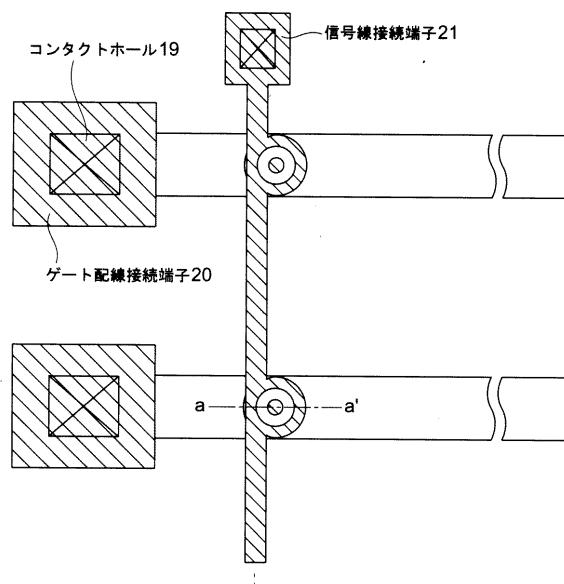

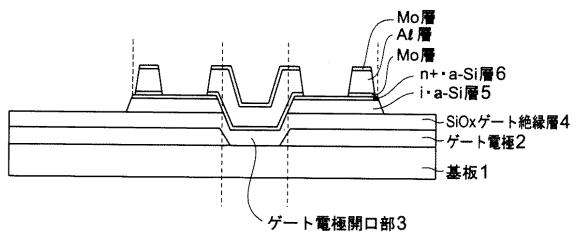

## 【0033】

次に、上記シリコンアイランドを含むガラス基板上に30nm厚のMo層、その上に300nm厚のA1層、次いで20nm厚のMo層をスパッタリングにより成膜する。続いて、食刻工程によりソース及びドレイン電極及び信号配線、並びにコンタクトホール19上にゲート配線接続端子20を形成する。この際ソース及びドレイン電極は、図4Aに示されるように、a-Si島17上に同心円状に形成され、D=10μm径のソース電極を中心にL=5μm幅のチャネル領域11を挟んで4μm幅のドレイン電極が同心円状に配置される。信号線は10μmの幅を有する。ドレイン電極は上記シリコンアイランドよりも1μm程度内側に作製すると共に、その外径がゲート電極・配線2の上表面内に納まるように配置される。尚、本発明においては、必ずしもドレイン電極の外径がゲート電極・配線2の上表面内に納まる必要はなく、チャネル領域11の下部全域にゲート電極が存在する限りにおいて、ドレイン電極の配置を設定できる。他の実施例においても同様である。

40

50

## 【0034】

ゲート電極開口部3は、その外径がソース電極の外径より小さく、ソース電極の下方に同軸上に配置されている。尚、本発明においては、必ずしも同軸上にゲート電極開口部3及びソース電極を配置する必要はなく、ゲート電極開口部3の外径がソース電極の外径内に納まるように配置すればよい。他の実施例においても同様である。

## 【0035】

図8は、ゲート電極上に作製されたソース、ドレイン電極、及び信号配線、コンタクトホール19、ゲート配線接続端子20及び信号線接続端子21の配置を示す概略上面図である。図9は、図8のa-a'線に沿って切断した場合の、上記ソース及びドレイン電極が形成された状態を示す断面図である。

10

## 【0036】

次に、作製されたソース及びドレイン電極をマスクとして、チャンネル領域11に対応する $n^+ \cdot a\text{-Si:H}$ 層6をドライエッチングにより除去する。この際、下部層のi-a-Si:H層5がおよそ30nmエッチングにより除去されてしまう。このようなドライエッチングによりチャンネル領域11の $n^+ \cdot a\text{-Si:H}$ 層が除去された後の構造を図10に示す。

## 【0037】

このように作製された薄膜トランジスタの各構成要素の寸法を、上記1乃至3式に当てはめると、式1のS'が47.25、すなわち $148 \mu\text{m}^2$ となり、式2のW/Lが9.4、式3のFが15.7となる。尚、総TFT面積は $672 \mu\text{m}^2$ である。得られたS'は、従来例と比較して約66%に削減出来た。

20

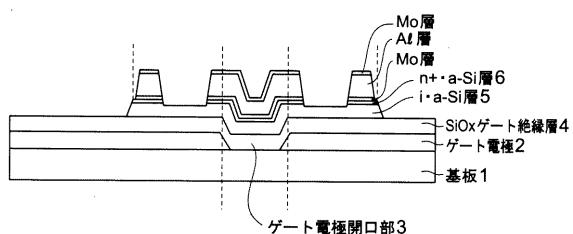

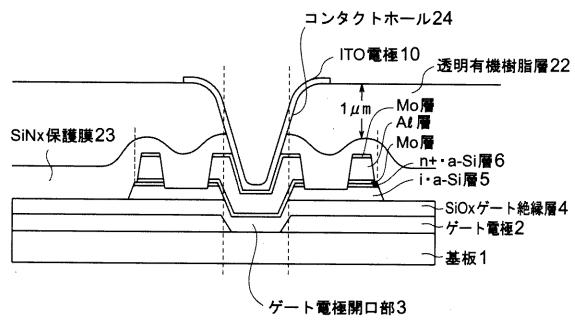

## 【0038】

本実施例においては、図11に示すように、上記により得られた図10の構造物上に400nm厚のSiNx保護膜23をプラズマCVD法により形成し、更に、平坦性を改善するために、上記保護膜上に突起部でおよそ1μmの厚さを有する透明有機樹脂層22を形成することも可能である。

## 【0039】

次いで、ソース電極上面の一部に達するコンタクトホール24、並びに図8に示されるゲート配線及び信号線接続端子20、21へのコンタクトホールを上記保護膜23、並びに平坦化のための透明有機樹脂層22に形成する。続いて、上記透明有機樹脂層22上に、50nm厚のITO層をスパッタリングにより堆積させ、食刻工程によりITO電極10を形成する。図11は、このように形成された本発明の薄膜トランジスタの断面図を示す。

30

## 【実施例2】

## 【0040】

図12Aは、本実施例における本発明の他の態様の薄膜トランジスタの構成を示す上面図である。図12Bは、図12AのB-B'線に沿って切断された断面図である。

## 【0041】

上記実施例1における図5Dに対応するフォトレジスト13への露光に代えて、以下の露光工程(図13D)を行うことを除き、実施例1と同様の工程に従い、リング形状a-Si島17'を形成した。

40

## 【0042】

図13A,A',B',C,D,D',E,E',F,F'は、図12B中、ガラス基板上にゲート電極、ゲート電極開口部、ゲート絶縁層、半導体層(本実施例においては、真性非晶質シリコン(i-a-Si:H)層、及び $n^+$ 非晶質シリコン( $n^+ \cdot a\text{-Si:H}$ )層を含むa-Si島)の形成を示す工程図である。図13A,A',B,C,C'に示される工程は、上記実施例1の図5A,A',B',Cの工程と同様である。

## 【0043】

図13Dに示すように、開口部3が形成されたゲート電極2をマスクとして、ガラス基板1の背面側より紫外線(UV)を自己整合的に露光し、フォトレジスト13'を感光させる。次いで、図13Dに示されるように、円形状の遮光膜15'が形成されたフォトマス

50

ク14'を介して、UVにより正面露光を行う。ここで、前記遮光膜15'は、前記ゲート電極・配線層2の上部表面内に納まるように配置すると共に、その下方に位置するゲート配線開口部3との関係で、同軸上に配置される。上記背面及び正面露光により感光された部分を現像除去し、図13E及びE'に示されるような、リング形状フォトレジスト16'を形成する。次いで、このリング形状フォトレジスト16'に対応する部分を残して、i-a-Si:H層5及びn<sup>+</sup>·a-Si:H層6を通常のケミカルドライエッティング技術を用いて除去し、図13F及びF'に示されるような直径30μmのリング形状a-Si島17'を形成する。このように形成されたリング形状a-Si島17'の中央に形成されたリング形状a-Si島内径開口部18の端部は、上記のようにゲート電極2の開口部3に自己整合され、それゆえ寸法的、形状的及び位置的に高い精度を有する。

10

#### 【0044】

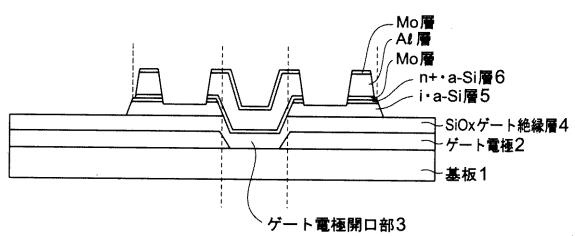

次に、上記シリコンアイランドを含むガラス基板上に30nm厚のMo層、その上に300nm厚のAl層、次いで20nm厚のMo層をスパッタリングにより成膜する。続いて、食刻工程によりソース及びドレイン電極及び信号配線、並びにコンタクトホール19上にゲート配線接続端子20を形成する。この際ソース及びドレイン電極は、図12Aに示されるように、a-Si島17上に同心円状に形成され、D=10μm径のソース電極を中心L=5μm幅のチャネル領域11を挟んで4μm幅のドレイン電極が同心円状に配置される。信号線は10μmの幅を有する。ドレイン電極は上記シリコンアイランドよりも1μm程度内側に作製すると共に、その外径がゲート電極・配線2の上表面内に納まるように配置される。ゲート電極開口部3は、その外径がソース電極の外径より小さく、ソース電極の下方に同軸上に配置されている。図8は、ゲート電極上に作製されたソース、ドレイン電極、及び信号配線、コンタクトホール19、ゲート配線接続端子20及び信号線接続端子21の配置を示す概略上面図である。図14は、図8のa-a'線に沿って切断した場合の、上記ソース及びドレイン電極が形成された状態を示す断面図である。

20

#### 【0045】

次に、作製されたソース及びドレイン電極をマスクとして、チャネル領域11に対応するn<sup>+</sup>·a-Si:H層6をドライエッティングにより除去する。この際、下部層のi-a-Si:H層5がおよそ30nmエッティングにより除去されてしまう。このようなドライエッティングによりチャネル領域のn<sup>+</sup>·a-Si:H層が除去された後の構造を図15に示す。

30

#### 【0046】

このように形成された薄膜トランジスタにおいても、上記実施例1の工程により製造された薄膜トランジスタと同様に、S'が従来例と比較して約66%に削減出来たことにより、同様の効果を達成した。

#### 【0047】

本実施例においては、実施例1と同様に、図16に示すように、上記により得られた図15の構造物上に400nm厚のSiNx保護膜23をプラズマCVD法により形成し、更に、平坦性を改善するために、上記保護膜上に突起部でおよそ1μmの厚さを有する透明有機樹脂層22を形成することも可能である。

#### 【0048】

次いで、ソース電極上面の一部に達するコンタクトホール24、並びに図8に示されるゲート配線及び信号線接続端子20、21へのコンタクトホールを上記保護膜23、並びに平坦化のための透明有機樹脂層22に形成する。続いて、上記透明有機樹脂層22上に、50nm厚のITO層をスパッタリングにより堆積させ、食刻工程によりITO電極10を形成する。図16は、このように形成された本発明の薄膜トランジスタの断面図を示す。

40

#### 【実施例3】

#### 【0049】

更に別法として、実施例2におけるガラス基板1からの背面露光を行わず、中央部に開口を形成したリング形状の遮光膜15を有するフォトマスク14'を用いる正面露光のみにより、フォトレジスト13'を感光する方法も採用できる。本方法によれば、上記背面

50

露光を併用する場合に比べて、形成されるリング形状a-Si島17'の中央に形成されるリング形状a-Si島内径開口部18の寸法的、形状的及び位置的精度はわずかに劣るが、背面露光工程を減らすことが出来る利点がある。

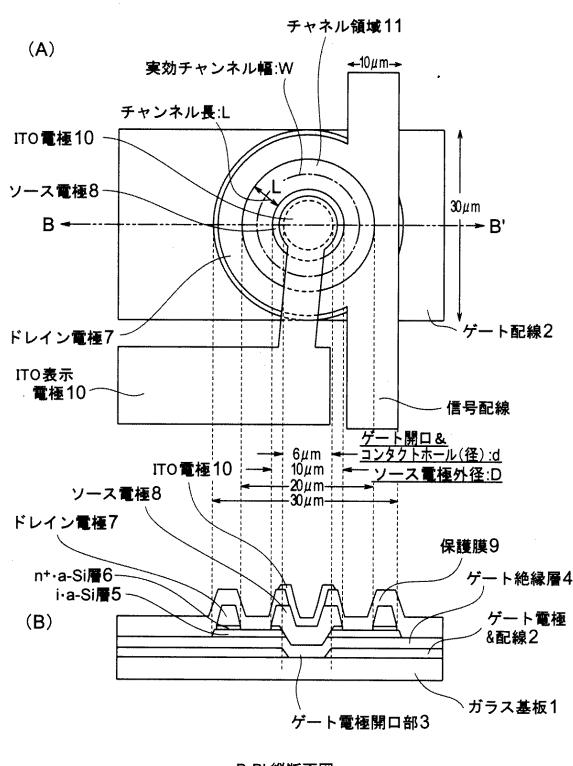

【実施例4】

【0050】

本発明は、以下のような更に他の態様も可能である。図17Aは、本態様の薄膜トランジスタの構成を示す上面図であるが、透明有機樹脂膜は使われない。図17Bは、図17AのB-B'線に沿って切断された断面図である。

【0051】

本態様においては、同心円状に形成された電極のうち、中央のソース電極と、ソース電極の周囲に同心円状に形成されたドレイン電極と、これら電極から分離して信号配線16を配置し、信号配線16をソース電極に接続し、ITO表示電極をドレイン電極に接続する構成を有する点を除いて、実施例1と同様の方法により作製される。

本実施例の薄膜トランジスタは、チャネル長Lが $5\text{ }\mu\text{m}$ 、チャネル幅Wが $4.7\text{ }\mu\text{m}$ 、W/Lが9.4、及び実効Cgs面積S'が $380\text{ }\mu\text{m}^2$ として作製される。

【0052】

尚、上記各実施例においては、ゲート電極として、図5に示されるようなゲートラインとゲート電極が同一の層に形成される構成を採用したが、画面サイズや画素数を勘案した上でゲート配線抵抗が同等なら、同じ幅の直線形状に限らず、幅に大小を持たせることも可能である。

【0053】

上記各実施例においては、同心円状に形成された電極の中央にソース電極を配置し、それを囲むようにドレイン電極を配置したが、本発明においては、中央にドレイン電極を配置し、その周囲にソース電極を配置することも可能である。

【0054】

本発明における薄膜トランジスタは、液晶表示装置(LCD)ばかりでなく、電界放出ディスプレイ(FED)、及びエレクトロルミネセンス(EL)ディスプレイ等に代表される平面表示装置に適用することも可能である。

【図面の簡単な説明】

【0055】

【図1】1Aは液晶表示装置に用いられる従来の薄膜トランジスタの構成図であり、1Bは1AのB-B'線に沿って切断された断面図である。

【図2】2A及び2Bは従来技術における薄膜トランジスタの構成図である。

【図3】3Aは表示パネル内に配置された従来の薄膜トランジスタの構成図であり、3Bは3Aのb-b'線に沿って切断された断面図である。

【図4】4Aは本発明の薄膜トランジスタの構成を示す上面図であり、4Bは4AのB-B'線に沿って切断された断面図である。

【図5】5A乃至5Fは、円形状a-Si島形成に至る工程断面図であり、5B'乃至5F'はそれぞれ5B乃至5Fの上面図である。

【図6】ゲート電極・配線層及びゲート電極・配線層に形成されたゲート電極開口部の配置を示す概略上面図である。

【図7】コンタクトホール19の配置を示す概略上面図である。

【図8】ゲート電極上に作製されたソース、ドレイン電極及び信号配線の配置を示す概略上面図である。

【図9】a-Si島上に形成されたソース及びドレイン電極を示す断面図である。

【図10】 $n^+$ ・a-Si:H層ドライエッチング後の構造を示す断面図である。

【図11】SiNx保護層上の透明有機樹脂層上にITO電極を設けた本発明の一態様の薄膜トランジスタの断面図である。

【図12】12Aは本発明の他の態様の薄膜トランジスタの構成を示す上面図であり、12Bは12のB-B'線に沿って切断された断面図である。

10

20

30

40

50

【図13】13A乃至13Fは、リング形状a-Si島形成に至る工程断面図であり、13B'乃至13F'はそれぞれ13B乃至13Fの上面図である。

【図14】a-Si島上に形成されたソース及びドレイン電極を示す断面図である。

【図15】n<sup>+</sup>・a-Si:H層ドライエッチング後の構造を示す断面図である。

【図16】SiNx保護層上の透明有機樹脂層上にITO電極を設けた本発明の一態様の薄膜トランジスタの断面図である。

【図17】17Aは本発明の他の態様の薄膜トランジスタの構成を示す上面図であり、17Bは17AのB-B'線に沿って切断された断面図である。

【符号の説明】

【0056】

1 ガラス基板

10

2 ゲート電極・配線

3 ゲート電極開口部

4 ゲート絶縁層

5 i・a-Si:H層

6 n<sup>+</sup>・a-Si:H層

7 ドレイン電極

8 ソース電極

9 保護膜

10 ITO電極

20

11 チャネル領域

13, 13' フォトレジスト

14, 14' フォトマスク

15, 15' 遮光膜

16 円形状フォトレジスト

16' リング形状フォトレジスト

17 円形状a-Si島

17' リング形状a-Si島

18 リング形状a-Si島内径開口部

19 コンタクトホール

30

20 ゲート配線接続端子

21 信号線接続端子

22 透明有機樹脂層

23 SiNx保護膜

24 コンタクトホール

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

B-B' 縦断面図

---

フロントページの続き

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 小穴 保久

神奈川県横浜市港北区新横浜3-17-5 ベネックスS-2, 8階 LG フィリップス LC

D 株式会社 日本研究所内

審査官 綿引 隆

(56)参考文献 特開2004-087682 (JP, A)

特開2006-352087 (JP, A)

特開2006-286772 (JP, A)

特表2005-524110 (JP, A)

特開昭64-082674 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/41

H01L 29/423

H01L 29/49

H01L 29/786