(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7010184号

(P7010184)

(45)発行日 令和4年1月26日(2022.1.26)

(24)登録日 令和4年1月17日(2022.1.17)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 29/739 (2006.01) | F I | H 01 L | 29/78 | 6 5 5 B |

| H 01 L | 29/78 (2006.01)  |     | H 01 L | 29/78 | 6 5 3 A |

|        |                  |     | H 01 L | 29/78 | 6 5 2 D |

請求項の数 4 (全16頁)

|          |                             |          |                                     |

|----------|-----------------------------|----------|-------------------------------------|

| (21)出願番号 | 特願2018-171732(P2018-171732) | (73)特許権者 | 000004260                           |

| (22)出願日  | 平成30年9月13日(2018.9.13)       |          | 株式会社デンソー                            |

| (65)公開番号 | 特開2020-43301(P2020-43301A)  |          | 愛知県刈谷市昭和町1丁目1番地                     |

| (43)公開日  | 令和2年3月19日(2020.3.19)        | (74)代理人  | 110001128                           |

| 審査請求日    | 令和3年2月17日(2021.2.17)        | (72)発明者  | 特許業務法人ゆうあい特許事務所<br>宮田 征典            |

|          |                             | (72)発明者  | 愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内<br>米田 秀司  |

|          |                             | (72)発明者  | 愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内<br>妹尾 賢   |

|          |                             | (72)発明者  | 愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内<br>薬師川 裕貴 |

|          |                             |          | 最終頁に続く                              |

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

フィールドストップ層(20)を有する半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層の表層部に形成された第1導電型のエミッタ領域(16)と、

前記ベース層のうちの前記ドリフト層と前記エミッタ領域との間に形成されたゲート絶縁膜(14)と、

前記ゲート絶縁膜上に形成されたゲート電極(15)と、

前記ドリフト層のうちの前記ベース層側と反対側に形成された第2導電型のコレクタ層(21)と、

前記コレクタ層と前記ドリフト層との間に形成され、前記ドリフト層よりも高キャリア濃度とされた第1導電型の前記フィールドストップ層と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(19)と、

前記コレクタ層と電気的に接続される第2電極(22)と、を備え、

前記フィールドストップ層および前記コレクタ層は、前記フィールドストップ層におけるキャリア濃度が最大となる最大ピーク位置と前記コレクタ層におけるキャリア濃度が最大となる最大ピーク位置との間の距離をX [μm]、前記フィールドストップ層を構成するドーズ量に対する前記コレクタ層を構成するドーズ量の比である不純物総量比をYとする

と、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たす構成とされており、

前記コレクタ層は、前記コレクタ層と前記フィールドストップ層との積層方向において、前記コレクタ層の最大ピーク位置が当該コレクタ層の中心（C1）より前記ドリフト層側に位置している半導体装置。

【請求項2】

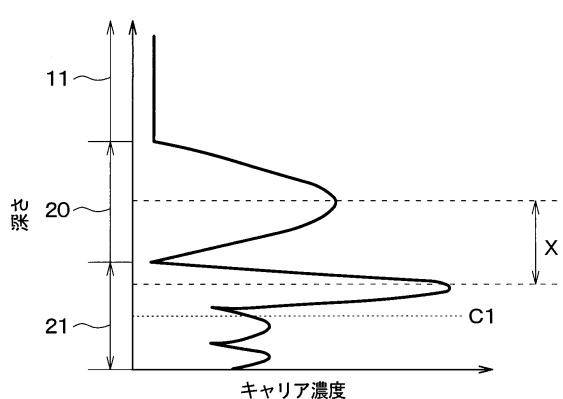

前記コレクタ層は、前記キャリア濃度が複数のピークを有するように構成され、前記中心より前記ドリフト層側と反対側に、前記キャリア濃度が最大となる最大ピークよりも小さい補助ピークを有している請求項1に記載の半導体装置。

【請求項3】

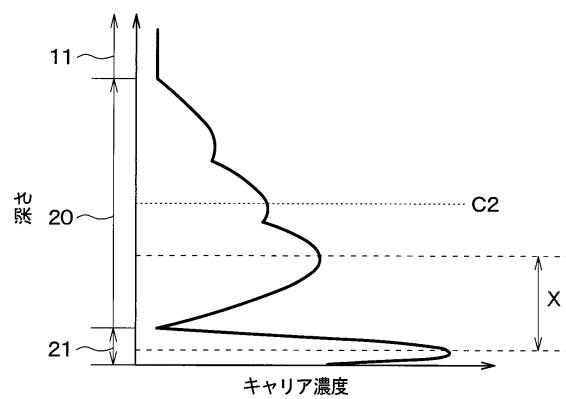

前記フィールドストップ層は、前記コレクタ層と前記フィールドストップ層との積層方向において、前記フィールドストップ層におけるキャリア濃度が最大となる最大ピーク位置が当該フィールドストップ層の中心（C2）より前記ドリフト層側に位置している請求項1または2に記載の半導体装置。

10

【請求項4】

前記フィールドストップ層は、前記コレクタ層と前記フィールドストップ層との積層方向において、前記フィールドストップ層におけるキャリア濃度が最大となる最大ピーク位置が当該フィールドストップ層の中心（C2）より前記コレクタ層側に位置している請求項1または2に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

20

本発明は、絶縁ゲートバイポーラトランジスタ（以下では、単にIGBTという）素子が形成された半導体装置に関するものである。

【背景技術】

【0002】

従来より、インバータ等に使用されるスイッチング素子として、IGBT素子が形成された半導体装置を用いることが提案されている（例えば、特許文献1参照）。具体的には、この半導体装置は、N-型のドリフト層を有し、このドリフト層上にP型のベース層が形成されている。そして、半導体装置では、ベース層を貫通するように複数のトレンチが形成されている。各トレンチには、トレンチの壁面を覆うようにゲート絶縁膜が形成され、ゲート絶縁膜上にゲート電極が形成されている。さらに、ベース層の表層部には、トレンチの側面に接するようにN+型のエミッタ領域が形成されている。

30

【0003】

ドリフト層を挟んでベース層と反対側には、P型のコレクタ層が形成されている。また、半導体装置には、ベース層およびエミッタ領域と電気的に接続される上部電極が形成されていると共に、コレクタ層と電気的に接続される下部電極が形成されている。

【0004】

さらに、この半導体装置では、耐圧を向上するため、コレクタ層上にドリフト層よりも高キャリア濃度とされたN型のフィールドストップ層（以下では、単にFS層という）が形成されている。

40

【先行技術文献】

【特許文献】

【0005】

【文献】特開2017-11000号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記半導体装置では、FS層が形成されていることにより、短絡時において、空乏層の端部がコレクタ層から遠くなり易い。このため、半導体装置では、空乏層の端部となる部分に注入される正孔が減少することによって電子が過多状態となり、電界強度のピークが下部電極側で発生する可能性がある。そして、半導体装置は、電界強度のピ

50

ークが下部電極側で発生すると当該ピーク部分の近傍でアバランシェ降伏が発生し、破壊されてしまう可能性がある。つまり、上記のようにFS層を有する半導体装置では、短絡耐量が低くなる可能性がある。

【0007】

本発明は上記点に鑑み、短絡耐量を向上できる半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するための請求項1では、FS層(20)を有する半導体装置であって、第1導電型のドリフト層(11)と、ドリフト層上に形成された第2導電型のベース層(12)と、ベース層の表層部に形成された第1導電型のエミッタ領域(16)と、ベース層のうちのドリフト層とエミッタ領域との間に形成されたゲート絶縁膜(14)と、ゲート絶縁膜上に形成されたゲート電極(15)と、ドリフト層のうちのベース層側と反対側に形成された第2導電型のコレクタ層(21)と、コレクタ層とドリフト層との間に形成され、ドリフト層よりも高キャリア濃度とされた第1導電型のFS層と、ベース層およびエミッタ領域と電気的に接続される第1電極(19)と、コレクタ層と電気的に接続される第2電極(22)と、を備え、FS層およびコレクタ層は、FS層におけるキャリア濃度が最大となる最大ピーク位置とコレクタ層におけるキャリア濃度が最大となる最大ピーク位置との間の距離をX[μm]、FS層を構成するドーズ量に対するコレクタ層を構成するドーズ量の比である不純物総量比をYとすると、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たす構成とされており、コレクタ層は、コレクタ層とフィールドストップ層との積層方向において、コレクタ層の最大ピーク位置が当該コレクタ層の中心(C1)よりドリフト層側に位置している。

10

20

【0010】

これによれば、短絡時に正孔が注入され易くなるため、下部電極側の電界強度が高くなることを抑制できる。したがって、短絡耐量の向上を図ることができる。

【図面の簡単な説明】

【0011】

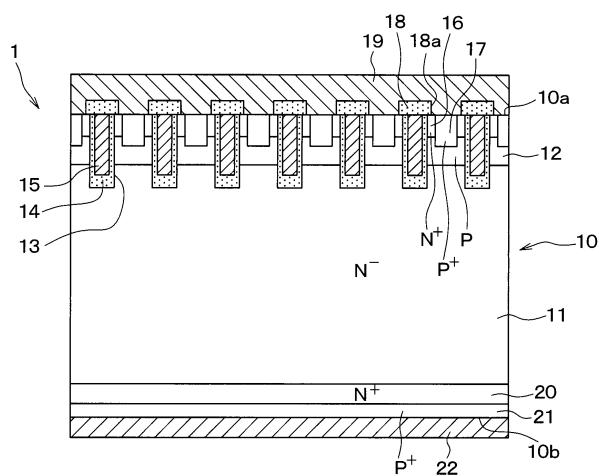

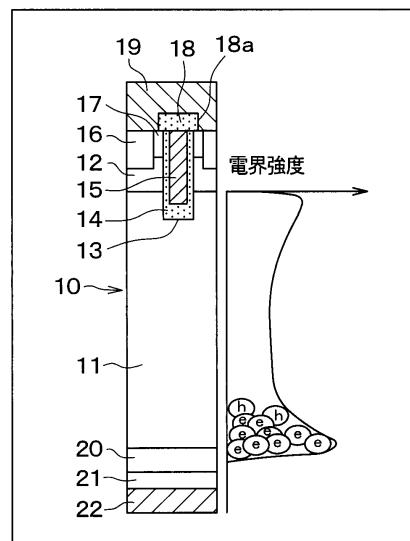

【図1】第1実施形態における半導体装置の断面図である。

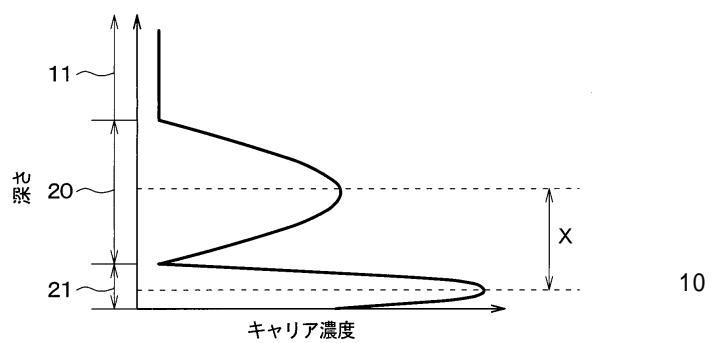

【図2】半導体基板の他面からの深さと、キャリア濃度との関係を示す図である。

30

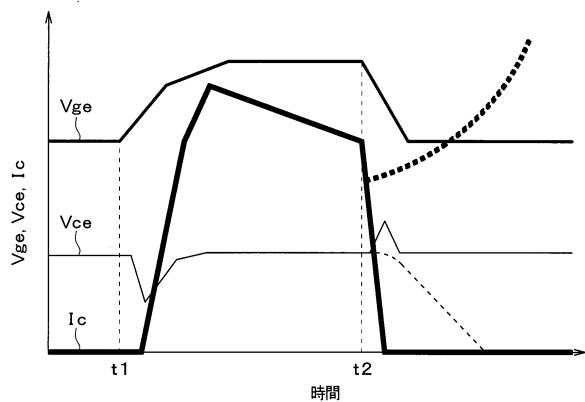

【図3】半導体装置の作動を示すタイミングチャートである。

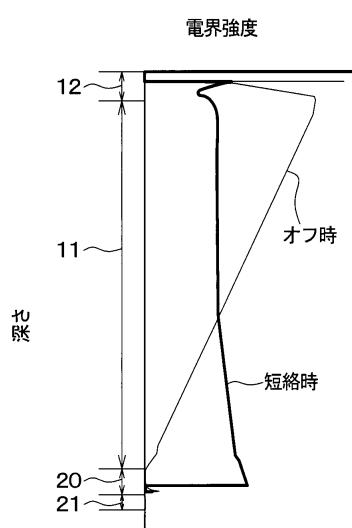

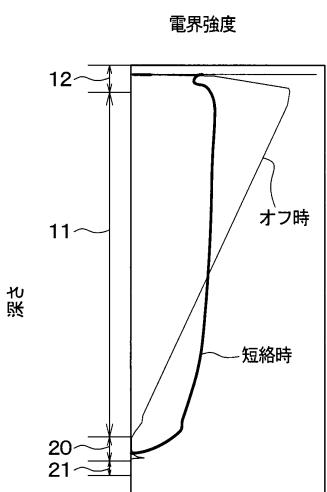

【図4】半導体装置の電界強度を示す図である。

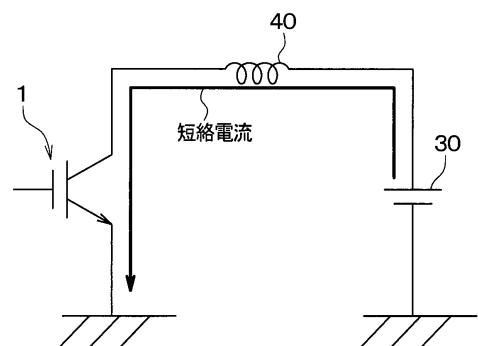

【図5】短絡評価を行う際の回路構成を示す図である。

【図6】短絡時において、電界強度のピークが下部電極側に発生する原理を説明するための図である。

【図7】半導体装置の電界強度を示す図である。

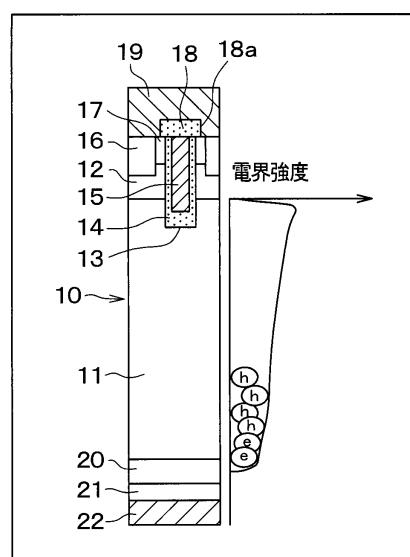

【図8】短絡時において、電界強度のピークが下部電極側に発生し難くなる原理を説明するための図である。

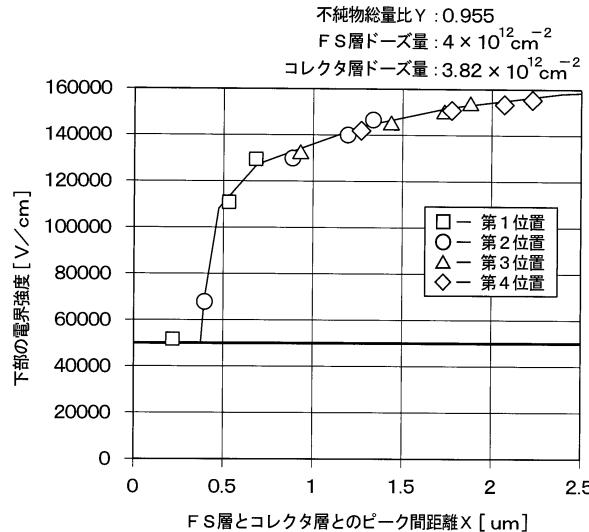

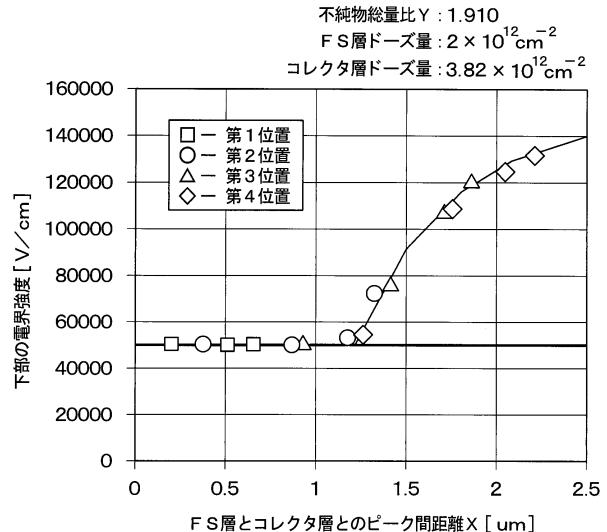

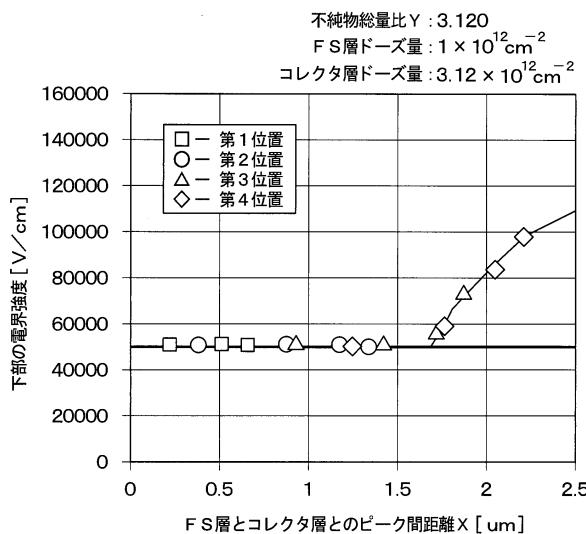

【図9A】FS層とコレクタ層とのピーク間距離と、下部の電界強度との関係を示す図である。

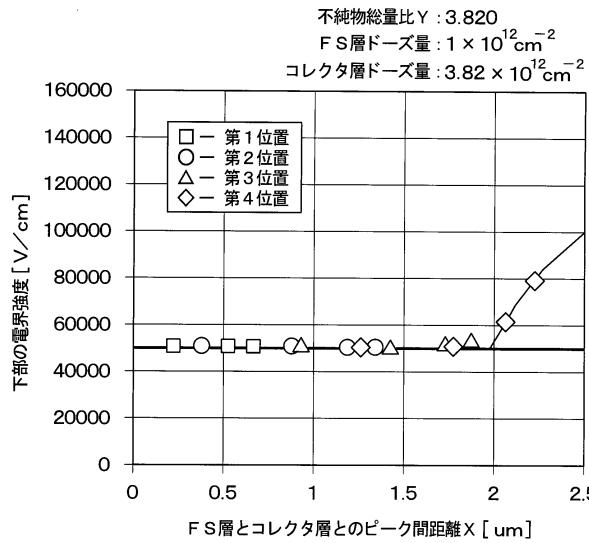

【図9B】FS層とコレクタ層とのピーク間距離と、下部の電界強度との関係を示す図である。

40

【図9C】FS層とコレクタ層とのピーク間距離と、下部の電界強度との関係を示す図である。

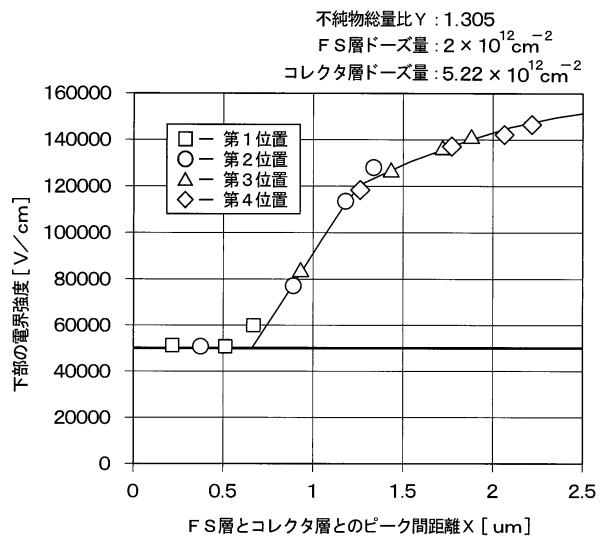

【図10A】FS層とコレクタ層とのピーク間距離と、下部の電界強度との関係を示す図である。

【図10B】FS層とコレクタ層とのピーク間距離と、下部の電界強度との関係を示す図である。

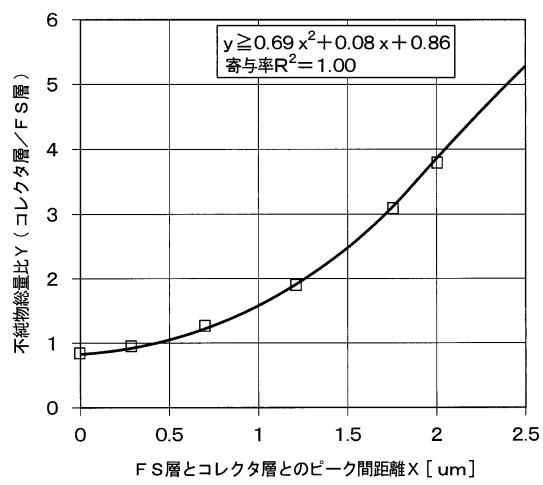

【図11】FS層とコレクタ層とのピーク間距離と、不純物総量比との関係を示す図である。

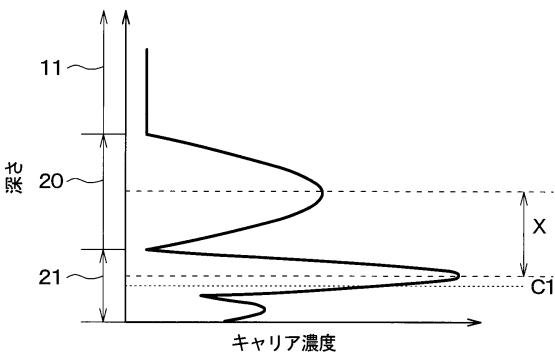

【図12】第2実施形態における半導体基板の他面からの深さと、キャリア濃度との関係

50

を示す図である。

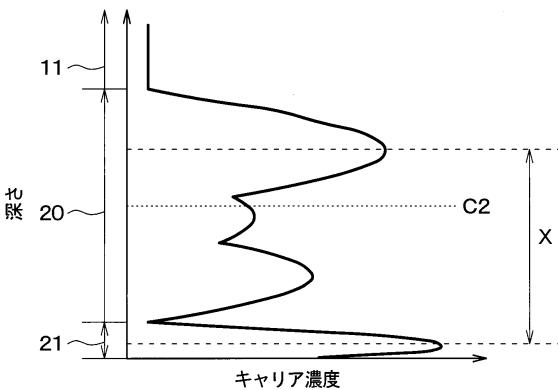

【図13】第3実施形態における半導体基板の他面からの深さと、キャリア濃度との関係を示す図である。

【図14】第4実施形態における半導体基板の他面からの深さと、キャリア濃度との関係を示す図である。

【図15】他の実施形態における半導体基板の他面からの深さと、キャリア濃度との関係を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

10

【0013】

(第1実施形態)

第1実施形態の半導体装置について図1を参照しつつ説明する。なお、本実施形態の半導体装置1は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

【0014】

図1に示されるように、半導体装置1は、ドリフト層11として機能するN-型の半導体基板10を有している。そして、ドリフト層11上(すなわち、半導体基板10の一面10a側)には、P型のベース層12が形成されている。

20

【0015】

また、半導体基板10には、ベース層12を貫通してドリフト層11に達する複数のトレンチ13が形成されており、ベース層12は複数のトレンチ13によって分断されている。本実施形態では、複数のトレンチ13は、半導体基板10の一面10aの面方向のうちの一方向(すなわち、図1中紙面奥行き方向)に沿ってストライプ状に等間隔に形成されている。

【0016】

そして、複数のトレンチ13は、それぞれトレンチ13の壁面を覆うように形成されたゲート絶縁膜14と、当該ゲート絶縁膜14の上に形成されたゲート電極15とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。なお、本実施形態では、ゲート絶縁膜14は、酸化膜等で構成され、ゲート電極15は、ドープトポリシリコン等で構成される。

30

【0017】

ベース層12の表層部には、N<sup>+</sup>型のエミッタ領域16およびP<sup>+</sup>型のボディ領域17が形成されている。具体的には、エミッタ領域16は、ドリフト層11よりも高キャリア濃度で構成され、ベース層12内において終端し、かつ、トレンチ13の側面に接するように形成されている。一方、ボディ領域17は、ベース層12よりも高キャリア濃度で構成され、エミッタ領域16と同様に、ベース層12内において終端するように形成されている。

【0018】

より詳しくは、エミッタ領域16は、トレンチ13間の領域において、トレンチ13の長手方向に沿ってトレンチ13の側面に接するように棒状に延設され、トレンチ13の先端よりも内側で終端する構造とされている。また、ボディ領域17は、2つのエミッタ領域16に挟まれてトレンチ13の長手方向(つまりエミッタ領域16)に沿って棒状に延設されている。なお、本実施形態のボディ領域17は、半導体基板10の一面10aを基準としてエミッタ領域16よりも深く形成されている。

40

【0019】

半導体基板10の一面10a上には、BPSG(Boro-phospho silicate glassの略)等で構成される層間絶縁膜18が形成されており、層間絶縁膜18には、エミッタ領域16の一部およびボディ領域17を露出させるコンタクトホール18aが形成されている。そ

50

して、層間絶縁膜 18 上には、コンタクトホール 18a を通じてエミッタ領域 16 およびボディ領域 17 と電気的に接続される上部電極 19 が形成されている。

【0020】

ドリフト層 11 のうちのベース層 12 側と反対側（すなわち、半導体基板 10 の他面 10b 側）には、ドリフト層 11 よりも高キャリア濃度とされたN<sup>+</sup>型のFS層 20 が形成されている。

【0021】

そして、FS層 20 を挟んでドリフト層 11 と反対側には、半導体基板 10 の他面 10b を構成するP<sup>+</sup>型のコレクタ層 21 が形成されている。コレクタ層 21 上（すなわち、半導体基板 10 の他面 10b 上）には、コレクタ層 21 と電気的に接続される下部電極 22 が形成されている。

10

【0022】

なお、本実施形態のFS層 20 およびコレクタ層 21 は、半導体基板 10 の他面 10b 側から不純物がイオン注入された後に熱処理されることで構成される。このため、FS層 20 およびコレクタ層 21 は、図 2 に示されるように、キャリア濃度が正規分布となっている。この場合、キャリア濃度は、1つのピークを有する分布となるため、このピークが最大ピークとなる。また、具体的には後述するが、本実施形態では、FS層 20 のキャリア濃度における最大ピーク位置と、コレクタ層 21 のキャリア濃度における最大ピーク位置との間の距離 X が規定される。以下では、FS層 20 のキャリア濃度における最大ピーク位置と、コレクタ層 21 のキャリア濃度における最大ピーク位置との間の距離 X を、単に FS層 20 とコレクタ層 21 とのピーク間距離 X ともいう。

20

【0023】

以上が本実施形態における半導体装置 1 の構成である。なお、本実施形態では、N型、N<sup>-</sup>型、N<sup>+</sup>型が本発明の第1導電型に相当し、P型、P<sup>+</sup>型が本発明の第2導電型に相当している。また、本実施形態では、上部電極 19 が第1電極に相当し、下部電極 22 が第2電極に相当している。そして、本実施形態の半導体基板 10 は、上記のように、コレクタ層 21、FS層 20、ドリフト層 11、ベース層 12、エミッタ領域 16、ボディ領域 17 を有する構成とされている。

【0024】

次に、このような半導体装置 1 の作動について、図 3 を参照しつつ説明する。

30

【0025】

まず、上記半導体装置 1 は、電流が流れるオン状態とされるには、上部電極 19 に下部電極 22 より低い電圧が印加されている状態において、時点 1 にてゲート電極 15 に所定の閾値以上の電圧が印加される。これにより、半導体装置 1 は、ゲート - エミッタ間電圧 V<sub>ge</sub> が上昇し、ベース層 12 のうちのトレンチ 13 と接する部分に N型の反転層（すなわち、チャネル）が形成される。そして、半導体装置 1 は、エミッタ領域 16 から反転層を介して電子がドリフト層 11 に供給されると共に、コレクタ層 21 からホールがドリフト層 11 に供給され、伝導度変調によりドリフト層 11 の抵抗値が低下してオン状態となる。つまり、半導体装置 1 には、コレクタ - エミッタ間電圧 V<sub>ce</sub> が低下して電流 I<sub>c</sub> が流れる。なお、所定の閾値以上の電圧とは、ゲート - エミッタ間電圧 V<sub>ge</sub> をMOSゲートの閾値電圧 V<sub>th</sub> より高くする電圧のことである。

40

【0026】

そして、半導体装置 1 は、時点 t<sub>2</sub> にてゲート電極 15 に印加されていた電圧が停止されると、ゲート - エミッタ間電圧 V<sub>ge</sub> が低下し、反転層が消滅してオフ状態となる。つまり、半導体装置 1 は、電流 I<sub>c</sub> が減少してオフ状態となる。この場合、半導体装置 1 は、短絡が発生すると、図 3 中の点線で示されるように、電流 I<sub>c</sub> が急峻に増加しつつ、コレクタ - エミッタ間電圧 V<sub>ce</sub> が急峻に低下する。

【0027】

ここで、短絡時における半導体装置 1 の電界強度について、図 4 を参照しつつ説明する。

なお、図 4 は、図 5 に示されるように、半導体装置 1 を電源 30 にコイル 40 を介して接

50

続した状態で短絡評価を行った際のシミュレーション結果を示す図である。また、図4は、FS層20を $2.0 \times 10^{12} \text{ cm}^{-2}$ のドーズ量で構成し、コレクタ層21を $3.56 \times 10^{12} \text{ cm}^{-2}$ のドーズ量で構成し、FS層20とコレクタ層21とのピーク間距離Xを $1.5 \mu\text{m}$ とした場合のシミュレーション結果を示す図である。

【0028】

図4に示されるように、半導体装置1におけるオフ時の電界強度は、ベース層12とドリフト層11との接合部近傍でピークが発生し、コレクタ層21側に向かって徐々に小さくなる。一方、半導体装置1における短絡時の電界強度は、ベース層12とドリフト層11との接合部近傍よりも下部電極22側であるFS層20内でピークが発生している。このように、短絡時において、電界強度のピークがFS層20内で発生するのは、図6に示されるように、FS層20のうちの電界強度における下部電極22側の端部となる部分に注入される正孔が少なく、電子が過多状態となるためである。そして、半導体装置1は、このように電界強度のピークが下部電極22側で発生すると、アバランシェ降伏が発生して破壊される可能性がある。なお、図6では、正孔をhで示し、電子をeで示している。

10

【0029】

このため、本発明者らは、短絡時において、FS層20のうちの電界強度のピークと成り得る位置に注入される正孔を増加して電子の過多状態を緩和することにより、電界強度のピークが下部電極22側で発生し難くなると考えた。そして、本発明者らは、まず、FS層20のうちの電界強度のピークと成り得る位置に注入される正孔が増加するように、コレクタ層21のキャリア濃度を高くして同様のシミュレーションを行い、図7に示す結果を得た。なお、図7は、FS層20を $2.0 \times 10^{12} \text{ cm}^{-2}$ のドーズ量で構成し、コレクタ層を $1.65 \times 10^{13} \text{ cm}^{-2}$ のドーズ量で構成し、FS層20とコレクタ層21とのピーク間距離Xを $1.5 \mu\text{m}$ とした場合のシミュレーション結果を示す図である。

20

【0030】

図7に示されるように、コレクタ層21を高キャリア濃度にしても、半導体装置1におけるオフ時の電界強度はほとんど変化しない。一方、半導体装置1における短絡時の電界強度は、FS層20内にピークが発生しておらず、ベース層12とドリフト層11との接合部近傍がピークとなっていることが確認される。このように、電界強度のピークがFS層20内で発生し難くなるのは、図8に示されるように、コレクタ層21のキャリア濃度を高くすることにより、FS層20のうちの電界強度のピークと成り得る位置に注入される正孔が増加して電子の過多状態が緩和されるためである。なお、図8では、正孔をhで示し、電子をeで示している。

30

【0031】

以上より、短絡時において、電界強度のピークが下部電極22側で発生し難いようにするためにには、FS層20のうちの電界強度のピークと成り得る位置に注入される正孔を増加させればよいことになる。なお、短絡時において、FS層20のうちの電界強度のピークと成り得る位置は、FS層20のキャリア濃度およびFS層20のキャリア濃度の最大ピーク位置に依存する。また、FS層20のうちの電界強度のピークと成り得る位置に注入される正孔の量は、コレクタ層21のキャリア濃度、およびFS層20とコレクタ層21とのピーク間距離Xに依存する。

40

【0032】

このため、本発明者らは、FS層20のキャリア濃度、コレクタ層21のキャリア濃度、FS層20とコレクタ層21とのピーク間距離Xについてさらに詳細な検討を行った。言い換えると、本発明者らは、FS層20を構成するドーズ量、コレクタ層21を構成するドーズ量、FS層20とコレクタ層21とのピーク間距離Xについてさらに詳細な検討を行った。そして、本発明者らは、図9A～図9Cに示されるシミュレーション結果を得た。

【0033】

なお、図9A～図9Cは、コレクタ層21を構成するドーズ量を $3.82 \times 10^{12} \text{ cm}^{-2}$ で一定とし、FS層20を構成するドーズ量を変化させた場合の図である。つまり、図9A～図9Cは、コレクタ層21のキャリア濃度を一定とし、FS層20のキャリア濃

50

度を変化させた場合の図である。また、図9A～図9Cは、電源電圧を757V、ゲート電極15に印加される電圧を16Vとしたシミュレーション結果であって、短絡時の下部電極22側の電界強度を示している。以下では、短絡時の下部電極22側の電界強度を単に下部の電界強度ともいう。

【0034】

さらに、図9A～図9Cにおいて、第1～第4位置は、FS層20におけるキャリア濃度のピークの位置を示しており、第1位置が他面10b側に最も近く、第2、第3、第4位置の順に他面10bから離れた位置となっている。さらに、図9A～図9C中の不純物総量比Yは、FS層20を構成するドーズ量に対するコレクタ層21を構成するドーズ量の比である。但し、FS層20のキャリア濃度は、FS層20を構成するドーズ量に依存し、コレクタ層21のキャリア濃度は、コレクタ層21を構成するドーズ量に依存する。このため、不純物総量比Yは、FS層20のキャリア濃度に対するコレクタ層21のキャリア濃度の比ということもできる。

10

【0035】

図9A～図9Cに示されるように、第1～第4位置における各プロットを用いて導出される近似曲線は、同じであることが確認される。つまり、下部の電界強度は、FS層20におけるキャリア濃度のピーク位置には依存せず、FS層20とコレクタ層21とのピーク間距離Xに依存することが確認される。すなわち、下部の電界強度は、FS層20とコレクタ層21とのピーク間距離Xが等しければ、FS層20におけるキャリア濃度のピーク位置が異なっていても同じとなる。

20

【0036】

そして、図9Aに示されるように、半導体装置1は、FS層20を構成する際のドーズ量が $4 \times 10^{12} \text{ cm}^{-2}$ である場合、つまり不純物総量比Yが0.955の場合には、ピーク間距離Xが $0.4 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。なお、下部の電界強度が上昇し始めるとは、短絡時にアバランシェ降伏が発生し易くなることである。

【0037】

同様に、図9Bに示されるように、半導体装置1は、FS層20を構成する際のドーズ量が $2 \times 10^{12} \text{ cm}^{-2}$ である場合、つまり不純物総量比Yが1.910の場合には、ピーク間距離Xが $1.2 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。

30

【0038】

さらに、図9Cに示されるように、半導体装置1は、FS層20を構成する際のドーズ量が $1 \times 10^{12} \text{ cm}^{-2}$ である場合、つまり不純物総量比Yが3.820の場合には、ピーク間距離Xが $1.8 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。

【0039】

また、本発明者らは、FS層20を構成するドーズ量およびコレクタ層21を構成するドーズ量を変化させて同様のシミュレーションを行い、図10Aおよび図10Bに示す結果を得た。

【0040】

すなわち、図10Aに示されるように、半導体装置1は、FS層20を構成する際のドーズ量が $2 \times 10^{12} \text{ cm}^{-2}$ であり、コレクタ層21を構成する際のドーズ量が $5.22 \times 10^{12} \text{ cm}^{-2}$ である場合、ピーク間距離Xが $0.7 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。つまり、半導体装置1は、不純物総量比Yが1.305である場合、ピーク間距離Xが $0.7 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。

40

【0041】

また、図10Bに示されるように、半導体装置1は、FS層20を構成する際のドーズ量が $1 \times 10^{12} \text{ cm}^{-2}$ であり、コレクタ層21を構成する際のドーズ量が $3.12 \times 10^{12} \text{ cm}^{-2}$ である場合、ピーク間距離Xが $1.7 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。つまり、半導体装置1は、不純物総量比Yが3.120である場合、ピーク間距離Xが $1.7 \mu\text{m}$ 以上になると下部の電界強度が上昇し始める。

【0042】

50

以上より、下部の電界強度は、不純物総量比Yと、FS層20とコレクタ層21とのピーク間距離Xとに依存することが確認される。そして、上記図9A～図9C、図10A、および図10Bを用いて不純物総量比YとFS層20とコレクタ層21とのピーク間距離Xとの関係について纏めると、図11に示されるようになる。なお、図11は、図9A～図9C、図10Aおよび図10Bにおける各不純物総量比Yの下部の電界強度が上昇し始めるFS層20とコレクタ層21とのピーク間距離Xをプロットした図である。

#### 【0043】

図11に示されるように、半導体装置1は、FS層20とコレクタ層21とのピーク間距離をX[μm]、不純物総量比をYとすると、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たせば、下部の電界強度が増加することを抑制できることが確認される。このため、本実施形態では、FS層20およびコレクタ層21は、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たすように形成されている。これにより、下部の電界強度が高くなることを抑制でき、短絡耐量を向上できる。

10

#### 【0044】

なお、FS層20およびコレクタ層21は、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たす範囲で形成されれば短絡耐量を向上できるが、不純物総量比Yを高くし過ぎると、テール電流によってスイッチング速度が低下する可能性がある。このため、不純物総量比Yは、用途に応じて適宜設計されることが好ましく、例えば、スイッチング速度が重要視される場合には、 $0.69X^2 + 0.08X + 0.86$ で設定される値の近傍の値とされることが好ましい。これによれば、スイッチング速度が低下することを抑制しつつ、短絡耐量の向上を図ることができる。

20

#### 【0045】

また、上記のように、FS層20とコレクタ層21とのピーク間距離Xおよび不純物総量比Yを選択する場合、コレクタ層21は、他面10bを構成する部分のキャリア濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 以上となるようにされることが好ましい。これにより、コレクタ層21を下部電極22とオーミック接触された状態とできる。

#### 【0046】

以上説明したように、本実施形態では、FS層20およびコレクタ層21は、 $Y = 0.69X^2 + 0.08X + 0.86$ を満たすように形成されている。このため、短絡時において、下部の電界強度が高くなることを抑制でき、短絡耐量の向上を図ることができる。

30

#### 【0047】

##### (第2実施形態)

第2実施形態について説明する。第2実施形態は、第1実施形態に対し、コレクタ層21におけるキャリア濃度の分布を変更したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

#### 【0048】

本実施形態の半導体装置1は、基本的な構成は上記第1実施形態と同様である。そして、本実施形態では、コレクタ層21は、図12に示されるように、キャリア濃度が複数のピークを有するように構成されている。具体的には、コレクタ層21とFS層20との積層方向を厚さ方向とすると、コレクタ層21は、厚さ方向において、キャリア濃度の最大ピーク位置が中心C1よりもドリフト層11側に位置するように形成されている。また、コレクタ層21は、厚さ方向において、キャリア濃度における最大ピークよりも小さい補助ピークが中心C1よりも他面10b側に位置するように形成されている。つまり、コレクタ層21は、厚さ方向における中心C1を基準として、キャリア濃度の分布が非対称となるように形成されている。

40

#### 【0049】

なお、このようなコレクタ層21は、例えば、加速電圧を変更した複数回のイオン注入を行うことによって形成される。

#### 【0050】

以上説明したように、本実施形態では、コレクタ層21は、キャリア濃度の最大ピーク位

50

置が中心 C 1 よりもドリフト層 1 1 側に位置するように形成されている。このため、半導体装置 1 では、F S 層 2 0 とコレクタ層 2 1 とのピーク間距離 X を短くし易くなる。したがって、例えば、コレクタ層 2 1 におけるキャリア濃度の最大ピーク位置が中心 C 1 よりも他面 1 0 b 側に位置している場合と比較して、F S 層 2 0 のうちの電界強度のピークと成り得る位置に注入される正孔を増加し易くなり、短絡耐量の向上を図ることができる。

#### 【 0 0 5 1 】

また、コレクタ層 2 1 は、当該コレクタ層 2 1 の中心 C 1 より他面側に補助ピークを有するように形成されている。このため、コレクタ層 2 1 を他面 1 0 b から深くまで形成しても、コレクタ層 2 1 における他面 1 0 b を構成する部分のキャリア濃度を  $1.0 \times 10^{-16} \text{ cm}^{-3}$  以上とし易くできる。また、コレクタ層 2 1 を他面 1 0 b から深くまで形成し易くできるため、F S 層 2 0 とコレクタ層 2 1 との界面を他面 1 0 b から深い位置にし易くできる。つまり、F S 層 2 0 と他面 1 0 b との間隔を長くし易くできる。

10

#### 【 0 0 5 2 】

ここで、上記のような半導体装置 1 は、所定の製造プロセスが行われることによって製造され、製造プロセスにおいて、例えば、半導体基板 1 0 が他面 1 0 b 側から研削等して薄くされたり、搬送等されたりする。この場合、半導体基板 1 0 の他面 1 0 b 側に傷が導入される可能性がある。そして、F S 層 2 0 が形成されている場合に F S 層 2 0 に傷が達する、または F S 層 2 0 が形成される前に F S 層 2 0 が形成される部分まで傷が達すると、当該傷によって半導体装置 1 の耐圧が変化してしまう。つまり、半導体装置 1 の特性が変化してしまう。特に、オフ時において、空乏層の端部が位置する部分まで傷が達してしまった場合には、半導体装置 1 の特性が大きく変化してしまう。

20

#### 【 0 0 5 3 】

しかしながら、本実施形態では、上記のようにコレクタ層 2 1 を形成することにより、F S 層 2 0 と他面 1 0 b との間隔を長くし易くできる。このため、本実施形態の半導体装置 1 では、F S 層 2 0 に傷が達し難い構成とできる。したがって、本実施形態では、半導体装置 1 の特性が変化することも抑制できる。言い換えると、本実施形態では、半導体装置 1 の良品効率の向上を図ることができる。

#### 【 0 0 5 4 】

##### ( 第 3 実施形態 )

第 3 実施形態について説明する。第 3 実施形態は、第 1 実施形態に対し、F S 層 2 0 におけるキャリア濃度の分布を変更したものである。その他に関しては、第 1 実施形態と同様であるため、ここでは説明を省略する。

30

#### 【 0 0 5 5 】

本実施形態の半導体装置 1 は、基本的な構成は上記第 1 実施形態と同様である。そして、本実施形態では、F S 層 2 0 は、図 1 3 に示されるように、キャリア濃度が複数のピークを有するように構成されている。具体的には、F S 層 2 0 は、厚さ方向において、キャリア濃度の最大ピーク位置が中心 C 2 よりもドリフト層 1 1 側に位置するように形成されている。

#### 【 0 0 5 6 】

これによれば、F S 層 2 0 は、最大ピーク位置が当該 F S 層 2 0 の中心 C 2 よりもドリフト層 1 1 側に位置している。このため、例えば、最大ピーク位置が当該 F S 層 2 0 の中心 C 2 に位置している場合と比較して、空乏層の端部をドリフト層 1 1 側に位置させることができる。したがって、傷が空乏層の端部となる位置まで達し難くなり、半導体装置 1 の特性が変化することを抑制できる。

40

#### 【 0 0 5 7 】

##### ( 第 4 実施形態 )

第 4 実施形態について説明する。第 4 実施形態は、第 1 実施形態に対し、F S 層 2 0 におけるキャリア濃度の分布を変更したものである。その他に関しては、第 1 実施形態と同様であるため、ここでは説明を省略する。

#### 【 0 0 5 8 】

50

本実施形態の半導体装置 1 は、基本的な構成は上記第 1 実施形態と同様である。そして、本実施形態では、F S 層 2 0 は、図 1 4 に示されるように、キャリア濃度が複数のピークを有するように構成されている。具体的には、F S 層 2 0 は、厚さ方向において、キャリア濃度の最大ピーク位置が中心 C 2 よりもコレクタ層 2 1 側に位置するように形成されている。

【 0 0 5 9 】

これによれば、F S 層 2 0 は、最大ピーク位置が当該 F S 層 2 0 の中心 C 2 よりもコレクタ層 2 1 側に位置している。このため、例えば、最大ピーク位置が当該 F S 層 2 0 の中心 C 2 に位置している場合と比較して、F S 層 2 0 とコレクタ層 2 1 とのピーク間距離 X を短くし易くできる。したがって、短絡耐量の向上を図り易くなる。

10

【 0 0 6 0 】

( 他の実施形態 )

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

【 0 0 6 1 】

例えば、上記各実施形態は、第 1 導電型が P 型であり、第 2 導電型が N 型とされていてもよい。

【 0 0 6 2 】

また、上記各実施形態は、半導体基板 1 0 の他面 1 0 b 側に N 型のカソード層が形成された R C ( Reverse-Conducting の略 ) - I G B T に適用されてもよい。

20

【 0 0 6 3 】

さらに、上記各実施形態は、トレンチ 1 3 が形成されておらず、ゲート電極 1 5 が半導体基板 1 0 の一面 1 0 a 上に形成されていてもよい。すなわち、上記各実施形態は、プレナ型の半導体装置 1 に適用することもできる。

【 0 0 6 4 】

また、上記第 2 実施形態において、図 1 5 に示されるように、コレクタ層 2 1 は、キャリア濃度の分布において、最大ピークよりも小さい補助ピークを複数有する構成とされているてもよい。さらに、上記第 2 実施形態において、コレクタ層 2 1 は、補助ピークを有しない構成とされていてもよい。

【 0 0 6 5 】

30

そして、上記各実施形態を適宜組み合わせてもよい。例えば、上記第 2 実施形態を上記第 3 、第 4 実施形態に組み合わせ、コレクタ層 2 1 のキャリア濃度が複数のピークを有するように構成されていてもよい。

【 符号の説明 】

【 0 0 6 6 】

1 0 半導体基板

1 1 ドリフト層

1 2 ベース層

1 4 ゲート絶縁膜

1 5 ゲート電極

40

1 6 エミッタ領域

1 9 第 1 電極

2 2 第 2 電極

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図 5】

【図 6】

10

【図 7】

【図 8】

20

30

40

50

【図 9 A】

【図 9 B】

【図 9 C】

【図 10 A】

10

20

30

40

50

【図 1 0 B】

【図 1 1】

【図 1 2】

【図 1 3】

10

20

30

40

50

【図 1 4】

【図 1 5】

10

20

30

40

50

---

フロントページの続き

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

審査官 岩本 勉

(56)参考文献 国際公開第2016/204126 (WO, A1)

特開2012-156207 (JP, A)

米国特許出願公開第2008/0001257 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 29/739

H01L 29/78