(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4238377号

(P4238377)

(45) 発行日 平成21年3月18日(2009.3.18)

(24) 登録日 平成21年1月9日(2009.1.9)

(51) Int.Cl.

H04N 5/335 (2006.01)

H01L 27/146 (2006.01)

F 1

H04N 5/335

H01L 27/14E

A

請求項の数 7 (全 15 頁)

(21) 出願番号 特願平10-22867

(22) 出願日 平成10年2月4日(1998.2.4)

(65) 公開番号 特開平11-122534

(43) 公開日 平成11年4月30日(1999.4.30)

審査請求日 平成17年1月14日(2005.1.14)

(31) 優先権主張番号 特願平9-220264

(32) 優先日 平成9年8月15日(1997.8.15)

(33) 優先権主張国 日本国(JP)

前置審査

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100086298

弁理士 舟橋 國則

(72) 発明者 塩野 浩一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 鈴木 亮司

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 上野 貴久

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像素子およびその駆動方法

(57) 【特許請求の範囲】

【請求項 1】

入射光を光電変換しあつ光電変換によって得られた信号電荷を蓄積する光電変換素子と、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセッ

トスイッチをオン／オフ制御するリセット選択スイッチと

を有し、前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通の垂直信号線を経由して出力する単位画素と、

前記単位画素から出力されたリセット前の信号とリセット後の信号のそれぞれの差分をとる差分回路とを備え、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

ことを特徴とする固体撮像素子。

【請求項 2】

前記単位画素が行列状に2次元配置されてなる

10

20

ことを特徴とする請求項1記載の固体撮像素子。

**【請求項3】**

前記垂直信号線と水平信号線との間に、前記垂直信号線に導出された前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通に出力する水平選択スイッチを備えた

ことを特徴とする請求項2記載の固体撮像素子。

**【請求項4】**

前記差分回路は、相関二重サンプリング回路である

ことを特徴とする請求項1記載の固体撮像素子。

**【請求項5】**

前記単位画素が直線状に1次元配置されてなる

ことを特徴とする請求項1記載の固体撮像素子。

**【請求項6】**

前記リセットスイッチは前記光電変換素子と電源線の間に接続されている

ことを特徴とする請求項5記載の固体撮像素子。

**【請求項7】**

入射光を光電変換しあつ光電変換によって得られた信号電荷を蓄積する光電変換素子と

、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセットスイッチをオン／オフ制御するリセット選択スイッチとを有し、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

単位画素を備えた固体撮像素子において、

単位画素の各々において画素信号を出力するごとに前記リセットスイッチによって前記光電変換素子をリセットし、

単位画素の各々から前記リセットスイッチによるリセット前の信号とリセット後の信号とを導出しあつ共通の伝送経路を経由して伝送し、

かかる後リセット前の信号とリセット後の信号のそれぞれの差分をとる

ことを特徴とする固体撮像素子の駆動方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、固体撮像素子およびその駆動方法に関し、特に単位画素ごとに増幅機能を持つMOS型イメージセンサなどの増幅型固体撮像素子およびその駆動方法に関する。

**【0002】**

**【従来の技術】**

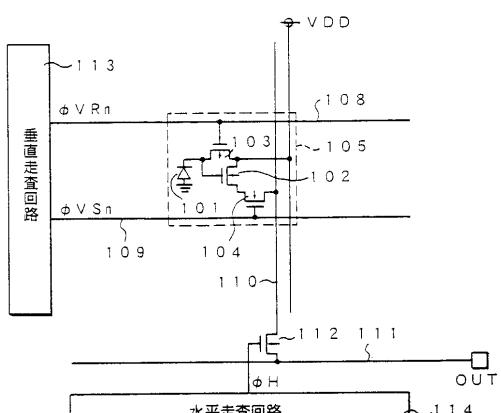

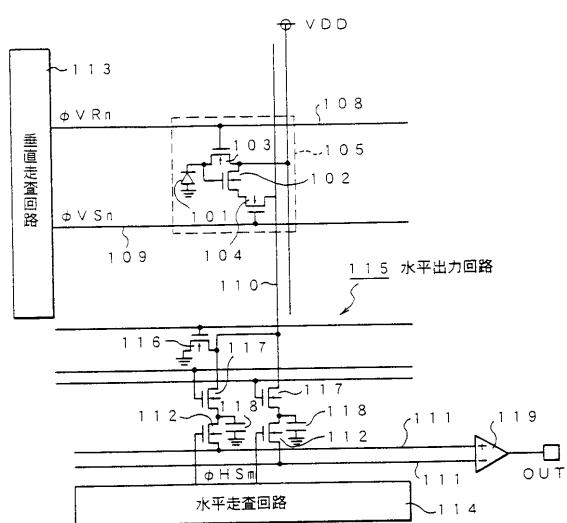

従来、この種の増幅型固体撮像素子として、図13に示す構成の2次元固体撮像素子が知られている。すなわち、図13において、フォトダイオード101、増幅用MOSトランジスタ102、リセット用MOSトランジスタ103および垂直選択用MOSトランジスタ104によって単位画素105が構成され、リセット用MOSトランジスタ103のゲート電極が垂直リセット線108に、垂直選択用MOSトランジスタ104のゲート電極が垂直選択線109に、垂直選択用MOSトランジスタ104のソース電極が垂直信号線110にそれぞれ接続されている。

**【0003】**

また、垂直信号線110の一端と水平信号線111の間には、水平選択用MOSトランジ

10

20

30

40

50

スタ 1 1 2 が接続されている。そして、行選択をする垂直走査回路 1 1 3 から出力される 2 種類の垂直走査パルス V S n , V R n により各行ごとに画素の動作が制御され、列選択をする水平走査回路 1 1 4 から出力される水平走査パルス H m により制御される水平選択用 M O S ドラゴンジスタ 1 1 2 を介して画素信号が水平信号線 1 1 1 に出力される。その際、光電変換によってフォトダイオード 1 0 1 に蓄積された信号電荷が、増幅用 M O S ドラゴンジスタ 1 0 2 によって信号電流に変換されて撮像素子の出力信号として導出される。

#### 【 0 0 0 4 】

##### 【発明が解決しようとする課題】

しかしながら、上記構成の従来の増幅型 2 次元固体撮像素子では、各画素を構成する能動素子、主に増幅用 M O S ドラゴンジスタ 1 0 2 の特性の画素ごとのバラツキ、特に M O S ドラゴンジスタの V t h ( 閾値 ) バラツキがそのまま撮像素子の出力信号に乗ってきてしまう。この特性のバラツキは、画素ごとに固定の値を持つため、画面上に固定パターンノイズ ( F P N ; Fixed Patern Noise) として現れる。この固定パターンノイズを抑圧するためには、デバイスの外部にフレームメモリやラインメモリを用いたノイズ除去回路を設けて画素の特性のバラツキに起因するノイズ成分を除去する必要があり、したがって本固体撮像素子を撮像デバイスとして用いる例えばカメラシステムでは、ノイズ除去回路を外付けとする分だけ規模が大きくなってしまう。

#### 【 0 0 0 5 】

これに対し、固定パターンノイズをデバイスの内部で抑圧できるようにした増幅型固体撮像素子として、図 1 4 に示す構成のものが考えられる。この増幅型固体撮像素子においては、単位画素 1 0 5 の構成は図 1 3 と同じであるが、各画素 1 0 5 の特性のバラツキに起因する固定パターンノイズを抑圧するための水平出力回路 1 1 5 を設け、この水平出力回路 1 1 5 で画素 1 0 5 の読み出し前後 ( リセット前後 ) の信号の差分をとる処理を行うようしている点が違う。

#### 【 0 0 0 6 】

図 1 4 において、垂直信号線 1 1 0 とグランドとの間には、増幅用 M O S ドラゴンジスタ 1 0 2 のソースフォロワ動作の負荷として働く負荷用 M O S ドラゴンジスタ 1 1 6 が接続されている。また、垂直信号線 1 1 0 には、一対の信号スイッチ用 M O S ドラゴンジスタ 1 1 7 , 1 1 7 の各一方の主電極が接続されている。この一対の信号スイッチ用 M O S ドラゴンジスタ 1 1 7 , 1 1 7 の其他方の主電極とグランドとの間には、一対の信号保持用キャパシタ 1 1 8 , 1 1 8 がそれぞれ接続されている。

#### 【 0 0 0 7 】

また、一対の信号スイッチ用 M O S ドラゴンジスタ 1 1 7 , 1 1 7 の其他方の主電極と一対の水平信号線 1 1 1 , 1 1 1 の間には、一対の水平選択用 M O S ドラゴンジスタ 1 1 2 , 1 1 2 がそれぞれ接続されている。一対の水平信号線 1 1 1 , 1 1 1 には、差動アンプ 1 1 9 の非反転 ( + ) 入力端および反転 ( - ) 入力端がそれぞれ接続されている。

#### 【 0 0 0 8 】

上記構成の増幅型固体撮像素子においては、画素リセット前とリセット後のそれぞれの信号が、信号スイッチ用 M O S ドラゴンジスタ 1 1 7 , 1 1 7 を介して信号保持用キャパシタ 1 1 8 , 1 1 8 に保持され、水平選択用 M O S ドラゴンジスタ 1 1 2 , 1 1 2 および水平信号線 1 1 1 , 1 1 1 を介して差動アンプ 1 1 9 に供給される。そして、差動アンプ 1 1 9 において、画素リセット前とリセット後のそれぞれの信号の差分がとられることにより、単位画素ごとの特性のバラツキに起因する固定パターンノイズが除去される。

#### 【 0 0 0 9 】

しかしながら、上記構成の増幅型固体撮像素子では、単位画素ごとの特性のバラツキに起因する固定パターンノイズについては抑圧することはできるものの、画素リセット前とリセット後のそれぞれの信号が別々の信号経路を通じて差動アンプ 1 1 9 に至ることから、一対の信号スイッチ用 M O S ドラゴンジスタ 1 1 7 , 1 1 7 や一対の水平選択用 M O S ドラゴンジスタ 1 1 2 , 1 1 2 の特性のバラツキが、垂直に相關を持つ縦筋状の固定パター

10

20

30

40

50

ンノイズとして画面上に現れることになる。したがって、この構成の場合にも、縦筋状の固定パターンノイズを抑圧するための補正回路がデバイスの外部に必要となる。

#### 【0010】

本発明は、上記課題に鑑みてなされたものであり、その目的とするところは、単位画素ごとの特性のバラツキに起因する固定パターンノイズのみならず、縦筋状の固定パターンノイズをもデバイス内部で抑圧可能な増幅型固体撮像素子およびその駆動方法を提供することにある。

#### 【0011】

##### 【課題を解決するための手段】

本発明による固体撮像素子は、

10

入射光を光電変換しあつ光電変換によって得られた信号電荷を蓄積する光電変換素子と、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセットスイッチをオン／オフ制御するリセット選択スイッチと

を有し、前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通の垂直信号線を経由して出力する単位画素と、

20

前記単位画素から出力されたリセット前の信号とリセット後の信号のそれぞれの差分をとる差分回路とを備え、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

構成となっている。

#### 【0012】

また、本発明による駆動方法は、上記構成の固体撮像素子において、単位画素の各々で画素信号を出力するごとに光電変換素子をリセットスイッチによってリセットし、単位画素の各々からリセットスイッチによるリセット前の信号とリセット後の信号とを導出しあつ共通の伝送経路を経由して伝送し、しかる後リセット前の信号とリセット後の信号のそれぞれの差分をとるようにする。

30

#### 【0013】

上記構成の固体撮像素子の単位画素の各々において、画素信号を出力するごとに光電変換素子をリセットすることで、各単位画素からはリセット前とリセット後の信号が1画素ごとに順次出力される。このとき、画素の特性のバラツキに起因する固定パターンノイズが、各画素の増幅素子からオフセット成分として発生することから、リセット前とリセット後の信号の差分をとることで、ノイズ成分をキャンセルできる。また、2次元固体撮像素子においては、リセット前とリセット後の信号を垂直信号線から水平信号線へ同一の信号経路を経由して出力することで、垂直に相關を持つ縦筋状のノイズ成分も原理的に発生しない。

40

#### 【0014】

##### 【発明の実施の形態】

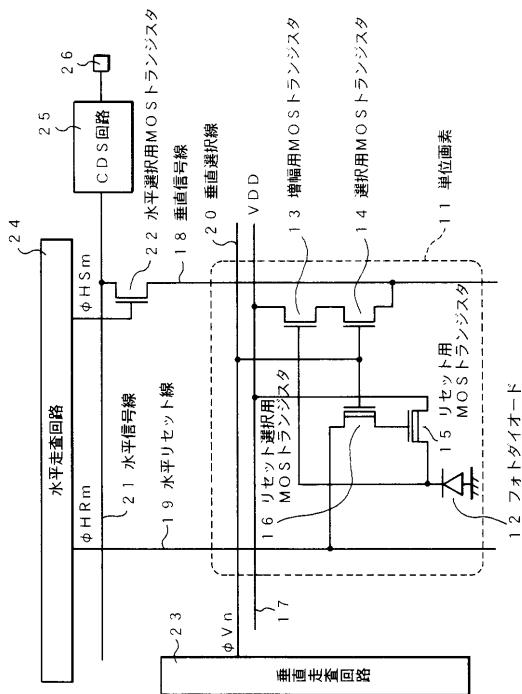

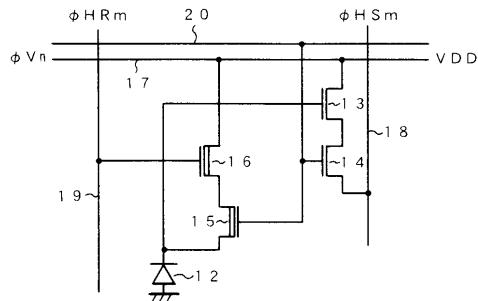

以下、本発明の実施の形態について図面を用いて詳細に説明する。図1は、2次元固体撮像素子に適用された本発明の第1実施形態を示す構成図である。

#### 【0015】

図1において、破線で囲まれた領域が単位画素11を表している。この単位画素11は、光電変換素子であるフォトダイオード(PD)12と、増幅素子である増幅用MOSトランジスタ13と、選択スイッチである選択用MOSトランジスタ14と、リセットスイッチであるリセット用MOSトランジスタ15と、リセット選択用MOSトランジスタ16

50

とから構成され、行列状に2次元配置されている。なお、図面上においては、簡略化のため、m列n行目の単位画素11のみを示している。

#### 【0016】

この単位画素11において、フォトダイオード12は入射光を光電変換しつつ光電変換によって得られた信号電荷を蓄積する機能を持つ。このフォトダイオード12のカソード電極には、増幅用MOSトランジスタ13のゲート電極が接続されている。増幅用MOSトランジスタ13のドレイン電極は、電源(VDD)線17に接続されている。増幅用MOSトランジスタ13のソース電極と垂直信号線18の間には、選択用MOSトランジスタ14が接続されている。

#### 【0017】

また、フォトダイオード12のカソード電極と電源線17の間には、リセット用MOSトランジスタ15が接続されている。リセット用MOSトランジスタ15のゲート電極と水平リセット線19の間には、リセット選択用MOSトランジスタ16が接続されている。リセット用MOSトランジスタ15およびリセット選択用MOSトランジスタ16としては、デプレッション型トランジスタが用いられている。このリセット選択用MOSトランジスタ16のゲート電極は、選択用MOSトランジスタ14のゲート電極と共に、垂直選択線20に接続されている。また、垂直信号線18と水平信号線21の間には、水平選択用MOSトランジスタ22が接続されている。

#### 【0018】

また、行選択のための垂直走査回路23および列選択のための水平走査回路24が設けられている。そして、垂直走査回路23から出力される垂直走査パルスVnが垂直選択線20に印加され、水平走査回路24から出力される水平リセットパルスHRmが水平リセット線19に、水平走査パルスHSmが水平選択用MOSトランジスタ22のゲート電極にそれぞれ印加される。すなわち、水平走査回路24が、水平リセットパルスHRmを発生するリセット回路を兼ねることにより、回路構成の簡略化を図っている。

#### 【0019】

水平信号線21の出力端側には、画素リセット前とリセット後のそれぞれの信号の差分をとる差分回路として、例えば回路構成が簡単な相関二重サンプリング回路(以下、CDS(Correlated Double Sampling)回路と称する)25が設けられている。このCDS回路25の具体的な回路構成およびその回路動作については、後で詳細に説明する。CDS回路25の出力端は、本撮像素子の出力端子26に接続されている。

#### 【0020】

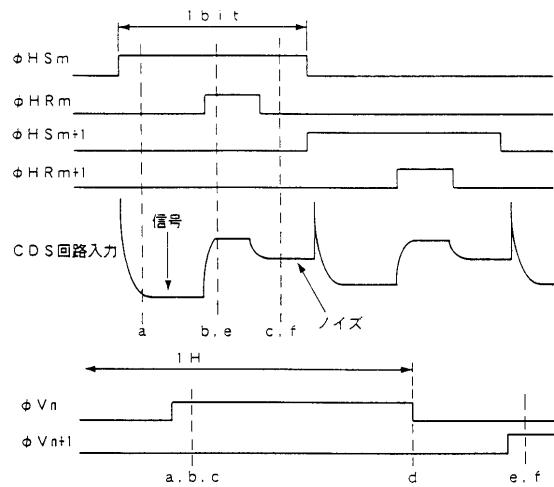

次に、上記構成の第1実施形態に係る増幅型固体撮像素子の動作について、図2のタイミングチャートを用いて説明する。

#### 【0021】

先ず、光電変換によってフォトダイオード12に蓄積された信号電荷(電子)は、増幅用MOSトランジスタ13によって電気信号に変換される。そして、水平映像期間に入ると、垂直走査回路23から垂直走査パルスVnが出力され、垂直選択線20を介して選択用MOSトランジスタ14およびリセット選択用MOSトランジスタ16の各ゲート電極に印加される。これにより、両MOSトランジスタ14, 16が導通状態になり、選択用MOSトランジスタ14を通して信号電流が垂直信号線18に現れる。

#### 【0022】

この水平映像期間中に、水平走査回路24から水平走査パルスHSmが出力され、水平選択用MOSトランジスタ22のゲート電極に印加されることによって当該MOSトランジスタ22が導通状態になる。これにより、垂直信号線20に現れた信号電流は、水平選択用MOSトランジスタ22を通して水平信号線21に流れ、この水平信号線21を経てCDS回路25に供給される。

#### 【0023】

その後すぐに、信号電流を出力したその同一画素に対し、水平走査回路24から水平リセットパルスHRmが水平リセット線19に対して出力される。このとき、リセット選択

10

20

30

40

50

用MOSトランジスタ16が導通状態にあることから、水平リセットパルス H R mはこのリセット選択用MOSトランジスタ16を通してリセット用MOSトランジスタ15のゲート電極に印加される。これにより、リセット用MOSトランジスタ15が導通状態になるため、フォトダイオード12はVDDレベルにリセットされる。

#### 【0024】

この水平リセットパルス H R mは、図2のタイミングチャートから明らかなように、水平走査パルス H S mの発生期間のほぼ中間で発生される。したがって、水平リセットパルス H R mの消滅後、即ちリセット後のフォトダイオード12の電荷（ノイズ成分）が増幅用MOSトランジスタ13で電流に変換され、そのリセット電流が導通状態にある選択用MOSトランジスタ14、垂直信号線18および導通状態にある水平選択用MOSトランジスタ22を通して水平信号線21に流れ、この水平信号線21を経てCDS回路25に供給される。10

#### 【0025】

以上の一連の動作により、1つの画素11について信号出力 P D リセット ノイズ出力という形で信号出力とリセット出力が順次得られる。これを垂直走査回路23で選択された画素行に対して、水平走査回路24によって順次画素選択を行うことにより、m列n行（信号出力 P D リセット ノイズ出力）、m+1列n行（信号出力 P D リセット ノイズ出力）、……という順番で水平信号線21に出力され、CDS回路25に供給される。そして、このCDS回路25において、リセット前の信号出力とリセット後のノイズ出力を使って相關二重サンプリングを行うことにより、主に増幅用MOSトランジスタ13の特性のバラツキ成分を除去することができる。20

#### 【0026】

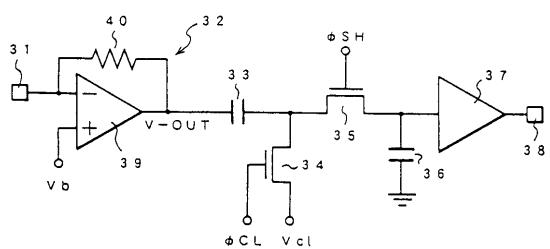

図3に、CDS回路25の具体的な回路構成の一例を示す。このCDS回路25は、入力端子31に入力端が接続された電流電圧変換回路32と、この電流電圧変換回路32の出力端に一端が接続されたクランプキャパシタ33と、このクランプキャパシタ33の他端に一方の主電極が接続されたクランプMOSトランジスタ34と、クランプキャパシタ33の他端に一方の主電極が接続されたサンプルホールドMOSトランジスタ35と、このサンプルホールドMOSトランジスタ35の他方の主電極とグランドとの間に接続されたサンプルホールドキャパシタ36と、サンプルホールドMOSトランジスタ35の他方の主電極と出力端子38との間に接続されたバッファアンプ37とから構成されている。30

#### 【0027】

このCDS回路25において、電流電圧変換回路32は、入力端子31を介して供給される信号電流を反転（-）入力とし、所定のバイアス電圧Vbを非反転（+）入力とする差動アンプ39と、この差動アンプ39の反転入力端と出力端間に接続された帰還抵抗40とからなり、信号電流を信号電圧に変換する。クランプMOSトランジスタ34の他方の主電極にはクランプ電圧Vc1が、そのゲート電極にはクランプパルス CL がそれぞれ印加される。また、サンプルホールドMOSトランジスタ35のゲート電極には、サンプルホールドパルス SH が印加される。

#### 【0028】

上記構成のCDS回路25を差分回路として用い、リセット前の信号出力とリセット後のノイズ出力を使って相關二重サンプリングを行うことにより、増幅用MOSトランジスタ13の特性の画素ごとのバラツキ、特にMOSトランジスタのVthバラツキを除去することができる。40

#### 【0029】

上述したように、各単位画素11のフォトダイオード12のリセットを、1画素の信号が出力されるごとにに行うようにするとともに、リセット前の信号出力とリセット後のノイズ出力を使って相關二重サンプリングを行うようにしたことにより、画素の特性のバラツキに起因する固定パターンノイズおよび垂直信号線18に接続されたスイッチ素子（水平選択用MOSトランジスタ22）の特性のバラツキに起因する縦筋状の固定パターンノイズを抑圧できる。50

**【0030】**

すなわち、画素の特性のバラツキに起因する固定パターンノイズについては、単位画素11の増幅用MOSトランジスタ13からオフセット成分として発生するが、原理的に、画素リセット前とリセット後の信号を相關二重サンプリングすることによって除去できる。また、垂直信号線18に接続されたスイッチ素子の特性のバラツキに起因する縦筋状の固定パターンノイズについては、画素リセット前とリセット後の信号が同一の信号経路を通る構成となっており、別々のスイッチ素子（水平選択用MOSトランジスタなど）を通ることがないため、これも原理的に発生することがない。

**【0031】**

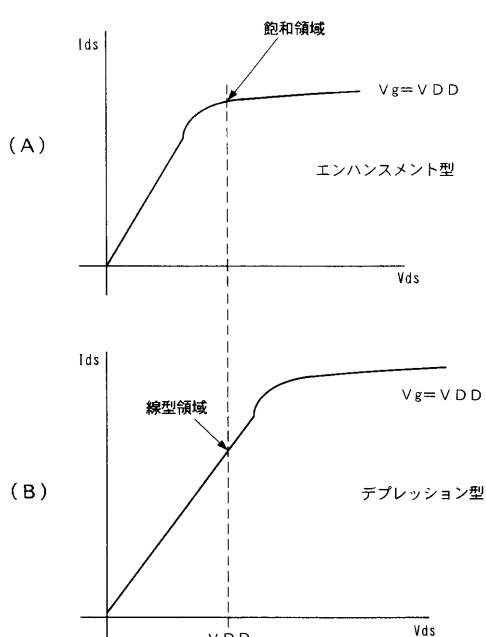

ここで、フォトダイオード12のリセット動作についてさらに詳しく述べる。なお、図1から明らかのように、リセット用MOSトランジスタ15およびリセット選択用MOSトランジスタ16として、デプレッション型トランジスタが用いられている。10

**【0032】**

フォトダイオード12をVDDレベルにリセットする際に、リセット選択用MOSトランジスタ16にエンハンスマント型トランジスタを使った場合には、垂直走査パルスVnによって選択された状態において、水平リセットパルスHRmがリセット選択用MOSトランジスタ16のドレイン電極に印加されても、図4(A)に示すように、飽和領域の動作となるために、ソース側の電位はドレイン側の電位よりも落ちてしまうことになる。

**【0033】**

これに対し、リセット選択用MOSトランジスタ16としてデプレッション型トランジスタを使うことにより、図4(B)に示すように、線型領域での動作となり、ソース側の電位がほぼドレイン側の電位まで達する。同様に、リセット用MOSトランジスタ15にもエンハンスマント型トランジスタを用いると、飽和領域でのリセット動作となり、リセットの時間が短いと電荷の取り残しが生じ、残像の原因となる。これに対し、デプレッション型トランジスタを用いて線型領域でリセットすることにより、電荷の取り残しの無い、完全なリセット動作が可能となる。20

**【0034】**

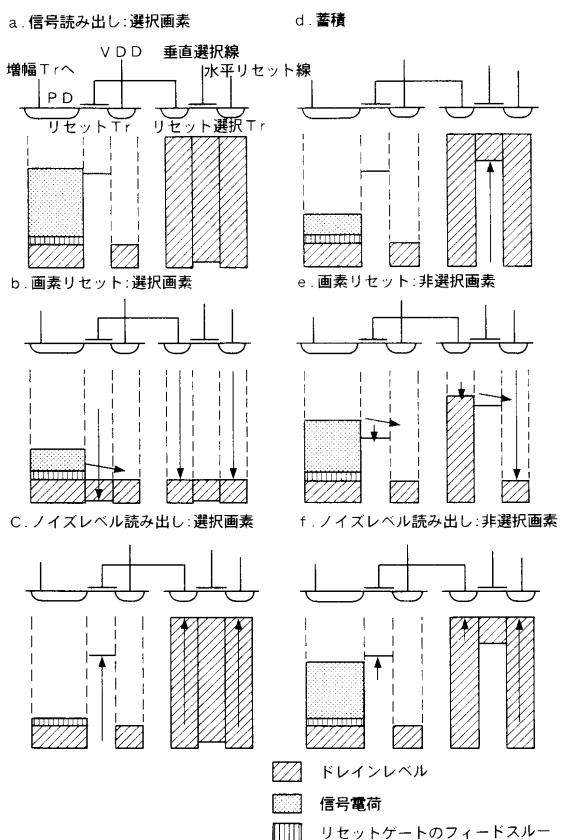

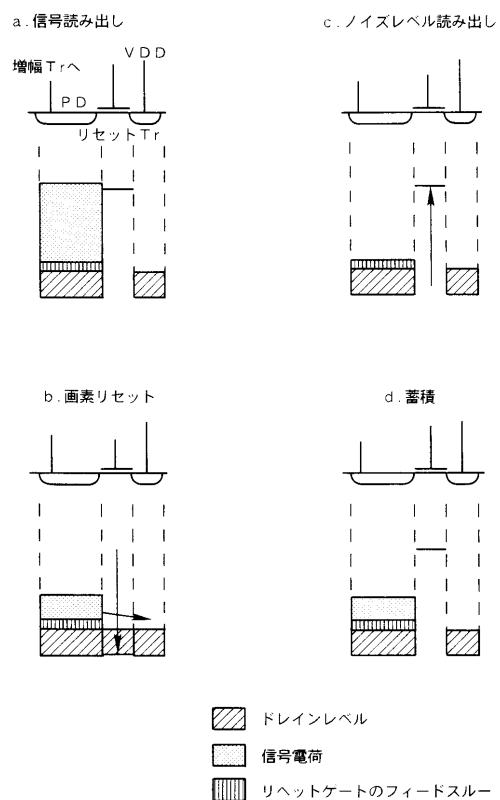

次に、上記構成の第1実施形態に係る増幅型固体撮像素子の動作について、図2のタイミングチャートに基づいて図5のポテンシャル図を用いて説明する。

**【0035】**

選択画素の信号読み出し時（図2のタイミングa）には、垂直走査パルスVnによってリセット選択用MOSトランジスタ16が導通状態となり、ソース側の電位である水平リセットパルスHRmの“L”レベルの電位がリセット用MOSトランジスタ15のゲート電極に印加される。このとき、リセット用MOSトランジスタ15は導通状態にならないので、フォトダイオード12に蓄積された信号電荷が増幅用MOSトランジスタ13で信号電流に変換される。30

**【0036】**

選択画素のリセット時（図2のタイミングb）には、“H”レベルの水平リセットパルスHRmが導通状態のリセット選択用MOSトランジスタ16を経てリセット用MOSトランジスタ15のゲート電極に印加され、これによりリセット用MOSトランジスタ15が導通状態となるため、フォトダイオード12がVDDレベルにリニア領域で完全リセットされる。40

**【0037】**

選択画素のノイズレベル読み出し時（図2のタイミングc）には、水平リセットパルスHRmが“L”レベルの状態にあり、この“L”レベルが導通状態のリセット選択用MOSトランジスタ16を経てリセット用MOSトランジスタ15のゲート電極に印加されることによってリセット用MOSトランジスタ15が非導通状態になる。これにより、リセットのレベルが増幅用MOSトランジスタ13でノイズ電流に変換される。また、この時点より次のフレーム蓄積が開始される。

**【0038】**

信号電荷の蓄積時(図2のタイミングd)、即ち他の行の他の列の読み出し時には、垂直走査パルス  $V_m$  が“L”レベルに遷移するが、リセット選択用MOSトランジスタ16がデプレッション型であるために、リセット用MOSトランジスタ15のゲート電極はフローティング状態にはならず、“L”レベルに保たれる。

#### 【0039】

非選択画素のリセット時(図2のタイミングe)には、“H”レベルの水平リセットパルス  $H_{Rm}$  によりリセット選択用MOSトランジスタ16のドレインがVDDレベルになると、リセット選択用MOSトランジスタ16のゲート電極の“L”レベルのポテンシャルに応じた電位が、リセット用MOSトランジスタ15のゲート電極に印加される。なお、フォトダイオード12は、デプレッションのリセットゲートがそのまま横型オーバーフローバリアになっていて、このレベルを超える電荷は電源へと捨てられるようになっているが、この時点でオーバーフローバリアが下がり、ここでオーバーフローレベルが決まる。

10

#### 【0040】

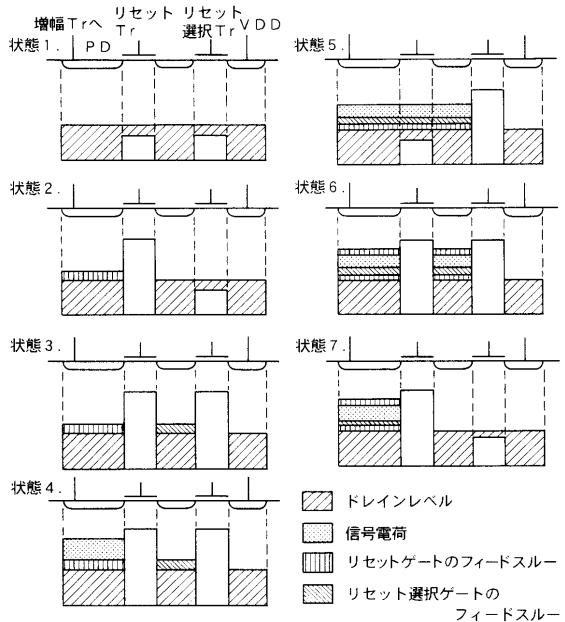

ところで、単位画素の構成を考えた場合に、図6又は図7に示すように、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16を、フォトダイオード12のカソード電極と電源線17の間に直列に接続し、リセット用MOSトランジスタ15のゲート電極に水平リセットパルス  $H_{Rm}$  又は垂直走査パルス  $V_n$  を、リセット選択用MOSトランジスタ16のゲート電極に垂直走査パルス  $V_n$  又は水平リセットパルス  $H_{Rm}$  を印加する構成が一般的に考えられる。

20

#### 【0041】

しかしながら、これらの構成の場合には、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16によるフィードスルーが、信号レベルを読み出す際とノイズレベルを読み出す際で異なってしまい、これが画素ごとのバラツキの原因となる。その理由について、図6の構成に対応した図8のポテンシャル図を用いて以下に説明する。

#### 【0042】

先ず、垂直走査パルス  $V_n$  の発生によって画素が選択され、水平リセットパルス  $H_{Rm}$  の発生によってリセットされているときを状態1.とする。この状態1.では、フォトダイオード12はVDDレベルにリセットされている。そして、状態2.では、水平リセットパルス  $H_{Rm}$  が消滅し、リセット用MOSトランジスタ15がオフする際のフィードスルーの影響で、フォトダイオード12のポテンシャルはVDDレベルよりも僅かに浅くなる。この状態でノイズレベルの読み出しどとなる。

30

#### 【0043】

状態3.では、垂直走査パルス  $V_n$  が消滅することで非選択状態となる。リセット選択用MOSトランジスタ16がオフする際のフィードスルーの影響で、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16の間の拡散領域のポテンシャルはVDDレベルよりも僅かに浅くなる。

#### 【0044】

状態4.は電荷の蓄積状態であり、フォトダイオード12のポテンシャルが蓄積された電荷により浅くなっていく。状態5.は、非選択のリセット状態、即ち他の行の同じ列がリセットされている状態であり、水平リセットパルス  $H_{Rm}$  の発生により、リセット用MOSトランジスタ15が導通状態となり、信号電荷とリセットゲートのフィードスルーおよびリセット選択ゲートのフィードスルーが合わされる。

40

#### 【0045】

状態6.で水平リセットパルス  $H_{Rm}$  が消滅するときに、さらにフォトダイオード12にリセットゲートのフィードスルーが加わる。他の行を読み出している期間中、状態5.状態6.を繰り返す。状態7.で、垂直走査パルス  $V_n$  の発生により、リセット選択用MOSトランジスタ16が導通状態となり、この状態で信号レベルが読み出される。この後、状態1.に戻る。

#### 【0046】

50

図8のポテンシャル図において、状態2.と状態7.の比較から明らかなように、状態7.の信号レベルの読み出し時と、状態2.のノイズレベルの読み出し時では、フォトダイオード12に蓄えられているフィードスルーによる電荷の量が異なる。フィードスルーの量は、Vthバラツキと同様に個々のトランジスタによって異なるので、信号レベルの読み出しとノイズレベルの読み出しのフィードスルーの違いは、画素バラツキを抑圧するためのCDS回路25ではキャンセルすることができず、そのまま画素バラツキとして残ってしまう。

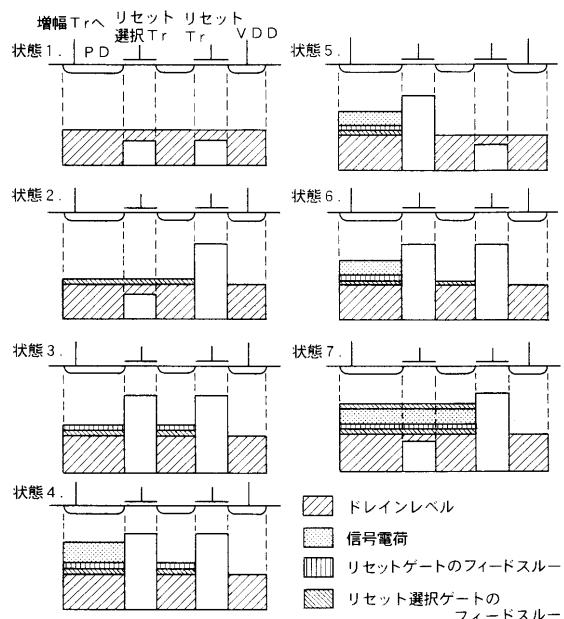

#### 【0047】

リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16の接続関係を逆にした図7の構成の場合にも、図9のポテンシャル図から明らかなように、図6の構成の場合と同様のことが言える。10

#### 【0048】

これに対し、本実施形態においては、リセット用MOSトランジスタ15のゲート電極に、リセット選択用MOSトランジスタ16のソース電極を接続し、リセット選択用MOSトランジスタ16のドレイン電極、ソース電極を介してリセット用MOSトランジスタ15のゲート電極に水平リセットパルス HRmを印加する構成としたことで、ノイズ読み出し時、信号読み出し時のいずれにおいても、リセット選択ゲートによるフィードスルーの影響がないので、各画素ごとのリセットゲートによるフィードスルーのバラツキは後段のCDS回路25で抑圧することができる。

#### 【0049】

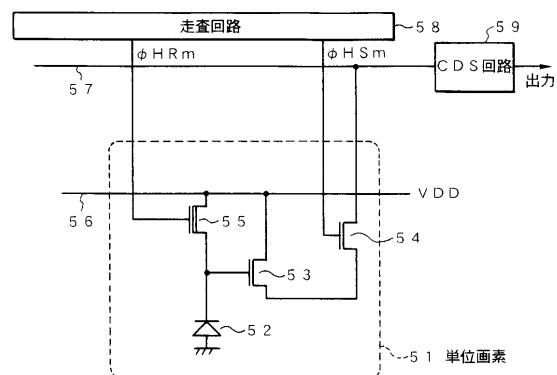

図10は、1次元固体撮像素子に適用された本発明の第2実施形態を示す構成図である。20

#### 【0050】

図10において、破線で囲まれた領域が単位画素51を表している。この単位画素51は、光電変換素子であるフォトダイオード(PD)52と、增幅素子である増幅用MOSトランジスタ53と、選択スイッチである選択用MOSトランジスタ54と、リセットスイッチであるリセット用MOSトランジスタ55とから構成され、直線状に1次元配置されている。

#### 【0051】

この単位画素51において、フォトダイオード52は入射光を光電変換しつつ光電変換によって得られた信号電荷を蓄積する機能を持つ。このフォトダイオード52のカソード電極には、増幅用MOSトランジスタ53のゲート電極が接続されている。増幅用MOSトランジスタ53のドレイン電極は、電源(VDD)線56に接続されている。30

#### 【0052】

増幅用MOSトランジスタ53のソース電極と信号線57の間には、選択用MOSトランジスタ54が接続されている。また、フォトダイオード52のカソード電極と電源線56の間には、リセット用MOSトランジスタ55が接続されている。このリセット用MOSトランジスタ55としては、デプレッション型トランジスタが用いられている。

#### 【0053】

また、1次元配列された単位画素51を順に選択するための走査回路58が設けられている。そして、この走査回路58から出力される走査パルス HSmが選択用MOSトランジスタ54のゲート電極に、リセットパルス HRmがリセット用MOSトランジスタ55のゲート電極にそれぞれ印加される。すなわち、走査回路58が、リセットパルス HRmを発生するリセット回路を兼ねることにより、回路構成の簡略化を図っている。40

#### 【0054】

信号線57の出力端側には、画素リセット前とリセット後のそれぞれの信号の差分をとる差分回路として、例えば回路構成が簡単なCDS回路59が設けられている。このCDS回路59としては、先の実施形態の場合と同様に、図3に示す回路構成のものが用いられる。

#### 【0055】

10

20

30

40

50

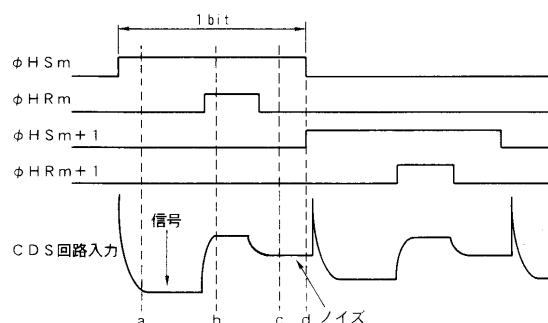

次に、上記構成の第2実施形態に係る増幅型固体撮像素子の動作について、図11のタイミングチャートを用いて説明する。

#### 【0056】

先ず、光電変換によってフォトダイオード52に蓄積された信号電荷（電子）は、増幅用MOSトランジスタ53によって電荷信号に変換される。そして、走査回路58から走査パルスHSmが出力されると、選択用MOSトランジスタ54が導通状態になり、この選択用MOSトランジスタ54を通して信号電流が信号線57を経てCDS回路59に供給される。

#### 【0057】

その後すぐに、信号電流を出力した同一画素に対し、走査回路58からリセットパルスH Rmが出力され、リセット用MOSトランジスタ55のゲート電極に印加される。これにより、リセット用MOSトランジスタ55が導通状態となるため、フォトダイオード52はVDDレベルにリセットされる。

10

#### 【0058】

このリセットパルスH Rmは、図11のタイミングチャートから明らかなように、走査パルスHSmの発生期間（“H”レベルの期間）内で発生される。したがって、リセットパルスH Rmの消滅後、即ちリセット後のフォトダイオード52の電荷（ノイズ成分）が増幅用MOSトランジスタ53で電流に変換され、そのリセット電流が導通状態にある選択用MOSトランジスタ54を通して信号線57に流れ、この信号線57を経てCDS回路59に供給される。

20

#### 【0059】

以上の一連の動作により、1つの画素51について信号出力PDLリセットノイズ出力という形で信号出力とリセット出力が順次得られ、CDS回路59に供給される。そして、CDS回路59において、リセット前の信号出力とリセット後のノイズ出力を使って相關二重サンプリングを行うことにより、主に増幅用MOSトランジスタ53の特性のバラツキ成分を抑圧することができる。

#### 【0060】

ここで、フォトダイオード52のリセット動作についてさらに詳しく述べる。なお、図10から明らかなように、リセット用MOSトランジスタ55として、デプレッション型トランジスタが用いられている。

30

#### 【0061】

フォトダイオード52をVDDレベルにリセットする際に、リセット用MOSトランジスタ55にエンハンスマント型トランジスタを使った場合には、リセットパルスH Rmによって選択された状態でリセット用MOSトランジスタ55のドレイン電極に電源VDDが印加されても、図4(A)に示すように、飽和領域の動作となるため、ソース側の電位はドレイン側の電位よりも落ちてしまい、リセットの時間が短いと電荷の取り残しが生じ、残像の原因となる。

#### 【0062】

これに対して、リセット用MOSトランジスタ55としてデプレッション型トランジスタを使うことにより、図4(B)に示すように、線型領域での動作となり、ソース側の電位がほぼドレイン側の電位まで達するため、電荷の取り残しの無い、完全なリセット動作が可能となる。

40

#### 【0063】

続いて、上記構成の第2実施形態に係る増幅型固体撮像素子の動作について、図11のタイミングチャートに基づいて図12のポテンシャル図を用いて説明する。

#### 【0064】

信号読み出し時（図11のタイミングa）には、リセット用MOSトランジスタ55は導通状態にはならないので、フォトダイオード52に蓄積された信号電荷が増幅用MOSトランジスタ53で信号電流に変換される。

#### 【0065】

50

リセット時(図11のタイミングb)には、“H”レベルのリセットパルス H R mがリセット用MOSトランジスタ55のゲート電極に印加され、これによりリセット用MOSトランジスタ55が導通状態となるため、フォトダイオード52がVDDレベルにリニア領域で完全リセットされる。

#### 【0066】

ノイズレベル読み出し時(図11のタイミングc)には、リセットパルス H R mが“L”レベルの状態にあり、リセット用MOSトランジスタ55が非導通状態になる。これにより、リセットのレベルが増幅用MOSトランジスタ53でノイズ電流に変換される。また、この時点(図11のタイミングd)より次のフレーム蓄積が開始される。

#### 【0067】

なお、フォトダイオード52は、デプレッションのリセットゲートがそのまま横型オーバーフローバリアになっていて、このレベルを超える電荷は電源へと捨てられるようになっている。オーバーフローレベルは、リセット用MOSトランジスタ55のゲート電位の“L”レベルのポテンシャルである。

#### 【0068】

#### 【発明の効果】

以上説明したように、本発明によれば、単位画素ごとに増幅機能を持つ固体撮像素子において、単位画素の各々で画素信号を出力するごとに光電変換素子を完全リセットする構成としたことにより、各画素より信号成分とノイズ成分を順次出力することができるので、リセット前後の差分をとることによって固定パターンノイズを抑圧することができる。また、各画素を完全リセットしているので残像の発生もなく、さらに2次元固体撮像素子においては、信号成分とノイズ成分が垂直信号線から水平信号線へ同一の経路を経由して出力されるので、縦筋状の固定パターンノイズの発生も抑えることができる。

#### 【図面の簡単な説明】

【図1】本発明の第1実施形態を示す構成図である。

【図2】第1実施形態の動作説明のためのタイミングチャートである。

【図3】CDS回路の回路構成の一例を示す回路図である。

【図4】エンハンスマント型MOSトランジスタ(A)とデプレッション型MOSトランジスタ(B)のId-Vd特性図である。

【図5】第1実施形態に係るリセット部の動作説明のためのポテンシャル図である。

【図6】単位画素の他の構成例を示す回路図である。

【図7】単位画素のさらに他の構成例を示す回路図である。

【図8】図5の構成に対応したポテンシャル図である。

【図9】図6の構成に対応したポテンシャル図である。

【図10】本発明の第2実施形態を示す構成図である。

【図11】第2実施形態の動作説明のためのタイミングチャートである。

【図12】第2実施形態に係るリセット部の動作説明のためのポテンシャル図である。

【図13】従来例を示す構成図である。

【図14】課題を説明するための構成図である。

#### 【符号の説明】

11, 51…単位画素、12, 52…フォトダイオード(光電変換素子)、13, 53…増幅用MOSトランジスタ、14, 54…選択用MOSトランジスタ、15, 55…リセット用MOSトランジスタ、16…リセット選択用MOSトランジスタ、17, 56…電源(VDD)線、18…垂直信号線、19…水平リセット線、20…垂直選択線、21…水平信号線、22…水平選択用MOSトランジスタ、23…垂直走査回路、24…水平走査回路、25, 59…CDS(相関二重サンプリング)回路、57…信号線、58…走査回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 米本 和也

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 内田 勝久

(56)参考文献 特開平02-171088(JP,A)

特開平07-284024(JP,A)

特開平01-117485(JP,A)

特開平04-000880(JP,A)

特開平04-241586(JP,A)

特開平11-122532(JP,A)

特開平11-112018(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 ~ 5/335