(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6485299号

(P6485299)

(45) 発行日 平成31年3月20日(2019.3.20)

(24) 登録日 平成31年3月1日(2019.3.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652C |

| HO1L 29/12  | (2006.01) | HO1L 29/78 | 652J |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 653A |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652T |

| HO1L 21/20  | (2006.01) | HO1L 29/78 | 658E |

請求項の数 27 (全 27 頁) 最終頁に続く

(21) 出願番号

特願2015-178990 (P2015-178990)

(22) 出願日

平成27年9月11日 (2015.9.11)

(65) 公開番号

特開2017-5236 (P2017-5236A)

(43) 公開日

平成29年1月5日 (2017.1.5)

審査請求日

平成29年10月24日 (2017.10.24)

(31) 優先権主張番号

特願2015-114375 (P2015-114375)

(32) 優先日

平成27年6月5日 (2015.6.5)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000241463

豊田合成株式会社

愛知県清須市春日長畑1番地

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(72) 発明者 藤井 隆弘

愛知県清須市春日長畑1番地 豊田合成株式会社内

(72) 発明者 小寄 正芳

愛知県清須市春日長畑1番地 豊田合成株式会社内

(72) 発明者 丹羽 隆樹

愛知県清須市春日長畑1番地 豊田合成株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法ならびに電力変換装置

(57) 【特許請求の範囲】

【請求項 1】

半導体装置であって、

上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する第1のn型半導体層と、

前記周囲面と前記側面とが成す角部から少なくとも前記側面にわたって形成された第1のp型半導体層と、

前記第1のp型半導体層より低い濃度でアクセプタ元素を含有し、前記第1のp型半導体層の上に形成された第2のp型半導体層と、

前記第1のn型半導体層より高い濃度でドナー元素を含有し、前記第2のp型半導体層の上に形成された第2のn型半導体層と、

前記第2のn型半導体層から前記第2のp型半導体層を貫通し前記上面の内側に至るまで落ち込んだ溝部と、

前記溝部の表面に形成された絶縁膜と、

前記絶縁膜を介して前記溝部に形成された電極と

を備え、

前記第1のp型半導体層の厚さは、前記メサ構造から離れるに従って薄くなる、半導体装置。

【請求項 2】

前記第1のp型半導体層は、前記上面から前記第2のn型半導体層が位置する側へ

10

20

0 nm の位置より、前記周囲面が位置する側に形成されている、請求項 1 に記載の半導体装置。

【請求項 3】

前記第 1 の p 型半導体層は、前記上面より前記周囲面が位置する側に形成されている、請求項 1 または請求項 2 に記載の半導体装置。

【請求項 4】

前記第 2 の p 型半導体層は、前記第 1 の p 型半導体層の上から前記上面にわたって形成されている、請求項 1 から請求項 3 までのいずれか一項に記載の半導体装置。

【請求項 5】

前記第 1 の p 型半導体層と前記第 2 の p 型半導体層との界面が前記上面と成す角度は、

10

0° 以上 90° 以下である、請求項 1 から請求項 4 までのいずれか一項に記載の半導体装置。

【請求項 6】

前記第 1 の p 型半導体層と前記第 2 の p 型半導体層との界面が前記上面と成す角度は、

30

30° 以上 80° 以下である、請求項 1 から請求項 5 までのいずれか一項に記載の半導体装置。

【請求項 7】

前記第 1 の p 型半導体層と前記第 2 の p 型半導体層との界面が前記上面と成す角度は、

20

40° 以上 60° 以下である、請求項 1 から請求項 6 までのいずれか一項に記載の半導体装置。

【請求項 8】

前記上面、前記側面および前記周囲面の少なくとも 1 つの面は、アクセプタ元素がデルタドーピングされた界面である、請求項 1 から請求項 7 までのいずれか一項に記載の半導体装置。

【請求項 9】

前記溝部は、前記周囲面より前記第 2 の n 型半導体層が位置する側に形成されている、

請求項 1 から請求項 8 までのいずれか一項に記載の半導体装置。

【請求項 10】

前記第 1 の p 型半導体層および前記第 2 の p 型半導体層は、ガリウム ( Ga ) を含有する

30

窒化物半導体である、請求項 1 から請求項 9 までのいずれか一項に記載の半導体装置。

【請求項 11】

前記第 1 の p 型半導体層および前記第 2 の p 型半導体層は、窒化ガリウム ( GaN ) から主に成る、請求項 1 から請求項 10 までのいずれか一項に記載の半導体装置。

【請求項 12】

前記第 1 の p 型半導体層および前記第 2 の p 型半導体層に含まれるアクセプタ元素は、マグネシウム ( Mg ) である、請求項 1 から請求項 11 までのいずれか一項に記載の半導体装置。

【請求項 13】

前記第 1 の p 型半導体層に含まれるアクセプタ元素の濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$  以上

40

$8 \times 10^{19} \text{ cm}^{-3}$  以下である、請求項 1 から請求項 12 までのいずれか一項に記載の半導体装置。

【請求項 14】

前記第 1 の n 型半導体層および前記第 2 の n 型半導体層に含まれるドナー元素は、ケイ素 ( Si ) である、請求項 1 から請求項 13 までのいずれか一項に記載の半導体装置。

【請求項 15】

前記側面における結晶面は、a 面または m 面である、請求項 1 から請求項 14 までのいずれか一項に記載の半導体装置。

【請求項 16】

請求項 1 から請求項 15 までのいずれか一項に記載の半導体装置であって、

前記第 1 の p 型半導体層は、前記側面の全域にわたって形成され、

50

前記第2のp型半導体層は、前記第1のp型半導体層の上から前記上面にわたって形成されている、半導体装置。

【請求項17】

請求項1から請求項16までのいずれか一項に記載の半導体装置を備える電力変換装置。

【請求項18】

半導体装置の製造方法であって、

n型およびp型のうち一方の特性を有する第1の半導体層に、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面とを形成し、

III族原料とV族原料とを第1のV/III比で含有する原料ガスを用いたエピタキシャル成長によって、n型およびp型のうち前記一方の特性とは異なる他方の特性を有する第2の半導体層を、前記周囲面と前記側面とが成す角部から少なくとも前記側面にわたって形成し、

前記第1のV/III比より低い第2のV/III比でIII族原料とV族原料とを含有する原料ガスを用いたエピタキシャル成長によって、前記他方の特性に寄与するドーパント元素を前記第2の半導体層より低い濃度で含有する第3の半導体層を、前記第2の半導体層の上に形成し、

前記メサ構造から離れるに従って厚さが薄くなるように前記第2の半導体層を形成する、

半導体装置の製造方法。

【請求項19】

請求項18に記載の半導体装置の製造方法であって、

前記一方の特性はn型であり、前記他方の特性はp型であり、

前記第1の半導体層より高い濃度でドナー元素を含有する第4の半導体層を、前記第3の半導体層の上に形成し、

前記第3の半導体層から前記第2の半導体層を貫通し前記上面の内側に至るまで落ち込んだ溝部を形成し、

前記溝部の表面に絶縁膜を形成し、

前記絶縁膜を介して前記溝部に電極を形成する、半導体装置の製造方法。

【請求項20】

前記第2の半導体層および前記第3の半導体層を形成する前に、前記上面、前記側面および前記周囲面の少なくとも1つの面に対して、前記他方の特性に寄与するドーパント元素をデルタドーピングする、請求項18または請求項19までのいずれか一項に記載の半導体装置の製造方法。

【請求項21】

請求項18から請求項20までのいずれか一項に記載の半導体装置の製造方法であって、

前記一方の特性はn型であり、前記他方の特性はp型であり、

前記第2の半導体層に含まれるアクセプタ元素の濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下となるように前記第2の半導体層を形成する、半導体装置の製造方法。

【請求項22】

前記側面における結晶面がa面またはm面となるように前記メサ構造を形成する、請求項18から請求項21までのいずれか一項に記載の半導体装置の製造方法。

【請求項23】

請求項18から請求項22までのいずれか一項に記載の半導体装置の製造方法であって、

前記側面の全域にわたって前記第2の半導体層を形成し、

前記第2の半導体層の上から前記上面にわたって前記第3の半導体層を形成する、半導体装置の製造方法。

【請求項24】

10

20

30

40

50

前記第1のV/III比は、1500以上3000以下である、請求項1\_8から請求項2\_3までのいずれか一項に記載の半導体装置の製造方法。

【請求項25】

前記第1のV/III比は、2500以上3000以下である、請求項1\_8から請求項2\_4までのいずれか一項に記載の半導体装置の製造方法。

【請求項26】

前記第2の半導体層をエピタキシャル成長させる温度は、950以上1200以下である、請求項1\_8から請求項2\_5までのいずれか一項に記載の半導体装置の製造方法。

【請求項27】

前記第2の半導体層をエピタキシャル成長させる圧力は、1kPa以上100kPa以下である、請求項1\_8から請求項2\_6までのいずれか一項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法ならびに電力変換装置に関する。

【背景技術】

【0002】

半導体装置（半導体デバイス、半導体素子）の構造として、トレンチ（溝部）にゲート電極を形成したトレンチゲート構造が知られている。特許文献1,2には、n型半導体層に形成されたメサ構造（凸部）にトレンチの底部を設け、メサ構造の周囲に形成されたp型半導体によって、トレンチの底部に発生する電界集中を緩和する技術が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009-117593号公報

【特許文献2】特開2014-209540号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の技術では、p型ベース領域におけるチャネルを構成する部位に沿ってp<sup>+</sup>型ディープ層が隣接しているため、p<sup>+</sup>型ディープ層からチャネルへとアクセプタ元素が拡散することによって、チャネルにおける電気特性が低下する可能性があった。その対策として、チャネルとp<sup>+</sup>型ディープ層との距離を大きく取った場合、トレンチ底部とp<sup>+</sup>型ディープ層との距離も大きくなるため、トレンチ底部における電界集中を十分に緩和できない可能性があった。したがって、特許文献1の技術では、チャネルにおける電気特性の確保と、トレンチ底部における電界集中の緩和とを両立させることが難しいという問題があった。

【0005】

そのため、トレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる技術が望まれていた。そのほか、半導体装置においては、低コスト化、微細化、製造の容易化、省資源化、使い勝手の向上、耐久性の向上などが望まれていた。

【課題を解決するための手段】

【0006】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態として実現することが可能である。

【形態1】半導体装置であって、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する第1のn型半導体層と、前記周囲面と前記側面

10

20

30

40

50

とが成す角部から少なくとも前記側面にわたって形成された第1のp型半導体層と、前記第1のp型半導体層より低い濃度でアクセプタ元素を含有し、前記第1のp型半導体層の上に形成された第2のp型半導体層と、前記第1のn型半導体層より高い濃度でドナー元素を含有し、前記第2のp型半導体層の上に形成された第2のn型半導体層と、前記第2のn型半導体層から前記第2のp型半導体層を貫通し前記上面の内側に至るまで落ち込んだ溝部と、前記溝部の表面に形成された絶縁膜と、前記絶縁膜を介して前記溝部に形成された電極とを備え、前記第1のp型半導体層の厚さは、前記メサ構造から離れるに従って薄くなる、半導体装置。

[形態2]半導体装置の製造方法であって、n型およびp型のうち一方の特性を有する第1の半導体層に、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面とを形成し、III族原料とV族原料とを第1のV/III比で含有する原料ガスを用いたエピタキシャル成長によって、n型およびp型のうち前記一方の特性とは異なる他方の特性を有する第2の半導体層を、前記周囲面と前記側面とが成す角部から少なくとも前記側面にわたって形成し、前記第1のV/III比より低い第2のV/III比でIII族原料とV族原料とを含有する原料ガスを用いたエピタキシャル成長によって、前記他方の特性に寄与するドーパント元素を前記第2の半導体層より低い濃度で含有する第3の半導体層を、前記第2の半導体層の上に形成し、前記メサ構造から離れるに従って厚さが薄くなるように前記第2の半導体層を形成する、半導体装置の製造方法。

#### 【0007】

(1) 本発明の一形態によれば、半導体装置が提供される。この半導体装置は、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面と、を有する第1のn型半導体層と；前記周囲面と前記側面とが成す角部から少なくとも前記側面にわたって形成された第1のp型半導体層と；前記第1のp型半導体層より低い濃度でアクセプタ元素を含有し、前記第1のp型半導体層の上に形成された第2のp型半導体層と；前記第1のn型半導体層より高い濃度でドナー元素を含有し、前記第2のp型半導体層の上に形成された第2のn型半導体層と；前記第2のn型半導体層から前記第2のp型半導体層を貫通し前記上面の内側に至るまで落ち込んだ溝部と；前記溝部の表面に形成された絶縁膜と；前記絶縁膜を介して前記溝部に形成された電極とを備える。この形態によれば、第1のp型半導体層が角部から側面にわたって形成されているため、第1のp型半導体層のアクセプタ元素によって角部および側面において空乏層を十分に形成できる。また、第1のp型半導体層の上に第2のp型半導体層が形成されているため、第2のp型半導体層におけるチャネルを構成する部位へと第1のp型半導体層から拡散するアクセプタ元素を抑制できる。これらの結果、トレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

#### 【0008】

(2) 上記形態の半導体装置において、前記第1のp型半導体層は、前記上面から前記第2のn型半導体層が位置する側へ100nmの位置より、前記周囲面が位置する側に形成されていてもよい。この形態によれば、第1のp型半導体層に含まれるアクセプタ元素に起因するオン抵抗の増大を抑制できる。したがって、チャネルの電気特性を十分に確保できる。

#### 【0009】

(3) 上記形態の半導体装置において、前記第1のp型半導体層は、前記上面より前記周囲面が位置する側に形成されていてもよい。この形態によれば、第1のp型半導体層に含まれるアクセプタ元素に起因するオン抵抗の増大をいっそう抑制できる。したがって、チャネルの電気特性をいっそう十分に確保できる。

#### 【0010】

(4) 上記形態の半導体装置において、前記第2のp型半導体層は、前記第1のp型半導体層の上から前記上面にわたって形成されていてもよい。この形態によれば、第2のp型半導体層が上面に形成されていない構造と比較して、第1のp型半導体層に含まれるアクセプタ元素に起因するオン抵抗の増大を抑制できる。したがって、チャネルの電気特性を

10

20

30

40

50

十分に確保できる。

【0011】

(5) 上記形態の半導体装置において、前記第1のp型半導体層の厚さは、前記メサ構造から離れるに従って薄くなってもよい。この形態によれば、第2のp型半導体層におけるチャネルを構成する部位へと第1のp型半導体層から拡散するアクセプタ元素をいっそう抑制できる。

【0012】

(6) 上記形態の半導体装置において、前記第1のp型半導体層と前記第2のp型半導体層との界面が前記上面と成す角度は、0°以上90°以下であってもよい。この形態によれば、角部および側面における空乏層の形成と、第1のp型半導体層からチャネルへと拡散するアクセプタ元素の抑制との両立を図ることができる。

10

【0013】

(7) 上記形態の半導体装置において、前記第1のp型半導体層と前記第2のp型半導体層との界面が前記上面と成す角度は、30°以上80°以下であってもよい。この形態によれば、角部および側面における空乏層の形成と、第1のp型半導体層からチャネルへと拡散するアクセプタ元素の抑制との両立を効果的に図ることができる。

【0014】

(8) 上記形態の半導体装置において、前記第1のp型半導体層と前記第2のp型半導体層との界面が前記上面と成す角度は、40°以上60°以下であってもよい。この形態によれば、角部および側面における空乏層の形成と、第1のp型半導体層からチャネルへと拡散するアクセプタ元素の抑制との両立をいっそう効果的に図ることができる。

20

【0015】

(9) 上記形態の半導体装置において、前記上面、前記側面および前記周囲面の少なくとも1つの面は、アクセプタ元素がデルタドーピングされた界面であってもよい。この形態によれば、デルタドーピングされた界面において空乏層をいっそう十分に形成できる。

【0016】

(10) 上記形態の半導体装置において、前記溝部は、前記周囲面より前記第2のn型半導体層が位置する側に形成されていてもよい。この形態によれば、溝部の底部における電界集中を効果的に緩和できる。

【0017】

30

(11) 上記形態の半導体装置において、前記第1のp型半導体層および前記第2のp型半導体層は、ガリウム(Ga)を含有する窒化物半導体であってもよい。この形態によれば、アクセプタ元素が拡散しやすい窒化物半導体を用いたトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

【0018】

(12) 上記形態の半導体装置において、前記第1のp型半導体層および前記第2のp型半導体層は、窒化ガリウム(GaN)から主に成ってもよい。この形態によれば、アクセプタ元素が拡散しやすい窒化ガリウムを用いたトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

【0019】

40

(13) 上記形態の半導体装置において、前記第1のp型半導体層および前記第2のp型半導体層に含まれるアクセプタ元素は、マグネシウム(Mg)であってもよい。この形態によれば、アクセプタ元素にマグネシウムを用いたトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

【0020】

(14) 上記形態の半導体装置において、前記第1のp型半導体層に含まれるアクセプタ元素の濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下であってもよい。この形態によれば、角部および側面において空乏層を効果的に形成できる。

【0021】

(15) 上記形態の半導体装置において、前記第1のn型半導体層および前記第2のn型

50

半導体層に含まれるドナー元素は、ケイ素(Si)であってもよい。この形態によれば、ドナー元素にケイ素を用いたトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

(16) 上記形態の半導体装置において、前記側面における結晶面は、a面またはm面であってもよい。この形態によれば、側面における第1のp型半導体層の結晶品質を向上させることができる。

(17) 上記形態の半導体装置において、前記第1のp型半導体層は、前記側面の全域にわたって形成され、前記第2のp型半導体層は、前記第1のp型半導体層の上から前記上面にわたって形成されていてもよい。この形態によれば、角部および側面において空乏層を効果的に形成できる。

10

#### 【0022】

本発明の一形態によれば、半導体装置の製造方法が提供される。この製造方法は、n型およびp型のうち一方の特性を有する第1の半導体層に、上面と側面とを有する台地状を成すメサ構造と、前記メサ構造の周囲に広がる周囲面とを形成し；III族原料とV族原料とを第1のV/III比で含有する原料ガスを用いたエピタキシャル成長によって、n型およびp型のうち前記一方の特性とは異なる他方の特性を有する第2の半導体層を、前記周囲面と前記側面とが成す角部から少なくとも前記側面にわたって形成し；前記第1のV/III比より低い第2のV/III比でIII族原料とV族原料とを含有する原料ガスを用いたエピタキシャル成長によって、前記他方の特性に寄与するドーパント元素を前記第2の半導体層より低い濃度で含有する第3の半導体層を、前記第2の半導体層の上に形成する。この形態によれば、上面の上方に位置する第3の半導体層へと第2の半導体層から拡散するドーパント元素が抑制されるように、第2の半導体層を角部から側面にわたって容易に形成できる。

20

#### 【0023】

上記形態の製造方法において、前記一方の特性はn型であり、前記他方の特性はp型であり；前記第1の半導体層より高い濃度でドナー元素を含有する第4の半導体層を、前記第3の半導体層の上に形成し；前記第3の半導体層から前記第2の半導体層を貫通し前記上面の内側に至るまで落ち込んだ溝部を形成し；前記溝部の表面に絶縁膜を形成し；前記絶縁膜を介して前記溝部に電極を形成してもよい。この形態によれば、トレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

30

#### 【0024】

上記形態の製造方法において、前記メサ構造から離れるに従って厚さが薄くなるように前記第2の半導体層を形成してもよい。この形態によれば、上面の上方に位置する第3の半導体層へと第2の半導体層から拡散するドーパント元素をいっそう抑制できる。

#### 【0025】

上記形態の製造方法において、前記第2の半導体層および前記第3の半導体層を形成する前に、前記上面、前記側面および前記周囲面の少なくとも1つの面に対して、前記他方の特性に寄与するドーパント元素をデルタドーピングしてもよい。この形態によれば、デルタドーピングされた界面において空乏層をいっそう十分に形成できる。

#### 【0026】

40

上記形態の製造方法において、前記一方の特性はn型であり、前記他方の特性はp型であり、前記第2の半導体層に含まれるアクセプタ元素の濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下となるように前記第2の半導体層を形成してもよい。この形態によれば、角部および側面において空乏層を効果的に形成可能に第2の半導体層を形成できる。

#### 【0027】

上記形態の製造方法において、前記側面における結晶面がa面またはm面となるように前記メサ構造を形成してもよい。a面またはm面ではc面と比較して第2の半導体層の成長速度が速いため、角部および側面に対して第2の半導体層を容易に形成できる。なお、a面ではm面と比較して第2の半導体層の成長速度がいっそう速い。

50

## 【0028】

上記形態の製造方法において、前記側面の全域にわたって前記第2の半導体層を形成し、前記第2の半導体層の上から前記上面にわたって前記第3の半導体層を形成してもよい。この形態によれば、角部および側面において空乏層を効果的に形成可能に第2および第3の半導体層を形成できる。

## 【0029】

上記形態の製造方法において、前記第1のV/III比は、1500以上3000以下であってもよい。この形態によれば、角部および側面に対して第2の半導体層を容易に形成できる。

## 【0030】

上記形態の製造方法において、前記第1のV/III比は、2500以上3000以下であってもよい。この形態によれば、角部および側面に対して第2の半導体層をいっそう容易に形成できる。

## 【0031】

上記形態の製造方法において、前記第2の半導体層をエピタキシャル成長させる温度は、950以上1200以下であってもよい。この形態によれば、角部および側面に対して第2の半導体層を容易に形成できる。

## 【0032】

上記形態の製造方法において、前記第2の半導体層をエピタキシャル成長させる圧力は、1kPa以上100kPa以下であってもよい。この形態によれば、角部および側面に対して第2の半導体層を容易に形成できる。

## 【0033】

本発明は、半導体装置およびその製造方法以外の種々の形態で実現することも可能であり、例えば、上記形態の半導体装置を備える電力変換装置、上記形態の製造方法を実施する製造装置などの形態で実現できる。

## 【発明の効果】

## 【0034】

本願発明の半導体装置によれば、トレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。また、本願発明の半導体装置の製造方法によれば、上面の上方に位置する第3の半導体層へと第2の半導体層から拡散するドーパント元素が抑制されるように、第2の半導体層を角部から側面にわたって容易に形成できる。

## 【図面の簡単な説明】

## 【0035】

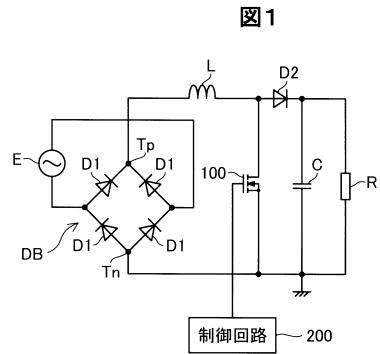

【図1】電力変換装置の構成を示す説明図である。

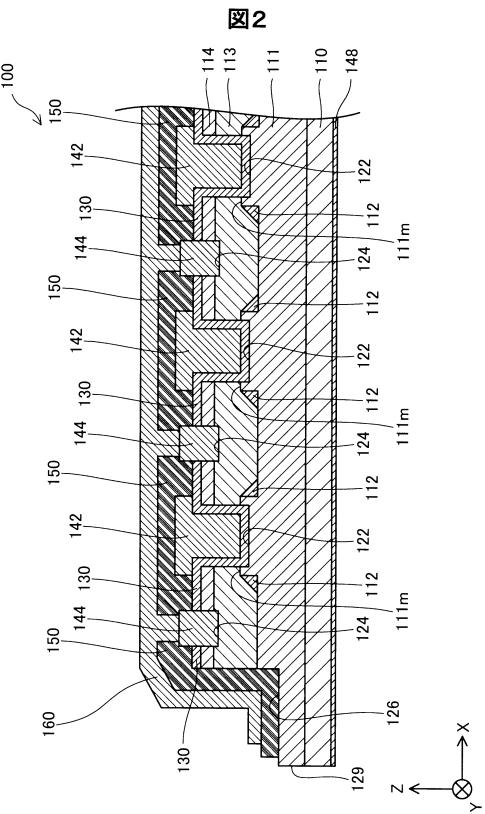

【図2】第1実施形態における半導体装置の構成を模式的に示す断面図である。

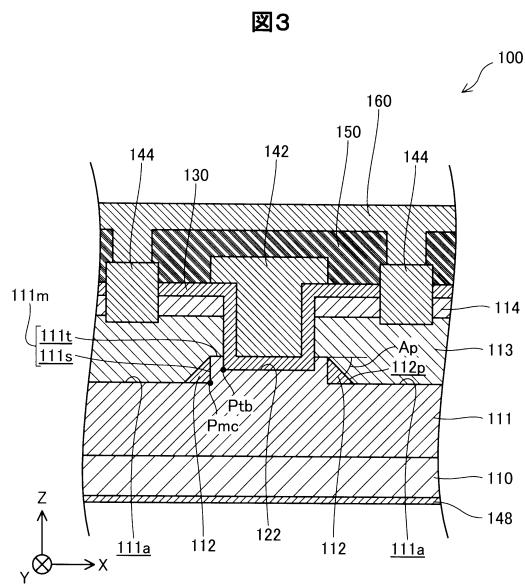

【図3】第1実施形態における半導体装置の詳細構成を模式的に示す断面図である。

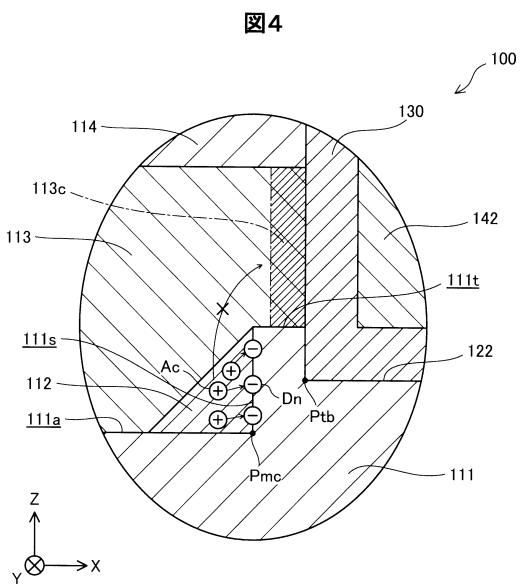

【図4】p型半導体層の作用を示す説明図である。

【図5】p型半導体層の作用を示す説明図である。

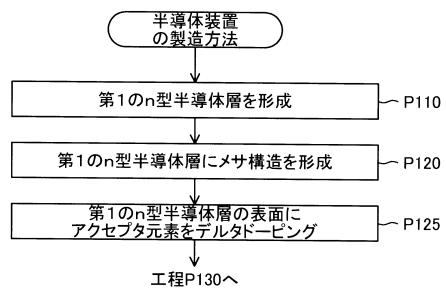

【図6】第1実施形態における半導体装置の製造方法を示す工程図である。

【図7】半導体装置を製造する様子を示す説明図である。

【図8】半導体装置を製造する様子を示す説明図である。

【図9】半導体装置を製造する様子を示す説明図である。

【図10】半導体装置を製造する様子を示す説明図である。

【図11】半導体装置を製造する様子を示す説明図である。

【図12】半導体装置を製造する様子を示す説明図である。

【図13】半導体装置を製造する様子を示す説明図である。

【図14】第1実施形態の変形例における半導体装置の製造方法を示す工程図である。

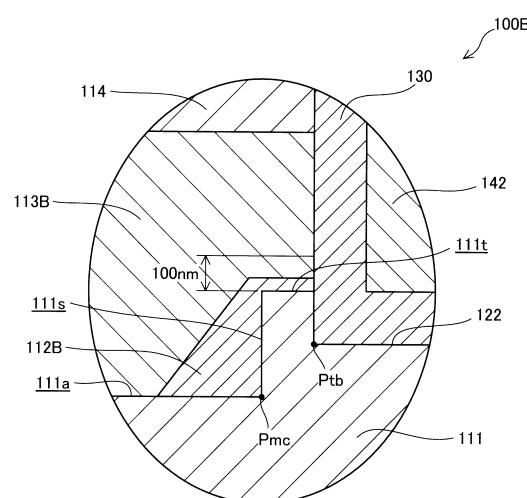

【図15】第2実施形態における半導体装置の詳細構成を示す説明図である。

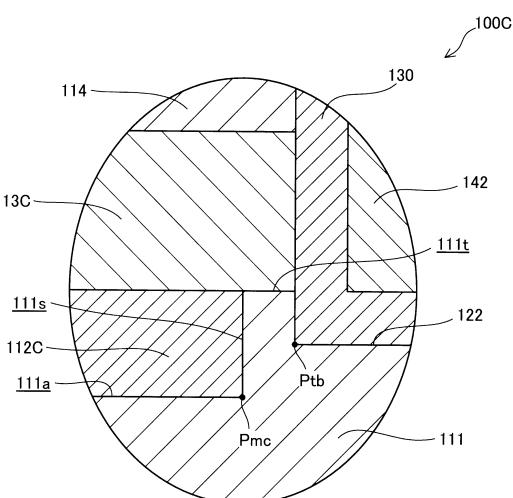

【図16】第3実施形態における半導体装置の詳細構成を示す説明図である。

10

20

30

40

50

【図17】第4実施形態における半導体装置の詳細構成を示す説明図である。

【図18】第5実施形態における半導体装置の詳細構成を示す説明図である。

【図19】第6実施形態における半導体装置の詳細構成を示す説明図である。

【図20】第7実施形態における半導体装置の構成を示す説明図である。

【発明を実施するための形態】

【0036】

#### A. 第1実施形態

##### A-1. 電力変換装置の構成

図1は、電力変換装置10の構成を示す説明図である。電力変換装置10は、交流電源Eから負荷Rに供給される電力を変換する装置である。電力変換装置10は、交流電源Eの力率を改善する力率改善回路の構成部品として、半導体装置100と、制御回路200と、4つのダイオードD1と、コイルLと、ダイオードD2と、キャパシタCとを備える。

10

【0037】

電力変換装置10において、4つのダイオードD1は、交流電源Eの交流電圧を整流するダイオードブリッジDBを構成する。ダイオードブリッジDBは、直流側の端子として、正極出力端Tpと、負極出力端Tnとを有する。コイルLは、ダイオードブリッジDBの正極出力端Tpに接続されている。ダイオードD2のアノード側は、コイルLを介して正極出力端Tpに接続されている。ダイオードD2のカソード側は、キャパシタCを介して負極出力端Tnに接続されている。負荷Rは、キャパシタCと並列に接続されている。

20

【0038】

電力変換装置10の半導体装置100は、FET(Field-Effect Transistor)である。半導体装置100のソース側は、負極出力端Tnに接続されている。半導体装置100のドレイン側は、コイルLを介して正極出力端Tpに接続されている。半導体装置100のゲート側は、制御回路200に接続されている。電力変換装置10の制御回路200は、交流電源Eの力率が改善されるように、負荷Rに出力される電圧、および、ダイオードブリッジDBにおける電流に基づいて、半導体装置100のソース-ドレイン間の電流を制御する。

【0039】

##### A-2. 半導体装置の構成

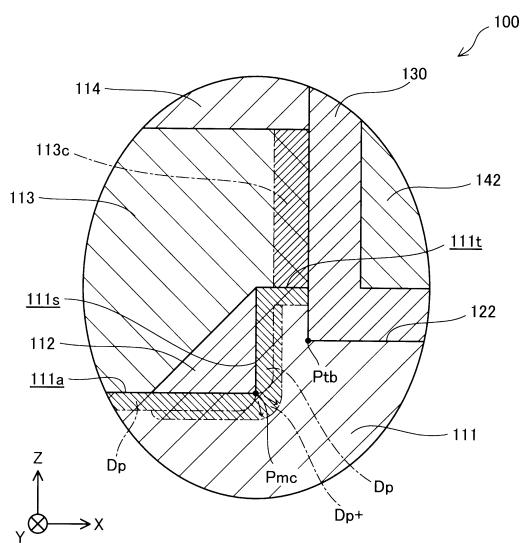

図2は、第1実施形態における半導体装置100の構成を模式的に示す断面図である。図2には、相互に直交するXYZ軸が図示されている。図2のXYZ軸のうち、X軸は、図2の紙面左から紙面右に向かう軸である。+X軸方向は、紙面右に向かう方向であり、-X軸方向は、紙面左に向かう方向である。図2のXYZ軸のうち、Y軸は、図2の紙面手前から紙面奥に向かう軸である。+Y軸方向は、紙面奥に向かう方向であり、-Y軸方向は、紙面手前に向かう方向である。図2のXYZ軸のうち、Z軸は、図2の紙面下から紙面上に向かう軸である。+Z軸方向は、紙面上に向かう方向であり、-Z軸方向は、紙面下に向かう方向である。図2のXYZ軸は、他の図のXYZ軸に対応する。

30

【0040】

半導体装置100は、ガリウム(Ga)を含有する窒化物半導体を用いて形成された半導体装置である。本実施形態では、半導体装置100は、窒化ガリウム(GaN)を用いて形成されたGaN系の半導体装置である。本実施形態では、半導体装置100は、縦型トレンチMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)である。本実施形態では、半導体装置100は、電力制御に用いられ、パワーデバイスとも呼ばれる。

40

【0041】

半導体装置100は、基板110と、n型半導体層111と、p型半導体層112と、p型半導体層113と、n型半導体層114とを備える。半導体装置100は、これらの半導体層に形成された構造として、トレンチ122と、リセス124と、段差部126と、終端部129とを有する。半導体装置100は、更に、絶縁膜130と、ゲート電極1

50

42と、ソース電極144と、ドレン電極148とを備える。本実施形態では、半導体装置100は、更に、絶縁膜150と、配線電極160とを備える。

#### 【0042】

図3は、第1実施形態における半導体装置100の詳細構成を模式的に示す断面図である。図3には、トレンチ122を中心に半導体装置100の断面が図示されている。

#### 【0043】

半導体装置100の基板110は、X軸およびY軸に沿って広がる板状を成す半導体である。本実施形態では、基板110は、窒化ガリウム(GaN)から主に成る。本明細書の説明において、「窒化ガリウム(GaN)から主に成る」とは、モル分率において窒化ガリウム(GaN)を90%以上含有することを意味する。本実施形態では、基板110は、ケイ素(Si)をドナー元素として含有するn型半導体である。本実施形態では、基板110に含まれるケイ素(Si)濃度の平均値は、約 $1 \times 10^{18} \text{ cm}^{-3}$ である。

10

#### 【0044】

半導体装置100のn型半導体層111は、n型の特性を有する第1の半導体層である。本実施形態では、n型半導体層111は、基板110の+Z軸方向側に位置し、X軸およびY軸に沿って広がる。本実施形態では、n型半導体層111は、窒化ガリウム(GaN)から主に成る。本実施形態では、n型半導体層111は、ケイ素(Si)をドナー元素(n型不純物、n型ドーパント元素)として含有する。本実施形態では、n型半導体層111に含まれるケイ素(Si)濃度の平均値は、約 $1 \times 10^{16} \text{ cm}^{-3}$ 以下であり、例えば、 $1 \times 10^{16} \text{ cm}^{-3}$ である。

20

#### 【0045】

n型半導体層111は、メサ構造111mと、周囲面111aとを有する。n型半導体層111のメサ構造111mは、上面111tと側面111sとを有する台地状を成す凸部である。n型半導体層111の周囲面111aは、メサ構造111mの周囲に広がる界面である。メサ構造111mは、周囲面111aから+Z軸方向に突出している。本実施形態では、メサ構造111mおよび周囲面111aは、n型半導体層111に対するドライエッチングおよびウェットエッチングによって形成された構造である。

#### 【0046】

本実施形態では、メサ構造111mの高さ(Z軸方向の長さ)は、約1μm(マイクロメートル)である。本実施形態では、上面111tおよび周囲面111aは、+Z軸方向を向いた界面である。側面111sと周囲面111aとが成す角度は、本実施形態では、約90°であり、他の実施形態では、90°以上であってもよい。n型半導体層111の厚さ(Z軸方向の長さ)は、上面111tにおいて、5μm以上30μm以下であり、本実施形態では、約10μmである。

30

#### 【0047】

本実施形態では、側面111sの結晶面はa面であり、周囲面111aおよび上面111tはc面である。他の実施形態では、側面111sの結晶面はm面であり、周囲面111aおよび上面111tはc面であってもよい。角部Pmcおよび側面111sに対してp型半導体層112を容易に形成する観点から、a面またはm面ではc面と比較してp型半導体層112の成長速度が速いため、側面111sの結晶面はa面またはm面であることが好ましく、p型半導体層112の成長速度がより速いa面であることがいっそう好ましい。

40

#### 【0048】

半導体装置100のp型半導体層112は、p型の特性を有する第2の半導体層である。p型半導体層112は、ガリウム(Ga)を含有する窒化物半導体であり、本実施形態では、窒化ガリウム(GaN)から主に成る。本実施形態では、p型半導体層112は、マグネシウム(Mg)をアクセプタ元素(p型不純物、p型ドーパント元素)として含有する。p型半導体層112は、p型半導体層113より高い濃度でアクセプタ元素を含有する。p型半導体層112に含まれるマグネシウム(Mg)濃度の平均値は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下が好ましく、本実施形態では、約 $4 \times 10^{19} \text{ cm}^{-3}$

50

$\text{cm}^{-3}$  である。

【0049】

p型半導体層112は、周囲面111aと側面111sとが成す角部Pmcから少なくとも側面111sにわたって形成されている。p型半導体層112は、本実施形態では、上面111tより-Z軸方向に形成されている。本実施形態では、p型半導体層112の厚さ（Z軸方向の長さ）は、メサ構造111mから離れるに従って薄くなる。

【0050】

p型半導体層112とp型半導体層113との界面112pが上面111tと成す角度Apは、0°以上90°以下であることが好ましく、30°以上80°以下であることがさらに好ましく、40°以上60°以下であることがいっそう好ましい。本実施形態では、角度Apは、約45°である。

10

【0051】

本実施形態では、p型半導体層112は、エピタキシャル成長（結晶成長）によって形成された半導体層である。他の実施形態では、p型半導体層112は、n型半導体層111の一部に対するイオン注入によって形成された半導体層であってもよい。

【0052】

半導体装置100のp型半導体層113は、p型の特性を有する第3の半導体層である。p型半導体層113は、ガリウム（Ga）を含有する窒化物半導体であり、本実施形態では、窒化ガリウム（GaN）から主に成る。本実施形態では、p型半導体層113は、マグネシウム（Mg）をアクセプタ元素（p型不純物、p型ドーパント元素）として含有する。p型半導体層113は、p型半導体層112より低い濃度でアクセプタ元素を含有する。本実施形態では、p型半導体層113に含まれるマグネシウム（Mg）濃度の平均値は、約 $1 \times 10^{18} \text{ cm}^{-3}$ である。

20

【0053】

p型半導体層113がn型半導体層111に隣接する界面（側面111s、周囲面111aの一部）では、p型半導体層113のアクセプタ元素によって、ドナー性不純物（n型不純物）のシート濃度は、 $5 \times 10^{12} \text{ cm}^{-2}$ 以下となる。このシート濃度は、界面近傍におけるドナー性不純物の濃度である。

【0054】

p型半導体層113は、n型半導体層111およびp型半導体層112の+Z軸方向側に位置し、X軸およびY軸に沿って広がる。p型半導体層113は、p型半導体層112の上に形成されている。本実施形態では、p型半導体層113は、p型半導体層112の上からn型半導体層111の上面111tにわたって形成されている。本実施形態では、p型半導体層113は、n型半導体層111の周囲面111aから、p型半導体層112の上を経由し、n型半導体層111の上面111tにわたって形成されている。本実施形態では、p型半導体層113の厚さ（Z軸方向の長さ）は、上面111tに接する部位において、約0.7μmである。

30

【0055】

半導体装置100のn型半導体層114は、n型の特性を有する第4の半導体層である。本実施形態では、n型半導体層114は、p型半導体層113の+Z軸方向側に位置し、X軸およびY軸に沿って広がる。本実施形態では、n型半導体層114は、窒化ガリウム（GaN）から主に成る。本実施形態では、n型半導体層114は、ケイ素（Si）をドナー元素（n型不純物、n型ドーパント元素）として含有する。n型半導体層114は、n型半導体層111より高い濃度でドナー元素を含有する。本実施形態では、n型半導体層114に含まれるケイ素（Si）濃度の平均値は、約 $3 \times 10^{18} \text{ cm}^{-3}$ である。本実施形態では、n型半導体層114の厚さ（Z軸方向の長さ）は、約0.2μmである。

40

【0056】

半導体装置100のトレンチ122は、n型半導体層114からp型半導体層113を貫通し上面111tの内側に至るまで落ち込んだ溝部である。トレンチ122の底部Pt

50

b は、上面 1 1 1 t より - Z 軸方向側から、周囲面 1 1 1 a より + Z 軸方向側までの範囲に位置する。本実施形態では、トレンチ 1 2 2 は、上面 1 1 1 t より - Z 軸方向側にまで落ち込んでおり、トレンチ 1 2 2 の底部 P t b は、Z 軸方向において上面 1 1 1 t と周囲面 1 1 1 a との間に位置する。本実施形態では、トレンチ 1 2 2 は、各半導体層に対するドライエッチングによって形成された構造である。

## 【 0 0 5 7 】

半導体装置 1 0 0 のリセス 1 2 4 は、n 型半導体層 1 1 4 の + Z 軸方向側から p 型半導体層 1 1 3 にわたって窪んだ凹部である。本実施形態では、リセス 1 2 4 は、各半導体層に対するドライエッチングによって形成された構造である。

## 【 0 0 5 8 】

半導体装置 1 0 0 の段差部 1 2 6 は、n 型半導体層 1 1 4 の + Z 軸方向側から p 型半導体層 1 1 3 を貫通し n 型半導体層 1 1 1 にまで落ち込んだ部位である。本実施形態では、段差部 1 2 6 は、ドライエッチングによって形成された構造である。

## 【 0 0 5 9 】

半導体装置 1 0 0 の終端部 1 2 9 は、段差部 1 2 6 に隣接し、半導体装置 1 0 0 の終端を構成する部位である。本実施形態では、終端部 1 2 9 は、ダイシングによって形成された構造である。

## 【 0 0 6 0 】

半導体装置 1 0 0 の絶縁膜 1 3 0 は、トレンチ 1 2 2 の表面に形成され、電気絶縁性を有する膜である。本実施形態では、絶縁膜 1 3 0 は、トレンチ 1 2 2 の内側から外側にわたって形成されている。本実施形態では、絶縁膜 1 3 0 は、二酸化ケイ素 ( SiO<sub>2</sub> ) から主に成る。

## 【 0 0 6 1 】

半導体装置 1 0 0 のゲート電極 1 4 2 は、絶縁膜 1 3 0 を介してトレンチ 1 2 2 に形成された電極である。本実施形態では、ゲート電極 1 4 2 は、トレンチ 1 2 2 の内側に加え、トレンチ 1 2 2 の外側にわたって形成されている。本実施形態では、ゲート電極 1 4 2 は、アルミニウム ( Al ) から主に成る。ゲート電極 1 4 2 に電圧が印加された場合、p 型半導体層 1 1 3 に反転層が形成され、この反転層がチャネルとして機能することによって、ソース電極 1 4 4 とドレイン電極 1 4 8 との間に導通経路が形成される。

## 【 0 0 6 2 】

半導体装置 1 0 0 のソース電極 1 4 4 は、リセス 1 2 4 に形成され、n 型半導体層 1 1 4 にオーミック接触する電極である。本実施形態では、ソース電極 1 4 4 は、チタン ( Ti ) から主に成る層にアルミニウム ( Al ) から主に成る層を積層した後に熱処理を加えた電極である。

## 【 0 0 6 3 】

半導体装置 1 0 0 のドレイン電極 1 4 8 は、基板 1 1 0 の - Z 軸方向側の表面にオーミック接触する電極である。本実施形態では、ドレイン電極 1 4 8 は、チタン ( Ti ) から主に成る層にアルミニウム ( Al ) から主に成る層を積層した後に熱処理を加えた電極である。

## 【 0 0 6 4 】

図 4 は、p 型半導体層 1 1 2 の作用を示す説明図である。発明者が鋭意検討した結果、図 4 において、p 型半導体層 1 1 2 がない場合と比較して、p 型半導体層 1 1 2 がある構造にすることにより、チャネルの電気特性を維持しつつ、さらに耐圧を向上させることができることがわかった。トレンチ 1 2 2 の底部 P t b に発生する電界集中は、角部 P m c における p 型半導体層 1 1 2 によって緩和される。p 型半導体層 1 1 2 は、p 型半導体層 1 1 3 より高い濃度でアクセプタ元素 A c を含有する。p 型半導体層 1 1 2 に存在する十分なアクセプタ元素 A c は、メサ構造 1 1 1 m の側面 1 1 1 s へと拡散する。メサ構造 1 1 1 m 形成時のドナー性欠陥の発生や形成後の大気にさらした場合のドナー性不純物の付着などにより、メサ構造 1 1 1 m を形成する際にドナー D n ( ドナー性欠陥およびドナー性不純物の少なくとも一方 ) が側面 1 1 1 s に発生した場合であっても、側面 1 1 1 s の

10

20

30

40

50

ドナー D<sub>n</sub> は、 p 型半導体層 112 から拡散したアクセプタ元素 A<sub>c</sub> によって補償される。その結果、リーグパス形成を大幅に抑制して耐圧を著しく向上させることが可能となる。その一方、 p 型半導体層 113 のうち p 型半導体層 112 から Z 軸方向に離れた部位にチャネル 113c が形成されるため、チャネル 113c へと p 型半導体層 113 から拡散するアクセプタ元素 A<sub>c</sub> は抑制される。このため、 p 型半導体層 112 を形成してもチャネルの電気特性に影響を与えないようにできる。

#### 【 0065 】

図 5 は、 p 型半導体層 112 の作用を示す説明図である。 n 型半導体層 111 と p 型半導体層 112, 113 とが接触する p-n 接合界面には、 n 型半導体層 111 側に空乏層 D<sub>p</sub>, D<sub>p+</sub> が形成される。 p 型半導体層 112 は、 p 型半導体層 113 より高い濃度でアクセプタ元素 A<sub>c</sub> を含有するため、 p 型半導体層 112 と接触する p-n 接合界面には、 p 型半導体層 113 と接触する p-n 接合界面より広い範囲に空乏層 D<sub>p+</sub> が形成される。空乏層 D<sub>p</sub> は、 p 型半導体層 112 の部分を p 型半導体層 113 に置き換えた場合に形成される空乏層である。空乏層 D<sub>p+</sub> は、 p 型半導体層 112 によって拡張された空乏層である。空乏層 D<sub>p+</sub> は、角部 Pmc における十分な空乏層として機能する。この結果、メサ角部での空乏層の幅をさらに広げることができるので耐圧を向上させることができると。

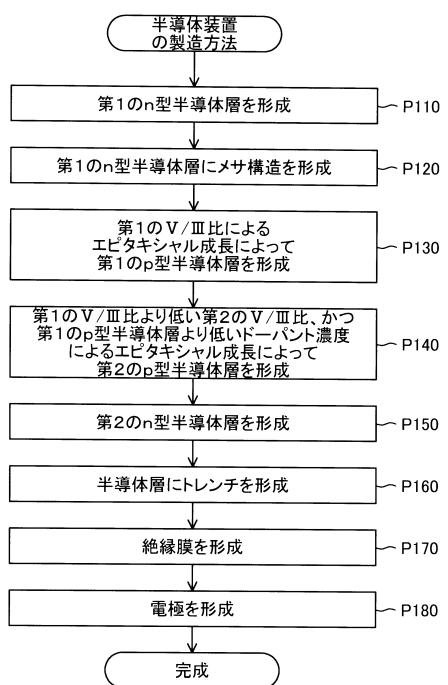

#### 【 0066 】

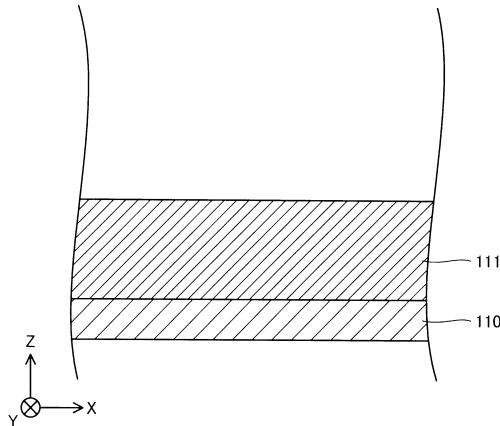

##### A - 3 . 半導体装置の製造方法

図 6 は、第 1 実施形態における半導体装置 100 の製造方法を示す工程図である。図 7 から図 13 は、半導体装置 100 を製造する様子を示す説明図である。

#### 【 0067 】

まず、製造者は、基板 110 の上に n 型半導体層 111 をエピタキシャル成長によって形成する（工程 P110、図 7）。これによって、製造者は、製造途中にある半導体装置 100 として、基板 110 の上に n 型半導体層 111 が形成された半導体装置 100a を得る。本実施形態では、製造者は、基板 110 における +Z 軸方向側の表面に n 型半導体層 111 を形成する。本実施形態では、製造者は、有機金属気相成長法（MOCVD：Metal Organic Chemical Vapor Deposition）によって n 型半導体層 111 を形成する。本実施形態では、n 型半導体層 111 を形成する原料ガスの V / III 比は、900 以上 300 以下である。V / III 比は、III族原料に対する V 族原料のモル比である。

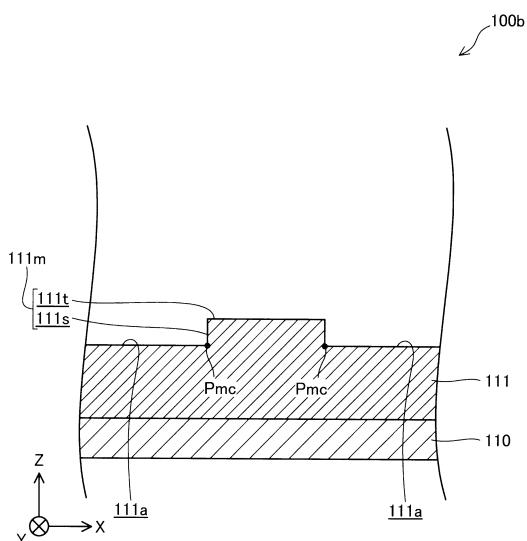

#### 【 0068 】

n 型半導体層 111 を形成した後（工程 P110）、製造者は、ドライエッチングおよびウェットエッチングによって n 型半導体層 111 にメサ構造 111m を形成する（工程 P120、図 8）。これによって、製造者は、製造途中にある半導体装置 100 として、n 型半導体層 111 にメサ構造 111m が形成された半導体装置 100b を得る。本実施形態では、製造者は、上面 111t となる部位にマスクを形成した後、n 型半導体層 111 の +Z 軸方向側の部位をドライエッチングによって除去する。これによって、n 型半導体層 111 に側面 111s および周囲面 111a が形成される。その後、製造者は、上面 111t からマスクを除去する。その後、製造者は、上面 111t 、側面 111s および周囲面 111a をウェットエッチングによって処理した後、上面 111t 、側面 111s および周囲面 111a を洗浄する。

#### 【 0069 】

本実施形態では、製造者は、側面 111s の結晶面が a 面となり、周囲面 111a および上面 111t が c 面となるように、メサ構造 111m を形成する。他の実施形態では、製造者は、側面 111s の結晶面が m 面となり、周囲面 111a および上面 111t が c 面となるように、メサ構造 111m を形成してもよい。角部 Pmc および側面 111s に対して p 型半導体層 112 を容易に形成する観点から、a 面または m 面では c 面と比較して p 型半導体層 112 の成長速度が速いため、側面 111s の結晶面は a 面または m 面であることが好ましく、p 型半導体層 112 の成長速度がより速い a 面であることがいっそ好ましい。

10

20

30

40

50

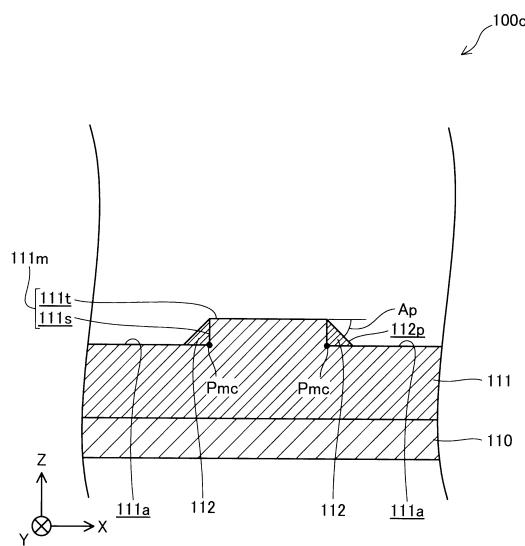

## 【0070】

メサ構造 111m を形成した後（工程 P120）、製造者は、III族原料とV族原料とを第1のV/III比で含有する原料ガスを用いたエピタキシャル成長によって、p型半導体層112を形成する（工程 P130、図9）。これによって、製造者は、製造途中にある半導体装置100として、角部Pmcから側面111sにわたってp型半導体層112が形成された半導体装置100cを得る。本実施形態では、製造者は、メサ構造111mから離れるに従って厚さ（Z軸方向の長さ）が薄くなるようにp型半導体層112を形成する。

## 【0071】

本実施形態では、製造者は、半導体装置100bにマスクを形成することなく、有機金属気相成長法（MOCVD）によってp型半導体層112を形成する。本実施形態では、製造者は、キャリアガスである水素（H<sub>2</sub>）とともに、V族原料であるアンモニア（NH<sub>3</sub>）を炉内に導入しつつ、炉内の半導体装置100bを1050まで昇温する。その後、製造者は、キャリアガスである水素（H<sub>2</sub>）とともに、III族原料であるトリメチルガリウム（TMGa：Tri-Methyl-Gallium）と、アクセプタ不純物であるビスシクロペニタジエニルマグネシウム（Cp<sub>2</sub>Mg）とを炉内に導入することによって、半導体装置100bの角部Pmcに三角状にp型半導体層112を成長させる。これによって、半導体装置100cが完成する。

## 【0072】

製造者は、p型半導体層112に含まれるアクセプタ元素の濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下となるように、Cp<sub>2</sub>Mgの流量を制御する。本実施形態では、Cp<sub>2</sub>Mgの流量は、300sccmである。p型半導体層112に含まれるアクセプタ元素の濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下が好ましい。p型半導体層112に含まれるアクセプタ元素の濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 未満である場合、大気中から側面111sに付着するドナー性不純物を、p型半導体層112のアクセプタ元素によって十分に補償できなくなる。p型半導体層112に含まれるアクセプタ元素の濃度が $8 \times 10^{19} \text{ cm}^{-3}$ 超過である場合、p型半導体層112の結晶中にドナー性欠陥が増加するとともに、p型半導体層112の結晶性が低下する。本実施形態では、p型半導体層112に含まれるアクセプタ元素の濃度は、約 $4 \times 10^{19} \text{ cm}^{-3}$ である。

## 【0073】

側面111sにおけるリークパスを防止する観点から、p型半導体層112を側面111sの全域に形成することが好ましい。

## 【0074】

チャネル113cの電気特性としてオン抵抗を低減する観点から、上面111tにp型半導体層112が形成されないことが好ましい。上面111tにp型半導体層112が形成される場合であっても、上面111tから+Z軸方向へ100nmの位置より-Z軸方向側であることが好ましい。

## 【0075】

上面111tへのp型半導体層112の形成を抑制する観点から、横方向（X軸方向およびY軸方向）への成長レートが高い条件として、p型半導体層112を形成するV/III比は、1500以上3000以下が好ましく、2500以上3000以下がいっそう好ましい。本実施形態では、p型半導体層112を形成するV/III比は、2500である。

## 【0076】

p型半導体層112をエピタキシャル成長させる温度は、950以上1200以下が好ましく、1000以上1100以下がいっそう好ましく、本実施形態では、1050である。p型半導体層112の成長温度が950未満である場合、結晶化に必要なエネルギーが十分にガリウム原子（Ga）および窒素原子（N）に供給されないため、結晶の異常成長によってp型半導体層112に空洞が発生する場合がある。p型半導体層1

10

20

30

40

50

12の成長温度が1100℃超過である場合、過剰な熱エネルギーによってn型半導体層111からガリウム原子(Ga)および窒素原子(N)が抜け出すことによってn型半導体層111の結晶構造が崩壊するため、p型半導体層112を成長させることができなくなる。

【0077】

p型半導体層112をエピタキシャル成長させる圧力は、1kPa以上100kPa以下が好ましく、10kPa以上100kPa以下がいっそう好ましく、本実施形態では、100kPaである。p型半導体層112の成長圧力が1kPa未満である場合、p型半導体層112に炭素原子(C)が過剰に取り込まれることによって、p型半導体層112のp型特性が劣化する。

10

【0078】

他の形態では、製造者は、p型半導体層112を形成した後、炉内温度を維持した状態で、III族原料、V族原料およびアクセプタ不純物の供給を止めて、キャリアガスである水素(H<sub>2</sub>)を用いて、上面111tに形成されたp型半導体層112を除去してもよい。これによって、p型半導体層112の後に形成されるp型半導体層113のチャネル113cにおける移動度を向上させることができる。

【0079】

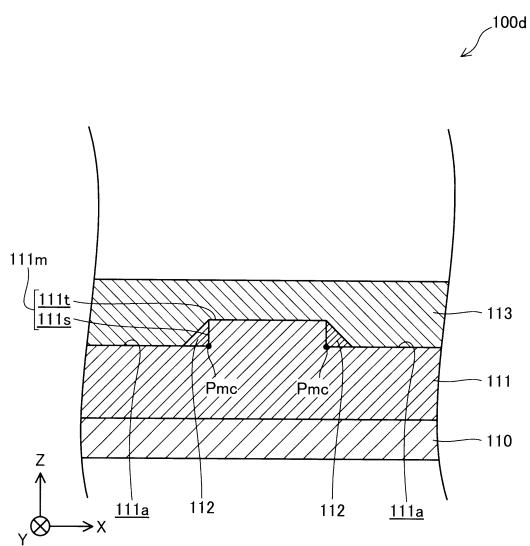

p型半導体層112を形成した後(工程P130)、製造者は、第1のV/III比より低い第2のV/III比でIII族原料とV族原料とを含有する原料ガスを用いたエピタキシャル成長によって、p型半導体層112の上にp型半導体層113を形成する(工程P140、図10)。これによって、製造者は、製造途中にある半導体装置100として、p型半導体層112の上にp型半導体層113が形成された半導体装置100dを得る。本実施形態では、製造者は、p型半導体層112を形成した第1のV/III比より低い第2のV/III比で原料ガスを炉内に導入するとともに、p型半導体層112を形成する際よりアクセプタ不純物の供給量を減少させることによって、p型半導体層112の上にp型半導体層113を成長させる。p型半導体層113を形成する原料ガスのV/III比は、250以上3000以下が好ましく、本実施形態では、1500である。

20

【0080】

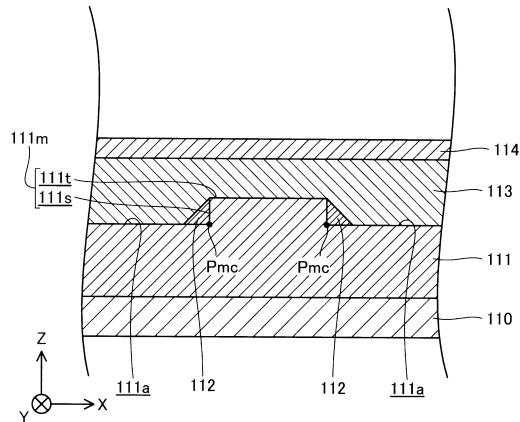

p型半導体層113を形成した後(工程P140)、製造者は、エピタキシャル成長によってp型半導体層113の上にn型半導体層114を形成する(工程P150、図11)。これによって、製造者は、製造途中にある半導体装置100として、p型半導体層113の上にn型半導体層114が形成された半導体装置100eを得る。本実施形態では、n型半導体層114を形成する原料ガスのV/III比は、900以上3000以下である。

30

【0081】

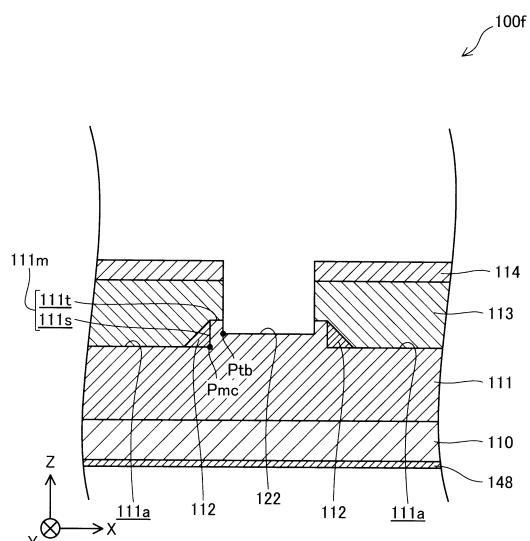

n型半導体層114を形成した後(工程P150)、製造者は、トレンチ122を形成する(工程P160、図12)。これによって、製造者は、製造途中にある半導体装置100として、トレンチ122が形成された半導体装置100fを得る。本実施形態では、製造者は、塩素系ガスを用いたドライエッチングによってトレンチ122を形成する。

【0082】

40

トレンチ122を形成した後(工程P160)、製造者は、絶縁膜130を形成する(工程P170、図13)。これによって、製造者は、製造途中にある半導体装置100として、トレンチ122に絶縁膜130が形成された半導体装置100gを得る。本実施形態では、製造者は、二酸化ケイ素(SiO<sub>2</sub>)を用いて絶縁膜130を形成する。本実施形態では、製造者は、原子層堆積法(ALD:Atomic Layer Deposition)によって絶縁膜130を形成する。他の実施形態では、製造者は、スパッタ法、プラズマCVDなどによって絶縁膜130を形成してもよい。本実施形態では、製造者は、トレンチ122の内側から外側にわたって絶縁膜130を形成する。

【0083】

絶縁膜130を形成した後(工程P170)、製造者は、各電極を形成する(工程P1

50

80)。本実施形態では、まず、製造者は、トレンチ122にゲート電極142を形成する。その後、製造者は、ドライエッティングによってリセス124を形成し、そのリセス124にソース電極144を形成する。その後、製造者は、ドレイン電極148を形成する。

【0084】

各電極を形成した後(工程P180)、絶縁膜150および配線電極160の形成を経て、半導体装置100が完成する。

【0085】

A-4.効果

以上説明した第1実施形態によれば、p型半導体層112が角部Pmcから側面111sにわたって形成されているため、p型半導体層112のアクセプタ元素によって角部Pmcおよび側面111sにおいて空乏層Dp,Dp+を十分に形成できる。また、p型半導体層112の上にp型半導体層113が形成されているため、p型半導体層113におけるチャネル113cを構成する部位へとp型半導体層112から拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置100のトレンチゲート構造において、チャネル113cの電気特性を確保しつつ、耐電圧特性を向上させることができる。

【0086】

また、p型半導体層112は、上面111tより周囲面111aが位置する-Z軸方向側に形成されている。これによって、p型半導体層112に含まれるアクセプタ元素に起因するオン抵抗の増大をいっそう抑制できる。したがって、チャネル113cの電気特性をいっそう十分に確保できる。

【0087】

また、p型半導体層112は、p型半導体層112の上から上面111tにわたって形成されている。これによって、p型半導体層112が上面111tに形成されていない構造と比較して、p型半導体層112に含まれるアクセプタ元素に起因するオン抵抗の増大を抑制できる。したがって、チャネル113cの電気特性を十分に確保できる。

【0088】

また、p型半導体層112の厚さは、メサ構造111mから離れるに従って薄くなるため、p型半導体層113におけるチャネル113cを構成する部位へとp型半導体層112から拡散するアクセプタ元素をいっそう抑制できる。

【0089】

また、p型半導体層112とp型半導体層113との界面112pが上面111tと成す角度Apは、約45°であるため、角部Pmcおよび側面111sにおける空乏層Dp,Dp+の形成と、p型半導体層112からチャネル113cへと拡散するアクセプタ元素の抑制との両立を図ることができる。

【0090】

また、トレンチ122は、周囲面111aよりn型半導体層114が位置する+Z軸方向側に形成されているため、トレンチ122の底部Ptbにおける電界集中を効果的に緩和できる。

【0091】

また、p型半導体層112に含まれるアクセプタ元素の濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上 $8 \times 10^{19} \text{ cm}^{-3}$ 以下であるため、角部Pmcおよび側面111sにおいて空乏層Dp,Dp+を効果的に形成できる。

【0092】

また、側面111sにおける結晶面がa面であるため、側面111sにおけるp型半導体層112の結晶品質を向上させることができる。

【0093】

また、p型半導体層112は、側面111sの全域にわたって形成され、p型半導体層113は、p型半導体層112の上から上面111tにわたって形成されているため、角部Pmcおよび側面111sにおいて空乏層を効果的に形成できる。

10

20

30

40

50

## 【0094】

また、半導体装置100の製造方法は、第1のV/III比で含有する原料ガスを用いたエピタキシャル成長によって、p型半導体層112を、角部Pmcから少なくとも側面111sにわたって形成し；第1のV/III比より低い第2のV/III比でIII族原料とV族原料とを含有する原料ガスを用いたエピタキシャル成長によって、アクセプタ元素をp型半導体層112より低い濃度で含有するp型半導体層113を、p型半導体層112の上に形成する。これによって、上面111tの上方に位置するp型半導体層113へとp型半導体層112から拡散するアクセプタ元素が抑制されるように、p型半導体層112を角部Pmcから側面111sにわたって容易に形成できる。

## 【0095】

また、p型半導体層112に含まれるアクセプタ元素Acの濃度が $1 \times 10^{-9} \text{ cm}^{-3}$ 以上 $8 \times 10^{-9} \text{ cm}^{-3}$ 以下となるようにp型半導体層112を形成するため、角部Pmcおよび側面111sにおいて空乏層を効果的に形成可能にp型半導体層112を形成できる。

## 【0096】

また、側面111sにおける結晶面がa面となるようにメサ構造111mを形成するため、a面ではm面およびc面と比較してp型半導体層112の成長速度が速いため、角部Pmcおよび側面111sに対してp型半導体層112を容易に形成できる。

## 【0097】

また、側面111sの全域にわたってp型半導体層112を形成し、p型半導体層112の上から上面111tにわたってp型半導体層113を形成するため、角部Pmcおよび側面111sにおいて空乏層を効果的に形成可能にp型半導体層112およびp型半導体層113を形成できる。

## 【0098】

また、p型半導体層112を形成するV/III比は、2500以上3000以下であるため、角部Pmcおよび側面111sに対してp型半導体層112を容易に形成できる。

## 【0099】

また、p型半導体層112をエピタキシャル成長させる温度は、950以上1200以下であるため、角部Pmcおよび側面111sに対してp型半導体層112をいっそう容易に形成できる。

## 【0100】

また、p型半導体層112をエピタキシャル成長させる圧力は、1kPa以上100kPa以下であるため、角部Pmcおよび側面111sに対してp型半導体層112をいっそう容易に形成できる。

## 【0101】

## A - 5 . 変形例

図14は、第1実施形態の変形例における半導体装置100の製造方法を示す工程図である。第1実施形態の変形例における製造方法は、n型半導体層111の界面にアクセプタ元素をデルタドーピングする点を除き、上述の製造方法と同様である。第1実施形態の変形例では、n型半導体層111にメサ構造111mを形成した後（工程P120、図8）、製造者は、n型半導体層111の上面111t、側面111sおよび周囲面111aの各面に対して、アクセプタ元素としてマグネシウム（Mg）をデルタドーピングする（工程P125）。これによって、上面111t、側面111sおよび周囲面111aの各面は、アクセプタ元素がデルタドーピングされた界面となる。アクセプタ元素をデルタドーピングする面は、上面111t、側面111sおよび周囲面111aの各面ではなく、これらのうち少なくとも1つの面であればよい。本変形例によれば、デルタドーピングされた界面において空乏層Dp, Dp+をいっそう十分に形成できる。

## 【0102】

## B . 第2実施形態

図15は、第2実施形態における半導体装置100Bの詳細構成を示す説明図である。

10

20

30

40

50

半導体装置 100B は、p 型半導体層 112 および p 型半導体層 113 に代えて、p 型半導体層 112B および p 型半導体層 113B を備える点を除き、第 1 実施形態の半導体装置 100 と同様である。

#### 【0103】

半導体装置 100B の p 型半導体層 112B は、角部 Pmc から側面 111s に加え、上面 111t にわたって形成されている点を除き、第 1 実施形態の p 型半導体層 112 と同様である。p 型半導体層 112B は、上面 111t から +Z 軸方向へ 100nm の位置より -Z 軸方向側に形成されている。半導体装置 100B の p 型半導体層 113B は、上面 111t との間に p 型半導体層 112B を挟む点を除き、第 1 実施形態の p 型半導体層 113 と同様である。

10

#### 【0104】

第 2 実施形態によれば、第 1 実施形態と同様に、p 型半導体層 112B が角部 Pmc から側面 111s にわたって形成されているため、p 型半導体層 112B のアクセプタ元素によって角部 Pmc および側面 111s において空乏層を十分に形成できる。また、p 型半導体層 112B の上に p 型半導体層 113B が形成されているため、p 型半導体層 113B におけるチャネルを構成する部位へと p 型半導体層 112B から拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置 100B のトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

#### 【0105】

また、p 型半導体層 112B は、上面 111t から n 型半導体層 114 が位置する +Z 軸方向側へ 100nm の位置より、周囲面 111a が位置する -Z 軸方向側に形成されている。これによって、p 型半導体層 112B に含まれるアクセプタ元素に起因するオン抵抗の増大を防止できる。したがって、チャネルの電気特性を十分に確保できる。

20

#### 【0106】

##### C. 第 3 実施形態

図 16 は、第 3 実施形態における半導体装置 100C の詳細構成を示す説明図である。半導体装置 100C は、p 型半導体層 112 および p 型半導体層 113 に代えて、p 型半導体層 112C および p 型半導体層 113C を備える点を除き、第 1 実施形態の半導体装置 100 と同様である。

#### 【0107】

半導体装置 100C の p 型半導体層 112C は、Z 軸方向において上面 111t と同じ位置まで、周囲面 111a の全域にわたって形成されている点を除き、第 1 実施形態の p 型半導体層 112 と同様である。半導体装置 100C の p 型半導体層 113C は、上面 111t および p 型半導体層 112C の上にわたって形成されている点を除き、第 1 実施形態の p 型半導体層 113 と同様である。第 3 実施形態では、p 型半導体層 112C と p 型半導体層 113C との界面が上面 111t と成す角度は、0° である。

30

#### 【0108】

第 3 実施形態によれば、第 1 実施形態と同様に、p 型半導体層 112C が角部 Pmc から側面 111s にわたって形成されているため、p 型半導体層 112C のアクセプタ元素によって角部 Pmc および側面 111s において空乏層を十分に形成できる。また、p 型半導体層 112C の上に p 型半導体層 113C が形成されているため、p 型半導体層 113C におけるチャネルを構成する部位へと p 型半導体層 112C から拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置 100C のトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

40

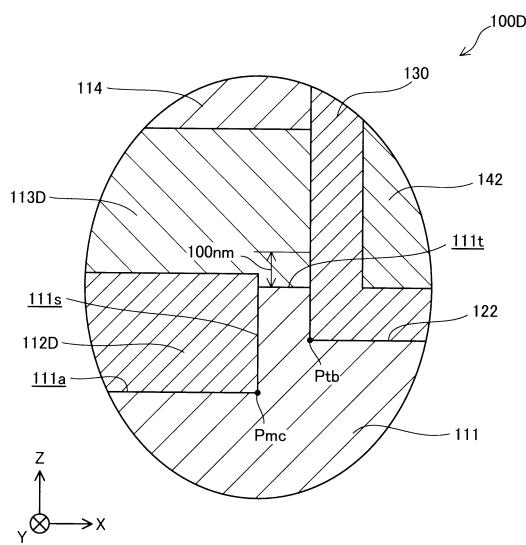

#### 【0109】

##### D. 第 4 実施形態

図 17 は、第 4 実施形態における半導体装置 100D の詳細構成を示す説明図である。半導体装置 100D は、p 型半導体層 112 および p 型半導体層 113 に代えて、p 型半導体層 112D および p 型半導体層 113D を備える点を除き、第 1 実施形態の半導体装置 100 と同様である。

50

## 【0110】

半導体装置100Dのp型半導体層112Dは、Z軸方向において上面111tから+Z軸方向へ100nmの範囲まで、周囲面111aの全域にわたって形成されている点を除き、第1実施形態のp型半導体層112と同様である。半導体装置100Dのp型半導体層113Dは、上面111tおよびp型半導体層112Dの上にわたって形成されている点を除き、第1実施形態のp型半導体層113と同様である。

## 【0111】

第4実施形態によれば、第1実施形態と同様に、p型半導体層112Dが角部Pmcから側面111sにわたって形成されているため、p型半導体層112Dのアクセプタ元素によって角部Pmcおよび側面111sにおいて空乏層を十分に形成できる。また、p型半導体層112Dの上にp型半導体層113Dが形成されているため、p型半導体層113Dにおけるチャネルを構成する部位へとp型半導体層112Dから拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置100Dのトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

10

## 【0112】

また、p型半導体層112Dは、上面111tからn型半導体層114が位置する+Z軸方向側へ100nmの位置より、周囲面111aが位置する-Z軸方向側に形成されている。これによって、p型半導体層112Dに含まれるアクセプタ元素に起因するオン抵抗の増大を防止できる。したがって、チャネルの電気特性を十分に確保できる。

20

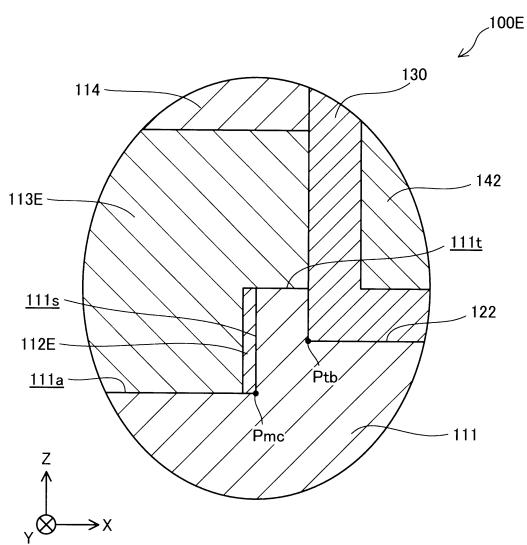

## 【0113】

## E. 第5実施形態

図18は、第5実施形態における半導体装置100Eの詳細構成を示す説明図である。半導体装置100Eは、p型半導体層112およびp型半導体層113に代えて、p型半導体層112Eおよびp型半導体層113Eを備える点を除き、第1実施形態の半導体装置100と同様である。

## 【0114】

半導体装置100Eのp型半導体層112Eは、Z軸方向において上面111tと同じ位置まで、角部Pmcから側面111sに沿って形成されている点を除き、第1実施形態のp型半導体層112と同様である。半導体装置100Eのp型半導体層113Eは、上面111t、周囲面111aおよびp型半導体層112Eの上にわたって形成されている点を除き、第1実施形態のp型半導体層113と同様である。第5実施形態では、p型半導体層112Eとp型半導体層113Eとの界面が上面111tと成す角度は、90°である。

30

## 【0115】

第5実施形態によれば、第1実施形態と同様に、p型半導体層112Eが角部Pmcから側面111sにわたって形成されているため、p型半導体層112Eのアクセプタ元素によって角部Pmcおよび側面111sにおいて空乏層を十分に形成できる。また、p型半導体層112Eの上にp型半導体層113Eが形成されているため、p型半導体層113Eにおけるチャネルを構成する部位へとp型半導体層112Eから拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置100Eのトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

40

## 【0116】

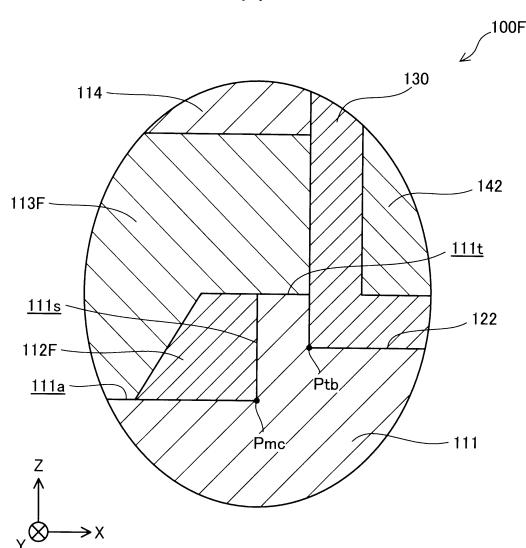

## F. 第6実施形態

図19は、第6実施形態における半導体装置100Fの詳細構成を示す説明図である。半導体装置100Fは、p型半導体層112およびp型半導体層113に代えて、p型半導体層112Fおよびp型半導体層113Fを備える点を除き、第1実施形態の半導体装置100と同様である。

## 【0117】

半導体装置100Fのp型半導体層112Fは、側面111s付近において一定の厚さ(Z軸方向の長さ)を有する点を除き、第1実施形態のp型半導体層112と同様である

50

。半導体装置 100F の p 型半導体層 113F は、上面 111t、周囲面 111a および p 型半導体層 112F の上にわたって形成されている点を除き、第 1 実施形態の p 型半導体層 113 と同様である。

#### 【 0118 】

第 6 実施形態によれば、第 1 実施形態と同様に、p 型半導体層 112F が角部 Pmc から側面 111s にわたって形成されているため、p 型半導体層 112F のアクセプタ元素によって角部 Pmc および側面 111s において空乏層を十分に形成できる。また、p 型半導体層 112F の上に p 型半導体層 113F が形成されているため、p 型半導体層 113F におけるチャネルを構成する部位へと p 型半導体層 112F から拡散するアクセプタ元素を抑制できる。これらの結果、半導体装置 100F のトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

10

#### 【 0119 】

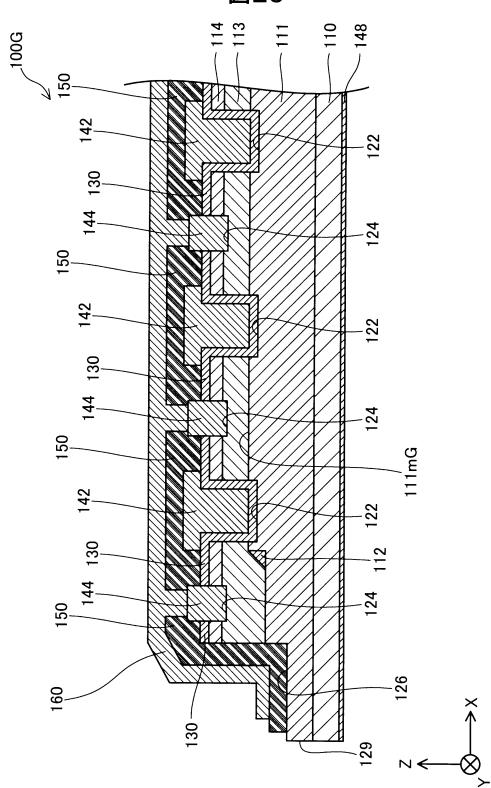

#### G. 第 7 実施形態

図 20 は、第 7 実施形態における半導体装置 100G の構成を示す説明図である。半導体装置 100G は、n 型半導体層 111 にメサ構造 111mG が形成されている点を除き、第 1 実施形態の半導体装置 100 と同様である。半導体装置 100G のメサ構造 111mG は、複数のトレンチ 122 が形成されている点を除き、第 1 実施形態のメサ構造 111m と同様である。第 7 実施形態によれば、第 1 実施形態と同様に、半導体装置 100G のトレンチゲート構造において、チャネルの電気特性を確保しつつ、耐電圧特性を向上させることができる。

20

#### 【 0120 】

#### H. 他の実施形態

本発明は、上述の実施形態や実施例、変形例に限られるものではなく、その趣旨を逸脱しない範囲において種々の構成で実現することができる。例えば、発明の概要の欄に記載した各形態中の技術的特徴に対応する実施形態、実施例、変形例中の技術的特徴は、上述の課題の一部または全部を解決するために、あるいは、上述の効果の一部または全部を達成するために、適宜、差し替えや、組み合わせを行うことが可能である。また、その技術的特徴が本明細書中に必須なものとして説明されていなければ、適宜、削除することが可能である。

30

#### 【 0121 】

本発明が適用される半導体装置は、上述の実施形態で説明した縦型トレンチ MOSFET に限られず、例えば、絶縁ゲートバイポーラトランジスタ ( IGBT : Insulated Gate Bipolar Transistor ) 、 MESFET ( metal-semiconductor field effect transistor ) などであってもよい。本発明の構造は、終端構造に適用できる。本発明の製造方法は、n 型半導体層と p 型半導体層とを相互に置き換えた構造の製造に適用できる。

#### 【 0122 】

上述の実施形態において、基板の材質は、窒化ガリウム ( GaN ) に限らず、ケイ素 ( Si ) 、サファイア ( Al<sub>2</sub>O<sub>3</sub> ) および炭化ケイ素 ( SiC ) などのいずれであってもよい。上述の実施形態において、各半導体層の材質は、窒化ガリウム ( GaN ) に限らず、ガリウム ( Ga ) を含有する窒化物半導体であればよい。

40

#### 【 0123 】

上述の実施形態において、n 型半導体層に含まれるドナー元素は、ケイ素 ( Si ) に限らず、ゲルマニウム ( Ge ) 、酸素 ( O ) などであってもよい。

#### 【 0124 】

上述の実施形態において、p 型半導体層に含まれるアクセプタ元素は、マグネシウム ( Mg ) に限らず、亜鉛 ( Zn ) 、炭素 ( C ) などであってもよい。

#### 【 0125 】

上述の実施形態において、絶縁膜 130 の材質は、電気絶縁性を有する材質であればよく、二酸化ケイ素 ( SiO<sub>2</sub> ) の他、窒化ケイ素 ( SiNx ) 、酸化アルミニウム ( Al<sub>2</sub>O<sub>3</sub> ) 、窒化アルミニウム ( AlN ) 、酸化ジルコニア ( ZrO<sub>2</sub> ) 、酸化ハフニウム ( HfO<sub>2</sub> ) などであってもよい。

50

ム ( HfO<sub>2</sub> ) 、酸窒化ケイ素 ( SiON ) 、酸窒化アルミニウム ( AlON ) 、酸窒化ジルコニウム ( ZrON ) 、酸窒化ハフニウム ( HfON ) などの少なくとも 1 つであってもよい。絶縁膜 130 は、単層であってもよいし、2 層以上であってもよい。

## 【 0126 】

上述の実施形態において、各電極の材質は、上述の実施形態の材質に限らず、他の材質であってもよい。

## 【 符号の説明 】

## 【 0127 】

|                  |                       |

|------------------|-----------------------|

| 10               | 10 ... 電力変換装置         |

| 100              | 100B ~ 100G ... 半導体装置 |

| 100a ~ 100g      | ... 半導体装置             |

| 110              | ... 基板                |

| 111              | ... n 型半導体層           |

| 111a             | ... 周囲面               |

| 111m, 111mG      | ... メサ構造              |

| 111s             | ... 側面                |

| 111t             | ... 上面                |

| 112, 112B ~ 112F | ... p 型半導体層           |

| 112p             | ... 界面                |

| 113, 113B ~ 113F | ... p 型半導体層           |

| 113c             | ... チャネル              |

| 114              | ... n 型半導体層           |

| 122              | ... トレンチ              |

| 124              | ... リセス               |

| 126              | ... 段差部               |

| 129              | ... 終端部               |

| 130              | ... 絶縁膜               |

| 142              | ... ゲート電極             |

| 144              | ... ソース電極             |

| 148              | ... ドレイン電極            |

| 150              | ... 絶縁膜               |

| 160              | ... 配線電極              |

| 200              | ... 制御回路              |

| A p              | ... 角度                |

| A c              | ... アクセプタ元素           |

| D n              | ... ドナー               |

| P t b            | ... 底部                |

| P m c            | ... 角部                |

| D p              | ... 空乏層               |

| D p +            | ... 空乏層               |

| C                | ... キャパシタ             |

| D 1, D 2         | ... ダイオード             |

| D B              | ... ダイオードブリッジ         |

| E                | ... 交流電源              |

| L                | ... コイル               |

| R                | ... 負荷                |

| T n              | ... 負極出力端             |

| T p              | ... 正極出力端             |

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

### 【図17】

図17

【 図 1 8 】

図18

### 【図19】

图 19

【図20】

図20

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/06 | 3 0 1 D |

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 21/20 |         |

審査官 杉山 芳弘

(56)参考文献 特開2009-260253 (JP, A)

特開平10-294463 (JP, A)

特開2014-236189 (JP, A)

国際公開第2015/072052 (WO, A1)

特開2004-040097 (JP, A)

特開2010-062381 (JP, A)

特開2009-141363 (JP, A)

特開2014-192934 (JP, A)

特表2003-526907 (JP, A)

特開2013-222932 (JP, A)

特開2014-209540 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 29 / 12