(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4879413号

(P4879413)

(45) 発行日 平成24年2月22日(2012.2.22)

(24) 登録日 平成23年12月9日(2011.12.9)

(51) Int.Cl.

F 1

|             |             |                  |      |      |         |

|-------------|-------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/36</b> | <b>(2006.01)</b> | G09G | 3/36 |         |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

| <b>G09G</b> | <b>3/30</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 3 G |

|             |             |                  | G09G | 3/20 | 6 2 4 B |

|             |             |                  | G09G | 3/30 | J       |

請求項の数 9 (全 33 頁)

(21) 出願番号

特願2001-224405 (P2001-224405)

(22) 出願日

平成13年7月25日 (2001.7.25)

(65) 公開番号

特開2002-132233 (P2002-132233A)

(43) 公開日

平成14年5月9日 (2002.5.9)

審査請求日

平成20年7月18日 (2008.7.18)

(31) 優先権主張番号

特願2000-224479 (P2000-224479)

(32) 優先日

平成12年7月25日 (2000.7.25)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 棚田 好文

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 中村 直行

(56) 参考文献 特開平10-177371 (JP, A)

特開平08-171080 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

保持回路と、

ソース又はドレインの一方が前記保持回路の入力端に電気的に接続され、他方が第1の配線と電気的に接続された第1のトランジスタと、

前記保持回路の入力端と、第2の配線との間に直列に設けられた第2乃至第4のトランジスタとを有し、

前記第1のトランジスタのゲートには、プリチャージ信号が入力されることによって、前記保持回路の入力端と、前記第1の配線との導通、非導通が制御され、

前記第2のトランジスタのゲートにサンプリングパルスが入力され、前記第3のトランジスタのゲートにマルチブレクス信号が入力され、前記第4のトランジスタのゲートにデジタル映像信号が入力されることによって、前記保持回路の入力端と、前記第2の配線との導通、非導通が制御され、

前記第1のトランジスタは、帰線期間中にオンになることを特徴とする半導体装置。

【請求項 2】

保持回路と、

ソース又はドレインの一方が前記保持回路の入力端に電気的に接続され、他方が第1の配線と電気的に接続された第1のトランジスタと、

前記保持回路の入力端と、第2の配線との間に直列に設けられた第2乃至第4のトランジスタと

10

ソース又はドレンの一方が前記保持回路の入力端に電気的に接続され、他方が前記第1の配線と電気的に接続され、ゲートが前記第2の配線と電気的に接続された第5のトランジスタとを有し、

前記第1のトランジスタのゲートには、プリチャージ信号が入力されることによって、前記保持回路の入力端と、前記第1の配線との導通、非導通が制御され、

前記第2のトランジスタのゲートにサンプリングパルスが入力され、前記第3のトランジスタのゲートにマルチプレクス信号が入力され、前記第4のトランジスタのゲートにデジタル映像信号が入力されることによって、前記保持回路の入力端と、前記第2の配線との導通、非導通が制御され、

前記第1のトランジスタは帰線期間中にオンになることを特徴とする半導体装置。

10

**【請求項3】**

請求項1又は請求項2において、

前記マルチプレクス信号の一段分のパルス幅は、前記サンプリングパルスの一段分のパルス幅よりも小さく、かつその一段分の出力期間は前記サンプリングパルスの一段分の出力期間に含まれ、

前記デジタル映像信号の一段分のパルス幅は、前記サンプリングパルスの一段分のパルス幅よりも小さく、かつその一段分の出力期間は前記サンプリングパルスの一段分の出力期間に含まれることを特徴とする半導体装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一において、

20

前記保持回路は、一方の出力端が他方の入力端と電気的に接続されるように、ループ状に設けられた2個のインバータを含むことを特徴とする半導体装置。

**【請求項5】**

請求項1乃至請求項3のいずれか一において、

前記保持回路は、保持容量を含むことを特徴とする半導体装置。

**【請求項6】**

請求項1乃至請求項5のいずれか一において、

前記第1の配線には、第1の電源電位が入力され、前記第2の配線には、前記第1の電源電位とは異なる第2の電源電位が入力されることを特徴とする半導体装置。

**【請求項7】**

30

請求項1乃至請求項6のいずれか一項において、

前記サンプリングパルス、前記マルチプレクス信号及び前記デジタル映像信号の振幅は、前記第1の配線と前記第2の配線との電位差よりも小さいことを特徴とする半導体装置。

**【請求項8】**

請求項1乃至請求項7のいずれか一項において、

第2の保持回路を有し、

ラッチ信号に応じて、前記保持回路に保持されている信号が前記第2の保持回路へと転送されることを特徴とする半導体装置。

**【請求項9】**

40

請求項1乃至請求項8のいずれか一に記載の半導体装置と、操作スイッチとを具備したことを特徴とする電子機器。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

**【0002】**

本発明は、半導体表示装置（以下表示装置と表記する）の駆動回路および駆動回路を用いた表示装置に関し、特に、絶縁体上に作成される薄膜トランジスタ（以下TFTと表記する）を有するアクティブマトリクス型表示装置の駆動回路および駆動回路を用いたアクティブマトリクス型表示装置に関する。その中で特に、デジタル映像信号を入力するアクテ

50

イブマトリクス型表示装置の駆動回路および駆動回路を用いたアクティブマトリクス型表示装置に関する。

【0003】

【従来の技術】

近年、絶縁体上、特にガラス基板上に半導体薄膜を形成した表示装置、特にTFTを用いたアクティブマトリクス型表示装置の普及が進んでいる。TFTを使用したアクティブマトリクス型表示装置は、マトリクス状に配置された数十万から数百万のTFTを有し、各画素の電荷を制御することによって映像の表示を行っている。

【0004】

さらに最近の技術として、画素を構成する画素TFTの他に、画素部の周辺部に、TFTを用いて駆動回路を同時形成するポリシリコンTFTに関する技術が発展してきている。 10

【0005】

また、ここで同時形成される駆動回路も、アナログ映像信号対応のものにとどまらず、デジタル映像信号に対応したものが実現されている。

【0006】

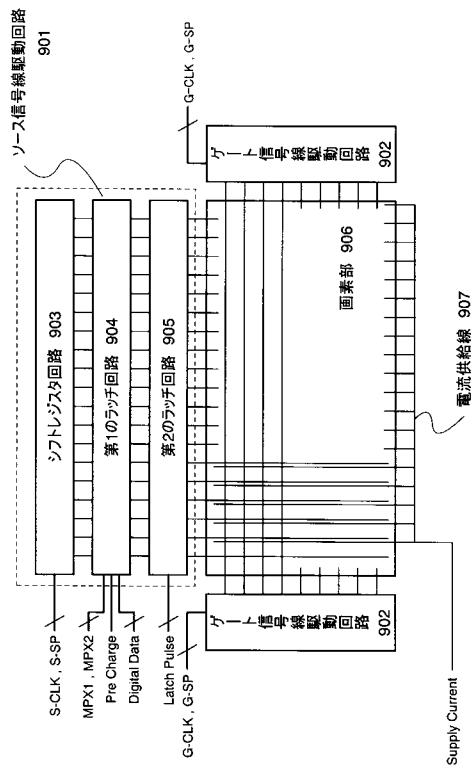

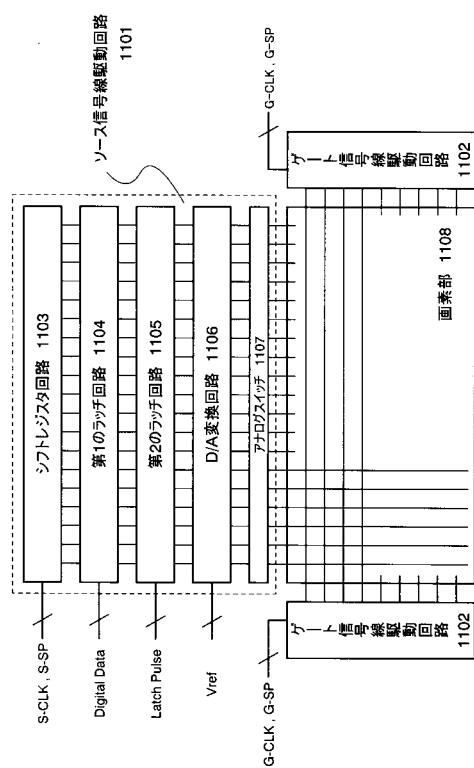

通常のデジタル映像信号入力方式の表示装置の概略図を、図11に示す。中央に画素部1108が配置されている。画素部の上側には、ソース信号線を制御するための、ソース信号線駆動回路1101が配置されている。ソース信号線駆動回路1101は、第1のラッチ回路1104、第2のラッチ回路1105、D/A変換回路1106、アナログスイッチ1107等を有する。画素部の左右には、ゲート信号線を制御するための、ゲート信号線駆動回路1102が配置されている。なお、図11においては、ゲート信号線駆動回路1102は、画素部の左右両側に配置されているが、片側配置でも構わない。ただし、両側配置とした方が、駆動効率、駆動信頼性の面から見て望ましい。 20

【0007】

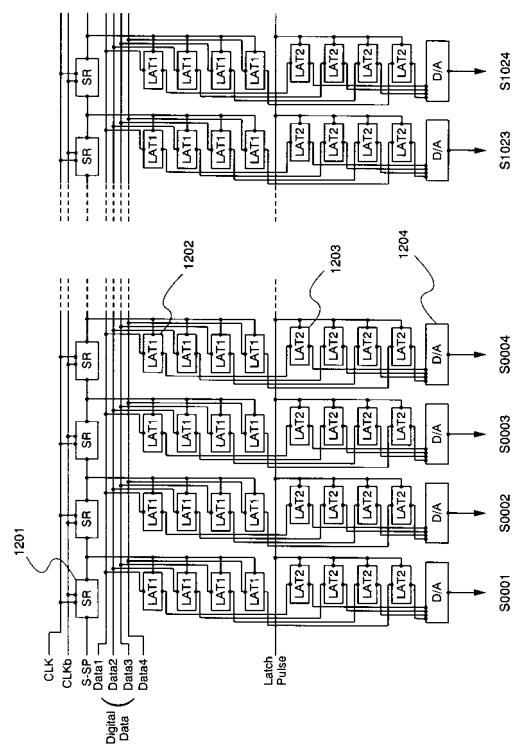

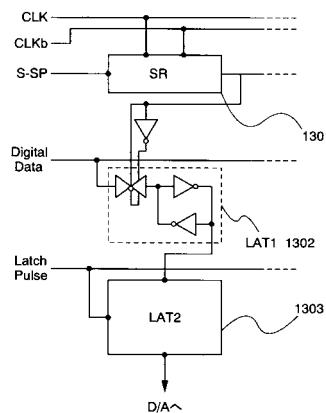

ソース信号線駆動回路1101に関しては、図12に示すような構成を有している。この駆動回路は、水平方向解像度1024画素、4ビット階調表示能力を有する表示装置のソース信号線駆動回路であり、シフトレジスタ回路1201(SR)、第1のラッチ回路1202(LAT1)、第2のラッチ回路1203(LAT2)、D/A変換回路1204(D/A)等を有する。なお、図12では、図11におけるアナログスイッチ1107は図示していない。また、必要に応じて、バッファ回路あるいはレベルシフタ回路等を追加配置しても良い。 30

【0008】

また、本明細書において、順次サンプリングパルスを出力するための回路を具体的に示す際には、シフトレジスタ回路と統一して記述しているが、本発明に関し、必ずしもシフトレジスタ回路によってサンプリングパルスを出力するという限定はしない。

【0009】

図11および図12を用いて回路の動作について簡潔に説明する。まず、シフトレジスタ回路1201に、クロック信号(CLK)、クロック反転信号(CLKb)およびスタートパルス(S-SP)が入力され、順次サンプリングパルスが出力される。第1のラッチ回路1202においては、サンプリングパルスの入力に伴って、デジタル映像信号(Digital Data)をそれぞれ保持していく。図12では、4ビットのデジタル映像信号を扱うため、最下位から最上位までの各ビットのデータを同時に保持するよう、1段のシフトレジスタ回路から出力されるサンプリングパルスによって4つの第1のラッチ回路が同時に動作する。第1のラッチ回路1202において、1水平周期分の映像信号の保持が完了すると、帰線期間中にラッチ信号(Latch Pulse)が入力され、第1のラッチ回路1202で保持されている映像信号は一斉に第2のラッチ回路1203へと転送される。 40

【0010】

その後、再びシフトレジスタ回路1201の第1段目からサンプリングパルスが出力され、続く水平周期分の映像信号の保持が開始される。同時に、第2のラッチ回路1203に 50

て保持されている映像信号は、D/A変換回路1204に入力され、アナログ信号へと変換される。ここでアナログ化された映像信号は、ソース信号線(S0001～S1024)を経由して画素(図示せず)へと書き込まれる。この動作を繰り返すことによって、映像の表示が行われる。

【0011】

【発明が解決しようとする課題】

図13は、図12に示したソース信号線駆動回路の一部分を図示したものである。サンプリングパルスが第1のラッチ回路1302に入力され、1ビット分のデジタル映像信号を保持し、1水平期間分のデジタル映像信号の保持が完了すると、ラッチ信号(Latch Pulse)の入力により、第2のラッチ回路1303へと転送される。ここで、第2のラッチ回路は、第1のラッチ回路と同様の回路構成で良い。

10

【0012】

ところで、クロック信号(CLK)クロック反転信号(CLKb)、スタートパルス(SP)、デジタル映像信号(Digital Data)およびラッチ信号(Latch Pulse)は、ともに外部から直接入力される信号であり、任意のタイミングでの入力が可能である。一方、デジタル映像信号を保持するパルスのタイミングは、シフトレジスタ回路1301から出力されるサンプリングパルスのタイミングによる。映像信号を正常に保持するためには、両者のタイミングが合致している必要があるが、サンプリングパルスは、既に複数の回路を通過しているため、図2(A)に示すように、タイミングチャート上のサンプリングパルスに対して、201で示すだけの遅延が生ずる。デジタル映像信号は当初、タイミングチャート上でのサンプリングパルスに合わせて入力されるため、この状態では正常に映像信号を保持できない。よってこのような場合は、遅延を生じた実際のパルスの出力に合わせて、デジタル映像信号の入力タイミングの微調整が必要となる。

20

【0013】

さらに、この遅延時間は、回路を構成するTFTの特性のばらつき等によっても変化するため、表示装置ごとに異なる場合が多い。よってその都度、個々に合わせて微調整する必要がある。

【0014】

加えて、近年のLCDの急速な高解像度化、高精細化に伴い、駆動回路全体の駆動周波数が高くなっているため、わずかに生じた遅延であっても、デジタル映像信号の保持動作を正常に行なうことが出来なくなる場合がある。

30

【0015】

本発明は、このような課題を解決するためになされたものであり、サンプリングパルスの遅延がデジタル映像信号の保持動作に影響しにくい構造を有する駆動回路を提供することを目的とする。

【0016】

【課題を解決するための手段】

前述した課題を解決するために、本発明においては以下のようないくつかの手段を講じた。

【0017】

図11～図13に示した従来例のような駆動回路においては、サンプリングパルスの遅延時間に合わせて、デジタル映像信号の入力タイミングの微調整を行う必要があり、さらにその遅延時間が表示装置ごとのばらつきがあるために個々について行わなければならなかつた。

40

【0018】

これに対して、本発明の駆動回路においては、第1のラッチ回路の保持タイミングを、外部からの信号入力によって直接決定する方法をとり、サンプリングパルスの少々の遅延が、保持タイミングに影響しないようにした。つまり、表示装置ごとにばらつきがあったとしても、保持タイミング用の信号とデジタル映像信号を同時に外部から入力することで、両者が常に決まったタイミングで回路に入力され、常に正常に保持動作が行われる。また

50

、従来のように、タイミングを回路の遅延に合わせて微調整するのではなく、複数の信号の入力段階であらかじめタイミングを合わせて入力するだけであるため、その調整が大変容易になる。

【0019】

以下に、本発明の表示装置の駆動回路の構成について記載する。

【0020】

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

前記保持回路の信号入力部と、第1の電源との間に設けられたプリチャージ回路と、

前記保持回路の信号入力部と、デジタル映像信号線との間に設けられた保持動作選択回路とを有し、

10

前記プリチャージ回路には、プリチャージ信号が入力され、

前記保持動作選択回路には、サンプリングパルスと、マルチプレクス信号と、デジタル映像信号とが入力されることを特徴としている。

【0021】

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

前記保持回路の信号入力部と、第1の電源との間に設けられたプリチャージ回路と、

前記保持回路の信号入力部と、デジタル映像信号線との間に設けられた保持動作選択回路とを有し、

20

前記プリチャージ回路には、プリチャージ信号が入力され、

前記保持動作選択回路には、サンプリングパルスと、マルチプレクス信号と、デジタル映像信号とが入力され、

前記プリチャージ回路は、前記プリチャージ信号の入力により、前記保持部の信号入力部と前記第1の電源とを導通し、

前記保持動作選択回路において、前記サンプリングパルスと、前記マルチプレクス信号と、前記デジタル映像信号の入力が重複する期間で、前記保持回路において、前記デジタル映像信号の保持を行うことを特徴としている。

【0022】

本発明の表示装置の駆動回路は、

30

入力されたデジタル映像信号の保持を行う保持回路と、

第1の電源と前記保持回路の信号入力部との間に設けられた第1のトランジスタと、

第2の電源と前記保持回路の信号入力部との間に直列に設けられた第2、第3および第4のトランジスタとを有し、

前記第1のトランジスタのゲート電極にはプリチャージ信号が入力され、

前記第2のトランジスタのゲート電極にはマルチプレクス信号が入力され、

前記第3のトランジスタのゲート電極にはデジタル映像信号が入力され、

前記第4のトランジスタのゲート電極にはサンプリングパルスが入力されることを特徴としている。

【0023】

40

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

第1の電源と前記保持回路の信号入力部との間に設けられた第1のトランジスタと、

第2の電源と前記保持回路の信号入力部との間に直列に設けられた第2、第3および第4のトランジスタとを有し、

前記第1のトランジスタのゲート電極にはプリチャージ信号が入力され、

前記第2のトランジスタのゲート電極にはマルチプレクス信号が入力され、

前記第3のトランジスタのゲート電極にはデジタル映像信号が入力され、

前記第4のトランジスタのゲート電極にはサンプリングパルスが入力され、

前期保持回路は、前記マルチプレクス信号と、前記デジタル映像信号と、前記サンプリ

50

グパルスとの入力が重複する期間において、前記デジタル映像信号の保持を行うことを特徴としている。

【0024】

本発明の表示装置の駆動回路は、

請求項3または請求項4に記載の表示装置の駆動回路において、

前記プリチャージ信号の入力により第1のトランジスタが導通し、前記保持回路の信号入力部における電位が第1の電源電位をとり、

サンプリングパルスが出力されている期間内にマルチプレクス信号およびデジタル映像信号が入力され、前記第2～第4のトランジスタが導通し、前記保持回路の信号入力部における電位が第2の電源電位に変化し、

10

以後、次の帰線期間までの間、前記保持回路において第2の電源電位が保持されることを特徴としている。

【0025】

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

第1の電源と前記保持回路の信号入力部との間に並列配置された第1および第2のトランジスタと、

第2の電源と前記保持回路の信号入力部との間に直列配置された第3、第4および第5のトランジスタとを有し、

前記第1のトランジスタのゲート電極にはプリチャージ信号が入力され、

20

前記第2のトランジスタのゲート電極には第2の電源電位が印加され、

前記第3のトランジスタのゲート電極にはマルチプレクス信号が入力され、

前記第4のトランジスタのゲート電極にはデジタル映像信号が入力され、

前記第5のトランジスタのゲート電極にはサンプリングパルスが入力されることを特徴としている。

【0026】

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

第1の電源と前記保持回路の信号入力部との間に並列配置された第1および第2のトランジスタと、

30

第2の電源と前記保持回路の信号入力部との間に直列配置された第3、第4および第5のトランジスタとを有し、

前記第1のトランジスタのゲート電極にはプリチャージ信号が入力され、

前記第2のトランジスタのゲート電極には第2の電源電位が印加され、

前記第3のトランジスタのゲート電極にはマルチプレクス信号が入力され、

前記第4のトランジスタのゲート電極にはデジタル映像信号が入力され、

前記第5のトランジスタのゲート電極にはサンプリングパルスが入力され、

前期保持回路は、前記マルチプレクス信号と、前記デジタル映像信号と、前記サンプリングパルスとの入力が重複する期間において前記デジタル映像信号の保持を行うことを特徴としている。

40

【0027】

本発明の表示装置の駆動回路は、

請求項6または請求項7に記載の表示装置の駆動回路において、

前記プリチャージ信号の入力により第1のトランジスタが導通し、前記保持回路の信号入力部における電位が第1の電源電位をとり、

サンプリングパルスが出力されている期間内にマルチプレクス信号およびデジタル映像信号が入力され、前記第3～第5のトランジスタが導通し、前記保持回路の信号入力部における電位が第2の電源電位に変化し、

以後、次の帰線期間までの間、前記保持部において第2の電源電位が保持されることを特徴としている。

50

## 【0028】

本発明の表示装置の駆動回路は、

入力されたデジタル映像信号の保持を行う保持回路と、

N A N D 回路と、

アナログスイッチとを有し、

前記 N A N D 回路には、サンプリングパルスと、マルチプレクス信号とが入力され、

前記保持回路には、デジタル映像信号が前記アナログスイッチを介して入力され、

前記アナログスイッチは、前記 N A N D 回路の出力によって導通、非導通の制御がなされ、

前記アナログスイッチの導通に伴い、前記保持回路への映像信号の書き込みが行われ、

以後、次の帰線期間までの間、前記保持回路において映像信号が保持されることを特徴としている。

10

## 【0029】

本発明の表示装置の駆動回路は、

請求項 1 乃至請求項 9 のいずれか 1 項に記載の表示装置の駆動回路において、前記マルチプレクス信号および前記デジタル映像信号は、共に外部からの直接入力によるこことを特徴としている。

## 【0030】

本発明の表示装置の駆動回路は、

請求項 1 乃至請求項 10 のいずれか 1 項に記載の表示装置の駆動回路において、

前記デジタル映像信号のパルス幅と、前記マルチプレクス信号のパルス幅は、いずれも前記サンプリングパルスのパルス幅よりも小さいことを特徴としている。

20

## 【0031】

本発明の表示装置の駆動回路は、

請求項 1 乃至請求項 11 のいずれか 1 項に記載の表示装置の駆動回路において、

前記保持回路における電位の保持は、ループ状に設けられた 2 個のインバータによる保持回路によってなされることを特徴としている。

## 【0032】

本発明の表示装置の駆動回路は、

請求項 1 乃至請求項 11 のいずれか 1 項に記載の表示装置の駆動回路において、

前記保持回路における電位の保持は、保持容量によってなされることを特徴としている。

30

## 【0033】

の本発明の表示装置の駆動回路によると、

請求項 1 乃至請求項 13 のいずれか 1 項に記載の表示装置の駆動回路を用いることを特徴とする表示装置の提供が可能となる。

## 【0034】

## 【発明の実施の形態】

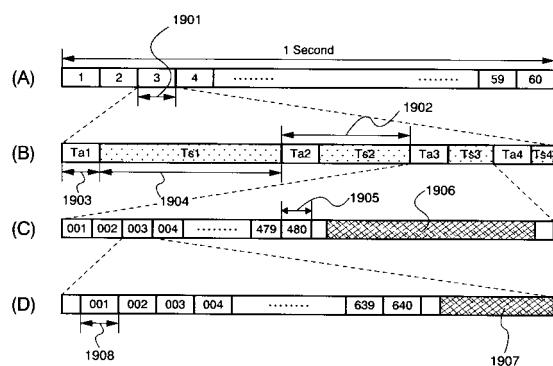

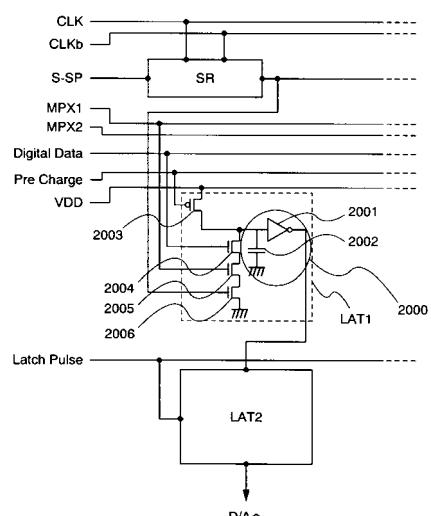

## [実施の形態 1]

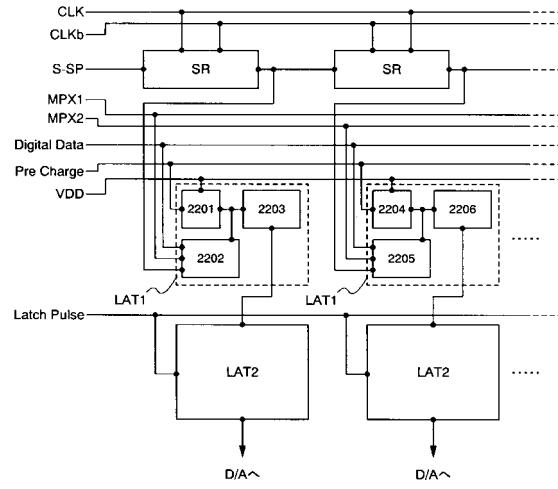

図 22 に、本発明の一実施形態を示す。図 22 は、図 12 において、シフトレジスタ ( S R ) ~ 第 1 のラッチ回路 ( L A T 1 ) ~ 第 2 のラッチ回路 ( L A T 2 ) に相当する部分を、2 段分書き表したものである。第 1 段目における第 1 のラッチ回路 ( L A T 1 ) は、プリチャージ回路 2201 、保持動作選択回路 2202 、保持回路 2203 を有し、保持回路 2203 の出力は、第 2 のラッチ回路 ( L A T 2 ) に入力される。第 1 段目における第 1 のラッチ回路 ( L A T 1 ) は、プリチャージ回路 2204 、保持動作選択回路 2205 、保持回路 2206 を有し、保持回路 2206 の出力は、同様に第 2 のラッチ回路 ( L A T 2 ) に入力される。

40

## 【0035】

回路の動作について説明する。ここで、第 1 の電源の電位は V D D , 第 2 の電源の電位は V S S とする。まず、ある帰線期間中に、プリチャージ信号が入力されることによって、プリチャージ回路 2201 および 2204 が動作し、保持回路 2203 および 2206 の

50

信号入力部の電位をVDDとする。続いて帰線期間が終了し、1段目のシフトレジスタよりサンプリングパルスが outputされ、保持動作選択回路2202に入力される。また、保持動作選択回路2202には、さらにマルチプレクス信号1(MPX1)およびデジタル映像信号(Digital Data)も入力される。

#### 【0036】

保持動作選択回路では、サンプリングパルス、マルチプレクス信号、デジタル映像信号が全て入力されている期間において、保持回路2203にデジタル映像信号の書き込みを許可する。保持回路2203においては、ここで書き込まれたデジタル映像信号を、水平期間が終了するまで保持する。

10

#### 【0037】

次に、2段目において同様の処理が行われる。このとき、保持動作選択回路には、サンプリングパルス、マルチプレクス信号2(MPX2)、デジタル映像信号(Digital Data)が入力される。つまり、第1段目、第3段目、第5段目・・・、第(2m-1)段目においてはマルチプレクス信号1(MPX1)を用い、第2段目、第4段目、第6段目・・・、第(2m)段目においてはマルチプレクス信号2(MPX2)を用いる。

#### 【0038】

続いて、帰線期間中にラッチ信号(Latch Pulse)が入力され、第1のラッチ回路の保持部2203、2206で保持されていた信号は、一斉に第2のラッチ回路へと転送される。以降、D/A変換、画素への書き込み等の動作は、従来例に記述したとおりの動作による。

20

#### 【0039】

##### [実施の形態2]

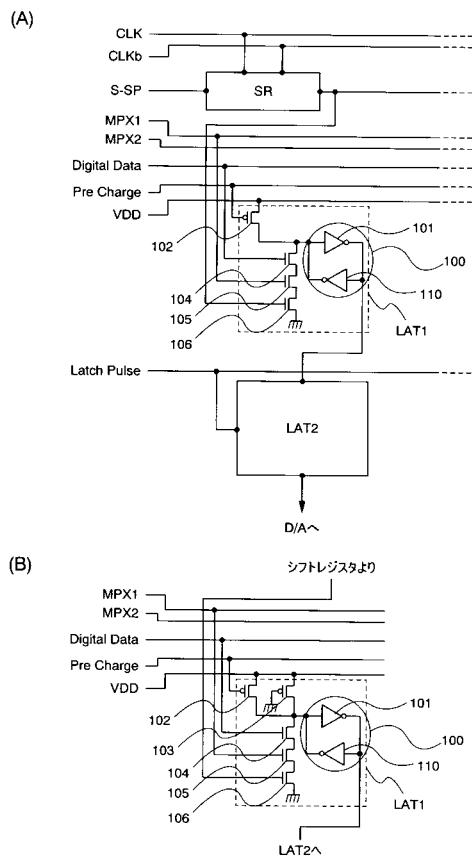

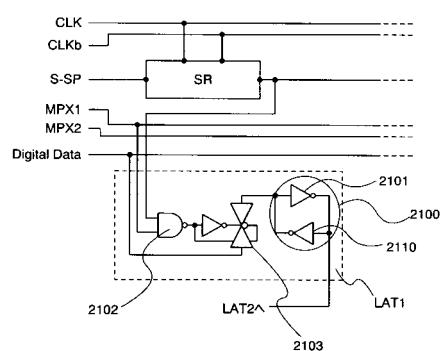

実施の形態1にて示した回路において、プリチャージ回路2201、保持動作選択回路2202、保持回路2203の詳細な構成を含む図を図1に示す。図1ではシフトレジスタ～第1のラッチ回路～第2のラッチ回路に相当する1段分のみを示している。

#### 【0040】

図1(A)(B)に示す回路は、映像信号保持部100、プリチャージ用の第1のTFT102(以降、プリチャージTFTと表記する。)、第2のTFT104、第3のTFT105、第4のTFT106を有している。図1(A)では、第1のTFTにはPチャネル型を用い、第2～第4のTFTにはNチャネル型を用いている。ここで、TFT102が図22におけるプリチャージ回路2201に相当し、TFT104、105、106を用いてなる回路が図22における保持動作選択回路2202に相当する。

30

#### 【0041】

保持回路100は、2個のインバータを用いて構成される。101は駆動用インバータ、110は保持用インバータであり、両者がループを形成するように接続されている。駆動用インバータ101への入力が不定となる場合でも、保持用インバータ110の出力によって、駆動用インバータ101の出力が確定される。

#### 【0042】

TFT102のソース領域は第1の電源電位(ここではVDD)に接続され、ドレイン領域は保持部100の入力端子に接続されている。TFT104～106は、第2の電源電位(ここではGND)と、保持部100の入力端子との間に直列配置され、それぞれのゲート電極には、マルチプレクス信号(MPX1、MPX2)、デジタル映像信号(Digital Data)およびサンプリングパルスがそれぞれ入力される。プリチャージTFT102のゲート電極には、プリチャージ用信号(Pre Charge)が入力される。

40

#### 【0043】

図1(A)に示した第1のラッチ回路の動作について説明する。なお、ここで用いる電位は、信号の振幅に合わせて、高電位側(Hi電位と表記する)をVDD、低電位側(Lo電位と表記する)をGNDとする。また、特別の記述のない限り、デジタル映像信号、サ

50

ンプリングパルスおよびマルチプレクス信号に関しては、H i電位(V D D)の時に信号の入力があったものと解釈されたい。

【0044】

まず、ある帰線期間中に、プリチャージ信号にL oを入力する。これによってプリチャージT F T 1 0 2が導通し、保持部1 0 0の入力端子における電位がH i電位(V D D)に引き上げられる。その後、水平期間に入る時にプリチャージ信号はH iとなり、プリチャージT F T 1 0 2は非導通状態に戻る。

【0045】

次に、水平期間に入つてからの動作の説明に移る。シフトレジスタ回路が動作し、サンプリングパルスが出力されて、Nチャネル型T F T 1 0 6のゲート電極にH iが入力される。このパルスがH i状態となっている期間内に、マルチプレクス信号(M P X 1)、デジタル映像信号(D i g i t a l D a t a)が、Nチャネル型T F T 1 0 4、1 0 5のゲート電極にそれぞれ入力される。シフトレジスタからの出力パルス、マルチプレクス信号、デジタル映像信号の3信号が全てH iのとき、Nチャネル型T F T 1 0 4～1 0 6が全て導通し、保持部1 0 0の入力端子にL o電位(G N D)が入力される。一度L o電位(G N D)になると、Nチャネル型T F T 1 0 4～1 0 6間が非導通状態に戻った後も、次の帰線期間の開始まで、保持部1 0 0によって保持される。

【0046】

このとき、保持部1 0 0の入力端子におけるH i電位は、デジタル映像信号の保持動作が行われるまでの間はそのまま保持されている必要がある。よって、図1(B)に示すように、定電流供給用のT F T 1 0 3を追加して、電位の保持を保障しても良い。定電流T F T 1 0 3には、ここではPチャネル型を用い、ゲート電極には常にL o(G N D)が入力されているようにしている。ただし、デジタル映像信号の保持を阻害しないよう、定電流T F T 1 0 3の電流能力が、保持部1 0 0を構成するT F Tの電流能力に対して十分に小さくなるように設計することが望ましい。

【0047】

続いて、帰線期間中にラッチ信号(L a t c h P u l s e)が入力され、第1のラッチ回路の保持部1 0 0で保持されていた信号は、一齊に第2のラッチ回路へと転送される。以降、D / A変換、画素への書き込み等の動作は、従来例に記述したとおりの動作による。

【0048】

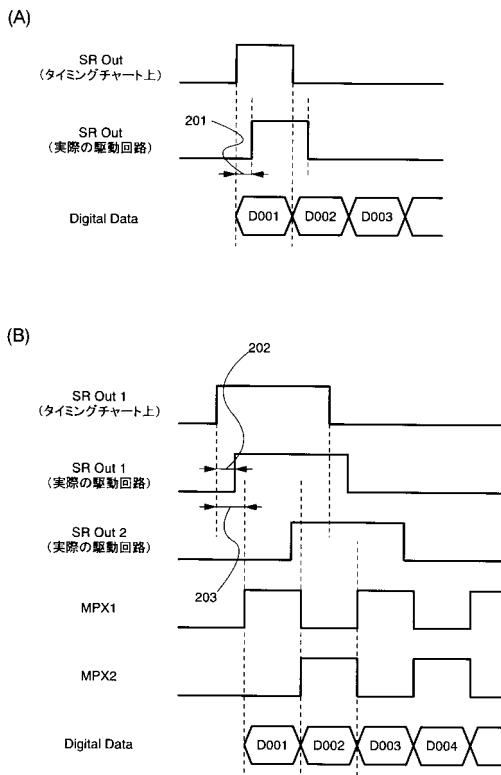

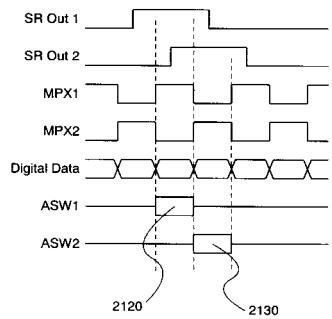

図2(B)に、本発明の駆動回路によるシフトレジスタ回路の動作と、デジタル映像信号の入力および保持動作のタイミングについて示す。本発明のラッチ回路においては、シフトレジスタ回路の駆動周波数を、図2(A)に示した従来の回路に対して1/2とし、パルス幅を2倍に広げている。S R O u t 1と表記してあるパルスは、例えば1段目のシフトレジスタ回路から出力されるサンプリングパルスであり、S R O u t 2と表記してあるパルスは、次段のシフトレジスタ回路から出力されるサンプリングパルスである。実際のサンプリングパルスは、タイミングチャート上のサンプリングパルスに対し、2 0 2で示すような遅延を生ずる。

【0049】

ここで、従来例においては、第1のラッチ回路における保持動作のタイミングが、サンプリングパルスのタイミングに依存していたため、図2(A)で示すように、遅延が起こると正常にデジタル映像信号の保持を行うことができなくなっていた。したがって、その都度、デジタル映像信号の入力のタイミングの微調整が必要となっていた。

【0050】

これに対し、前述の動作の説明および図2からわかるように、本発明のラッチ回路における保持動作のタイミングは、サンプリングパルス(S R O u t #)、マルチプレクス信号(M P X #)およびデジタル映像信号(D i g i t a l D a t a)の3信号により決定される。そして、サンプリングパルスを除く他の信号は、全て外部からの直接入力であるため、ラッチ回路における事実上の保持動作のタイミングは、このマルチプレクス信号

10

20

30

40

50

とデジタル映像信号との入力タイミングにより決定されるといえる。すなわち、サンプリングパルスの出力に少々の遅延が生じた場合にも、保持動作のタイミングは変化しない(図2(B)の場合、遅延は203で示す長さだけ許される)。

#### 【0051】

また、外部から入力されるマルチプレクス信号とデジタル映像信号に関しては容易にタイミングを揃えることが出来るため、従来のラッチ回路と比較しても大幅に調整が容易になつている。

#### 【0052】

この実施形態において、図1に示した本発明のラッチ回路の構成について、各部を構成するTFT102～106の極性は、サンプリングパルス、プリチャージ信号、デジタル映像信号およびマルチプレクス信号等の正負(各パルスがHi電位で出力されるか、Lo電位で出力されるか)により、本例とは異なる極性のTFTであっても、動作原理は変わらない。

10

#### 【0053】

このようなラッチ回路を用いることにより、従来のラッチ回路周辺で問題となっていた、回路から出力される信号の遅延によるタイミングの微調整を必要としない駆動回路を提供することが出来る。加えて、シフトレジスタ回路の駆動周波数は1/2となっているため、信頼性の向上も期待出来る。

#### 【0054】

さらに、第1のラッチ回路に入力される信号(デジタル映像信号、マルチプレクス信号、サンプリングパルス)に関しては、TFT104～106が確実に導通するだけの電圧振幅を有していれば良い。よって、ラッチ回路に接続されている電源であるVDD-GND間の電圧よりも小さい電圧振幅であっても、前述の条件を満足する限りは十分に正常動作が可能であるので、入力信号の振幅を縮小することによる低消費電力化が見込める。

20

#### 【0055】

また、本発明のラッチ回路を有する駆動回路は、デジタル映像信号を扱う表示装置であれば、画素部に液晶素子を用いた液晶表示装置(LCD:液晶ディスプレイ等)、エレクトロルミネッセンス(EL)素子を用いたEL表示装置(OLED:有機ELディスプレイ等)等の表示装置に適用が可能である。

#### 【0056】

30

#### 【実施例】

本発明の主旨は、デジタル映像信号の保持のタイミングが、サンプリングパルスの遅延に依存せず、かつ保持のタイミングを容易に外部から制御可能な表示装置の駆動回路を提供する点にある。実施形態に示した一例に限らず、本発明には多種の応用例が挙げられる。以下にその実施例について記す。

#### 【0057】

##### [実施例1]

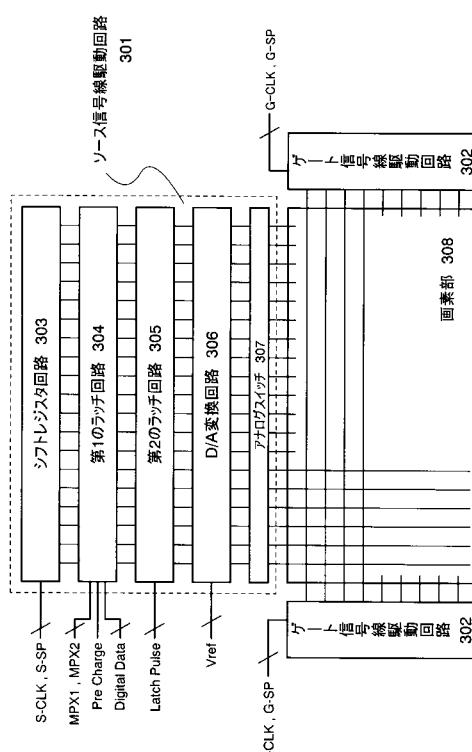

図3に、本発明のラッチ回路を有する駆動回路を用いた表示装置の概略図を示す。中央に画素部308が配置されている。画素部の上側には、ソース信号線を制御するための、ソース信号線駆動回路301が配置されている。ソース信号線駆動回路301は、第1のラッチ回路304、第2のラッチ回路305、D/A変換回路306、アナログスイッチ307等を有する。第1のラッチ回路304は、図1で示したような構造を有している。他の構成部分に関しては、従来例と同様で良い。画素部の左右には、ゲート信号線を制御するための、ゲート信号線駆動回路302が配置されている。なお、図3においては、ゲート信号線駆動回路302は、画素部の左右両側に配置されているが、片側配置でも構わない。ただし、両側配置とした方が、駆動効率、駆動信頼性の面から見て望ましい。

40

#### 【0058】

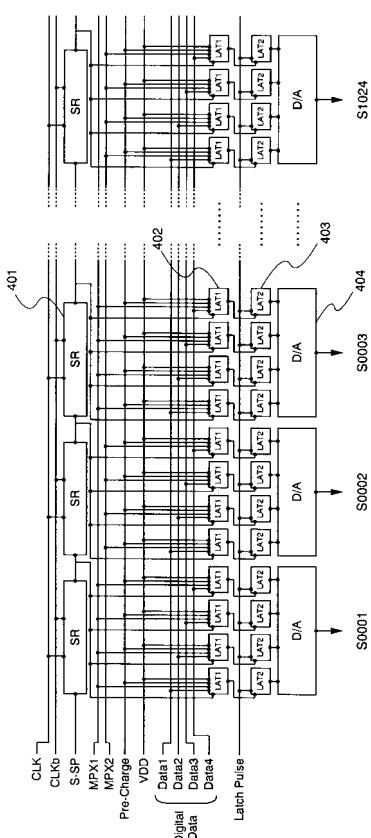

ソース信号線駆動回路301に関しては、図4に示すような構成を有している。この駆動回路は、水平方向解像度1024画素、4ビット階調表示能力を有する表示装置のソース信号線駆動回路であり、シフトレジスタ回路401(SR)、第1のラッチ回路402(

50

L A T 1 )、第 2 のラッチ回路 4 0 3 ( L A T 2 )、D / A 変換回路 4 0 4 ( D / A )等を有する。なお、図 4 では、図 3 におけるアナログスイッチ 3 0 7 は図示していない。また、必要に応じて、バッファ回路あるいはレベルシフタ回路等を追加配置しても良い。

【 0 0 5 9 】

第 1 のラッチ回路 4 0 2 には、サンプリングパルスの他に、プリチャージ信号 ( P r e C h a r g e )、マルチプレクス信号 ( M P X 1 、 M P X 2 )、デジタル映像信号 ( D i g i t a l D a t a ) 等が入力される。また、図 4 中、 V D D と表記してある配線は信号線ではなく、第 1 のラッチ回路の電位を帰線期間中に H i に引き上げるために供給される電源線である。

【 0 0 6 0 】

マルチプレクス信号 ( M P X 1 、 M P X 2 ) は、奇数段目の第 1 のラッチ回路 ( 図 4 において、ソース信号線 S <sub>0001</sub> 、 S <sub>0003</sub> 、 … S <sub>2n-1</sub> に書き込まれる映像信号の保持を行う第 1 のラッチ回路 ) の保持タイミングの決定には M P X 1 に入力される信号を用い、偶数段目の第 1 のラッチ回路 ( 図 4 において、ソース信号線 S <sub>0002</sub> 、 S <sub>0004</sub> 、 … S <sub>2n</sub> に書き込まれる映像信号の保持を行う第 1 のラッチ回路 ) の保持タイミングの決定には M P X 2 に入力される信号を用いることで、互いに隣接したパルスの重なり合いが生じないよう 10 にしている。

【 0 0 6 1 】

[ 実施例 2 ]

図 1 に示した本発明の駆動回路においては、保持部 1 0 0 は駆動用インバータ 1 0 1 と、保持用インバータ 1 1 0 とを用いてループを形成し、保持用インバータ 1 1 0 を用いて信号の保持を行っていた。この他の方法として、図 2 0 に示すような構成であっても同様の機能を実現することが出来る。 20

【 0 0 6 2 】

図 2 0 に示すラッチ回路の保持部 2 0 0 0 は、駆動用インバータ 2 0 0 1 と、容量 2 0 0 2 によって構成される。帰線期間中にプリチャージ T F T 2 0 0 3 によって、保持部 2 0 0 0 への入力端子における電位が H i 電位 ( V D D ) に引き上げられたとき、もしくはサンプリングパルス、デジタル映像信号、マルチプレクス信号の入力によって保持部 2 0 0 0 に L o 電位 ( G N D ) が入力されて映像信号が保持されるとき、いずれの場合も、容量 2 0 0 2 が電荷の保持をまかぬ。 30

【 0 0 6 3 】

回路の駆動、信号の入力に関しては図 1 に示した回路と同様で良い。

【 0 0 6 4 】

[ 実施例 3 ]

本実施例においては、帰線期間におけるプリチャージ動作を省略した場合の回路の構成とその動作について説明する。

【 0 0 6 5 】

図 2 1 に、回路の構成図とタイミングチャートを示す。図 2 1 ( A ) に示すように、本実施例のラッチ回路は、保持部 2 1 0 0 と、 N A N D 回路 2 1 0 2 と、アナログスイッチ 2 1 0 3 とを有する。 N A N D 回路 2 1 0 2 には、サンプリングパルスおよびマルチプレクス信号が入力され、 2 信号にともに H i 電位 ( V D D ) の入力があったときに、 L o 電位 ( G N D ) を出力する。 N A N D 出力によって、アナログスイッチ 2 1 0 3 の導通、非導通が決定される。すなわち、サンプリングパルスとマルチプレクス信号がともに H i 入力のとき、アナログスイッチ 2 1 0 3 が導通し、デジタル映像信号が保持部 2 1 0 0 の駆動用インバータ 2 1 0 1 に入力される。以後、アナログスイッチが非導通状態となると、デジタル映像信号は、ループ状に接続された保持用インバータ 2 1 1 0 によって、次の帰線期間までの間保持される。 40

【 0 0 6 6 】

マルチプレクス信号 ( M P X 1 、 M P X 2 ) は、奇数段目の第 1 のラッチ回路 ( 図 4 において、ソース信号線 S <sub>0001</sub> 、 S <sub>0003</sub> 、 … S <sub>2n-1</sub> に書き込まれる映像信号の保持を行う 50

第1のラッチ回路)の保持タイミングの決定にはMPX1に入力される信号を用い、偶数段目の第1のラッチ回路(図4において、ソース信号線S<sub>0002</sub>、S<sub>0004</sub>、…S<sub>2n</sub>に書き込まれる映像信号の保持を行う第1のラッチ回路)の保持タイミングの決定にはMPX2に入力される信号を用いることで、図21(B)において、2120、2130で示すように、隣接したアナログスイッチ2103の導通タイミングが同時期に重複しないようにしている。

【0067】

また、保持部2100に関しては、実施例2にて示したように、保持用インバータ2110に替えて、保持容量を用いて構成しても良い。

【0068】

各信号の入力のタイミングは他の実施例と同様で良い。この方法により、帰線期間におけるプリチャージ動作を行わずとも、本発明による同様の利点を有するラッチ回路を提供することが出来る。

【0069】

[実施例4]

本実施例では、表示装置の画素部とその周辺に設けられる本発明の駆動回路部(ソース信号線側駆動回路、ゲート信号線側駆動回路、画素選択信号線側駆動回路)のTFTを同時に作製する方法について説明する。但し、説明を簡単にするために、駆動回路部に関しては基本単位であるCMOS回路を図示することとする。

【0070】

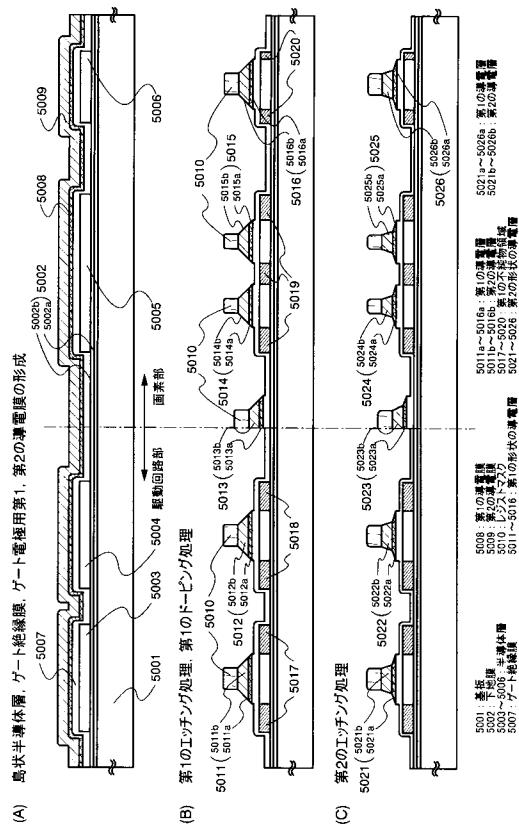

まず、図5(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスから成る基板5001上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜5002を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜5002aを10～200[nm](好ましくは50～100[nm])形成し、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜5002bを50～200[nm](好ましくは100～150[nm])の厚さに積層形成する。本実施例では下地膜5002を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

【0071】

島状半導体層5003～5006は、非晶質構造を有する半導体膜をレーザー結晶化法や公知の熱結晶化法を用いて作製した結晶質半導体膜で形成する。この島状半導体層5003～5006の厚さは25～80[nm](好ましくは30～60[nm])の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

【0072】

レーザー結晶化法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30[Hz]とし、レーザーエネルギー密度を100～400[mJ/cm<sup>2</sup>](代表的には200～300[mJ/cm<sup>2</sup>])とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数1～10[kHz]とし、レーザーエネルギー密度を300～600[mJ/cm<sup>2</sup>](代表的には350～500[mJ/cm<sup>2</sup>])とすると良い。そして幅100～1000[μm]、例えば400[μm]で線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を80～98[%]として行う。

【0073】

次いで、島状半導体層5003～5006を覆うゲート絶縁膜5007を形成する。ゲート絶縁膜5007はプラズマCVD法またはスパッタ法を用い、厚さを40～150[nm]

10

20

30

40

50

としてシリコンを含む絶縁膜で形成する。本実施例では、120 [nm]の厚さで酸化窒化シリコン膜で形成する。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS (Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40 [Pa]、基板温度300～400 [°C]とし、高周波(13.56 [MHz])、電力密度0.5～0.8 [W/cm<sup>2</sup>]で放電させて形成することが出来る。このようにして作製される酸化シリコン膜は、その後400～500 [°C]の熱アーニールによりゲート絶縁膜として良好な特性を得ることが出来る。

#### 【0074】

そして、ゲート絶縁膜5007上にゲート電極を形成するための第1の導電膜5008と第2の導電膜5009とを形成する。本実施例では、第1の導電膜5008をTaで50～100 [nm]の厚さに形成し、第2の導電膜5009をWで100～300 [nm]の厚さに形成する。

10

#### 【0075】

Ta膜はスパッタ法で、TaのターゲットをArでスパッタすることにより形成する。この場合、Arに適量のXeやKrを加えると、Ta膜の内部応力を緩和して膜の剥離を防止することが出来る。また、Ta相のTa膜の抵抗率は20 [μΩ cm]程度でありゲート電極に使用することが出来るが、W相のTa膜の抵抗率は180 [μΩ cm]程度でありゲート電極とするには不向きである。よって、W相のTa膜を形成するために、TaのW相に近い結晶構造をもつ窒化タンタルを10～50 [nm]程度の厚さでTaの下地に形成しておくと相のTa膜を容易に得ることが出来る。

20

#### 【0076】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することも出来る。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20 [μΩ cm]以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることが出来るが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999 [%]のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9～20 [μΩ cm]を実現することが出来る。

30

#### 【0077】

なお、本実施例では、第1の導電膜5008をTa、第2の導電膜5009をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cuなどから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。本実施例以外の他の組み合わせの一例で望ましいものとしては、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をWとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をAlとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をCuとする組み合わせ等が挙げられる。

40

#### 【0078】

次に、レジストによるマスク5010を形成し、電極及び配線を形成するための第1のエッチング処理を行う。本実施例ではICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を行い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、1 [Pa]の圧力でコイル型の電極に500 [W]のRF(13.56 [MHz])電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100 [W]のRF(13.56 [MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはW膜及びTa膜とも同程度にエッチングされる。

#### 【0079】

上記エッチング条件では、レジストによるマスクの形状を適したものとすることにより、

50

基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。テーパー部の角度は15～45°となる。ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10～20[%]程度の割合でエッティング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2～4（代表的には3）であるので、オーバーエッティング処理により、酸化窒化シリコン膜が露出した面は20～50[nm]程度エッティングされることになる。こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5011～5016（第1の導電層5011a～5016aと第2の導電層5011b～5016b）を形成する。このとき、ゲート絶縁膜5007においては、第1の形状の導電層5011～5016で覆われない領域は20～50[nm]程度エッティングされ薄くなった領域が形成される。

（図5（A））

#### 【0080】

そして、第1のドーピング処理を行いN型を付与する不純物元素を添加する。ドーピングの方法はイオンドープ法もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14} [\text{atoms/cm}^2]$ とし、加速電圧を60～100[keV]として行う。N型を付与する不純物元素として15族に属する元素、典型的にはリン（P）または砒素（As）を用いるが、ここではリン（P）を用いる。この場合、導電層5011～5016がN型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域5017～5020が形成される。第1の不純物領域5017～5020には $1 \times 10^{20} \sim 1 \times 10^{21} [\text{atoms/cm}^3]$ の濃度範囲でN型を付与する不純物元素を添加する。（図5（B））

#### 【0081】

次に、図5（C）に示すように、レジストマスクは除去しないまま、第2のエッティング処理を行う。エッティングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、W膜を選択的にエッティングする。この時、第2のエッティング処理により第2の形状の導電層5021～5026（第1の導電層5021a～5026aと第2の導電層5021b～5026b）を形成する。このとき、ゲート絶縁膜5007においては、第2の形状の導電層5021～5026で覆われない領域はさらに20～50[nm]程度エッティングされ薄くなった領域が形成される。

#### 【0082】

W膜やTa膜のCF<sub>4</sub>とCl<sub>2</sub>の混合ガスによるエッティング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することが出来る。WとTaのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF<sub>6</sub>が極端に高く、その他のWC<sub>1.5</sub>、TaF<sub>5</sub>、TaC<sub>1.5</sub>は同程度である。従って、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスではW膜及びTa膜共にエッティングされる。しかし、この混合ガスに適量のO<sub>2</sub>を添加するとCF<sub>4</sub>とO<sub>2</sub>が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッティング速度が増大する。一方、TaはFが増大しても相対的にエッティング速度の増加は少ない。また、TaはWに比較して酸化されやすいので、O<sub>2</sub>を添加することでTaの表面が酸化される。Taの酸化物はフッ素や塩素と反応しないためさらにTa膜のエッティング速度は低下する。従って、W膜とTa膜とのエッティング速度に差を作ることが可能となりW膜のエッティング速度をTa膜よりも大きくすることが可能となる。

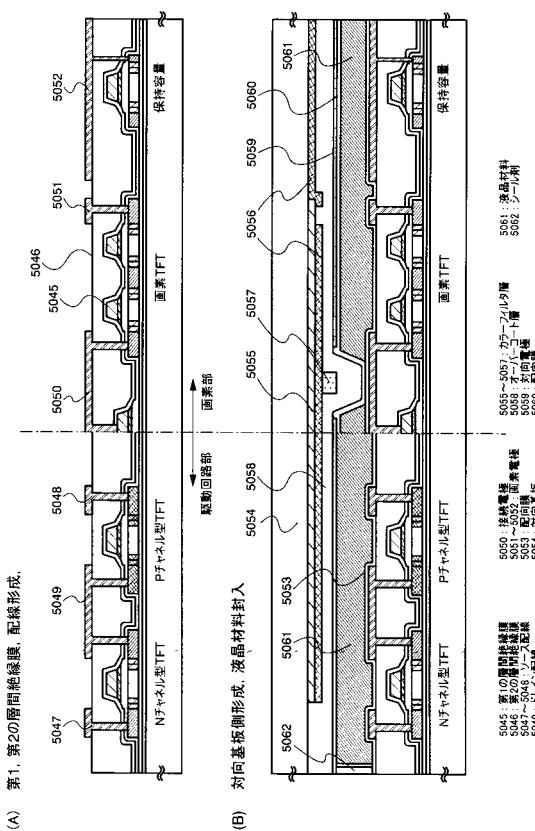

#### 【0083】

そして、図6（A）に示すように第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げる高い加速電圧の条件としてN型を付与する不純物元素をドーピングする。例えば、加速電圧を70～120[keV]とし、 $1 \times 10^{13} [\text{atoms/cm}^2]$ のドーズ量で行い、図5（B）で島状半導体層に形成された第1の不純物領域の内側に新たな不純物領域を形成する。ドーピングは、第2の形状の導電層5021～5026を不純物元素に対するマスクとして用い、第1の導電層5021a～5026aの下側の領域の半導体層にも不純物元素が添加されるようにドーピングする。こうして、第2の不純物領

10

20

30

40

50

域 5 0 2 7 ~ 5 0 3 1 が形成される。この第 2 の不純物領域 5 0 2 7 ~ 5 0 3 1 に添加されたリン (P) の濃度は、第 1 の導電層 5 0 2 1 a ~ 5 0 2 6 a のテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第 1 の導電層 5 0 2 1 a ~ 5 0 2 6 a のテーパー部と重なる半導体層において、第 1 の導電層 5 0 2 1 a ~ 5 0 2 6 a のテーパー部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。

#### 【 0 0 8 4 】

続いて、図 6 (B) に示すように第 3 のエッティング処理を行う。エッティングガスに C H F<sub>6</sub> を用い、反応性イオンエッティング法 (RIE 法) を用いて行う。第 3 のエッティング処理により、第 1 の導電層 5 0 2 1 a ~ 5 0 2 6 a のテーパー部を部分的にエッティングして、第 1 の導電層が半導体層と重なる領域が縮小される。第 3 のエッティング処理によって、第 3 の形状の導電層 5 0 3 2 ~ 5 0 3 7 (第 1 の導電層 5 0 3 2 a ~ 5 0 3 7 a と第 2 の導電層 5 0 3 2 b ~ 5 0 3 7 b) を形成する。このとき、ゲート絶縁膜 5 0 0 7 においては、第 3 の形状の導電層 5 0 3 2 ~ 5 0 3 7 で覆われない領域はさらに 2 0 ~ 5 0 [nm] 程度エッティングされ薄くなった領域が形成される。

#### 【 0 0 8 5 】

第 3 のエッティング処理によって、第 2 の不純物領域 5 0 2 7 ~ 5 0 3 1 においては、第 1 の導電層 5 0 3 2 a ~ 5 0 3 7 a と重なる第 2 の不純物領域 5 0 2 7 a ~ 5 0 3 1 a と、第 1 の不純物領域と第 2 の不純物領域との間の第 3 の不純物領域 5 0 2 7 b ~ 5 0 3 1 b とが形成される。

#### 【 0 0 8 6 】

そして、図 6 (C) に示すように、P チャネル型 TFT を形成する島状半導体層 5 0 0 4 に、第 1 の導電型とは逆の導電型の第 4 の不純物領域 5 0 3 9 ~ 5 0 4 4 を形成する。第 3 の形状の導電層 5 0 3 3 b を不純物元素に対するマスクとして用い、自己整合的に不純物領域を形成する。このとき、N チャネル型 TFT を形成する島状半導体層 5 0 0 3 、 5 0 0 5 、保持容量部 5 0 0 6 および配線部 5 0 3 4 はレジストマスク 5 0 3 8 で全面を被覆しておく。不純物領域 5 0 3 9 ~ 5 0 4 4 にはそれぞれ異なる濃度でリンが添加されているが、ジボラン (B<sub>2</sub>H<sub>6</sub>) を用いたイオンドープ法で形成し、そのいずれの領域においても不純物濃度が  $2 \times 10^{20} \sim 2 \times 10^{21}$  [atoms/cm<sup>3</sup>] となるようにする。

#### 【 0 0 8 7 】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。島状半導体層と重なる第 3 の形状の導電層 5 0 3 2 、 5 0 3 3 、 5 0 3 5 、 5 0 3 6 がゲート電極として機能する。また、5 0 3 4 は島状のソース信号線として機能する。5 0 3 7 は容量配線として機能する。

#### 【 0 0 8 8 】

レジストマスク 5 0 3 8 を除去した後、導電型の制御を目的として、それぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーハニール法、またはラピッドサーマルアニール法 (RTA 法) を適用することが出来る。熱アニール法では酸素濃度が 1 [ppm] 以下、好ましくは 0.1 [ppm] 以下の窒素雰囲気中で 400 ~ 700 [ ]、代表的には 500 ~ 600 [ ] で行うものであり、本実施例では 500 [ ] で 4 時間の熱処理を行う。ただし、第 3 の形状の導電層 5 0 3 7 ~ 5 0 4 2 に用いた配線材料が熱に弱い場合には、配線等を保護するため層間絶縁膜 (シリコンを主成分とする) を形成した後で活性化を行うことが好ましい。

#### 【 0 0 8 9 】

さらに、3 ~ 100 [%] の水素を含む雰囲気中で、300 ~ 450 [ ] で 1 ~ 12 時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化 (プラズマにより励起された水素を用いる) を行っても良い。

#### 【 0 0 9 0 】

10

20

30

40

50

次いで、第1の層間絶縁膜5045は酸化窒化シリコン膜から100～200[nm]の厚さで形成する。その上に有機絶縁物材料から成る第2の層間絶縁膜5046を形成する。次いで、コンタクトホールを形成するためのエッチング工程を行う。

【0091】

そして、駆動回路部において島状半導体層のソース領域とコンタクトを形成するソース配線5047、5048、ドレイン領域とコンタクトを形成するドレイン配線5049を形成する。また、画素部においては、接続電極5050、画素電極5051、5052を形成する(図7(A))。この接続電極5050により、ソース信号線5034は、画素TFTと電気的な接続が形成される。なお、画素電極5052及び保持容量は隣り合う画素のものである。

10

【0092】

以上のようにして、Nチャネル型TFT、Pチャネル型TFTを有する駆動回路部と、画素TFT、保持容量を有する画素部とを同一基板上に形成することができる。本明細書中ではこのような基板をアクティブマトリクス基板と呼ぶ。

【0093】

本実施例は、ブラックマトリクスを用いることなく、画素電極間の隙間を遮光することができるよう、画素電極の端部を信号線や走査線と重なるように配置されている。

【0094】

また、本実施例で示す工程に従えば、アクティブマトリクス基板の作製に必要なフォトマスクの数を5枚(島状半導体層パターン、第1配線パターン(走査線、信号線、容量配線)、Pチャネル領域のマスクパターン、コンタクトホールパターン、第2配線パターン(画素電極、接続電極含む))とすることができます。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することができる。

20

【0095】

続いて、図7(B)の状態のアクティブマトリクス基板を得た後、アクティブマトリクス基板上に配向膜5053を形成しラビング処理を行う。

【0096】

一方、対向基板5054を用意する。対向基板5054にはカラーフィルタ層5055～5057、オーバーコート層5058を形成する。カラーフィルタ層はTFTの上方で赤色のカラーフィルタ層5055と青色のカラーフィルタ層5056とを重ねて形成し遮光膜を兼ねる構成とする。少なくともTFTと、接続電極と画素電極との間を遮光する必要があるため、それらの位置を遮光するように赤色のカラーフィルタと青色のカラーフィルタを重ねて配置することが好ましい。

30

【0097】

また、接続電極5050に合わせて赤色のカラーフィルタ層5055、青色のカラーフィルタ層5056、緑色のカラーフィルタ層5057とを重ね合わせてスペーサーを形成する。各色のカラーフィルタはアクリル樹脂に顔料を混合したもので1～3[μm]の厚さで形成する。これは感光性材料を用い、マスクを用いて所定のパターンに形成することができる。スペーサーの高さはオーバーコート層5058の厚さ1～4[μm]を考慮することにより2～7[μm]、好ましくは4～6[μm]とすることができ、この高さによりアクティブマトリクス基板と対向基板とを貼り合わせた時のギャップを形成する。オーバーコート層5058は光硬化型または熱硬化型の有機樹脂材料で形成し、例えば、ポリイミドやアクリル樹脂などを用いる。

40

【0098】

スペーサーの配置は任意に決定すれば良いが、例えば図7(B)で示すように接続電極上に位置が合うように対向基板5054上に配置すると良い。また、駆動回路部のTFT上にその位置を合わせてスペーサーを対向基板5054上に配置してもよい。このスペーサーは駆動回路部の全面に渡って配置しても良いし、ソース配線およびドレイン配線を覆うようにして配置しても良い。

【0099】

50

オーバーコート層 5058 を形成した後、対向電極 5059 をパターニング形成し、配向膜 5060 を形成した後ラビング処理を行う。

【0100】

そして、画素部と駆動回路部が形成されたアクティブマトリクス基板と対向基板とをシール剤 5062 で貼り合わせる。シール剤 5062 にはフィラーが混入されていて、このフィラーとスペーサーによって均一な間隔を持って 2 枚の基板が貼り合わせられる。その後、両基板の間に液晶材料 5061 を注入し、封止剤（図示せず）によって完全に封止する。液晶材料 5061 には公知の液晶材料を用いれば良い。このようにして図 7 (B) に示すアクティブマトリクス型液晶表示装置が完成する。

【0101】

なお、上記の行程により作成される TFT はトップゲート構造であるが、ボトムゲート構造の TFT やその他の構造の TFT に対しても本実施例は容易に適用され得る。

【0102】

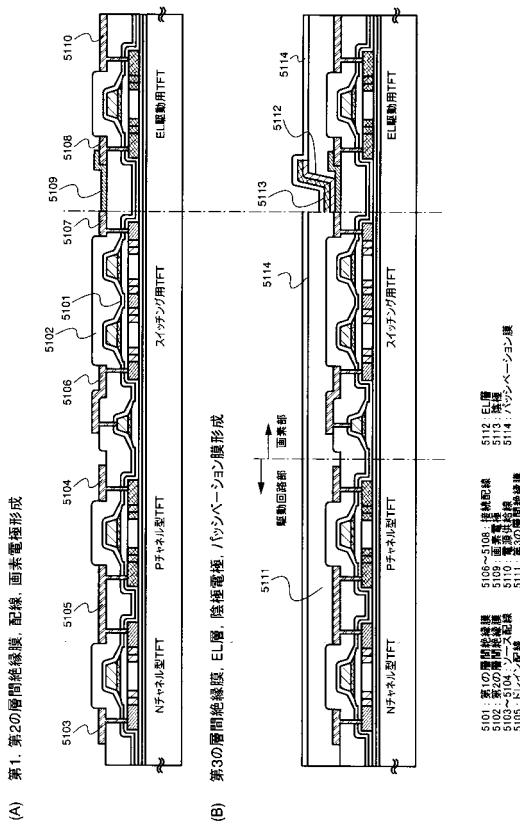

[実施例 5]

本実施例では、本発明のラッチ回路を有する駆動回路を、EL 素子を画素部に用いた EL 表示装置に適用し、その EL 表示装置を絶縁体上に一体形成する方法について説明する。但し、説明を簡単にするために、駆動回路部に関しては基本単位である CMOS 回路を図示することとする。

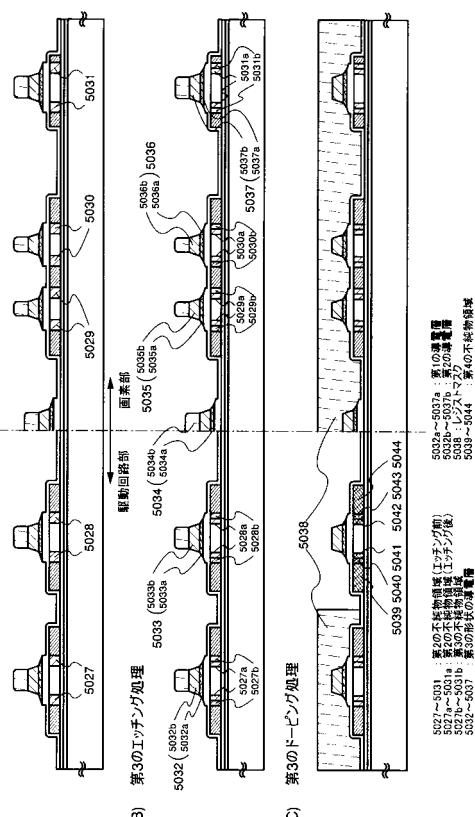

【0103】

まず、実施例 4 に従い、図 6 (C) の状態まで作成する。第 3 のドーピング工程の終了後、レジストを剥離して CMOS 回路部と画素部の TFT が完成する。なお、実施例 4 においては、画素部には画素 TFT と保持容量とを図示していたが、本実施例においては、図 8 (A) に示すように、画素部にはスイッチング用 TFT と EL 駆動用 TFT とを図示している。ただし、TFT の形成工程は同様である。

【0104】

図 8 (A) に示すように、第 1 の層間絶縁膜 5101 を酸化窒化シリコン膜から 100 ~ 200 [nm] の厚さで形成する。その上に有機絶縁物材料から成る第 2 の層間絶縁膜 5102 を形成した後、第 1 の層間絶縁膜 5101、第 2 の層間絶縁膜 5102、およびゲート絶縁膜 5007 に対してコンタクトホールを形成し、各配線（接続配線、信号線を含む）5103 ~ 5108、5110 をパターニング形成した後、接続配線 5108 に接する画素電極 5109 をパターニング形成する。

【0105】

第 2 の層間絶縁膜 5102 としては、有機樹脂を材料とする膜を用い、その有機樹脂としてはポリイミド、ポリアミド、アクリル、BCB（ベンゾシクロブテン）等を使用することが出来る。特に、第 2 の層間絶縁膜 5102 は平坦化の意味合いが強いので、平坦性に優れたアクリルが好ましい。本実施例では TFT によって形成される段差を十分に平坦化しうる膜厚でアクリル膜を形成する。好ましくは 1 ~ 5 [μm]（さらに好ましくは 2 ~ 4 [μm]）とすれば良い。

【0106】

コンタクトホールの形成は、ドライエッティングまたはウエットエッティングを用い、各 TFT のソース領域、ドレイン領域およびゲート電極に達するようにそれぞれ形成する。

【0107】

また、配線（接続配線、信号線を含む）5103 ~ 5108、5110 として、Ti 膜を 100 [nm]、Ti を含むアルミニウム膜を 300 [nm]、Ti 膜 150 [nm] をスパッタ法で連続形成した 3 層構造の積層膜を所望の形状にパターニングしたものを用いる。勿論、他の導電膜を用いても良い。

【0108】

また、本実施例では、画素電極 5109 としてITO 膜を 110 [nm] の厚さに形成し、パターニングを行った。画素電極 5109 を接続配線 5108 と接して重なるように配置することでコンタクトを取っている。また、酸化インジウムに 2 ~ 20 [%] の酸化亜鉛 (Z

$nO$  )を混合した透明導電膜を用いても良い。この画素電極 5109 が EL 素子の陽極となる。(図 8 (A))

【0109】

次に、図 8 (B) に示すように、珪素を含む絶縁膜(本実施例では酸化珪素膜)を 500 [nm]の厚さに形成し、画素電極 5109 に対応する位置に開口部を形成して、バンクとして機能する第 3 の層間絶縁膜 5111 を形成する。開口部を形成する際、ウエットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因する EL 層の劣化が顕著な問題となってしまうため、注意が必要である。

【0110】

次に、EL 層 5112 および陰極 (MgAg 電極) 5113 を、真空蒸着法を用いて大気解放しないで連続形成する。なお、EL 層 5112 の膜厚は 80 ~ 200 [nm] (典型的には 100 ~ 120 [nm])、陰極 5113 の厚さは 180 ~ 300 [nm] (典型的には 200 ~ 250 [nm]) とすれば良い。

【0111】

この工程では、赤色に対応する画素、緑色に対応する画素および青色に対応する画素に対して順次、EL 層および陰極を形成する。但し、EL 層は溶液に対する耐性に乏しいためフォトリソグラフィ技術を用いずに各色個別に形成しなくてはならない。そこでメタルマスクを用いて所望の画素以外を隠し、必要箇所だけ選択的に EL 層および陰極を形成するのが好ましい。

【0112】

即ち、まず赤色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて赤色発光の EL 層を選択的に形成する。次いで、緑色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて緑色発光の EL 層を選択的に形成する。次いで、同様に青色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて青色発光の EL 層を選択的に形成する。なお、ここでは全て異なるマスクを用いるように記載しているが、同じマスクを使いまわしても構わない。

【0113】

ここでは RGB に対応した 3 種類の EL 素子を形成する方式を用いたが、白色発光の EL 素子とカラーフィルタを組み合わせた方式、青色または青緑発光の EL 素子と蛍光体(蛍光性の色変換層: CCM)とを組み合わせた方式、陰極(対向電極)に透明電極を利用して RGB に対応した EL 素子を重ねる方式などを用いても良い。

【0114】

なお、EL 層 5112 としては公知の材料を用いることが出来る。公知の材料としては、駆動電圧を考慮すると有機材料を用いるのが好ましい。例えば正孔注入層、正孔輸送層、発光層および電子注入層でなる 4 層構造を EL 層とすれば良い。

【0115】

次に、同じゲート信号線にゲート電極が接続されたスイッチング用 TFT を有する画素(同じラインの画素)上に、メタルマスクを用いて陰極 5113 を形成する。なお本実施例では陰極 5113 として MgAg を用いたが、本発明はこれに限定されない。陰極 5113 として他の公知の材料を用いても良い。

【0116】

最後に、窒化珪素膜でなるパッシベーション膜 5114 を 300 [nm]の厚さに形成する。パッシベーション膜 5114 を形成しておくことで、EL 層 5112 を水分等から保護することができ、EL 素子の信頼性をさらに高めることが出来る。

【0117】

こうして図 8 (B) に示すような構造の EL ディスプレイが完成する。なお、本実施例における EL ディスプレイの作成工程においては、回路の構成および工程の関係上、ゲート電極を形成している材料である Ta、W によってソース信号線を形成し、ソース、ドレイン電極を形成している配線材料である Al によってゲート信号線を形成しているが、異な

10

20

30

40

50

る材料を用いても良い。

【0118】

ところで、本実施例のELディスプレイは、画素部だけでなく駆動回路部にも最適な構造のTFTを配置することにより、非常に高い信頼性を示し、動作特性も向上しうる。また結晶化工程においてNi等の金属触媒を添加し、結晶性を高めることも可能である。それによって、ソース信号線駆動回路の駆動周波数を10[MHz]以上にすることが可能である。

【0119】

まず、極力動作速度を落とさないようにホットキャリア注入を低減させる構造を有するTFTを、駆動回路部を形成するCMOS回路のNチャネル型TFTとして用いる。なお、ここでいう駆動回路としては、シフトレジスタ、バッファ、レベルシフタ、線順次駆動におけるラッチ、点順次駆動におけるトランスマッショングートなどが含まれる。

【0120】

本実施例の場合、Nチャネル型TFTの活性層は、ソース領域、ドレイン領域、ゲート絶縁膜を間に挟んでゲート電極と重なるオーバーラップLDD領域( $L_{OV}$ 領域)、ゲート絶縁膜を間に挟んでゲート電極と重ならないオフセットLDD領域( $L_{OFF}$ 領域)およびチャネル形成領域を含む。

【0121】

また、CMOS回路のPチャネル型TFTは、ホットキャリア注入による劣化が殆ど気にならないので、特にLDD領域を設けなくても良い。勿論、Nチャネル型TFTと同様にLDD領域を設け、ホットキャリア対策を講じることも可能である。

【0122】

その他、駆動回路において、チャネル形成領域を双方に電流が流れるようなCMOS回路、即ち、ソース領域とドレイン領域の役割が入れ替わるようなCMOS回路が用いられる場合、CMOS回路を形成するNチャネル型TFTは、チャネル形成領域の両サイドにチャネル形成領域を挟む形でLDD領域を形成することが好ましい。このような例としては、点順次駆動に用いられるトランスマッショングートなどが挙げられる。また駆動回路において、オフ電流を極力低く抑える必要のあるCMOS回路が用いられる場合、CMOS回路を形成するNチャネル型TFTは、 $L_{OV}$ 領域を有していることが好ましい。このような例としては、やはり、点順次駆動に用いられるトランスマッショングートなどが挙げられる。

【0123】

なお、実際には図8(B)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

【0124】

また、パッケージング等の処理により気密性を高めたら、基板上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキシブルプリントサーキット: FPC)を取り付けて製品として完成する。このような出荷出来る状態にまでした状態を本明細書中ではEL表示装置という。

【0125】

また、本実施例で示す工程に従えば、EL表示装置の作製に必要なフォトマスクの数を抑えることが出来る。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することが出来る。

【0126】

[実施例6]

本発明のラッチ回路を有する駆動回路は、液晶表示装置のみならず、デジタル映像信号を扱う形式のEL表示装置への適用も容易に出来る。図9に、本発明のラッチ回路を有する

10

20

30

40

50

駆動回路を用いた E L 表示装置の概略図を示す。中央に画素部 9 0 6 が配置されている。画素部には、 E L 素子に電流を供給するための電流供給線 9 0 7 が配置されている。画素部の上側には、ソース信号線を制御するための、ソース信号線駆動回路 9 0 1 が配置されている。ソース信号線駆動回路 9 0 1 は、シフトレジスタ回路 9 0 3 、第 1 のラッチ回路 9 0 4 、第 2 のラッチ回路 9 0 5 等を有する。第 1 のラッチ回路 9 0 4 は、図 1 で示したような構造を有している。他の構成部分に関しては、従来例と同様で良い。画素部の左右には、ゲート信号線を制御するための、ゲート信号線駆動回路 9 0 2 が配置されている。なお、図 9 においては、ゲート信号線駆動回路 9 0 2 は、画素部の左右両側に配置されているが、片側配置でも構わない。ただし、両側配置とした方が、駆動効率、駆動信頼性の面から見て望ましい。

10

#### 【 0 1 2 7 】

図 9 に示した E L 表示装置のソース信号線駆動回路は、図 1 8 に示すような構成をとる。シフトレジスタ回路 1 8 0 1 、第 1 のラッチ回路 ( L A T 1 ) 1 8 0 2 および第 2 のラッチ回路 ( L A T 2 ) 1 8 0 3 の動作は、実施例 1 に示した液晶表示装置のソース信号線駆動回路のものと同様である。 E L 表示装置の場合、ラッチ回路で保持されたデジタル映像信号は、 D / A 変換されることなく直接画素部に書き込まれる。

#### 【 0 1 2 8 】

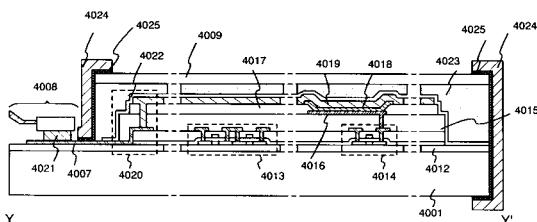

図 1 9 に、 E L 表示装置において多階調表示を行うための方式について示す。例として、 V G A 、 4 ビット階調の E L 表示装置のものを挙げた。

20

#### 【 0 1 2 9 】

映像 ( 静止画、動画を問わない ) の表示を行う際には、図 1 9 ( A ) に示すように、 1 秒間に 6 0 回程度、画面表示の更新が行われており、 1 9 0 1 で示す 1 画面分の表示期間を 1 フレーム期間という。 E L 素子は、アナログ量の信号を用いて輝度の表示を行うのが難しいため、デジタル的に O N の状態と O F F の状態の 2 つの状態のみを用いて階調の表現を行う時間階調方式が表示方法の 1 つとして用いられる。

#### 【 0 1 3 0 】

図 1 9 ( B ) に示すように、 1 フレーム期間は複数のサブフレーム期間に分割されている。このサブフレーム期間の数は、 n ビットの階調表現を行う際には n 個となる。つまり、図 1 9 ( B ) の場合、 4 ビットの階調を表現することができる。 1 つのサブフレーム期間 1 9 0 2 は、それぞれアドレス ( 書き込み ) 期間 1 9 0 3 と、サステイン ( 点灯 ) 期間 1 9 0 4 とを有し、アドレス期間は、 1 画面分の画素への書き込みを行う期間であり、 T a 1 ~ T a 4 の全ての期間で長さが等しい。対して、サステイン期間は、 n ビット階調表示の場合、 T s 1 : T s 2 : . . . : T s n = 2^n : 2^{n-1} : . . . : 2^0 と、 2 のべき乗の比の長さとなっている。図 1 9 ( B ) の場合は、 T s 1 : T s 2 : T s 3 : T s 4 = 8 : 4 : 2 : 1 となる。それぞれのサステイン期間を組み合わせて、 E L 素子の点灯時間の長さの差を利用して階調表示を行う。例えば、 4 ビット階調において、最も暗い階調を 0 、最も明るい階調を 15 としたとき、 1 1 の階調を表現する場合には、 T s 1 、 T s 3 、 T s 4 で点灯させる。これにより、点灯期間の和は、 8 + 2 + 1 = 11 となり、 15 の点灯時間による階調と、 1 1 の点灯時間による階調との間に明るさの差を生ずることが出来る。

30

#### 【 0 1 3 1 】

1 つのサブフレーム期間を詳細に示したものを図 1 9 ( C ) に示す。アドレス期間においては、 1 画面分の信号の書き込みを、ゲート信号線ごとに順次行う。 1 9 0 5 で示される期間が、 1 ゲート信号線選択期間であり、第 1 列目のゲート信号線を選択して信号の書き込みを行う期間 ( 図 1 9 ( C ) で 0 0 1 で示す期間 ) から、最終段のゲート信号線を選択して信号の書き込みを行う期間 ( 図 1 9 ( C ) で 4 8 0 で示す期間 ) までを、アドレス期間内に行う。その後、 1 9 0 6 で示すように、サステイン期間に入る。

40

#### 【 0 1 3 2 】

さらに、 1 つのゲート信号線選択期間を詳細に示したものを図 1 9 ( D ) に示す。 1 ゲート信号線選択期間内では、デジタル映像信号を第 1 のラッチ回路で保持するドットデータ

50

サンプリング期間と、第1のラッチ回路に保持されているデジタル映像信号を、第2のラッチ回路に転送するラインデータラッチ期間1907に分かれている。ドットデータサンプリング期間においては、ソース信号線1本ごとに書き込む信号の保持が、第1列目(図19(D)において、001で示す期間)から最終列(図19(D)において、001で示す期間)まで、順次行われる。1水平期間分の信号が、第1のラッチ回路から第2のラッチ回路に一斉に転送される。EL表示装置においては、以上のような方法で映像の表示を行う。このように、EL表示装置においても、本発明のラッチ回路を有する駆動回路は、特別に表示方法を変えることなく、容易に適用が可能である。

【0133】

[実施例7]

10

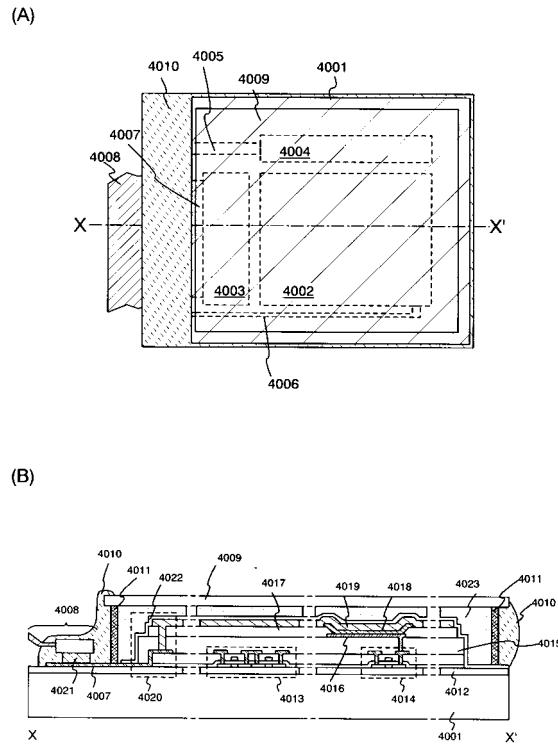

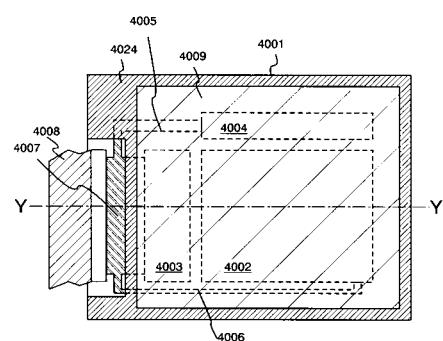

図10(A)は本発明を用いたEL表示装置の上面図であり、図10(A)をX-X'面で切断した断面図を図10(B)に示す。図10(A)において、4001は基板、4002は画素部、4003はソース信号線側駆動回路、4004はゲート信号線側駆動回路であり、それぞれの駆動回路は配線4005、4006、4007を経てFPC4008に至り、外部機器へと接続される。

【0134】

このとき、画素部、好ましくは駆動回路および画素部を囲むようにしてカバー材4009、密封材4010、シーリング材(ハウジング材ともいう)4011(図10(B)に図示)が設けられている。

【0135】

20

また、図10(B)は本実施例のEL表示装置の断面構造であり、基板4001、下地膜4012の上に駆動回路用TFT(但し、ここではNチャネル型TFTとPチャネル型TFTを組み合わせたCMOS回路を図示している)4013および画素部用TFT4014(但し、ここではEL素子への電流を制御するEL駆動用TFTだけ図示している)が形成されている。これらのTFTは公知の構造(トップゲート構造あるいはボトムゲート構造)を用いれば良い。

【0136】

公知の作製方法を用いて駆動回路用TFT4013、画素部用TFT4014が完成したら、樹脂材料でなる層間絶縁膜(平坦化膜)4015の上に画素部用TFT4014のドレインと電気的に接続する透明導電膜でなる画素電極4016を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物を用いることができる。そして、画素電極4016を形成したら、絶縁膜4017を形成し、画素電極4016上に開口部を形成する。

30

【0137】

次に、EL層4018を形成する。EL層4018は公知のEL材料(正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンドルコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

40

【0138】

本実施例では、シャドウマスクを用いて蒸着法によりEL層を形成する。シャドウマスクを用いて画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層および青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルタを組み合わせた方式、白色発光層とカラーフィルタを組み合わせた方式があるがいずれの方法を用いても良い。勿論、単色発光のEL表示装置とすることもできる。

【0139】

EL層4018を形成したら、その上に陰極4019を形成する。陰極4019とEL層4018の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空

50

中で E L 層 4 0 1 8 と陰極 4 0 1 9 を連続成膜するか、 E L 層 4 0 1 8 を不活性雰囲気で形成し、大気解放しないで陰極 4 0 1 9 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式（クラスターツール方式）の成膜装置を用いることで上述のような成膜を可能とする。

【 0 1 4 0 】

なお、本実施例では陰極 4 0 1 9 として、 L i F ( フッ化リチウム ) 膜と A l ( アルミニウム ) 膜の積層構造を用いる。具体的には E L 層 4 0 1 8 上に蒸着法で 1 [ nm ] 厚の L i F ( フッ化リチウム ) 膜を形成し、その上に 3 0 0 [ nm ] 厚のアルミニウム膜を形成する。勿論、公知の陰極材料である M g A g 電極を用いても良い。そして陰極 4 0 1 9 は 4 0 2 0 で示される領域において配線 4 0 0 7 に接続される。配線 4 0 0 7 は陰極 4 0 1 9 に所定の電圧を与えるための電源線であり、導電性ペースト材料 4 0 2 1 を介して F P C 4 0 0 8 に接続される。

【 0 1 4 1 】

4 0 2 0 に示された領域において陰極 4 0 1 9 と配線 4 0 0 7 とを電気的に接続するためには、層間絶縁膜 4 0 1 5 および絶縁膜 4 0 1 7 にコンタクトホールを形成する必要がある。これらは層間絶縁膜 4 0 1 5 のエッティング時（画素電極用コンタクトホールの形成時）や絶縁膜 4 0 1 7 のエッティング時（ E L 層形成前の開口部の形成時）に形成しておけば良い。また、絶縁膜 4 0 1 7 をエッティングする際に、層間絶縁膜 4 0 1 5 まで一括でエッティングしても良い。この場合、層間絶縁膜 4 0 1 5 と絶縁膜 4 0 1 7 が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができます。

【 0 1 4 2 】

このようにして形成された E L 素子の表面を覆って、パッシベーション膜 4 0 2 2 、充填材 4 0 2 3 、カバー材 4 0 0 9 が形成される。

【 0 1 4 3 】

さらに、 E L 素子部を囲むようにして、カバー材 4 0 0 9 と基板 4 0 0 1 の内側にシーリング材 4 0 1 1 が設けられ、さらにシーリング材 4 0 1 1 の外側には密封材（第 2 のシーリング材） 4 0 1 0 が形成される。

【 0 1 4 4 】

このとき、この充填材 4 0 2 3 は、カバー材 4 0 0 9 を接着するための接着剤としても機能する。充填材 4 0 2 3 としては、 P V C ( ポリビニルクロライド ) 、エポキシ樹脂、シリコン樹脂、 P V B ( ポリビニルブチラル ) または E V A ( エチレンビニルアセテート ) を用いることができる。この充填材 4 0 2 3 の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。また充填材 4 0 2 3 の内部に、酸素を捕捉する効果を有する酸化防止剤等を配置することで、 E L 層の劣化を抑えて良い。

【 0 1 4 5 】

また、充填材 4 0 2 3 の中にスペーサーを含有させてもよい。このとき、スペーサーを B a O などからなる粒状物質とし、スペーサー自身に吸湿性をもたせてよい。

【 0 1 4 6 】

スペーサーを設けた場合、パッシベーション膜 4 0 2 2 はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてよい。

【 0 1 4 7 】

また、カバー材 4 0 0 9 としては、ガラス板、アルミニウム板、ステンレス板、 F R P ( Fiberglass-Reinforced Plastics ) 板、 P V F ( ポリビニルフルオライド ) フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材 4 0 2 3 として P V B や E V A を用いる場合、数十 [ μm ] のアルミニウムホイルを P V F フィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【 0 1 4 8 】

但し、 E L 素子からの発光方向（光の放射方向）によっては、カバー材 4 0 0 9 が透光性

10

20

30

40

50

を有する必要がある。

【0149】

また、配線4007はシーリング材4011および密封材4010と基板4001との隙間を通ってFPC4008に電気的に接続される。なお、ここでは配線4007について説明したが、他の配線4005、4006も同様にしてシーリング材4011および密封材4010の下を通ってFPC4008に電気的に接続される。

【0150】

なお本実施例では、充填材4023を設けてからカバー材4009を接着し、充填材4023の側面(露呈面)を覆うようにシーリング材4011を取り付けているが、カバー材4009およびシーリング材4011を取り付けてから、充填材4023を設けても良い。この場合、基板4001、カバー材4009およびシーリング材4011で形成されている空隙に通じる充填材の注入口を設ける。そして前記空隙を真空状態( $10^{-2}$  [Torr]以下)にし、充填材の入っている水槽に注入口を浸してから、空隙の外の気圧を空隙の中の気圧よりも高くして、充填材を空隙の中に充填する。

【0151】

[実施例8]

本実施例では、本発明を用いて実施例7とは異なる形態のEL表示装置を作製した例について、図17(A)、(B)を用いて説明する。図10(A)、(B)と同じ番号のものは同じ部分を指しているので説明は省略する。

【0152】

図17(A)は本実施例のEL表示装置の上面図であり、図17(A)をY-Y'面で切断した断面図を図17(B)に示す。

【0153】

実施例5に従って、EL素子の表面を覆ってパッシベーション膜4022までを形成する。

【0154】

さらに、EL素子を覆うようにして充填材4023を設ける。この充填材4023は、カバー材4009を接着するための接着剤としても機能する。充填材4023としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材4023の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。また充填材4023の内部に、酸素を捕捉する効果を有する酸化防止剤等を配置することで、EL層の劣化を抑えても良い。

【0155】

また、充填材4023の中にスペーサーを含有させてもよい。このとき、スペーサーをBaOなどからなる粒状物質とし、スペーサー自体に吸湿性をもたせててもよい。

【0156】

スペーサーを設けた場合、パッシベーション膜4022はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0157】

また、カバー材4009としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材4023としてPVBやEVAを用いる場合、数十[μm]のアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0158】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材4009が透光性を有する必要がある。

10

20

30

40

50

## 【0159】

次に、充填材4023を用いてカバー材4009を接着した後、充填材4023の側面（露呈面）を覆うようにフレーム材4024を取り付ける。フレーム材4024はシーリング材（接着剤として機能する）4025によって接着される。このとき、シーリング材4025としては、光硬化性樹脂を用いるのが好ましいが、EL層の耐熱性が許せば熱硬化性樹脂を用いても良い。なお、シーリング材4025はできるだけ水分や酸素を透過しない材料であることが望ましい。また、シーリング材4025の内部に乾燥剤を添加しても良い。

## 【0160】

また、配線4007はシーリング材4025と基板4001との隙間を通してFPC4008に電気的に接続される。なお、ここでは配線4007について説明したが、他の配線4005、4006も同様にしてシーリング材4025の下を通してFPC4008に電気的に接続される。

## 【0161】

なお本実施例では、充填材4023を設けてからカバー材4009を接着し、充填材4023の側面（露呈面）を覆うようにフレーム材4024を取り付けているが、カバー材4009、シーリング材4025およびフレーム材4024を取り付けてから、充填材4023を設けても良い。この場合、基板4001、カバー材4009、シーリング材4025およびフレーム材4024で形成されている空隙に通じる充填材の注入口を設ける。そして前記空隙を真空状態（ $10^{-2}$  [Torr] 以下）にし、充填材の入っている水槽に注入口を浸してから、空隙の外の気圧を空隙の中の気圧よりも高くして、充填材を空隙の中に充填する。

## 【0162】

## [実施例9]

本発明を用いたアクティブマトリクス型表示装置には様々な用途がある。本実施例では、本発明の駆動回路を用いた表示装置を組み込んだ半導体装置について説明する。

## 【0163】

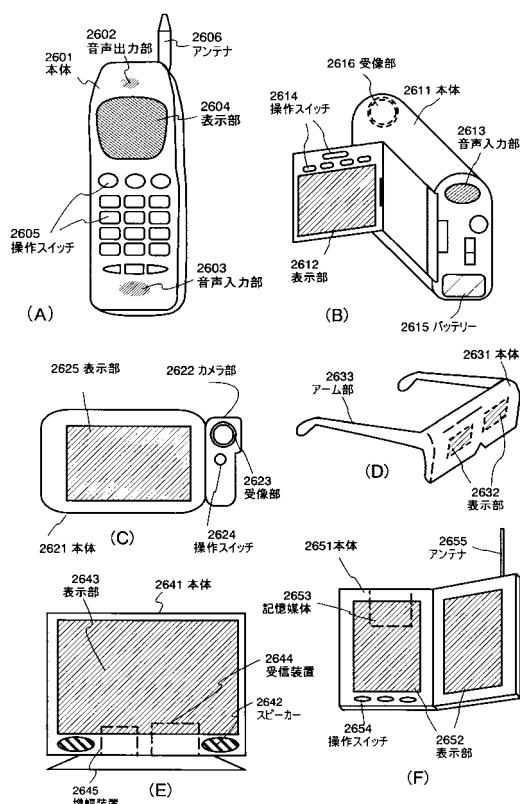

このような表示装置には、携帯情報端末（電子手帳、モバイルコンピュータ、携帯電話等）、ビデオカメラ、デジタルカメラ、パーソナルコンピュータ、テレビ、プロジェクタ装置等が挙げられる。それらの一例を図14、図15および図16に示す。

## 【0164】

図14（A）は携帯電話であり、本体2601、音声出力部2602、音声入力部2603、表示部2604、操作スイッチ2605、アンテナ2606から構成されている。本発明は表示部2604に適用することができる。

## 【0165】

図14（B）はビデオカメラであり、本体2611、表示部2612、音声入力部2613、操作スイッチ2614、バッテリー2615、受像部2616から成っている。本発明は表示部2612に適用することができる。

## 【0166】

図14（C）はモバイルコンピュータあるいは携帯型情報端末であり、本体2621、カメラ部2622、受像部2623、操作スイッチ2624、表示部2625で構成されている。本発明は表示部2625に適用することができる。

## 【0167】

図14（D）はヘッドマウントディスプレイであり、本体2631、表示部2632、アーム部2633で構成される。本発明は表示部2632に適用することができる。

## 【0168】

図14（E）はテレビであり、本体2641、スピーカー2642、表示部2643、受信装置2644、増幅装置2645等で構成される。本発明は表示部2643に適用することができる。

## 【0169】

10

20

30

40

50

図14(F)は携帯書籍であり、本体2651、表示部2652、記憶媒体2653、操作スイッチ2654、アンテナ2655から構成されており、ミニディスク(MD)やDVD(Digital Versatile Disc)に記憶されたデータや、アンテナで受信したデータを表示するものである。本発明は表示部2652に適用することができる。

【0170】

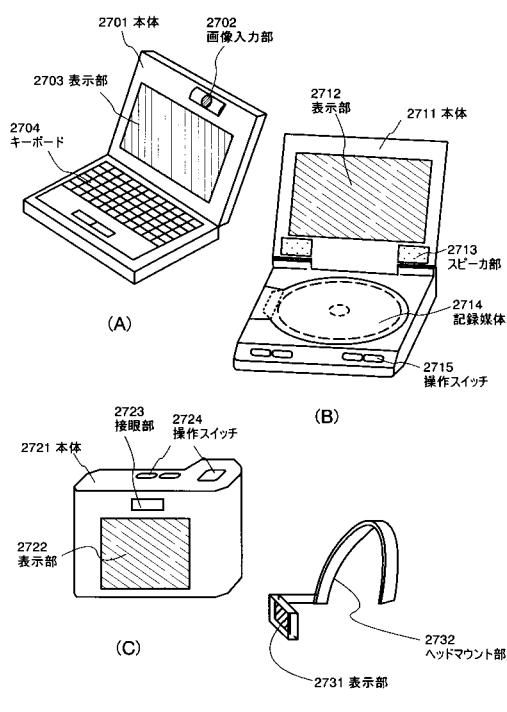

図15(A)はパーソナルコンピュータであり、本体2701、映像入力部2702、表示部2703、キーボード2704で構成される。本発明は表示部2703に適用することができる。

【0171】

図15(B)はプログラムを記録した記録媒体を用いるプレーヤーであり、本体2711、表示部2712、スピーカー部2713、記録媒体2714、操作スイッチ2715で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2612に適用することができる。

【0172】

図15(C)はデジタルカメラであり、本体2721、表示部2722、接眼部2723、操作スイッチ2724、受像部(図示しない)で構成される。本発明は表示部2722に適用することができる。

【0173】

図15(D)は片眼のヘッドマウントディスプレイであり、表示部2731、バンド部2732で構成される。本発明は表示部2731に適用することができる。

【0174】

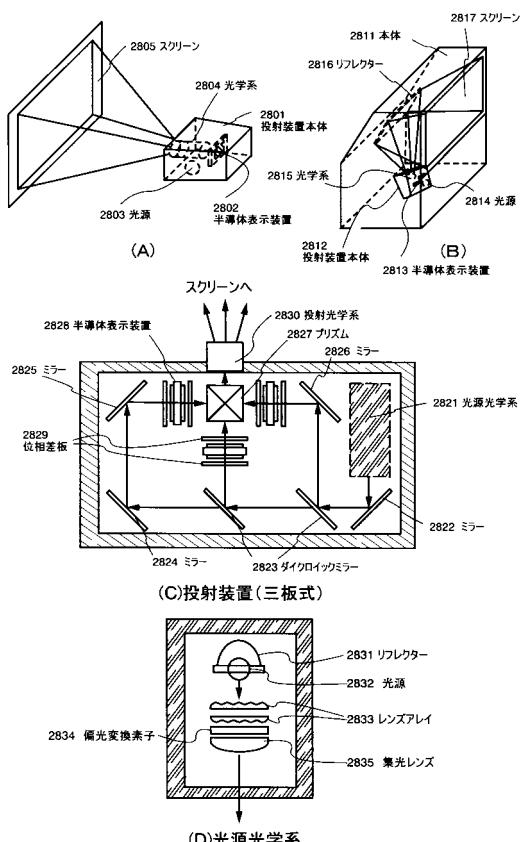

図16(A)はフロント型プロジェクタであり、投射装置本体2801、表示装置2802、光源2803、光学系2804、スクリーン2805で構成されている。なお、投射装置2801には単版式のものを用いても良いし、R、G、Bの光にそれぞれ対応した三板式のものを用いても良い。本発明は表示装置2802に適用することができる。

【0175】

図16(B)はリア型プロジェクタであり、本体2811、投射装置本体2812、表示装置2813、光源2814、光学系2815、リフレクター2816、スクリーン2817で構成されている。なお、投射装置2813には単版式のものを用いても良いし、R、G、Bの光にそれぞれ対応した三板式のものを用いても良い。本発明は表示装置2813に適用することができる。

【0176】

なお、図16(C)は、図16(A)及び図16(B)中における投射装置本体2801、2812の構造の一例を示した図である。投射装置2801、2812は、光源光学系2821、ミラー2822、2824～2826、ダイクロイックミラー2823、プリズム2827、表示装置2828、位相差板2829、投射光学系2830で構成される。投射光学系2830は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単版式であっても良い。また、図16(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けても良い。

【0177】

また、図16(D)は、図16(C)中における光源光学系2821の構造の一例を示した図である。本実施例では、図16(C)中における光源光学系2821は、図16(D)中におけるリフレクター2831、光源2832、レンズアレイ2833、偏光変換素子2834、集光レンズ2835で構成される。なお、図16(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けても良い。

10

20

30

40

50

**【発明の効果】**

本発明のラッチ回路を有する駆動回路を表示装置に用いることにより、従来のラッチ回路周辺で問題となっていた、回路から出力される信号の遅延に、映像信号の保持タイミングが依存することによる、表示装置ごとのタイミングの微調整をすることなく、外部から入力する信号の調整のみを考えることによって保持タイミングを決定することが出来る。加えて、シフトレジスタ回路の駆動周波数は1/2となっているため、信頼性の向上も期待出来る。

**【図面の簡単な説明】**

- 【図1】 本発明のラッチ回路を含む周辺回路の構成例を示す図。

- 【図2】 デジタル映像信号の入力と、デジタル映像信号を保持するパルスの遅延との関係を従来と本発明とで比較する図。 10

- 【図3】 本発明のラッチ回路を用いて表示装置を構成する場合の表示装置全体の概略図。

- 【図4】 図3に示した表示装置のソース信号線駆動回路の回路構成例を示す図。

- 【図5】 液晶表示装置の作成工程例を示す図。

- 【図6】 液晶表示装置の作成工程例を示す図。

- 【図7】 液晶表示装置の作成工程例を示す図。

- 【図8】 EL表示装置の作成工程例を示す図。

- 【図9】 本発明のラッチ回路を用いてEL表示装置を構成する場合のEL表示装置全体の概略図。 20

- 【図10】 EL表示装置の正面図および断面図。

- 【図11】 従来のデジタル映像信号入力式の表示装置の全体の概略図。

- 【図12】 図11に示した表示装置のソース信号線駆動回路の回路構成を示す図。

- 【図13】 従来のラッチ回路周辺の構成を示す図。

- 【図14】 本発明のラッチ回路を含む駆動回路の適用が可能な電子装置の例を示す図。

- 【図15】 本発明のラッチ回路を含む駆動回路の適用が可能な電子装置の例を示す図。

- 【図16】 本発明のラッチ回路を含む駆動回路の適用が可能な電子装置の例を示す図。 30

- 【図17】 EL表示装置の正面図および断面図。

- 【図18】 EL表示装置のソース信号線駆動回路の回路構成例を示す図。

- 【図19】 EL表示装置における、時間階調方式を説明するためのタイミングチャートを示す図。

- 【図20】 本発明のラッチ回路を含む周辺回路の構成例を示す図。

- 【図21】 本発明のラッチ回路を含む周辺回路の構成例およびタイミングチャートを示す図。

- 【図22】 本発明のラッチ回路を含む周辺回路の構成例を示す図。

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 义 7 】

【 図 6 】

【 図 8 】

【図 9】

【図 11】

【図 10】

【図 12】

【図13】

【図14】

【図15】

【図16】

【図17】

(A)

(B)

【図18】

【図19】

【図20】

【図21】

(A)

(B)

【図22】

2201, 2204 : プリチャージ回路

2202, 2205 : 保持動作選択回路

2203, 2206 : 保持回路

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

G09G 3/00 - 3/38