US 20080068389A1

## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2008/0068389 A1 Bakalash et al. (43) Pub. Date: Mar. 20, 2008

(54) MULTI-MODE PARALLEL GRAPHICS RENDERING SYSTEM (MMPGRS) EMBODIED WITHIN A HOST COMPUTING SYSTEM AND EMPLOYING THE PROFILING OF SCENES IN GRAPHICS-BASED APPLICATIONS

(76) Inventors: **Reuven Bakalash**, Shdema (IL); **Yaniv Leviathan**, Savyon (IL)

Correspondence Address:

Thomas J. Perkowski, Esq. 1266 East Main Street Stamford, CT 06902 (US)

(21) Appl. No.: 11/901,713

(22) Filed: Sep. 18, 2007

## Related U.S. Application Data

Continuation of application No. 11/897,536, filed on

Aug. 30, 2007, which is a continuation-in-part of application No. 11/789,039, filed on Apr. 23, 2007, and which is a continuation-in-part of application No. 11/655,735, filed on Jan. 18, 2007.

Said application No. 11/897,536 is a continuation-in-part of application No. 11/648,160, filed on Dec. 31, 2006, and which is a continuation-in-part of application No. 11/386,454, filed on Mar. 22, 2006, and which is a continuation-in-part of application No. 11/340,402, filed on Jan. 25, 2006.

(43) **Pub. Date:** Mar. 20, 2008

Said application No. 11/897,536 is a continuation-inpart of application No. 10/579,682, filed on Mar. 23, 2007, filed as 371 of international application No. PCT/IL04/01069, filed on Nov. 19, 2004.

(60) Provisional application No. 60/759,608, filed on Jan. 18, 2006. Provisional application No. 60/647,146, filed on Jan. 25, 2005. Provisional application No. 60/523,084, filed on Nov. 19, 2003.

## **Publication Classification**

**ABSTRACT**

Multi-mode parallel graphics rendering system (MMGRPS) embodied within a host computing system and employing the profiling of scenes in a graphics-based application. The MMPGRS supports multiple modes of parallel operation selected from the group consisting of object division, image division, and time division. A plurality of graphic processing pipelines (GPPLs) support a parallel graphics rendering process that employs one or more of the object division, image division and/or time division modes of parallel operation in order to execute graphic commands and process graphics data, and render pixel-composited images containing graphics for display on a display device during the run-time of the graphics-based application. An automatic mode control module automatically controls the mode of parallel operation of the MMPGRS during the run-time of the graphics-based application.

(57)

Fig.1A2 (Prior Art)

Fig. 1A3 (Prior Art)

Fig. 1B3 (Prior Art)

Fig. 1B4 (Prior Art)

Fig.1B5 (Prior Art)

Fig. 1C (Prior Art)

Fig.2A3 (Prior Art)

Fig. 2A4 (Prior Art)

Fig. 2B (Prior Art)

Fig. 2C (Prior Art)

FIG. 3A (Prior Art)

Fig. 3B (Prior Art)

| Parallel<br>mode   | Data<br>Transfer | Memory | Geometry | Pixel |

|--------------------|------------------|--------|----------|-------|

| Image<br>Division  |                  |        |          | >     |

| Time<br>Division   |                  |        | ^        | >     |

| Object<br>Division | ^                | >      | >        | >     |

Fig. 3C2 (Prior Art)

FIG. 4*F*

Fig. 4B1

Fig. 4B2

Fig. 4B3

Sub-states definitions

| -qns  | Decomposition    | Distribution | Recomposition | Parallel    |

|-------|------------------|--------------|---------------|-------------|

| state | ٧                | В            | ၁             | mode        |

| 1     | Object decomp.   | Divide       | Test based    | Object div. |

| 2     | Image decomp.    | Broadcast    | Screen based  | Image div.  |

| 3     | Alternate frames | Single       | None          | Time div.   |

| 4     | Single           |              |               | Single GPU  |

Fig. 4C

Fig. 5A

Fig. 5B

-1g. 6CZ

| je<br>e | Hub device | Hub device | Hub device | Hub device | Consol interna |

|---------|------------|------------|------------|------------|----------------|

|         |            |            |            |            |                |

|         |            |            |            |            |                |

| MMGPRS<br>Architecture | Profiling and<br>Control<br>(PCM) | Decomp (1) | Decomp (2)    | Distribution<br>module | Cluster of<br>GPPLs            | Recomp.<br>module               |

|------------------------|-----------------------------------|------------|---------------|------------------------|--------------------------------|---------------------------------|

| 1. HMS (software)      | HMS                               | HMS        | HMS           | Bridge                 | Ext. GPU                       | HMS                             |

| 2. HMS + IGD           | нмѕ                               | HMS        | НМЅ           | Bridge                 | Bridge (IGD) +<br>ext. GPU     | HMS                             |

| 3. HMS + Fusion        | ЯМЯ                               | SWH        | нмѕ           | Bridge                 | Ext. GPU                       | GPU                             |

| 4. HMS + multicore     | нмѕ                               | · SWH      | HMS           | Processor die          | Processor die<br>+ ext. GPU    | Processor die                   |

| 5. HMS + GPU-recomp.   | нмѕ                               | HMS        | нмѕ           | HMS                    | Ext. GPU                       | GPU                             |

| 6. Hub                 | нмѕ                               | HMS        | Hub device    | Hub device             | Ext. GPU                       | Hub device                      |

| 7. Hub +GPU-recomp.    | NMS                               | SMH        | Hub device    | Hub device             | Ext. GPU                       | GPU                             |

| 8. Chipset             | нмѕ                               | HMS        | Bridge        | Bridge                 | Bridge +<br>Ext. GPU           | Bridge or Ext.<br>GPU           |

| 9. CPU/GPU fusion      | HMS or<br>Processor die           | HMS        | Processor die | Processor die          | Processor die<br>+<br>Ext. GPU | Processor die<br>or<br>Ext. GPU |

| 10. Multicore CPU      | HMS or<br>Processor die           | HMS        | Processor die | Processor die          | Processor die<br>+ Ext. GPU    | Processor die<br>or<br>Ext. GPU |

| 11. Game console       | Hub device                        | Hub device | Hub device    | Hub device             | Consol internal                | Hub device<br>or GPU            |

-ia. 7A2

Fig. 7A3

Fig. 7A4

Fig. 7A5

```

else if ((depth1.r == depth2.r) && (depth1.g == depth2.g) && (depth1.b > depth2.b)) {

else if ((depth1.r == depth2.r) && (depth1.g > depth2.g)) {

vec4 depth1 = texture2D(dep1,gl_TexCoord[0].st);

vec4 depth2 = texture2D(dep2,gl_TexCoord[0].st);

vec4 texel2 = texture2D(tex2,gl_TexCoord[0].st);

vec4 texel1 = texture2D(tex1,gl_TexCoord[0].st);

uniform sampler2D dep1,dep2; void main(void)

uniform sampler2D tex1,tex2;

if (depth1.r > depth2.r) {

color = texel2;

gl_FragColor = (color);

vec4 color = texel1;

color = texel2;

color = texel2;

```

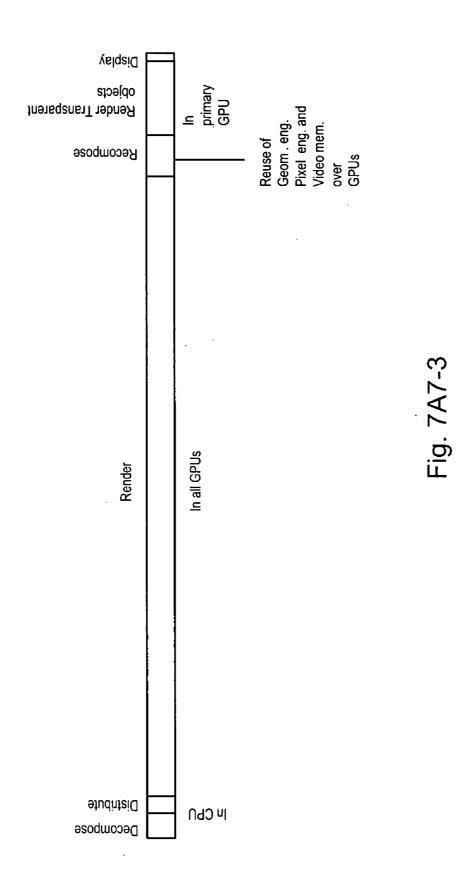

Fig. 7A7-2

Fig. 7B4-1

Fig. 7B5

Fig. 7B6

Fig. 7B6-1

Fig. 7B7

Fig. 7B7-1

Fig. 7B9-1

Fig. 7B9-2

Fig. 11C1

Fig. 11C

### MULTI-MODE PARALLEL GRAPHICS RENDERING SYSTEM (MMPGRS) EMBODIED WITHIN A HOST COMPUTING SYSTEM AND EMPLOYING THE PROFILING OF SCENES IN GRAPHICS-BASED APPLICATIONS

#### CROSS-REFERENCE TO RELATED CASES

[0001] The present application is a Continuation of U.S. application Ser. No. 11/897,536 filed Aug. 30, 2007; which is a Continuation-in-Part (CIP) of the following Applications: U.S. application Ser. No. 11/789,039 filed Apr. 23, 2007; U.S. application Ser. No. 11/655,735 filed Jan. 18, 2007, which is based on Provisional Application Ser. No. 60/759,608 filed Jan. 18, 2006; U.S. application Ser. No. 11/648,160 filed Dec. 31, 2006; U.S. application Ser. No. 11/386,454 filed Mar. 22, 2006; U.S. application Ser. No. 11/340,402 filed Jan. 25, 2006, which is based on Provisional Application No. 60/647,146 filed Jan. 25, 2005; U.S. application Ser. No. 10/579,682 filed May 17, 2006, which is a National Stage Entry of International Application No. PCT/IL2004/001069 filed Nov. 19, 2004, which is based on Provisional Application Ser. No. 60/523,084 filed Nov. 19, 2003; each said patent application being commonly owned by Lucid Information Technology, Ltd., and being incorporated herein by reference as if set forth fully herein.

### BACKGROUND OF INVENTION

[0002] 1. Field of Invention

[0003] The present invention relates generally to the field of computer graphics rendering, and more particularly, ways of and means for improving the performance of parallel graphics rendering processes supported on multiple 3D graphics processing pipeline (GPPL) platforms associated with diverse types of computing machinery, including, but not limited, to PC-level computers, game console systems, graphics-supporting application servers, and the like.

[0004] 2. Brief Description of the State of Knowledge in the Art

[0005] There is a great demand for high performance three-dimensional (3D) computer graphics systems in the fields of product design, simulation, virtual-reality, videogaming, scientific research, and personal computing (PC). Clearly a major goal of the computer graphics industry is to realize real-time photo-realistic 3D imagery on PC-based workstations, desktops, laptops, and mobile computing devices. In general, there are two fundamentally different classes of machines in the 3D computer graphics field, namely: (1) Object-Oriented Graphics Systems, wherein 3D scenes are represented as a complex of geometric objects (primitives) in 3D continuous geometric space, and 2D views or images of such 3D scenes are computed using geometrical projection, ray tracing, and light scattering/ reflection/absorption modeling techniques, typically based upon laws of physics; and (2) VOlume ELement (VOXEL) Graphics Systems, wherein 3D scenes and objects are represented as a complex of voxels (x,y,z volume elements) represented in 3D Cartesian Space, and 2D views or images of such 3D voxel-based scenes are also computed using geometrical projection, ray tracing, and light scattering/ reflection/absorption modeling techniques, again typically based upon laws of physics. Examples of early GDL-based graphics systems are disclosed in U.S. Pat. No. 4,862,155,

whereas examples of early voxel-based 3D graphics systems are disclosed in U.S. Pat. No. 4,985,856, each incorporated herein by reference in its entirety. In the contemporary period, most PC-based computing systems include a 3D graphics subsystem based the "Object-Orient Graphics" system design. In such graphics system design, "objects" within a 3D scene are represented by 3D geometrical models, and these geometrical models are typically constructed from continuous-type 3D geometric representations including, for example, 3D straight line segments, planar polygons, polyhedra, cubic polynomial curves, surfaces, volumes, circles, and quadratic objects such as spheres, cones, and cylinders (i.e. geometrical data and commands). These 3D geometrical representations are used to model various parts of the 3D scene or object, and are expressed in the form of mathematical functions evaluated over particular values of coordinates in continuous Cartesian space. Typically, the 3D geometrical representations of the 3D geometric model are stored in the format of a graphical display list (i.e. a structured collection of 2D and 3D geometric primitives). Currently, planar polygons, mathematically described by a set of vertices, are the most popular form of 3D geometric representation.

[0006] Once modeled using continuous 3D geometrical representations, the 3D scene is graphically displayed (as a 2D view of the 3D geometrical model) along a particular viewing direction, by repeatedly scan-converting the stream of graphics commands and data (GCAD). At the current state of the art, the scan-conversion process can be viewed as a "computational geometry" process which involves the use of (i) a geometry processor (i.e. geometry processing subsystem or engine) as well as a pixel processor (i.e. pixel processing subsystem or engine) which together transform (i.e. project, shade and color) the graphics objects and bit-mapped textures, respectively, into an unstructured matrix of pixels. The composed set of pixel data is stored within a 2D frame buffer (i.e. Z buffer) before being transmitted to and displayed on the surface of a display screen.

[0007] A video processor/engine refreshes the display screen using the pixel data stored in the 2D frame buffer. Any changes in the 3D scene requires that the geometry and pixel processors repeat the whole computationally-intensive pixel-generation pipeline process, again and again, to meet the requirements of the graphics application at hand. For every small change or modification in viewing direction of the human system user, the graphical display list must be manipulated and repeatedly scan-converted. This, in turn, causes both computational and buffer contention challenges which slow down the working rate of the graphics system. To accelerate this computationally-intensive graphics processing pipeline process, custom hardware including geometry, pixel and video engines, have been developed and incorporated into most conventional graphics system designs.

[0008] In order to render a 3D scene (from its underlying graphics commands and data) and produce high-resolution graphical projections for display on a display device, such as a LCD panel, early 3D graphics systems attempted to relieve the host CPU of computational loading by employing a single graphics pipeline comprising a single graphics processing unit (GPU), supported by video memory.

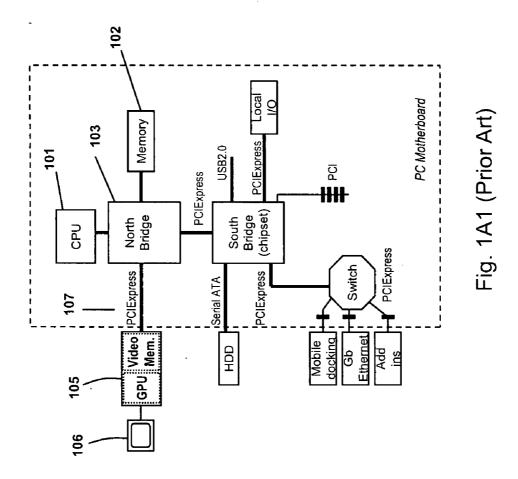

[0009] As shown in FIGS. 1A1, 1A2 and 1A3, a typical PC based graphic architecture has an external graphics card

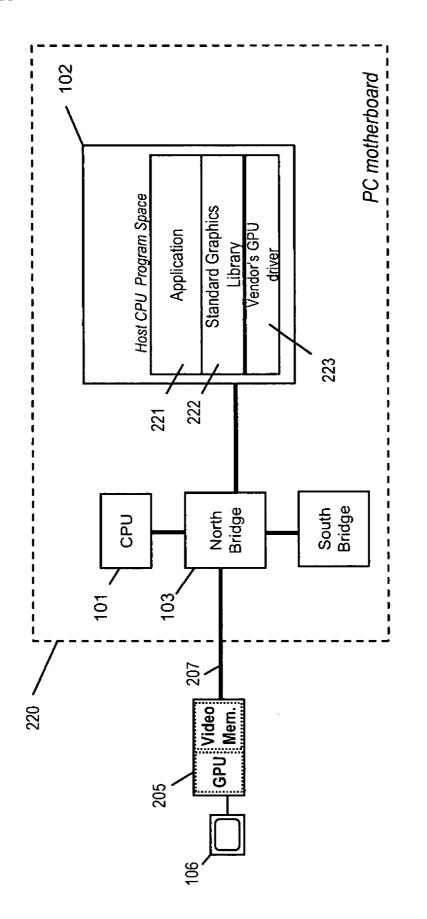

105 comprising a graphics processing unit (GPU) and video memory. As shown, the graphic card is connected to the display 106 on one side, and the CPU 101 through bus (e.g. PCI-Express) 107 and Memory Bridge 103 (termed also "chipset", e.g. 975 by Intel), on the other side. As shown in FIG. 1A3, the host CPU program/memory space stores the graphics applications, the standard graphics library, and the vendor's GPU drivers.

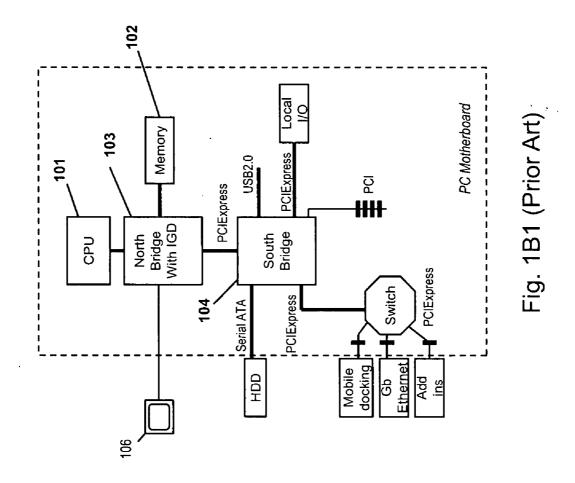

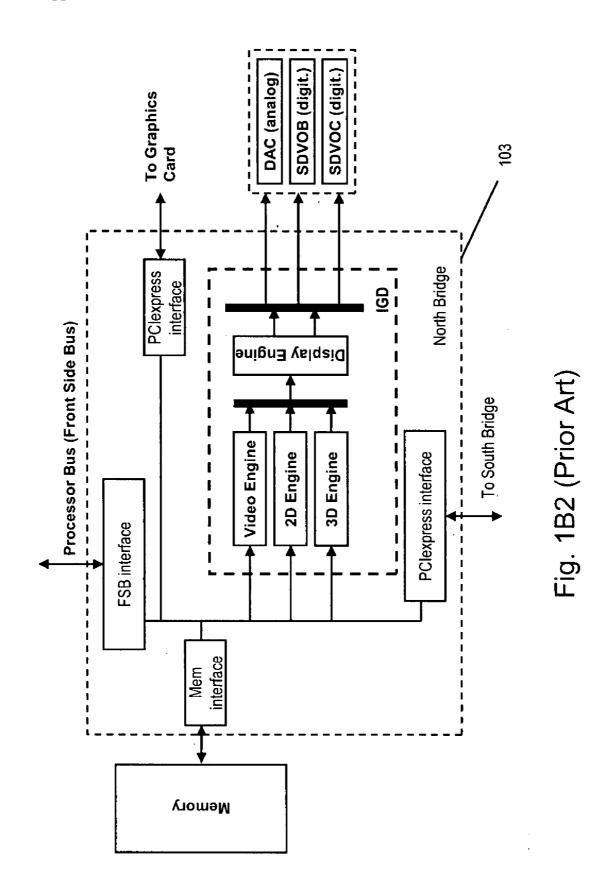

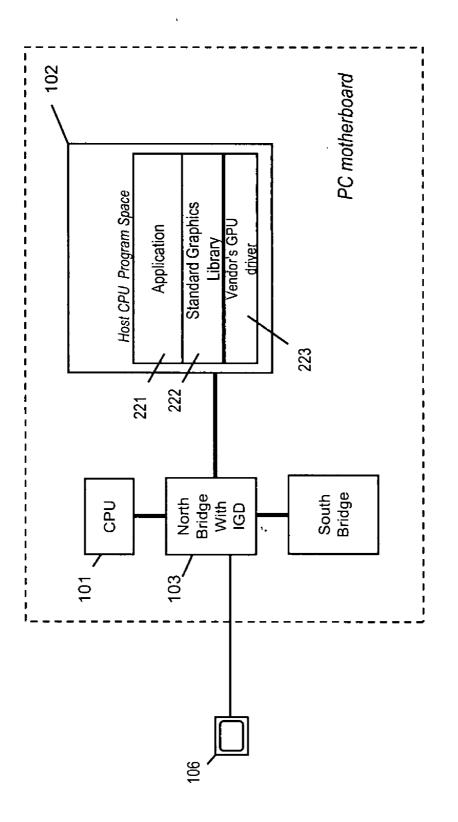

[0010] As shown in FIGS. 1B1, 1B2 and 1B3, a typical prior art PC-based computing system employs a conventional graphics architecture employing a North memory bridge with an integrated graphics device (IGD) 103. The IGD supports a single graphics pipeline process, and is operably coupled to a South bridge, via a PCI-express bus, for supporting the input/output ports of the system. As shown, the IGD includes a video engine, a 2D engine, a 3D engine, and a display engine.

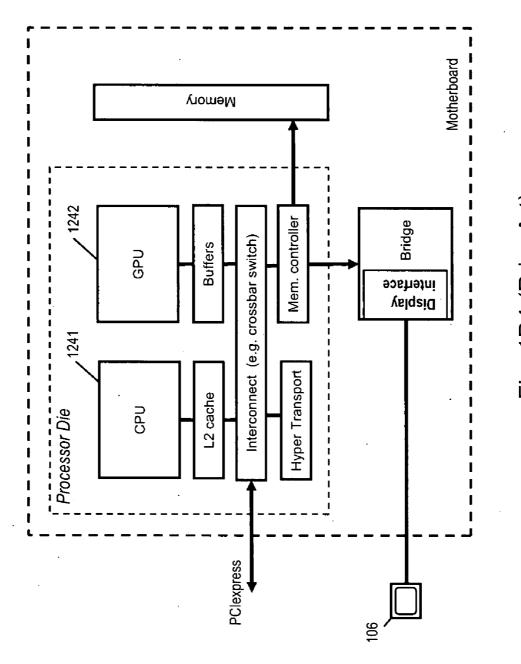

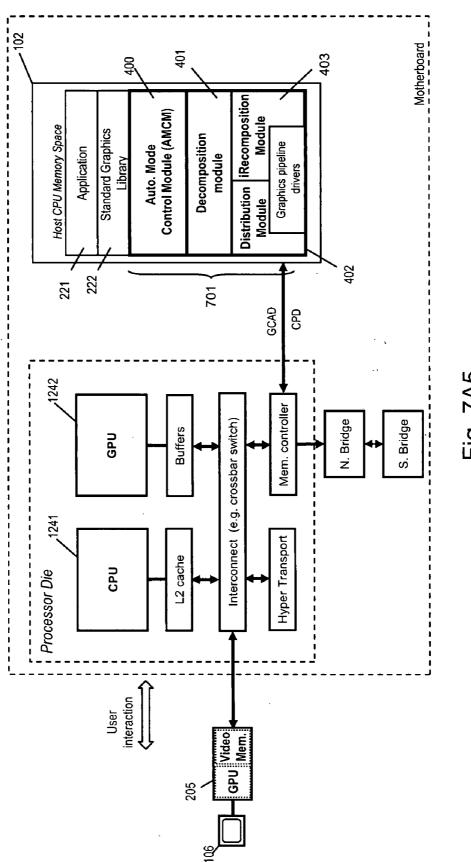

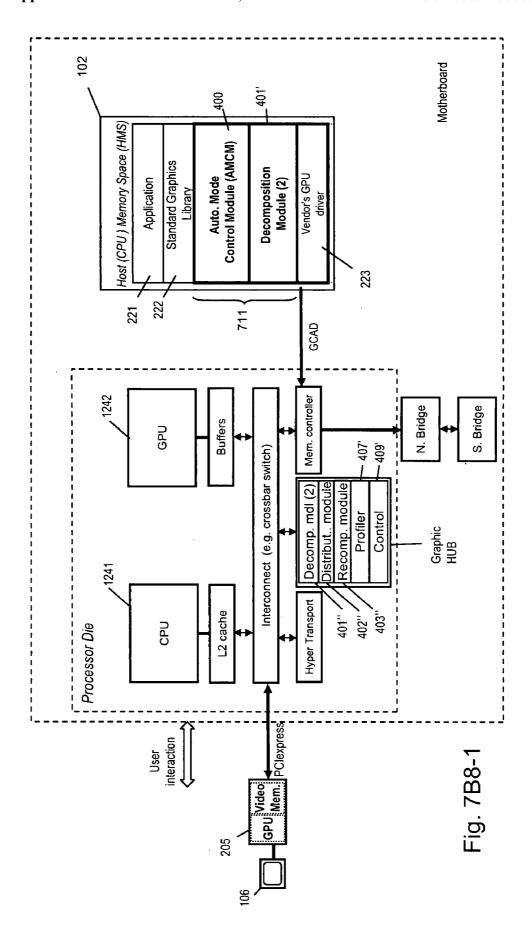

[0011] As shown in FIG. 1B4, a prior art PC-based computing system employs a conventional Fusion-type CPU/GPU hybrid architecture, wherein a single GPU implemented on the same die as the CPU is used to support a graphics pipeline that drives an external display device. As shown, the motherboard supports the processor die, memory, a bridge with a display interface for connecting to a display device 106, and a PCI-express bus. As shown, the processor die supports a CPU 1241, a GPU 1242, L2 cache, buffers, an Interconnect (e.g. crossbar switch), a hyper transport mechanism and a memory controller.

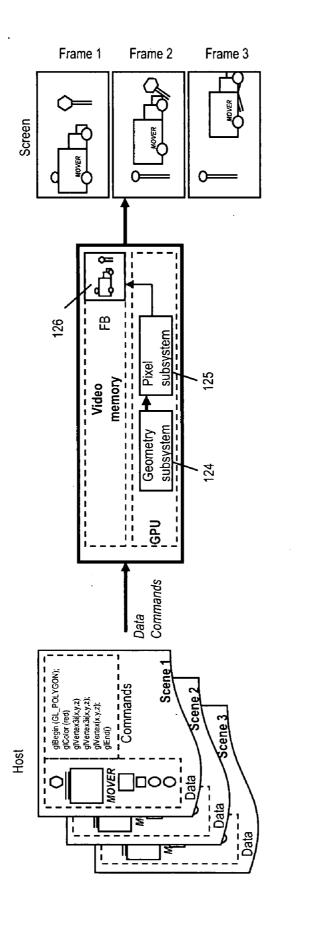

[0012] As shown in FIG. 1C, the process of rendering three successive frames by a single GPU is graphically illustrated. Notably, this graphical rendering process may be supported using any of the single GPU-based computing systems described above. During operation, the application, assisted by the graphics library, creates a stream of graphics commands and data describing a 3D scene. The stream is then pipelined through the GPU's geometry and pixel subsystems so as to create a bitmap of pixels in the Frame Buffer, and finally a rendered image of the scene is displayed on a display screen. The generation of a sequence of successive frames produces a visual illusion of a dynamic picture.

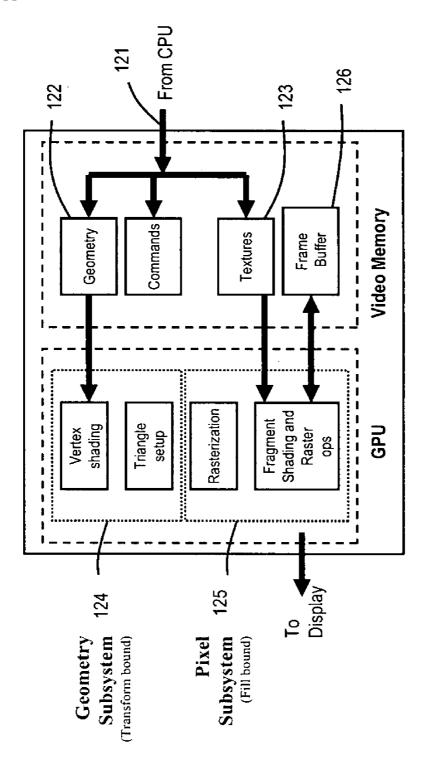

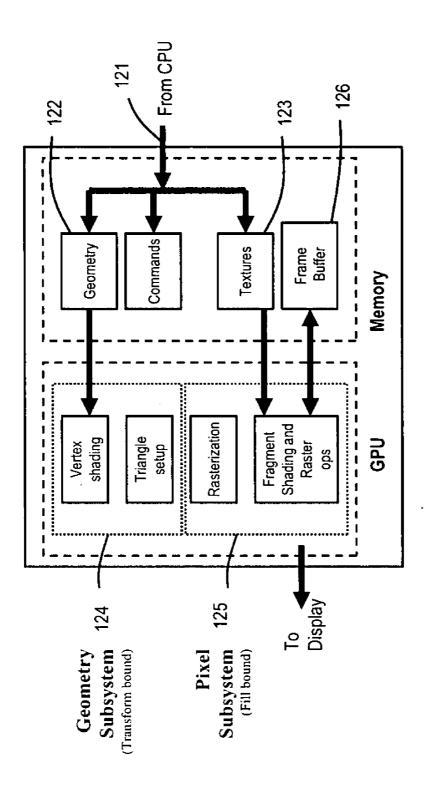

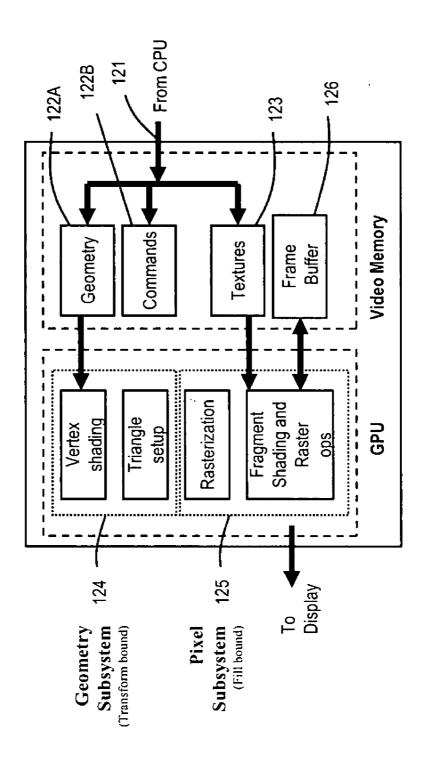

[0013] While the performance of single-GPU powered computing systems have greatly improved in As shown in FIG. 1B5, the structure of a GPU subsystem 124 on a graphics card or in an IGD comprises: a video memory which is external to GPU, and two 3D engines: (i) a transform bound geometry subsystem 224 for processing 3D graphics primitives; (ii) and a fill bound pixel subsystem 225. The video memory shares its storage resources among geometry buffer 222 through which all geometric (i.e. polygonal) data is transferred, commands buffer, texture buffers 223, and Frame Buffer 226.

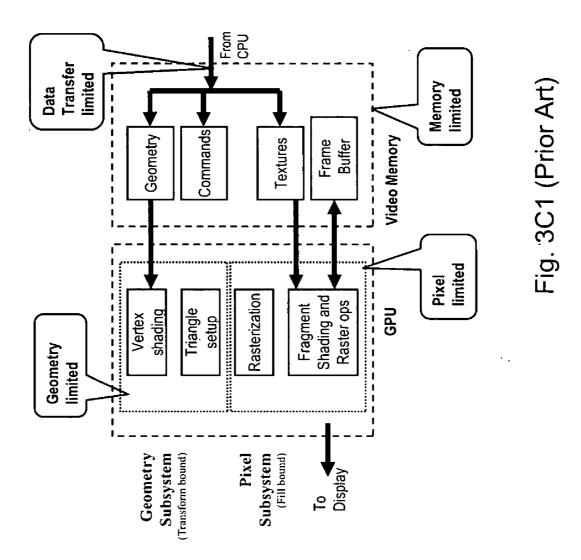

[0014] Limitations of a single graphics pipeline arise from its typical bottlenecks. The first potential bottleneck 221 stems from transferring data from CPU to GPU. Two other bottlenecks are video memory related: geometry data memory limits 222, and texture data memory limits 223. There are two additional bottlenecks inside the GPU: transform bound 224 in the geometry subsystem, and fragment rendering 225 in pixel subsystem. These bottlenecks determine overall throughput. In general, the bottlenecks vary over the course of a graphics application.

[0015] In high-performance graphics applications, the number of computations required to render a 3D scene and produce high-resolution graphical projections, greatly exceeds the capabilities of systems employing a single GPU graphics subsystem. Consequently, the use of parallel graphics pipelines, and multiple graphics processing units (GPUs), have become the rule for high-performance graphics system architecture and design, in order to relieve the overload presented by the different bottlenecks associated with single GPU graphics subsystems.

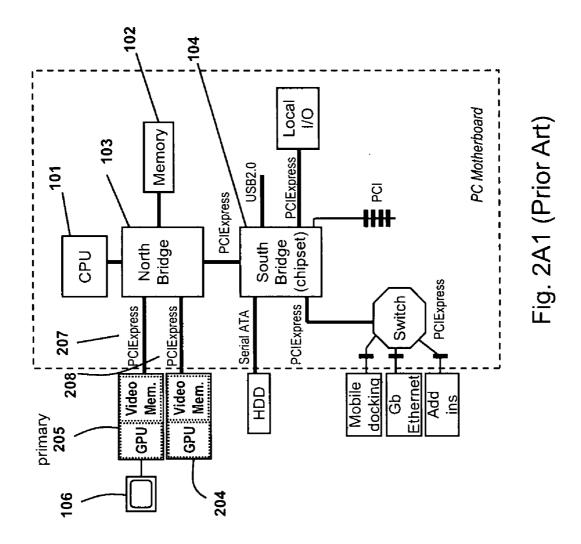

[0016] In FIG. 2A, there is shown an advanced chipset (e.g. Bearlake by Intel) having two buses 107, 108 instead of one, and allowing the interconnection of two external graphics cards in parallel: primary card 105 and secondary card 104, to share the computation load associated with the 3D graphics rendering process. As shown, the display 106 is attached to the primary card 105. It is anticipated that even more advanced commercial chipsets with greater than two buses will appear in the future, allowing the interconnection of more than two graphic cards.

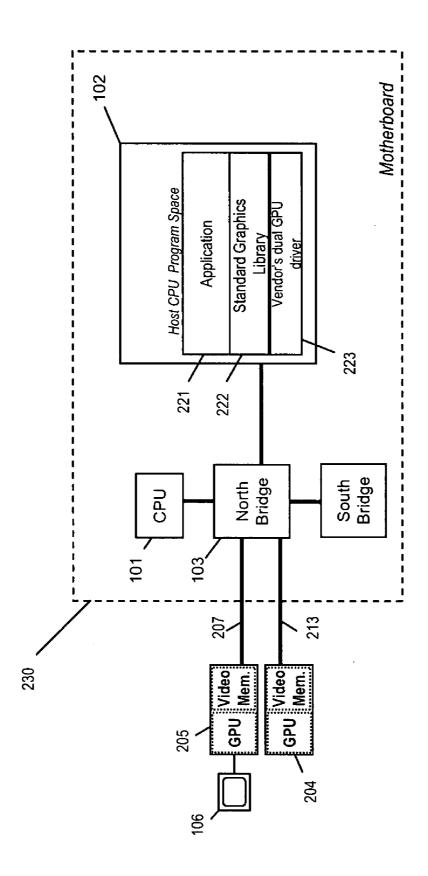

[0017] As shown in FIG. 2B, the general software architecture of prior art graphic system 200 comprises: the graphics application 201, standard graphics library 202, and the vendor's GPU drivers (203). This graphic software environment resides in the "program space" of main memory 102 on the host computer system. As shown, the graphic application 201 runs in the program space (i.e. memory space), building up the 3D scene, typically as a data base of polygons, where each polygon is represented as a set of vertices. The vertices and others components of these polygons are transferred to the graphic card(s) for rendering, and displayed as a 2D image, on the display screen.

[0018] In FIG. 2C, the structure of a GPU subsystem on the graphics card is shown comprising: a video memory disposed external to the GPU, and two 3D engines: (i) a transform bound geometry subsystem 224 for processing 3D graphics primitives; and (ii) a fill bound pixel subsystem 225. The video memory shares its storage resources among geometry buffer 222, through which all geometric (i.e. polygonal) data is transferred to the commands buffer, texture buffers 223, and Frame Buffer FB 226.

[0019] As shown in FIG. 2C, the division of graphics data among GPUs reduces (i) the bottleneck 222 posed by the video memory footprint at each GPU, (ii) the transform bound processing bottleneck 224, and (iii) the fill bound processing bottleneck 225.

[0020] However, when using a multiple GPU graphics architecture of the type shown in FIGS. 2A through 2C, there is a need to distribute the computational workload associated with interactive parallel graphics rendering processes. To achieve this objective, two different kind of parallel rendering methods have been applied to PC-based dual GPU graphics systems of the kind illustrated in FIGS. 2A through 2C, namely: the Time Division Method of Parallel Graphics Rendering illustrated in FIG. 2D; and the Image Division Method of Parallel Graphics Rendering illustrated in FIG. 2E.

[0021] Notably, a third type of method of parallel graphics rendering, referred to as the Object Division Method, has been developed over the years and practiced exclusively on complex computing platforms requiring complex and

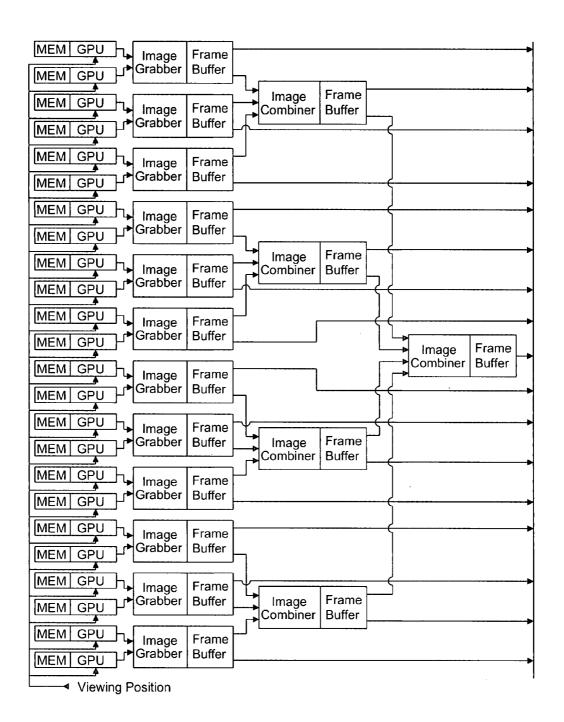

expensive hardware platforms for compositing the pixel output of the multiple graphics processing pipelines (GPPLs). The Object Division Method, illustrated in FIG. 3A, can be found applied on conventional graphics platforms of the kind shown in FIG. 3, as well as on specialized graphics computing platforms as described in US Patent Application Publication No. US 2002/0015055, assigned to Silicon Graphics, Inc. (SGI), published on Feb. 7, 2002, and incorporated herein by reference.

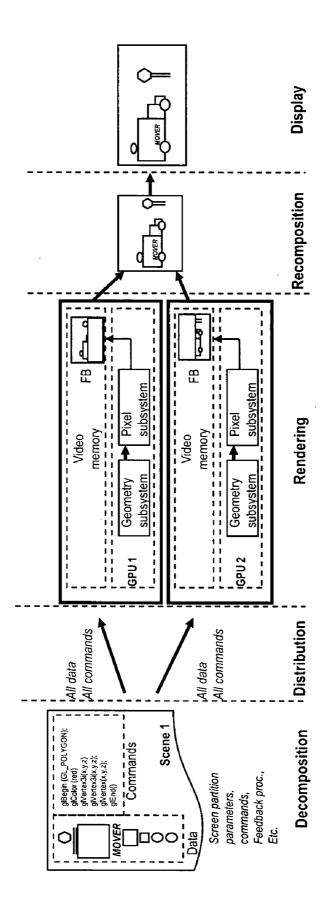

[0022] While the differences between the Image, Frame and Object Division Methods of Parallel Graphics Rendering will be described below, it will be helpful to first briefly describe the five (5) basic stages or phases of the parallel graphics rendering process, which all three such methods of parallel rendering have in common, namely:

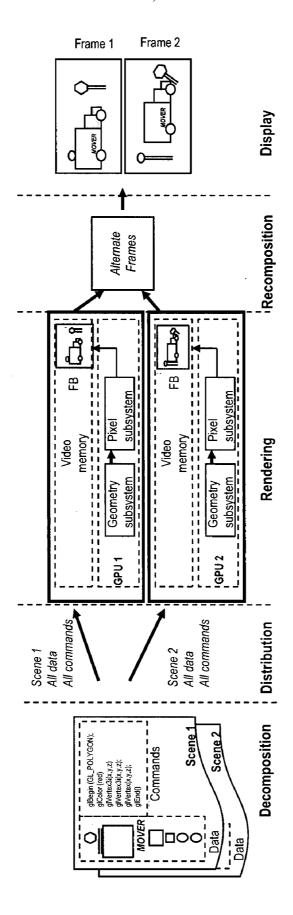

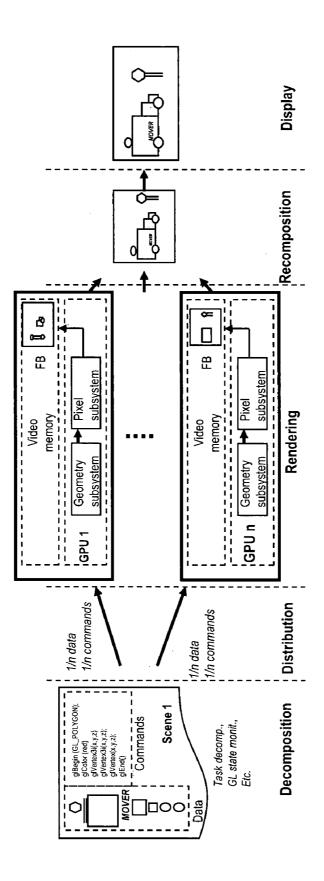

[0023] (1) the Decomposition Phase, wherein the 3D scene or object is analyzed and its corresponding graphics display list data and commands are assigned to particular graphics pipelines available on the parallel multiple GPU-based graphics platform;

[0024] (2) the Distribution Phase, wherein the graphics data and commands are distributed to particular available graphics processing pipelines determined during the Decomposition Phase;

[0025] (3) the Rendering Phase, wherein the geometry processing subsystem/engine and the pixel processing subsystem/engine along each graphics processing pipeline of the parallel graphics platform uses the graphics data and commands distributed to its pipeline, and transforms (i.e. projects, shades and colors) the graphics objects and bitmapped textures into a subset of unstructured matrix of pixels;

[0026] (4) the Recomposition Phase, wherein the parallel graphics platform uses the multiple sets of pixel data generated by each graphics pipeline to synthesize (or compose) a final set of pixels that are representative of the 3D scene (taken along the specified viewing direction), and this final set of pixel data is then stored in a frame buffer (FB); and

[0027] (5) the Display Phase, wherein the final set of pixel data retrieved from the frame buffer, and provided to the screen of the device device of the system.

[0028] As will be explained below with reference to FIGS. 3B through 3D, each of these three different methods of parallel graphics rendering has both advantages and disadvantages.

Image Division Method of Parallel Graphics Rendering

[0029] As illustrated in FIG. 2D, the Image Division (Sort-First) Method of Parallel Graphics Rendering distributes all graphics display list data and commands to each of the graphics pipelines, and decomposes the final view (i.e. projected 2D image) in Screen Space, so that, each graphical contributor (e.g. graphics pipeline and GPU) renders a 2D tile of the final view. This mode has a limited scalability due to the parallel overhead caused by objects rendered on multiple tiles. There are two image domain modes, all well known in prior art. They differ by the way the final image is divided among GPUs.

[0030] (1) The Split Frame Rendering mode divides up the screen among GPUs by continuous segments. e.g. two GPUs

each one handles about one half of the screen. The exact division may change dynamically due to changing load across the screen image. This method is used in nVidia's SLI<sup>TM</sup> multiple-GPU graphics product.

[0031] (2) Tiled Frame Rendering mode divides up the image into small tiles. Each GPU is assigned tiles that are spread out across the screen, contributing to good load balancing. This method is implemented by ATI's Crossfire<sup>TM</sup> multiple GPU graphics card solution.

[0032] In image division, the entire database is broadcast to each GPU for geometric processing. However, the processing load at each Pixel Subsystem is reduced to about 1/N. This way of parallelism relieves the fill bound bottleneck 225. Thus, the image division method ideally suits graphics applications requiring intensive pixel processing.

Time Division (DPlex) Method of Parallel Graphics Rendering

[0033] As illustrated in FIG. 2F, the Time Division (DPlex) Method of Parallel Graphics Rendering distributes all display list graphics data and commands associated with a first scene to the first graphics pipeline, and all graphics display list data and commands associated with a second/ subsequent scene to the second graphics pipeline, so that each graphics pipeline (and its individual rendering node or GPU) handles the processing of a full, alternating image frame. Notably, while this method scales very well, the latency between user input and final display increases with scale, which is often irritating for the user. Each GPU is give extra time of N time frames (for N parallel GPUs) to process a frame. Referring to FIG. 3, the released bottlenecks are those of transform bound 224 at geometry subsystem, and fill bound 225 at pixel subsystem. Though, with large data sets, each GPU must access all of the data. This requires either maintaining multiple copies of large data sets or creating possible access conflicts to the source copy at the host swelling up the video memory bottlenecks 222, 223 and data transfer bottleneck 221.

Object Division (Sort-Last) Method of Parallel Graphics Rendering

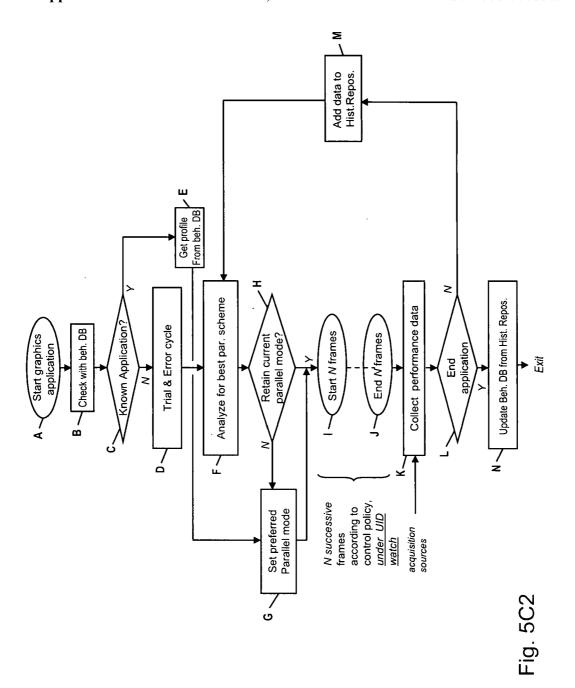

[0034] As illustrated in FIG. 3B, the Object Division (Sort-Last) Method of Parallel Graphics Rendering decomposes the 3D scene (i.e. rendered database) and distributes graphics display list data and commands associated with a portion of the scene to the particular graphics pipeline (i.e. rendering unit), and recombines the partially rendered pixel frames, during recomposition. The geometric database is therefore shared among GPUs, reducing the load on the geometry buffer, the geometry subsystem, and even to some extent, the pixel subsystem. The main concern is how to divide the data in order to keep load balance. An exemplary multiple-GPU platform of FIG. 3B for supporting the object-division method is shown in FIG. 3A. The platform requires complex and costly pixel compositing hardware which prevents its current application in a modern PC-based computer architecture.

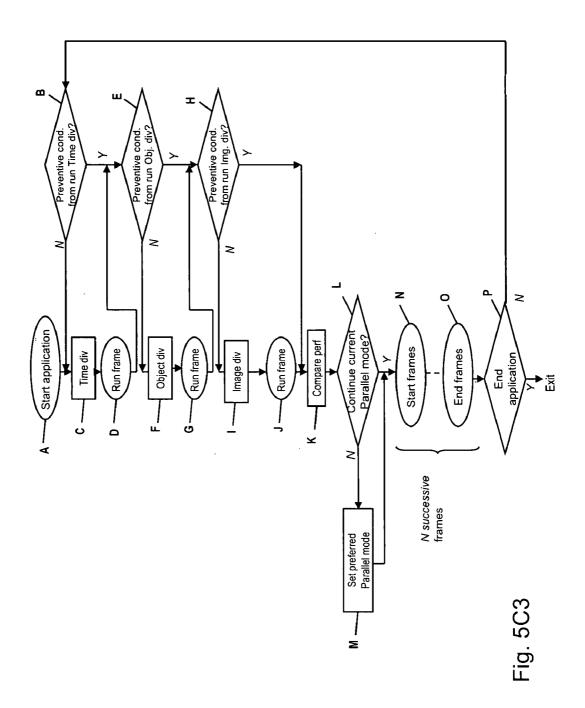

[0035] Today, real-time graphics applications, such as advanced video games, are more demanding than ever, utilizing massive textures, abundance of polygons, high depth-complexity, anti-aliasing, multi-pass rendering, etc., with such robustness growing exponentially over time.

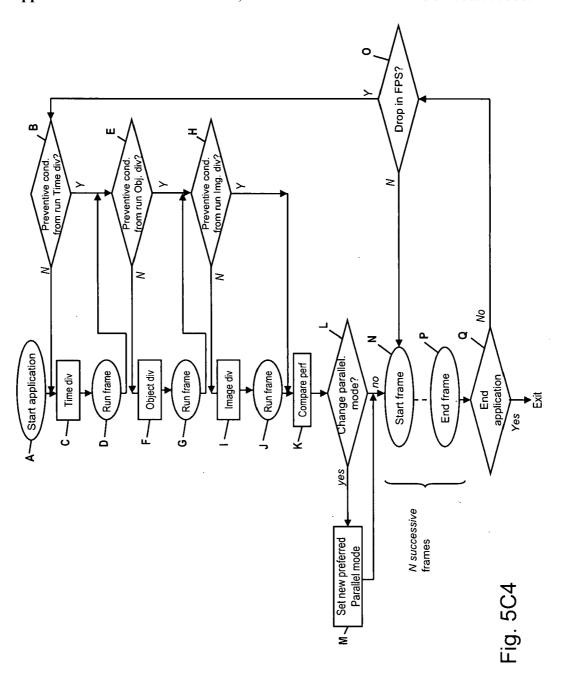

[0036] Conventional PC-level dual-mode parallel graphics systems employing multiple-GPUs, such as nVidia's SLI<sup>TM</sup> multiple-GPU graphics platform, support either the Time Division Mode (termed Alternate Frame Rendering) of parallelism, or the Image Division Mode (termed Split Frame Rendering) of parallelism, which is automatically selected during application set-up (e.g. by the vendor's driver). However, once a graphics-based application is set-up and the time or image division mode of parallel operation selected, the selected mode of parallel operation is fixed during application run-time.

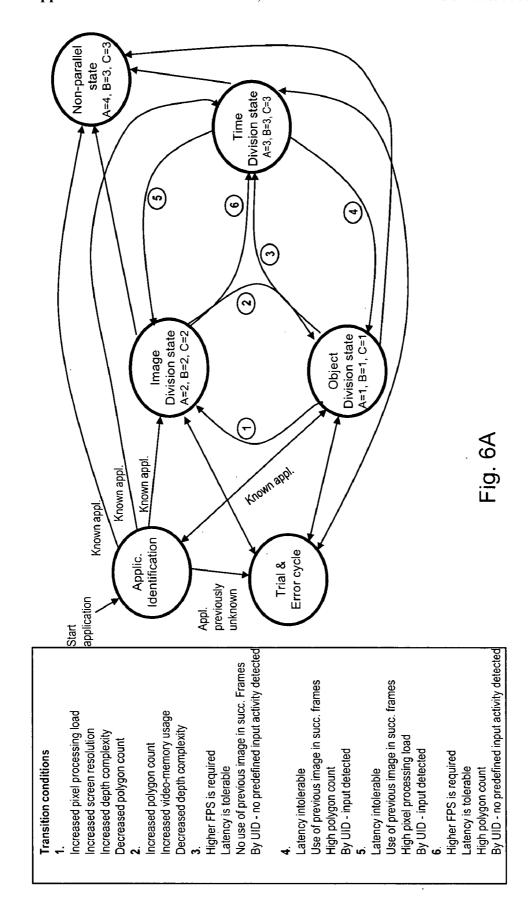

[0037] Clearly, conventional PC-based graphics systems fail to address the dynamically changing needs of modern graphics applications. By their very nature, prior art PC-based graphics systems are unable to resolve the variety of bottlenecks (e.g. geometry limited, pixel limited, data transfer limited, and memory limited) summarized in FIG. 3C1, that dynamically arise along 3D graphic pipelines. Consequently, such prior art graphics systems are often unable to maintain a high and steady level of performance throughout a particular graphics application.

[0038] Indeed, a given graphics processing pipeline along a parallel graphics rendering system is only as strong as the weakest link of it stages, and thus a single bottleneck determines the overall throughput along the graphics pipelines, resulting in unstable frame-rate, poor scalability, and poor performance.

[0039] And while each parallelization mode described above and summarized in FIG. 3C2 solves only part of the bottleneck dilemma currently existing along the PC-based graphics pipelines, no one parallelization method, in and of itself, is sufficient to resolve all bottlenecks in demanding graphics applications, and enable quantum leaps in graphics performance necessary for photo-realistic imagery demanded in real-time interactive graphics environments.

[0040] Thus, there is a great need in the art for a new and improved way of and means for practicing parallel 3D graphics rendering processes in modern multiple-GPU based computer graphics systems, while avoiding the shortcomings and drawbacks of such prior art methodologies and apparatus.

### SUMMARY AND OBJECTS OF THE PRESENT INVENTION

[0041] Accordingly, a primary object of the present invention is to provide a new and improved method of and apparatus for practicing parallel 3D graphics rendering processes in modern multiple-GPU based computer graphics systems, while avoiding the shortcomings and drawbacks associated with prior art apparatus and methodologies.

[0042] Another object of the present invention is to provide a novel multi-mode parallel graphics rendering system (MMPGRS) embodied within a host computing system having (i) host memory space (HMS) for storing one or more graphics-based applications and a graphics library for generating graphics commands and data (GCAD) during the run-time (i.e. execution) of the graphics-based application, (ii) one or more CPUs for executing said graphics-based applications, and (iii) a display device for displaying images containing graphics during the execution of said graphics-based applications.

[0043] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system comprising: a multi-mode parallel graphics rendering subsystem supporting multiple modes of parallel operation selected from the group consisting of object division, image division, and time division; a plurality of graphic processing pipelines (GPPLs) supporting a parallel graphics rendering process that employs one of the object division, image division and/or time division modes of parallel operation in order to execute graphic commands and process graphics data (GCAD) render pixel-composited images containing graphics for display on a display device during the run-time of the graphics-based application; and an automatic mode control module (AMCM) for automatically controlling the mode of parallel operation during the run-time of the graphics-based application.

[0044] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the automatic mode control module employs the profiling of scenes in said graphics-based application.

[0045] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the automatic mode control module employs the profiling of scenes in the graphics-based application, on an image frame by image frame basis.

[0046] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the profiling of scenes in the graphics-based application, is carried out in real-time, during run-time of the graphics-based application, on an image frame by image frame basis.

[0047] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein said real-time profiling of scenes in the graphics-based application involves (i) collecting and analyzing performance data associated with the MMPGRS and the host computing system, during application run-time, (ii) constructing scene profiles for the image frames associated with particular scenes in the particular graphics-based application, and (iii) maintaining the scene profiles in a application/scene profile database that is accessible to the automatic mode control module during run-time, so that during the run-time of the graphics-based application, the automatic mode control module can access and use the scene profiles maintained in the application/scene profile database and determine how to dynamically control the modes of parallel operation of the MMPGRS to optimize system performance.

[0048] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the automatic mode control module employs real-time detection of scene profile indices directly programmed within pre-profiled scenes of the graphics-based application; wherein the pre-profiled scenes are analyzed prior to run-time, and indexed with the scene profile indices; and wherein and mode control parameters (MCPs) corresponding to the scene profile indices, are stored within an application/scene profile database accessible to the automatic mode control module during application run-time.

[0049] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and

display system, wherein during run-time, the automatic mode control module automatically detects the scene profile indices and uses the detected said scene profile indices to access corresponding MCPs from the application/scene profile database so as to determine how to dynamically control the modes of parallel operation of the MMPGRS to optimize system performance.

[0050] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the automatic mode control module employs real-time detection of mode control commands (MCCs) directly programmed within pre-profiled scenes of the graphics-based application; wherein the pre-profiled scenes are analyzed prior to run-time, and the MCCs are directly programmed within the individual image frames of each scene; and wherein during run-time, the automatic mode control module automatically detects the MCCs along the graphics command and data stream, and uses the MCCs so as to determine how to dynamically control the modes of parallel operation of the MMPGRS to optimize system performance.

[0051] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein the automatic mode control module employs a user interaction detection (UID) mechanism for real-time detection of the user's interaction with the host computing system.

[0052] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, wherein, in conjunction with scene profiling, the automatic mode control module also uses said UID mechanism to determine how to dynamically control the modes of parallel operation of the MMPGRS to optimize system performance, at any instance in time during run-time of the graphics-based application.

[0053] Another object of the present invention is to provide a multi-mode parallel graphics rendering system (MMPGRS), having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having time, frame and object division modes of operation, wherein each GPPL comprises video memory and a GPU having a geometry processing subsystem and a pixel processing subsystem, and wherein 3D scene profiling is performed in real-time, and the parallelization state/mode of the system is dynamically controlled to meet graphics application requirements.

[0054] Another object of the present invention is to provide a multi-mode parallel graphics rendering and display system having multiple graphics processing pipelines (GPPLs), each having a GPU and video memory, and supporting multiple modes of parallel graphics rendering using real-time graphics application profiling and automatic configuration of the multiple graphics processing pipelines supporting multiple modes of parallel graphics rendering, including a time-division mode, a frame-division mode, and an object-division mode of parallel operation.

[0055] Another object of the present invention is to provide such a multi-mode parallel graphics rendering and display system, which is capable of dynamically handling bottlenecks that are automatically detected during any particular graphics application running on the host computing system.

[0056] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, wherein different parallelization schemes are employed to reduce pipeline bottlenecks, and increase graphics performance.

[0057] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, wherein image, time and object division methods of parallelization are implemented on the same parallel graphics platform.

[0058] Another object of the present invention is to provide a method of multi-mode parallel graphics rendering that can be practiced on a multiple GPU-based PC-level graphics system, and which, during application run-time, dynamically alternates among Time, Frame/image and Object division modes of parallel operation, adapting the optimal method of parallel operation to the real time needs of the graphics application.

[0059] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, which is capable of supervising the performance level of a graphic application by dynamically adapting different parallelization schemes to solve instantaneous bottlenecks along the graphic pipelines thereof.

[0060] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, having run-time configuration flexibility for various parallel schemes to achieve the best system performance.

[0061] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system having architectural flexibility and real-time profiling and control capabilities which enable utilization of different modes of parallel operation for high and steady performance along the application running on the associated host system.

[0062] Another object of the present invention is to provide a novel method of multi-mode parallel graphics rendering on a multiple GPU-based graphics system, which achieves improved system performance by using adaptive parallelization of multiple graphics processing units (GPUs), on conventional and non-conventional platform architectures, as well as on monolithic platforms, such as multiple GPU chips or integrated graphic devices (IGD).

[0063] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, wherein bottlenecks are dynamically handled.

[0064] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, wherein stable performance is maintained throughout course of a graphics application.

[0065] Another object of the present invention to provide a multi-mode parallel graphics rendering system supporting software-based adaptive graphics parallelism for the best performance, seamlessly to the graphics application, and compliant with graphic standards (e.g. OpenGL and Direct3D).

[0066] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, wherein all parallel modes are implemented in a single architecture.

[0067] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, wherein the architecture is flexible, supporting fast intermode transitions.

[0068] Another object of the present invention is to provide a multi-mode parallel graphics rendering system which is adaptive to changing to meet the needs of any graphics application during the course of its operation.

[0069] Another object of the present invention is to provide a multi-mode parallel graphics rendering system which employs a user interaction detection (UID) subsystem for enabling the automatic and dynamic detection of the user's interaction with the host computing system.

[0070] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system, continuously processes user-system interaction data, and automatically detects user-system interactivity (e.g. mouse click, keyboard depression, eye-movement, etc).

[0071] Another object of the present invention is to provide such a multi-mode parallel graphics rendering system the system, wherein absent preventive conditions (such as CPU bottlenecks and need for the same FB in successive frames), the user interaction detection (UID) subsystem enables timely implementation of the Time Division Mode only when no user-system interactivity is detected so that system performance is automatically optimized.

[0072] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be implemented using a software implementation of present invention.

[0073] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be realized using a hardware implementation.

[0074] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, can be realized as chip implementation.

[0075] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be realized as an integrated monolithic implementation.

[0076] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be implemented using IGD technology.

[0077] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, characterized by run-time configuration flexibility for various parallel schemes to achieve the best parallel performance.

[0078] Another object of the present invention is to provide a multi-mode parallel graphics rendering system that operates seamlessly to the application and is compliant with graphic standards (e.g. OpenGL and Direct3D).

[0079] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be implemented on conventional multi-GPU platforms replacing image division or time division parallelism.

[0080] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which enables the multiple GPU platform vendors to incorporate

the solution in their systems supporting only image division and time division modes of operation.

[0081] Another object of the present invention is to provide such multiple GPU-based graphics system, which enables implementation using low cost multi-GPU cards.

[0082] Another object of the present invention is to provide a multi-mode parallel graphics rendering system implemented using IGD technology, and wherein it is impossible for the IGD to get disconnected by the BIOS when an external graphics card is connected and operating.

[0083] Another object of the present invention is to provide a multiple GPU-based graphics system, wherein a new method of dynamically controlled parallelism improves the system's efficiency and performance.

[0084] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be implemented using an IGD supporting more than one external GPU.

[0085] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which can be implemented using an IGD-based chipset having two or more IGDs.

[0086] Another object of the present invention is to provide a multi-mode parallel graphics rendering system, which employs a user interaction detection (UID) subsystem that enables automatic and dynamic detection of the user's interaction with the system, so that absent preventive conditions (such as CPU bottlenecks and need for the same FB in successive frames), this subsystem enables timely implementation of the Time Division Mode only when no user-system interactivity is detected, thereby achieving the highest performance mode of parallel graphics rendering at runtime, and automatically optimizing the graphics performance of the host computing system.

[0087] Another object of the present invention is to provide a parallel graphics rendering system employing multiple graphics processing pipelines supporting the object division mode of parallel graphics rendering using pixel processing resources provided therewithin.

[0088] Another object of the present invention is to provide a parallel graphics rendering system for carrying out the object division method of parallel graphics rendering on multiple GPU-based graphics platforms associated with diverse types of computing machinery.

[0089] Another object of the present invention is to provide a novel method having multiple graphics processing pipelines (GPPLs) with multiple GPUs or CPU-cores supporting a parallel graphics rendering process having an object division mode of operation, wherein each GPPL includes video memory, a geometry processing subsystem, and a pixel processing subsystem, wherein pixel (color and z depth) data buffered in the video memory of each GPPL is communicated to the video memory of a primary GPPL, and wherein the video memory and the pixel processing subsystem in the primary GPPL are used to carry out the image recomposition phase of the object division mode of parallel graphics rendering process.

[0090] Another object of the present invention is to provide a parallel graphics rendering system having multiple

graphics processing pipelines (GPPLs) with multiple GPUs or CPU-cores supporting a parallel graphics rendering process having an object division mode of operation, wherein each GPU comprises video memory, a geometry processing subsystem and a pixel processing subsystem, wherein pixel (color and z depth) data buffered in the video memory of each GPPL is communicated to the video memory of a primary GPPL, and wherein the video memory and the pixel processing subsystem in the primary GPPL are used to carry out the image recomposition phase of the object division mode of the parallel graphics rendering process.

[0091] Another object of the present invention is to provide a parallel graphics rendering system having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having an object division mode of operation, wherein each GPU comprises video memory, a geometry processing subsystem and a pixel processing subsystem, wherein pixel (color and z depth) data buffered in the video memory of each GPU is communicated to the video memory of a primary GPU, and wherein the video memory and both the geometry and pixel processing subsystems in the primary GPU are used to carry out the image recomposition phase of the object division mode of parallel graphics rendering process.

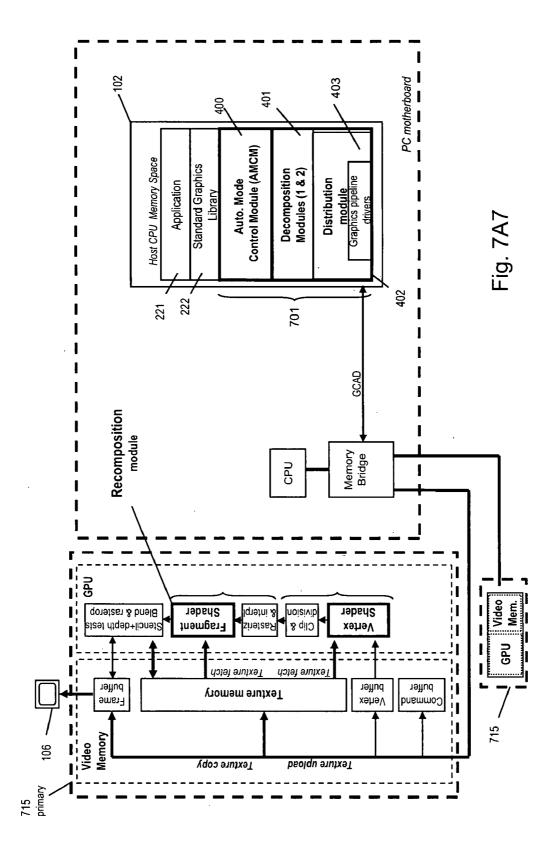

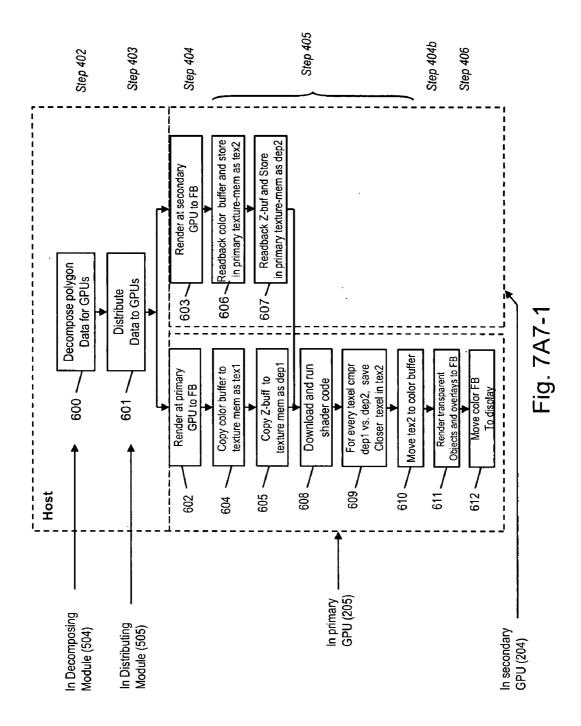

[0092] Another object of the present invention is to provide a parallel rendering graphics system having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having an object division mode of operation, wherein the video memory of each GPPL includes texture memory and a pixel frame buffer, wherein the geometry processing subsystem includes a vertex shading unit, wherein the pixel processing subsystem includes a fragment/pixel shading unit, wherein pixel (color and z depth) data buffered in the video memory of each GPPL is communicated to the video memory of a primary GPPL, and wherein the texture memory and the fragment/pixel shading unit are used to carry out the image recomposition phase of the object division mode of the parallel graphics rendering process.

[0093] Another object of the present invention is to provide a parallel graphics rendering system having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having an object division mode of operation, wherein the video memory of each GPPL includes texture memory and a pixel frame buffer, wherein the geometry processing subsystem includes a vertex shading unit, wherein the pixel processing subsystem includes a fragment/pixel shading unit, wherein pixel (color and z depth) data buffered in the video memory of each GPPL is communicated to the video memory of a primary GPPL, and wherein the texture memory and the vertex shading unit are used to carry out the image recomposition phase of the object division mode of the parallel graphics rendering process.

[0094] Another object of the present invention is to provide a parallel graphics rendering system having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having an object division mode of operation, which does not require compositing in main, shared or distributed memory of the host computing system (e.g. involving the movement of pixel data from the frame buffers or FBs to main memory,

processing the pixel data in the CPU of the host for composition, and moving the result out to the primary GPPL for display) thereby avoiding the use of expensive procedure and resources of the system (e.g. buses, caches, memory, and CPU bandwidth).

[0095] Another object of the present invention is to provide a novel method of operating a parallel graphics rendering system having multiple graphics processing pipelines (GPPLs) with multiple GPUs supporting a parallel graphics rendering process having an object division mode of operation, wherein implementation of the pixel composition phase of the parallel graphics rendering process is carried out using the computational resources within the GPUs, thereby avoiding the need for dedicated or specialized pixel image compositing hardware and/or software based apparatus.

[0096] Another object of the present invention is to provide a novel method of object division parallel graphics rendering carried out on a multi-mode parallel graphics rendering system (MMPGRS) or platform supporting multiple graphical processing pipelines (GPPLs) with multiple graphical processing units (GPUs), wherein the recomposition stage of the rendering process is carried out using computational resources (e.g. video memory and the geometry and/or pixel processing subsystems/engines) supplied by the GPPLs employed on the MMPGRS platform.

[0097] Another object of the present invention is to provide a novel method of object division parallel rendering of pixel-composited images for graphics-based applications running on a host computing system embodying a multimode parallel graphics rendering system or platform (MMPGRS), wherein the movement and merging of composited pixel data occurs during the recomposition stage of the parallel graphics rendering process in a manner that is transparent to the graphics-based application.

[0098] Another object of the present invention is to provide a novel parallel rendering graphics system having multiple graphics processing pipelines (GPPLs) supporting a parallel graphics rendering process having an object division mode of operation, wherein each GPPL comprises video memory, a geometry processing subsystem and a pixel processing subsystem, wherein pixel (color and z depth) data buffered in the video memory of each GPPL is communicated (via an inter-GPPL communication process) to the video memory of a primary GPPL, and wherein the video memory and the geometry and/or pixel processing subsystems in the primary GPPL are used to carry out the image recomposition phase of the object division mode of the parallel graphics rendering process.

[0099] Another object of the present invention is to provide a novel parallel graphics rendering system supporting multiple modes of parallel operation during graphical rendering which allows users to enjoy sharp videos and photos, smooth video playback, astonishing effects, and vibrant colors, as well as texture-rich 3D performance in next-generation games.

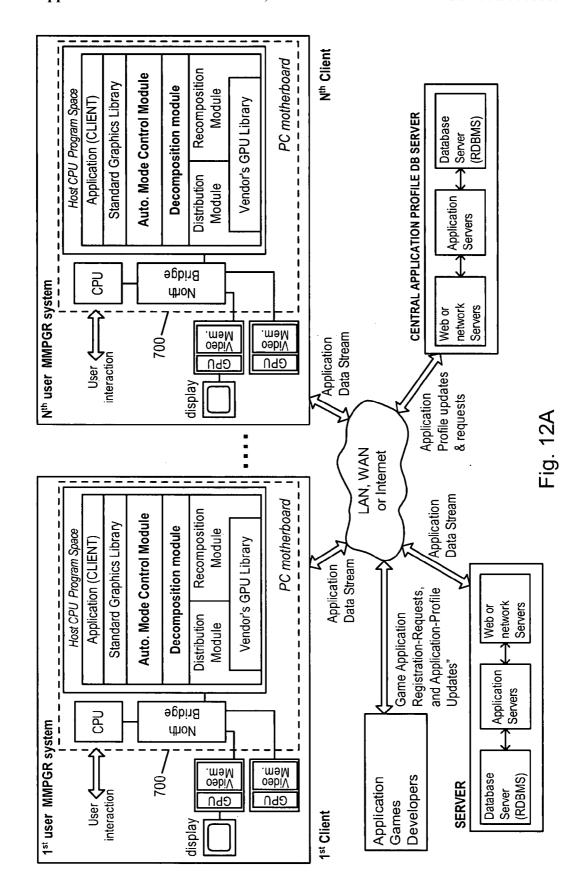

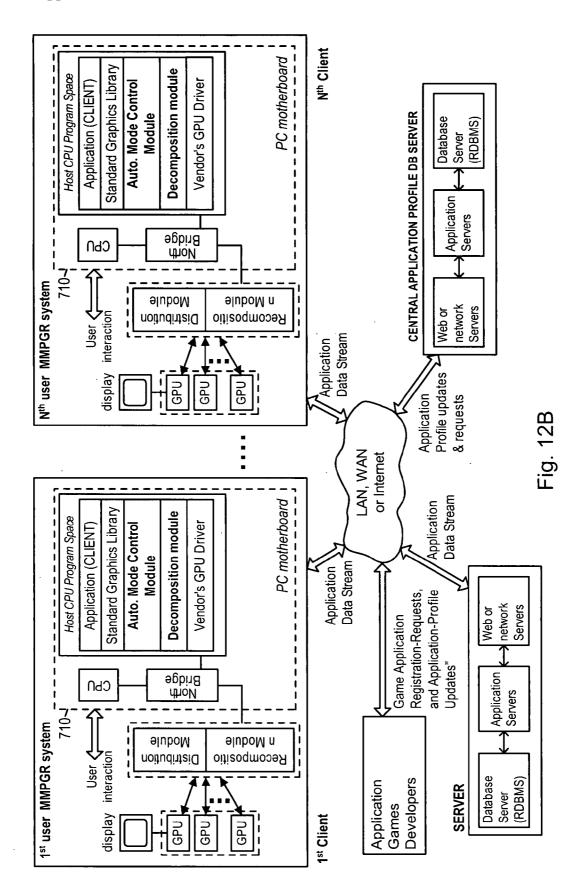

[0100] Another object of the present invention is to provide a novel multi-user computer network supporting a plurality of client machines, wherein each client machine employs the MMPGRS of the present invention based on a software architecture and responds to user-interaction input data streams from one or more network users who might be

local to each other as over a LAN, or be remote to each other, as when operating over a WAN or the Internet infrastructure.

[0101] Another object of the present invention is to provide a novel multi-user computer network supporting a plurality of client machines, wherein each client machine employs the MMPGRS of the present invention based on a hardware architecture and responds to user-interaction input data streams from one or more network users who might be local to each other as over a LAN, or be remote to each other, as when operating over a WAN or the Internet infrastructure.

[0102] Another object of the present invention is to provide an Internet-based central application profile database server system for automatically updating, over the Internet, graphic application profiles (GAPs) within the MMPGRS of client machines.

[0103] Another object of the present invention is to provide such Internet-based Central Application Profile Database Server System which ensures that each MMPGRS is optimally programmed at all possible times so that it quickly and continuously offers users high graphics performance through its adaptive multi-modal parallel graphics operation.

[0104] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System which supports a Web-based Game Application Registration and Profile Management Application, that provides a number of Web-based services, including:

[0105] (1) the registration of Game Application Developers within the RDBMS of the Server System;

[0106] (2) the registration of game applications with the RDBMS of the Central Application Profile Database Server System, by registered game application developers;

[0107] (3) the registration of each MMPGRS deployed on a client machine or server system having Internet-connectivity, and requesting subscription to periodic/automatic Graphic Application Profile (GAP) Updates (downloaded to the MMPGRS over the Internet) from the Central Application Profile Database Server System; and

[0108] (4) the registration of each deployed MMPGRS requesting the periodic uploading of its Game Application Profiles (GAPS)—stored in an Application/Scene Profile Database and Historical Repository—to the Central Application Profile Database Server System for the purpose of automated analysis and processing so as to formulate "expert" Game Application Profiles (GAPs) that have been based on robust user-experience and which are optimized for particular client machine configurations.

[0109] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System that enables the MMGPRS of registered client computing machines to automatically and periodically upload, over the Internet, Graphic Application Profiles (GAPs) for storage and use within the Application/Scene Profile Database of the MMPGRS.

[0110] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System which, by enabling the automatic uploading of expert GAPs into the MMPGRS, graphic application users (e.g. gamers) can immediately enjoy high

performance graphics on the display devices of their client machines, without having to develop a robust behavioral profile based on many hours of actual user-system interaction

[0111] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System, wherein "expert" GAPs are automatically generated by the Central Application Profile Database Server System by analyzing the GAPs of thousands of different game application users connected to the Internet, and participating in the system.

[0112] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System, wherein for MMPGRS users subscribing to the Automatic GAP Management Services, each such MMPGRS runs an application profiling and control algorithm that uses the most recently uploaded expert GAP loaded into its automatic mode control mechanism (AMCM), and then allow system-user interaction, user behavior, and application performance to modify the expert GAP profile over time until the next update occurs.

[0113] Another object of the present invention is to provide such an Internet-based Central Application Profile Database Server System, wherein the Application Profiling and Analysis Module in each MMGPRS subscribing to the Automatic GAP Management Services supported by the Central Application Profile Database Server System of the present invention, modifies and improves the downloaded expert GAP within particularly set limits and constraints, and according to particular criteria, so that the expert GAP is allowed to evolve in an optimal manner, without performance regression.

[0114] These and other objects of the present invention will become apparent hereinafter and in the claims to invention.

## BRIEF DESCRIPTION OF DRAWINGS OF PRESENT INVENTION

[0115] For a more complete understanding of how to practice the Objects of the Present Invention, the following Detailed Description of the Illustrative Embodiments can be read in conjunction with the accompanying Drawings, briefly described below:

[0116] FIG. 1A1 is a graphical representation of a typical prior art PC-based computing system employing a conventional graphics architecture driving a single external graphic card 105;

[0117] FIG. 1A2 a graphical representation of a conventional GPU subsystem supported on the graphics card of the PC-based graphics system of FIG. 1A1;

[0118] FIG. 1A3 is a graphical representation illustrating the general software architecture of the prior art computing system shown in FIG. 1A2;

[0119] FIG. 1B1 is a graphical representation of a typical prior art PC-based computing system employing a conventional graphics architecture employing a North memory bridge circuit (i.e. semiconductor chip of monolithic construction) with an integrated graphics device (IGD) 103 supporting a single graphics pipeline process, and being

operably coupled to a South bridge circuit (i.e. semiconductor chip of monolithic construction) supporting the input/output ports of the system;

[0120] FIG. 1B2 is graphical representation of the North memory bridge employed in the system of FIG. 1B1, showing in greater detail the micro-architecture of the IGD supporting the single graphics pipeline process therewithin;

[0121] FIG. 1B3 is a graphical representation illustrating the general software architecture of the prior art PC-based IGD-driven computing system shown in FIGS. 1B1 and 1B2:

[0122] FIG. 1B4 is a graphical representation of a prior art PC-based computing system employing a conventional Fusion-type CPU/GPU hybrid architecture, wherein a single GPU 1242 implemented on the same semiconductor die as the CPU 1241 is used to support a graphics pipeline that drives an external display device, e.g. LCD panel, projection display or the like 106, via a bridge circuit, with display interface, as shown;

[0123] FIG. 1B5 is a schematic representation showing the structure of a prior art GPU subsystem mounted on a graphics card or in an IGD, and comprising a GPU, and a video memory which is external to the GPU, wherein the GPU has includes two 3D engines, namely, (i) a transform bound geometry subsystem 124 for processing 3D graphics primitives 121, and (ii) and a fill bound pixel subsystem 125, and wherein the video memory shares its storage resources among a geometry buffer 122A through which all geometric (i.e. polygonal) data 121 is transferred, a commands buffer 122B, texture buffers 123, and a Frame Buffer 126;

[0124] FIG. 1C is a graphical representation illustrating a conventional process for rendering successive 3D scenes using a single GPU graphics platform to support a single graphics pipeline process, as shown in FIGS. 1A1 through 1R5:

[0125] FIG. 2A1 is a graphical representation of a prior art PC-based computing system employing a conventional dual-GPU graphic architecture comprising two external graphic cards 205204 and two PCI-e buses, e.g. Bearlake by Intel 207, 208, wherein the primary and secondary graphics cards are connected to and driven by the North memory bridge circuit 103, while a display device 106 is attached to the primary graphics card 205, and Ethernet and mobile docking ports and other local I/O ports are driven by the South bridge circuit, as shown;

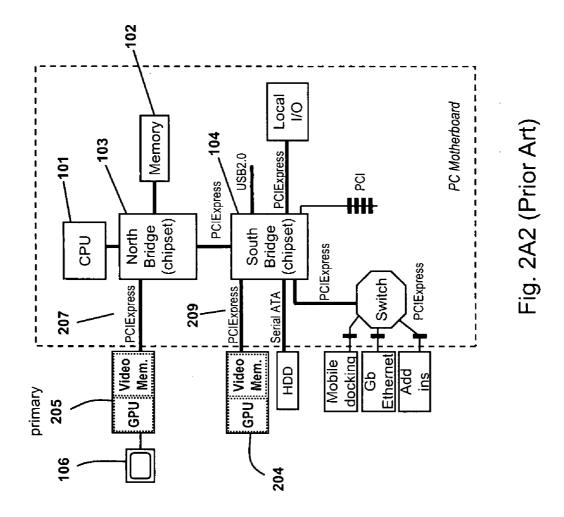

[0126] FIG. 2A2 is a graphical representation of a prior art PC-based computing system employing a conventional dual-GPU graphic architecture comprising two external graphic cards 204, 205 and two PCI-e buses (e.g. Bearlake by Intel), wherein the primary graphics card 205 is connected to and driven by the North memory bridge via the first PCI-e bus with a display device 106 is attached to the primary graphics card 205, and wherein the secondary graphics card 204 is connected to and driven by the South bridge via the second PCI-e bus;

[0127] FIG. 2A3 is a graphical representation of a conventional GPU subsystem supported on each of the graphics cards employed in the prior art PC-based computing systems of FIGS. 2A1 and 2A2;

[0128] FIG. 2A4 is a graphical representation illustrating the general software architecture of the prior art PC-based graphics systems shown in FIG. 2A1, as well as FIG. 2A2;

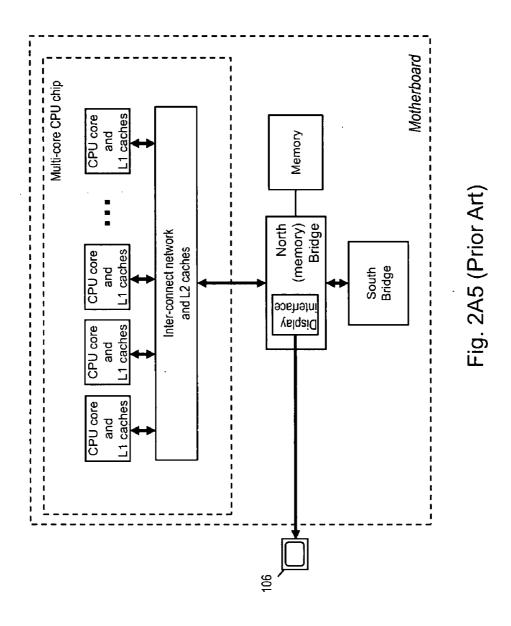

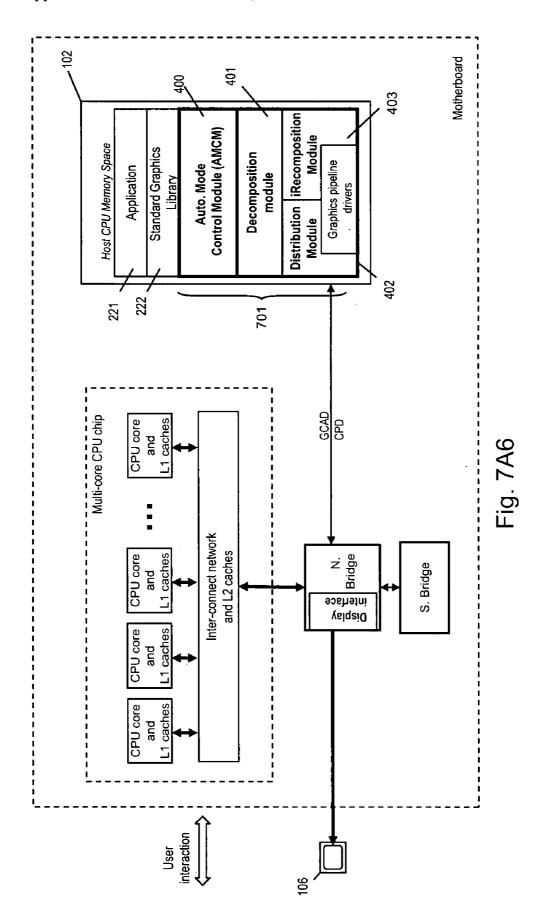

[0129] FIG. 2A5 is a graphical representation of a prior art PC-based computing system employing a conventional multi-core microprocessor (CPU) chip to implement multiple processing cores in a single physical package, wherein some of the cores can be potentially used as soft graphic graphics pipelines, and wherein a display device 106 is connected to and driven by the North (memory) bridge chip on the motherboard;

[0130] FIG. 2B is a graphical representation of a conventional parallel graphics rendering process being carried out according to the Image Division Method of parallelism using the dual GPUs provided on the prior art graphics platform illustrated in FIGS. 2A1 through 2A3;

[0131] FIG. 2C is a graphical representation of a conventional parallel graphics rendering process being carried out according to the Time Division Method of parallelism using the dual GPUs provided on the prior art graphics platforms illustrated in FIGS. 2A1 through 2A5;

[0132] FIG. 3A is a schematic representation of a prior art parallel graphics rendering platform comprising multiple parallel graphics pipelines, each supporting video memory and a GPU, and feeding complex pixel compositing hardware for composing a final pixel-based images for display on the display device;

[0133] FIG. 3B is a graphical representation of a conventional parallel graphics rendering process being carried out according to the Object Division Method of parallelism using multiple GPUs on the prior art graphics platform of FIG. 3A:

[0134] FIG. 3C1 is a schematic representation of the GPU and Video Memory structure employed in conventional multi-GPU PC-based computing systems, and illustrating the various kinds of bottlenecks (e.g. geometry limited, pixel limited, data transfer limited, and memory limited) that occur in such systems;

[0135] FIG. 3C2 is a table summarizing the kinds of bottleneck problems which conventional parallelization modes are currently capable of mitigating along the multi-GPU pipelines of conventional PC-based computing systems:

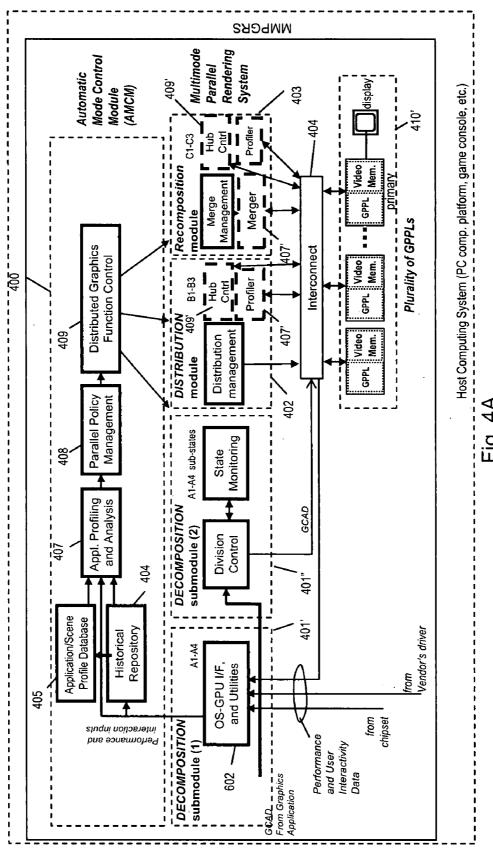

[0136] FIG. 4A is a schematic representation of a generalized embodiment of the multi-mode parallel 3D graphics rendering system (MMPGRS) of the present invention shown comprising (i) an automatic mode control module or mechanism (AMCM) 400 for supporting automatic mode control using diverse types of 3D scene profiling techniques and/or system-user interaction detection techniques, (ii) a multi-mode parallel graphics rendering subsystem 41 for supporting at least three primary parallelization stages of decomposition, distribution and recomposition implemented using the Decomposition Module 401, the Distribution Module 402 and the Recomposition Module 403, respectively, and (ii) a plurality of either GPU and/or CPU based "graphics processing pipelines (GPPLs)"410', wherein each parallelization stage performed by its corresponding Module is configured (i.e. set up) into a "sub-state" by set of parameters, and wherein the "graphics rendering parallelism

state" for the overall multi-mode parallel graphics system is established or otherwise determined by the combination of sub-states of these component stages;

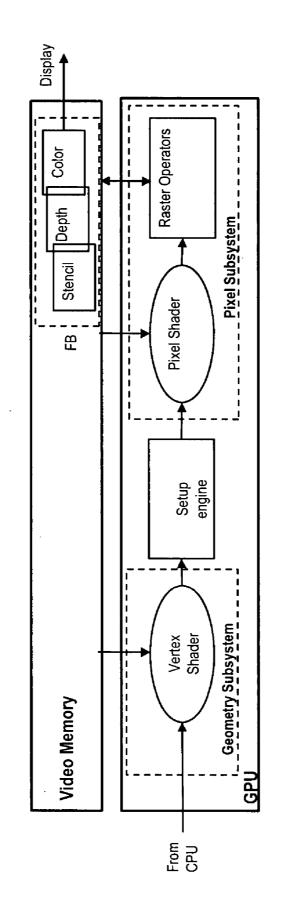

[0137] FIG. 4B1 is a schematic representation of the subcomponents of a first illustrative embodiment of a GPU-based graphics processing pipeline (GPPL) that can be employed in the MMPGRS of the present invention depicted in FIG. 4A, shown comprising (i) a video memory structure supporting a frame buffer (FB) including stencil, depth and color buffers, and (ii) a graphics processing unit (GPU) supporting (1) a geometry subsystem having an input assembler and a vertex shader, (2) a set up engine, and (3) a pixel subsystem including a pixel shader receiving pixel data from the frame buffer and a raster operators operating on pixel data in the frame buffers;

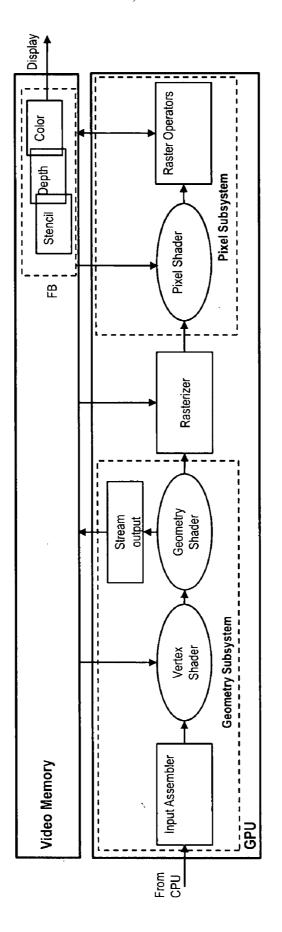

[0138] FIG. 4B2 is a schematic representation of the subcomponents of a second illustrative embodiment of a GPU-based graphics processing pipeline (GPPL) that can be employed in the MMPGRS of the present invention depicted in FIG. 4A, shown comprising (i) a video memory structure supporting a frame buffer (FB) including stencil, depth and color buffers, and (ii) a graphics processing unit (GPU) supporting (1) a geometry subsystem having an input assembler, a vertex shader and a geometry shader, (2) a rasterizer, and (3) a pixel subsystem including a pixel shader receiving pixel data from the frame buffer and a raster operators operating on pixel data in the frame buffers;

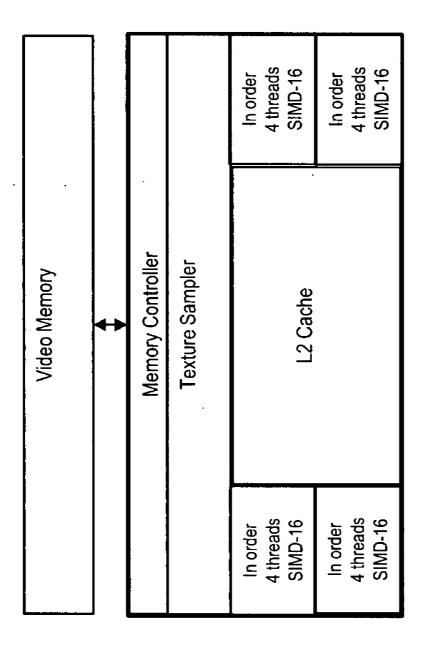

[0139] FIG. 4B3 is a schematic representation of the subcomponents of a illustrative embodiment of a CPU-based graphics processing pipeline that can be employed in the MMPGRS of the present invention depicted in FIG. 4A, shown comprising (i) a video memory structure supporting a frame buffer including stencil, depth and color buffers, and (ii) a graphics processing pipeline realized by one cell of a multi-core CPU chip, consisting of 16 in-order SIMD processors, and further including a GPU-specific extension, namely, a texture sampler that loads texture maps from memory, filters them for level-of-detail, and feeds to pixel processing portion of the pipeline;

[0140] FIG. 4C is a schematic representation for the Mode Definition Table which shows the four combinations of sub-modes (i.e. sub-states) A:B:C for realizing the three (3) Parallel Modes of the MMPGRS of the present invention (i.e. Object Division Mode, Image Division Mode and Time/Alternative Division Mode), and the one (1) Single GPU (i.e. Non-Parallel Functioning) Mode of the system;

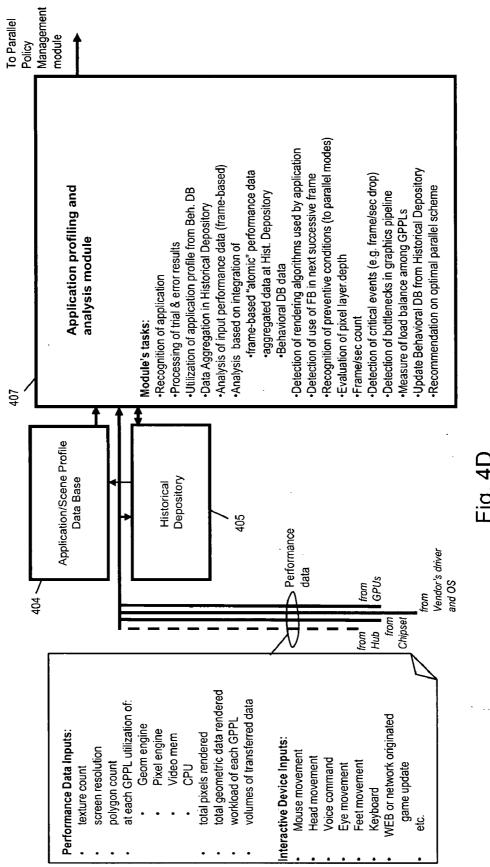

[0141] FIG. 4D is a schematic representation illustrating the various Performance and Interactive Device Data Inputs supplied to the Application Profiling and Analysis Module (within the Automatic Mode Control Module (AMCM)) employed in the MMPGRS of present invention shown in FIG. 4A, as well as the Tasks carried out by the Application Profiling and Analysis Module,

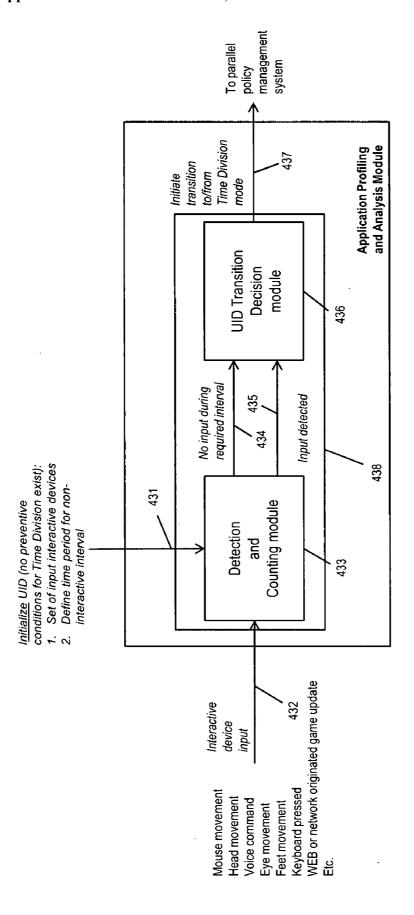

[0142] FIG. 5A is a schematic representation of the User Interaction Detection (UID) Subsystem employed within the Application Profiling and Analysis Module of the Automatic Mode Control Module (AMCM) in the MMPGRS of the present invention, wherein the UID Subsystem is shown comprising a Detection and Counting Module arranged in combination with a UID Transition Decision Module;

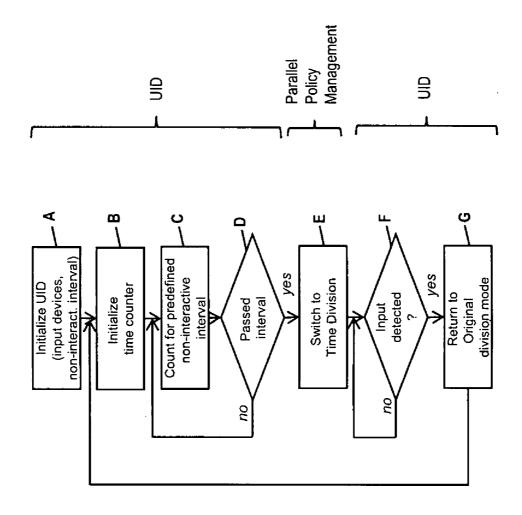

[0143] FIG. 5B is a flow chart representation of the state transition process between Object-Division/Image-Division

Modes and the Time Division Mode initiated by the UID subsystem employed in the MMPGRS of the present invention:

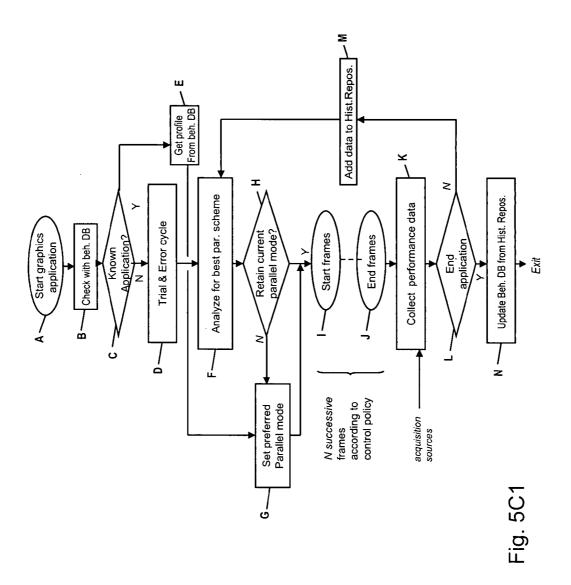

[0144] FIG. 5C1 is a schematic representation of the process carried out by the Profiling and Control Cycle in the Automatic Mode Control Module (AMCM) in the MMPGRS of present invention, while the UID Subsystem is disabled;

[0145] FIG. 5C2 is a schematic representation of the process carried out by the Profiling and Control Cycle in the Automatic Mode Control Module in the MMPGRS of present invention, while the UID Subsystem is enabled;

[0146] FIG. 5C3 is a schematic representation of the process carried out by the Periodical Trial & Error Based Control Cycle in the Automatic Mode Control Module employed in the MMPGRS of present invention, shown in FIG. 4A;

[0147] FIG. 5C4 is a schematic representation of the process carried out by the Event Driven Trial & Error Control Cycle in the Automatic Mode Control Module employed in the MMPGRS of present invention, shown in FIG. 4A;

[0148] FIG. 6A is a State Transition Diagram for the MMPGRS of present invention, illustrating that a parallel state is characterized by A, B, C sub-state parameters, that the non-parallel state (single GPPL) is an exceptional state, reachable from any state by a graphics application or AMCM requirement, and that all state transitions in the system are controlled by Automatic Mode Control Module (AMCM), wherein in those cases of known and previously analyzed graphics applications, the AMCM, when triggered by events (e.g. drop in frames per second FPS rate), automatically consults the Application/Scene Profile Database during the course of the Application, or otherwise, makes decisions which are supported by continuous profiling and analysis of listed parameters, and/or trial and error event driven or periodical cycles;

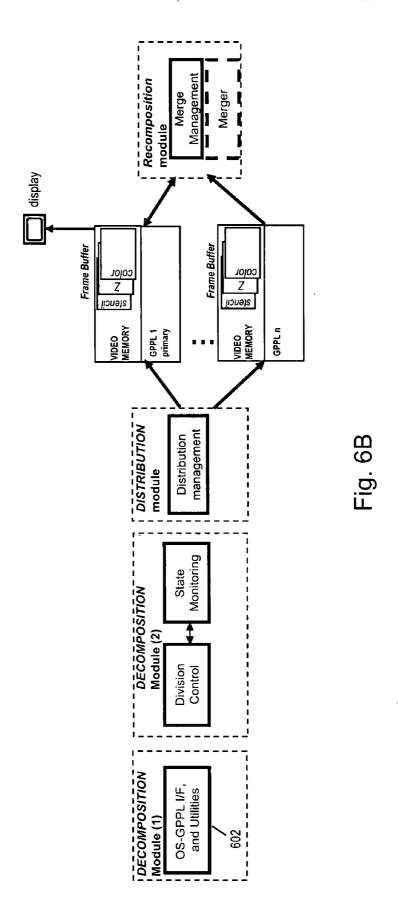

[0149] FIG. 6B is a schematic representation of the MMPGRS of the present invention supporting multiple graphic processing pipelines (GPPLs), with dynamic application profiling and parallelism mode control, in accordance with the principles of the present invention;

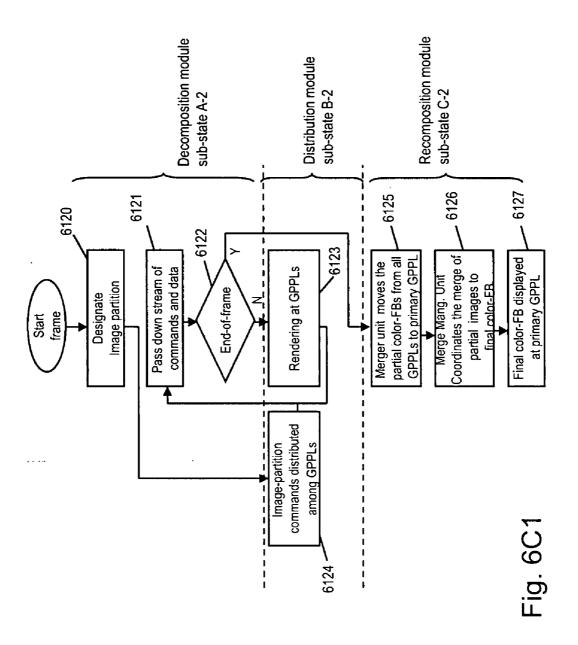

[0150] FIG. 6C1 is a flow chart illustrating the processing of a sequence of pipelined image frames during the Image Division Mode of parallel graphics rendering supported on the MMPGRS of the present invention depicted in FIGS. 4A through 6A;

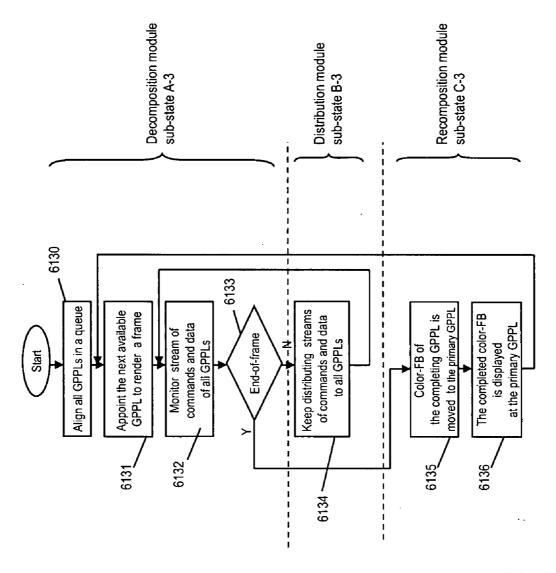

[0151] FIG. 6C2 is a flow chart illustrating the processing of a sequence of pipelined image frames during the Time Division Mode of parallel graphics rendering supported on the MMPGRS of the present invention depicted in FIGS. 4A through 6A;

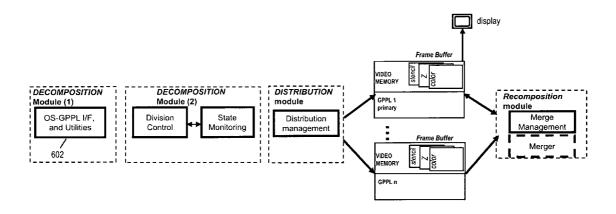

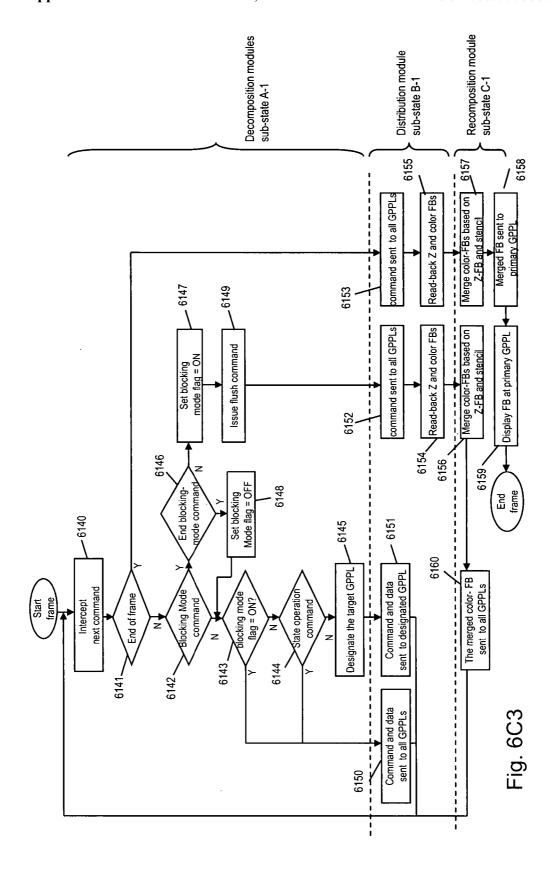

[0152] FIG. 6C3 is a flow chart illustrating the processing of a single image frame during the Object Division mode of parallel graphics rendering supported on the MMPGRS of the present invention depicted in FIGS. 4A through 6A;

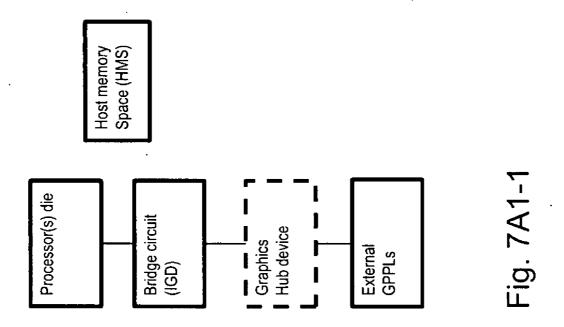

[0153] FIG. 7A1-1 is a schematic representation of various possible graphics architectural spaces within which the components of the MMPGRS of the present invention can

be embodied in any given application, namely: Host Memory Space (HMS), Processor/CPU Die Space, Bridge Circuit (IGD) Space, Graphics Hub Space, and External GPU Space;

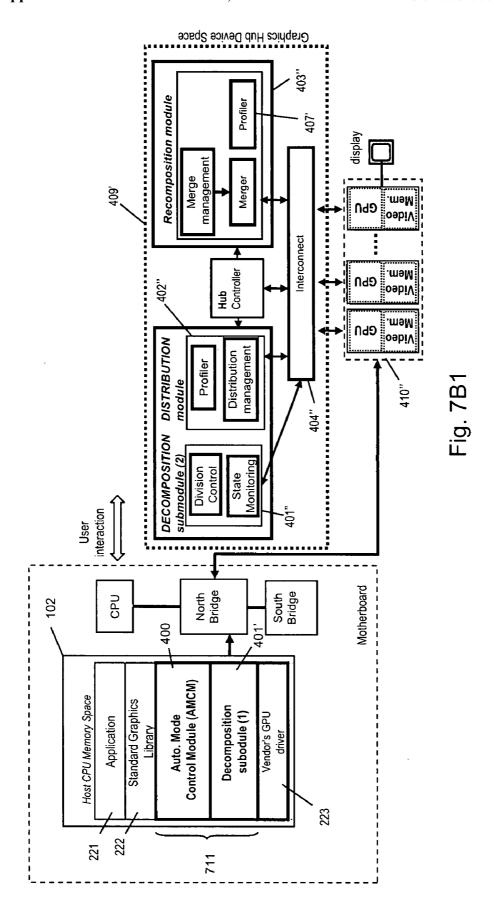

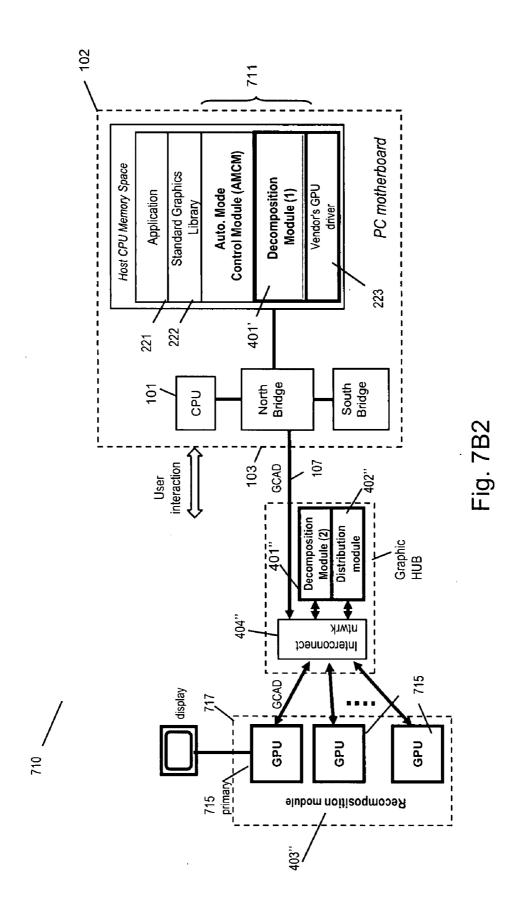

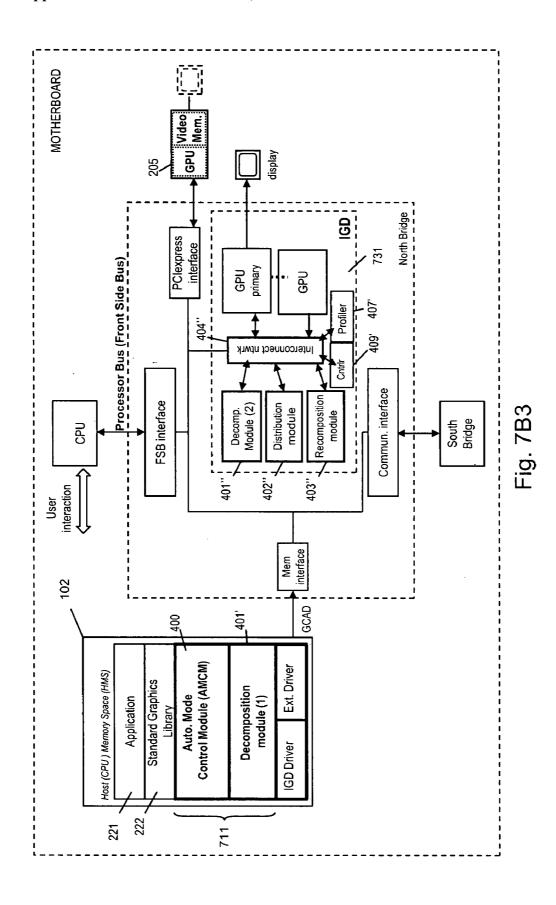

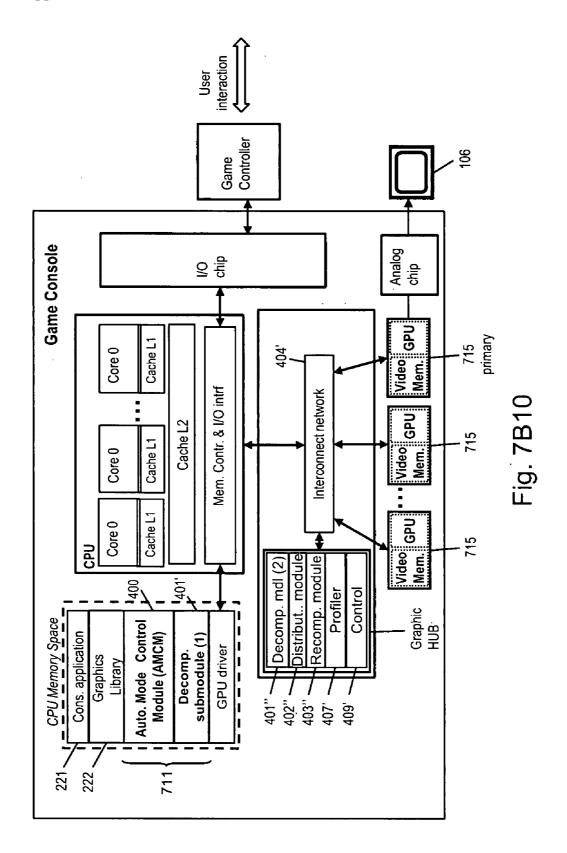

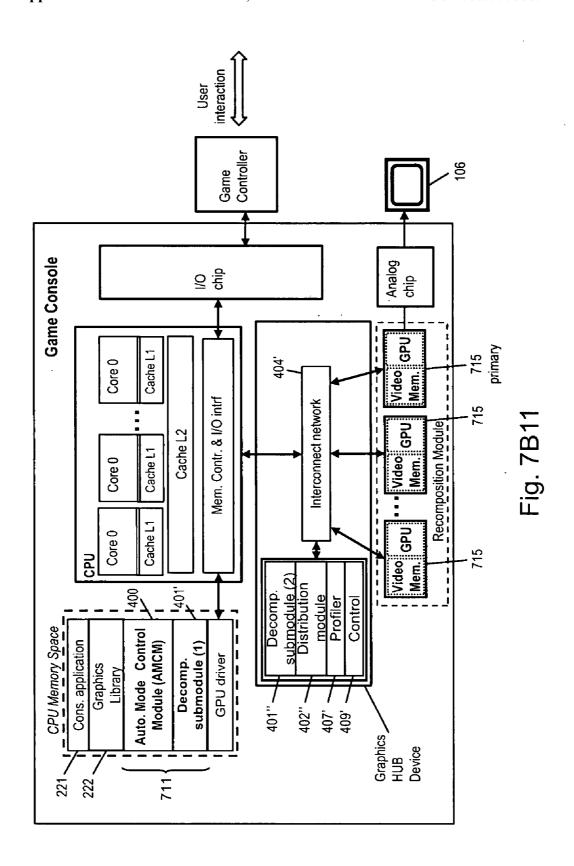

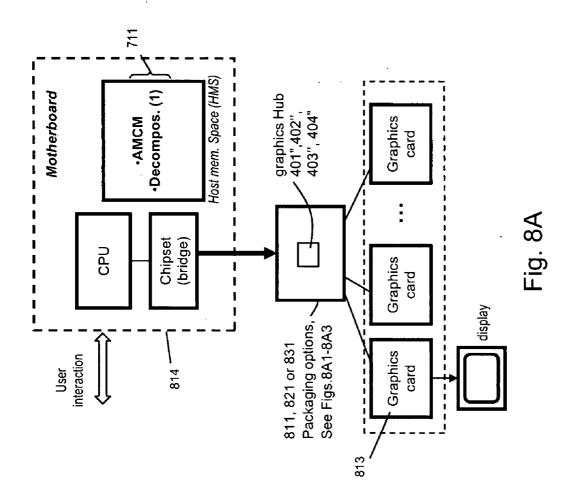

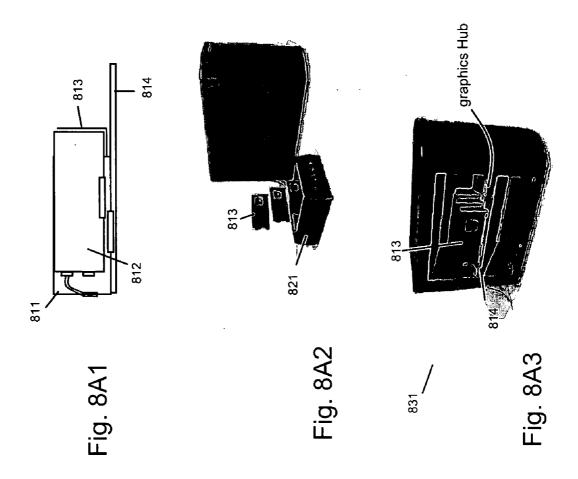

[0154] FIG. 7A1-2 sets forth a table listing diverse classes of system architectures in which the MMPGRS can be embodied, expressed in terms of the different kinds of architectural spaces, identified in FIG. 7A1-1, in which the primary MMPGRS components (i.e. AMCM, Decomposition Submodule 1, Decomposition Module 2, Distribution Module, Multiple GPUs and Recomposition Module) can be embodied in each such class of MMPGRS Architecture, namely—Host Memory Space HMS (software), HMS+IGD, HMS+Fusion, HMS+Multicore, HMS+GPU-Recomposition, HUB; HUB+GPU-Recomposition, Chipset; CPU/GPU Fusion, Multicore CPU, and Game Console;

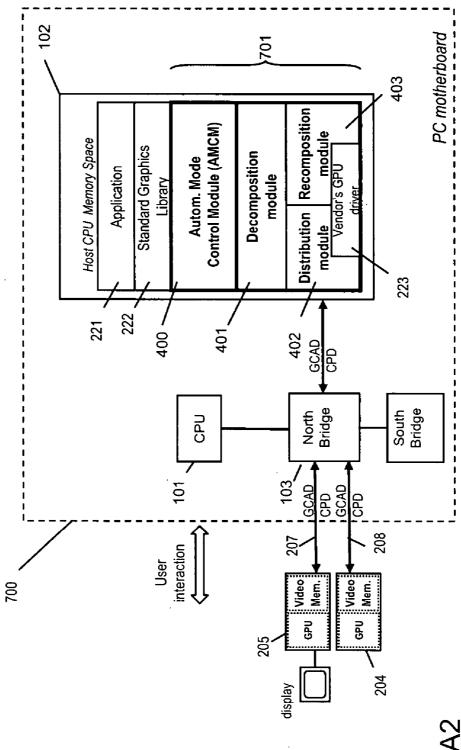

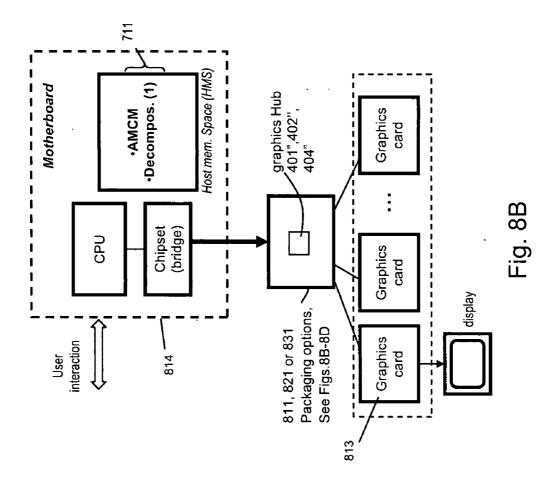

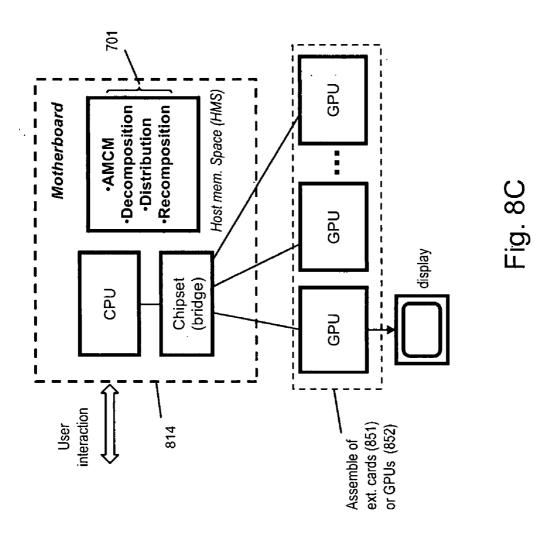

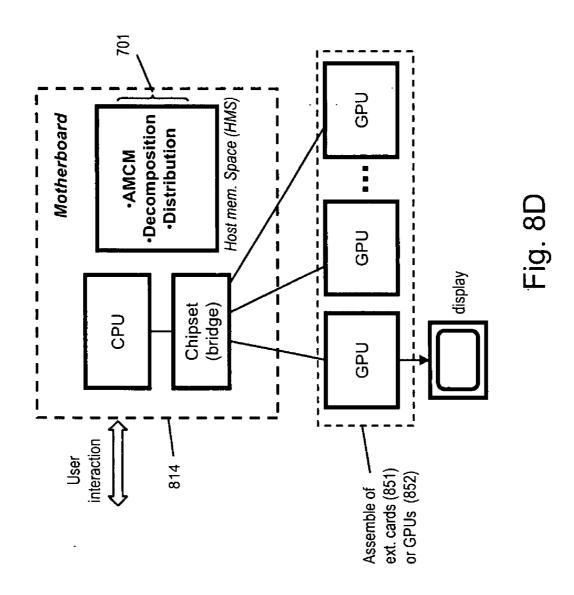

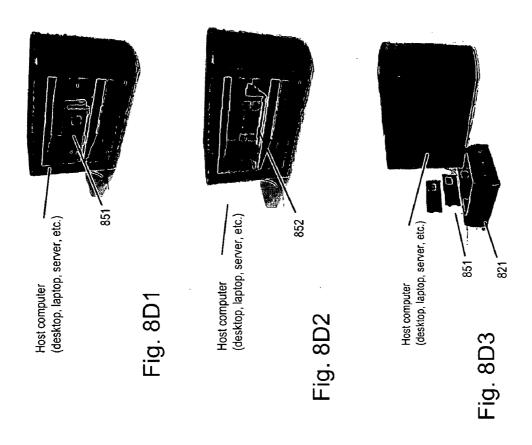

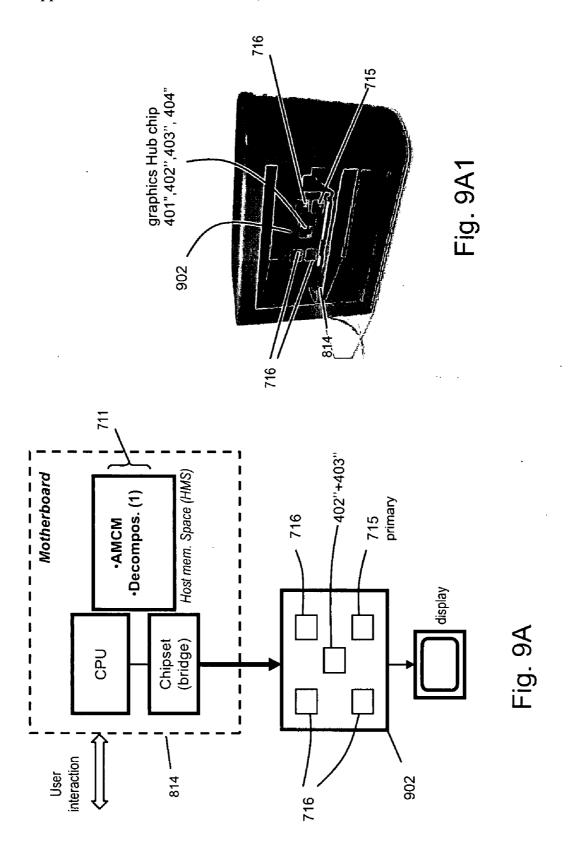

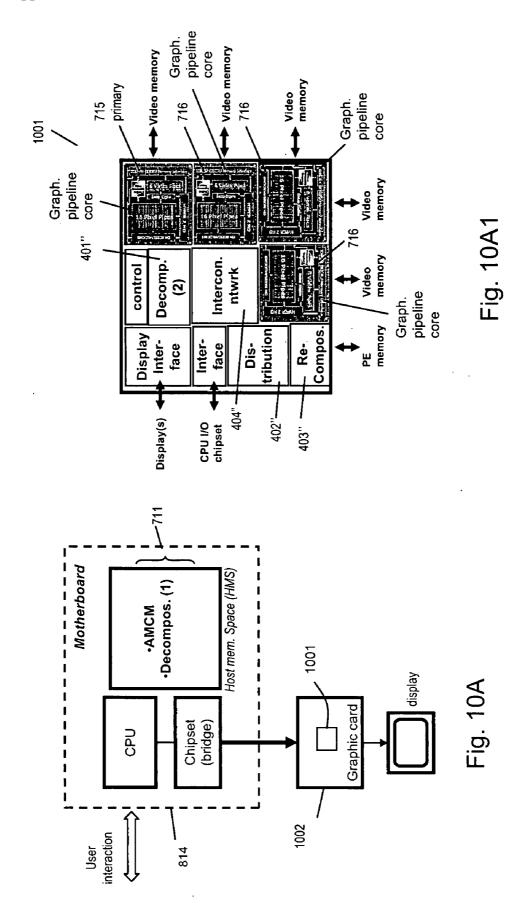

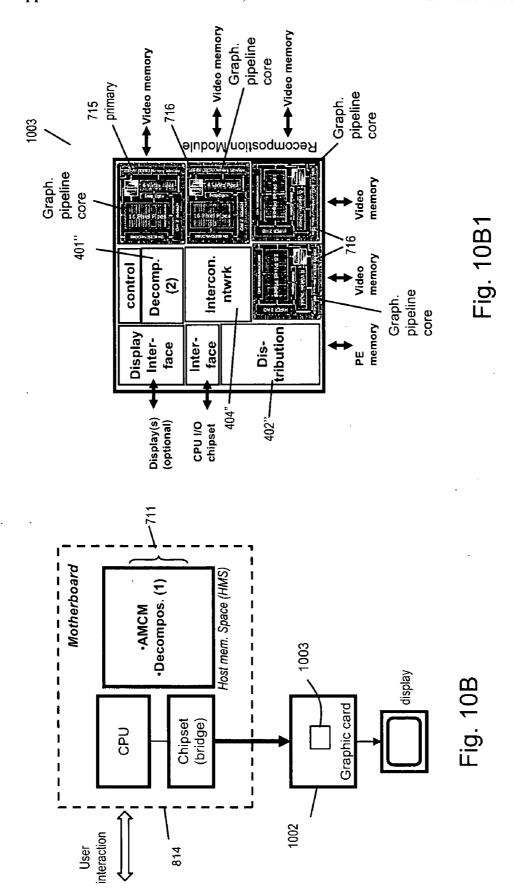

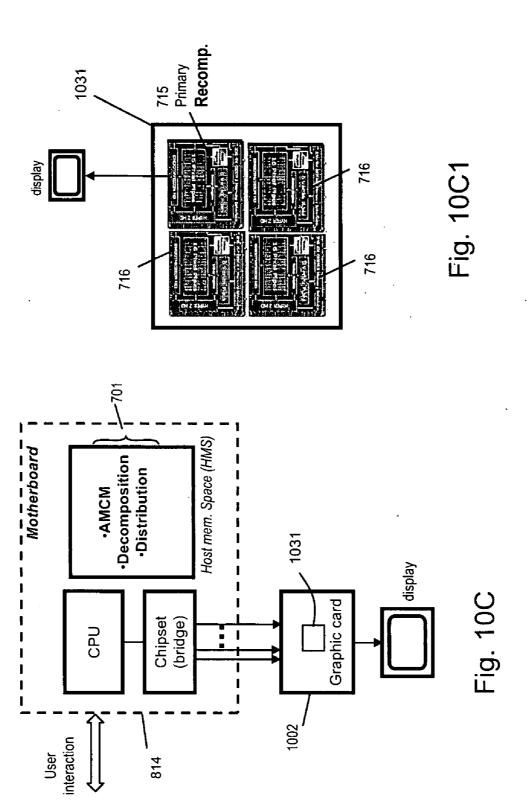

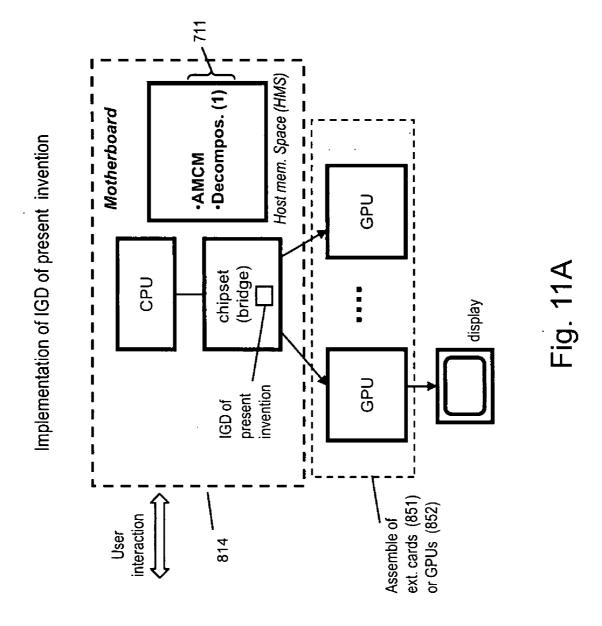

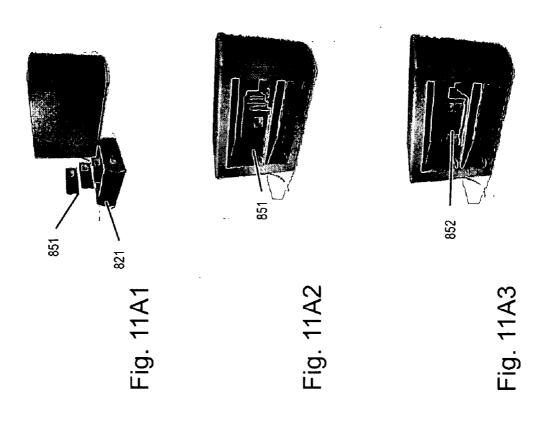

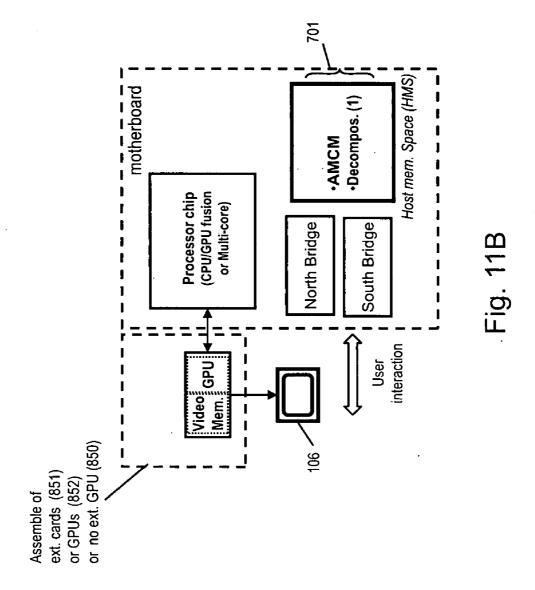

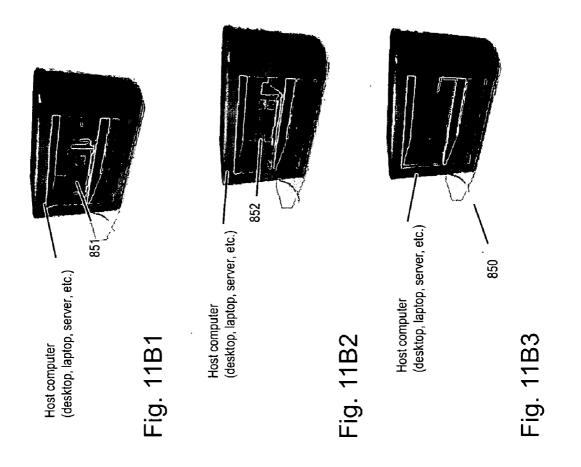

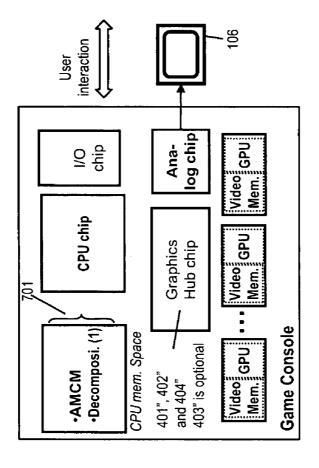

[0155] FIG. 7A2 is a schematic representation of a first illustrative embodiment of the MMPGRS of the present invention, following the HMS Class of MMPGRS Architecture described in FIG. 7A1-2, and showing (i) that the Automatic Mode Control Module (AMCM) 400 and the Decomposition, Distribution and Recomposition Modules 401, 402, 403, respectively, of the Multimode Parallel Graphics Rendering Subsystem resides as a software package 701 in the Host Memory Space (HMS) while multiple GPUs are supported on a pair of external graphic cards 204, 205 connected to a North memory bridge chip 103 and driven in a parallelized manner under the control of the AMCM, (ii) the Decomposition Module 401 divides (i.e. splits up) the stream of graphic commands and data (GCAD) according to the required parallelization mode, operative at any instant in time, (iii) the Distribution Module 402 uses the North bridge chip to distribute graphic commands and data (GCAD) to the multiple GPUs on board the external graphics cards, (iv) the Recomposition Module 403 uses the North bridge chip to transfer composited pixel data (CPD) between the Recomposition Module (or CPU) and the multiple GPUs during the image recomposition stage, and (v) finally recomposited pixel data sets are displayed as graphical images on one or more display devices connected to the external graphics cards via a PCI-express interface (which is connected to the North bridge chip);

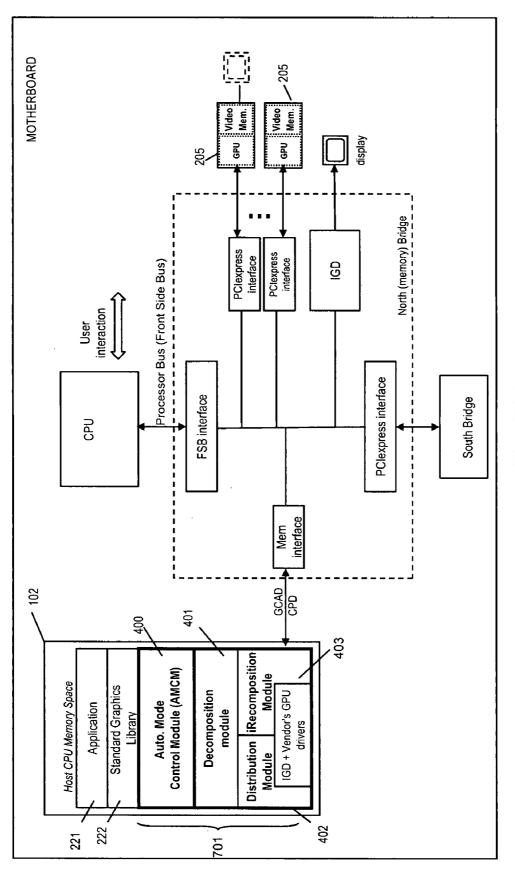

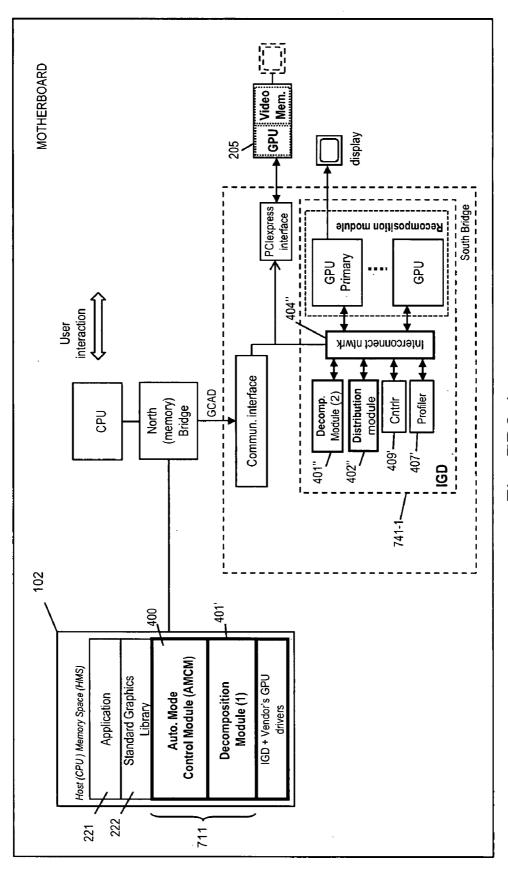

[0156] FIG. 7A3 is a schematic representation of a second illustrative embodiment of the MMPGRS of the present invention, following the HMS+IGD Class of MMPGRS Architecture described in FIG. 7A1-2, and showing (i) that the Automatic Mode Control Module (AMCM) 400 and the Decomposition, Distribution and Recomposition Modules 401, 402, 403, respectively, of the Multimode Parallel Graphics Rendering Subsystem resides as a software package 701 in the Host or CPU Memory Space (HMS) while multiple GPUs are supported in an IGD within the North memory bridge circuit as well as on external graphic cards connected to the North memory bridge chip and driven in a parallelized manner under the control of the AMCM, (ii) the Decomposition Module 401 divides (i.e. splits up) the stream of graphic commands and data (GCAD) according to the required parallelization mode, operative at any instant in time, (iii) the Distribution Module 402 uses the North bridge chip to distribute the graphic commands and data (GCAD) to the multiple GPUs located in the IGD and on the external graphics cards, (iv) the Recomposition Module 403 uses the North bridge chip to transfer composited pixel data (CPD) between the Recomposition Module (or CPU) and the multiple GPUs during the image recomposition stage, and (v) finally recomposited pixel data sets are displayed as graphical images on one or more display devices connected to one of the external graphics cards or the IGD;

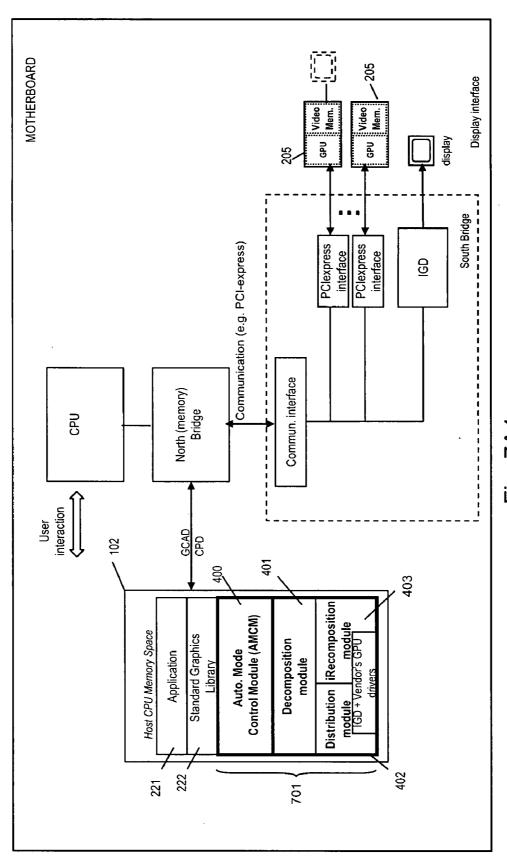

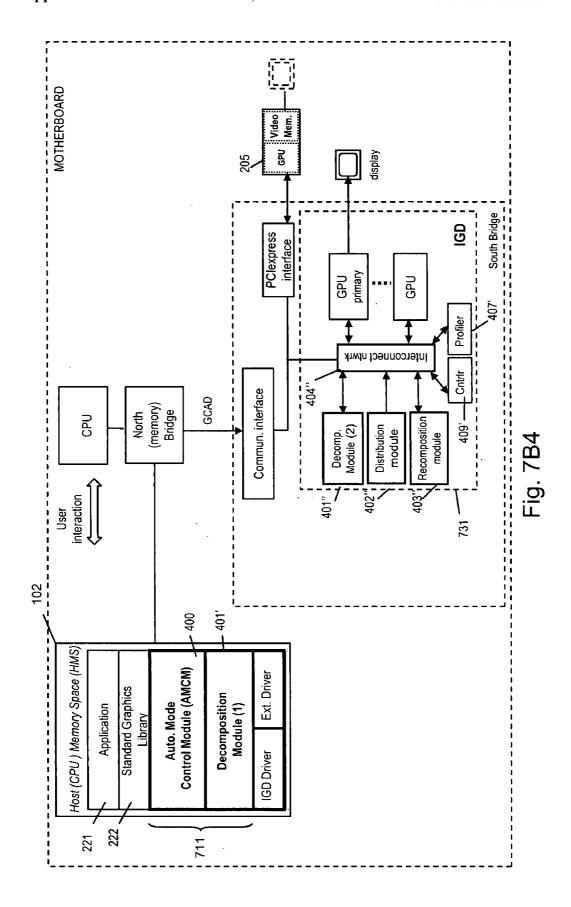

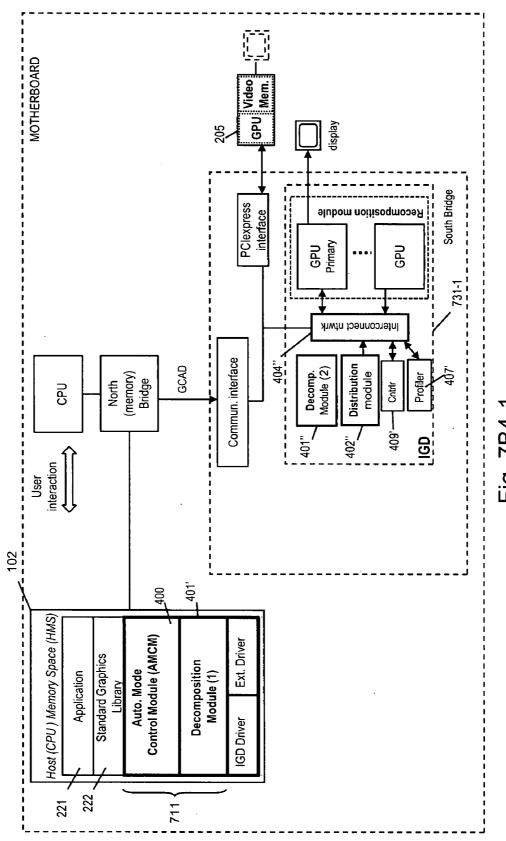

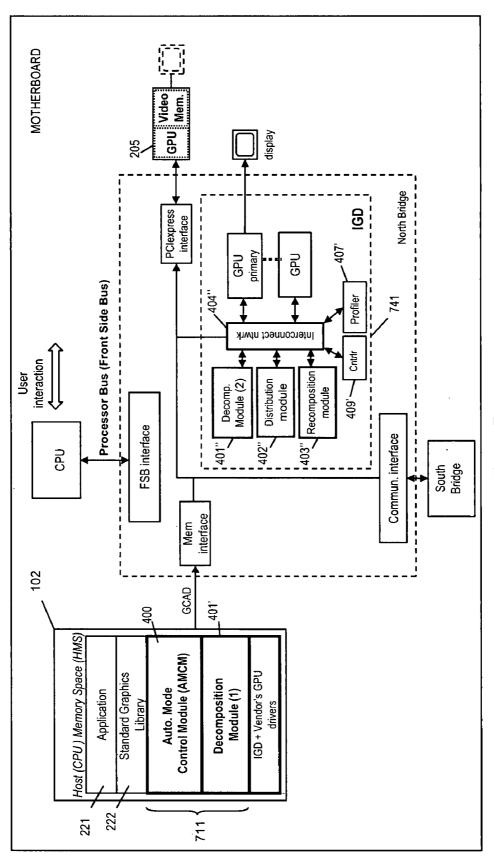

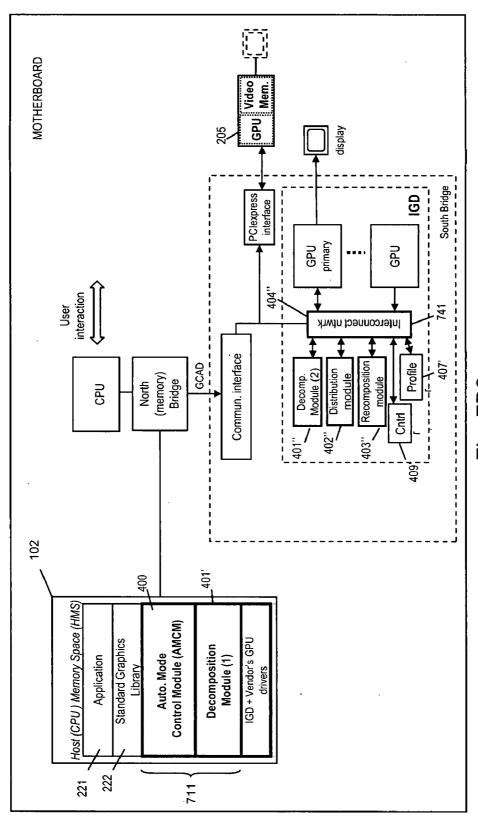

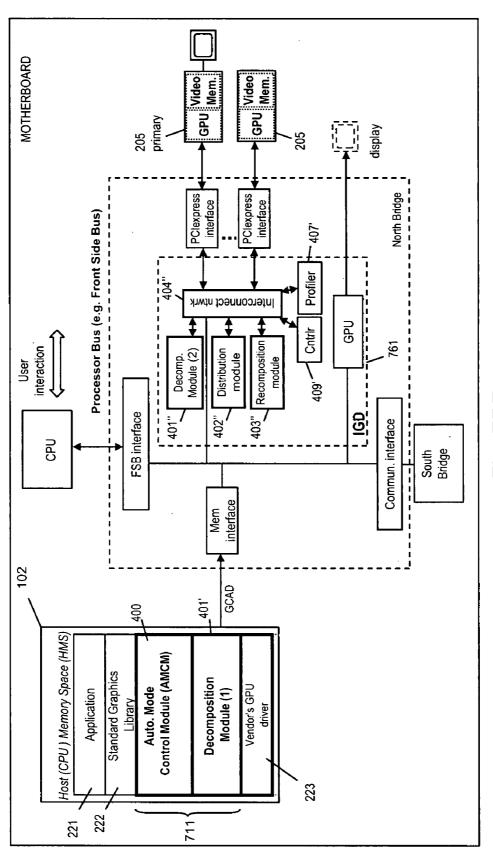

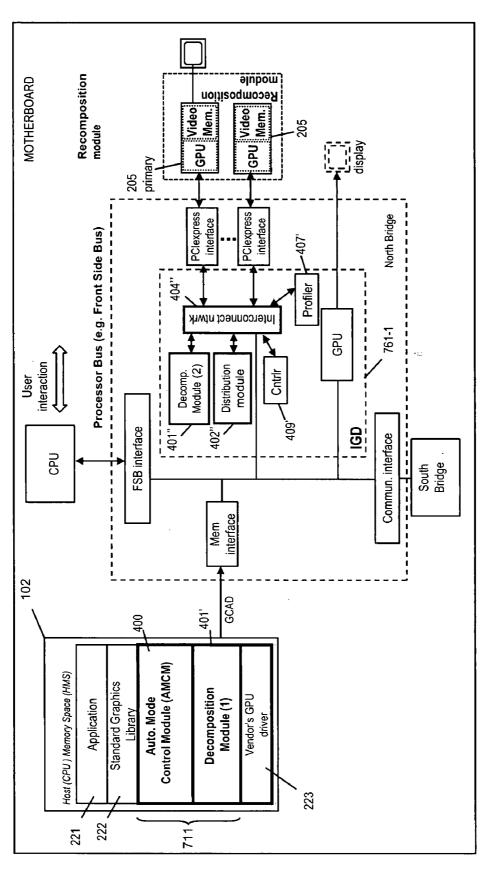

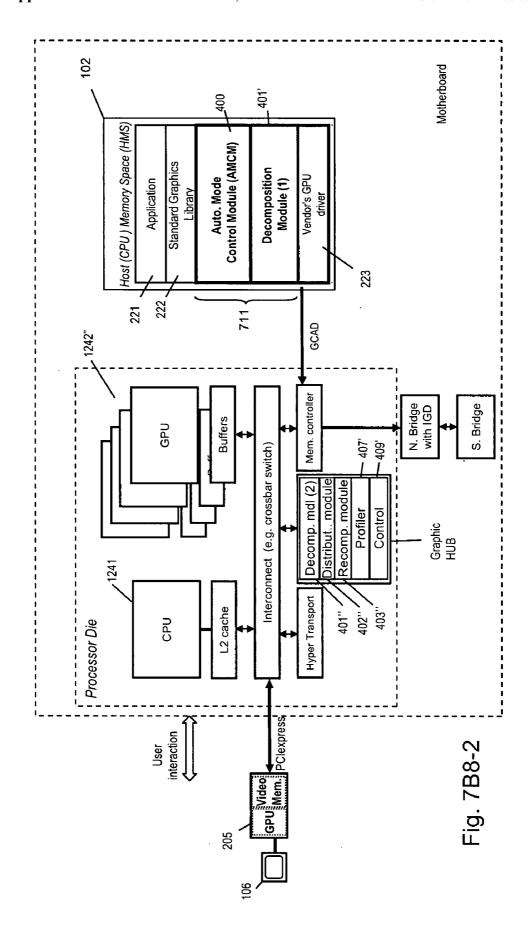

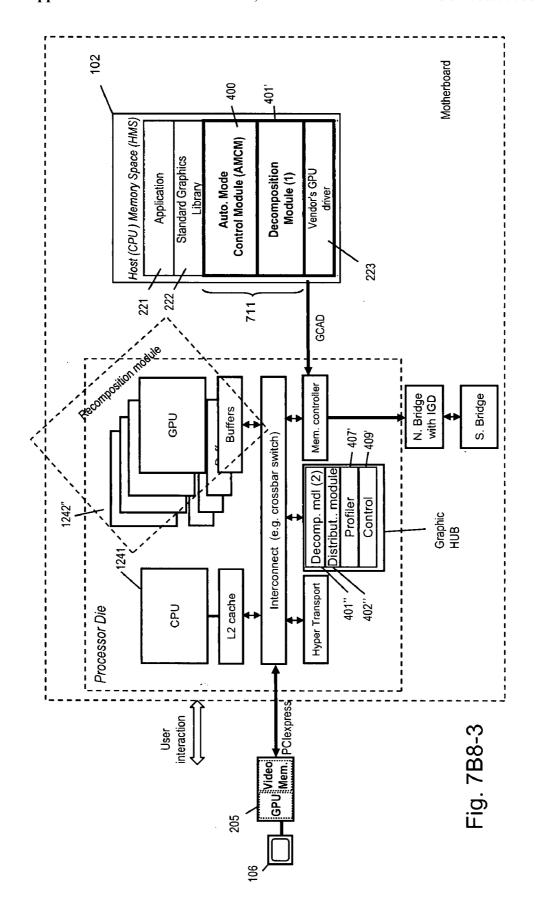

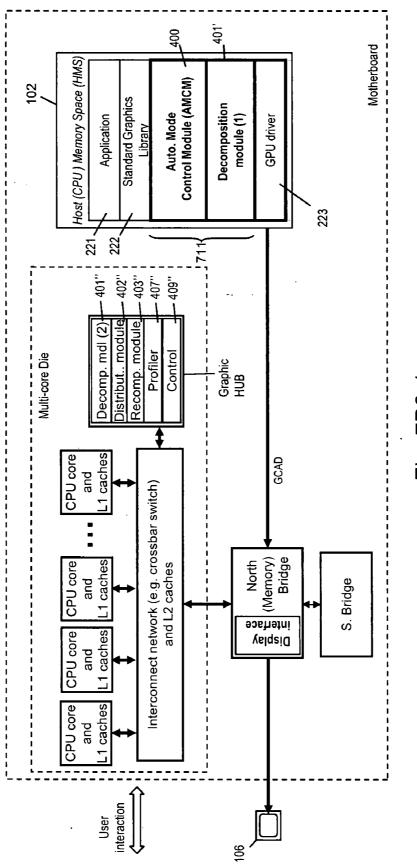

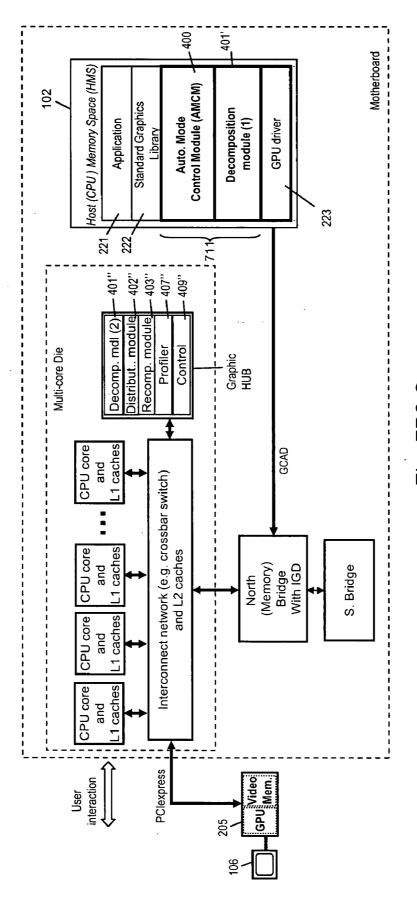

[0157] FIG. 7A4 is a schematic representation of a third illustrative embodiment of the MMPGRS of the present invention, following the HMS+IGD Class of MMPGRS Architecture described in FIG. 7A1-2, and showing (i) that the Automatic Mode Control Module (AMCM) 400 and the Decomposition, Distribution and Recomposition Modules 401, 402, 403, respectively, of the Multimode Parallel Graphics Rendering Subsystem resides as a software package 701 in the Host Memory Space (HMS) while multiple GPUs are supported in an IGD within the South bridge circuit as well as on external graphic cards connected to the South bridge chip, and driven in a parallelized manner under the control of the AMCM, (ii) the Decomposition Module 401 divides (i.e. splits up) the stream of graphic commands and data (GCAD) according to the required parallelization mode, operative at any instant in time, (iii) that the Distribution Module 402 uses the North bridge chip to distribute graphic commands and data (CGAD) to the multiple GPUs located in the IGD and on external graphics cards, (iv) the Recomposition Module 403 uses the South bridge chip to transfer recomposited pixel data between the Recomposition Module (or CPU) and the multiple GPUs during the image recomposition stage, and (v) finally recomposited pixel data sets are displayed as graphical images on one or more display devices connected to one of the external graphics cards or the IGD: