(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-250833

(P2005-250833A)

(43) 公開日 平成17年9月15日(2005.9.15)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

G06F 13/36

G06F 13/36

530A

5B061

G06F 13/362

G06F 13/362

520Z

審査請求 未請求 請求項の数 7 O L (全 9 頁)

(21) 出願番号

特願2004-60172 (P2004-60172)

(22) 出願日

平成16年3月4日(2004.3.4)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 成相 恭一

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

Fターム(参考) 5B061 BA01 FF01 GG13

(54) 【発明の名称】バスシステム及びアクセス制御方法

## (57) 【要約】

## 【課題】

最適なアクセス制限を行なうことができるバスシステム及びアクセス制御方法を提供すること。

## 【解決手段】

本発明にかかるバスシステムは、複数のマスター1と、複数のスレーブ3と、マルチレイヤスイッチ2とを備えている。このバスシステムは、さらに予め定められたセキュアマスター1によってアクセス制限情報を設定可能なアクセス制限レジスタ4を備えている。マルチレイヤスイッチ2は、スイッチ内マスター部20と、スイッチ内スレーブ部21とを備えている。セキュアマスター以外のマスターと対応するスイッチ内マスター部は、当該マスターよりスレーブに対してアクセスがあった場合に、アクセス先のアドレス情報とアクセス制限レジスタに格納されたアクセス制限情報に基いてアクセス制限領域へのアクセスが否かを判定する。そして、アクセス制限領域へのアクセスであると判断した場合には、当該アクセスを制限する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチとを備えたバスシステムであって、

このバスシステムは、さらに予め定められたセキュアマスタによってアクセス制限情報を設定可能なアクセス制限レジスタを備え、

前記マルチレイヤスイッチは、前記マスタに対応したスイッチ内マスタ部と、前記スレーブに対応したスイッチ内スレーブ部とを備え、

前記セキュアマスタ以外のマスタと対応する前記スイッチ内マスタ部は、当該マスタより前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と前記アクセス制限レジスタに格納されたアクセス制限情報を基いてアクセス制限領域へのアクセスか否かを判定し、アクセス制限領域へのアクセスであると判断した場合には、当該アクセスを制限するバスシステム。

**【請求項 2】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブが接続されたシステムバスと、前記システムバスの使用権を設定するアービタを備えたバスシステムであって、

予め定められたセキュアマスタによってアクセス制限情報を設定可能なアクセス制限レジスタと、

前記セキュアマスタ以外のマスタと前記システムバスとの間に設けられたスイッチとをさらに備え、

前記アービタは、前記セキュアマスタ以外のマスタより前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と前記アクセス制限レジスタに格納されたアクセス制限情報を基いてアクセス制限領域へのアクセスか否かを判定し、アクセス制限領域へのアクセスであると判断した場合には、当該アクセスを前記スイッチによって制限するバスシステム。

**【請求項 3】**

前記セキュアマスタと前記アクセス制限レジスタに対しては、常時電源が供給されることを特徴とする請求項 1 又は 2 記載のバスシステム。

**【請求項 4】**

前記セキュアマスタを除く他のマスタ、及び / 又はスレーブは、前記セキュアマスタによって電源制御されることを特徴とする請求項 3 記載のバスシステム。

**【請求項 5】**

前記アクセス制限レジスタは、アクセス制限領域を設定する範囲設定情報を格納する範囲設定レジスタと、制限対象となるマスタを特定する制限対象情報を格納する制限対象レジスタを含むことを特徴とする請求項 1 乃至 3 いずれかに記載のバスシステム。

**【請求項 6】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチとを備えたバスシステムにおけるアクセス制御方法であって、

予め定められたセキュアマスタによってアクセス制限情報をアクセス制限レジスタに対して設定するステップと、

前記セキュアマスタ以外のマスタから前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と、アクセス制限レジスタに対して設定されたアクセス制限情報を比較して、アクセス制限領域へのアクセスか否かを判定するステップと、

アクセス制限領域へのアクセスであると判断した場合には、前記マルチレイヤシステムにおけるスイッチ内マスタ部によって当該アクセスを制限するステップとを備えたアクセス制御方法。

**【請求項 7】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブが接続されたシステム

10

20

30

40

50

バスと、前記システムバスの使用権を設定するアービタを備えたバスシステムにおけるアクセス制御方法であって、

予め定められたセキュアマスタによってアクセス制限情報をアクセス制限レジスタに対して設定するステップと、

前記セキュアマスタ以外のマスタから前記スレーブに対してアクセスがあった場合に、前記アービタによってアクセス先のアドレス情報と、前記アクセス制限レジスタに設定されたアクセス制限情報に基いてアクセス制限領域へのアクセスか否かを判定するステップと、

前記アービタによってアクセス制限領域へのアクセスであると判断した場合には、前記マスタと前記システムバス間に設けられたスイッチによって当該アクセスを制限するステップとを備えたアクセス制御方法。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、複数のマスタやスレーブと接続されたバスシステム及びアクセス制御方法に関する。

##### 【背景技術】

##### 【0002】

複数のマスタやスレーブと接続されたバスシステムにおいて、特定のマスタ以外のマスタから特定のスレーブに対するアクセスを禁止しなければならない場合がある。例えば、所定のメモリに秘密情報やキー情報が格納されているときに、CPU等の演算処理装置から当該メモリへのアクセスは許可される一方で、他のマスタから当該メモリへのアクセスは禁止しなければならない場合である。

20

##### 【0003】

かかるアクセス制限に関する技術が、例えば特許文献1に記載されている。特許文献1においては、複数のマスタそれぞれにマスタ識別信号発生回路を設け、さらにマスタ識別信号を識別するマスタ識別回路を設けている。デコーダは、識別結果に基づき所定の制御信号を生成するとともにアクセスが有効か否かをアクセスを行なったマスタに知らせる。そして生成した制御信号によりI/Oを制御し、かつアクセスが有効か否かをアクセスを行なったマスタに対して知らせて、データ入出力回路への不正なアクセスを規制している。

30

##### 【0004】

しかしながら、特許文献1に記載された技術によれば、データ入出力回路にマスタ識別回路とデコーダがあり、デコーダはマスタ識別回路から出力されるアクセス許可信号が接続されて、この信号に基づきアクセスの可否を決定する構成となっているので、次のような欠点が生じる。まず、アクセス制限する領域がハードウェアで決まってしまうので、システムの中で制限できる領域がマスタ識別回路を実装したデータ入出力回路部分に固定されてしまう。また、データ入出力回路のI/Oの一部だけをアクセス制限することはできない。さらに、アクセスの保護をデータ入出力側で行うので、一つのマスタが保護された部分をアクセスすると、システムバスにトランザクションが発生してしまう。このため、マスタが偶然にあるいは故意にアクセス制限のかかったデータ入出力回路を連続してアクセスすると、システムバスの性能がそのトランザクションにより著しく劣化してしまう。

40

##### 【0005】

他方、近年、携帯電話機においては、本来の電話機能のみならず、インターネット接続機能やカメラ機能も備えており、多機能化が進んでいる。また、携帯電話機においては、小型化、軽量化、低消費電力化の観点から、複数の機能を1チップ上で実現するSOC(システム オン チップ)技術が開発されている。

##### 【0006】

50

かかる携帯電話機では、高速に各種の処理を同時にを行う必要がある。そのため、複数のスレーブに対して同時にアクセス可能なマルチレイヤスイッチが提案されている。

【0007】

このマルチレイヤスイッチを用いると、例えば、カメラで撮影した画像データを所定のメモリ領域に書き込む処理と、メモリに格納された画像データを読み出してディスプレイに表示する処理とを同時に行なうことができる。かかるマルチレイヤスイッチにおいても、特許文献1において説明したような問題点が発生しうる。

【特許文献1】特開平5-257516号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

上述のように、従来のバスシステムにおいては、アクセス制限がかかったスレーブに対する連続アクセスにより、バスの性能が著しく低下する等といった問題点があった。

【0009】

本発明の目的は、かかる問題を解消し、最適なアクセス制限を行なうことができるバスシステム及びアクセス制御方法を提供することである。

【課題を解決するための手段】

【0010】

本発明にかかるバスシステムは、複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチとを備えたバスシステムであって、このバスシステムは、さらに予め定められたセキュアマスタによってアクセス制限情報を設定可能なアクセス制限レジスタを備え、前記マルチレイヤスイッチは、前記マスタに対応したスイッチ内マスタ部と、前記スレーブに対応したスイッチ内スレーブ部とを備え、前記セキュアマスタ以外のマスタと対応する前記スイッチ内マスタ部は、当該マスタより前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と前記アクセス制限レジスタに格納されたアクセス制限情報に基いてアクセス制限領域へのアクセスか否かを判定し、アクセス制限領域へのアクセスであると判断した場合には、当該アクセスを制限するものである。

【0011】

本発明にかかる他のバスシステムは、複数のマスタと、複数のスレーブと、前記マスタと前記スレーブが接続されたシステムバスと、前記システムバスの使用権を設定するアービタを備えたバスシステムであって、予め定められたセキュアマスタによってアクセス制限情報を設定可能なアクセス制限レジスタと、前記セキュアマスタ以外のマスタと前記システムバスとの間に設けられたスイッチとをさらに備え、前記アービタは、前記セキュアマスタ以外のマスタより前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と前記アクセス制限レジスタに格納されたアクセス制限情報に基いてアクセス制限領域へのアクセスか否かを判定し、アクセス制限領域へのアクセスであると判断した場合には、当該アクセスを前記スイッチによって制限するものである。

【0012】

ここで、前記セキュアマスタと前記アクセス制限レジスタに対しては、常時電源が供給されることが望ましい。

【0013】

また、前記セキュアマスタを除く他のマスタ、及び／又はスレーブは、前記セキュアマスタによって電源制御されることが好ましい。

【0014】

さらに、前記アクセス制限レジスタには、アクセス制限領域を設定する範囲設定情報を格納する範囲設定レジスタと、制限対象となるマスタを特定する制限対象情報を格納する制限対象レジスタが含まれる。

【0015】

本発明にかかるアクセス制御方法は、複数のマスタと、複数のスレーブと、前記マスタ

10

20

30

40

50

と前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチとを備えたバスシステムにおけるアクセス制御方法であって、予め定められたセキュアマスタによってアクセス制限情報をアクセス制限レジスタに対して設定するステップと、前記セキュアマスタ以外のマスタから前記スレーブに対してアクセスがあった場合に、アクセス先のアドレス情報と、アクセス制限レジスタに対して設定されたアクセス制限情報を比較して、アクセス制限領域へのアクセスか否かを判定するステップと、アクセス制限領域へのアクセスであると判断した場合には、前記マルチレイヤシステムにおけるスイッチ内マスタ部によって当該アクセスを制限するステップとを備えたものである。

#### 【0016】

本発明にかかる他のアクセス制御方法は、複数のマスタと、複数のスレーブと、前記マスタと前記スレーブが接続されたシステムバスと、前記システムバスの使用権を設定するアービタを備えたバスシステムにおけるアクセス制御方法であって、予め定められたセキュアマスタによってアクセス制限情報をアクセス制限レジスタに対して設定するステップと、前記セキュアマスタ以外のマスタから前記スレーブに対してアクセスがあった場合に、前記アービタによってアクセス先のアドレス情報と、前記アクセス制限レジスタに設定されたアクセス制限情報に基いてアクセス制限領域へのアクセスか否かを判定するステップと、前記アービタによってアクセス制限領域へのアクセスであると判断した場合には、前記マスタと前記システムバス間に設けられたスイッチによって当該アクセスを制限するステップとを備えたものである。

#### 【発明の効果】

#### 【0017】

本発明によれば、最適なアクセス制限を行なうことができるバスシステム及びアクセス制御方法を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0018】

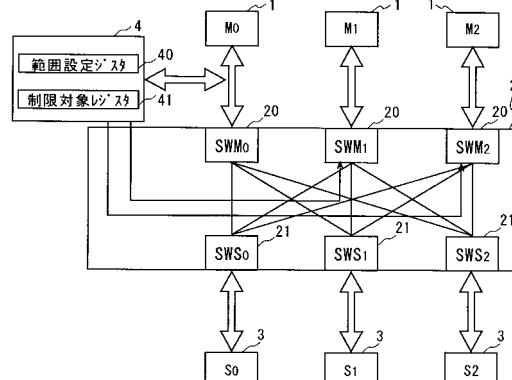

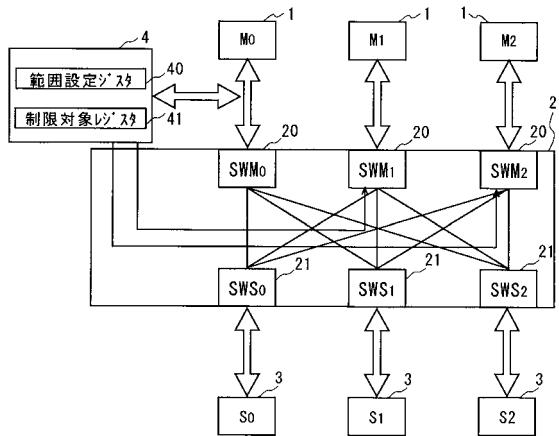

発明の実施の形態1.

本発明の実施の形態1にかかるバスシステムの構成を図1に示す。発明の実施の形態1におけるバスシステムは、マルチレイヤシステムである。当該マルチレイヤシステムは、複数のマスタ1(M0、M1、M2)と、複数のスレーブ3(S0、S1、S2)と、マスタ1とスレーブ3の間に設けられたマルチレイヤスイッチ2を基本的な構成としている。この例では、さらに、アクセス制限レジスタ4を備えている。

#### 【0019】

マスタ1は、システムを制御するモジュールである。例えば、CPU(Central Processor Unit)、DSP(Digital Signal Processor)、画像回転器、カメラ画像処理回路、LCD(Liquid Crystal Display)コントローラ等がある。この例におけるM0は、常時動作しているCPU又はDSP等の演算処理回路である。M1、M2は、M0からの指示により必要な時だけ動作するモジュールである。

#### 【0020】

マルチレイヤスイッチ2は、複数のマスタから出される命令の同時処理を可能にするものである。マルチレイヤスイッチ2は、システム内の複数のマスタ-スレーブ間でパラレル・アクセス・バスの使用を可能にする相互接続バスシステムである。このバスシステムは、より複雑な相互接続マトリックスを使用することによって実現され、システム・アーキテクチャの選択肢や全体のバス帯域幅が広がるといったメリットを提供する。かかるマルチレイヤスイッチ2は、例えば、アーム株式会社よりマルチレイヤAHB(Advanced High-performance Bus)、AHB-Lite(商標)として提供されている。

#### 【0021】

スレーブ3は、マスタ1からの制御対象となるモジュールである。例えば、スレーブ3には、メモリ、レジスタ、タイマ、シリアルインターフェース回路等が含まれる。

#### 【0022】

マルチレイヤスイッチ2の構成についてさらに詳細に説明する。マルチレイヤスイッチ

10

20

30

40

50

2は、個々のマスタ1(M0、M1、M2)に接続されたスイッチ内マスタ部20(SWM0、SWM1、SWM2)及び個々のスレーブ3に接続されたスイッチ内スレーブ部21(SWS0、SWS1、SWS2)を備えている。

#### 【0023】

スイッチ内マスタ部20は、マスタ1からのアクセスがどのスレーブ3への接続かをアクセス先を特定するアドレス情報に基づき判別し、接続先のスレーブ3に対応するスイッチ内スレーブ部21に対してアクセス要求を出す機能を有する。さらに、この例にかかるスイッチ内マスタ部20は、アドレス比較回路(図示せず)を備えている。アドレス比較回路は、アクセス制限レジスタ4からアクセス制限情報に含まれるアドレス情報と、マスタ1からのアクセスに含まれるアドレス情報とを比較し、一致する場合にアドレス情報により特定されるスレーブへのアクセスを制限する。

#### 【0024】

スイッチ内スレーブ部21は、各スイッチ内マスタ部20からのアクセス信号の調停を行い、一つのアクセスを選択して、選択したスレーブ3に対して接続することをその主要な機能とする。

#### 【0025】

アクセス制限レジスタ4は、範囲設定レジスタ40と制限対象レジスタ41を備え、アクセス制限情報を格納する。アクセス制限情報には、これらの制限範囲情報と制限対象情報が含まれる。制限範囲情報は、スレーブ3におけるアクセス制限領域を特定する情報であり、制限設定レジスタ40に格納される。また、制限対象情報は、どのマスタ1に対してアクセス制限を有効とするかを特定する情報であり、制限対象レジスタ41に格納される。

#### 【0026】

範囲設定レジスタ40及び制限対象レジスタ41への情報の設定は、セキュアなマスタ(以下、セキュアマスタ)であるM0のみが行なうことができ、他のマスタ(M1、M2等)はできない。このとき、ハードウェア構成により、範囲設定レジスタ40及び制限対象レジスタ41への情報の設定は、セキュアマスタであるM0のみが行なうができるように作りこむことが好ましい。具体的には、セキュアマスタであるM0のローカルバスへの接続や、アドレス比較回路ヘデフォルトでM0以外のマスタがアクセスできない領域を作成する。

#### 【0027】

範囲設定レジスタ40及び制限対象レジスタ41は、信号線によりSWM1及びSWM2に接続されている。より具体的には、SWM1及びSWM2に含まれるアドレス比較回路は、信号線を介して範囲設定レジスタ40及び制限対象レジスタ41と接続されており、かかる信号線の電位を検出することにより範囲設定レジスタ40及び制限対象レジスタ41に格納されたアドレス制限情報を認識することができる。

#### 【0028】

続いて、本発明の実施の形態1にかかるマルチレイヤシステムにおける処理動作について説明する。ここでは、S2は、メモリであり、かかるメモリの8000番地からFFFF番地に秘密情報が格納されており、M0以外のマスタ1(例えば、M1、M2)はアクセスを制限されている。そして、アクセス制限対象であるM1から当該S2の8000番地からFFF F番地に含まれる8000番地の情報に対してアクセスが行なわれた場合を想定する。

#### 【0029】

M1は、アクセス先(ここではS2)のアドレス信号(8000番地)や、リード/ライト信号等の制御信号を、マルチレイヤスイッチ2のスイッチ内マスタ部20であるSWM1に対して出力する

#### 【0030】

SWM1は、M1から入力したアドレス信号に基づいて、どのスレーブ3に対してアクセスするかを判別する。SWM1では、さらに、アドレス比較回路によって、M1から入

10

20

30

40

50

力したアドレス信号に含まれるアドレス情報と範囲設定レジスタ40に設定された制限範囲情報に含まれるアドレス情報とを比較する。この場合、範囲レジスタ40に8000番地からFFF0番地の領域をアクセス制限範囲として設定しているので、SWM1はM1のアクセスしようとしている8000番地が制限範囲内であるとして処理を行う。即ち、SWM1は、M1が、設定されたアクセス制限領域へのアクセスを行なったものと判定する。この場合に、SWM1は、トランザクションをマルチレイヤスイッチ2のSWS2には伝達せずに、M1に対してエラーレスポンスを返して、アドレス制限領域へのアクセスを禁止する。

【0031】

このように本発明の実施の形態においては、スイッチ内マスター部20において、アクセス制限レジスタ4を参照して、アクセス制限を行なうようにしたので、仮に特定のマスターからアクセス制限が行なわれているスレーブに対してアクセスが繰り返されたとしても、スイッチ内スレーブ部21やスレーブ3に対するアクセスは発生しないため、マルチレイヤスイッチ2に接続されている前記特定マスター以外のマスターのバスアクセスの性能の低下は発生しない。

【0032】

また、本発明の実施の形態においては、アクセス制限領域をシステムのメモリマップの任意の領域に設定することができる。そして、設定した領域へのアクセス制限を、どのマスターに対して適用するかを設定することができる。

【0033】

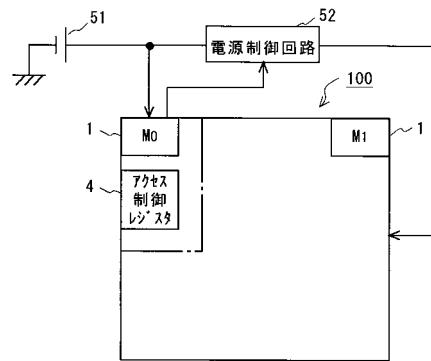

本発明の実施の形態1におけるセキュアなマスターであるM0及びアクセス制限レジスタ4に関しては、他の回路等とは別の電源制御が行なわれることが好ましい。図2にチップ100のレイアウト例及び電源関連の回路構成例を示す。図2に示されるように、M0及びアクセス制限レジスタ4に対しては、常時、電源51から電源が供給される。その一方で、M1を含む他の回路に対しては、電源制御回路52を介して電源が供給される。この電源制御回路52は、M0の制御に基いて動作し、必要としない状態においては各マスター1やスレーブ3等の電源供給が制限される。これによって、チップ100における省電力化を達成できる。

【0034】

電源制御回路52によってM1等の他の回路の電源がオフされた状態でも、アクセス制限レジスタ4に対しては電源がオン状態にあるため、当該アクセス制限レジスタ4に設定されたデータは消去されない。

【0035】

発明の実施の形態2.

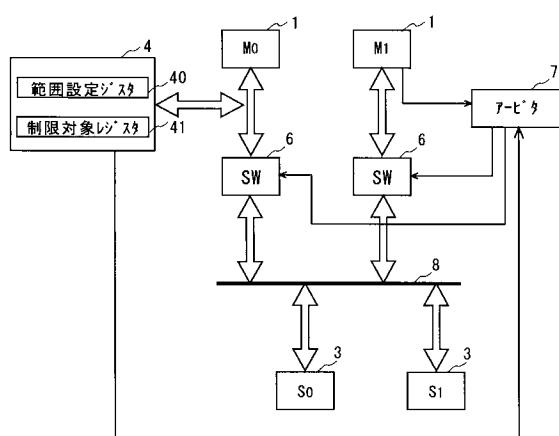

発明の実施の形態2では、マルチレイヤシステムではなく、通常のバスを用いている。図3に当該発明の実施の形態2にかかるバスシステムの構成を示す。図に示されるように、システムバス8の接続ポイントと、マスター1との間には、スイッチ6が設けられている。そして、M1のアクセス先のアドレスは、アービタ7(調停回路)に対して入力される。また、範囲設定レジスタ40や制限対象レジスタ41に格納されたアクセス制限情報も、アービタ7に対して入力される。アクセス制限レジスタ4へのアクセス制限情報の設定は、セキュアなマスターであるM0のみが行なうことができる。アービタ7は、バス1によるシステムバス8の使用権を設定する機能を有する。

【0036】

続いて、本発明の実施の形態2にかかるバスシステムにおける処理動作について説明する。M1は、アクセス先のアドレス信号をアービタ7に対して出力する。アービタ7は、当該アドレス信号に含まれるアドレス情報と、アクセス制限レジスタ4に格納されたアクセス制限情報に含まれるアドレス情報とを比較し、比較結果を出力する。この例では、アービタ7は、M1が、設定されたアクセス制限領域へのアクセスを行なったものと判定する。この場合に、アービタ7は、M1とシステムバス8の接続ポイントとの間にスイッチ6に対して、M1によるシステムバス8へのアクセスの制限を要求する。スイッチ6

10

20

30

40

50

は、この要求に対して、アクセスが不可能であることを示すエラー応答信号をマスターに對して返す。これにより、M 1 のアクセス制限領域へのアクセスは制限される。

【0037】

このように本発明の実施の形態においては、アービタ7において、アクセス制限レジスタ4を参照して、システムバス8の接続ポイントとマスター1との間に設けられたスイッチ6によってアクセス制限を行なうようにしたので、仮に特定のマスターからアクセス制限が行なわれているスレーブに対してアクセスが繰り返されたとしても、システムバス8に対するアクセスは発生しないため、システムバスの性能低下は無い。

【0038】

また、本発明の実施の形態においては、アクセス制限領域をシステムのメモリマップの任意の領域に設定することができる。そして、設定した領域へのアクセス制限を、どのマスターに対して適用するかを設定することができる。

【図面の簡単な説明】

【0039】

【図1】本発明によるバスシステムの構成図である。

【図2】本発明によるバスシステムを適用したチップのレイアウト例及び電源関連の回路構成例を示す図である。

【図3】本発明による他のバスシステムの構成図である。

【符号の説明】

【0040】

- 1 マスター

- 2 マルチレイヤスイッチ

- 3 スレーブ

- 4 アクセス制限レジスタ

- 6 スイッチ

- 7 アービタ

- 8 システムバス

- 20 20 スイッチ内マスター部

21 スイッチ内スレーブ部

【図1】

【図2】

【図3】