(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4384792号

(P4384792)

(45) 発行日 平成21年12月16日(2009.12.16)

(24) 登録日 平成21年10月2日(2009.10.2)

(51) Int.Cl.

F 1

|                     |                  |            |      |

|---------------------|------------------|------------|------|

| <b>H03K 19/0175</b> | <b>(2006.01)</b> | H03K 19/00 | 101S |

| <b>G06F 3/00</b>    | <b>(2006.01)</b> | G06F 3/00  | W    |

| <b>G06F 13/12</b>   | <b>(2006.01)</b> | G06F 13/12 | 340Z |

| <b>G06F 15/78</b>   | <b>(2006.01)</b> | G06F 15/78 | 510E |

| <b>H03K 5/13</b>    | <b>(2006.01)</b> | H03K 5/13  |      |

請求項の数 6 (全 12 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2000-206692 (P2000-206692) |

| (22) 出願日  | 平成12年7月7日 (2000.7.7)         |

| (65) 公開番号 | 特開2002-26713 (P2002-26713A)  |

| (43) 公開日  | 平成14年1月25日 (2002.1.25)       |

| 審査請求日     | 平成18年10月27日 (2006.10.27)     |

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 特許権者 | 308033711<br>OKIセミコンダクタ株式会社<br>東京都八王子市東浅川町550番地1 |

| (74) 代理人  | 100086807<br>弁理士 柿本 恒成                           |

| (72) 発明者  | 遊佐 敦史<br>東京都港区虎ノ門1丁目7番12号 沖電<br>気工業株式会社内         |

審査官 宮島 郁美

|           |                                                                                              |

|-----------|----------------------------------------------------------------------------------------------|

| (56) 参考文献 | 特開平05-014167 (JP, A)<br>特開平03-027617 (JP, A)<br>特開平05-094549 (JP, A)<br>特開平09-162719 (JP, A) |

|-----------|----------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】入出力回路

## (57) 【特許請求の範囲】

## 【請求項 1】

マイクロコントローラの集積回路に組込まれ、前記集積回路の入出力端子を介して接続される外部回路との間でデータまたは信号の入出力を行う入出力回路において、

前記入出力端子に出力する前記データまたは前記信号を遅延させる遅延手段を備え、

前記遅延手段は、直列に接続された複数の遅延素子を有し、前記複数の遅延素子のうちの任意のいくつかの前記遅延素子の出力を用いて複数の遅延時間分遅延させた複数の遅延信号を生成し、制御情報に基づいて、生成された前記複数の遅延信号のいずれか1つあるいは、前記複数の遅延信号の任意のいくつかを組合せた信号を出力信号として前記入出力端子へ出力することを特徴とする入出力回路。

10

## 【請求項 2】

請求項 1記載の入出力回路は、更に、

駆動能力の異なる複数の出力バッファを有し、前記出力バッファの中から予め選択された前記出力バッファを介して前記データまたは前記信号を前記入出力端子に出力する出力手段を備えたことを特徴とする入出力回路。

## 【請求項 3】

請求項 1または2記載の入出力回路は、更に、

入力特性の異なる複数の入力バッファを有し、前記入出力端子に与えられた前記データまたは前記信号を前記入力バッファの中から予め選択された前記入力バッファを介して入力する入力手段を備えたことを特徴とする入出力回路。

20

**【請求項 4】**

入力モード時に、前記入出力端子を所定の電位にするか否かを選択的に制御可能な構成にしたことを特徴とする請求項 3 記載の入出力回路。

**【請求項 5】**

前記遅延手段において、

前記制御情報は第 1 の情報と第 2 の情報とを有し、更に、

前記第 1 の情報に基づき、前記複数の遅延信号のうちのいくつかを選択的に出力する選択出力段と、

前記選択出力段から選択的に出力された信号に基づいて組合せた信号を生成し、前記第 2 の情報に基づき、前記複数の遅延信号のいずれか 1 つあるいは、前記複数の遅延信号の任意のいくつかを組合せた前記出力信号を出力する信号生成段と、

を有することを特徴とする請求項 1 ~ 4 のいずれか 1 項に記載の入出力回路。

**【請求項 6】**

前記信号生成段は、

選択的に出力された前記信号に基づいて組合せた前記信号を生成して出力する第 1 の信号生成回路と、

前記第 2 の情報に基づいて、前記第 1 の信号生成回路の出力から、前記出力信号を生成して出力する第 2 の信号生成回路と、

を有することを特徴とする請求項 5 記載の入出力回路。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、マイクロコントローラの集積回路において、外部回路を接続するための入出力回路に関するものである。

**【0002】****【従来の技術】**

一般に、マイクロコンピュータ等のマイクロコントローラで用いられる入出力回路は、機能設定用レジスタをプログラムで書替えることにより、1つの外部接続用インターフェースを、デジタル信号の入力または出力回路として切替えて使用することができるようになっている。更に、2次機能として外部バス用のアドレス信号及びデータ信号等の出力回路や、プルアップ付き入力回路として使用できるようになった入出力回路もある。

**【0003】**

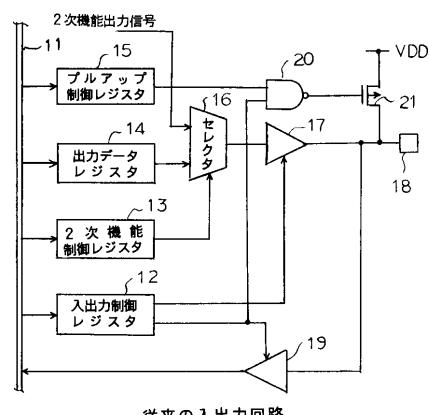

図 2 は、従来の入出力回路の一例を示す構成図である。

この入出力回路は、マイクロコンピュータの集積回路に組込まれるもので、内部バス 11 に接続された入出力制御レジスタ 12、2次機能制御レジスタ 13、出力データレジスタ 14、及びプルアップ制御レジスタ 15 等の機能設定用レジスタを有している。

**【0004】**

入出力制御レジスタ 12 は、内部バス 11 を介して与えられる入力モードまたは出力モードの制御コマンドを保持して入出力動作の切替えを行うものである。出力データレジスタ 14 は、出力モード時に内部バス 11 を介して与えられる出力データを保持するものである。2次機能制御レジスタ 13 は、出力モード時に、出力データレジスタ 14 内のデータを出力するか、2次機能として与えられるアドレス信号等を出力するかの切替え用の制御情報を保持するものである。プルアップ制御レジスタ 15 は、入力モード時に入力端子をプルアップするか否かの制御情報を保持するものである。

**【0005】**

出力データレジスタ 14 の出力側は、セレクタ 16 の第 1 の入力側に接続され、このセレクタ 16 の第 2 の入力側には、例えばアドレス信号等の2次機能出力信号が与えられるようになっている。セレクタ 16 は、2次機能制御レジスタ 13 から与えられる制御情報に基づいて、第 1 または第 2 の入力側の信号を選択して出力するものである。セレクタ 16 の出力側は、出力バッファ 17 を介して外部回路接続用の入出力端子 18 に接続されてい

10

20

30

40

50

る。出力バッファ 17 は、入出力制御レジスタ 12 から与えられる出力モード信号 OUT がレベル “H” になったときに、セレクタ 16 の出力信号を増幅して入出力端子 18 に接続された外部回路を駆動するものである。出力モード信号 OUT がレベル “L” のときは、出力バッファ 17 の出力側はハイインピーダンス状態となって入出力端子 18 から切離されるようになっている。

#### 【0006】

入出力端子 18 には、入力バッファ 19 の入力側が接続されている。入力バッファ 19 は、入出力制御レジスタ 12 から与えられる入力モード信号 IN が “H” になったときに、入出力端子 18 に外部回路から与えられる入力信号を内部バス 11 に出力するものである。入力モード信号 IN が “L” のときは、入力バッファ 19 の出力側はハイインピーダンス状態となって内部バス 11 から切離されるようになっている。10

#### 【0007】

入出力制御レジスタ 12 から出力される入力モード信号 IN とプルアップ制御レジスタ 15 の出力信号は、2 入力の否定的論理積ゲート（以下、「NAND」という）20 の入力側に与えられるようになっている。NAND 20 の出力側は、P チャネル MOS トランジスタ（以下、「PMOS」という）21 のゲートに接続されている。PMOS 21 のソースは電源電位 VDD に接続され、ドレインが入出力端子 18 に接続されている。

#### 【0008】

このような入出力回路では、内部バス 11 を介して入出力制御レジスタ 12 に、入力モードまたは出力モードを設定することによって、入力回路とするか出力回路とするかの選択をすることができる。20

入力モードを設定したときには、更にプルアップ制御レジスタ 15 に制御信号を設定することにより、PMOS 21 が導通状態になり、入出力端子 18 をプルアップすることができる。そして、外部回路から入出力端子 18 に入力された入力信号は入力バッファ 19 を介して内部バス 11 へ与えられる。

#### 【0009】

一方、出力モードを設定したときには、更に 2 次機能制御レジスタ 13 に制御信号を設定することにより、出力データレジスタ 14 に格納されたデータ、または 2 次機能出力信号のいずれかをセレクタ 16 で選択して出力することができる。セレクタ 16 で選択された出力信号は、出力バッファ 17 で電力増幅されて入出力端子 18 に出力され、この入出力端子 18 に接続された外部回路が駆動される。30

#### 【0010】

##### 【発明が解決しようとする課題】

しかしながら、従来の入出力回路では、次のような課題があった。

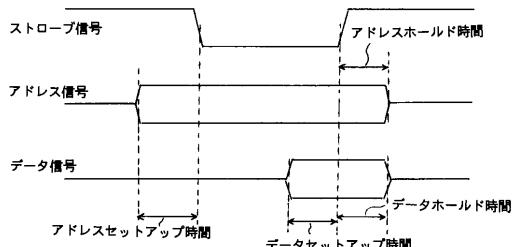

図 3 は、スタティック・ランダムアクセス・メモリ（以下、「SRAM」という）のデータ書き込み時の信号タイミングを示す信号波形図である。

#### 【0011】

この図 3 に示すように、SRAM では、まずアドレス信号を与え、所定のアドレスセンス時間が経過して SRAM 内のデコーダ等の状態が確定した時点で、ストローブ信号を与える（“L” にする）必要がある。また、書込むべきデータ信号を与えた後、所定のデータセットアップ時間が経過した後に、ストローブ信号を “H” にしなければならない。更に、ストローブ信号が “H” になった後も、所定のアドレスホールド時間の間、アドレス信号を変化させてはならない。また、所定のデータホールド時間の間、データ信号を変化させてはならない。これらのタイミング条件が満たされないと、SRAM にデータを正常に書込むことができなくなる。40

#### 【0012】

図 2 の入出力回路の出力モード時には、入出力端子 18 に接続される外部回路および接続方法により、出力信号と入力側外部回路とでタイミングに不整合が発生した場合、その外部回路が使用できなくなることがある。例えば SRAM を外部回路として接続した場合、入出力端子 18 からの出力信号であるアドレス信号、データ信号、ストローブ信号との間50

に適切なタイミング条件が整わないと、アクセスが困難になるという課題があった。更に、入力バッファ19や出力バッファ17の能力が、入出力端子18に接続される外部回路の入出力条件に整合していない場合、入出力波形の劣化により、データ誤りやデータ速度の低下を引起こすという課題があった。

【0013】

本発明は、前記従来技術が持っていた課題を解決し、入出力信号のタイミング調整や、入出力条件の選択が可能な入出力回路を提供するものである。

【0014】

【課題を解決するための手段】

前記課題を解決するために、本発明のうちの請求項1に係る発明は、マイクロコントローラの集積回路に組込まれ、前記集積回路の入出力端子を介して接続される外部回路との間でデータまたは信号の入出力を行う入出力回路において、前記入出力端子に出力する前記データまたは前記信号を遅延させる遅延手段を備え、前記遅延手段は、直列に接続された複数の遅延素子を有し、前記複数の遅延素子のうちの任意のいくつかの前記遅延素子の出力を用いて複数の遅延時間分遅延させた複数の遅延信号を生成し、制御情報に基づいて、生成された前記複数の遅延信号のいずれか1つあるいは、前記複数の遅延信号の任意のいくつかを組合せた信号を出力信号として前記入出力端子へ出力するものであることを特徴とする。

【0015】

請求項2に係る発明は、請求項1記載の入出力回路において、更に、駆動能力の異なる複数の出力バッファを有し、前記出力バッファの中から予め選択された前記出力バッファを介して前記データまたは前記信号を前記入出力端子に出力する出力手段を備えたことを特徴とする。

【0016】

請求項3に係る発明は、請求項1または2記載の入出力回路において、更に、入力特性の異なる複数の入力バッファを有し、前記入出力端子に与えられた前記データまたは前記信号を前記入力バッファの中から予め選択された前記入力バッファを介して入力する入力手段を備えたことを特徴とする。

【0017】

請求項4に係る発明は、請求項3記載の入出力回路において、入力モード時に、前記入出力端子を所定の電位にするか否かを選択的に制御可能な構成にしたことを特徴とする。

【0018】

請求項5に係る発明は、請求項1～4のいずれか1項に記載の入出力回路中の遅延手段において、前記制御情報は第1の情報と第2の情報を有し、更に、前記第1の情報に基づき、前記複数の遅延信号のうちのいくつかを選択的に出力する選択出力段と、前記選択出力段から選択的に出力された信号に基づいて組合せた信号を生成し、前記第2の情報に基づき、前記複数の遅延信号のいずれか1つあるいは、前記複数の遅延信号の任意のいくつかを組合せた前記出力信号を出力する信号生成段とを有することを特徴とする。

【0019】

請求項6に係る発明は、請求項5記載の入出力回路において、前記信号生成段は、選択的に出力された前記信号に基づいて組合せた前記信号を生成して出力する第1の信号生成回路と、前記第2の情報に基づいて、前記第1の信号生成回路の出力から、前記出力信号を生成して出力する第2の信号生成回路とを有することを特徴とする。

【0020】

【発明の実施の形態】

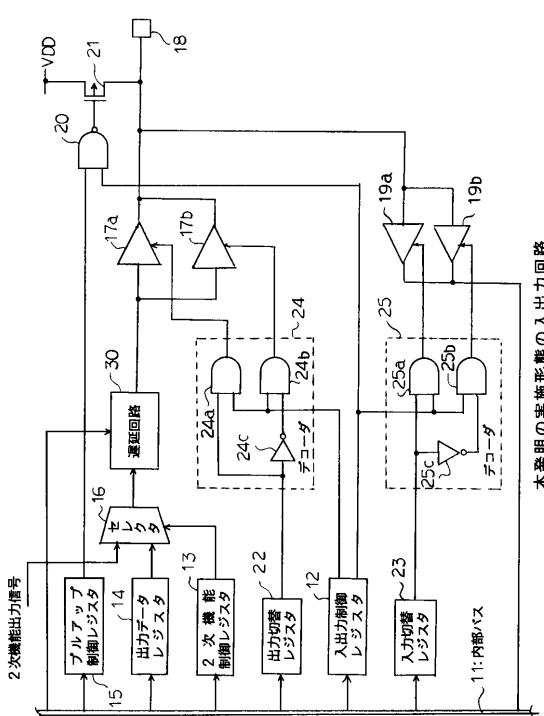

図1は、本発明の実施形態を示す入出力回路の構成図であり、図2中の要素と共通の要素には共通の符号が付されている。

この入出力回路は、マイクロコンピュータ等の集積回路に組込まれるものである。この入出力回路は、図2と同様の入出力制御レジスタ12、2次機能制御レジスタ13、出力データレジスタ14、及びプルアップ制御レジスタ15に加えて、出力切替レジスタ22及

10

20

30

40

50

び入力切替レジスタ 2 3 の機能設定用レジスタを有している。これらのレジスタは、内部バス 1 1 に接続されている。

【 0 0 2 1 】

入出力制御レジスタ 1 2 は、内部バス 1 1 を介して与えられる入力モードまたは出力モードを指定するための制御コマンドを保持し、入出力動作の切替えを行うものである。入出力制御レジスタ 1 2 に入力モードが設定されたときには、“ H ” の入力モード信号 I N が出力され、出力モードが設定されたときには、“ H ” の出力モード信号 O U T が出力されるようになっている。

【 0 0 2 2 】

出力データレジスタ 1 4 は、出力モード時に内部バス 1 1 を介して与えられる出力データを保持するものである。2 次機能制御レジスタ 1 3 は、出力モード時に、出力データレジスタ 1 4 内のデータを出力するか、2 次機能として与えられるアドレス信号等を出力するかの切替え用の制御情報を保持するものである。プルアップ制御レジスタ 1 5 は、入力モード時に入出力端子 1 8 をプルアップするか否かの制御情報を保持するものである。

10

【 0 0 2 3 】

一方、出力切替レジスタ 2 2 は、出力バッファの駆動能力を切替えるための制御信号を保持するものである。例えば、駆動能力の高い出力バッファを選択するときには、出力切替レジスタ 2 2 に“ H ” の制御信号を保持し、駆動能力の低い出力バッファを選択するときには、“ L ” の制御信号を保持するようになっている。また、入力切替レジスタ 2 3 は、入力バッファの入力レベルを切替えるための制御信号を保持するものである。例えば、 T T L レベルの入力バッファを選択するときには、入力切替レジスタに“ H ” の制御信号を保持し、 C M O S レベルの入力バッファを選択するときには、“ L ” の制御信号を保持するようになっている。

20

【 0 0 2 4 】

出力データレジスタ 1 4 の出力側は、セレクタ 1 6 の第 1 の入力側に接続され、このセレクタ 1 6 の第 2 の入力側には、例えばアドレス信号等の2 次機能出力信号が与えられるようになっている。セレクタ 1 6 は、2 次機能制御レジスタ 1 3 から与えられる制御情報に基づいて、第 1 または第 2 の入力側の信号を選択して出力するものである。セレクタ 1 6 の出力側は、遅延手段（例えば、遅延回路）3 0 の入力側に接続されている。

30

【 0 0 2 5 】

遅延回路 3 0 は、セレクタ 1 6 の出力信号を、内部バス 1 1 から与えられる制御信号に基づいて遅延させるものであり、この遅延回路 3 0 の出力側が、駆動能力の異なる出力バッファ 1 7 a , 1 7 b の入力側に接続されている。出力バッファ 1 7 a , 1 7 b の出力側は、外部回路接続用の入出力端子 1 8 に接続されている。出力バッファ 1 7 a , 1 7 b は、いずれも制御端子に与えられる制御信号が“ H ” の時に、遅延回路 3 0 の出力信号を増幅して入出力端子 1 8 に接続された外部回路を駆動するものである。また、出力バッファ 1 7 a , 1 7 b の制御端子に与えられる制御信号が“ L ” の時には、その出力側がハイインピーダンス状態となって入出力端子 1 8 から切離されるようになっている。なお、出力バッファ 1 7 a は、出力バッファ 1 7 b に比べて駆動能力が大きく設定されている。

40

【 0 0 2 6 】

出力切替レジスタ 2 2 の出力側には、デコーダ 2 4 が接続されている。デコーダ 2 4 は、例えば 2 入力の論理積ゲート（以下、「 A N D 」という）2 4 a , 2 4 b とインバータ 2 4 c で構成されている。デコーダ 2 4 は、入出力制御レジスタ 1 2 から出力される出力モード信号 O U T が“ H ” のとき、出力切替レジスタ 2 2 の出力信号の“ H ” , “ L ” に対応して、それぞれ A N D 2 4 a , 2 4 b から“ H ” の信号を出力するものである。 A N D 2 4 a , 2 4 b の出力側は、それぞれ出力バッファ 1 7 a , 1 7 b の制御端子に接続されている。

【 0 0 2 7 】

入出力端子 1 8 には、入力バッファ 1 9 a , 1 9 b の入力側が接続されている。入力バッファ 1 9 a , 1 9 b は、制御端子に与えられる制御信号が“ H ” になったときに、入出力

50

端子 18 に外部回路から与えられる入力信号を内部バス 11 に出力するものである。制御信号が“L”的ときは、入力バッファ 19a, 19b の出力側はハイインピーダンス状態となって内部バス 11 から切離されるようになっている。入力バッファ 19a は、TTL レベルのバッファであり、また入力バッファ 19b は CMOS レベルのバッファである。

#### 【0028】

入力切替レジスタ 23 の出力側には、デコーダ 25 が接続されている。デコーダ 25 は、例えば 2 入力の AND 25a, 25b とインバータ 25c で構成されている。デコーダ 25 は、入出力制御レジスタ 12 から出力される入力モード信号 IN が“H”的とき、入力切替レジスタ 23 の出力信号の“H”, “L”に対応して、それぞれ AND 25a, 25b から“H”的信号を出力するものである。AND 25a, 25b の出力側は、それぞれ入力バッファ 19a, 19b の制御端子に接続されている。

#### 【0029】

入出力制御レジスタ 12 から出力される入力モード信号 IN とプルアップ制御レジスタ 15 の出力信号は、2 入力の NAND 20 の入力側に与えられるようになっている。NAND 20 の出力側は、PMOS 21 のゲートに接続されている。PMOS 21 のソースは電源電位 VDD に接続され、ドレインが入出力端子 18 に接続されている。これらの入出力制御レジスタ 12、プルアップ制御レジスタ 15、NAND 20、及び PMOS 21 により、入力モード時に、入出力端子 18 を所定の電位（プルアップ）にするか否かを選択的に制御可能な構成になっている。

#### 【0030】

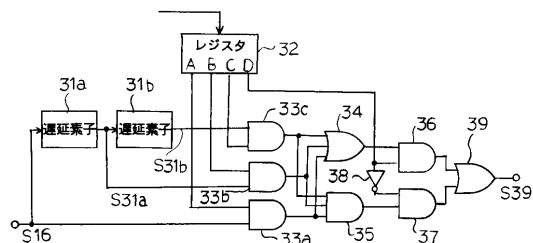

図 4 は、図 1 中の遅延回路 30 の一例を示す回路図である。

この遅延回路 30 は、セレクタ 16 の出力信号が与えられる遅延素子 31a とこの後段に接続された遅延素子 31b、及び内部バス 11 から制御信号が設定されるレジスタ 32 を有している。レジスタ 32 は、制御情報のうちの第 1 の情報を出力する出力端子 A, B, C と、制御情報のうちの第 2 の情報を出力する出力端子 D を有している。遅延素子 31a の入力側と出力側、及び遅延素子 31b の出力側は、それぞれ 2 入力の AND 33a, 33b, 33c からなる選択出力段の第 1 の入力側に接続されている。AND 33a ~ 33c の第 2 の入力側は、それぞれレジスタ 32 の出力端子 A, B, C に接続されている。

#### 【0031】

AND 33a ~ 33c の出力側は、3 入力の論理ゲート（以下、「OR」という）34、及び AND 35 からなる第 1 の信号生成回路の入力側に接続されている。OR 34 及び AND 35 の出力側は、それぞれ 2 入力の AND 36, 37 の第 1 の入力側に接続されている。AND 36 の第 2 の入力側はレジスタ 32 の出力端子 D に接続され、AND 37 の第 2 の入力側はインバータ 38 を介してレジスタ 32 の出力端子 D に接続されている。更に、AND 36, 37 の出力側は 2 入力の OR 39 の入力側に接続され、この OR 39 の出力側が出力バッファ 17a, 17b の入力側に接続されている。AND 36, 37 及び OR 39 により、第 2 の信号生成回路が構成され、この第 2 の信号生成回路と、前記第 1 の信号生成回路とにより、信号生成段が構成されている。

#### 【0032】

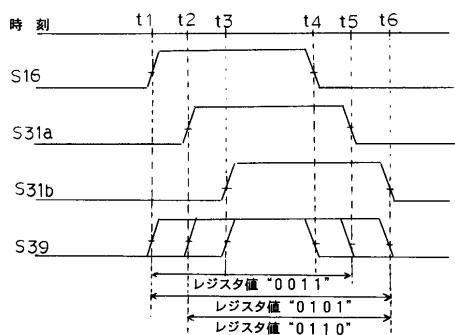

図 5 は、図 4 の遅延回路 30 の機能を説明するための信号波形図である。

図 4 において、入力された信号 S16 は、遅延素子 31a, 31b で遅延されて、それぞれ信号 S31a, S31b となる。これらの信号 S16, S31a, S31b は、レジスタ 32 の出力端子 A, B, C, D から出力される 4 ビットの制御信号の内のビット 0 (A), 1 (B), 2 (C) に対応している。制御信号の対応するビットが論理値“1”に設定された信号が、AND 33a ~ 33c で選択され、OR 34 及び AND 35 からそれぞれ信号 S34, S35 が output される。信号 S34, S35 は、AND 36, 37、インバータ 38 及び OR 39 で構成されるセレクタに入力され、レジスタ 32 の出力端子 D から出力される制御信号に従って、いずれか一方が選択されて信号 S39 として出力される。

#### 【0033】

10

20

30

40

50

図5に示すように、例えば時刻  $t_1$  で信号  $S_{16}$  が立上ると、この信号  $S_{16}$  は遅延素子  $31a$  で遅延され、時刻  $t_2$  で信号  $S_{31a}$  が立上がる。更に信号  $S_{31a}$  は遅延素子  $31b$  で遅延され、時刻  $t_3$  で信号  $S_{31b}$  が立上がる。

時刻  $t_4$  で信号  $S_{16}$  が立下ると、この信号  $S_{16}$  は遅延素子  $31a$  で遅延され、時刻  $t_5$  で信号  $S_{31a}$  が立下がる。更に信号  $S_{31a}$  は遅延素子  $31b$  で遅延され、時刻  $t_6$  で信号  $S_{31b}$  が立下がる。

#### 【0034】

ここで、レジスタ32の設定値を“0001”とすれば、信号  $S_{16}$  と同じタイミングの信号が信号  $S_{39}$  として出力される。また、レジスタ32の設定値を“0010”とすれば、信号  $S_{31a}$  と同じタイミングの信号が信号  $S_{39}$  として出力され、更にレジスタ32の設定値を“0100”とすれば、信号  $S_{31b}$  と同じタイミングの信号が信号  $S_{39}$  として出力される。

10

#### 【0035】

また、レジスタ32のビット0～2の内の2ビットを“1”に設定することにより、信号  $S_{16}$  及び信号  $S_{31a}$  ,  $S_{31b}$  を組合せたタイミングの信号を信号  $S_{39}$  として出力することができる。例えば、レジスタ32の設定値を“0011”とすれば、時刻  $t_1$  ～  $t_5$  の幅を有する信号  $S_{39}$  が得られる。また、レジスタ32の設定値を“0101”とすれば、時刻  $t_1$  ～  $t_6$  の幅を有する信号  $S_{39}$  が得られ、この設定値を“0110”とすれば、時刻  $t_2$  ～  $t_6$  の幅を有する信号  $S_{39}$  が得られる。

20

#### 【0036】

更に、レジスタ32のビット3を“1”に設定することにより、それぞれビット0～2で指定した信号  $S_{16}$  ,  $S_{31a}$  ,  $S_{31b}$  ,  $S_{39}$  の反転信号を得ることができる。

#### 【0037】

次に、図1の動作を、(I)入力モードと、(II)出力モードに分けて説明する。

##### (I) 入力モード

内部バス11を介して入出力制御レジスタ12に、入力モードを設定すると、この入出力制御レジスタ12から出力される入力モード信号INが“H”となる。一方、入出力制御レジスタ12から出力される出力モード信号OUTは“L”となり、デコーダ24の出力信号は2つとも“L”となって出力バッファ17a , 17bの出力側はハイインピーダンス状態となって入出力端子18から切離される。

30

#### 【0038】

また、入出力端子18に接続される外部回路の出力条件がTTLレベルかCMOSレベルかに基づいて、入力切替レジスタ23に“1”または“0”を設定する。ここで、入力切替レジスタ23に“1”を設定すると、デコーダ25のAND25aの出力信号が“H”となり、入出力端子18はTTLレベルの入力バッファ19aを介して内部バス11に接続される。一方、入力切替レジスタ23に“0”を設定すると、デコーダ25のAND25bの出力信号が“H”となり、入出力端子18はCMOSレベルの入力バッファ19bを介して内部バス11に接続される。

#### 【0039】

更に、入出力端子18をプルアップする場合、プルアップ制御レジスタ15に“1”を設定する。これにより、NAND20の出力信号が“L”となり、PMOS21がオン状態になって入出力端子18がプルアップされる。一方、プルアップ制御レジスタ15に“0”を設定すると、NAND20の出力信号は“H”となり、PMOS21はオフ状態となってプルアップは行われない。

40

#### 【0040】

このように、入力切替レジスタ23によって入力レベルの設定を行って入力バッファ19a , 19bのいずれかを選択し、プルアップ制御レジスタ15によってプルアップの要否を設定することにより、この入出力回路は、外部回路のインターフェース条件に合った入力回路に設定される。そして、入出力端子18に入力された入力信号は、入力バッファ19aまたは19bを介して内部バス11へ出力される。

50

## 【0041】

## (11) 出力モード

内部バス11を介して入出力制御レジスタ12に、出力モードを設定すると、この入出力制御レジスタ12から出力される出力モード信号OUTが“H”となる。一方、入出力制御レジスタ12から出力される入力モード信号INは“L”となり、デコーダ25の出力信号は2つとも“L”となって入力バッファ19a, 19bの出力側はハイインピーダンス状態となって内部バス11から切離される。更に、NAND20の出力信号は“H”となって、PMOS21はオフ状態となる。

## 【0042】

また、入出力端子18に接続される外部回路の負荷の大小に基づいて、出力切替レジスタ22に“1”または“0”を設定する。ここで、出力切替レジスタ22に“1”を設定すると、デコーダ24のAND24aの出力信号が“H”となり、遅延回路30の出力側は、駆動能力の大きな出力バッファ17aを介して入出力端子18に接続される。一方、出力切替レジスタ22に“0”を設定すると、デコーダ24のAND24bの出力信号が“H”となり、遅延回路30の出力側は、駆動能力の小さな出力バッファ17bを介して入出力端子18に接続される。

## 【0043】

更に、内部バス11から遅延回路30に対して遅延時間を設定すると共に、出力データレジスタ14に格納されたデータ及び2次機能出力信号のいずれを出力するかの制御信号を、2次機能制御レジスタ13に設定する。

これにより、セレクタ16で選択された出力信号が、遅延回路30で所定の時間だけ遅延され、出力バッファ17aまたは17bで所定の電力に増幅されて入出力端子18に出力され、この入出力端子18に接続された外部回路が駆動される。

## 【0044】

このように、本実施形態の入出力回路は、次の(1)~(3)のような利点がある。

(1) 出力モード時に、アドレス信号等の2次機能出力信号や出力データの出力タイミングを任意の時間だけ遅延させたり、出力する信号の時間を増減することができる遅延回路30を有している。これにより、この入出力回路を外部バス機能として使用した場合に、2次機能として出力するアドレス信号、データ信号、及びストローブ信号等の出力タイミングを変更することが可能となり、入出力端子18に接続されるSRAM等の外部回路のタイミング条件に合わせることができる。また、クロック同期式シリアルポートの出力回路として使用する場合、送信用クロック信号及び送信データのタイミングを変更することができる所以、通信相手となる外部回路の周辺装置に合わせて、送信データセットアップ時間や送信データホールド時間を調整することができる。これにより、接続可能な外部回路の種類を増やすことができる。

## 【0045】

(2) 駆動能力の異なる出力バッファ17a, 17bを有すると共に、これらの出力バッファ17a, 17bを切替えるための出力切替レジスタ22及びデコーダ24を有している。これにより、外部回路の負荷容量の増大により、能力の小さな出力バッファ17bでは駆動能力が不足した場合に、駆動能力の大きな出力バッファ17aに切替えることにより、出力信号の鈍りによる遅延を解消することができる。また、2次機能である外部バス機能及び同期式シリアルポート使用時にも、駆動能力を変更することができるので、出力信号の立ち上がりを速くしたり、遅くしたりすることで、出力信号のセットアップ時間及びホールド時間を調整することができる。

## 【0046】

(3) 入力レベルの異なる入力バッファ19a, 19bを有すると共に、これらの入力バッファ19a, 19bを切替えるための入力切替レジスタ23及びデコーダ25を有している。これにより、外部回路の出力条件に合わせることができるので、接続可能な外部回路の種類を増やすことができる。また、外部バス機能及び同期式シリアルポート使用時にも、入力レベルを変更することができるので、入力信号の取り込みを速くしたり、遅く

10

20

30

40

50

したりすることで、入力信号のセットアップ時間及びホールド時間を調整することが可能である。

【0047】

なお、本発明は、上記実施形態に限定されず、種々の変形が可能である。この変形例としては、例えば、次の(a)～(f)のようなものがある。

(a) 遅延回路30の構成は、図4に限定されない。即ち、遅延素子を3個以上に増加して設定できる遅延時間の数を増やすことができる。これにより、時間調整範囲が広がり接続可能な外部回路の種類を更に増やすことができる。また、遅延素子にカウンタを用いることによりクロックベースで遅延時間の調整が可能である。

【0048】

(b) 遅延回路30は、レジスタ32によって遅延時間の設定がプログラム可能になっているが、このレジスタ32に代えて遅延時間設定用のスイッチや外部端子を設けても良い。このような設定スイッチ等は、電源投入当初の初期設定以前に、正常な動作が必要な入出力回路の場合に有効である。

【0049】

(c) 選択可能な入力バッファや出力バッファの数は2つに限定されない。例えば、入力バッファの種類は、TTLやCMOS等のレベル変換を行うものに限定されず、ヒステリシス特性を有するシュミット回路等を使用することもできる。入力バッファや出力バッファの数や種類を多くすることにより、接続可能な外部回路の種類を更に増やすことができる。

【0050】

(d) プルアップ制御レジスタ15と出力切替レジスタ22は、同時に使用することはないので、共用することが可能である。或いは、入力切替レジスタ23と出力切替レジスタ22を共用しても良い。

【0051】

(e) 外部回路の出力レベルが、例えばCMOSに決まっているのであれば、2種類の入力バッファを設ける必要はない。その場合、入力切替レジスタ23及びデコーダ25は不要となる。

【0052】

(f) 外部回路に対する駆動能力を切替える必要がなければ、2種類の出力バッファを設ける必要はない。その場合、出力切替レジスタ22及びデコーダ24は不要となる。

【0053】

【発明の効果】

以上詳細に説明したように、第1の発明(請求項1、5、6に係る発明)によれば、入出力端子に出力するデータまたは信号を、遅延させる遅延手段を有している。この遅延手段では、複数の遅延信号を生成して、これら遅延信号のいくつかを組合せた信号を生成してこれを出力信号として入出力端子へ出力する構成になっているので、入出力端子に出力する信号を任意の時間だけ遅延させたり、出力する信号の時間を増減することができる。これにより、外部回路のタイミング条件に合わせることが可能になり、タイミング条件が異なる各種のメモリや周辺回路に適合させて、効率の良い入出力動作が可能になる。

【0054】

第2の発明(請求項2、5、6に係る発明)によれば、予め選択した駆動能力を有する出力バッファを介してデータまたは信号を出力する出力手段を有している。これにより、外部回路の負荷容量に見合った出力バッファを使用することが可能になり、効率の良い入出力動作が可能になる。

【0055】

第3の発明(請求項3～6に係る発明)によれば、予め選択した入力特性を有する入力バッファを介してデータまたは信号を入力する入力手段を有している。これにより、外部回路の出力条件に合致した入力バッファを使用することが可能になり、各種の外部回路に対応することができる。

10

20

30

40

50

## 【図面の簡単な説明】

【図1】本発明の実施形態を示す入出力回路の構成図である。

【図2】従来の入出力回路の一例を示す構成図である。

【図3】S R A M のデータ書き込み時の信号タイミングを示す信号波形図である。

【図4】図1中の遅延回路30の一例を示す回路図である。

【図5】図4の遅延回路30の機能を説明するための信号波形図である。

## 【符号の説明】

|               |             |    |

|---------------|-------------|----|

| 1 1           | 内部バス        |    |

| 1 2           | 入出力制御レジスタ   |    |

| 1 3           | 2次機能制御レジスタ  | 10 |

| 1 4           | 出力データレジスタ   |    |

| 1 5           | プルアップ制御レジスタ |    |

| 1 6           | セレクタ        |    |

| 1 7 a , 1 7 b | 出力バッファ      |    |

| 1 8           | 入出力端子       |    |

| 1 9 a , 1 9 b | 入力バッファ      |    |

| 2 0           | N A N D     |    |

| 2 1           | P M O S     |    |

| 2 2           | 出力切替レジスタ    | 20 |

| 2 3           | 入力切替レジスタ    |    |

| 2 4 , 2 5     | デコーダ        |    |

【図1】

本発明の実施形態の入出力回路

【図2】

従来の入出力回路

【図3】

S R A M のデータ書き込み時の信号タイミング

【図4】

図1中の遅延回路30

【図5】

図4の信号波形

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H03K19/00,19/01-19/082,19/092-19/096

G06F3/00,3/18,13/10-13/14,15/78