(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5156434号

(P5156434)

(45) 発行日 平成25年3月6日(2013.3.6)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

F 1

H04N 5/357 (2011.01)

H04N 5/335 570

H04N 5/374 (2011.01)

H04N 5/335 740

H04N 5/378 (2011.01)

H04N 5/335 780

請求項の数 9 (全 13 頁)

(21) 出願番号

特願2008-51122(P2008-51122)

(22) 出願日

平成20年2月29日(2008.2.29)

(65) 公開番号

特開2009-212604(P2009-212604A)

(43) 公開日

平成21年9月17日(2009.9.17)

審査請求日

平成23年2月24日(2011.2.24)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配列された複数の画素を有する画素アレイを備える撮像装置であつて、

前記画素アレイから出力される信号を処理する信号処理回路と、共通読出し線と、

前記共通読出し線に接続された第1入力端子、および第2入力端子を有し、前記第1入力端子に入力される信号に応じたレベルと前記第2入力端子に供給されるレベルとの差分を増幅して、第1出力線に非反転出力信号を出力するとともに第2出力線に反転出力信号を出力する増幅部と、

リセット信号に応答して前記第1出力線と前記第2出力線とを短絡するスイッチと、基準レベル供給部と、を備え、前記信号処理回路は、

前記画素アレイからの信号を読み出すために、各々が前記画素アレイの列に対応して設けられた複数の列読出し回路と、

前記複数の列読出し回路のそれぞれの出力と前記共通読出し線との間にそれぞれ配置された複数の列選択スイッチと、

前記複数の列読み出し回路のそれぞれの出力と前記基準レベル供給部との間にそれぞれ配置された複数の入力側リセットスイッチと、を含み、

前記共通読出し線は、前記基準レベル供給部から供給される基準レベルによって、前記複数の列選択スイッチのうちオン状態の列選択スイッチおよび前記複数の入力側リセット

10

20

スイッチのうち当該オン状態の列選択スイッチに対応する入力側リセットスイッチを通してリセットされる、

ことを特徴とする撮像装置。

**【請求項 2】**

前記第2入力端子に前記基準レベル供給部が接続されて前記基準レベルが供給されることを特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記入力側リセットスイッチは、前記リセット信号に同期して制御されることを特徴とする請求項1又は2に記載の撮像装置。

**【請求項 4】**

前記增幅部は、前記画素アレイの複数の列に対して共通に設けられていることを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

10

**【請求項 5】**

前記撮像装置は、第1出力パッド及び第2出力パッドを有する半導体チップとして構成され、

前記第1出力パッドに前記第1出力線が接続され、前記第2出力パッドに前記第2出力線が接続される

ことを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

**【請求項 6】**

前記半導体チップは、前記リセット信号を受ける入力パッドを更に有することを特徴とする請求項5に記載の撮像装置。

20

**【請求項 7】**

前記第1出力線と前記第2出力線とを短絡する前記スイッチは、ゲートに供給される前記リセット信号に応答して前記第1出力線と前記第2出力線とを短絡するMOSトランジスタを含むことを特徴とする請求項1乃至6のいずれか1項に記載の撮像装置。

**【請求項 8】**

前記半導体チップは、前記リセット信号を反転させた論理レベルを有する反転リセット信号を受ける第2入力パッドを更に有し、

前記リセット信号はアクティブルーレベルがハイレベルであり、前記反転リセット信号はアクティブルーレベルがローレベルであり、

30

前記第1出力線と前記第2出力線とを短絡する前記スイッチは、ゲートに供給される前記リセット信号に応答して前記第1出力線と前記第2出力線とを短絡するNMOSトランジスタと、ゲートに供給される前記反転リセット信号に応答して前記第1出力線と前記第2出力線とを短絡するPMOSトランジスタとを含む、

ことを特徴とする請求項6に記載の撮像装置。

**【請求項 9】**

請求項1乃至8のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面への像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備えることを特徴とする撮像システム。

40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像装置およびそれを備える撮像システムに関する。

**【背景技術】**

**【0002】**

C MOSイメージセンサ等の撮像装置では、画像信号の出力速度の高速化を図るため、転送用に速いクロックが必要となる。クロックの周波数を高くすると、水平方向に画素からの信号を伝達する共通読出し線の寄生抵抗や寄生容量が無視できなくなり、その容量を充放電する時間が無視できなくなる。これは、例えば、撮像装置からの出力信号又は撮像

50

装置の内部における信号の波形が鈍る現象として把握される。

【特許文献 1】特開 2003-234957 号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

クロック信号の周波数がある程度以上に高くなると、信号波形のレベルが、次の信号が入力されるまでに元のレベルに戻らないという現象が生じる。この現象に対処する発明として、たとえば特許文献 1 にその一例をみることができる。この発明では、撮像装置の出力段に差動增幅回路を備え、鈍った信号波形でも、なるべく正しい信号が得られるように工夫されている。しかしながら、画像信号の出力速度を更に高速にするには、さらなる工夫が必要とされる。10

【0004】

本発明は、上記の背景に基づいてなされたものであり、例えば、撮像装置からの信号出力の高速化に有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明の 1 つの側面は、行列状に配列された複数の画素を有する画素アレイを備える撮像装置に係り、前記撮像装置は、前記画素アレイから出力される信号を処理する信号処理回路と、共通読出し線と、前記共通読出し線に接続された第 1 入力端子、および、第 2 入力端子を有し、前記第 1 入力端子に入力される信号に応じたレベルと前記第 2 入力端子に供給されるレベルとの差分を増幅して、第 1 出力線に非反転出力信号を出力するとともに第 2 出力線に反転出力信号を出力する増幅部と、リセット信号に応答して前記第 1 出力線と前記第 2 出力線とを短絡するスイッチと、基準レベル供給部と、を備え、前記信号処理回路は、前記画素アレイからの信号を読み出すために、各々が前記画素アレイの列に対応して設けられた複数の列読出し回路と、前記複数の列読出し回路のそれぞれの出力と前記共通読出し線との間にそれぞれ配置された複数の列選択スイッチと、前記複数の列読み出し回路のそれぞれの出力と前記基準レベル供給部との間にそれぞれ配置された複数の入力側リセットスイッチと、を含み、前記共通読出し線は、前記基準レベル供給部から供給される基準レベルによって、前記複数の列選択スイッチのうちオン状態の列選択スイッチおよび前記複数の入力側リセットスイッチのうち当該オン状態の列選択スイッチに対応する入力側リセットスイッチを通してリセットされる。20

【発明の効果】

【0006】

本発明によれば、例えば、撮像装置からの信号出力の高速化に有利な技術を提供することができる。

【発明を実施するための最良の形態】

【0007】

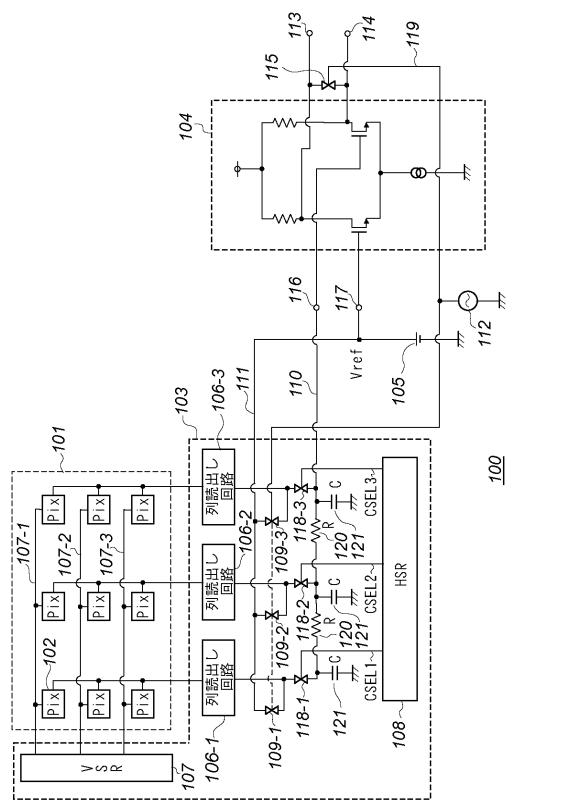

本発明の好適な実施形態について、図 1 から図 9 までの図を参照しながら説明する。

[第 1 実施形態]

図 1 は本発明の撮像装置の第 1 実施形態を示すブロック図である。40

【0008】

本発明の好適な実施形態の撮像装置 100 は、画素アレイ 101、信号処理回路 103、増幅部の一部としての増幅回路 104、基準レベル供給部 105、およびリセットタイミング供給部 112 を備える。画素アレイ 101 は、列方向と行方向の 2 次元状に配置された複数の画素 102 を有し、各画素は光量を電荷に変換する。信号処理回路 103 は、垂直シフトレジスタ 107、水平シフトレジスタ 108、列読出し回路 106-1 ~ 106-3 を含む。行選択回路あるいは垂直走査回路としての垂直シフトレジスタ 107 は、行選択線 107-1 ~ 107-3 によって画素アレイ 101 の行を選択する。選択された行に属する画素の信号は、列読出し回路 106-1 ~ 106-3 によって読み出される。列選択回路あるいは水平走査回路としての水平シフトレジスタ 108 は、複数の列選択スイッチ 109 を含む。各列選択スイッチ 109 は、各列読出し回路 106 と接続され、各列選択スイッチ 109 の出力は、各列選択回路 107 と接続される。各列選択回路 107 の出力は、各増幅回路 104 と接続される。各増幅回路 104 の出力は、各基準レベル供給部 105 と接続される。各基準レベル供給部 105 の出力は、各リセットタイミング供給部 112 と接続される。各リセットタイミング供給部 112 の出力は、各画素アレイ 101 と接続される。50

チ 1 1 8 - 1 ~ 1 1 8 - 3 を複数の列選択線 C S E L 1 ~ C S E L 3 を介し、所定の順序で選択される。そして選択された列読出し回路 1 0 6 - 1 ~ 1 0 6 - 3 の出力を共通読み出し線 1 1 0 に伝達させる。

#### 【 0 0 0 9 】

信号処理回路 1 0 3 から共通読み出し線 1 1 0 に出力された信号は、増幅部としての増幅回路 1 0 4 で増幅される。また、増幅回路 1 0 4 の 2 つの入力を基準レベルに合わせるために、基準レベル供給部 1 0 5 と、基準レベルタイミングを与えるリセット信号 1 1 9 を出力するリセットタイミング供給部 1 1 2 が備えられる。共通読み出し線 1 1 0 上の信号又はレベルは、増幅回路 1 0 4 の第 1 入力端子に供給され、基準レベル供給部 1 0 5 から出力される基準レベル ( $V_{ref}$ ) は、増幅回路 1 0 4 の第 2 入力端子に供給される。また、基準レベル供給部 1 0 5 は、リセット線 1 1 1 から入力側スイッチ 1 0 9 - 1 ~ 1 0 9 - 3 を介して、共通読み出し線 1 1 0 へ基準レベルの電位を与える。リセットタイミング供給部 1 1 2 が、入力側スイッチ 1 0 9 - 1 ~ 1 0 9 - 3 をオンにするタイミング信号を活性化することで、共通読み出し線 1 1 0 のレベルが基準レベルに設定される。この動作により、増幅回路 1 0 4 から第 1 出力線 1 1 3 および第 2 出力線 1 1 4 に出力される信号のレベルが互いに近づくように増幅回路 1 0 4 が動作する。10

#### 【 0 0 1 0 】

図 1において、差動増幅回路として構成された増幅回路 1 0 4 の例が示されている。共通読み出し線 1 1 0 を介して増幅回路 1 0 4 の第 1 入力端子 1 1 6 に供給される信号又はレベルと増幅回路 1 0 4 の第 2 入力端子 1 1 7 に供給される基準レベルとの差分の信号が、増幅される。そして非反転信号として増幅回路 1 0 4 の第 1 出力線 1 1 3 に出力され、その反転信号が第 2 出力線 1 1 4 に出力される。この非反転出力信号と反転出力信号の波形出力は、基準レベルに関し対象となる。20

#### 【 0 0 1 1 】

第 1 出力線 1 1 3 と第 2 出力線 1 1 4 との間には、それらを短絡するためのスイッチ 1 1 5 が備えられる。リセットタイミング供給部 1 1 2 からスイッチ 1 1 5 にリセット信号 1 1 9 を供給することにより、このスイッチ 1 1 5 が導通状態となる。すなわち、第 1 出力線 1 1 3 と第 2 出力線 1 1 4 とを短絡させることにより、たとえ基準レベルに対する電位差が大きな信号が増幅回路 1 0 4 に入力されても、次の信号が入力されるまでに、その信号出力を共通電位  $V_{com}$  に強制的に設定することが可能となる。第 1 実施形態においては、1 つのリセットタイミング供給部 1 1 2 、によりスイッチ 1 1 5 と共に読み出し線 1 1 0 のレベルをリセットするタイミングを供給する構成をとっている。しかしながら、バッファなどを用いて、共通読み出し線 1 1 0 のレベルをリセットするタイミングに同期させた信号を別に用意して、スイッチ 1 1 5 の両端子を導通させても良い。また、2 つのリセットタイミング供給部を用いて、別々にタイミングを供給しても良い。30

#### 【 0 0 1 2 】

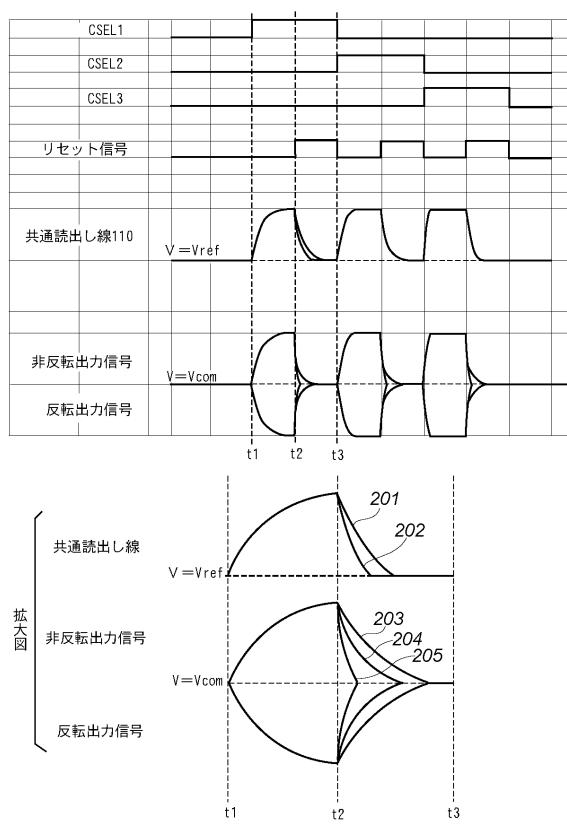

図 2 に、第 1 実施形態についての主要信号のタイミング関係を示す。

#### 【 0 0 1 3 】

時刻  $t_1$  において、列読出し回路 1 0 6 - 1 ~ 1 0 6 - 3 のうち列読出し回路 1 0 6 - 1 が選択され、共通読み出し線 1 1 0 の出力にその信号波形が現れる。リセット信号 1 1 9 は、この信号出力が完了した時刻  $t_2$  から次の信号が出力される時刻  $t_3$  までの間、スイッチ 1 1 5 及び入力側リセットスイッチ 1 0 9 - 1 ~ 1 0 9 - 3 に供給される。いま、共通読み出し線 1 1 0 の増幅回路 1 0 4 付近での入力波形は、例えば図 2 のような波形となる。ここで注目すべきは、3 つの列読出し回路 1 0 6 - 1 ~ 1 0 6 - 3 の物理的な配置の相違により、増幅回路 1 0 4 付近の信号入力波形が異なることである。すなわち増幅回路 1 0 4 からもっとも遠い入力側リセットスイッチ 1 0 9 - 1 付近から送信された共通読み出し線 1 1 0 の信号は、共通読み出し線 1 1 0 の寄生抵抗 1 2 0 と寄生容量 1 2 1 の影響を最も大きく受ける。したがって、例えば時刻  $t_2$  から時刻  $t_3$  の期間において、図 2 の共通読み出し線 1 1 0 の信号波形 2 0 1 に示すように、かなり波形が鈍ってしまう。すなわち、基準レベルに戻る時間が長くなる。反対に、最も近いスイッチ 1 0 7 c からの信号の増幅回4050

路 104への共通読出し線 110の信号波形に関しては、共通読出し線 110の寄生抵抗 120と寄生容量 121の影響をあまり受けない。したがって、図 2 に示す波形 202 に示すように、その波形は比較的シャープであり、基準レベルに戻る時間も短くなる。

#### 【0014】

増幅回路 104 の出力は、この 2 つの入力の差分を増幅して出力されるので、その出力はこの入力波形からさらに鈍ってしまうことになる。その結果、図 2 の第 1 出力線 113 に出力される非反転出力および第 2 出力線 114 に出力される反転出力の信号は、図 2 の波形 203, 204 のように、かなりの時間をかけてなだらかに基準レベルに戻ことになる。もし第 1 入力端子 116 の信号が基準レベルに対して著しく大きくなると、次の信号がはじめの信号に埋もれてしまう可能性があることがわかる。

10

#### 【0015】

したがって、本発明の好適な実施形態では、リセット信号供給部 112 からリセット信号 119 をスイッチ 115 に供給し、リセット信号 119 にスイッチ 115 が応答して、第 1 出力線 113 と第 2 出力線 114 とを短絡させる。ここで、リセット信号 119 は、出力が完了した時刻  $t_2$  から次の信号が出力される時刻  $t_3$ までの間、スイッチ 115 及び入力側リセットスイッチ 109 - 1 ~ 109 - 3 に供給される。この結果、非反転出力信号が出力される第 1 出力線 113 と反転出力信号が出力される第 1 出力線 114 のレベルを共通レベル  $V_{com}$  に高速に設定することが可能となる。第 1 出力線 113 と第 2 出力線 114 がスイッチ 115 で短絡されると、第 1 出力線 113 の非反転出力信号と第 2 出力線 114 の反転出力信号 114 の波形 205 は、短絡されない波形、203 と 204 に比べて短時間で共通電位  $V_{com}$  に設定される。これにより、共通読出し線の寄生抵抗 120 および寄生容量 121 に無関係に、非反転出力信号と反転出力信号のレベルが共通電位  $V_{com}$  に急速に設定させることが可能となる。

20

#### 【0016】

##### [第 2 実施形態]

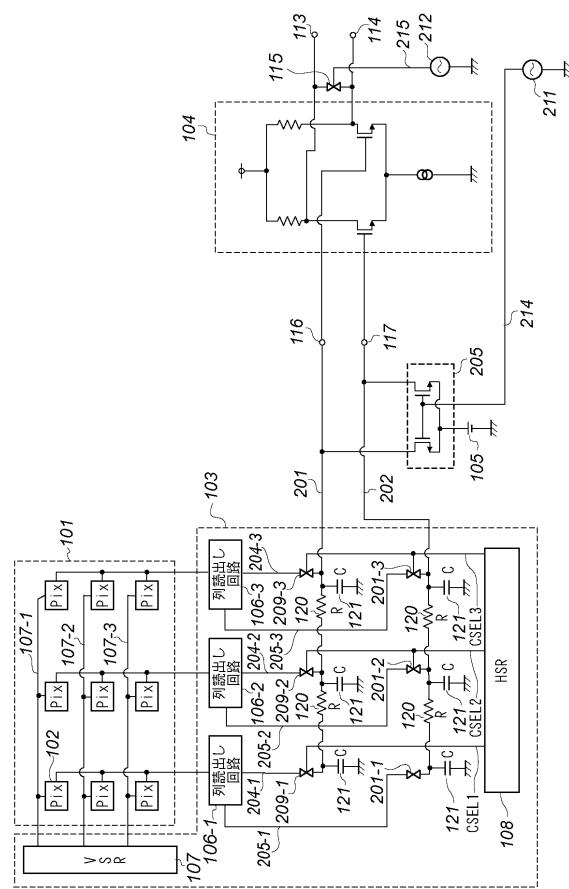

図 3 および図 4 に本発明の第 2 実施形態のブロック図およびタイミング図を示す。

#### 【0017】

第 2 実施形態には、第 1 実施形態と同様に、画素アレイ 101、信号処理回路 103、増幅回路 104、基準レベル供給部 105、およびリセットタイミング供給部を備える。第 1 実施形態と異なるのは、共通読み出し線 110 に代えて第 1 共通読み出し線 201 及び第 2 共通読み出し線 202 を設けていることである。

30

#### 【0018】

第 1 共通読み出し線 201 へ、画素アレイ 101 からの信号と列信号読み出し回路 106 - 1 ~ 106 - 3 の（素子の製造バラツキなど、他の要因によってもオフセットは発生します）オフセット電圧が第 1 転送線 204 - 1 ~ 204 - 3 により転送される。そして、第 2 共通読み出し線 201 へは、列読み出し回路 106 - 1 ~ 106 - 3 のオフセット電圧のみが第 2 転送線 205 - 1 ~ 205 - 3 により転送される。水平シフトレジスタ 108 は、第 1 入力側スイッチ 209 - 1 ~ 209 - 3 と第 2 入力側スイッチ 201 - 1 ~ 201 - 3 を選択的にオンさせて、複数の列読み出し回路 106 - 1 ~ 106 - 3 を所定の順序で選択する。

40

#### 【0019】

列読み出し回路 106 - 1 ~ 106 - 3 からの画像およびオフセット信号を、第 1 共通読み出し線 201 を介して増幅回路 104 の第 1 入力端子 116 に入力するため、第 1 入力側スイッチ 209 - 1 ~ 209 - 3 が備えられる。また、列読み出し回路 106 - 1 ~ 106 - 3 から出力されるオフセット電圧を第 2 共通読み出し線 202 を介して増幅回路 104 の第 2 入力端子 117 に入力するため、第 2 入力側スイッチ 201 - 1 ~ 201 - 3 が備えられる。

#### 【0020】

リセット信号 214, 215 の供給にも、2つのリセット信号供給部、すなわち第 1 リセット信号供給部 210 と第 2 リセット信号供給部 211 が備えられる。第 1 リセット信

50

号供給部 211 は、入力側リセットスイッチ 205 に第 1 リセット信号 214 を供給することにより、第 1 共通読出し線 201 を基準レベルにリセットすると同時に、增幅回路 104 の第 2 入力端子 117 へ基準レベルを供給する。また、第 2 リセット信号供給部 212 は、スイッチ 115 に第 2 リセット信号 215 を供給する。この動作により、第 1 共通読出し線 201 と第 2 共通読出し線 202 が基準レベルに設定され、增幅回路 104 から第 1 出力線 113 および第 2 出力線 114 に出力される信号のレベルが互いに近づくよう 10 に増幅回路 104 が動作する。

#### 【0021】

この動作により、第 1 共通読出し線 201 と第 2 共通読出し線 202 が基準レベルに設定され、增幅回路 104 から第 1 出力線 113 および第 2 出力線 114 に出力される信号のレベルが互いに近づくよう 10 に増幅回路 104 が動作する。

#### 【0022】

したがって、この実施形態では、共通読出し線 201, 202 を 2 本にし、その差分信号をとりだすことにより、オフセット電圧を除くことができる。また、共通読み出し線 201, 202 が並行して配列されていると、外乱ノイズは双方の共通読み出し線に同様に作用するので外乱ノイズによる成分を除去することができるので、外乱のノイズに強い読み出しが可能となる。

#### 【0023】

また、非反転信号出力信号と反転信号出力信号も共通電位に対し対象的な反転信号になる。このため、増幅回路 104 の第 1 出力線 113 と第 2 出力線を短絡したとき 2 入力のアンバランスの影響がなく、共通電位 Vcom に近づき、高速なリセットが可能となる。 20

#### 【0024】

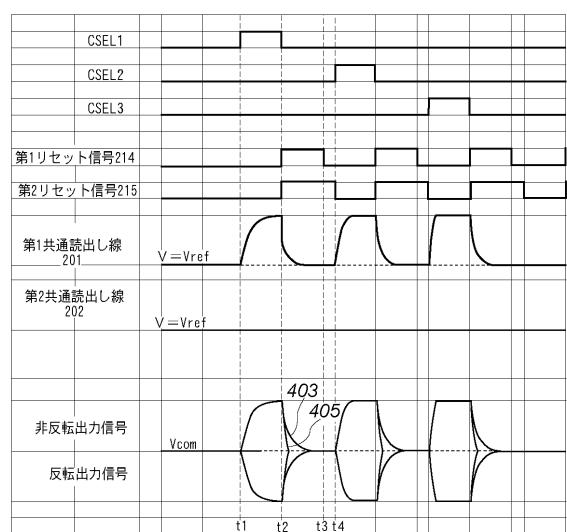

図 4 に主要信号のタイミング動作を示す。

#### 【0025】

時刻 t1において、列読出し回路 106-1 ~ 106-3 のうち列読出し回路 106-1 が選択され、第 1 共通読出し線 201 の出力と第 2 共通読出し線 202 にその信号波形が現れる。第 1 リセット信号 211 は、この信号の出力が完了する時刻 t2 から時刻 t3 までの間、スイッチ 205 に供給される。また、時刻 t2 から次の信号が出力される時刻 t4 までの間、スイッチ 115 に供給される。第 1 出力線 113 と第 2 出力線 114 がスイッチ 115 により短絡された場合、第 1 出力線 113 の非反転出力信号および第 2 出力線 114 の反転出力信号 405 は、短絡されない場合の波形、403 に比べて短時間で共通電位、Vcom に設定される。これにより、共通読出し線の寄生抵抗 120 および寄生容量 121 に無関係に、非反転出力信号と反転出力信号のレベルを共通電位 Vcom に急速に設定させることができる。 30

#### 【0026】

しかしながら、第 1 リセット信号供給部 211 の立ち下がり時刻 T = t3 と、第 1 入力側スイッチ 209-1 ~ 209-3 及び第 2 入力側スイッチ 201-1 ~ 201-3 がオンする時刻 T = t4 との間には、時間的な遅れが必要となる。理想的には、第 1 リセット信号供給部の立下りと同時に第 1 入力側スイッチ 209-1 ~ 209-3 と第 2 入力側スイッチ 201-1 ~ 201-3 がオンすれば良い。しかし、第 1 リセット信号供給部 211 の立ち下がりタイミングと第 1 入力側スイッチ 209-1 ~ 209-3 と第 2 入力側スイッチ 201-1 ~ 201-3 のオンタイミングが重なると列読出し回路 106-1 ~ 106-3 の信号の一部がリセットされてしまう。この現象により第 1 共通読出し線 201 と第 2 共通読出し線 202 において、その信号が時刻 t3 ~ t4 の期間、基準レベルへのリセットも転送もされないことになる。 40

#### 【0027】

一方、スイッチ 115 を作動させる第 2 リセット信号供給部 212 は、第 1 入力側スイッチ 209-1 ~ 209-3 と第 2 入力側スイッチ 201-1 ~ 201-3 がオンとなるタイミングと重なっても良い。なぜなら、列読出し回路 106-1 ~ 106-3 の信号の一部がリセットされてしまう恐れはなく、第 2 リセット信号供給部 212 は増幅回路 10 50

4の第1出力線113と第2出力線114を導通させ、2つの出力信号を短絡しているだけであるからである。そこで、第2リセット信号供給部212のスイッチ115に供給するタイミングは第1入力側スイッチ209-1~209-3と第2入力側スイッチ201-1~201-3の立ち下がりの時刻t3と重ねてしまっても問題ない。こうすることで、基準レベルへの設定と転送のための時間を有効に使用することができる。

#### 【0028】

また、入力側リセットスイッチ205の配置を増幅回路104の近傍にすると、スイッチ115に対しても近くなるので、第1リセット信号供給部211と第2リセット信号供給部212の同期がとり易くなる。近傍に配置することで、時間遅れなどの問題が軽減し、基準レベルへの設定と転送の時間を更に有効に利用することができる。

10

#### 【0029】

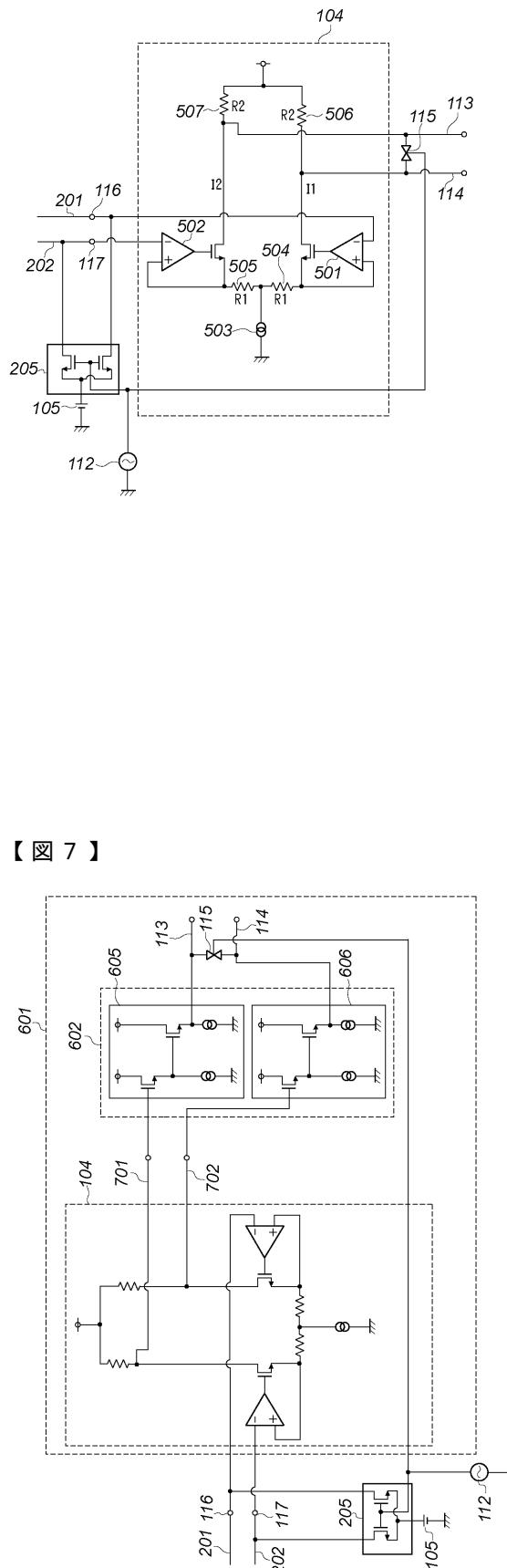

[第3実施形態]

図5は本発明の第3実施形態を示した回路図である。本実施形態は、第1と第2実施形態と増幅回路の構成が異なるものである。増幅回路の第1入力端子と第2入力端子に至るまでの構成は、図3に示す第2の実施形態と同一である。この増幅回路には、まず2つのオペアンプ501、502を有し、負の入力端子には、各々第1入力端子201と第2入力端子202に接続される。増幅回路104にはこのオペアンプのほかに、定電流源503および抵抗を有する。抵抗504と抵抗505は抵抗値R1の抵抗素子であり、抵抗506と抵抗507は抵抗値R2の抵抗素子である。本回路の電源電圧をVDDとし、抵抗504と抵抗506に流れる電流をI1とする。また、抵抗505と抵抗507に流れる電流をI2とし、抵抗504と、抵抗505の接続されている点の電位をV0とする。更に、第1共通読出し線201と第2共通読出し線202の電位それぞれ、Vchs、Vchn、その出力をVout、VoutBとすると、増幅回路の2出力差と2入力差の関係は次のように、表わされる。

20

#### 【0030】

$$V_{out} = V_{DD} - R_2 * I_2 \quad (1)$$

$$V_{outB} = V_{DD} - R_2 * I_1 \quad (2)$$

これらから、

$$V_{out} - V_{outB} = R_2 * (I_1 - I_2) \quad (3)$$

一方、

$$V_{chs} = V_0 + R_1 * I_1 \quad (4)$$

$$V_{chn} = V_0 + R_1 * I_2 \quad (5)$$

これらから、

$$V_{chs} - V_{chn} = R_1 * (I_1 - I_2) \quad (6)$$

(3)式と(6)式から

$$V_{out} - V_{outB} = (R_2 / R_1) * (V_{chs} - V_{chn}) \quad (7)$$

が得られる。

30

#### 【0031】

増幅回路104を図5の構成にすることで、入力電圧の差電圧に対してR2/R1のゲインとの積になる関係が得られ、リニアリティの良好な出力を得られることがわかる。

40

#### 【0032】

もちろん、スイッチ115を増幅回路104の出力に備え短絡することで、本実施形態においても非反転出力信号113と反転出力信号114を共通電位レベルVcomに強制的に設定させることが可能となる。

#### 【0033】

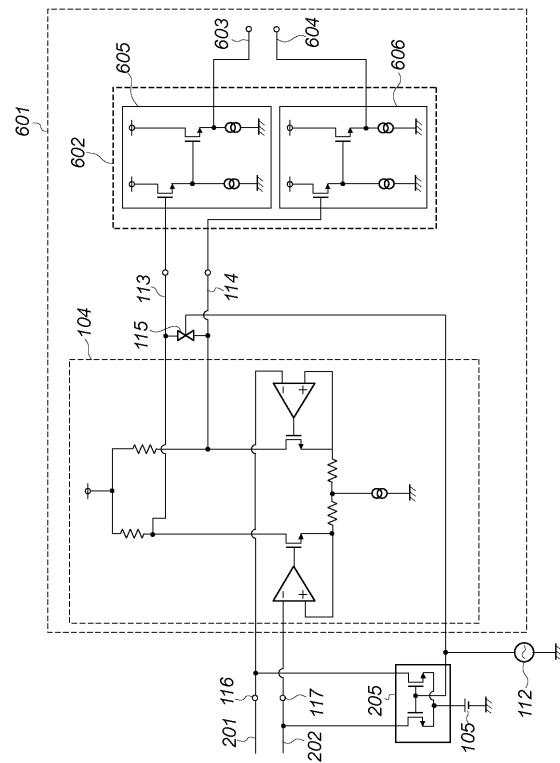

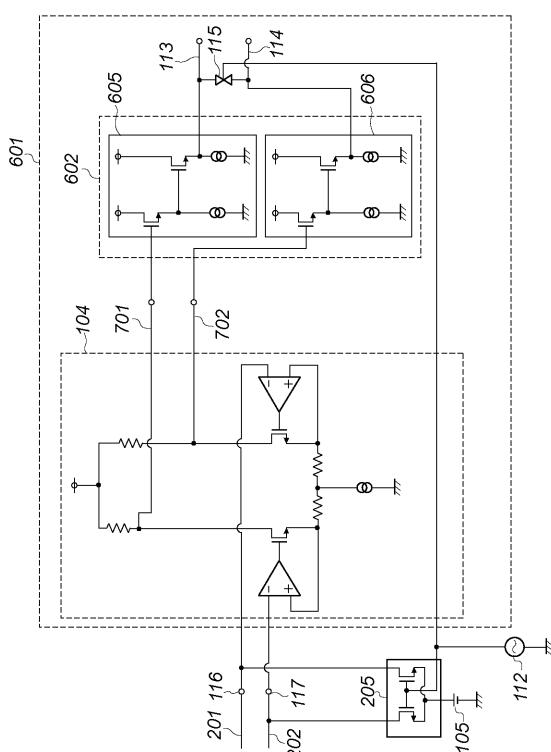

[第4実施形態]

図6は本発明の第4実施形態を示した回路図である。図6において、増幅部601は、増幅回路104およびバッファ回路602を有する。

#### 【0034】

本実施形態が第3実施形態と異なる点は、増幅回路104に続くスイッチ115の後段

50

に、外部に対してバッファリングするバッファ回路 602 を設けていることにある。バッファ回路 602 は、増幅回路 104 の第 1 出力線 113 と第 2 出力線 114 から出力される非反転出力信号と反転信号出力の各々に対して備えられている。すなわち、バッファ回路 602 には、非反転出力信号をバッファリングする第 1 バッファ回路 605 と反転出力信号をバッファリングする第 2 バッファ回路 606 が含まれる。

#### 【0035】

スイッチ 115 を増幅回路 104 の出力に備え短絡することで、本実施形態においても非反転出力信号 113 と反転出力信号 114 を共通電位レベル Vcom に強制的に設定させることができるとなる。またバッファ回路 602 の構成をとることでより大きな出力負荷に対しても駆動することができる。また、本実施形態では入力側リセットスイッチ 205 およびスイッチ 115 に供給するリセットのタイミングのためにリセット信号供給部 112 を 1 つ用いている。しかしながら、第 2 実施形態のごとく、独立に 2 つのリセット信号供給部 211, 212 を用いても良い。10

#### 【0036】

##### [第 5 実施形態]

図 7 は本発明の第 5 実施形態を示した回路図である。図 7 において、増幅部 601 は、増幅回路 104、バッファ回路 602 を有する。

#### 【0037】

本実施形態が第 3 実施形態と異なる点は、増幅回路 104 に続いてバッファ回路 115 が設けられ、その後段に、増幅部 601 の第 1 出力端子 113 と第 1 出力端子 114 を短絡させるスイッチ 115 が設けられる点である。また、バッファ回路 602 には、増幅器 104 から出力される第 1 非反転出力信号 701 をバッファリングする第 1 バッファ回路 605 と、第 1 反転出力信号 702 をバッファリングする第 2 バッファ回路 606 が含まれる。そして、第 1 バッファ回路 605 は、バッファリングした信号を非反転出力信号として第 1 出力線 113 に出力し、第 2 バッファ回路 606 は、バッファリングした信号を反転出力信号として第 2 出力線 114 に出力する構成をとる。20

#### 【0038】

スイッチ 115 を短絡することで、第 1 バッファ回路 605 から第 1 出力線 113 に出力される非反転出力信号と第 2 出力線 114 に出力される非反転出力信号反転出力信号 114 を共通電位レベル、Vcom に強制的に設定させることができるとなる。また、本実施例では入力側リセットスイッチ 205 およびスイッチ 115 に供給するリセットタイミングのためにリセット信号供給部 112 を 1 つ用いている。しかしながら、第 2 実施形態のごとく、独立に 2 つのリセット信号供給部 211, 212 を用いても良い。30

#### 【0039】

##### [その他]

上述の実施形態における列読み出し回路は、例えば画素アレイからの信号を増幅する回路や、画素アレイからの信号に含まれるノイズ成分を除去する CDS 回路や、画素アレイからの信号を一時的に保持する容量などであっても良い。

#### 【0040】

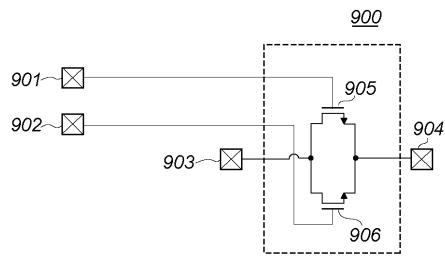

図 9 は、半導体基板に形成された撮像装置（半導体チップ）において、第 1 から第 5 実施形態で使用されたスイッチ 115 の一実施例である MOS スイッチ 900 を示す。増幅部 601 における第 1 出力線 113 と第 2 出力線 114 は、それぞれ MOS スイッチ 900 の第 1 出力パッド 903 と第 2 出力パッド 904 に接続されている。MOS スイッチ 900 は、リセット信号を受ける第 1 入力パッド 901 と第 2 入力パッド 902 のゲートを有する。また、この MOS スイッチ 900 は、動作スイッチとして、NMOS トランジスタ 905 と PMOS トランジスタ 906 の 2 つのトランジスタが備えられる。第 1 入力パッド 901 には、アクティブルーレベルがハイレベルのリセット信号が入力され、NMOS トランジスタ 905 が導通状態となる。またそれと同時に、第 2 入力パッド 902 には、論理レベルとしてこのリセット信号を反転させ、アクティブルーレベルがローレベルの反転リセット信号が入力され、PMOS 906 が導通状態となる。NMOS 905 トランジスタと4050

P M O S 9 0 6 トランジスタが同時に導通状態となることで、増幅部 6 0 1 の第 1 出力線 1 1 3 と第 2 出力線 1 1 4 の各々に出力される非反転出力信号と反転出力信号のレベルを共通電位 V c o m に急速に設定できる。

#### 【 0 0 4 1 】

このM O Sスイッチ9 0 0は、電源からグランドまでのすべての信号を低い抵抗で導通させることができる特徴を有する。また、正論理リセット信号とそれを反転させた負論理リセット信号を同時に入力することで、半導体基板の外部への放射ノイズが減少し、センサーへのノイズ信号の混入を抑制することが可能となる特徴も有する。

#### 【 0 0 4 2 】

ところで、固体撮像装置においては、画素の各列に増幅器を設ける技術が知られている。

そこで、第 1 実施形態のひとつのオプションとして、図 1 に示す信号処理回路 1 0 3 において画素の各列に増幅器を設ける構成が考えられる。つまり、図 1 においては増幅回路 1 0 4 が全列に共通で設けられているが、増幅回路 1 0 4 の構成を画素の各列に設けることが考えられる。例えば列読み出し回路 1 0 6 - 1 ~ 1 0 6 - 3 のそれぞれに増幅回路 1 0 4 と同様の構成が含まれる。各列に設けられた増幅回路の第 1 入力端子には各列からの信号を入力し、基準レベルを第 2 入力端子に入れるものとして、増幅回路は、この 2 入力の差分を増幅し、第 1 出力線 1 1 3 に非反転出力を出し、第 2 出力線 1 1 4 にその反転出力を出力する構成であってもよい。

#### 【 0 0 4 3 】

このように画素アレイの各列に本発明に係る増幅部を設けても、その出力間を短絡することにより速やかに共通電位 V c o m を出力することができる。一般に、例えば図 1 における増幅回路 1 0 4 は、画素アレイの各列に設けられる増幅部よりも高速に動作する必要がある。したがって、本発明は図 1 や図 3 に示されるように、画素アレイの複数の列に共通に設けられた場合に特に有効である。撮像装置 1 0 0 は一般に半導体基板上に形成され、その出力部（図示していない）は増幅部 6 0 1 に含まれる。

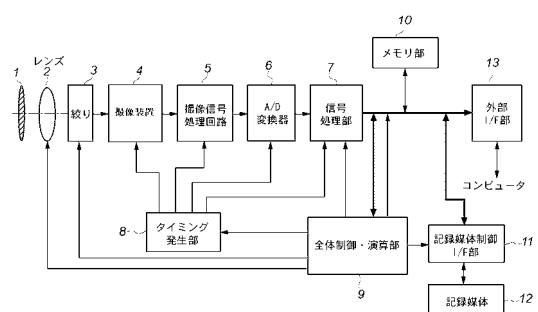

#### 【 0 0 4 4 】

##### [ 第 6 実施形態 ]

図 8 は、前述した各実施形態の撮像装置を備える撮像システムの構成図である。撮像システムには、まず撮像面へ像を形成する光学系として、レンズのプロテクトとメインスイッチを兼ねるバリア 1 、被写体の光学像を撮像素子 4 に結像させるレンズ 2 、レンズ 2 を通った光量を可変するための絞り 3 がある。そして、レンズ 2 で結像された被写体を画像信号として取り込むための撮像装置 4 がある。ここで、撮像装置 4 は上記の各実施形態で説明した撮像装置の部分がある。さらにシステムとして、撮像装置 4 から出力される画像信号に各種の補正、クランプ等の処理を行う撮像信号処理回路 5 、撮像素子 4 より出力される画像信号のアナログ - ディジタル変換を行う A / D 変換器 6 、 A / D 変換器 6 より出力された画像データを生成し、各種の補正を行いデータを圧縮する信号処理部 7 がある。また、撮像装置 4 及び撮像信号処理回路 5 及び A / D 変換器 6 及び信号処理部 7 に各種タイミング信号を出力するタイミング発生部 8 から構成される。なお、 5 ~ 8 の各回路は撮像装置 4 と同一チップ上に形成しても良い。また、各種演算とスチルビデオカメラ全体を制御する全体制御・演算部 9 、画像データを一時的に記憶するためのメモリ部 1 0 、記録媒体に記録又は読み出しを行うための記録媒体制御インターフェース部 1 1 、画像データの記録又は読み出しを行うための半導体メモリ等の着脱可能な記録媒体 1 2 、外部コンピュータ等と通信するための外部インターフェース ( I / F ) 部 1 3 で撮像システムは構成される。

#### 【 0 0 4 5 】

次に、図 8 の動作について説明する。バリア 1 がオープンされるとメイン電源がオンされ、次にコントロール系の電源がオンし、さらに、 A / D 変換器 6 などの撮像系回路の電源がオンされる。それから、露光量を制御するために、全体制御・演算部 9 は絞り 3 を開放にし、撮像装置 4 から出力された信号は、撮像信号処理回路 5 をスルーして A / D 変換器 6 へ出力される。 A / D 変換器 6 は、その信号を A / D 変換して、信号処理回路 7 に出

10

20

30

40

50

力する。信号処理部7は、そのデータを基に露出の演算を全体制御・演算部9で行う。

【0046】

この測光を行った結果により明るさを判断し、その結果に応じて全体制御・演算部9は絞りを制御する。次に、撮像装置4から出力された信号をもとに、高周波成分を取り出し被写体までの距離の演算を全体制御・演算部9で行う。その後、レンズ2を駆動して合焦か否かを判断し、合焦していないと判断したときは、再びレンズ2を駆動し測距を行う。

【0047】

そして、合焦が確認された後に本露光が始まる。露光が終了すると、撮像装置4から出力された画像信号は、撮像信号処理回路5において補正等がされ、さらにA/D変換器6でA/D変換され、信号処理部7を通り全体制御・演算部9によりメモリ部10に蓄積される。その後、メモリ部10に蓄積されたデータは、全体制御・演算部9の制御により記録媒体制御I/F部を通り半導体メモリ等の着脱可能な記録媒体12に記録される。また外部I/F部13を通り直接コンピュータ等に入力して画像の加工を行ってもよい。

【0048】

本発明を撮像装置として適用すれば、高品質な撮像システムを構築することができる。

【図面の簡単な説明】

【0049】

【図1】本発明の第1実施形態を示すブロック図である。

【図2】本発明の第1実施形態の主要信号のタイミング図である。

【図3】本発明の第2実施形態を示すブロック図である。

【図4】本発明の第2実施形態の主要信号のタイミング図である。

【図5】本発明の第3実施形態を示す増幅回路の図である。

【図6】本発明の第4実施形態を示す増幅回路の図である。

【図7】本発明の第5実施形態を示す増幅回路の図である。

【図8】本発明の撮像装置の全体を示すシステム図である。

【図9】本発明のスイッチの一例を示す図である。

【符号の説明】

【0050】

100 撮像装置

101 画素アレイ

103 信号処理回路

104 増幅回路

106 列読出し回路

109 入力側リセットスイッチ

110 共通読出し線

105 基準レベル供給部

112 リセットタイミング供給部

113 第1出力線

114 第2出力線

115 スイッチ

116 第1入力端子

117 第2入力端子

118 列選択スイッチ

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【 6 】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 沖田 彰

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 桜木 孝正

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 鈴木 覚

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2006-174091(JP,A)

特開2003-198949(JP,A)

特開2004-186790(JP,A)

特開2004-312039(JP,A)

特開2003-283269(JP,A)

国際公開第2006/118184(WO,A1)

特開2007-047342(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H03F 1/00 - 3/45

H03F 3/50 - 3/52

H03F 3/62 - 3/64

H03F 3/68 - 3/72