(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-241237

(P2007-241237A)

(43) 公開日 平成19年9月20日(2007.9.20)

| (51) Int.CI.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/1368 | 2 H 092     |

| <b>G09F 9/30 (2006.01)</b>   | G09F 9/30   | 3 3 8       |

| <b>H01L 21/336 (2006.01)</b> | H01L 29/78  | 6 1 2 D     |

| <b>H01L 29/786 (2006.01)</b> | H01L 29/78  | 6 1 2 C     |

| <b>H01L 21/768 (2006.01)</b> | H01L 29/78  | 6 1 6 U     |

審査請求 有 請求項の数 30 O L 外国語出願 (全 38 頁) 最終頁に続く

|              |                              |          |                                                                                                                                         |

|--------------|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-294422 (P2006-294422) | (71) 出願人 | 593132010<br>インダストリアル・テクノロジー・リサーチ・インスティテュート<br>INDUSTRIAL TECHNOLOGY RESEARCH INSTITUTE<br>台灣シンチュ・シエン、チュトゥエン、チュンーシン・ロード、セクション4、19<br>5番 |

| (22) 出願日     | 平成18年10月30日 (2006.10.30)     | (74) 代理人 | 100101454<br>弁理士 山田 卓二                                                                                                                  |

| (31) 優先権主張番号 | 11/369,624                   | (74) 代理人 | 100081422<br>弁理士 田中 光雄                                                                                                                  |

| (32) 優先日     | 平成18年3月7日 (2006.3.7)         | (74) 代理人 | 100105016<br>弁理士 加野 博                                                                                                                   |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】二層金属ラインを有する薄膜トランジスタディスプレイアレイを製造するための方法

## (57) 【要約】

【課題】TFTアレイを製造するための方法に提供する。

【解決手段】TFTアレイを製造するための方法は、基板と、複数の第1の導電性ラインと複数の第2の導電性ラインとを有し基板上にパターニングされた第1の金属層と、パターニングされた第1の金属層の上の絶縁層と、パターニングされたシリコン層と、パターニングされたシリコン層の上のパターニングされた保護層と、パターニングされた保護層の上のパターニングされたドープシリコン層及びパターニングされた第2の金属層とを準備し、パターニングされたシリコン層の露出した部分と第1の導電性ラインと第2の導電性ラインの露出した部分を埋め、パターニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインを備え、そのそれぞれが、複数の第1の導電性ラインと複数の第2の導電性ラインの1つにそれぞれに対応する。

【選択図】図1H

**【特許請求の範囲】****【請求項 1】**

薄膜トランジスタ（「TFT」）アレイを製造するための方法であって、

基板を用意するステップと、

前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の

金属層が、複数の第1の導電性ラインと該第1の導電性ラインに直交して配置される複数

の第2の導電性ラインとを有し、前記第1の導電性ラインのそれぞれが、複数のゲート電

極を有し、該ゲート電極のそれぞれが、1つの前記第1の導電性ラインと1つの前記第2

の導電性ラインの交点の近くに配置されるステップと、

前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、

10

パターニングされたシリコン層を形成するステップと、

前記パターニングされたシリコン層と前記パターニングされた第1の金属層の上にパタ

ーニングされた保護層を形成し、前記パターニングされたシリコン層の一部とそれぞれ1

つの前記第1の導電性ライン及びそれぞれ1つの前記第2の導電性ラインの一部とを露出

させるステップと、

前記パターニングされた保護層の上にパターニングされたドープシリコン層とパターニ

ングされた第2の金属層とを形成し、前記パターニングされたシリコン層の露出した部分

と前記第1の導電性ライン及び前記第2の導電性ラインの露出した部分とを埋め、前記パタ

ーニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインと

を有し、前記第3の導電性ラインと前記第4の導電性ラインのそれぞれが、前記複数

の第1の導電性ラインの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応す

るステップと、

20

を備えていることを特徴とする方法。

**【請求項 2】**

前記パターニングされた第2の金属層と前記パターニングされた保護層の上にパターニ

ングされた画素電極層を形成するステップをさらに備えていることを特徴とする請求項1

に記載の方法。

**【請求項 3】**

前記パターニングされたシリコン層の上に保護層を形成するステップと、

30

前記保護層の上にパターニングされた画素電極層を形成するステップと、

前記保護層をパターニングし、前記パターニングされたシリコン層の一部と前記第1の

導電性ライン又は第2の導電性ラインの一部とを露出させるステップと、

をさらに備えていることを特徴とする請求項1に記載の方法。

**【請求項 4】**

前記パターニングされた保護層の上にパターニングされた画素電極層を形成するステッ

プと、

前記パターニングされた保護層と前記パターニングされた画素電極層の上に、パターニ

ングされたドープシリコン層とパターニングされた第2の金属層とを形成し、前記パタ

ーニングされたドープシリコン層の露出した部分と前記第1の導電性ライン又は第2の導電

性ラインの露出した部分とを埋めるステップと、

40

をさらに備えていることを特徴とする請求項1に記載の方法。

**【請求項 5】**

前記パターニングされた第1の金属層の前記第1の導電性ラインと第2の導電性ライン

の少なくとも1つの上の前記保護層と前記絶縁層にトレンチを形成するステップをさらに

備えていることを特徴とする請求項1に記載の方法。

**【請求項 6】**

前記トレンチを通じて前記パターニングされた第1の金属層と前記パターニングされた

第2の金属層とを電気的に接続させるステップをさらに備えていることを特徴とする請求

項5に記載の方法。

**【請求項 7】**

50

前記パターニングされた第1の金属層の前記第1の導電性ラインと前記第2の導電性ラインの少なくとも1つの上の前記保護層と前記絶縁層に複数のコンタクトホールを形成するステップをさらに備えていることを特徴とする請求項1に記載の方法。

【請求項8】

前記複数のコンタクトホールを通じて前記パターニングされた第1の金属層と前記パターニングされた第2の金属層とを電気的に接続させるステップをさらに備えていることを特徴とする請求項7に記載の方法。

【請求項9】

前記パターニングされた第1の金属層のそれぞれの前記第2の導電性ラインが、互いに離れている複数の分岐ラインを備えていることを特徴とする請求項1に記載の方法。 10

【請求項10】

前記それぞれの分岐ラインと、同じ前記第2の導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記分岐ラインのそれぞれの長さの比が、約2から20の範囲であることを特徴とする請求項9に記載の方法。

【請求項11】

前記パターニングされた第2の金属層のそれぞれの前記第3の導電性ラインが、互いに離れている複数の分岐ラインを備えていることを特徴とする請求項1に記載の方法。

【請求項12】

前記それぞれの分岐ラインと、同じ前記第3の導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記分岐ラインのそれぞれの長さの比が、約2から20の範囲であることを特徴とする請求項11に記載の方法。 20

【請求項13】

アモルファスシリコン層又は多結晶シリコン層の1つを有するパターニングされたシリコン層を形成するステップをさらに備えていることを特徴とする請求項1に記載の方法。

【請求項14】

薄膜トランジスタ（「TFT」）アレイを製造するための方法であって、

基板を用意するステップと、

前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の金属層が、複数の第1の導電性ラインと該第1の導電性ラインに直交して配置される複数の第2の導電性ラインとを有し、前記第1の導電性ラインのそれぞれが、複数のゲート電極を有し、該ゲート電極のそれぞれが、1つの前記第1の導電性ラインと1つの前記第2の導電性ラインの交点の近くに配置されるステップと、 30

前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、

パターニングされたシリコン層を形成するステップと、

前記パターニングされたシリコン層と前記パターニングされた第1の金属層の上にパターニングされた保護層を形成し、前記パターニングされたシリコン層の一部と前記第1の導電性ライン及び前記第2の導電性ラインのそれぞれの一部とを露出させるステップと、

前記パターニングされたシリコン層の露出した部分の中へ不純物をドープするステップと、

前記パターニングされた保護層の上にパターニングされた第2の金属層を形成し、前記パターニングされたシリコン層の露出した部分と前記第1の導電性ライン又は第2の導電性ラインの露出した部分とを埋め、前記パターニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインとを有し、前記第3の導電性ラインと前記第4の導電性ラインのそれぞれが、前記パターニングされた第1の金属層の前記複数の第1の導電性ラインの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応するステップと、 40

を備えていることを特徴とする方法。

【請求項15】

前記パターニングされた第2の金属層と前記パターニングされた保護層の上にパターニングされた画素電極層を形成するステップをさらに備えていることを特徴とする請求項1 50

4に記載の方法。

【請求項 16】

前記パターニングされたシリコン層の上に保護層を形成するステップと、

前記保護層の上にパターニングされた画素電極層を形成するステップと、

前記保護層をパターニングし、前記パターニングされたシリコン層の一部と前記第1の導電性ライン又は第2の導電性ラインの一部とを露出させるステップと、

をさらに備えていることを特徴とする請求項14に記載の方法。

【請求項 17】

前記パターニングされたシリコン層の露出した部分の中へ不純物をドープするステップと、

前記パターニングされた保護層の上にパターニングされた画素電極層を形成するステップと、

前記パターニングされた保護層と前記パターニングされた画素電極層の上にパターニングされた第2の金属層を形成し、前記パターニングされたシリコン層の露出した部分と前記第1の導電性ライン又は第2の導電性ラインの露出した部分とを埋めるステップと、

をさらに備えていることを特徴とする請求項14に記載の方法。

【請求項 18】

前記パターニングされた第1の金属層の前記第1の導電性ライン又は第2の導電性ラインの少なくとも1つの上の前記保護層と前記絶縁層にトレンチを形成するステップをさらに備えていることを特徴とする請求項14に記載の方法。

【請求項 19】

前記トレンチを通じて前記パターニングされた第1の金属層と前記パターニングされた第2の金属層とを電気的に接続させるステップをさらに備えていることを特徴とする請求項18に記載の方法。

【請求項 20】

前記パターニングされた第1の金属層の前記第1の導電性ラインと前記第2の導電性ラインの少なくとも1つの上の前記保護層と前記絶縁層に複数のコンタクトホールを形成するステップをさらに備えていることを特徴とする請求項14に記載の方法。

【請求項 21】

前記複数のコンタクトホールを通じて前記パターニングされた第1の金属層と前記パターニングされた第2の金属層とを電気的に接続させるステップをさらに備えていることを特徴とする請求項20に記載の方法。

【請求項 22】

前記パターニングされた第1の金属層のそれぞれの前記第2の導電性ラインが、互いに離れている複数の分岐ラインを備えていることを特徴とする請求項14に記載の方法。

【請求項 23】

前記それぞれの分岐ラインと、同じ前記第2の導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記分岐ラインのそれぞれの長さの比が、約2から20の範囲であることを特徴とする請求項22に記載の方法。

【請求項 24】

前記パターニングされた第2の金属層のそれぞれの前記第3の導電性ラインが、互いに離れている複数の分岐ラインを備えていることを特徴とする請求項14に記載の方法。

【請求項 25】

前記それぞれの分岐ラインと、同じ前記第1の導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記分岐ラインのそれぞれの長さの比が、約2から20の範囲であることを特徴とする請求項24に記載の方法。

【請求項 26】

アモルファスシリコン層又は多結晶シリコン層の1つを有するパターニングされたシリコン層を形成するステップをさらに備えていることを特徴とする請求項14に記載の方法。

10

20

30

40

50

**【請求項 27】**

薄膜トランジスタ（「TFT」）アレイを製造するための方法であって、

基板を用意するステップと、

前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の

金属層が、複数の第1の導電性ラインと該第1の導電性ラインに直交して配置される複数

の第2の導電性ラインとを有し、前記第2の導電性ラインのそれぞれが、互いに離れて

いる複数の分岐ラインを有するステップと、

前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、

前記絶縁層の上にパターニングされたシリコン層を形成するステップと、

それぞれの前記第1の導電性ラインの一部と前記パターニングされた第1の金属層のそ

れぞれの前記第2の導電性ラインの分岐ラインを露出させるステップと、

10

前記パターニングされたシリコン層の上にパターニングされた第2の金属層を形成し、

それぞれの前記第1の導電性ラインの露出した部分とそれぞれの前記第2の導電性ライン

の露出した部分を埋め、前記パターニングされた第2の金属層が、複数の第3の導電性ラ

インと複数の第4の導電性ラインとを有し、前記第3の導電性ラインと前記第4の導電性

ラインのそれぞれが、前記パターニングされた第1の金属層の前記複数の第1の導電性ラ

インの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応するステップと、

を備えていることを特徴とする方法。

**【請求項 28】**

前記パターニングされた第2の金属層のそれぞれの前記第3の導電性ラインが、互いに

離れている複数の分岐ラインを備えていることを特徴とする請求項27に記載の方法。

20

**【請求項 29】**

前記それぞれの分岐ラインと、前記パターニングされた第1の金属層の同じ前記第3の

導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記それぞれの

分岐ラインの長さの比が、約2から20の範囲であることを特徴とする請求項28に記載

の方法。

**【請求項 30】**

前記それぞれの分岐ラインと、前記パターニングされた第2の金属層の同じ前記第4の

導電性ライン上に配置され直接隣接する分岐ラインとの間の距離に対する前記それぞれの

分岐ラインの長さの比が、約2から20の範囲であることを特徴とする請求項27に記載

の方法。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、概略的に言えば、複数の薄膜トランジスタ（「TFT」）に関し、より詳し

く言えば、TFTアレイ（TFT array）を製造するための方法に関する。

**【背景技術】****【0002】**

半導体製造技術における進歩とともに、液晶ディスプレイ（「LCD」）装置などのフ

ラットパネルディスプレイ装置のパネルサイズが急速に増大している。その結果、フラット

パネルディスプレイ装置内の導電性ライン（conductive line）は、長さにおいてかなり

の増加を引き起こし、好ましくない抵抗・容量（「RC」）遅延を逆に招いている。かかるRC

遅延は、フラットパネル装置の性能に深刻な影響を及ぼし得る。37インチ又は

それ以上のパネルサイズを有する液晶ディスプレイテレビにおいて、走査線の内部のRC

遅延は、表示品質に悪影響を及ぼすことが見出されている。RC遅延問題に取り組む従来

の方法の1つは、両側駆動方式を提案しており、RC遅延をオフセットする、あるいは軽

減するために、パネルの両側にドライバが備えられている。

40

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

50

しかし、この方法は、更なる複数の駆動集積回路（「IC」）と、次にこれらの集積回路をパッケージングするための更なるコストを必要とする。従って、駆動方式に妥協することなく、TFTアレイ内の導電性ラインにおいてRC遅延を低減することができるTFTアレイを製造するための方法が望まれている。

#### 【0004】

本発明は、先行技術についての制限及び欠点から生じる1つ若しくはそれ以上の問題を取り除く、二層導電性ラインを有する薄膜トランジスタ（「TFT」）アレイを製造するための方法に指向される。

#### 【課題を解決するための手段】

#### 【0005】

本発明の一実施形態によれば 基板を用意するステップと、前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の金属層が、複数の第1の導電性ラインと該第1の導電性ラインに直交して配置される複数の第2の導電性ラインとを有し、前記第1の導電性ラインのそれぞれが、複数のゲート電極を有し、該ゲート電極のそれぞれが、1つの前記第1の導電性ラインと1つの前記第2の導電性ラインの交点の近くに配置されるステップと、前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、パターニングされたシリコン層を形成するステップと、前記パターニングされたシリコン層と前記パターニングされた第1の金属層の上にパターニングされた保護層を形成し、前記パターニングされたシリコン層の一部とそれぞれ1つの前記第1の導電性ライン及びそれぞれ1つの前記第2の導電性ラインの一部とを露出させるステップと、前記パターニングされた保護層の上にパターニングされたドープシリコン層とパターニングされた第2の金属層とを形成し、前記パターニングされたシリコン層の露出した部分と前記第1の導電性ライン及び前記第2の導電性ラインの露出した部分とを埋め、前記パターニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインとを有し、前記第3の導電性ラインと前記第4の導電性ラインのそれぞれが、前記複数の第1の導電性ラインの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応するステップとを備えている薄膜トランジスタ（「TFT」）アレイを製造するための方法が提供される。

#### 【0006】

また、本発明によれば、基板を用意するステップと、前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の金属層が、複数の第1の導電性ラインと該第1の導電性ラインに直交して配置される複数の第2の導電性ラインとを有し、前記第1の導電性ラインのそれぞれが、複数のゲート電極を有し、該ゲート電極のそれぞれが、1つの前記第1の導電性ラインと1つの前記第2の導電性ラインの交点の近くに配置されるステップと、前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、パターニングされたシリコン層を形成するステップと、前記パターニングされたシリコン層と前記パターニングされた第1の金属層の上にパターニングされた保護層を形成し、前記パターニングされたシリコン層の一部と前記第1の導電性ライン及び前記第2の導電性ラインのそれぞれの一部とを露出させるステップと、前記パターニングされたシリコン層の露出した部分の中へ不純物をドープするステップと、前記パターニングされた保護層の上にパターニングされた第2の金属層を形成し、前記パターニングされたシリコン層の露出した部分と前記第1の導電性ライン又は第2の導電性ラインの露出した部分とを埋め、前記パターニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインとを有し、前記第3の導電性ラインと前記第4の導電性ラインのそれぞれが、前記パターニングされた第1の金属層の前記複数の第1の導電性ラインの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応するステップとを備えている薄膜トランジスタ（「TFT」）アレイを製造するための方法が提供される。

#### 【0007】

更に、本発明によれば、基板を用意するステップと、前記基板上にパターニングされた第1の金属層を形成し、該パターニングされた第1の金属層が、複数の第1の導電性ライ

10

20

30

40

50

ンと該第1の導電性ラインに直交して配置される複数の第2の導電性ラインとを有し、前記第2の導電性ラインのそれぞれが、互いに離れている複数の分岐ラインを有するステップと、前記パターニングされた第1の金属層の上に絶縁層を形成するステップと、前記絶縁層の上にパターニングされたシリコン層を形成するステップと、それぞれの前記第1の導電性ラインの一部と前記パターニングされた第1の金属層のそれぞれの前記第2の導電性ラインの分岐ラインを露出させるステップと、前記パターニングされたシリコン層の上にパターニングされた第2の金属層を形成し、それぞれの前記第1の導電性ラインの露出した部分とそれぞれの前記第2の導電性ラインの露出した部分を埋め、前記パターニングされた第2の金属層が、複数の第3の導電性ラインと複数の第4の導電性ラインとを有し、前記第3の導電性ラインと前記第4の導電性ラインのそれぞれが、前記パターニングされた第1の金属層の前記複数の第1の導電性ラインの1つと前記複数の第2の導電性ラインの1つにそれぞれに対応するステップとを備えている薄膜トランジスタ（「TFT」）アレイを製造するための方法が提供される。

10

## 【0008】

本発明の更なる特徴及び利点は、以下の説明に部分的に記述されており、その説明からある程度明らかとなる、すなわち、本発明の実施によって確認されるであろう。本発明の特徴及び利点は、添付した特許請求の範囲において、特に示された要素及びその組合せによって実現され達せられるであろう。

20

## 【0009】

前述した概要及び以下の詳細な説明はともに、例示的なものであって説明のためのものであり、特許請求の範囲のように、本発明を限定するものではないことを理解すべきである。

## 【0010】

前述した概要は、以下の発明の詳細な説明と同様に、添付図面とともに読む場合により理解されるであろう。本発明を説明するために、現在好ましい実施形態が図面に示されている。しかし、本発明は、示される正確な配置や手段に限定されるものではないことを理解すべきである。

## 【発明を実施するための最良の形態】

## 【0011】

本発明の本実施形態に対して詳細に言及され、その実施例が添付図に表されている。可能な限り、図面を通じて、同一参照番号を同一又は類似部分を指して使用する。

30

## 【0012】

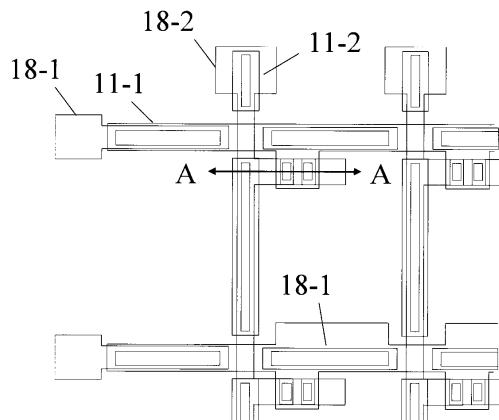

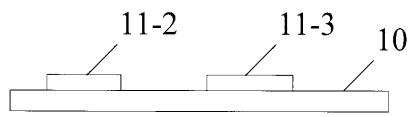

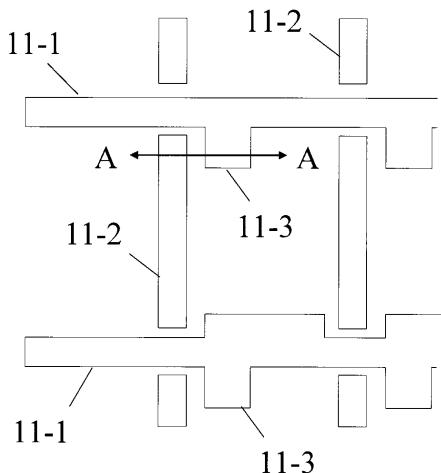

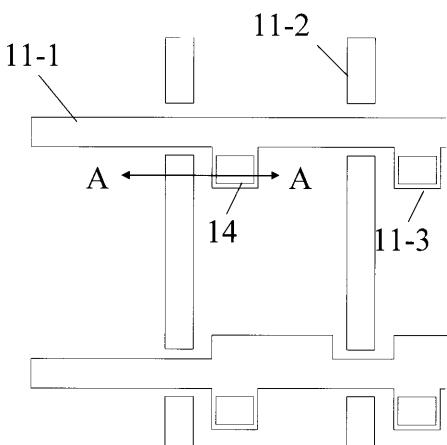

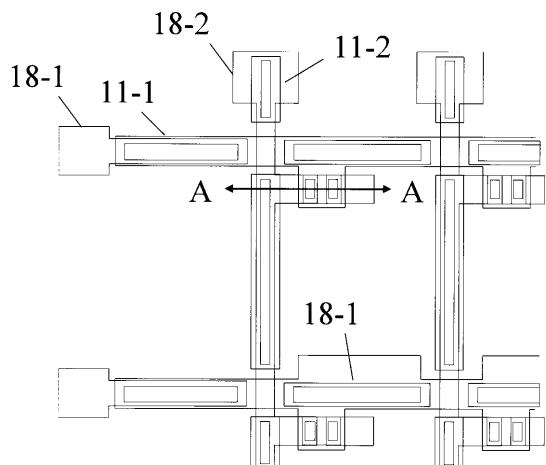

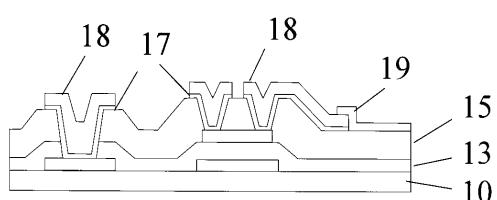

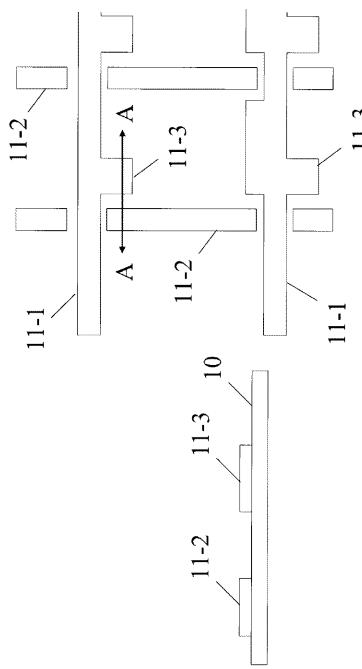

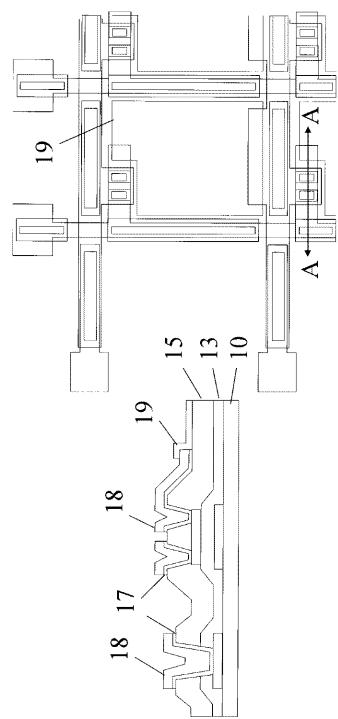

図1A～図1Jは、本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。図1Aは、図1Bに示される平面図のAA方向に沿った断面図である。図1Aによると、例えば、ガラス又は樹脂から作られる基板10が用意される。好ましくは、基板10の厚さは、約0.3～0.7mm（ミリメートル）の範囲であるが、これより薄くても厚くてもよい。次に、パターニングされた（patterned）第1の金属層11が、例えば、従来の物理的気相成長法（「PVD」）、スパッタリング又は他の好適なプロセスによって基板10上に第1の金属の層を形成し、その次に第1のマスクを使用し従来のパターニング及びエッチングプロセスによって、基板10上に形成される。図1Bによると、パターニングされた第1の金属層11は、互いに実質的に平行な複数の第1の導電性ライン11-1と、第1の導電性ライン11-1に実質的に直交する複数の第2の導電性ライン11-2とを備えている。第1の導電性ライン11-1のそれぞれは、ゲート電極11-3を備えている。それぞれのゲート電極11-3は、1つの第1の導電性ライン11-1と1つの第2の導電性ライン11-2の交点の近くに配置される。第1の金属層のための好適な材料は、TiAlTi、MoAlMo、CrAlCr、MoW、Cr及びCuであるが、これに限定されるものではない。好ましくは、ゲート電極11-3の厚さは、約1000から2000（オングストローム）の範囲であるが、他の厚さであってもよい。それぞれの第1の導電性ライン11-1は、最終的に二層配線（dual-layer wire）の主ライン（main line）となり、それぞれの第2の導電性

40

50

ライン 11 - 2 は、最終的に二層配線の分岐ライン (branch line) となる。二層若しくは多層配線構造は、2003年10月20に出願された米国特許出願第10/687759号及び2005年5月17日に出願された米国特許出願第11/131084号に開示され、それらは参照することによりここに組み込まれる。

#### 【0013】

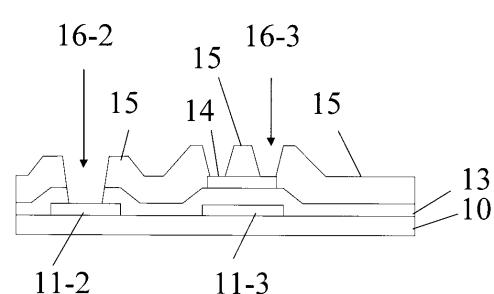

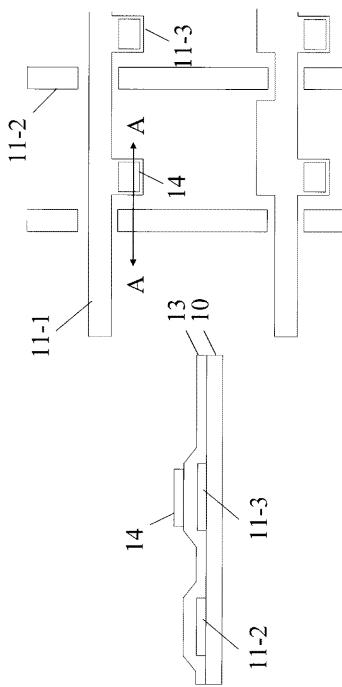

図1C及び図1Dによると、絶縁層13が、例えば従来の化学的気相成長法（「CVD」）プロセス又は他の好適なプロセスによってパターニングされた第1の金属層11上に形成される。絶縁層13のための好適な材料は、窒化ケイ素、酸化ケイ素及び酸窒化ケイ素である。好ましくは、絶縁層13の厚さは、約2500から4000の範囲である。次に、パターニングされたシリコン層14が、例えば従来のCVD又は他の好適なプロセスによってシリコンの層を形成し、その次に第2のマスクを使用し従来のパターニング及びエッチングプロセスによって、絶縁層13上に形成される。パターニングされたシリコン層14は、それぞれのゲート電極11-3の上に配置される活性領域を画定する。パターニングされたシリコン層14は、アモルファスシリコン層又は多結晶シリコン層を有している。好ましくは、パターニングされたシリコン層14の厚さは、約500から3000の範囲であるが、他の厚さであってもよい。

#### 【0014】

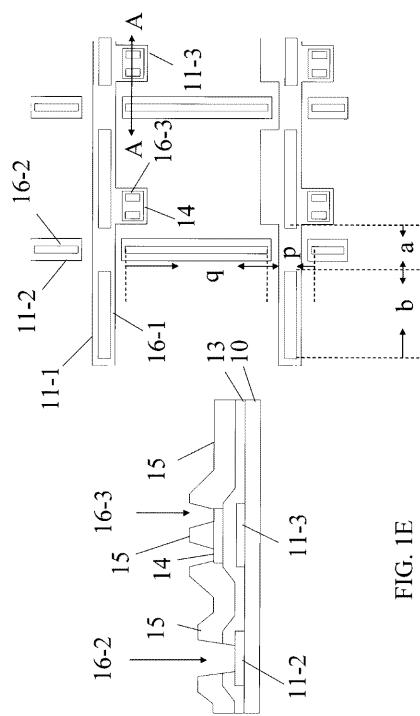

図1E及び図1Fによると、パターニングされた保護層15が、例えば従来のCVDプロセス又は他の好適なプロセスによって酸化物又は窒化物などの絶縁材料の層を形成し、その次に第3のマスクを使用し従来のパターニング及びエッチングプロセスによって、絶縁層13とパターニングされたシリコン層14の上に形成される。パターニングされた保護層15は、トレンチ(trench)16-1、16-2及び16-3を通じて第1の導電性ライン11-1、第2の導電性ライン11-2及びパターニングされたシリコン層14をそれぞれに露出させる。前記活性領域のそれぞれは、1対のトレンチ16-3を用いて形成され、対応するTFTトランジスタのためのソース領域とドレイン領域を規定する。好ましくは、パターニングされた保護層15の厚さは、約3000から5000の範囲である。

#### 【0015】

1つの第1の導電性ライン11-1の上に配置されるそれぞれのトレンチ16-1は、同じ1つの導電性ラインの上に配置される隣接するトレンチ16-1から、“a”として表示される距離だけ離れている。第1の実施形態では、距離“a”に対するトレンチの長さ“b”的比が、約2から20の範囲である。また、1つの第2の導電性ライン11-2の上に配置されるそれぞれのトレンチ16-2は、同じ1つの第2の導電性ライン11-2の上に配置される隣接するトレンチ16-2から、“p”として表示される距離だけ離れている。第1の実施形態では、距離“p”に対するトレンチ16-2の長さ“q”的比が、約2から20の範囲である。

#### 【0016】

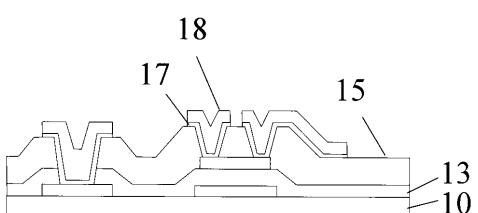

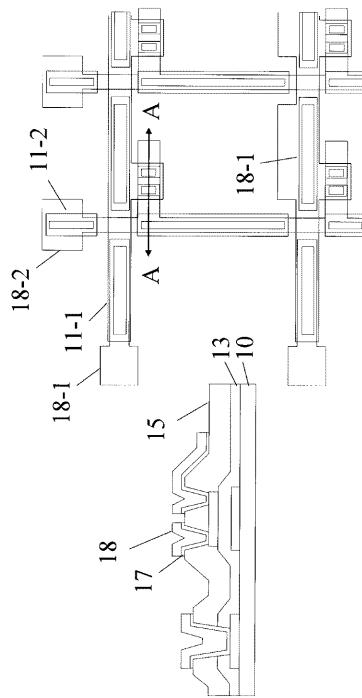

図1G及び図1Hによると、パターニングされたドープシリコン層(doped silicon layer)17とパターニングされた第2の金属層18とが、パターニングされた保護層15の上に形成され、トレンチ16-1、16-2及び16-3を埋める。パターニングされたシリコン層17とパターニングされた第2の金属層18とは、例えば従来のCVDプロセスによって高濃度にドープされたn型( $n^+$ )シリコンの層を形成し、その後に、例えば従来のPVDプロセスによって前記n型シリコン層上に第2の金属の層を形成し、その次に第4のマスクを使用し従来のパターニング及びエッチングプロセスによって、形成される。第2の金属層のための好適な材料は、TiAlTi、MoAlMo、CrAlCr、MoW、Cr及びCuであるが、これに限定されるものではない。好ましくは、パターニングされたドープシリコン層17の厚さは、約500であるが、それより厚いものでも薄いものでもよい。好ましくは、パターニングされた第2の金属層18の厚さは、約1000から3000の範囲である。

#### 【0017】

10

20

20

30

30

40

40

50

パターニングされた第2の金属層18は、複数の第3の導電性ライン18-1と、第3の導電性ライン18-1に直交する複数の第4の導電性ライン18-2とを備えている。それぞれの第3の導電性ライン18-1は、最終的に二層配線の分岐ラインとなり、それぞれの第4の導電性ライン18-2は、最終的に二層配線の主ラインとなる。パターニングされた第2の金属層18の第3の導電性ライン18-1は、TFTアレイのための二層配線、すなわち二層走査線を形成するために、トレンチ16-1を通じてパターニングされた第1の金属層11の第1の導電性ライン11-1に電気的に接続される。パターニングされた第2の金属層18の第4の導電性ライン18-2は、TFTアレイのための二層配線、すなわち二層データ線を形成するために、トレンチ16-2を通じてパターニングされた第1の金属層11の第2の導電性ライン11-2に電気的に接続される。主ラインに対応する分岐ラインと、同じ前記主ラインに対応する直接隣接する分岐ラインとの間の距離に対する前記主ラインに対応する分岐ラインの長さの比は、約2から20の範囲である。

10

20

30

## 【0018】

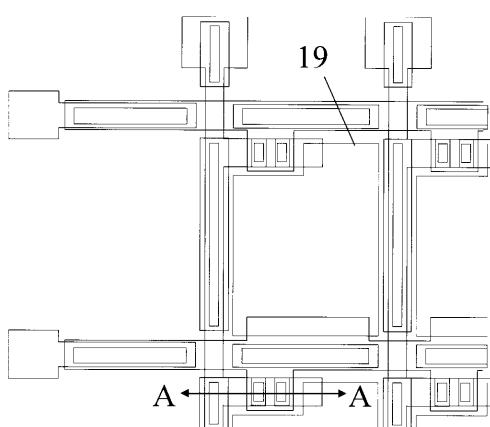

図1I及び図1Jによると、パターニングされた画素電極層19が、従来のPVDプロセスによって、パターニングされた第2の金属層18とパターニングされた保護層15の上に導電性材料、例えばインジウムスズ酸化物(ITO)の層を形成し、その次に第5のマスクを使用し従来のパターニング及びエッティングプロセスによって、形成される。パターニングされた画素電極層19は、TFTアレイのための画素電極としての機能を果たす。好ましくは、前記パターニングされた導電層の厚さは、約500から1000の範囲である。

20

## 【0019】

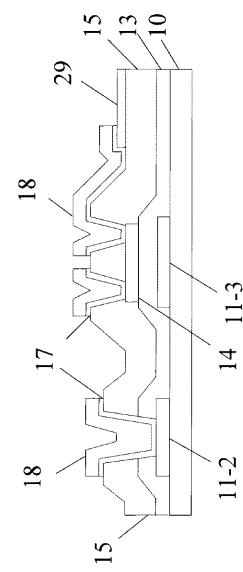

図2は、本発明の第2の実施形態に係るTFTアレイを製造するための方法を示す断面図である。図2によると、また図1A～図1Eを参照すると、第1のマスクが、パターニングされた第1の金属層11を規定するために使用される。次に、絶縁材料の層13が、パターニングされた第1の金属層11の上に形成される。第2のマスクが、パターニングされたシリコン層14を規定するために使用される。保護層15が、パターニングされたシリコン層14と絶縁層13の上に形成される。パターニングされた、例えばITO層などの画素電極層29が、従来のPVDプロセスによって、その次に第3のマスクを使用し従来のパターニング及びエッティングプロセスによって、前記保護層上に形成される。その後に、保護層15は、第4のマスクを使用し従来のパターニング及びエッティングプロセスを行うことによってパターニングされ、パターニングされたシリコン層14の一部とパターニングされた第1の金属層11-1と11-2の一部を露出させる。その後に、パターニングされたn型シリコン層17とパターニングされた第2の金属層18とが、第5のマスクを使用しパターニングされた画素電極層29とパターニングされた保護層15の上に形成される。

30

## 【0020】

また、図2及び図1A～図1Eを参照して、第1、第2及び第3のマスクが、パターニングされた第1の金属層11、パターニングされたシリコン層14及びパターニングされた保護層25を規定するためにそれぞれに使用されてもよい。パターニングされた画素電極層29は、従来のPVDプロセスによってITOなどの導電性材料の層を形成し、その後に第4のマスクを使用し従来のパターニング及びエッティングプロセスによって、パターニングされた保護層25の上に形成される。その後に、パターニングされたn型シリコン層17とパターニングされた第2の金属層18とが、第5のマスクを使用しパターニングされた画素電極層29とパターニングされた保護層25の上に形成される。

40

## 【0021】

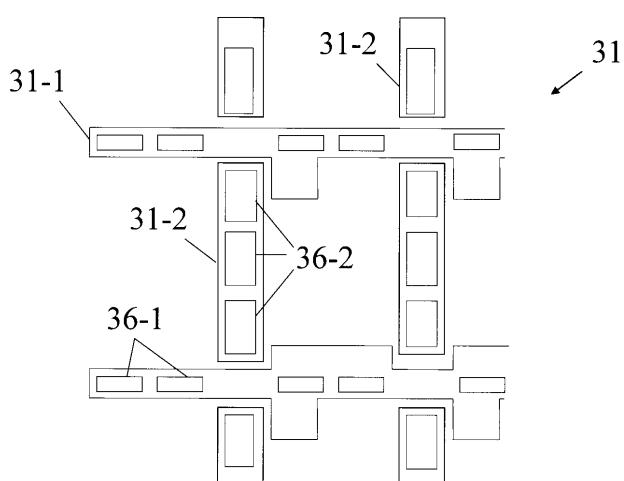

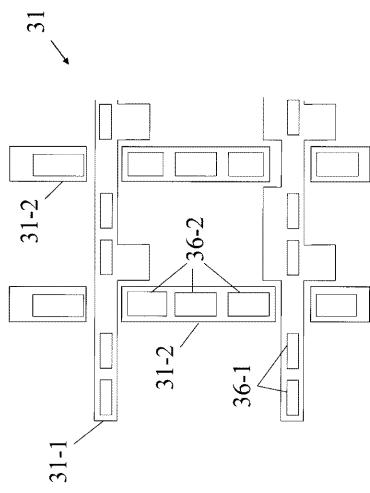

図3は、本発明の第3の実施形態に係るTFTアレイを製造するための方法を示す概略図である。図3によると、パターニングされた第1の金属層31は、複数の第1の導電性ライン31-1と複数の第2の導電性ライン31-2とを備えている。図1Fに示されるトレンチ16-2などのただ1つの連続的なトレンチの代わりに、複数のコンタクトホー

50

ル36-2が、2つの隣接する第1の導電性ライン31-1の間のそれぞれの第2の導電性ライン31-2に形成されている。また、複数のコンタクトホール36-1が、2つの隣接する第2の導電性ライン31-2の間のそれぞれの第1の導電性ライン31-1に形成されてもよい。

#### 【0022】

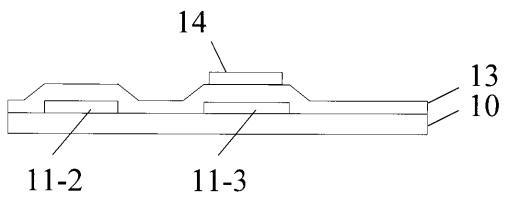

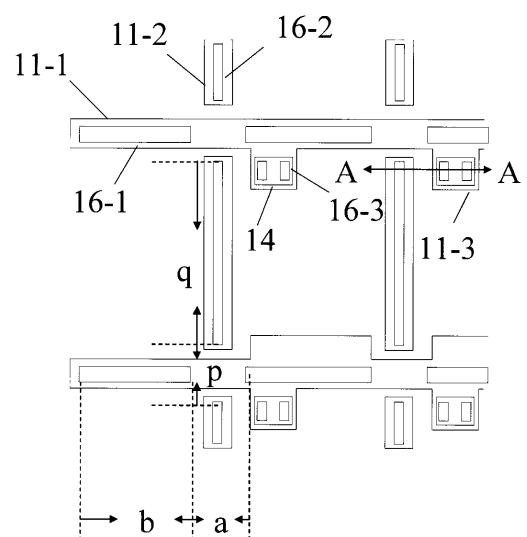

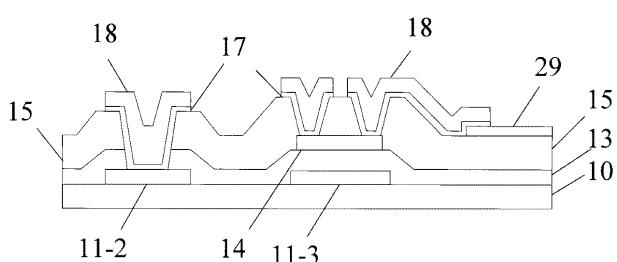

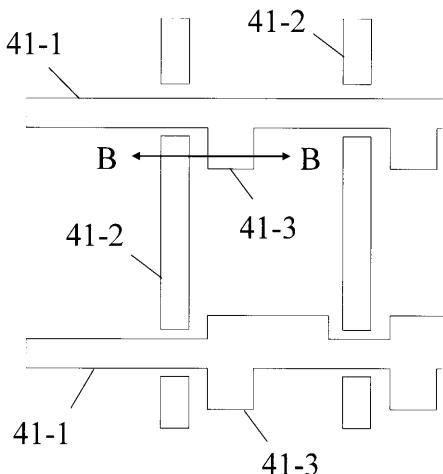

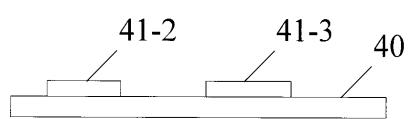

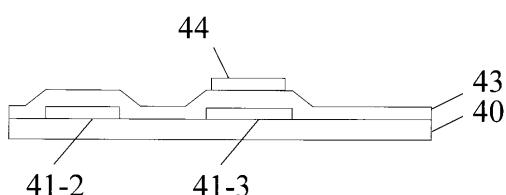

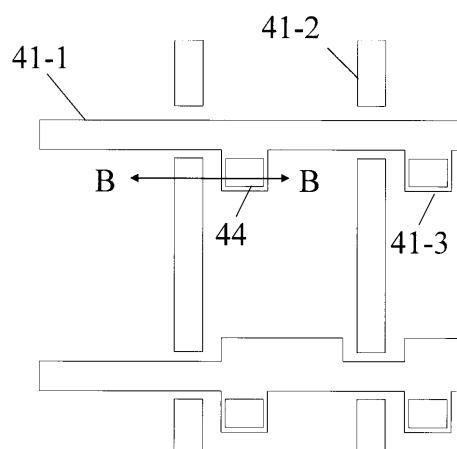

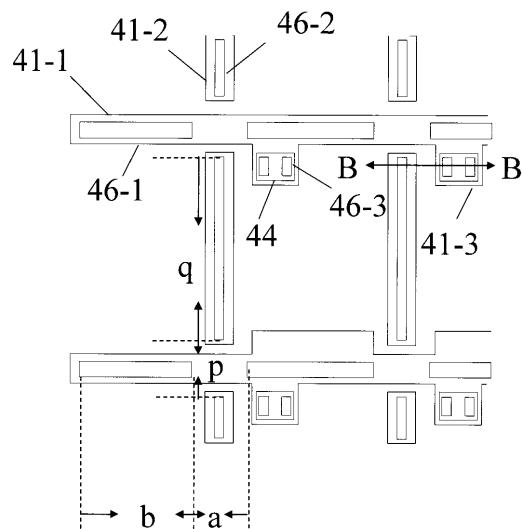

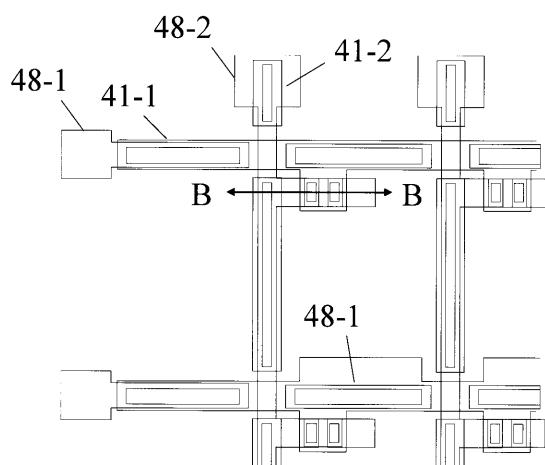

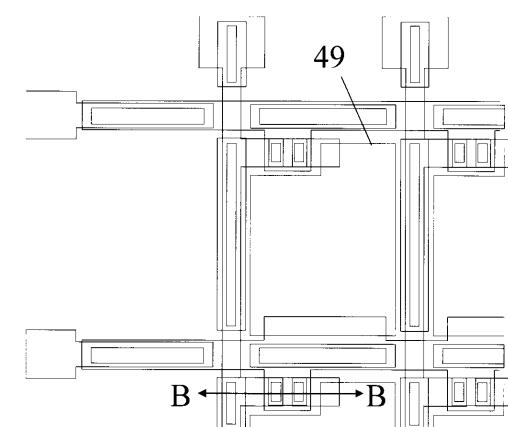

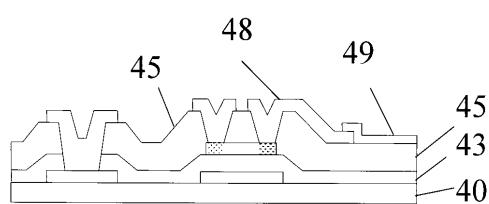

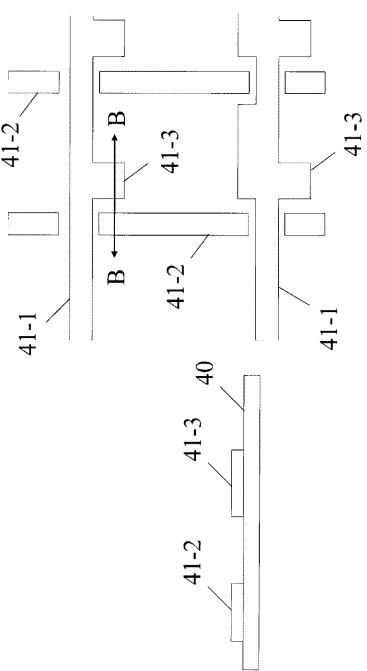

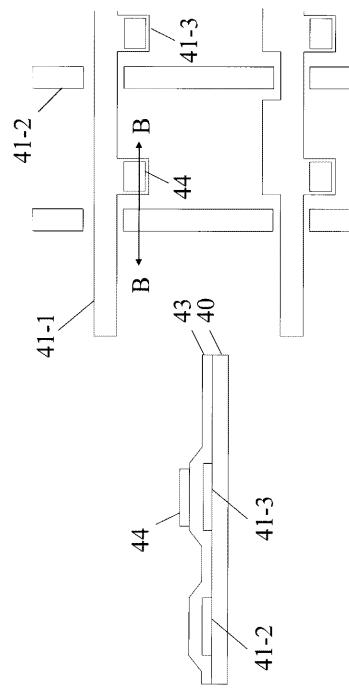

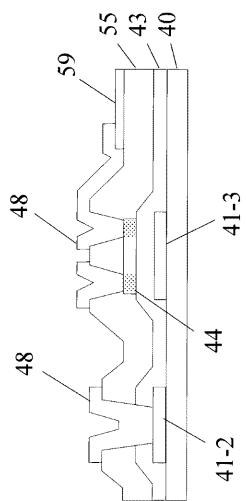

図4A～図4Jは、本発明の第4の実施形態に係る薄膜トランジスタ(「TFT」)アレイを製造するための方法を示す図である。図4Aは、図4Bに示される平面図のBB方向に沿った断面図である。図4Aによると、例えばガラス又は樹脂から作られる基板40が準備される。パターニングされた第1の金属層41が、従来のPVDプロセスによって基板40上に金属の層を形成し、その次に第1のマスクを使用し従来のパターニング及びエッチングプロセスによって、基板40上に形成される。パターニングされた第1の金属層41は、互いに実質的に平行な複数の第1の導電性ライン41-1と、第1の導電性ライン41-1に実質的に直交する複数の第2の導電性ライン41-2とを備えている。第1の導電性ライン41-1のそれぞれは、ゲート電極41-3を備えている。それぞれのゲート電極41-3は、1つの第1の導電性ライン41-1と1つの第2の導電性ライン41-2の交点の近くに配置される。それぞれの第1の導電性ライン41-1は、最終的に二層配線の主ラインとなり、それぞれの第2の導電性ライン41-2は、最終的に二層配線の分岐ラインとなる。

#### 【0023】

図4C及び図4Dによると、絶縁層43が、従来のCVDプロセス又は他の好適なプロセスによってパターニングされた第1の金属層41上に形成されている。次に、パターニングされたシリコン層44が、例えば従来のCVD、レーザアニーリング又は他の好適なプロセスによってシリコンの層を形成し、その次に第2のマスクを使用し従来のパターニング及びエッチングプロセスによって絶縁層43上に形成され、それぞれのゲート電極41-1の上に配置される活性領域を規定する。パターニングされたシリコン層44は、アモルファスシリコン層又は多結晶シリコン層の1つを有している。

#### 【0024】

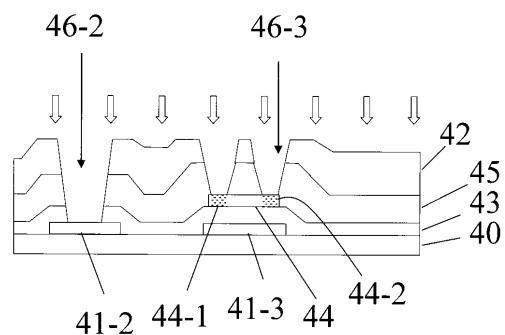

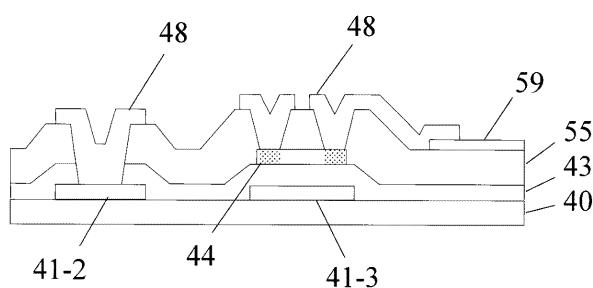

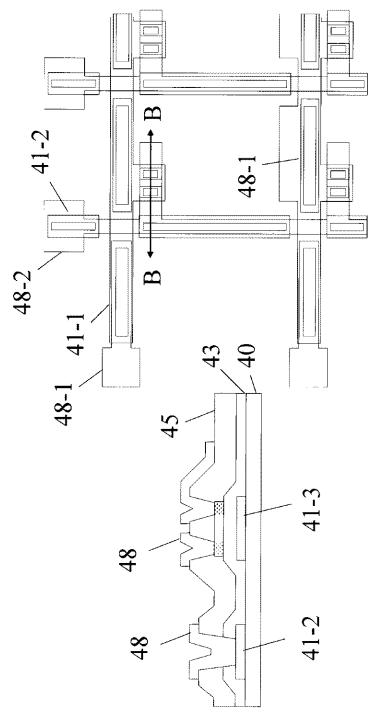

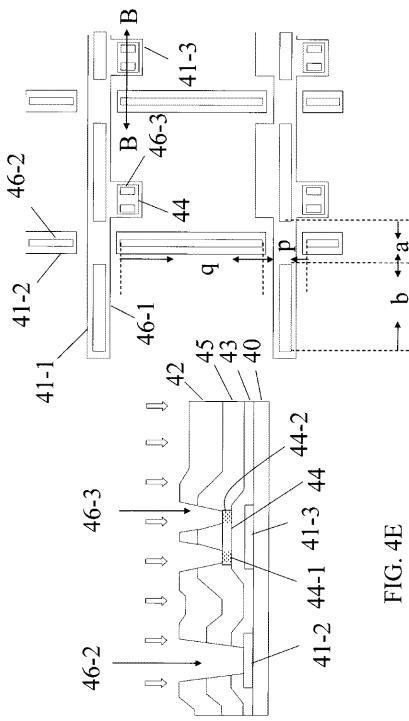

図4E及び図4Fによると、パターニングされた保護層45が、従来のCVDプロセスによって絶縁材料の層を形成し、その次に第3のマスクとフォトレジスト層を使用し従来のパターニング及びエッチングプロセスによって、絶縁層43とパターニングされたシリコン層44の上に形成されている。パターニングされた保護層45は、トレンチ46-1、46-2及び46-3を通じて第1の導電性ライン41-1、第2の導電性ライン41-2及びパターニングされたシリコン層44をそれぞれに露出させる。残りのフォトレジスト層42は、例えば従来の注入プロセス又は他の好適なプロセスによってパターニングされたシリコン層44の中へn型又はp型不純物をドープするためのマスクとして使用される。前記フォトレジスト層は、各TFTトランジスタのための第1の拡散領域44-1と第2の拡散領域44-2、すなわちソースとドレイン、又はその逆を規定する。残りのフォトレジスト層42は、その後に取り除かれる。

#### 【0025】

1つの第1の導電性ライン41-1の上に配置されるそれぞれのトレンチ46-1は、同じ1つの導電性ラインの上に配置される隣接するトレンチから距離“a”だけ離れている。第4の実施形態では、距離“a”に対するトレンチの長さ“b”的比が、約2から20の範囲である。また、1つの第2の導電性ライン41-2の上に配置されるそれぞれのトレンチ46-2は、同じ1つの導電性ラインの上に配置される隣接するトレンチから距離“p”だけ離れている。第4の実施形態では、距離“p”に対するトレンチの長さ“q”的比が、約2から20の範囲である。

#### 【0026】

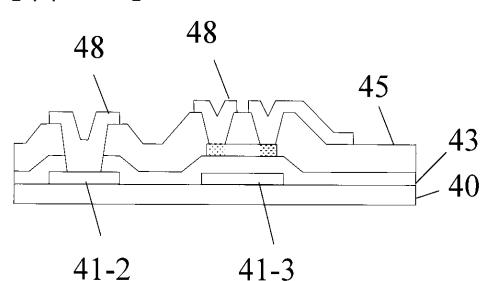

図4G及び図4Hによると、パターニングされた第2の金属層48が、パターニングされた保護層45の上に形成され、トレンチ46-1、46-2及び46-3を埋める。第2の金属層48は、従来のPVDプロセスによって金属の層を形成し、その次に第4のマ

10

20

30

40

50

スクを使用し従来のパターニング及びエッチングプロセスによって、形成される。

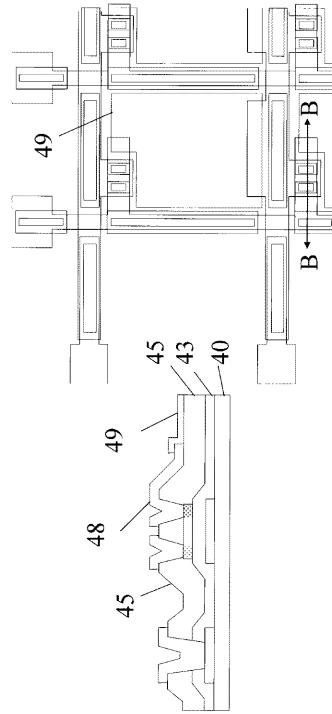

【0027】

パターニングされた第2の金属層48は、複数の第3の導電性ライン48-1と、第3の導電性ライン48-1に直交する複数の第4の導電性ライン48-2とを備えている。それぞれの第3の導電性ライン48-1は、最終的に二層配線の分岐ラインとなり、それぞれの第4の導電性ライン48-2は、最終的に二層配線の主ラインとなる。パターニングされた第2の金属層48の第3の導電性ライン48-1は、TFTアレイのための二層配線、すなわち二層走査線を形成するために、トレンチ46-1を通じてパターニングされた第1の金属層11の第1の導電性ライン41-1に電気的に接続される。パターニングされた第2の金属層48の第4の導電性ライン48-2は、TFTアレイのための二層配線、すなわち二層データ線を形成するために、トレンチ46-2を通じてパターニングされた第1の金属層41の第2の導電性ライン41-2に電気的に接続される。主ラインに対応する分岐ラインと、同じ前記主ラインに対応する直接隣接する分岐ラインとの間の距離に対する前記主ラインに対応する分岐ラインの長さの比は、約2から20の範囲である。

【0028】

図4I及び図4Jによると、パターニングされた画素電極層49が、従来のPVDプロセスによって、パターニングされた第2の金属層48とパターニングされた保護層45の上にITOなどの導電性材料の層を形成し、その次に第5のマスクを使用し従来のパターニング及びエッチングプロセスによって形成されている。パターニングされた画素電極層49は、TFTアレイのための画素電極としての機能を果たす。

【0029】

図5は、本発明の第5の実施形態に係るTFTアレイを製造するための方法を示す断面図である。図5によると、また図4A～図4Eを参照すると、第1のマスクが、パターニングされた第1の金属層41を規定するために使用される。次に、絶縁材料の層43が、パターニングされたシリコン層44の上に形成される。第2のマスクが、パターニングされたシリコン層44を規定するために使用される。保護層55が、パターニングされたシリコン層44と絶縁層43の上に形成される。パターニングされたITO膜などの画素電極層59が、従来のPVDプロセスによって、その次に第3のマスクを使用し従来のパターニング及びエッチングプロセスによって保護層55上に形成され、TFTアレイのための画素電極としての機能を果たす。その後に、保護層55は、第4のマスクを使用し従来のパターニング及びエッチングプロセスを行うことによってパターニングされ、パターニングされたシリコン層44の一部とパターニングされた第1の金属層41-1と41-2の一部を露出させる。次に、パターニングされたシリコン層44が、同じ第4のマスクを使用し従来の注入プロセスによってn型又はp型不純物を用いてドープされる。その後に、パターニングされた第2の金属層48が、第5のマスクを使用しパターニングされた導電層59とパターニングされた保護層55の上に形成される。

【0030】

また、図5及び図4A～図4Eを参照して、第1、第2及び第3のマスクは、パターニングされた第1の金属層41、パターニングされたシリコン層44及びパターニングされた保護層55を規定するためにそれぞれに使用される。次に、パターニングされたシリコン層44は、同じ第3のマスクを使用し従来の注入プロセスによって、n型又はp型不純物を用いてドープされる。パターニングされた画素電極層59は、従来のPVDプロセスによってITOなどの導電性材料の層を形成し、その次に第4のマスクを使用し従来のパターニング及びエッチングプロセスによって、パターニングされた保護層55の上に形成される。その後に、パターニングされた第2の金属層48が、第5のマスクを使用しパターニングされた画素電極層59とパターニングされた保護層55の上に形成される。

【0031】

その広範な発明概念から逸脱することなく上記実施形態に対する変更が行われ得ることが当業者により認識されるであろう。従って、本発明は開示される特定の実施形態に限定

されるものではないが、添付される特許請求の範囲によって規定されるように、本発明の精神及び範囲内での変更に及んでいることを意図するものであることを理解すべきである。

### 【0032】

更に、本発明の代表的な実施形態を記述することで、本明細書は、ステップの特定の順序として本発明の方法及び／又はプロセスを提供している。しかし、その方法又はプロセスが、ここに記述しているステップの特定の順番に依存するものでない限り、その方法又はプロセスは、記述されるステップの特定の順序に限定されるべきものではない。当業者が理解するように、ステップの他の順序が可能であり得る。従って、この明細書に記述されるステップの特定の順番は、特許請求の範囲において限定するものと解釈すべきものではない。加えて、本発明の方法及び／又はプロセスに指向された特許請求の範囲は、記載された順番でステップを行うものに限定されるべきものではなく、当業者は、その順序を変えることができ、また、本発明の精神及び範囲内にあることを容易に理解できる。

### 【図面の簡単な説明】

### 【0033】

【図1A】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1B】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1C】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1D】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1E】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1F】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1G】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1H】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1I】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図1J】本発明の第1の実施形態に係る薄膜トランジスタ（「TFT」）アレイを製造するための方法を示す図である。

【図2】本発明の第2の実施形態に係るTFTアレイを製造するための方法を示す断面図である。

【図3】本発明の第3の実施形態に係るTFTアレイを製造するための方法を示す概略図である。

【図4A】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4B】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4C】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4D】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4E】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4F】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

10

20

30

40

50

ある。

【図4G】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4H】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4I】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図4J】本発明の第4の実施形態に係るTFTアレイを製造するための方法を示す図である。

【図5】本発明の第5の実施形態に係るTFTアレイを製造するための方法を示す断面図 10 である。

【符号の説明】

【0034】

10、40 基板

11、31、41 第1の金属層

11-1、31-1、41-1、48-1 第1の導電性ライン

11-2、31-2、41-2、48-2 第2の導電性ライン

11-3、41-3 ゲート電極

13、43 絶縁層

14、44 シリコン層

15、45、55 保護層

17 ドープシリコン層

18、48 第2の金属層

18-1、48-1 第3の導電性ライン

18-2、48-2 第4の導電性ライン

19、29、49、59 画素電極層

16-1、16-2、16-3、46-1、46-2、46-3 トレンチ

36-1、36-2 コンタクトホール

10

20

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1J】

【図1I】

【図2】

【図3】

【図4B】

【図4A】

【図4C】

【図4D】

【図4F】

【図4E】

【図4G】

【図4H】

【図4J】

【図4I】

【図5】

## フロントページの続き

(51)Int.Cl. F I テーマコード(参考)

**H 01 L 23/522 (2006.01)** H 01 L 21/90 W

H 01 L 21/90 A

(72)発明者 チェン・ユ-・チェン

台湾300シンチュ・シティ、ジャンジョン・1ロード・ナンバー29番、16フロア-5

(72)発明者 チェン・フン・ツエ

台湾302シンチュ・カウンティ、ジュベイ・シティ、グオシェン・ストリート・ナンバー277

Fターム(参考) 2H092 JA26 JA28 JA34 JA37 JA41 JB24 JB33 KA05 KA15 MA05

MA07 MA13 MA17 MA30 NA22 NA23

5C094 AA02 AA14 AA21 AA44 BA03 BA43 CA19 DB01 EA04 EA10

FB12 GB10

5F033 GG03 HH04 HH07 HH11 HH22 JJ01 KK04 KK07 KK11 KK22

MM05 NN01 NN03 PP14 PP15 QQ08 QQ09 QQ37 UU05 VV06

VV15 XX27

5F110 AA03 AA28 BB01 CC07 CC08 DD01 DD02 EE02 EE03 EE04

EE06 EE14 EE15 EE37 EE42 FF02 FF03 FF04 FF29 GG02

GG13 GG15 GG25 GG44 HL02 HL03 HL04 HL06 HL08 HL11

HL12 HL22 HL24 HM19 NN02 NN04 NN35 NN72 PP03

## 【外国語明細書】

## TITLE OF THE INVENTION

[0001] Method for Manufacturing Thin Film Transistor Display Array with Dual-Layer Metal Line

## CROSS REFERENCE TO RELATED APPLICATIONS

5 [0002] This application is related to U.S. Patent Application No. 10/687,759, filed October 20, 2003 and U.S. Patent Application No. 11/131,084, filed May 17, 2005, each of which being incorporated herein by reference in their entirety.

## BACKGROUND OF THE INVENTION

[0003] The present invention relates generally to thin film transistors ("TFTs"), and more 10 particularly, to a method for manufacturing TFT arrays.

[0004] With the progress in semiconductor manufacturing techniques, the panel size of flat panel display devices such as liquid crystal display ("LCD") devices has been increasing rapidly. As a result, the conductive lines in a flat panel device have gained a considerable increase in length, adversely resulting in an undesirable resistor-capacitor ("RC") delay. Such an RC delay may 15 severely impact the performance of the flat panel device. For LCD TVs having a 37-inch or greater panel size, the RC delay within the scan lines has been found to adversely affect the display quality. One of conventional methods to address the RC delay issue proposes a two-sided driving scheme, wherein both sides of a panel are provided with drivers in order to offset or alleviate the RC delay. However, this method requires additional driving integrated circuits ("ICs"), and in turn the 20 additional cost for packaging these ICs. Consequently, it is desirable to have a method for manufacturing TFT arrays that is able to reduce RC delay in the conductive lines in the TFT arrays without compromising the driving scheme.

## BRIEF SUMMARY OF THE INVENTION

[0005] The present invention is directed to a method for manufacturing thin film transistor ("TFT") arrays including dual-layer conductive lines that obviate one or more problems resulting 25 from the limitations and disadvantages of the prior art.

[0006] In accordance with an embodiment of the present invention, there is provided a method for manufacturing a thin film transistor ("TFT") array that comprises providing a substrate, forming a patterned first metal layer on the substrate, the patterned first metal layer including a plurality of

- first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the first conductive lines including a plurality of gate electrodes, each of the gate electrodes being disposed near an intersection of one of the first conductive lines and one of the second conductive lines, forming an insulating layer over the patterned first metal layer, forming

- 5 a patterned silicon layer, forming a patterned passivation layer over the patterned silicon layer and the patterned first metal layer, exposing portions of the patterned silicon layer and a portion of each one of the first conductive lines and each one of the second conductive lines, and forming a patterned doped silicon layer and a patterned second metal layer over the patterned passivation layer, filling the exposed portions of the patterned silicon layer and the exposed portions of the first

- 10 conductive lines and the second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponds respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines.

- [0007]** Also in accordance with the present invention, there is provided a method for

- 15 manufacturing a thin film transistor ("TFT") array that comprises providing a substrate, forming a patterned first metal layer on the substrate, the patterned first metal layer including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the first conductive lines including a plurality of gate electrodes, each of the gate electrodes being disposed near an intersection of one of the first conductive lines and one of the second conductive lines, forming an insulating layer over the patterned first metal layer, forming

- 20 a patterned silicon layer, forming a patterned passivation layer over the patterned silicon layer and the patterned first metal layer, exposing portions of the patterned silicon layer and portions of each of the first conductive lines and the second conductive lines, doping impurity into the exposed portions of the patterned silicon layer, and forming a patterned second metal layer over the patterned passivation layer, filling the exposed portions of patterned silicon layer and the exposed portions of the first conductive lines or second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponds respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines of the patterned first metal layer.

- 25

- 30 **[0008]** Further in accordance with the present invention, there is provided a method for manufacturing a thin film transistor ("TFT") array that comprises providing a substrate, forming a

patterned first metal layer on the substrate, the patterned first metal layer including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the second conductive lines including a plurality of branch lines separated from each other, forming an insulating layer over the patterned first metal layer, forming a patterned silicon layer over the insulating layer, exposing portions of each of the first conductive lines and the branch lines of each of the second conductive lines of the patterned first metal layer, forming a patterned second metal layer over the patterned silicon layer, filling the exposed portions of each of the first conductive lines and the exposed branch lines of each of the second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponding respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines of the patterned first metal layer.

[0009] Additional features and advantages of the present invention will be set forth in portion in the description which follows, and in portion will be obvious from the description, or may be learned by practice of the invention. The features and advantages of the invention will be realized and attained by means of the elements and combinations particularly pointed out in the appended claims.

[0010] It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive of the invention, as claimed.

20 BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0011] The foregoing summary, as well as the following detailed description of the invention, will be better understood when read in conjunction with the appended drawings. For the purpose of illustrating the invention, there are shown in the drawings embodiments which are presently preferred. It should be understood, however, that the invention is not limited to the precise arrangements and instrumentalities shown.

[0012] In the drawings:

[0013] Figs. 1A to 1J are diagrams illustrating a method for manufacturing a thin film transistor ("TFT") array in accordance with a first embodiment of the present invention;

[0014] Fig. 2 is a cross-sectional diagram illustrating a method for manufacturing a TFT array in accordance with a second embodiment of the present invention;

[0015] Fig. 3 is a schematic diagram illustrating a method for manufacturing a TFT array in accordance with a third embodiment of the present invention;

5 [0016] Figs. 4A to 4J are diagrams illustrating a method for manufacturing a TFT array in accordance with a fourth embodiment of the present invention; and

[0017] Fig. 5 is a cross-sectional diagram illustrating a method for manufacturing a TFT array in accordance with a fifth embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

10 [0018] Reference will now be made in detail to the present embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like portions.

15 [0019] Figs. 1A to 1J are diagrams illustrating a method for manufacturing a thin film transistor (“TFT”) array in accordance with a first embodiment of the present invention. Fig. 1A is a cross-sectional view along the direction AA of a top view illustrated in Fig. 1B. Referring to Fig. 1A, a substrate 10, made of glass or resin, for example, is provided. Preferably the thickness of the substrate 10 ranges from approximately 0.3 to 0.7 mm (millimeter) but could be thinner or thicker.

— Next, a patterned first metal layer 11 is formed on the substrate 10 by forming a layer of first metal on the substrate 10 by, for example, a conventional physical vapor deposition (“PVD”), sputtering or

20 some other suitable process, followed by a conventional patterning and etching process, using a first mask. Referring to Fig. 1B, the patterned first metal layer 11 includes a plurality of first conductive lines 11-1 substantially in parallel with each other, and a plurality of second conductive lines 11-2 substantially orthogonal to the first conductive lines 11-1. Each of the first conductive lines 11-1 includes gate electrodes 11-3. Each of the gate electrodes 11-3 is disposed near an intersection of

25 one of the first conductive lines 11-1 and one of the second conductive lines 11-2. Suitable materials for the first metal layer include but are not limited to TiAlTi, MoAlMo, CrAlCr, MoW, Cr and Cu. Preferably, the thickness of gate electrodes 11-1 ranges from approximately 1000 to 2000 Å (angstrom) but could be some other thickness. Each of the first conductive lines 11-1 eventually becomes a main line of a dual-layer wire, and each of the second conductive lines 11-2 eventually becomes branch lines of a dual-layer wire. A dual-layer or multi-layer wire structure has been

30

disclosed in U.S. Patent Application No. 10/687,759, filed October 20, 2003 and U.S. Patent Application No. 11/131,084, filed May 17, 2005, which are herein incorporated by reference.

[0020] Referring to Figs. 1C and 1D, an insulation layer 13 is formed on the patterned first metal layer 11 by, for example, a conventional chemical vapor deposition (“CVD”) process or some other suitable process. Suitable materials for the insulation layer 13 include silicon nitride, silicon oxide and silicon oxynitride. Preferably, the thickness of the insulation layer 13 ranges from approximately 2500 to 4000 Å. Next, a patterned silicon layer 14 is formed on the insulation layer 13 by forming a layer of silicon by, for example, a conventional CVD or some other suitable process, followed by a conventional patterning and etching process, using a second mask. The patterned silicon layer 14 defines an active region disposed over each of the gate electrodes 11-1. The patterned silicon layer 14 comprises an amorphous silicon layer or a polycrystalline silicon layer. Preferably, the thickness of the patterned silicon layer 14 ranges from approximately 500 to 3000 Å but could be other thickness.

[0021] Referring to Figs. 1E and 1F, a patterned passivation layer 15 is formed over the insulation layer 13 and the patterned silicon layer 14 by forming a layer of insulating material such as oxide or nitride by, for example, a conventional CVD process or other suitable process followed by a conventional patterning and etching process, using a third mask. The patterned passivation layer 15 exposes the first conductive lines 11-1, the second conductive lines 11-2 and the patterned silicon layer 14 through trenches 16-1, 16-2 and 16-3, respectively. Each of the active regions is formed with a pair of trenches 16-3, which define a source region and a drain region for a corresponding TFT transistor. Preferably, the thickness of the patterned passivation layer 15 ranges from approximately 3000 to 5000 Å.

[0022] Each of the trenches 16-1 disposed over one of the first conductive lines 11-1 is separated from an adjacent trench 16-1 disposed over the same one conductive line by a distance denoted as “a”. In the first embodiment, the ratio of a length “b” of a trench to the distance “a” ranges from approximately 2 to 20. Likewise, each of the trenches 16-2 disposed over one of the second conductive lines 11-2 is separated from an adjacent trench 16-2 disposed over the same one second conductive line 11-2 by a distance denoted as “p”. In the first embodiment, the ratio of a length “q” of the trench 16-2 to the distance “p” ranges from approximately 2 to 20.

[0023] Referring to Figs. 1G and 1H, a patterned doped silicon layer 17 and a patterned second metal layer 18 are formed over the patterned passivation layer 15, filling the trenches 16-1, 16-2 and 16-3. The patterned silicon layer 17 and patterned second metal layer 18 are formed by forming a layer of heavily-doped n-type (n<sup>+</sup>) silicon by, for example, a conventional CVD process and then 5 forming a layer of second metal on the n<sup>+</sup> silicon layer by, for example, a conventional PVD process, followed by a conventional patterning and etching process, using a fourth mask. Suitable materials for the second metal layer include but are not limited to TiAlTi, MoAlMo, CrAlCr, MoW, Cr and Cu. Preferably, the thickness of the patterned doped silicon layer 17 is approximately 500 Å but could be other thicker or thinner. Preferably, the thickness of the patterned second metal layer 18 10 ranges from approximately 1000 to 3000 Å.

[0024] The patterned second metal layer 18 includes a plurality of third conductive lines 18-1 and a plurality of fourth conductive lines 18-2 orthogonal to the third conductive lines 18-1. Each of the third conductive lines 18-1 eventually becomes a branch line of a dual-layer wire, and each of the fourth conductive lines 18-2 eventually becomes a main line of a dual-layer wire. The third 15 conductive lines 18-1 of the patterned second metal layer 18 are electrically connected to the first conductive lines 11-1 of the patterned first metal layer 11 through the trenches 16-1 to form a dual-layer wire, i.e., a dual-layer scan line for the TFT array. The fourth conductive lines 18-2 of the patterned second metal layer 18 are electrically connected to the second conductive lines 11-2 of the patterned first metal layer 11 through the trenches 16-2 to form a dual-layer wire, i.e., a dual-layer 20 data line for the TFT array. The ratio of the length of a branch line corresponding to a main line to the distance between the branch line and an immediately adjacent branch line corresponding to the same main line ranges from approximately 2 to 20.

[0025] Referring to Figs. 1I and 1J, a patterned pixel electrode layer 19 is formed by forming a layer of conductive material, for example, indium tin oxide ("ITO") over the patterned second metal 25 layer 18 and the patterned passivation layer 15 by a conventional PVD process followed by a conventional patterning and etching process, using a fifth mask. The patterned pixel electrode layer 19 serves as pixel electrodes for the TFT array. Preferably, the thickness of the patterned conductive layer ranges from approximately 500 to 1000 Å.

[0026] Fig. 2 is a cross-sectional diagram illustrating a method for manufacturing a TFT array in accordance with a second embodiment of the present invention. Referring to Fig. 2, also referring to 30 Figs. 1A to 1E, a first mask is used to define the patterned first metal layer 11. Next, a layer of

- insulating material 13 is formed over the patterned first metal layer 11. A second mask is used to define the patterned silicon layer 14. A passivation layer 15 is formed over the patterned silicon layer 14 and insulating material 13. A patterned pixel electrode layer 29 such as an ITO layer is formed on the passivation layer by a conventional PVD process followed by a conventional patterning and etching process, using a third mask. Then, the passivation layer 15 is patterned by performing a conventional patterning and etching process, using a forth mask, exposing portions of the patterned silicon layer 14 and portions of the patterned first metal layer 11-1 and 11-2. Subsequently, the patterned n+ silicon layer 17 and the patterned second metal layer 18 are formed over the patterned pixel electrode layer 29 and the patterned passivation layer 15, using a fifth mask.

- 5 [0027] Alternatively, referring to Fig. 2 and also Figs. 1A to 1E, first, second and third masks may be used to define the patterned first metal layer 11, the patterned silicon layer 14 and the patterned passivation layer 25, respectively. A patterned pixel electrode layer 29 is formed over the patterned passivation layer 25 by forming a layer of conductive material such as ITO by a conventional PVD process followed by a conventional patterning and etching process, using a fourth

- 10 mask. Subsequently, the patterned n+ silicon layer 17 and the patterned second metal layer 18 are formed over the patterned pixel electrode layer 29 and the patterned passivation layer 25, using a fifth mask.

- 15 [0028] Fig. 3 is a schematic diagram illustrating a method for manufacturing a TFT array in accordance with a third embodiment of the present invention. Referring to Fig. 3, a patterned first metal layer 31 includes a plurality of first conductive lines 31-1 and a plurality of second conductive lines 31-2. Instead of a single, continuous trench such as the trench 16-2 illustrated in Fig. 1F, a plurality of contact holes 36-2 are formed in each of the second conductive lines 31-2 between two adjacent first conductive lines 31-1. Likewise, a plurality of contact holes 36-1 may be formed in each of the first conductive lines 31-1 between two adjacent second conductive lines 31-2.

- 20 [0029] Figs. 4A to 4J are diagrams illustrating a method for manufacturing a thin film transistor ("TFT") array in accordance with a fourth embodiment of the present invention. Fig. 4A is a cross-sectional view along the direction BB of a top view illustrated in Fig. 4B. Referring to Fig. 4A, a substrate 40, made of glass or resin, for example, is provided. A patterned first metal layer 41 is formed on the substrate 40 by forming a layer of metal on the substrate 40 by a conventional PVD

- 25 process followed by a conventional patterning and etching process, using a first mask. The patterned first metal layer 41 includes a plurality of first conductive lines 41-1 substantially in

parallel with each other, and a plurality of second conductive lines 41-2 substantially orthogonal to the first conductive lines 41-1. Each of the first conductive lines 41-1 includes gate electrodes 41-3. Each of the gate electrodes 41-3 is disposed near an intersection of one of the first conductive lines 41-1 and one of the second conductive lines 41-2. Each of the first conductive lines 41-1 eventually 5 becomes a main line of a dual-layer wire, and each of the second conductive lines 41-2 eventually becomes branch lines of a dual-layer wire.

[0030] Referring to Figs. 4C and 4D, an insulation layer 43 is formed on the patterned first metal layer 41 by a conventional CVD process or some other suitable process. Next, a patterned silicon layer 44 is formed on the insulation layer 43 by forming a layer of silicon by, for example, a 10 conventional CVD, laser annealing or some other suitable process, followed by a conventional patterning and etching process, using a second mask, which defines an active region disposed over each of the gate electrodes 41-1. The patterned silicon layer 44 comprises one of an amorphous silicon layer or a polycrystalline silicon layer.

[0031] Referring to Figs. 4E and 4F, a patterned passivation layer 45 is formed over the 15 insulation layer 43 and the patterned silicon layer 44 by forming a layer of insulating material by a conventional CVD process followed by a conventional patterning and etching process, using a third mask and a photoresist layer. The patterned passivation layer 45 exposes the first conductive lines 41-1, second conductive lines 41-2 and the patterned silicon layer 44 through trenches 46-1, 46-2 and 46-3, respectively. The remaining photoresist layer 42 is used as a mask for doping n-type or p- 20 type impurity into the patterned silicon layer 44 by, for example, a conventional implanting process or other suitable process. The photoresist layer defines a first diffused region 44-1 and a second diffused region 44-2, i.e., source and drain or vice versa, for each TFT transistor. The remaining photoresist layer 42 is then stripped off.

[0032] Each of the trenches 46-1 disposed over one of the first conductive lines 41-1 is 25 separated from an adjacent trench disposed over the same one conductive line by a distance "a". In the fourth embodiment, the ratio of a length "b" of a trench to the distance "a" ranges from approximately 2 to 20. Likewise, each of the trenches 46-2 disposed over one of the second conductive lines 41-2 is separated from an adjacent trench disposed over the same one conductive line by a distance "p". In the fourth embodiment, the ratio of the length "q" of a trench to the 30 distance "p" ranges from approximately 2 to 20.

[0033] Referring to Figs. 4G and 4H, a patterned second metal layer 48 is formed over the patterned passivation layer 45, filling the trenches 46-1, 46-2 and 46-3. The second metal layer 48 is formed by forming a layer of metal by a conventional PVD process followed by a conventional patterning and etching process, using a fourth mask.

- 5 [0034] The patterned second metal layer 48 includes a plurality of third conductive lines 48-1 and a plurality of fourth conductive lines 48-2 orthogonal to the third conductive lines 48-1. Each of the third conductive lines 48-1 eventually becomes branch lines of a dual-layer wire, and each of the fourth conductive lines 48-2 eventually becomes a main line of a dual-layer wire. The third conductive lines 48-1 of the patterned second metal layer 48 are electrically connected to the first conductive lines 41-1 of the patterned first metal layer 41 through the trenches 46-1 to form a dual-layer wire, i.e., a dual-layer scan line for the TFT array. The fourth conductive lines 48-2 of the patterned second metal layer 48 are electrically connected to the second conductive lines 41-2 of the patterned first metal layer 41 through the trenches 46-2 to form a dual-layer wire, i.e., a dual-layer data line for the TFT array. The ratio of the length of a branch line corresponding to a main line to the distance between the branch line and an immediately adjacent branch line corresponding to the same main line ranges from approximately 2 to 20.

- 10

- 15

- [0035] Referring to Figs. 4I and 4J, a patterned pixel electrode layer 49 is formed by forming a layer of conductive material such as ITO over the patterned second metal layer 48 and patterned passivation layer 45 by a conventional PVD process followed by a conventional patterning and etching process, using a fifth mask. The patterned pixel electrode layer 49 serves as pixel electrodes for the TFT array.

- 20

- [0036] Fig. 5 is a cross-sectional diagram illustrating a method for manufacturing a TFT array in accordance with a fifth embodiment of the present invention. Referring to Fig. 5, also referring to Figs. 4A to 4E, a first mask is used to define the patterned first metal layer 41. Next, a layer of insulating material 43 is formed over the patterned silicon layer 44. A second mask is used to define the patterned silicon layer 44. A passivation layer 55 is formed over the patterned silicon layer 44 and insulating material 43. A patterned pixel electrode layer 59 such as an ITO film is formed on the passivation layer 55 by a conventional PVD process followed by a conventional patterning and etching process, using a third mask, which serves as pixel electrodes for the TFT array. Then, the passivation layer 55 is patterned by performing a conventional patterning and etching process, using a fourth mask, exposing portions of the patterned silicon layer 44 and

- 25

- 30

portions of the patterned first metal layer 41-1 and 41-2. Next, the patterned silicon layer 44 is doped with n-type or p-type impurity by a conventional implantation process, using the same fourth mask. Subsequently, the patterned second metal layer 48 is formed over the patterned conductive layer 59 and the patterned passivation layer 55, using a fifth mask.

- 5   **[0037]**   Alternatively, referring to Fig. 5 and also Figs. 4A to 4E, first, second and third masks are used to define the patterned first metal layer 41, the patterned silicon layer 44 and the patterned passivation layer 55, respectively. Next, the patterned silicon layer 44 is doped with n-type or p-type impurity by a conventional implanting process, using the same third mask. The patterned pixel electrode layer 59 is formed over the patterned passivation layer 55 by forming a layer of conductive material such as ITO by a conventional PVD process followed by a conventional patterning and etching process, using a fourth mask. Subsequently, the patterned second metal layer 48 is formed over the patterned pixel electrode layer 59 and the patterned passivation layer 55, using a fifth mask.

- 10

- 15   **[0038]**   It will be appreciated by those skilled in the art that changes could be made to the embodiments described above without departing from the broad inventive concept thereof. It is understood, therefore, that this invention is not limited to the particular embodiments disclosed, but it is intended to cover modifications within the spirit and scope of the present invention as defined by the appended claims.

- 20   **[0039]**   Further, in describing representative embodiments of the present invention, the specification may have presented the method and/or process of the present invention as a particular sequence of steps. However, to the extent that the method or process does not rely on the particular order of steps set forth herein, the method or process should not be limited to the particular sequence of steps described. As one of ordinary skill in the art would appreciate, other sequences of steps may be possible. Therefore, the particular order of the steps set forth in the specification should not be construed as limitations on the claims. In addition, the claims directed to the method and/or process of the present invention should not be limited to the performance of their steps in the order written, and one skilled in the art can readily appreciate that the sequences may be varied and still remain within the spirit and scope of the present invention.

- 25

## CLAIMS

I/we claim:

1. A method for manufacturing a thin film transistor (“TFT”) array, comprising:

- providing a substrate;

- 5 forming a patterned first metal layer on the substrate, the patterned first metal layer including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the first conductive lines including a plurality of gate electrodes, each of the gate electrodes being disposed near an intersection of one of the first conductive lines and one of the second conductive lines;

- 10 forming an insulating layer over the patterned first metal layer;

- forming a patterned silicon layer;

- forming a patterned passivation layer over the patterned silicon layer and the patterned first metal layer, exposing portions of the patterned silicon layer and a portion of each one of the first conductive lines and each one of the second conductive lines; and

- 15 forming a patterned doped silicon layer and a patterned second metal layer over the patterned passivation layer, filling the exposed portions of the patterned silicon layer and the exposed portions of the first conductive lines and the second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponding respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines.

- 20

2. The method of claim 1, further comprising forming a patterned pixel electrode layer over the patterned second metal layer and the patterned passivation layer.

- 25 3. The method of claim 1, further comprising:

- forming a passivation layer over the patterned silicon layer;

- forming a patterned pixel electrode layer over the passivation layer; and

patterning the passivation layer, exposing portions of the patterned silicon layer and portions of the first conductive lines or second conductive lines.

4. The method of claim 1, further comprising:

5 forming a patterned pixel electrode layer over the patterned passivation layer; and

forming a patterned doped silicon layer and a patterned second metal layer over the patterned passivation layer and the patterned pixel electrode layer, filling the exposed portions of patterned doped silicon layer and the exposed portions of the first conductive lines or second conductive lines.

10

5. The method of claim 1, further comprising forming trenches in the passivation layer and the insulating layer over at least one of the first conductive lines and second conductive lines of the patterned first metal layer.

15 6. The method of claim 5, further comprising electrically connecting the patterned first metal layer and the patterned second metal layer through the trenches.

7. The method of claim 1, further comprising forming a plurality of contact holes in the passivation layer and the insulating layer over at least one of the first conductive lines and second conductive lines of the patterned first metal layer..

20 8. The method of claim 7, further comprising electrically connecting the patterned first metal layer and the patterned second metal layer through the plurality of contact holes.

25 9. The method of claim 1, wherein each of the second conductive lines of the patterned first metal layer includes a plurality of branch lines separated from each other.

10. The method of claim 9, wherein the ratio of the length of each of the branch lines to the distance between the each branch line and its immediately adjacent branch line disposed on the same second conductive line ranges from approximately 2 to 20.

- 5     11. The method of claim 1, wherein each of the third conductive lines of the patterned second metal layer includes a plurality of branch lines separated from each other.

12. The method of claim 11, wherein the ratio of the length of each of the branch lines to the distance between the each branch line and its immediately adjacent branch line disposed on the same third conductive line ranges from approximately 2 to 20.

- 10

13. The method of claim 1, further comprising forming a patterned silicon layer including one of an amorphous silicon layer or a polycrystalline silicon layer.

- 15     14. A method for manufacturing a thin film transistor (“TFT”) array, comprising:

- providing a substrate;

- forming a patterned first metal layer on the substrate, the patterned first metal layer including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the first conductive lines including a plurality of gate electrodes, each of the gate electrodes being disposed near an intersection of one of the first conductive lines and one of the second conductive lines;

- forming an insulating layer over the patterned first metal layer;

- forming a patterned silicon layer;

- forming a patterned passivation layer over the patterned silicon layer and the patterned first metal layer, exposing portions of the patterned silicon layer and portions of each of the first conductive lines and the second conductive lines;

- 25

- doping impurity into the exposed portions of the patterned silicon layer; and

forming a patterned second metal layer over the patterned passivation layer, filling the exposed portions of patterned silicon layer and the exposed portions of the first conductive lines or second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponds 5 respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines of the patterned first metal layer.

15. The method of claim 14, further comprising forming a patterned pixel electrode layer over the patterned second metal layer and the patterned passivation layer.

10

16. The method of claim 14, further comprising:

forming a passivation layer over the patterned silicon layer;

forming a patterned pixel electrode layer over the passivation layer; and

15 patterning the passivation layer, exposing portions of the patterned silicon layer and portions of the first conductive lines or second conductive lines.

17. The method of claim 14, further comprising:

doping impurity into the exposed portions of the patterned silicon layer;

forming a patterned pixel electrode layer over the patterned passivation layer; and

20 forming a patterned second metal layer over the patterned passivation layer and the patterned pixel electrode layer, filling the exposed portions of patterned silicon layer and the exposed portions of the first conductive lines or second conductive lines.

18. The method of claim 14, further comprising forming trenches in the passivation layer and the 25 insulating layer over at least one of the first conductive lines or second conductive lines of the patterned first metal layer.

19. The method of claim 18, further comprising electrically connecting the patterned first metal layer and the patterned second metal layer through the trenches.

20. The method of claim 14, further comprising forming a plurality of contact holes in the 5 passivation layer and the insulating layer over at least one of the first conductive lines and the second conductive lines of the patterned first metal layer.

21. The method of claim 20, further comprising electrically connecting the patterned first metal layer and the patterned second metal layer through the plurality of contact holes.

- 10

22. The method of claim 14, wherein each of the second conductive lines of the patterned first metal layer includes a plurality of branch lines separated from each other.

23. The method of claim 22, wherein the ratio of the length of each of the branch lines to the 15 distance between the each branch line and its immediately adjacent branch line disposed on the same second conductive line ranges from approximately 2 to 20.

24. The method of claim 14, wherein each of the third conductive lines of the patterned second metal layer includes a plurality of branch lines separated from each other.

- 20

25. The method of claim 24, wherein the ratio of the length of each of the branch lines to the distance between the each branch line and its immediately adjacent branch line disposed on the same first conductive line ranges from approximately 2 to 20.

26. The method of claim 14, further comprising forming a patterned silicon layer including one of 25 an amorphous silicon layer or a polycrystalline silicon layer.

27. A method for manufacturing a thin film transistor ("TFT") array, comprising:

providing a substrate;

forming a patterned first metal layer on the substrate, the patterned first metal layer including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines, each of the second conductive lines including a plurality of branch lines separated from each other;

5

forming an insulating layer over the patterned first metal layer;

forming a patterned silicon layer over the insulating layer;

exposing portions of each of the first conductive lines and the branch lines of each of the second conductive lines of the patterned first metal layer;

10

forming a patterned second metal layer over the patterned silicon layer, filling the exposed portions of each of the first conductive lines and the exposed branch lines of each of the second conductive lines, the patterned second metal layer including a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponding respectively to one of the plurality of first conductive lines and one of the plurality of second conductive lines of the patterned first metal layer.

15

28. The method of claim 27, wherein each of the third conductive lines of the patterned second metal layer includes a plurality of branch lines separated from each other.

20

29. The method of claim 28, wherein the ratio of the length of each of the branch lines to the distance between the each branch line and its immediately adjacent branch line disposed on the same third conductive line of the patterned first metal layer ranges from approximately 2 to 20.

25

30. The method of claim 27, wherein the ratio of the length of each of the branch lines to the distance between the each branch line and its immediately adjacent branch line disposed on the same fourth conductive line of the patterned second metal layer ranges from approximately 2 to 20.

**ABSTRACT OF THE DISCLOSURE**

A method for manufacturing a thin film transistor ("TFT") array includes providing a substrate, a patterned first metal layer on the substrate including a plurality of first conductive lines and a plurality of second conductive lines disposed orthogonal to the first conductive lines,

5 an insulating layer over the patterned first metal layer, a patterned silicon layer, a patterned passivation layer over the patterned silicon layer, and a patterned doped silicon layer and a patterned second metal layer over the patterned passivation layer, filling exposed portions of the patterned silicon layer and exposed portions of the first conductive lines and the second conductive lines, where the patterned second metal layer includes a plurality of third conductive lines and a plurality of fourth conductive lines, each of which corresponding respectively to one

10 of the plurality of first conductive lines and the plurality of second conductive lines.

FIG. 1B

FIG. 1D

FIG. 1F

FIG. 1C

FIG. 1J

FIG. 1I

FIG. 3

FIG. 2

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4G

FIG. 4D

FIG. 4E

FIG. 4F

FIG. 4I

FIG. 4J

FIG. 5