## (12) UK Patent Application (19) GB (11) 2 270 603 (13) A

(43) Date of A Publication 16.03.1994

- (21) Application No 9219054.5

- (22) Date of Filing 09.09.1992

- (71) Applicant(s)

**Sony United Kingdom Limited**

(Incorporated in the United Kingdom)

Sony House, South Street, STAINES, Middlesex, TW18 4PF, United Kingdom

(72) Inventor(s)

Clive Henry Gillard Michael John Ludgate

(74) Agent and/or Address for Service

D Young & Co 21 New Fetter Lane, LONDON, EC4A 1DA, United Kingdom

- (51) INT CL<sup>5</sup>

H03M 7/40

- (52) UK CL (Edition M )

H4F FD1A9 FD12M FD3 FD30K FRD

H4P PDCFD

- (56) Documents Cited

GB 2138184 A EP 0384782 A1 WO 89/07372 A1

US 4376933 A

**ONLINE DATABASES: WPI**

#### (54) Image data formatting

(57) Image data formatting apparatus for formatting variable bit length data words (luminance and chrominance) into successive fixed bit length data words comprises a 32-bit circular buffer (160) comprising a plurality of serially connected buffer sections, each buffer section having the same bit length (8 bits) as one of the fixed bit length data words. A modulo 32 counter (120) generates a count of the cumulative length of received variable bit length data words. Each received variable bit length data word is stored in the 32 bit circular buffer (160) at a bit position dependent on the count signal, and, in response to a detection that data has been stored in all of the bits of that buffer section, the stored data from that buffer section is output as a fixed bit length data word.

~

Fig. 2

Fig. 3

| Bits:                                              | Code V                          | Words:<br>3 4              | 5                     | 6                     | 7                     | 8                |     |

|----------------------------------------------------|---------------------------------|----------------------------|-----------------------|-----------------------|-----------------------|------------------|-----|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9     | X<br>X<br>X<br>X<br>X<br>X      | x<br>x<br>x<br>x<br>x<br>x |                       |                       | X                     | X<br>X<br>X<br>X | MSB |

| 10<br>11<br>12<br>13<br>14                         | X<br>X<br>X<br>X<br>X           |                            | X<br>X<br>X<br>X<br>X | <b>(X</b> )           |                       |                  | MSB |

| 15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | X<br>X<br>X<br>X<br>X<br>X<br>X |                            |                       | X<br>X<br>X<br>X<br>X |                       |                  | MSB |

| 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31       |                                 | X<br>X<br>X<br>X<br>X<br>X |                       | X<br>X                | x<br>x<br>x<br>x<br>x |                  | MSB |

Code Length: 10 14 4 12 7 11 7 6 Count mod 32: 10 24 28 8 15 26 1 7 Fig. 5

### DATA FORMATTING

This invention relates to the field of data formatting, and more particularly to the formatting of variable bit length data words into successive fixed bit length data words.

5

10

15

20

25

30

35

Some data compression systems produce compressed data comprising successive variable bit length code words. For example, in an image data compression system proposed by the Joint Photographic Experts Group (JPEG), image data are subjected to frequency separation, quantisation and then entropy encoding. The entropy encoding stage generates variable bit length data words in such a way that more commonly occurring data patterns (such as runs of zero-valued data) are encoded as shorter data words.

Although variable length encoding can allow data to be efficiently compressed, subsequent storage of the data or other processes such as error correction encoding generally operate on fixed length data words. It is therefore necessary to convert the variable length data words into fixed length data words. However, the data format conversion itself introduces an additional data processing overhead. In a non real time system, such as still image processing and display in a computer system, this is not a particular problem. However, in a system dealing with data such as real time video data, the high data rates present a particular challenge in providing data format conversion in a way that can keep pace with the overall data rate and only introduce a small time lag in the processing.

This invention provides a data formatting apparatus for formatting variable bit length data words into successive fixed bit length data words, the apparatus comprising: an N-bit circular buffer comprising a plurality of concatenated buffer sections, each buffer section having the same bit length as one of the fixed bit length data words; a modulo-N counter for generating a count signal in response to the cumulative length of received variable bit length data words; means for storing a current variable bit length data word in the N-bit circular buffer at a bit position dependent on the count signal; means associated with each buffer section for detecting whether data has been stored in all of the bits of that buffer section; and means responsive to a detection that data has been stored in all of the bits of a buffer

section for outputting the stored data from that buffer section as a fixed bit length data word.

~

In a preferred embodiment the means for storing comprises an N-bit barrel-rotator operable to barrel-rotate each variable bit length data word by a number of bits dependent upon the count signal generated by the modulo-N counter in respect of the preceding variable bit length data word. In this way the most significant bit of the current variable length data word can be barrel-rotated to a bit position adjacent to the least significant bit of the preceding variable length data word, before the current variable bit length data word is stored in the N-bit buffer.

5

10

15

20

25

30

35

Preferably the means for storing comprises an enable generator, responsive to the count signals generated by the modulo-N counter in respect of the current and the preceding variable bit length data words, for generating respective write-enable signals to control writing of each bit of the current variable bit length data word from the barrel-rotator to the N-bit buffer.

In advantageously simple embodiments the detecting means associated with each buffer section is operable to detect the generation of a write-enable signal to control writing to a predetermined bit in that buffer section.

Viewed from a second aspect this invention provides a method of formatting variable bit length data words into successive fixed bit length data words, the method comprising the steps of: generating a modulo-N count signal in response to the cumulative length of received variable bit length data words; storing a received variable bit length data word in an N-bit circular buffer at a bit position dependent on the count signal, the N-bit circular buffer comprising a plurality of concatenated buffer sections, each buffer section having the same bit length as one of the fixed bit length data words; detecting, for each buffer section, whether data has been stored in all of the bits of that buffer section; and outputting the stored data from a buffer section as a fixed bit length data word in response to a detection that data has been stored in all of the bits of that buffer section.

The invention will now be described by way of example with reference to the accompanying drawings, throughout which like parts are referred to by like references, and in which:

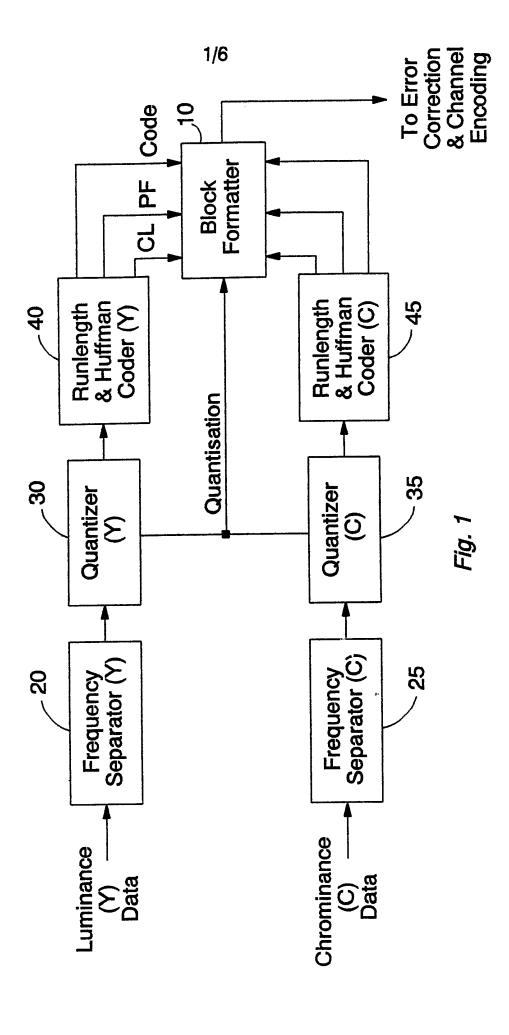

Figure 1 is a schematic block diagram of a video data compression system;

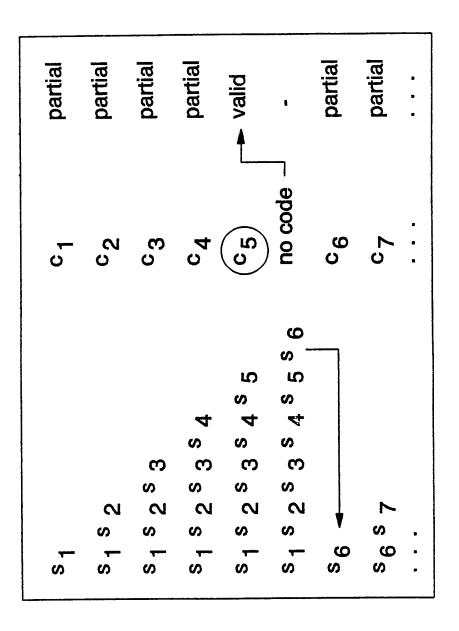

Figure 2 is a schematic illustration showing the operation of a runlength and Huffman coder;

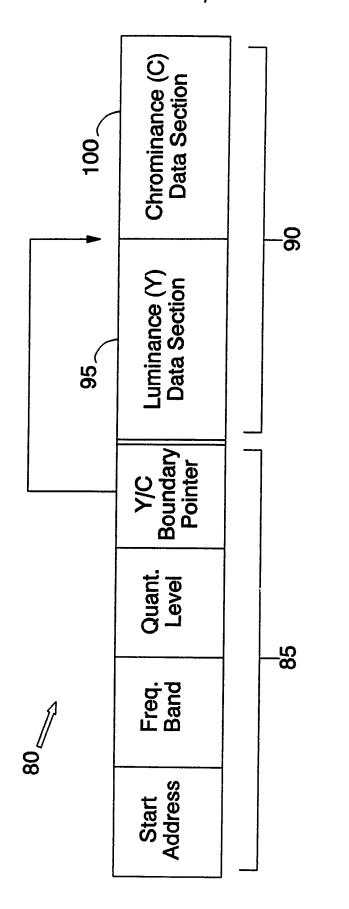

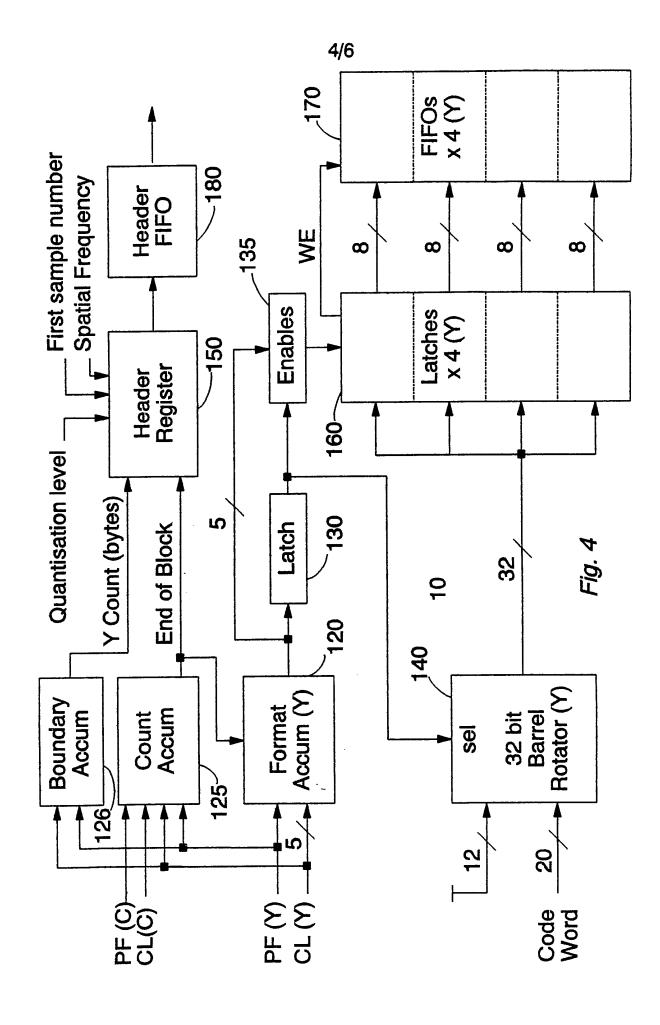

Figure 3 is a schematic illustration of a formatted data block; Figure 4 is a schematic block diagram of the data input side of a block formatter;

Figure 5 is a schematic illustration showing the operation of the apparatus of Figure 4; and

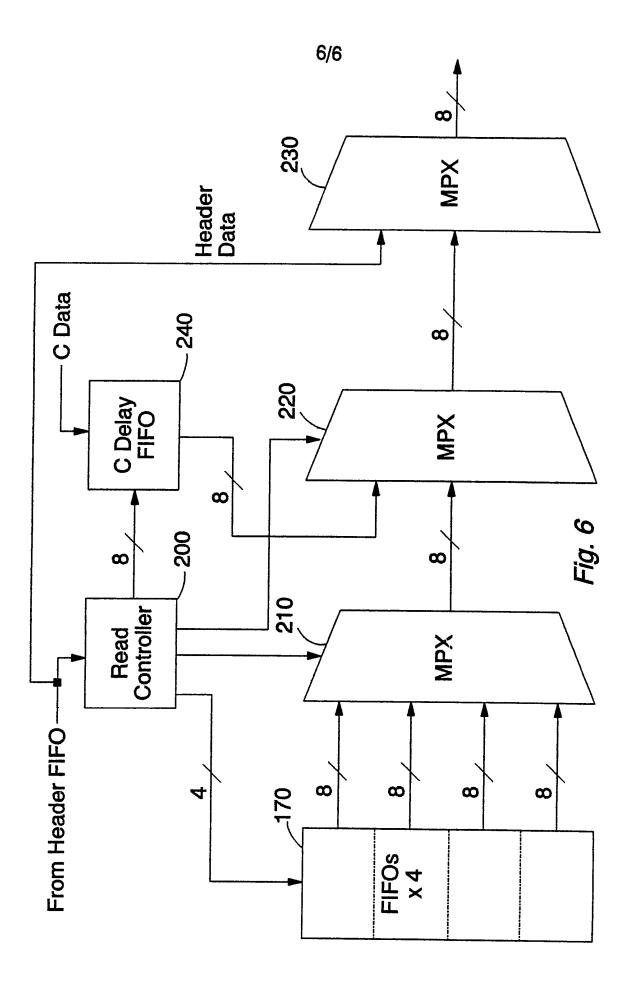

Figure 6 is a schematic block diagram of the data output side of a block formatter.

Referring now to Figure 1, a video data compression system is shown in which luminance (Y) and chrominance (C) video data are separately compressed before being combined into data blocks by a block formatter 10. The video data compression system shown is suitable for use in a digital video tape recorder (DVTR), in which case the data blocks output by the block formatter 10 are subjected to error correction processing and channel encoding before being recorded on a magnetic tape (not shown).

Substantially identical data compression processing is applied to the luminance data and the chrominance data, although the degree of compression applied may be different for the luminance data and for the The luminance and chrominance data are first chrominance data. supplied to respective frequency separators 20, 25 which include banks of horizontal and vertical finite impulse response filters that serve to split and decimate the data into respective frequency-transformed images comprising sub-band components in the two-dimensional spatial frequency domain. Data representing the frequency-transformed luminance and chrominance images are supplied from the frequency separators 20, 25 to respective quantisers 30, 35, in which the data are subjected to lossy quantisation. The quantised data are then passed, in the form of 12-bit data samples, to respective luminance and chrominance runlength and Huffman coders 40, 45. The runlength and Huffman coders 40, 45 exploit correlation within the quantised data to effect compression; their output comprises data words having a variable length in such a way that more commonly occurring data patterns within the quantised data are represented by shorter variable length data words.

15

10

5

20

25

30

35

5

10

15

20

25

30

35

Each of the runlength and Huffman coders 40, 45 processes the quantised data in a serial fashion. As each 12-bit data sample of the quantised data is received, a "partial" (or interim) Huffman code is generated to represent the pattern of data samples of the quantised data received since a "valid" (or complete) Huffman code was last output by the runlength and Huffman coder. If a received data sample (when added to the pattern of data samples for which a partial code has been generated) results in a data sample pattern to which a Huffman code has not been assigned, the most recent partial code is output by the runlength and Huffman coder as a "valid" code, and the coding starts again from that received data sample. This processing is illustrated in Figure 2, in which respective Huffman codes  $c_1$  to  $c_5$  are generated as the data samples  $s_1$  to  $s_5$  are received. The codes  $c_1$  to  $c_4$ are designated as partial codes, because, in each case, when the next data sample is received a new Huffman code can be generated. However, the data sample pattern formed by the concatenation of the pattern  $s_1s_2s_3s_4s_5$  and the received data sample  $s_6$  does not have a corresponding Huffman code and so cannot be encoded by the runlength and Huffman coder. The code  $c_5$ , representing the data sample pattern  $s_1s_2s_3s_4s_5$ , is therefore output as a valid Huffman code, and coding is restarted from the received data sample s6.

In the present embodiment, the Huffman codes comprise data words having a variable length of up to 20 bits. At each stage of coding (i.e. as each sample of the quantised data is processed by the runlength and Huffman coder), either a partial or a valid Huffman code is output by the coder on a 20-bit parallel data bus. Any bits of the data bus not occupied by bits of the Huffman code are set to logical 1. At the same time, a 5-bit number indicating the length in bits of the current Huffman code is supplied on a "code length" (CL) output, and a "partial flag" (PF) output from the runlength and Huffman coder indicates whether the current Huffman code is a partial or a valid code. These three sets of output signals from each of the runlength and Huffman coders 40, 45 are supplied to the block formatter 10.

The variable length data words output by the luminance and chrominance runlength and Huffman coders 40, 45 in Figure 1 are combined into a single data stream and formatted into fixed length data blocks by the block formatter 10. The block formatter 10 also receives

signals from the quantisers 30, 35 indicative of the degree of quantisation applied to the compressed data currently being received by the block formatter.

As mentioned above, the formatted data blocks output by the block formatter 10 are subjected to error correction processing and channel encoding before being recorded on a magnetic tape.

Figure 3 is a schematic illustration of a formatted data block 80 generated by the block formatter 10. The data block 80 comprises a 4-byte header section 85 and a 120-byte video data section 90.

The video data section 90 comprises a luminance data section 95 and a chrominance data section 100, which represent identical portions of the frequency-transformed luminance and chrominance images generated by the respective frequency separators 20, 25. However, the relative sizes of the luminance data section 95 and the chrominance data section 100 will depend (amongst other things) on the respective degrees of quantisation applied by the quantisers 30 and 35, and on the information content of those portions of the transformed luminance and chrominance images.

Each formatted data block 80 is self-contained, in so far as it can be replayed and decoded even when adjacently recorded data blocks are not successfully replayed. This means that it is still possible to recover video data during, for example, shuttle (high speed) tape replay when only some of the data blocks are successfully replayed. This feature is made possible by including in each formatted data block 80 the header section 85 defining the relative sizes of the luminance and chrominance data sections, the degree of compression applied to the data in the video data section 90 and the portion of the respective frequency-transformed images represented by the luminance chrominance data in the video data section 90. In particular, the header section 85 comprises a start address indicative of the position of the video data in the video data section 90 within the transformed images generated by the frequency separators 20 and 25; an indication of the spatial frequency band of the luminance and chrominance data in the data section 90; an indication of the degree of quantisation applied to that data; and a Y/C boundary pointer. The Y/C boundary pointer indicates the position within the video data section 90 of the boundary between the luminance data section 95 and the chrominance data

30

5

10

15

20

25

35

section 100.

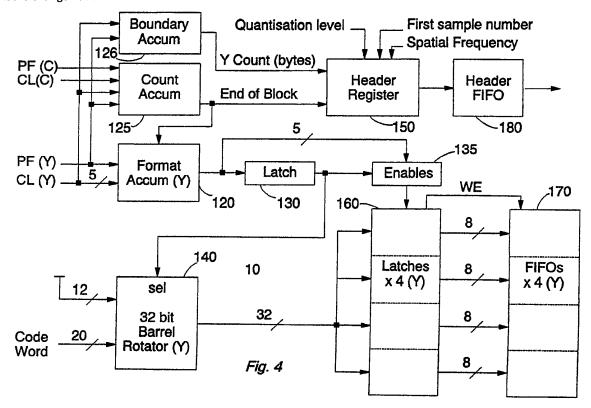

Figure 4 is a schematic block diagram of the data input side of the block formatter 10. In the block formatter 10, substantially identical processing is applied to the compressed luminance data received from the runlength and Huffman coder 40 and to the compressed chrominance data received from the runlength and Huffman coder 45. Accordingly, for clarity of the diagram, only the processing applied specifically to the luminance data, and the common processing applied to both luminance and chrominance data, have been shown.

The code length and partial code signals from the luminance runlength and Huffman coder 40 are received by a format accumulator 120. The format accumulator 120 generates a 5-bit output signal representing a modulo-32 count of the code lengths of valid luminance Huffman codes received during the formatting of a current data block. The count signal is supplied to a latch 130, to an enable generator 135, and (via the latch 130) to a 32-bit barrel-rotator 140.

A count accumulator 125 also receives the luminance code length and partial code signals, along with corresponding code length and partial code signals from the chrominance runlength and Huffman coder 45. The count accumulator 125 maintains a count of the cumulative lengths of valid luminance codes and of valid chrominance codes. These counts are then summed to generate a total count. When this total count reaches the available length of the video data section 90 (effectively 119 bytes, because the luminance and chrominance data sections are eventually rounded up to the nearest byte), an end of block signal is generated by the count accumulator 125. The end of block signal is supplied to the format accumulator 120, a header register 150, and the runlength and Huffman coders 40 and 45.

The value of the Y/C pointer is generated by a boundary accumulator 126. As described above, the Y/C pointer is included in the header section 85 of each formatted data block, and indicates the boundary between the luminance data section 95 and the chrominance data section 100 in that data block. The position of this boundary is defined only to the nearest byte (to reduce the number of bits required to represent the Y/C pointer) and is dependant on the quantity of luminance data contained in the luminance data section 95. Therefore, the boundary accumulator maintains a count of the cumulative length of

the luminance Huffman codes to be included in each data block. When the end of a block is detected, the boundary accumulator 126 supplies the cumulative luminance code length (rounded up to the nearest byte) to the header register 150 for inclusion in the block header as the Y/C pointer.

5

10

15

20

25

30

35

As each valid luminance Huffman code is received by the block formatter, the length of that code in bits is added to the count held The Huffman code word itself is by the format accumulator 120. received on a 20-bit parallel data bus by the 32-bit barrel-rotator 140, with any unused bits of the data bus being set to logical 1. (The 12 remaining inputs of the 32-bit barrel-rotator are also set to logical 1). The barrel-rotator 140 operates to barrel-rotate the code word at its input by a number of bits corresponding to the previous count output of the format accumulator 120. At the same time, the enable generator 135 is supplied with the current and previous count outputs of the format accumulator 120 (i.e. directly and via the latch From these two inputs, the enable generator 135 establishes which bits of the 32-bit barrel-rotator 140 are occupied by data bits of the Huffman code word, and sets corresponding enabling signals to control writing of only those bits from the barrel-rotator 140 into a 32-bit buffer 160.

The 32-bit buffer 160 comprises four 8-bit latches, concatenated together to form the 32-bit wide buffer.

The arrangement described above means that as each valid Huffman code word is received by the block formatter 10, that word is barrel-rotated so that that word's most significant bit (MSB) is stored in the buffer 160 immediately adjacent to the least significant bit (LSB) of the previously received valid code word. In this way, variable length Huffman code words received on a parallel data bus are abutted next to one another to form an essentially continuous data stream.

The abutted code words held in the buffer 160 are read out for storage in a first-in-first-out (FIFO) store 170. The transfer from the buffer 160 to the FIFO store 170 takes place in fixed length 8-bit data words. To achieve this, whenever the MSB of one of the four 8-bit latches is selected by the enable generator 135 (indicating that data has been written to the whole of that 8-bit latch) a write enable (WE) signal is generated to control the transfer of the 8 bits of data

previously held by that latch into the FIFO store 170.

When the count accumulator 125 detects that the end of a block of data has been reached, it supplies an end of block signal to the format accumulator 120. This has a number of effects. The current Huffman code is considered to be a valid code. The format accumulator 120 adds the current code length to its currently held count and rounds up the result to the nearest byte (i.e. the nearest multiple of 8 bits in modulo 2 arithmetic). Because the count has been rounded up to the nearest byte, the data transferred from the barrel-rotator 140 to the buffer 160 is padded with logical ones (if necessary) to fill a complete latch in the buffer 160. The logical ones are available either from unused bits of the 20-bit Huffman codes or from the twelve additional inputs to hte barrel rotator 140.

Padding the last fixed length data word of the luminance data section 95 (and of the chrominance data section 100) does not cause problems when the Huffman codes are subsequently decoded. This is because a succession of up to seven logical ones does not form a Huffman code which represents valid data. Instead, the succession of logical ones is ignored by a subsequent Huffman decoder.

The header register receives the end of block signal from the count accumulator 125, along with the total number of bytes of luminance data in the current data block. The header register also receives an indication of the degree of quantisation applied to the data in that block (from the quantisers 30, 35), along with an indication of the frequency band of that data and the sample address of the first sample represented by the data (both of which are determined by the runlength and Huffman coders 40, 45 from the position of the currently received data in the serial data stream received from the quantisers 30, 35). These items are concatenated to form the block header 85 for the current block; this block header is stored for later retrieval in a header FIFO 180.

Figure 5 is a schematic illustration showing the operation of the block formatter circuit of Figure 4. In Figure 4 the 32 bits of the buffer 160 are numbered from 0 to 31 in a vertical direction and are arranged into four groups of 8 bits, where each group represents one of the 8-bit latches. Eight consecutive valid Huffman code words are illustrated (numbered from 1 to 8) having respective code lengths of

10, 14, 4, 12, 7, 11, 7 and 6. In the example shown, the count held by the format accumulator 10 is assumed to be zero when the first of the code words (code word 1) is received.

Code word 1 has a length of 10 bits. It is barrel-rotated by a number of bits corresponding to the count previously held by the format accumulator (i.e. zero), and so is written to the bits 0 to 9 of the buffer 160. Bit 7 of the buffer 160 is a most significant bit (MSB) of one of the four 8-bit latches, so writing to bit 7 triggers the previous contents of that latch to be transferred as an 8-bit word to the FIFO store 170.

5

10

15

20

25

30

35

When the second valid code word (code word 2) is received, its length (14 bits) is added to the count currently held by the format accumulator 120 (10 bits). Code word 2 is barrel-rotated by 10 bits (the previously held count). The enable generator 125 receives the current count output by the format accumulator 120 and the previous count held by the latch 130. This causes write-enables to be generated to control writing of the second code word into the bits 10 to 23 of the buffer 160. Bits 15 and 23 of the buffer 160 are MSBs of two respective 8-bit latches, so the existing contents of those latches are transferred as fixed length 8-bit words to the FIFO store 170.

The third received code word has a length of 4 bits, taking the count held by the format accumulator 120 to 28 bits. The length of the fourth code word (12 bits) is added to 28 bits in modulo-23 arithmetic. This means that the count supplied directly to the enable generator 135 is 8, and the count supplied from the latch 130 is 28. Accordingly the bits of the fourth code word are barrel-rotated by 28 bits and are written to bits 28 to 31 and 0 to 7 of the buffer 160. The buffer 160 thus continues to be written to and read from in a circular fashion.

Figure 6 is a schematic block diagram of the data output side of the block formatter 10. A read controller 200, which receives information from the header FIFO 180, controls the reading of data from the FIFO store 170, the operation of 3 multiplexers 210, 220 and 230 and the operation of a delay FIFO 240.

For each formatted data block, the read controller receives from the header FIFO 180 an indication of the number of bytes of luminance data to be included in that data block. Since the bytes of luminance data were stored in the FIFO store in a cyclic fashion, they are read out under the control of the read controller 200 in an identical cyclic order. The bytes of luminance data read from the FIFO store are combined into a single 8-bit wide data stream by the multiplexer 210. In the data read from the FIFO store, the MSB of each Huffman code word is abutted against the LSB of the preceding code word. This means that the first byte to be read from the FIFO store must have the first bit of the first Huffman code word as its MSB.

5

10

15

20

25

A corresponding chrominance read controller (not shown) determines the number of chrominance data bytes to be included in the chrominance data section 100 of the data block by subtracting the number of bytes of luminance data from the total number of data bytes in the data block (i.e. 120 bytes). The chrominance read controller controls the reading of the appropriate number of bytes of chrominance data from the chrominance FIFO store into the delay FIFO 240, in which they are held during reading of the luminance data bytes from the FIFO The luminance and chrominance data bytes are then store 170. concatenated together by the multiplexer 220, and finally the header data is concatenated with these data by the multiplexer 230. output of the multiplexer 230 comprises successive formatted data blocks, each data block having the order of a header section 85. a luminance data section 95, and a chrominance data section 100. remaining space in the formatted data blocks is padded with logical ones.

As mentioned above, after the Huffman codes have been formatted into data blocks by the block formatter 10, the formatted data blocks are subjected to error correction processing and channel encoding before being recorded on a magnetic tape (not shown).

### **CLAIMS**

1. Data formatting apparatus for formatting variable bit length data words into successive fixed bit length data words, the apparatus comprising:

5

10

15

20

35

an N-bit circular buffer comprising a plurality of concatenated buffer sections, each buffer section having the same bit length as one of the fixed bit length data words;

a modulo-N counter for generating a count signal in response to the cumulative length of received variable bit length data words;

means for storing a current variable bit length data word in the N-bit circular buffer at a bit position dependent on the count signal;

means associated with each buffer section for detecting whether data has been stored in all of the bits of that buffer section; and

means responsive to a detection that data has been stored in all of the bits of a buffer section for outputting the stored data from that buffer section as a fixed bit length data word.

- 2. Apparatus according to claim 1, in which the means for storing comprises an N-bit barrel-rotator operable to barrel-rotate each variable bit length data word by a number of bits dependent upon the count signal generated by the modulo-N counter in respect of the preceding variable bit length data word.

- 3. Apparatus according to claim 2, in which the means for storing comprises an enable generator, responsive to the count signals generated by the modulo-N counter in respect of the current and the preceding variable bit length data words, for generating respective write-enable signals to control writing of each bit of the current variable bit length data word from the barrel-rotator to the N-bit buffer.

- 4. Apparatus according to claim 3, in which the detecting means associated with each buffer section is operable to detect the generation of a write-enable signal to control writing to a predetermined bit in that buffer section.

5. Apparatus according to any one of the preceding claims, in which variable bit length luminance and chrominance data words from a representation of an image are formatted into respective fixed bit length luminance and chrominance data words, the apparatus comprising:

5

10

15

a luminance data store for storing the fixed bit length luminance data words;

a chrominance data store for storing the fixed bit length chrominance data words; and

means for multiplexing fixed bit length luminance data words read from the luminance data store and fixed bit length chrominance data words read from the chrominance data store, to generate data blocks comprising a predetermined total number of fixed bit length data words.

6. Apparatus according to claim 5, in which each data block comprises:

a luminance data section, comprising a plurality of fixed bit length luminance data words, concatenated with a chrominance data section, comprising a plurality of fixed bit length chrominance data words; and

20

a block header indicative of the position in the data block of the boundary between the luminance data section and the chrominance data section.

25

7. Apparatus according to claim 6, in which the luminance data section and the chrominance data section in each data block comprise luminance and chrominance data from the same portion of the representation.

Apparatus according to claim 7, comprising:

30

means for receiving variable bit length luminance data words and variable bit length chrominance data words from corresponding positions in the representation;

35

a total counter for generating a total data count in response to the cumulative number of fixed bit length luminance data words generated from the received variable bit length luminance data words and fixed bit length chrominance data words generated from the received variable bit length chrominance data words; a boundary counter for generating a boundary count in response to the cumulative number of fixed bit length luminance data words generated from the received variable bit length luminance data words;

means for determining when the total data count reaches the predetermined total number; and

means responsive to a determination that the total data count has reached the predetermined total number for generating the block header in response to the boundary count, for resetting the total counter, and for resetting the boundary counter.

10

5

- 9. Apparatus according to any one of claims 5 to 8, in which the representation comprises frequency-separated image data representing the image in the two-dimensional spatial frequency domain.

- 15 10. Apparatus according to any one of claims 5 to 9, in which each data store comprises a first-in-first-out (FIFO) buffer.

- 11. Apparatus according to any one of the preceding claims, in which the variable bit length data words comprise Huffman code words.

20

- 12. Apparatus according to any one of the preceding claims, in which N = 32 and in which the N-bit circular buffer comprises four 8-bit buffer sections.

- 25 13. A method of formatting variable bit length data words into successive fixed bit length data words, the method comprising the steps of:

generating a modulo-N count signal in response to the cumulative length of received variable bit length data words;

30

storing a received variable bit length data word in an N-bit circular buffer at a bit position dependent on the count signal, the N-bit circular buffer comprising a plurality of concatenated buffer sections, each buffer section having the same bit length as one of the fixed bit length data words;

35

detecting, for each buffer section, whether data has been stored in all of the bits of that buffer section; and

outputting the stored data from a buffer section as a fixed bit

length data word in response to a detection that data has been stored in all of the bits of that buffer section.

14. Data formatting apparatus substantially as hereinbefore described with reference to the accompanying drawings.

5

15. A method of data formatting, the method being substantially as hereinbefore described with reference to the accompanying drawings.

# Examiner's report to the Comptroller under Section 17 (The Search Report)

,

GB 9219054.5

Relevant Technical fields

(i) UK C! (Edition K ) H4F-FRD, FRR, FRW, FRX, H4P-PDCFD

D H JONES

Search Examiner

(ii) Int CI (Edition

$^{5}$  )  $^{\text{H04N}}_{46\text{ G06F}} - \frac{7}{137} + \frac{103M}{100} - \frac{7}{40}$ , 42,

Date of Search

Databases (see over)

(i) UK Patent Office

26 NOVEMBER 1992

(ii) ONLINE DATABASES: WPI

**Documents considered relevant following a search in respect of claims** 1-13

| Category<br>(see over) | Identity of documen | Relevant to claim(s)                                                |                            |

|------------------------|---------------------|---------------------------------------------------------------------|----------------------------|

|                        | GB 2138184 A        | (CANON) See line 129 page 1 to line 7 page 2 and lines 53-81 page 2 | 1, 13 at<br>least          |

| х                      | EP 0384782 A1       | (GENERAL ELECTRIC) See<br>line 6 column 2 to line 14<br>column 4    | 1, 2, 11<br>13 at<br>least |

| Х                      | WO 89/07372 A1      | (GENERAL ELECTRIC) See<br>Figure 2 and lines 12-38<br>page 2        | 1, 13 at<br>least          |

| x                      | US 4376933 A        | (XEROX) See Figures la-lg<br>and lines 10-45 column 4               | 1, 13 at<br>least          |

|                        |                     |                                                                     |                            |

|                        |                     |                                                                     |                            |

|                        |                     |                                                                     |                            |

- Y: Document indicating lack of inventive step if combined with one or more other documents of the same category.

- A: Document indicating technological background and/or state of the art.

- E: Patent document published on or after, but with priority date earlier than, the filing date of the present application.

- & Member of the same patent family, corresponding document.

Databases: The UK Patent Office database comprises classified collections of GB, EP, WO and US patent specifications as outlined periodically in the Official Journal (Patents). The on-line databases considered for search are also listed periodically in the Official Journal (Patents).