【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成18年4月20日(2006.4.20)

【公表番号】特表2002-506250(P2002-506250A)

【公表日】平成14年2月26日(2002.2.26)

【出願番号】特願2000-534945(P2000-534945)

【国際特許分類】

**G 06 F 13/12 (2006.01)**

【F I】

G 06 F 13/12 330 F

【手続補正書】

【提出日】平成18年2月17日(2006.2.17)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】 第1および第2のバス・インターフェースと、

前記第1のバス・インターフェースを介して開始されたトランザクションの一部として前記第1および第2のバス・インターフェースの間で転送されるべき複数のブロックとしてデータを格納するバッファと、

書き込み要求が受け入れられて前記データを前記第1のバス・インターフェースから前記バッファに転送する前に、前記バッファにおいて利用可能な一つ又はそれ以上のデータブロックに等しい調節可能な空間量を指定する複数のビットを有する制御レジスタとを備える装置。

【請求項2】 ブリッジであって、

イニシエータからの第1の読み出し要求に応答してターゲットから前記ブリッジにより読み出された複数のデータブロックを格納するバッファであって、前記ブリッジがさらに、後続の読み出し要求を行った後に前記イニシエータが前記バッファ内の前記データブロックの全て未満を受け入れることに応答して前記バッファからの前記データブロックの一部を廃棄するように構成されるようなバッファと、

前記第1の読み出し要求に応答して前記ターゲットから前記ブリッジにより読み出せる調整可能な最大数のデータブロックを指示する制御レジスタとを備えるブリッジ。

【請求項3】 開始バスを、データバッファを通じてターゲットバスに結合するブリッジにおいて、

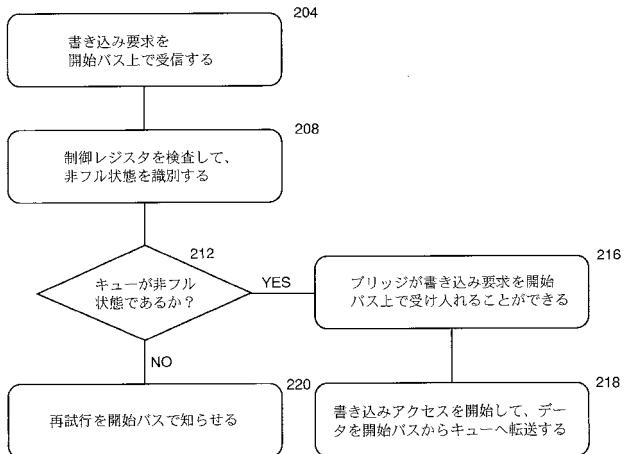

書き込み要求を前記開始バス上で受信するステップと、

前記書き込み要求が受け入れられる前に、前記バッファにおいて利用可能でなければならない一つ又はそれ以上のデータブロックに等しい調整可能な最小の空間量になっている前記バッファの非フル状態を判定するために制御レジスタの内容を点検するステップと、

前記バッファが前記最小の空間量を持たない場合に、前記開始バス上に再試行の信号を送り、前記バッファが前記最小の空間量を持つ場合に、書き込みアクセスを開始して前記開始バスから前記バッファにデータを転送するステップとを含む方法。

【請求項4】 開始バスを、データバッファを通じてターゲットバスに結合するブリッジにおいて、

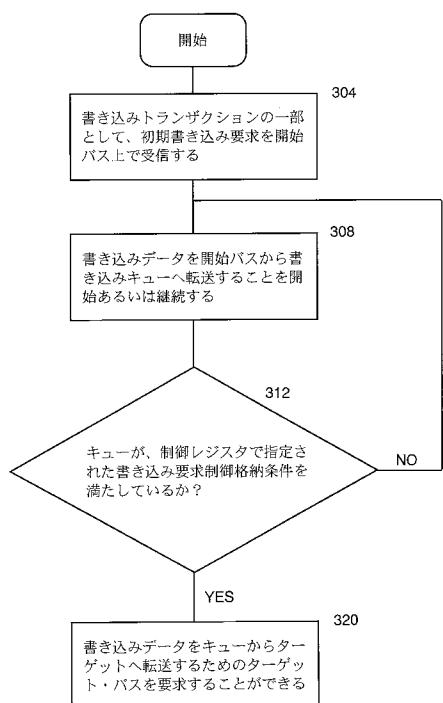

ロックの何れかが前記バッファから前記ターゲットバス転送可能となる前に前記バッ

ファに格納されるべき調整可能な最小数のデータブロックを指定するように制御レジスタへの書き込み要求制御条件をプログラムするステップと、

書き込み要求を前記開始バス上で受信するステップと、

前記制御レジスタを点検することにより前記バッファの前記書き込み要求制御条件を判定するステップと、

前記キューが前記書き込み要求制御条件を満たすまで前記開始バスから前記バッファにデータブロックを転送するステップと、

前記バッファから前記ターゲットバスに前記データブロックを転送するように前記ターゲットバスに要求するステップと

を含む方法。

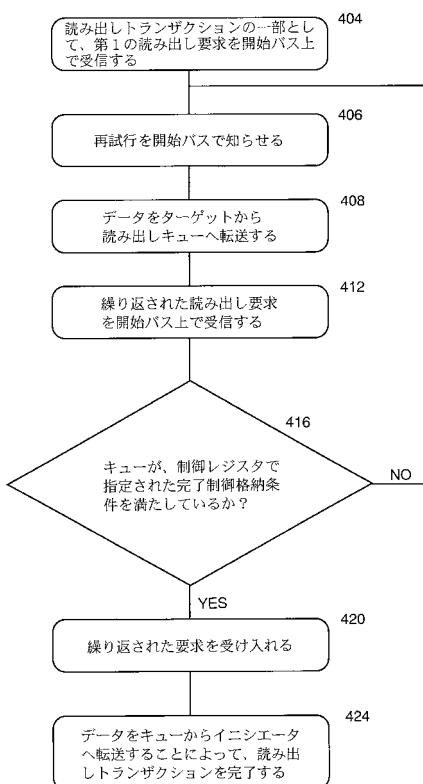

【請求項 5】 開始バス上のイニシエータを、データバッファを通じてターゲットバス上のターゲットに結合するブリッジにおいて、

複数のデータブロックに対して読み出しトランザクションの要求を前記開始バス上で受信するステップと、

前記ターゲットバス上での前記読み出しトランザクションを完了する前に、前記複数のデータブロックに対する後続の読み出し要求を前記開始バス上で受信するステップと、

最小数のデータブロックが調整されるようにする制御レジスタを点検することにより前記バッファに受け入れられねばならない最小数のデータブロックを判定するステップと、

前記バッファが前記制御レジスタにより指示された最小数のデータブロックを含む場合にのみ前記バッファから前記イニシエータに前記読み出しデータを転送することにより前記後続の読み出し要求を満たすステップと

を含む方法。

【請求項 6】 第1および第2のバス・インターフェースと、

前記第1および第2のバスの間を結合するブリッジであって、バッファと制御レジスタを有し、前記バッファは前記第2のバスがビジーの場合に前記データを前記バッファから前記第2のバスに移動できず、前記第1のバス上で開始された書き込みトランザクションの一部として前記第1のバスから前記第2のバスに転送されるべきデータを格納し、前記制御レジスタは前記ブリッジが前記バッファから前記データを移動するように前記第2のバスの制御を要求する前に前記バッファに格納される調節可能な最小数のデータブロックを指示することを特徴とするブリッジと

を備える装置。

【請求項 7】 第1および第2のバス・インターフェースと、

前記第1のバス・インターフェースを介して開始された読み出しトランザクションの一部として前記第2のバス・インターフェースから前記第1のバス・インターフェースに転送される複数のデータブロックを格納するバッファと、

前記第1のバス・インターフェースを介して開始された初期読み出し要求に続く後続の読み出し要求に応答して前記データブロックの何れかが前記バッファから前記第1のバスに移動される前に前記第2のバス・インターフェースから前記バッファに受け入れられねばならない最小数のブロックを指示する制御レジスタと

を備える装置。

【手続補正2】

【補正対象書類名】図面

【補正対象項目名】全図

【補正方法】変更

【補正の内容】

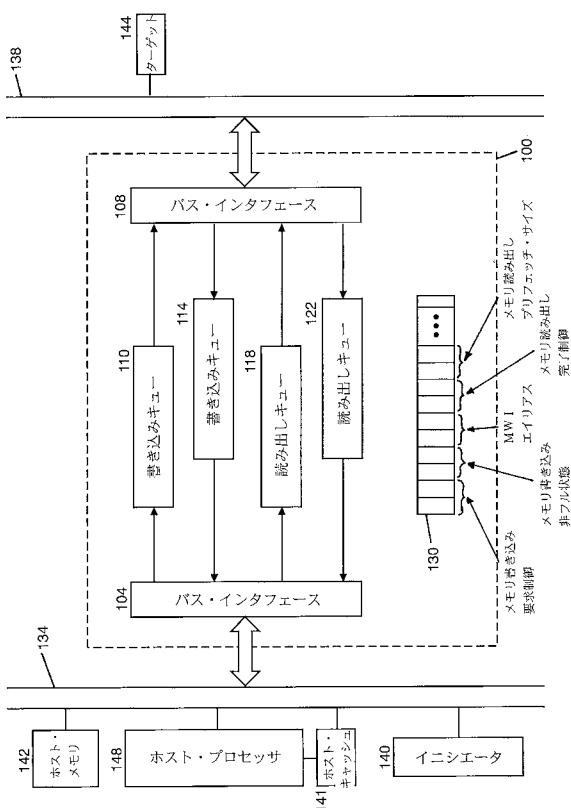

【図1】

【図2】

【図3】

【図4】

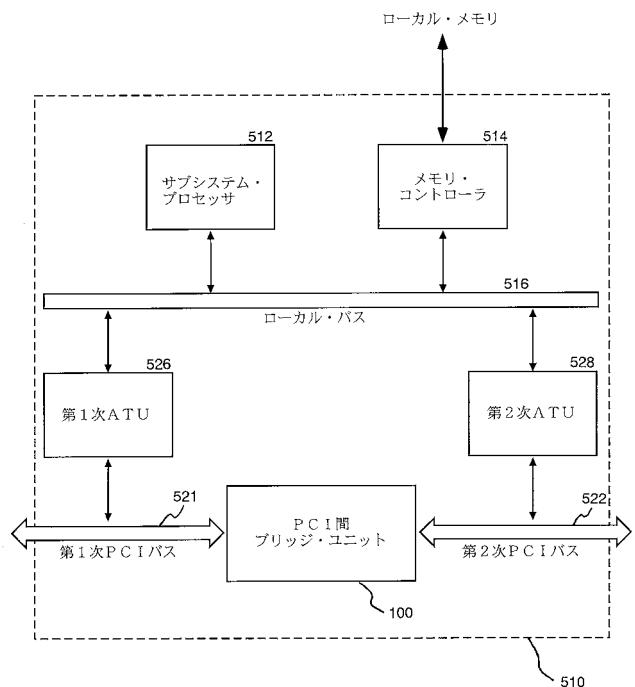

【図5】