(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7169171号**

**(P7169171)**

(45)発行日 令和4年11月10日(2022.11.10)

(24)登録日 令和4年11月1日(2022.11.1)

(51)国際特許分類

|         |                |     |         |      |         |

|---------|----------------|-----|---------|------|---------|

| G 0 1 C | 3/06 (2006.01) | F I | G 0 1 C | 3/06 | 1 2 0 Q |

| H 0 3 K | 5/26 (2006.01) |     | H 0 3 K | 5/26 | G       |

| H 0 3 M | 1/12 (2006.01) |     | H 0 3 M | 1/12 | C       |

| H 0 3 M | 1/60 (2006.01) |     | H 0 3 M | 1/60 |         |

請求項の数 12 (全17頁)

(21)出願番号 特願2018-216715(P2018-216715)

(22)出願日 平成30年11月19日(2018.11.19)

(65)公開番号 特開2020-85537(P2020-85537A)

(43)公開日 令和2年6月4日(2020.6.4)

審査請求日 令和3年8月4日(2021.8.4)

(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73)特許権者 317011920

東芝デバイス＆ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74)代理人 100091982

弁理士 永井 浩之

(74)代理人 100091487

弁理士 中村 行孝

(74)代理人 100082991

佐藤 泰和

(74)代理人 100105153

弁理士 朝倉 悟

(74)代理人 100107582

最終頁に続く

(54)【発明の名称】 半導体装置及び距離計測装置

**(57)【特許請求の範囲】****【請求項1】**

第1入力信号に応じて周波数が変調された発振信号を出力する発振器と、

前記発振信号の周期数を計測する周期数計測器と、

クロック信号の第1クロック周期に、前記周期数計測器で計測された第1周期数に基づいて、前記第1入力信号をデジタル変換した第1デジタル信号を出力する第1演算器と、

前記クロック信号の基準時点から第2入力信号が遷移するタイミングまでの期間に、前記周期数計測器で計測された第2周期数に基づいて、第2デジタル信号を出力する第2演算器と、を備える、半導体装置。

**【請求項2】**

前記第1入力信号の物理量を基準値と比較することにより、前記第2入力信号を生成する比較器を備える、請求項1に記載の半導体装置。

**【請求項3】**

前記第1デジタル信号及び前記第2デジタル信号に基づいて、光信号を出射してから前記光信号が物体で反射された反射光信号が受光されるまでの時間を計測し、前記時間に基づいて前記物体までの距離を算出する算出器を備える、請求項1又は2に記載の半導体装置。

**【請求項4】**

第1入力信号に応じて周波数が変調された発振信号を出力する発振器と、

クロック信号のクロック周期に前記発振信号の位相をサンプリングした第1位相デジタ

ル信号を出力する第1位相サンプラと、

第2入力信号が遷移したタイミングで前記発振信号の位相をサンプリングした第2位相デジタル信号を出力する第2位相サンプラと、

前記第2入力信号が遷移したタイミングで前記クロック信号の位相をサンプリングした第3位相デジタル信号を出力する第3位相サンプラと、

前記第1位相デジタル信号に基づいて、前記第1入力信号をデジタル変換した第1デジタル信号を生成する第1演算器と、

前記第1、第2及び第3位相デジタル信号に基づいて、前記第2入力信号が遷移するタイミングまでの期間に応じた第2デジタル信号を生成する第2演算器と、を備える、半導体装置。

10

#### 【請求項5】

前記第1演算器は、前記第1位相デジタル信号を時間微分することにより、前記第1デジタル信号を生成し、

前記第2演算器は、前記第2位相デジタル信号に近接した2以上の前記第1位相デジタル信号を内挿する処理と前記第3位相デジタル信号とに基づいて、前記第2デジタル信号を生成する、請求項4に記載の半導体装置。

#### 【請求項6】

前記第2演算器は、前記2以上の前記第1位相デジタル信号の多項式補間により前記第2位相デジタル信号に対応する小数時間を求めるとともに、前記第3位相デジタル信号に基づいて整数時間を求め、前記小数時間及び前記整数時間に基づいて前記第2デジタル信号を生成する、請求項5に記載の半導体装置。

20

#### 【請求項7】

前記第2入力信号を遅延させる遅延器を備え、

前記第2位相サンプラは、前記遅延器で遅延された第2入力信号が遷移したタイミングで前記第2位相デジタル信号を出力し、

前記第3位相サンプラは、前記遅延された第2入力信号が遷移したタイミングで前記第3位相デジタル信号を出力する、請求項4乃至6のいずれか一項に記載の半導体装置。

#### 【請求項8】

前記第1入力信号を遅延させる遅延器を備え、

前記発振器は、前記遅延器で遅延された第1入力信号の信号レベルに応じて周波数が変調された前記発振信号を出力する、請求項4乃至6のいずれか一項に記載の半導体装置。

30

#### 【請求項9】

前記第1入力信号の物理量を基準値と比較することにより、前記第2入力信号を生成する比較部を備える、請求項4乃至8のいずれか一項に記載の半導体装置。

#### 【請求項10】

前記物理量は、前記第1入力信号の電力、包絡線形状、周波数、積分値、又はパルス幅である、請求項9に記載の半導体装置。

#### 【請求項11】

前記第1位相デジタル信号を位相アナログ信号に変換するDA変換器と、

前記第1入力信号と前記位相アナログ信号との差信号を積分した信号を前記第1入力信号の代わりに前記発振器に入力するループフィルタと、を備える請求項4乃至10のいずれか一項に記載の半導体装置。

40

#### 【請求項12】

開始信号のタイミングに合わせて第1光信号を射出する光源と、

前記第1光信号が物体で反射された反射光信号を含む第2光信号を受光して、電気信号である前記第1入力信号に変換する光検出器と、

請求項1乃至11のいずれか一項に記載の半導体装置を有し、前記第1入力信号に基づいて、前記反射光信号の受光タイミングを表す前記第1デジタル信号及び前記第2デジタル信号を出力するフロントエンド部と、

前記第1デジタル信号及び前記第2デジタル信号に基づいて、前記開始信号のタイミン

50

グから前記第2入力信号が入力されるまでの時間を計測し、計測された時間に基づいて、前記物体までの距離を計測する距離演算部と、を備える、距離計測装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、半導体装置及び距離計測装置に関する。

**【背景技術】**

**【0002】**

自動運転技術に関する研究及び開発が進められている。自動運転技術では、乗物とその周囲の物体までの距離を精度よく計測する必要がある。距離計測は、乗物から光信号を放射してから、物体で反射された反射光信号が受光されるまでの時間を計測することにより行われる。上記の時間は、A/D変換器（以下、ADC）で大まかに計測し、時間デジタル変換器（以下、TDC）で高精度に計測するのが一般的である。

10

**【0003】**

従来、距離計測装置用のADCとTDCは、機能がそれぞれ異なることから、別々の回路で構成されており、これら回路を同一のチップ内に実装する際に、実装面積が大きくなり、消費電力も増える要因になっていた。

20

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【文献】特開平1-170221号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

本実施形態は、回路規模を縮小でき、かつ消費電力も削減できる半導体装置及び距離計測装置を提供するものである。

30

**【課題を解決するための手段】**

**【0006】**

本実施形態によれば、第1入力信号に応じて周波数が変調された発振信号を出力する発振器と、前記発振信号の周期数を計測する周期数計測器と、クロック信号の第1クロック周期に、前記周期数計測器で計測された第1周期数に基づいて、前記第1入力信号をデジタル変換した第1デジタル信号を出力する第1演算器と、前記クロック信号の基準時点から第2入力信号が遷移するタイミングまでの期間に、前記周期数計測器で計測された第2周期数に基づいて、第2デジタル信号を出力する第2演算器と、を備える、半導体装置が提供される。

40

**【図面の簡単な説明】**

**【0007】**

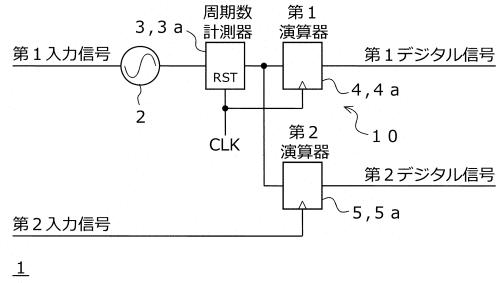

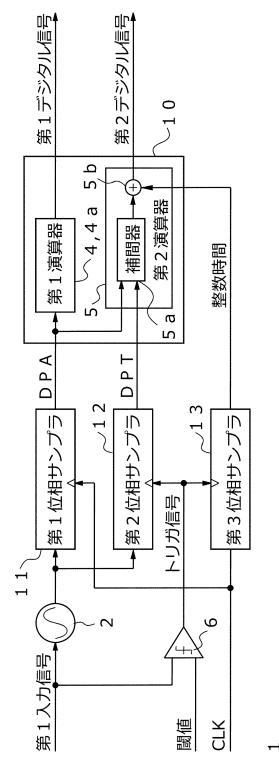

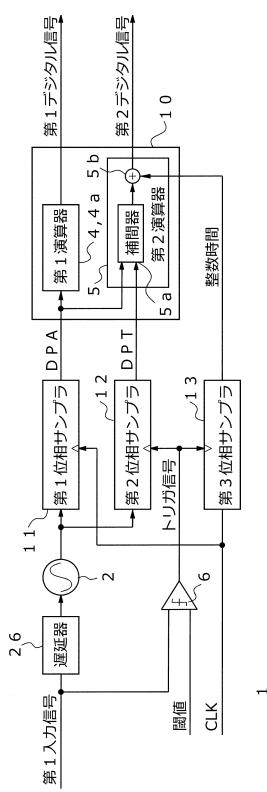

**【図1】第1の実施形態による半導体装置の概略構成を示すブロック図。**

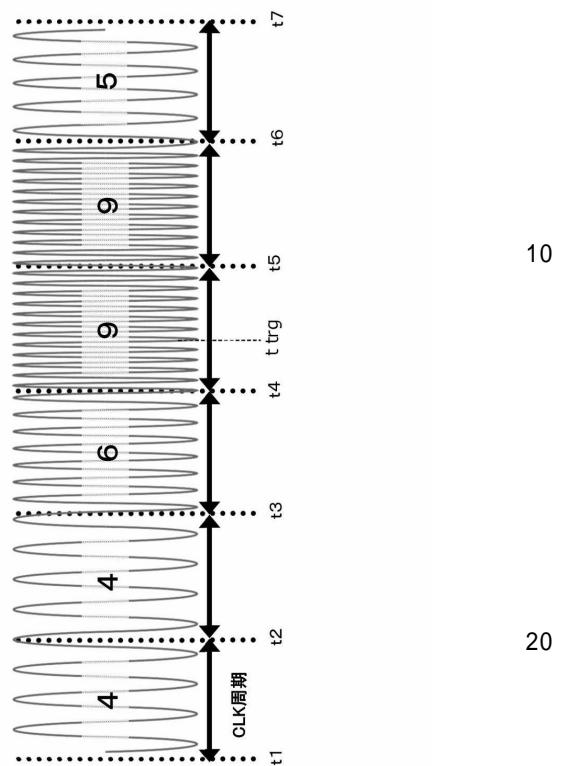

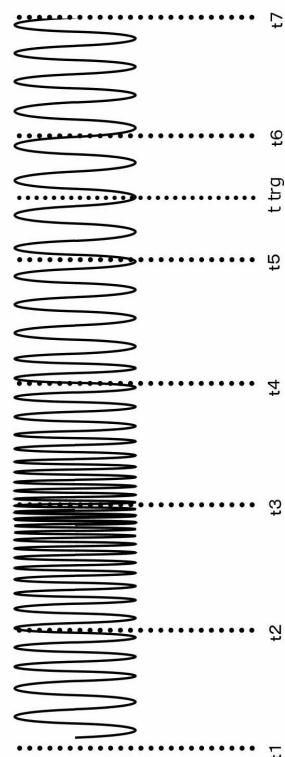

**【図2】図1の半導体装置の動作を説明する波形図。**

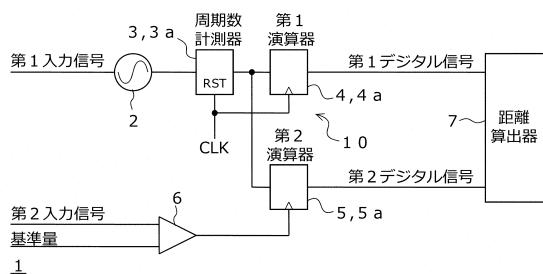

**【図3】図1の半導体装置に比較器と算出器を設けた半導体装置の概略構成を示すブロック図。**

40

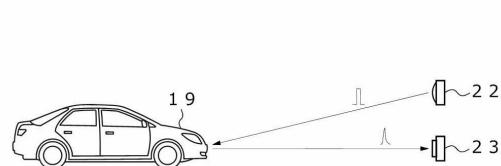

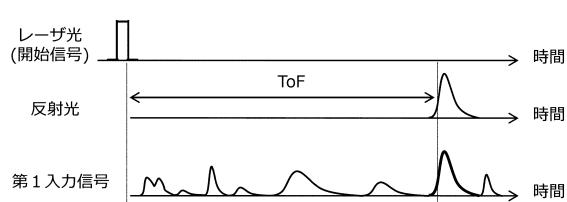

**【図4】開始信号と第1入力信号との関係を説明する図。**

**【図5】光源から出射される光信号と反射光信号の一例を示す波形図。**

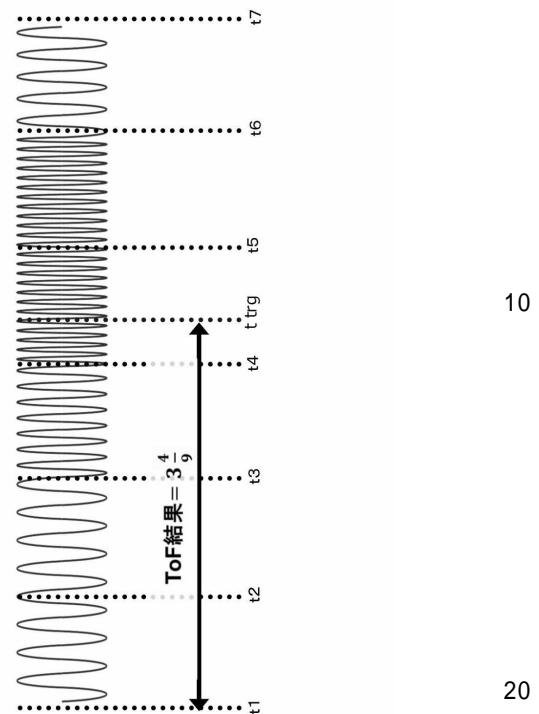

**【図6】図2の時刻  $t_{trg}$  のときに第2入力信号が遷移した場合の距離に対応する時間の計測方法を説明する図。**

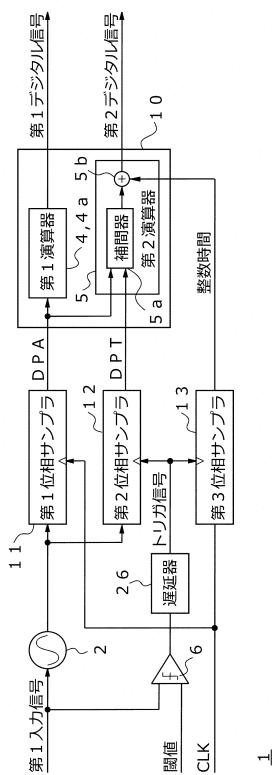

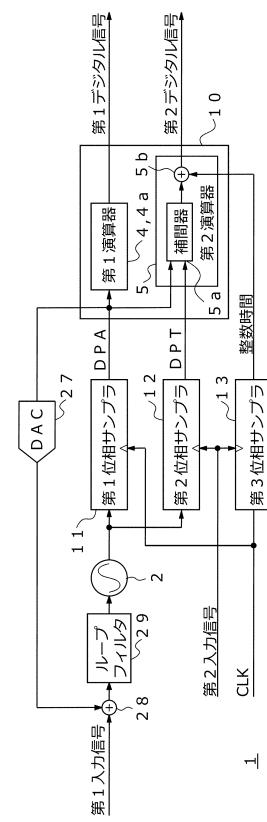

**【図7】第2の実施形態による半導体装置の概略構成を示すブロック図。**

**【図8】VCOの一例を示す回路図。**

**【図9】第1位相サンプラーの内部構成を示すブロック図。**

**【図10】第2の実施形態による半導体装置の入出力タイミングを示す信号波形図。**

**【図11】補間部の動作を説明する図。**

50

【図12】第3の実施形態による半導体装置を内蔵する距離計測装置20の概略構成を示すブロック図。

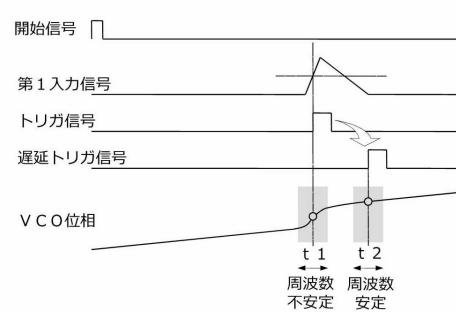

【図13】第4の実施形態による半導体装置の概略構成を示すブロック図。

【図14】クロック周期内に発振周波数が変化する例を示す波形図。

【図15】第5の実施形態による半導体装置の概略構成を示すブロック図。

【図16】第5の実施形態による半導体装置の入出力タイミングを示す信号波形図。

【図17】図15の一変形例による半導体装置の概略構成を示すブロック図。

【図18】第6の実施形態による半導体装置の概略構成を示すブロック図。

【発明を実施するための形態】

【0008】

以下、図面を参照して本発明の実施形態を説明する。以下の実施形態では、半導体装置及び距離計測装置内の特徴的な構成および動作を主に説明するが、半導体装置及び距離計測装置には以下の説明で省略した構成および動作が存在しうる。

【0009】

(第1の実施形態)

図1は第1の実施形態による半導体装置1の概略構成を示すブロック図である。図1の半導体装置1は、同一の半導体基板上に実装される回路構成を示している。図1の半導体装置1は、発振器2と、周期数計測器3と、第1演算器4と、第2演算器5とを備えている。本明細書では、第1演算器4と第2演算器5を総称して演算器10と呼ぶ。

【0010】

発振器2は、第1入力信号に応じて周波数が変調された発振信号を出力する。発振器2は、例えば電圧制御型発振器2(以下、VCO: Voltage Controlled Oscillator)である。VCO2は、第1入力信号の信号レベルに応じて周波数が変調された発振信号を出力する。

【0011】

周期数計測器3は、発振信号の周期数を計測する。より具体的には、周期数計測器3は、クロック信号CLKのクロック周期ごとに、クロック周期に含まれる発振信号の周期数を計測する。クロック信号CLKは、VCO2の発振信号とは非同期の信号である。VCO2の発振信号の周期は変動するが、クロック信号CLKの各クロック周期は同一である。

【0012】

第1演算器4は、クロック信号CLKの第1クロック周期に、周期数計測器3で計測された第1周期数に基づいて第1入力信号をデジタル変換した第1デジタル信号を出力する。第1デジタル信号は、各クロック周期ごとに、VCO2の発振周波数をデジタル変換した信号である。VCO2の発振周波数は第1入力信号の信号レベルに依存するため、第1デジタル信号は第1入力信号をデジタル変換した信号になる。

【0013】

周期数計測器3は、例えばカウンタ3aを有する。カウンタ3aは、各クロック周期ごとに、各クロック周期に含まれる発振信号の周期数をカウントする。カウンタ3aは、クロック信号CLKが遷移するタイミングでカウント値をリセットする。クロック信号CLKが遷移するタイミングとは、例えば、クロック信号CLKがローからハイになるタイミングである。

【0014】

第1演算器4は、例えばフリップフロップ(以下、FF)4aを有する。FF4aは、クロック信号CLKが遷移するタイミングで、カウンタ3aのカウント値を保持する。FF4aの保持信号が第1デジタル信号になる。このように、周期数計測器3と第1演算器4は、ADC変換器(以下、ADC: Analog Digital Converter)として機能する。

【0015】

第2演算器5は、クロック信号の基準時点から第2入力信号が遷移するタイミングまでの期間に周期数計測器3で計測された第2周期数に基づいて第2デジタル信号を出力する。第2演算器5は、例えばFF5aを有する。FF5aは、第2入力信号が遷移するタイ

10

20

30

40

50

ミングで、カウンタ 3 a のカウント値を保持する。FF 5 a の保持信号が第 2 デジタル信号になる。このように、周期数計測器 3 と第 2 演算器 5 は、時間デジタル変換器（以下、TDC : Time to Digital Converter）として機能する。

#### 【0016】

以上に説明したように、図 1 の半導体装置 1 は、発振器 2、ADC 及び TDC を統合させた回路構成を備えている。特に、ADC と TDC で発振器 2 とカウンタ 3 a を共有するため、ADC と TDC が個別に発振器 2 とカウンタ 3 a を備える必要がなくなり、回路規模と消費電力を削減できる。

#### 【0017】

図 2 は図 1 の半導体装置 1 の動作を説明する波形図であり、VCO 2 の発振信号の波形を示している。VCO 2 の発振信号の発振周波数は、第 1 入力信号の信号レベルに応じて変化する。図 2 の破線で区切られた各区間は、クロック信号 CLK の各クロック周期である。図 2 では、簡略化のため、VCO 2 の発振信号の発振周波数が各クロック周期ごとに変化する例を示しているが、実際には、1 つのクロック周期内でも、VCO 2 の発振信号の発振周波数が変化することがある。

10

#### 【0018】

図 2 の例では、時刻  $t_1 \sim t_2$ 、 $t_2 \sim t_3$ 、 $t_3 \sim t_4$ 、 $t_4 \sim t_5$ 、 $t_5 \sim t_6$ 、 $t_6 \sim t_7$  の各クロック周期では、カウンタ 3 a は、カウント値 = 4、4、6、9、9、5 をそれぞれカウントする。これらのカウント値はそれぞれ、時刻  $t_2$ 、 $t_3$ 、 $t_4$ 、 $t_5$ 、 $t_6$ 、 $t_7$  のときに FF 4 a に保持される。よって、第 1 デジタル信号は、クロック周期ごとに、4、4、6、9、9、5 の順に変化する。

20

#### 【0019】

仮に、時刻  $t_4$  と  $t_5$  の間の  $t_{trg}$  のときに第 2 入力信号が遷移したとすると、FF 4 a は、時刻  $t_{trg}$  にカウンタ 3 a のカウント値を保持する。この場合のカウント値は 4 であることから、第 2 デジタル信号は 4 になる。

#### 【0020】

図 3 は図 1 の半導体装置 1 に比較器 6 と算出器 7 を設けた半導体装置 1 の概略構成を示すブロック図である。

#### 【0021】

比較器 6 は、第 1 入力信号の物理量を基準値と比較することにより、第 2 入力信号を生成する。物理量とは、第 1 入力信号の電力、包絡線、周波数、積分値、又はパルス幅などであり、第 1 入力信号の特性を定量的に評価できる物理量であればよく、その具体的な内容は問わない。比較器 6 は、例えば、物理量が基準量を超えた場合に、第 2 入力信号を遷移させる。物理量が信号レベルの場合、比較器 6 は、第 1 入力信号の信号レベルが所定の閾値を超えた場合に第 2 入力信号を遷移させる。第 2 入力信号を遷移させるとは、例えば第 2 入力信号をローからハイに変化させることである。このように、第 2 入力信号はトリガ信号として機能し、比較器 6 はトリガ生成部として機能する。

30

#### 【0022】

算出器 7 は、第 1 デジタル信号及び第 2 デジタル信号に基づいて、光信号を射出してから光信号が物体で反射された反射光信号が受光されるまでの時間を計測し、計測された時間に基づいて物体までの距離を算出する。

40

#### 【0023】

図 4 は開始信号と第 1 入力信号との関係を説明する図である。開始信号のタイミングに応じて、光源 2 2 からレーザ光等の光信号が出射され、光信号が乗物等の物体に当たって反射された反射光信号が受光センサ等の光検出器 2 3 に入射されて、電気信号である第 1 入力信号に変換される。

#### 【0024】

図 5 は光源 2 2 から出射される光信号と反射光信号の一例を示す波形図である。反射光信号は、太陽光などの環境光とともに光検出器 2 3 に受光される。反射光信号の伝搬距離が長いほど、反射光信号の光強度は弱くなり、環境光との識別が困難になる。図 5 では、

50

反射光信号を太字で示している。

#### 【 0 0 2 5 】

比較器 6 は、例えば、第 1 入力信号の信号レベルが所定の閾値を超えた場合に、第 2 入力信号を遷移させる。算出器 7 は、開始信号のタイミングから、反射光信号が受光されて第 1 入力信号に変換されて発振器 2 に入力されるタイミングまでの時間を計測して、距離に変換する。

#### 【 0 0 2 6 】

図 6 は図 2 の時刻  $t_{trg}$  のときに第 2 入力信号が遷移した場合の距離に対応する時間 (  $T_{OF}$  : Time of Flight ) の計測方法を説明する図である。時刻  $t_1$  は、開始信号のタイミングである。時刻  $t_4 \sim t_5$  のクロック周期の間に第 1 演算器 4 から出力される第 1 デジタル信号は 9 であり、第 2 演算器 5 から出力される第 2 デジタル信号は 4 である。また、時刻  $t_1 \sim t_4$  までに 3 クロック周期あるため、算出器 7 は、開始信号のタイミングから第 2 入力信号の遷移タイミングまでの時間  $T_{OF}$  は  $3 + (4 / 9)$  と計測し、この時間  $T_{OF}$  から、光の速度を用いて距離を算出する。

10

#### 【 0 0 2 7 】

このように、第 1 の実施形態では、ADC として機能する第 1 演算器 4 と、TDC として機能する第 2 演算器 5 が、発振器 2 とカウンタ 3a を共有するため、ADC と TDC が専用の発振器 2 とカウンタ 3a を備える必要がなくなり、回路規模と消費電力を削減できる。

#### 【 0 0 2 8 】

##### ( 第 2 の実施形態 )

第 2 の実施形態は、第 1 の実施形態による半導体装置 1 の構成をより具体化したものである。

#### 【 0 0 2 9 】

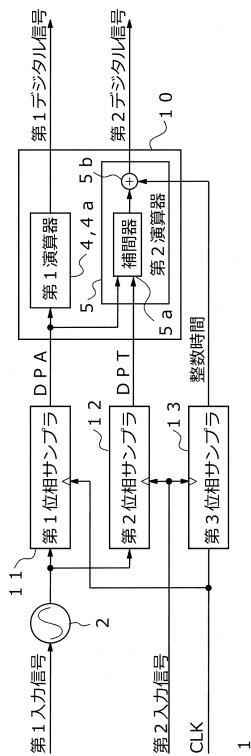

図 7 は第 2 の実施形態による半導体装置 1 の概略構成を示すブロック図である。図 7 の半導体装置 1 は、発振器 2 と、第 1 位相サンプラー 11 と、第 2 位相サンプラー 12 と、第 3 位相サンプラー 13 と、第 1 演算器 4 と、第 2 演算器 5 とを備えている。第 1 演算器 4 と第 2 演算器 5 で演算器 10 を構成している。

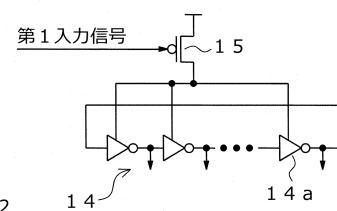

#### 【 0 0 3 0 】

発振器 2 は、第 1 入力信号に応じて周波数が変調された発振信号を出力する。発振器 2 は、例えば VCO 2 である。図 8 は VCO 2 の一例を示す回路図である。図 8 の VCO 2 は、リング発振器 14 と、PMOS トランジスタ 15 とを有する。リング発振器 14 は、遅延時間を制御可能な複数の可変遅延インバータ 14a をリング状に接続したものである。PMOS トランジスタ 15 は、第 1 入力信号の信号レベルに応じた電源電圧を複数の可変遅延インバータ 14a に供給する。各可変遅延インバータ 14a は、電源電圧レベルに応じて信号伝搬遅延時間を切り替える。各可変遅延インバータ 14a の信号伝搬遅延時間が変わると、リング発振器 14 の発振周波数も変化する。これにより、図 8 の VCO 2 は、第 1 入力信号の信号レベル、例えば電圧又は電流レベルに基づいて発振周波数を変調する。

30

#### 【 0 0 3 1 】

第 1 位相サンプラー 11 は、クロック信号 CLK の周期ごとに、VCO 2 の発振信号の位相をサンプリングした第 1 位相デジタル信号 DPA を出力する。第 2 位相サンプラー 12 は、第 2 入力信号が遷移したタイミングで、VCO 2 の発振信号の位相をサンプリングした第 2 位相デジタル信号 DPT を出力する。第 3 位相サンプラー 13 は、第 2 入力信号が遷移したタイミングでクロック信号 CLK の位相をサンプリングした第 3 位相デジタル信号を出力する。

40

#### 【 0 0 3 2 】

第 1 演算器 4 は、クロック信号 CLK のクロック周期ごとに、第 1 位相デジタル信号 DPA に基づいて第 1 入力信号をデジタル変換した第 1 デジタル信号を出力する。第 1 位相サンプラー 11 と第 1 演算器 4 は、ADC として機能する。

10

20

30

40

50

**【 0 0 3 3 】**

第2演算器5は、第2入力信号が遷移するタイミングまでの期間に応じた第2デジタル信号を出力する。第1位相サンプラ11と、第2位相サンプラ12と、第2演算器5はTDCとして動作する。

**【 0 0 3 4 】**

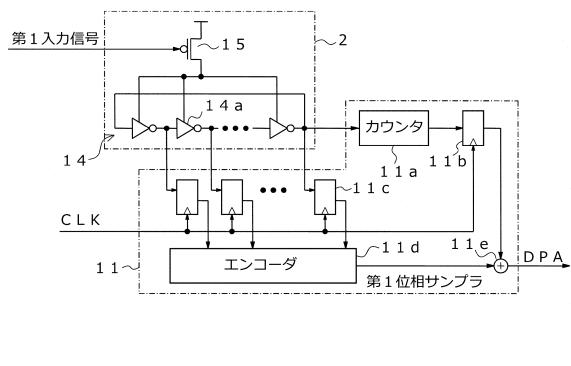

図9は第1位相サンプラ11の内部構成を示すブロック図である。図9に示すように、第1位相サンプラ11は、カウンタ11aと、FF11bと、複数のFF11cと、エンコーダ11dと、加算器11eとを有する。

**【 0 0 3 5 】**

カウンタ11aは、例えば、VCO2の発振信号の遷移タイミングでカウントアンプを行うアップカウンタ11aである。VCO2の発振信号の遷移タイミングとは、例えば発振信号がローからハイになるタイミングである。FF11bは、カウンタ11aのカウント値をクロック周期ごとに保持する。FF11bに保持された値は、VCO2の発振信号の整数位相デジタル信号に対応する。

10

**【 0 0 3 6 】**

複数のFF11cは、リンク発振器14内の複数の可変遅延インバータ14aの各出力信号を、クロック信号CLKの遷移タイミングに同期させて保持する。エンコーダ11dは、各FF11cが保持した信号を小数位相デジタル信号にエンコードして出力する。リンク発振器2内の各可変遅延インバータ14aの各出力信号をクロック信号CLKの遷移タイミングで保持することにより、VCO2の発振信号をカウンタ11aで計測した値よりも高い分解能での位相デジタル信号を取得できる。

20

**【 0 0 3 7 】**

加算器11eは、FF11bに保持された整数位相デジタル信号と、エンコーダ11dでエンコードされた小数位相デジタル信号とを加算して、第1位相デジタル信号DPAを生成する。

**【 0 0 3 8 】**

第2位相サンプラ12は、例えば図9と同様のブロック構成を有する。図9のクロック信号CLKの代わりに、第2入力信号が入力される。この場合、エンコーダ11dは、第2入力信号が遷移するタイミングで、VCO2の発振信号の小数位相デジタル信号を出力する。

30

**【 0 0 3 9 】**

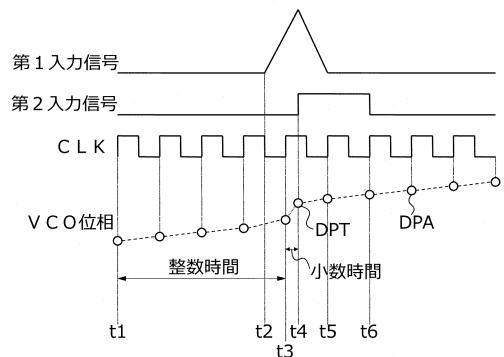

図10は第2の実施形態による半導体装置1の入出力タイミングを示す信号波形図である。時刻t1は開始信号のタイミングである。時刻t1～t2の間は、第1入力信号の信号レベルは所定の基底レベルである。なお、図10では、環境光等のノイズ信号は第1入力信号に含まれていないものとしている。第1入力信号の信号レベルが基底レベルのときは、VCO2は基底レベルに応じた固定の発振周波数で発振する。したがって、カウンタ3aのカウント値は、線形に増加する。図10の破線は、クロック信号CLKが遷移するタイミングを示しており、各破線の間隔はクロック周期である。

**【 0 0 4 0 】**

第1位相サンプラ11は、クロック信号CLKが遷移するタイミングに同期して、VCO2の発振信号の位相をデジタル化した第1位相デジタル信号DPAを出力する。

40

**【 0 0 4 1 】**

時刻t2～t5にかけて、第1入力信号の信号レベルが変化したとすると、その信号レベルに応じてVCO2の発振信号の発振周波数が変化する。図10の例では、時刻t4のときに第2入力信号が遷移した例を示している。第2位相サンプラ12は、第2入力信号が遷移したタイミングに同期させて、VCO2の発振信号の位相をデジタル化した第2位相デジタル信号DPTを出力する。第3位相サンプラ13は、第2入力信号が遷移したタイミングに同期させて、クロック信号CLKの位相をデジタル化した第3位相デジタル信号を出力する。この第3位相デジタル信号は、クロック信号CLKの整数時間を表している。

50

**【 0 0 4 2 】**

第1演算器4は、第1位相サンプラー11から出力された第1位相デジタル信号DPAを時間微分した第1デジタル信号を出力する。この第1デジタル信号は、クロック周期ごとのVCO2の発振信号の発振周波数をデジタル化した信号である。VCO2の発振信号の発振周波数は、第1入力信号に依存するため、第1デジタル信号は第1入力信号に依存する信号である。例えば、第1デジタル信号は、第1入力信号の信号レベルをデジタル化した信号になる。

**【 0 0 4 3 】**

第2演算器5は、第2位相デジタル信号DPTに近接した2以上の第1位相デジタル信号DPAを内挿する処理と第3位相デジタル信号に基づいて、第2デジタル信号を生成する。より具体的には、第2演算器5は、2以上の第1位相デジタル信号DPAを多項式補間により第2位相デジタル信号DPTに対応する小数時間を求めるとともに、第3位相デジタル信号に基づいて整数時間を求め、小数時間及び整数時間に基づいて第2デジタル信号を生成する。

10

**【 0 0 4 4 】**

第2演算器5は、例えば補間部5aと、加算器5bとを有する。補間部5aは、第1位相デジタル信号DPAと第2位相デジタル信号DPTとにに基づいて、小数時間信号を生成する。加算器5bは、第3位相サンプラー13で生成された、整数時間信号である第3位相デジタル信号と、補間部5aで生成された小数時間信号とを加算して、第2デジタル信号を生成する。第2デジタル信号は、開始信号のタイミングから、第2入力信号が遷移するタイミングまでの時間 - デジタル信号である。

20

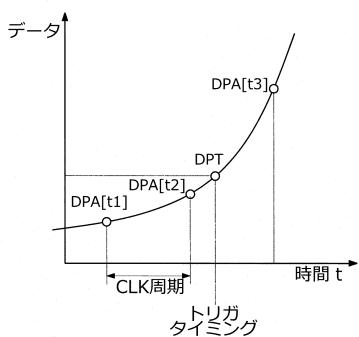

**【 0 0 4 5 】**

図11は補間部5aの動作を説明する図である。図11は、横軸を時間、縦軸を第1位相デジタル信号DPAと第2位相デジタル信号DPTのデータ値として、第1位相デジタル信号DPAをプロットした図である。第2位相デジタル信号DPTの近傍の3つの第1位相デジタル信号DPA[t1]、DPA[t2]、DPA[t3]をプロットし、これら3つのプロットを通る2次補間曲線を生成する。そして、第2位相デジタル信号DPTをこの2次補間曲線上に置いて、第2位相デジタル信号DPTの時間を求める。求めた時間が第2入力信号が遷移するタイミング、すなわちトリガタイミングである。

30

**【 0 0 4 6 】**

2次補間曲線は、例えば、以下の(1)式で表される。

$$f(t) = a t^2 + b t + c \quad \dots (1)$$

**【 0 0 4 7 】**

補間部5aは、(1)式の2次補間曲線から、以下の(2)式に基づいて小数時間を逆算する。

$$\text{小数時間} = f^{-1}(DPT) \quad \dots (2)$$

40

**【 0 0 4 8 】**

なお、補間部5aが行う補間処理は、上述した2次多項式補間以外に、ラグランジュ補間やニュートン補間など、任意の補間を行うことができる。補間部5aの補間処理は、VCO2の発振周波数が変化している間にも行うことができ、高精度の小数時間を計測できる。

**【 0 0 4 9 】**

上述したように、第2演算器5は、第2入力信号の遷移時間を基準としてクロック信号CLKの位相を検出することにより整数時間を求め、かつ第2入力信号の遷移時間を基準としてVCO2の発振信号の位相を検出することにより小数時間を求めることで、高精度の時間 - デジタル変換を行うことができる。

**【 0 0 5 0 】**

このように、第2の実施形態による半導体装置1は、ADCとして機能する第1演算器4と、TDCとして機能する第2演算器5とがVCO2と第1位相サンプラー11を共有するため、回路規模と消費電力を削減できる。

50

**【0051】**

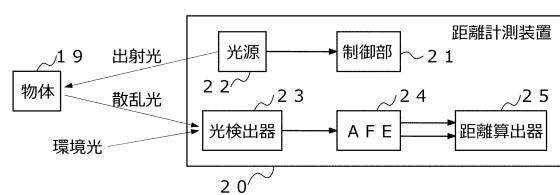

(第3の実施形態)

図12は第3の実施形態による半導体装置1を内蔵する距離計測装置20の概略構成を示すブロック図である。図12の距離計測装置20は、制御部21と、光源22と、光検出器23と、アナログフロントエンド(以下、AFE:Analog Front End)部24と、算出器25とを備えている。

**【0052】**

制御部21は、光源22の出射タイミングを制御する。制御部21が開始信号を光源22に送ると、光源22は光信号を出射する。光源22は、レーザダイオードやLED(Light Emitting Device)である。光源22から出射された光信号(以下、第1光信号)は、監視領域内の物体19によって散乱され、その散乱光が距離計測装置20に入射される。太陽光などの光源22以外の環境光も、直接光又は物体19からの反射光として、距離計測装置20に入射される。

10

**【0053】**

距離計測装置20に入射された光は、光検出器23によって電気信号に変換される。光検出器23は、例えはフォトダイオード、アバランシェ・フォトダイオード、シングルフォトン・アバランシェ・フォトダイオード等で構成することができる。光検出器23は、光源22から出射された第1光信号が物体19で反射された反射光信号を含む第2光信号を受光して、電気信号である第1入力信号に変換する。

20

**【0054】**

光検出器23で変換された電気信号である第1入力信号は、AFE部24に入力され、その電気信号の振幅情報及び時間情報がデジタル値に変換される。ここで、時間情報とは、電気信号の振幅がある閾値を超えたタイミングであり、出射光の出射タイミングから散乱光が光検出器23を介してAFE部24で検出されるまでの時間TOFを表している。AFE部24は、例えは第2の実施形態の半導体装置1で構成可能である。AFE部24は、第1入力信号に基づいて、反射光信号の受光タイミングを表す第1デジタル信号及び第2デジタル信号を出力する。

20

**【0055】**

算出器25は、第1光信号を反射した物体19までの距離を計測する。より具体的には、算出器25は、開始信号のタイミングから第2入力信号が遷移されるまでの時間を計測し、この時間に基づいて物体19までの距離を計測する。

30

**【0056】**

図12の距離計測装置20内の各部は、一つの半導体基板に実装可能であり、ワンチップ化することができる。あるいは、光源22だけを別チップにしてもよいし、光源22と光検出器23を別チップにしてもよい。

**【0057】**

このように、第3の実施形態では、第2の実施形態による半導体装置1を用いて距離計測装置20を構成することができる。

30

**【0058】**

(第4の実施形態)

図13は第4の実施形態による半導体装置1の概略構成を示すブロック図である。図13の半導体装置1は、図7の半導体装置1の構成に加えて、比較器6を備えている。比較器6は、第1入力信号に基づいて第2入力信号を生成する。より具体的には、比較器6は、第1入力信号の物理量を所定の基準量と比較することにより、第2入力信号を生成する。物理量が信号レベルの場合、比較器6は、第1入力信号の信号レベルが所定の基準レベルを超えた場合に、第2入力信号を遷移させてもよい。このように、比較器6は、トリガ信号である第2入力信号を生成するトリガ生成部として機能する。

40

**【0059】**

比較器6は、環境光の中に埋もれた反射光を適切に抽出するために、基準量や基準レベルを設定して、第1入力信号に含まれる反射光成分を検出する。反射光成分が検出される

50

と、第2入力信号を遷移させる。

#### 【0060】

図13の半導体装置1は、図12の距離計測装置20内のAFE部24に用いることができる。

#### 【0061】

このように、第4の実施形態では、比較器6を設けて、第1入力信号から第2入力信号を生成するため、距離計測装置20に入射された光から物体19の反射光を適切に抽出して、第2入力信号を生成できる。

#### 【0062】

(第5の実施形態)

VCO2の発振信号は、第1入力信号に応じて周波数変調されている。よって、図14に示すように、1つのクロック周期内でも、発振信号の発振周波数が大きく変化することがありうる。特に、第1入力信号に含まれる反射光成分に対応する信号領域は、短い時間幅で信号振幅が急激に大きくなることがある。このような場合、VCO2の発振信号の発振周波数が急激に大きくなつて、その後すぐに発振周波数が急激に小さくなり、発振周波数が不安定になる。

10

#### 【0063】

上述した第1～第3の実施形態による半導体装置1では、安定していない発振信号が入力されると、補完処理の精度が劣化する恐れがある。そこで、第5の実施形態による半導体装置1は、安定していない発振信号に対する対策を施したものである。

20

#### 【0064】

図15は第5の実施形態による半導体装置1の概略構成を示すブロック図、図16は第5の実施形態による半導体装置1の入出力タイミングを示す信号波形図である。図15の半導体装置1は、図13の半導体装置1の構成に加えて、遅延器26を備えている。遅延器26は、比較器6から出力された第2入力信号を所定時間遅延させる。所定時間とは、第1入力信号に含まれる反射光成分に対応する信号領域が終わるまでの時間である必要がある。より具体的には、所定時間は、反射光成分を含む信号領域が終わって、VCO2の発振信号の発振周波数が安定するまでの時間であるのが望ましい。

#### 【0065】

遅延器26で第2入力信号を所定時間遅延することで、本来は図16の時刻t1で第2信号が遷移する(トリガ信号が出る)のに対して、時刻t1から所定時間遅延した時刻t2で第2信号が遷移する(トリガ信号が出る)。時刻t2での発振信号がクロック周期内でそれほど周波数が変化せず安定している場合には、第1位相サンプラー11と第2位相サンプラー12は、第1位相デジタル信号DPAと第2位相デジタル信号DPTを精度よく生成することができる。

30

#### 【0066】

図17は図15の一変形例による半導体装置1の概略構成を示すブロック図である。図17の半導体装置1は、図13の半導体装置1の構成に加えて、VCO2の前段側に遅延器26を追加したものである。遅延器26は、第1入力信号を所定時間遅延させた後にVCO2に入力する。VCO2は、第1入力信号を所定時間遅延させた遅延入力信号に基づいて周波数変調された発振信号を出力する。

40

#### 【0067】

比較器6は、遅延されていない元の第1入力信号に基づいて第2入力信号を生成する。第1位相サンプラー11と第2位相サンプラー12は、遅延入力信号に基づいて周波数変調された発振信号に基づいて第1位相デジタル信号DPAと第2位相デジタル信号DPTを出力する。第1位相デジタル信号DPAと第2位相デジタル信号DPTは、第2入力信号の遷移タイミングよりも所定時間遅れている。よって、第1位相デジタル信号DPAと第2位相デジタル信号DPTは、安定化した発振信号に基づいて生成されるため、図15と同様に、発振信号が安定化した後に第1位相デジタル信号DPAと第2位相デジタル信号DPTを生成できる。

50

**【 0 0 6 8 】**

このように、第5の実施形態では、遅延器26を設けて、比較器6で生成した第2入力信号を所定時間遅延させるか、あるいはVCO2に入力される第1入力信号を所定時間遅延させるため、VCO2の発振信号の発振周波数が安定化した後に、第1位相サンプラー1と第2位相サンプラー12により、第1位相デジタル信号DPAと第2位相デジタル信号DPTを生成できる。

**【 0 0 6 9 】**

(第6の実施形態)

図18は第6の実施形態による半導体装置1の概略構成を示すブロック図である。図18の半導体装置1は、図7の半導体装置1の構成に加えて、DA変換器(DAC:Digital Analog Converter)27と、差分器28と、ループフィルタ29とを備えている。DAC27は、第1位相サンプラー11から出力された第1位相デジタル信号DPAを位相アナログ信号に変換する。差分器28は、第1入力信号とDAC27の出力信号と第1入力信号との差信号を出力する。ループフィルタ29は、この差信号を積分した信号を、第1入力信号の代わりにVCO2に入力する。ループフィルタ29は積分器として機能する。

10

**【 0 0 7 0 】**

図18の半導体装置1では、VCO2と第1位相サンプラー11とで、デルタ-シグマA/D変換器を構成している。第1位相デジタル信号DPAをDAC27とループフィルタ29にて、VCO2の入力側に帰還させるため、A/D変換時の量子化雑音をより低減できる。

20

**【 0 0 7 1 】**

なお、図18のDAC27と差分器28は、図15や図17の半導体装置1に付加してもよい。

**【 0 0 7 2 】**

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

30

**【 符号の説明 】****【 0 0 7 3 】**

1 半導体装置、2 発振器、3 周期数計測器、3a カウンタ、4 第1演算器、4a FF、5 第2演算器、5a FF、6 比較器、7 算出器、10 演算器、11 第1位相サンプラー、12 第2位相サンプラー、13 第3位相サンプラー、14 リング発振器、15 PMOSトランジスタ、19 物体、20 距離計測装置、21 制御部、22 光源、23 光検出器、24 AFE部、25 算出器、26 遅延器

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

【図 1 3】

【図 1 4】

10

20

【図 1 5】

【図 1 6】

30

40

50

【図 17】

【図 18】

10

20

30

40

50

---

フロントページの続き

弁理士 関根 毅

(74)代理人 100118876

弁理士 鈴木 順生

(74)代理人 100103263

弁理士 川崎 康

(72)発明者 近藤 智史

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 大國 英徳

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 タトアンタン

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 崔 明秀

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 山崎 和子

(56)参考文献 特開平01-208024(JP,A)

特開2017-063433(JP,A)

特開2003-139857(JP,A)

特開2000-028721(JP,A)

特開平04-015593(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G01C 3/00-3/32

G01S 7/48 - 7/51

17/00 - 17/95

H03K 5/00 - 5/02

5/08 - 5/1254

5/15 - 5/26

99/00

H03M 1/00 - 1/88