(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-21309

(P2013-21309A)

(43) 公開日 平成25年1月31日(2013.1.31)

(51) Int.Cl.

H01L 31/04 (2006.01)

F 1

H01L 31/04

A

テーマコード(参考)

5 F 1 5 1

審査請求 未請求 請求項の数 5 O L (全 14 頁)

(21) 出願番号 特願2012-134023 (P2012-134023)

(22) 出願日 平成24年6月13日 (2012.6.13)

(31) 優先権主張番号 特願2011-132101 (P2011-132101)

(32) 優先日 平成23年6月14日 (2011.6.14)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 一條 充弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

遠藤 俊弥

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 加藤 翔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】光電変換装置

## (57) 【要約】

【課題】シリコン基板の表面欠陥を低減するパッシバーション層を設けたヘテロ接合型の光電変換装置を提供する。

【解決手段】単結晶シリコン基板の一方の面に接する第1のシリコン半導体層と、該シリコン半導体層に接する第2のシリコン半導体層と、単結晶シリコン基板の他方の面に接する第3のシリコン半導体層と、該シリコン半導体層に接する第4のシリコン半導体層と、を有し、第1のシリコン半導体層及び第3のシリコン半導体層に含有されるフッ素の濃度を $1 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

一対の電極間に、

一導電型を有する単結晶シリコン基板と、

前記単結晶シリコン基板の一方の面に接する第1のシリコン半導体層と、

前記第1のシリコン半導体層に接し、前記単結晶シリコン基板とは逆の導電型を有する第2のシリコン半導体層と、

前記第2のシリコン半導体層に接する透光性導電膜と、

前記単結晶シリコン基板の他方の面に接する第3のシリコン半導体層と、

前記第3のシリコン半導体層に接し、前記単結晶シリコン基板と同じ導電型で、前記単結晶シリコン基板よりもキャリア密度の高い第4のシリコン半導体層と、

を有し、

前記第1のシリコン半導体層及び前記第3のシリコン半導体層に含有されるフッ素の濃度は、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以下であることを特徴とする光電変換装置。

**【請求項 2】**

請求項1において、前記単結晶シリコン基板の導電型はn型であることを特徴とする光電変換装置。

**【請求項 3】**

請求項1または2において、前記単結晶シリコン基板の酸素濃度は、 $8 \times 10^{17}$  atoms/cm<sup>3</sup>以下であることを特徴とする光電変換装置。

**【請求項 4】**

請求項1乃至3のいずれか一項において、前記第1のシリコン半導体層及び前記第3のシリコン半導体層に含有されるフッ素の濃度は、前記第1のシリコン半導体層及び前記第3のシリコン半導体層に含有される窒素の濃度よりも低いことを特徴とする光電変換装置。

**【請求項 5】**

請求項1乃至4のいずれか一項において、前記第1のシリコン半導体層及び前記第3のシリコン半導体層に含有されるフッ素の濃度は、前記第1のシリコン半導体層及び前記第3のシリコン半導体層に含有される酸素の濃度よりも低いことを特徴とする光電変換装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置に関する。

**【背景技術】****【0002】**

近年、二酸化炭素の排出量削減などを可能にするクリーンエネルギーとして、光電変換装置が注目されている。その代表例としては、単結晶シリコンや多結晶シリコンなどのシリコン基板を用いた太陽電池が知られており、その変換効率を高めるための研究開発が活発に行われている。

**【0003】**

シリコン基板を用いた太陽電池では、p型シリコン基板が多く用いられている。p型シリコン基板は、n型シリコン基板よりも拡散長が長く、基板内で発生した少数キャリアを効率良く収集しやすい。

**【0004】**

シリコン基板にp型の導電型を付与する不純物としては一般的にホウ素が用いられているが、シリコン基板中にホウ素と酸素が共存していると深い準位が形成され、該準位にキャリアが捕獲されやすくなる。このため、ライフタイムが低下してしまう。この現象は、光劣化ともいわれ、太陽電池の変換効率を低下させる一要因となっている。

**【0005】**

上記現象の対策として、p型の導電型を付与する不純物がガリウムであり、かつ低酸素濃度のシリコン基板を用いた技術が特許文献1に開示されている。

10

20

30

40

50

**【 0 0 0 6 】**

一方で、ホウ素を含まないn型シリコン基板は、光劣化の要因を有さない。また、一般的にシリコン基板中の不純物汚染の影響として、電子の捕獲断面積が正孔の捕獲断面積よりも大きくなるため、汚染量が十分に少なければ、n型シリコン基板の方がライフタイムを大きくすることができます。したがって、最近ではn型シリコン基板を用いた太陽電池の開発も進められている。

**【先行技術文献】****【特許文献】****【 0 0 0 7 】**

【特許文献1】特開2002-57351

10

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 8 】**

しかしながら、シリコン基板の実効的なライフタイムは、バルク特性だけでなく、表面欠陥の影響も強く受ける。そのため、バルク特性改善の効果を得るには、表面欠陥の低減が重要となる。

**【 0 0 0 9 】**

特に、光学的效果を付与するために表面に凹凸を設ける場合などにおいては、表面積が増加するため、表面欠陥の絶対量も増加してしまう。表面欠陥は表面再結合を促進し、実効的なライフタイムを低下させる原因となる。

20

**【 0 0 1 0 】**

すなわち、シリコン基板の表面欠陥を極力低減させることにより、実効的なライフタイムを更に向上させることができ、光電変換装置の電気特性を向上させることができる。特に、前述の理由から、n型シリコン基板を用いた場合に、その効果は顕著となる。

**【 0 0 1 1 】**

したがって、本発明の一態様は、シリコン基板の表面欠陥を低減するパッシベーション層を設けた光電変換装置を提供することを目的の一つとする。

**【課題を解決するための手段】****【 0 0 1 2 】**

本明細書で開示する本発明の一態様は、シリコン基板の表面欠陥を低減するパッシベーション層を設けたヘテロ接合型の光電変換装置に関する。

30

**【 0 0 1 3 】**

本明細書で開示する本発明の一態様は、一対の電極間に、一導電型を有する単結晶シリコン基板と、単結晶シリコン基板の一方の面に接する第1のシリコン半導体層と、第1のシリコン半導体層に接し、単結晶シリコン基板とは逆の導電型を有する第2のシリコン半導体層と、第2のシリコン半導体層に接する透光性導電膜と、単結晶シリコン基板の他方の面に接する第3のシリコン半導体層と、第3のシリコン半導体層に接し、単結晶シリコン基板と同じ導電型で、単結晶シリコン基板よりもキャリア密度の高い第4のシリコン半導体層と、を有し、第1のシリコン半導体層及び第3のシリコン半導体層に含有されるフッ素の濃度は、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以下であることを特徴とする光電変換装置である。

40

**【 0 0 1 4 】**

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付したものであり、順序や数を限定するものではないことを付記する。

**【 0 0 1 5 】**

上記単結晶シリコン基板の導電型はn型であることが好ましい。また、該単結晶シリコン基板に含まれる酸素の濃度は、 $8 \times 10^{17}$  atoms/cm<sup>3</sup>以下であることが好ましい。

**【 0 0 1 6 】**

上記第1のシリコン半導体層及び上記第3のシリコン半導体層に含有されるフッ素の濃度

50

は、該第1のシリコン半導体層及び該第3のシリコン半導体層に含有される窒素の濃度よりも低いことが好ましい。

【0017】

また、上記第1のシリコン半導体層及び上記第3のシリコン半導体層に含有されるフッ素の濃度は、該第1のシリコン半導体層及び該第3のシリコン半導体層に含有される酸素の濃度よりも低いことが好ましい。

【発明の効果】

【0018】

本発明の一態様を用いることにより、単結晶シリコン基板の実効的なライフタイムを向上させることができ、光電変換装置の電気特性を向上させることができる。

10

【図面の簡単な説明】

【0019】

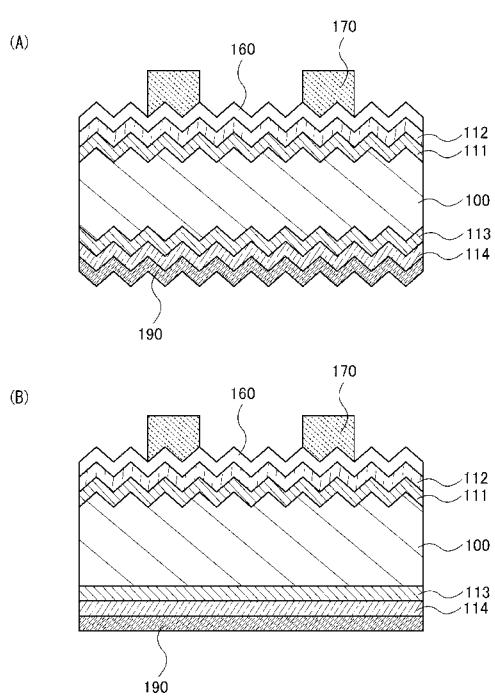

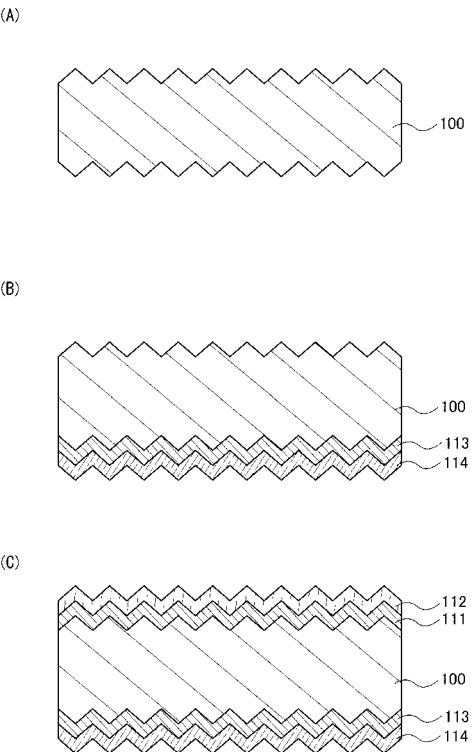

【図1】光電変換装置を説明する断面図。

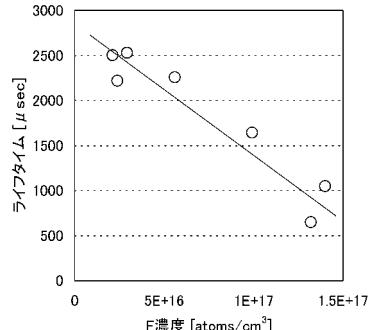

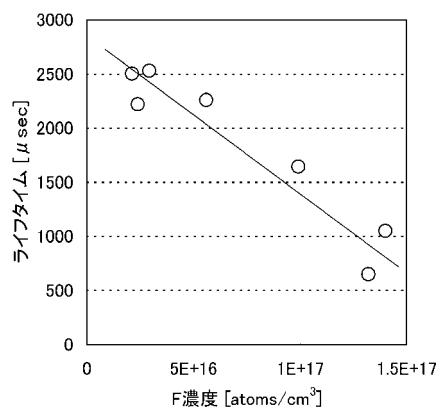

【図2】単結晶シリコン基板の両面にフッ素濃度の異なる非晶質シリコン半導体層を形成したサンプルのライフタイム測定結果。

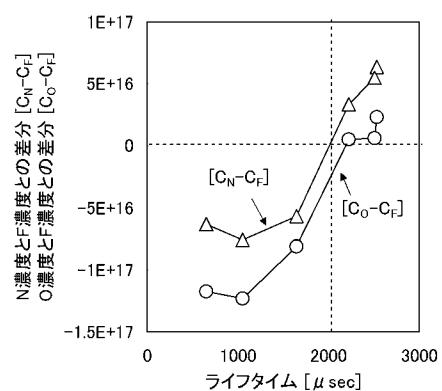

【図3】単結晶シリコン基板の両面にシリコン半導体層を形成した複数のサンプルにおいて、該シリコン半導体層の窒素濃度とフッ素濃度との差分( $C_N - C_F$ )及び酸素濃度とフッ素濃度との差分( $C_O - C_F$ )のそれぞれと、該サンプルのライフタイムとの関係を説明する図。

20

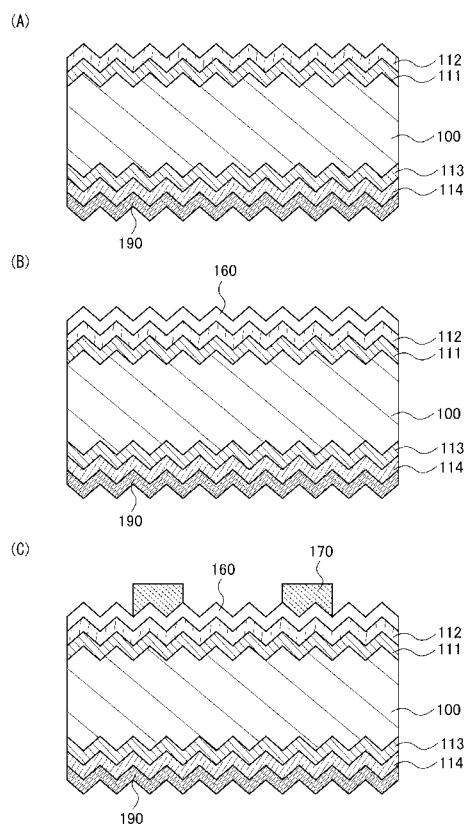

【図4】光電変換装置の作製方法を説明する断面図。

【図5】光電変換装置の作製方法を説明する断面図。

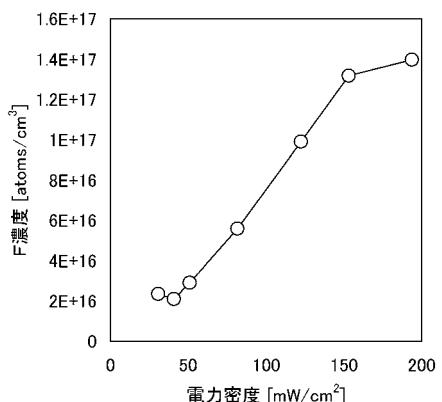

【図6】シリコン半導体層のフッ素濃度の成膜時の電力密度依存を説明する図。

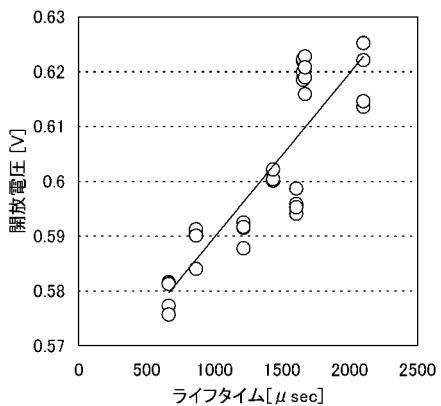

【図7】単結晶シリコン基板の両面に非晶質シリコン層および接合層を設けたサンプルのライフタイムと、該非晶質シリコン層と同一条件で形成したパッシベーション層を有する光電変換装置の開放電圧を比較した結果。

30

【発明を実施するための形態】

【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある。

30

【0021】

本実施の形態では、本発明の一態様における光電変換装置の構成及び作製方法について説明する。

【0022】

図1(A)、(B)は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、単結晶シリコン基板100の一方の面上に第1のシリコン半導体層111、第2のシリコン半導体層112、透光性導電膜160、第1の電極170が順に積層され、単結晶シリコン基板100の他方の面上には、第3のシリコン半導体層113、第4のシリコン半導体層114、第2の電極190が順に積層された構成を有している。なお、第1の電極170はグリッド電極であり、第1の電極170が形成された面側が受光面となる。また、第2の電極190もグリッド電極とし、両面を受光面とする構成としても良い。その場合は、第4のシリコン半導体層114と第2の電極190との間に、透光性導電膜を設けることが好ましい。

40

【0023】

図1(A)は、単結晶シリコン基板100の両面に周期及び高さが数十 $\mu m$ 以下の凹凸を形成した構造であり、凹凸を形成するエッチング加工時にマスクを用いず、単結晶シリコンの両面をエッチング加工することにより、該構造を形成することができる。また、図1(B)は、単結晶シリコン基板100の片面のみに凹凸を形成した構造であり、凹凸を形

50

成するエッティング加工時に、単結晶シリコン基板の他方の面をマスクで覆うことによって、単結晶シリコン基板の一方の面のみをエッティング加工することにより、該構造を形成することができる。なお、図示はしないが、単結晶シリコン基板 100 の表面に上記の凹凸を設けない構造としても良い。

#### 【0024】

凹凸加工された面では入射光が多重反射し、単結晶シリコン基板内には光が斜めに進行することから光路長が増大する。また、裏面反射光が表面で全反射する、所謂光閉じ込め効果を起こさせることもできる。

#### 【0025】

本発明の一態様において、単結晶シリコン基板 100 には n 型の単結晶シリコン基板を用いることが好ましい。極力不純物を低減した単結晶シリコン基板においても少なからず不純物が含まれており、該不純物が形成する準位にキャリアは捕獲される。該不純物の濃度が十分に小さく、かつ同程度である p 型単結晶シリコン基板及び n 型単結晶シリコン基板の比較においては、電子捕獲断面積が、正孔捕獲断面積より大きいため、正孔が少数キャリアとなる n 型シリコン基板の方がライフトайムが大きくなる。

10

#### 【0026】

しかしながら、一般的な単結晶シリコン基板では、電子を少数キャリアとする p 型単結晶シリコン基板の方が拡散長は長い。そのため、n 型単結晶シリコン基板を用いる場合には、拡散長に従って基板厚を薄くしなければならない。基板厚を薄くすると光の利用効率が低下するため、短絡電流密度が低下してしまう問題がある。

20

#### 【0027】

基板厚を薄くせずに n 型単結晶シリコン基板の拡散長を高めるには、不純物及び欠陥を低減することが必要となる。本発明の一態様においては、低酸素濃度の n 型単結晶シリコン基板を用いる。例えば、酸素濃度が  $8 \times 10^{17} \text{ atoms/cm}^3$  以下、好ましくは  $5 \times 10^{17} \text{ atoms/cm}^3$  以下、更に好ましくは  $3 \times 10^{17} \text{ atoms/cm}^3$  以下の n 型単結晶シリコン基板を用いる。ここで、単結晶シリコン中の酸素とは、格子間酸素を指す。このような低酸素濃度のシリコンウェハは、FZ (Floating Zone) 法や、MCZ (Magnetic field applied Czochralski) 法などで作製することができる。また、上記酸素濃度は、フーリエ変換赤外分光法 (換算係数  $4.81 \times 10^{17} / \text{cm}^2$ ) で求めることができる。

30

#### 【0028】

第 1 のシリコン半導体層 111 及び第 3 のシリコン半導体層 113 は、欠陥が少ない高品質な i 型半導体層であり、単結晶シリコン基板 100 の表面欠陥を低減することができる。なお、本明細書において、i 型の半導体とは、フェルミ準位がバンドギャップの中央に位置する所謂真性半導体の他、半導体に含まれる p 型を付与する不純物および n 型を付与する不純物が  $1 \times 10^{20} \text{ atoms/cm}^3$  以下の濃度であり、暗伝導度に対して光伝導度が高い半導体を指す。

#### 【0029】

例えば、第 1 のシリコン半導体層 111、第 3 のシリコン半導体層 113 には、プラズマ CVD 法等で形成される非晶質シリコンまたは微結晶シリコンを用いることができる。または、該シリコン半導体層に相当する領域が、結晶シリコン領域及び非晶質シリコン領域を含む領域であっても良い。

40

#### 【0030】

上記結晶シリコン領域は、単結晶シリコン基板 100 と接する領域においては、該単結晶シリコン基板の原子配列を受け継いだ、結晶成長領域である。したがって、該単結晶シリコン基板と該結晶シリコン領域との間には、明瞭な界面は形成されず、両者は実質的に一体となっている。すなわち、該結晶シリコン領域は、該単結晶シリコン基板と同程度の良好な結晶品質を有し、極めて不純物や欠陥の少ない領域であるといえる。

#### 【0031】

また、上記結晶シリコン領域上には、非晶質シリコン領域が形成されている。該非晶質シ

50

リコン領域は、該結晶シリコン領域と連続形成された領域である。例えば、該結晶シリコン領域及び該非晶質シリコン領域は、プラズマCVD法などを用いて該結晶シリコン領域を形成した後に、洗浄や搬送などを含む他の工程を一切介さずに該非晶質シリコン領域を形成する。または、該結晶シリコン領域の形成プロセス終了前に該非晶質シリコン領域の形成プロセスを開始することにより形成する。

#### 【0032】

このように、他の工程が行われずに連続形成された上記結晶シリコン領域と上記非晶質シリコン領域の間には、不純物濃度の高い領域や酸化層などが生成されることなく、明瞭な界面が形成されない。したがって、両者は実質的に連続した構造、または連続的に変化する構造を有しているということができる。

10

#### 【0033】

なお、上記結晶シリコン領域及び上記非晶質シリコン領域を含む領域においては、該結晶シリコン領域が占める割合が高いほど好ましい。しかしながら、結晶シリコンの表面は未結合手などの欠陥が多いため、少なくとも該結晶シリコン領域の表面が露出することがないように水素を含む非晶質シリコン領域で該結晶シリコン領域の表面を覆い、該欠陥を水素で終端する構成とすることが好ましい。

#### 【0034】

上記の説明の通り、単結晶シリコン基板100と上記結晶シリコン領域、及び上記結晶シリコン領域と上記非晶質シリコン領域との間には明瞭な界面が形成されないため、界面に存在する欠陥や不純物により形成される局在準位の影響を排除することができる。また、該結晶シリコン領域は欠陥が少なく、該結晶シリコン領域及び該非晶質シリコン領域を含む領域全体における欠陥の絶対量を少なくすることができるため、キャリアの再結合を低減させることができる。

20

#### 【0035】

また、上記結晶シリコン領域の表面は、高さ及び周期がナノメートルサイズの凹凸形状をしており、この形状も前述した凹凸の光学的作用と同等の作用を有する。したがって、図1(A)、(B)に示す光電変換装置は、マイクロメートルサイズの凹凸の表面にナノメートルサイズの凹凸を有する構造とすることができますため、光学的作用によって電気特性を大きく向上させることができる。

30

#### 【0036】

また、本発明の一態様では、第1のシリコン半導体層111及び第3のシリコン半導体層113に含まれる不純物元素を極力低減させることが好ましい。プラズマCVD法等で形成されるシリコン半導体層などには、原料ガスが高純度であっても成膜チャンバー中に残留する大気成分やクリーニングガス成分が不純物として膜中に取り込まれやすい。これらの不純物はエネルギーギャップ中に不純物準位を形成し、キャリアの捕獲などの悪影響を与える。

#### 【0037】

発明者らの実験結果では、窒素、酸素などの大気成分については、膜中の濃度を $1 \times 10^{17} \text{ atoms/cm}^3$ 以下とすることで、その影響をほとんど排除できることが判明している。また、クリーニングガスの成分であるフッ素の膜中濃度は、窒素及び/または酸素の膜中濃度以下にすることが好ましいことが判明している。

40

#### 【0038】

図2は、単結晶シリコン基板の両面にフッ素濃度の異なる非晶質シリコン半導体層を形成したサンプルのライフトライム測定結果である。該単結晶シリコン基板には酸素濃度が $8 \times 10^{17} \text{ atoms/cm}^3$ 以下のn型単結晶シリコン基板を用い、該非晶質シリコン半導体層は、フッ素濃度が変化するように成膜条件を調整して形成している。

#### 【0039】

バルク特性が良好な単結晶シリコン基板を用いているために、フッ素濃度が高めであっても $1000 \mu\text{sec}$ 前後のライフトライムを示しているが、フッ素濃度を $1 \times 10^{17} \text{ atoms/cm}^3$ 以下とすることで、ライフトライムは $1500 \mu\text{sec}$ 以上を示すようにな

50

る。更にはフッ素濃度を  $6 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とすることで、ライフタイムは極めて高い 2000 μsec 以上を示すようになる。したがって、単結晶シリコン基板の表面にパッシベーション層として形成するシリコン半導体層のフッ素濃度は、 $1 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とすることが好ましく、 $6 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とすることが更に好ましい。

#### 【0040】

また、上記シリコン半導体層のフッ素濃度は、該シリコン半導体層の窒素濃度、及び酸素濃度よりも低いことが好ましい。図3は、単結晶シリコン基板の両面にシリコン半導体層を形成した複数のサンプルにおいて、該シリコン半導体層の窒素濃度とフッ素濃度との差分 ( $C_N - C_F$ ) 及び酸素濃度とフッ素濃度との差分 ( $C_O - C_F$ ) のぞれぞれと、該サンプルのライフタイムを比較した結果である。10

#### 【0041】

図3より、ライフタイムが 2000 μsec 付近で  $C_N - C_F$  及び  $C_O - C_F$  の値の正負が入れ替わっていることがわかる。該値が正の場合は、窒素濃度または酸素濃度よりもフッ素濃度が低いことを示しており、該値が正であることは、高いライフタイムを達成するための明確な指標であることがわかる。

#### 【0042】

つまり、高いライフタイムを達成するためには、シリコン半導体層（パッシベーション層）のフッ素濃度を  $1 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とするだけでなく、該フッ素濃度をシリコン半導体層の窒素濃度及び酸素濃度のいずれか、または両方より低い値とすることが好ましい。なお、シリコン半導体層のフッ素濃度が  $1 \times 10^{17}$  atoms / cm<sup>3</sup> 以上である場合には、窒素濃度及び酸素濃度とライフタイムとの相関は見られない。20

#### 【0043】

上述したシリコン半導体層を第1のシリコン半導体層111及び第3のシリコン半導体層113として単結晶シリコン基板100の表面に形成することで、該単結晶シリコン基板のライフタイムを向上させることができ、電気特性が良好な光電変換装置を形成することができる。特に、該単結晶シリコン基板の表面に凹凸を設ける場合には、その効果が顕著となる。

#### 【0044】

単結晶シリコン基板100は一導電型を有し、第2のシリコン半導体層112は、単結晶シリコン基板100の導電型とは逆の導電型を有する半導体層である。単結晶シリコン基板100がn型の場合には、第2のシリコン半導体層112はp型であり、単結晶シリコン基板100と第2のシリコン半導体層112との間には、第1のシリコン半導体層111を介してp-n接合が形成される。30

#### 【0045】

また、第4のシリコン半導体層114は、単結晶シリコン基板100と同じ導電型を有し、該単結晶シリコン基板よりもキャリア密度の高い層である。本発明の一態様において、単結晶シリコン基板100がn型である場合には、単結晶シリコン基板100と第4のシリコン半導体層114との間には、第3のシリコン半導体層113を介してn-n<sup>+</sup>接合が形成される。つまり、第4のシリコン半導体層114は、BSF (Back Surf ace Field) 層として作用する。BSF層を形成することにより、少数キャリアがp-n接合側にはね返されることから、第2の電極190近傍でのキャリアの再結合を防止することができる。40

#### 【0046】

次に、図1(A)に示した光電変換装置の作製方法について図4及び図5を用いて説明する。

#### 【0047】

本実施の形態では、単結晶シリコン基板100にMCZ法で形成した酸素濃度が  $8 \times 10^{17}$  atoms / cm<sup>3</sup> 以下のn型単結晶シリコン基板を用いる。なお、単結晶シリコン基板の酸素濃度が  $8 \times 10^{17}$  atoms / cm<sup>3</sup> 以下であれば、その製法は問わない。50

また、表裏に凹凸加工を行う場合は、単結晶シリコン基板の表面に(100)面を有する基板を用いる。

【0048】

次に、単結晶シリコン基板100の表裏に凹凸加工を行う。

【0049】

初期の単結晶シリコン基板100がスライス加工のみである基板の場合は、単結晶シリコン基板100の表面から10~20μmに残留するダメージ層をウエットエッティング工程にて取り除く。エッティング液には、比較的高濃度のアルカリ溶液、例えば、10~50%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができる。または、フッ酸と硝酸を混合した混酸や、それらに酢酸を混合した混酸を用いても良い。10

。

【0050】

次に、ダメージ層除去後の単結晶シリコン基板表面に付着している不純物を酸洗浄で取り除く。酸としては、例えば、0.5%フッ酸と1%過酸化水素水の混合液(FPM)などを用いることができる。またはRCA洗浄などを行っても良い。なお、この酸洗浄工程は省いても良い。

【0051】

凹凸は、結晶シリコンのアルカリ溶液によるエッティングにおいて、面方位に対するエッティングレートの違いを利用して形成する。エッティング液には比較的低濃度のアルカリ溶液、例えば、1~5%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができ、好ましくは、数%のイソプロピルアルコールを添加する。エッティング液の温度は70~90とし、30~60分間、単結晶シリコン基板をエッティング液に浸漬する。この処理により、単結晶シリコン基板100表面に、微細な略四角錐状の複数の凸部、及び隣接する凸部間で構成される凹部からなる凹凸を形成することができる。20

【0052】

次に、上述の凹凸を形成するためのエッティング工程では、単結晶シリコン基板の表層に不均一な酸化層が形成されるため、該酸化層を取り除く。また、該酸化層にはアルカリ溶液の成分が残存しやすいため、それを取り除く目的もある。アルカリ金属、例えばNaイオンやKイオンがシリコン中に侵入するとライフタイムが劣化するため、光電変換装置の電気特性が著しく低下してしまう。なお、この酸化層を除去するには、1~5%の希フッ酸を用いれば良い。30

【0053】

次に、フッ酸と硝酸を混合した混酸、または、それらに酢酸を混合した混酸を用いて単結晶シリコン基板100の表面をエッティングし、金属成分などの不純物を除去することが好ましい。酢酸を混合することで、硝酸の酸化力を維持し、エッティング工程を安定にする効果、及びエッティングレートを調整する効果が得られる。例えば、各酸の体積比率は、フッ酸：硝酸：酢酸=1:(1.5~3):(2~4)とすることができる。なお、本明細書では、フッ酸、硝酸及び酢酸の混酸液をフッ硝酢酸と呼ぶ。また、このフッ硝酢酸を用いたエッティング工程では、凸部の頂点の断面における角度を大きくする方向に変化させることから、表面積が低減し、表面欠陥の絶対量を低減することができる。なお、このフッ硝酢酸を用いたエッティングを行う場合は、上述の希フッ酸を用いた酸化層の除去工程を省くこともできる。ここまででの工程により、図4(A)に示す単結晶シリコン基板の断面形状が形成される。40

【0054】

次いで、適切な洗浄の後、単結晶シリコン基板100の一面にプラズマCVD法を用いて第3のシリコン半導体層113を形成する。本実施の形態において、第3のシリコン半導体層113は、i型の非晶質シリコン半導体層とし、膜厚は3nm以上50nm以下とすることが好ましい。

【0055】

第3のシリコン半導体層113は、例えば、反応室にモノシランを導入し、反応室内の圧50

力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm<sup>2</sup>以上120mW/cm<sup>2</sup>以下、基板温度を150以上300以下とする条件で形成することができる。

#### 【0056】

なお、図6に示すように、シリコン半導体層のフッ素濃度は、成膜時の電力密度に強く依存する。したがって、フッ素濃度を低減させるには、電力密度を120mW/cm<sup>2</sup>以下、好ましくは80mW/cm<sup>2</sup>以下、更に好ましくは50mW/cm<sup>2</sup>以下とする。例えば、反応室内の圧力を150Pa、電極間隔を10mm、電力密度を40mW/cm<sup>2</sup>、基板温度を250とすれば良い。

#### 【0057】

次いで、第3のシリコン半導体層113上に第4のシリコン半導体層114を形成する(図4(B)参照)。第4のシリコン半導体層114の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層114はn型の非晶質シリコンであり、膜厚は10nmとする。

#### 【0058】

第4のシリコン半導体層114は、反応室にモノシラン及び水素ベースのホスフィン(0.5%)を1:(1~50)の流量比率で導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を10mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm<sup>2</sup>以上120mW/cm<sup>2</sup>以下、基板温度を150以上300以下とする条件で形成することができる。

#### 【0059】

次いで、単結晶シリコン基板100の逆の一面に、プラズマCVD法を用いて第1のシリコン半導体層111を形成する。第1のシリコン半導体層111の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態においては5nmとする。第1のシリコン半導体層111は、第3のシリコン半導体層113と同様の条件にて形成することができる。

#### 【0060】

次いで、第1のシリコン半導体層111上に第2のシリコン半導体層112を形成する(図4(C)参照)。第2のシリコン半導体層112の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第2のシリコン半導体層112はp型の非晶質シリコンであり、膜厚は10nmとする。

#### 【0061】

第2のシリコン半導体層112は、反応室にモノシラン及び水素ベースのジボラン(0.1%)を1:(2~50)の流量比率で導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を8mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm<sup>2</sup>以上50mW/cm<sup>2</sup>以下、基板温度を150以上300以下とする条件で形成することができる。

#### 【0062】

なお、本実施の形態において、上記シリコン半導体層の形成に用いる電源には、原料ガスの分解効率の良い周波数60MHzのRF電源を用いることが好ましい。原料ガスの分解効率を上げることで、第1のシリコン半導体層111および第3のシリコン半導体層113の形成時に単結晶シリコン基板100表面の未結合手を水素で終端しやすくなる。ただし、13.56MHz、27.12MHz、または100MHzのRF電源を用いても良い。また、連続放電だけでなく、パルス放電にて形成を行っても良い。ON/OFF制御、またはHigh/Low制御のパルス放電を行うことで、膜質の向上や気相中で発生するパーティクルを低減することができる。

#### 【0063】

次いで、第4のシリコン半導体層114上に第2の電極190を形成する(図5(A)参照)。第2の電極190には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法を

10

20

30

40

50

用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

**【0064】**

次いで、第2のシリコン半導体層112上に透光性導電膜160をスパッタ法で形成する(図5(B)参照)。透光性導電膜160には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜160は単層に限らず、異なる膜の積層でも良い。例えば、インジウム錫酸化物とアルミニウムを含む酸化亜鉛の積層や、インジウム錫酸化物とフッ素を含む酸化錫の積層などを用いることができる。膜厚は総厚で10nm以上1000nm以下とする。

10

**【0065】**

なお、単結晶シリコン基板100の表裏に設ける膜の形成順序は、上記の方法に限らず、図5(B)に示した構造が形成できればよい。例えば、第1のシリコン半導体層111を形成し、その次に第3のシリコン半導体層113を形成しても良い。

**【0066】**

次いで、スクリーン印刷法を用いて、透光性導電膜160上に導電性樹脂を供給し、焼成して第1の電極170を形成する。ここで用いる導電性樹脂には、銀ペースト、銅ペースト、ニッケルペースト、モリブデンペーストなどを用いることができる。また、第1の電極170は、銀ペーストと銅ペーストを積層するなど、異なる材料の積層であっても良い。

20

**【0067】**

以上により、本発明の一態様によって電気特性の優れた光電変換装置を形成することができる。

**【実施例】**

**【0068】**

本実施例では、光電変換装置のセル特性について説明する。

**【0069】**

本実施例で説明する光電変換装置は、図1(A)に示す構造であり、MCZ法を用いて作製した酸素濃度が $8 \times 10^{17}$ atoms/cm<sup>3</sup>以下のn型単結晶シリコン基板を用いて、実施の形態で説明した方法を用いて作製した。セルサイズは0.7cm<sup>2</sup>であり、測定には、ソーラーシミュレータにより発生させた疑似太陽光(AM1.5、照射強度は100mW/cm<sup>2</sup>)を用いた。

30

**【0070】**

図7は、単結晶シリコン基板の両面に非晶質シリコン層及び接合層を設けた図4(C)の構造で測定したライフタイムと、同サンプルに透光性導電膜及び電極を形成して図5(C)の構造とし、I-V測定から算出した開放電圧(Voc)との関係を示す図である。なお、ライフタイムの異なるサンプルは、該非晶質シリコン層の成膜時の電力密度を変化させることにより形成した。

**【0071】**

図7に示されている通り、開放電圧とライフタイムは強い相関があり、特にライフタイムを1500μsec以上にすることが有効であることが確かめられた。したがって、本発明の一態様は、光電変換装置の変換効率の向上に寄与することが明かとなった。

40

**【0072】**

本実施例は、他の実施の形態と自由に組み合わすことができる。

**【符号の説明】**

**【0073】**

100 単結晶シリコン基板

111 第1のシリコン半導体層

112 第2のシリコン半導体層

113 第3のシリコン半導体層

50

- 1 1 4 第4のシリコン半導体層

1 6 0 透光性導電膜

1 7 0 第1の電極

1 9 0 第2の電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

フロントページの続き

F ターム(参考) 5F151 AA02 AA05 AA16 CA02 CA03 CA04 CA07 CA08 CA16 CA34

CA35 CA36 CB03 CB21 DA03 FA02 FA03 FA04 FA08 FA14

FA15 GA04 GA15