(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4511598号

(P4511598)

(45) 発行日 平成22年7月28日(2010.7.28)

(24) 登録日 平成22年5月14日(2010.5.14)

(51) Int.Cl.

H01L 21/82 (2006.01)

G03F 1/08 (2006.01)

F 1

H01L 21/82

H01L 21/82

GO3F 1/08C

T

A

請求項の数 18 (全 14 頁)

(21) 出願番号 特願2007-536971 (P2007-536971)

(86) (22) 出願日 平成17年10月14日 (2005.10.14)

(65) 公表番号 特表2008-517467 (P2008-517467A)

(43) 公表日 平成20年5月22日 (2008.5.22)

(86) 國際出願番号 PCT/US2005/037145

(87) 國際公開番号 WO2006/044730

(87) 國際公開日 平成18年4月27日 (2006.4.27)

審査請求日 平成20年9月1日 (2008.9.1)

(31) 優先権主張番号 10/711,959

(32) 優先日 平成16年10月15日 (2004.10.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】集積回路設計の層、領域またはセルであるオブジェクトを選択的にスケーリングするための方法

、システム、およびプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

集積回路設計レイアウトの層、領域またはセルであるオブジェクトを選択的にスケーリングする方法であって、

大きなサイズまたはピッチに拡大スケーリングされるべき層、小さなサイズまたはピッチへの縮小スケーリングが可能な層、大きなサイズに拡大スケーリングされるべき領域、小さなサイズへの縮小スケーリングが可能な領域、互いに隣接して配置できないセル、または互いに近接して配置するために修正を必要とするセルを示す製造情報に基づいて、前記集積回路設計レイアウトのうち問題を生じている問題オブジェクトを識別するステップと、

各問題オブジェクトに対する基本寸法および制約を定義するステップと、

各問題オブジェクトに対してスケーリングファクタを確定するステップと、

複数のスケーリング技法のうちのどの1つの技法が、各問題オブジェクトに適用されるかを判定し、各問題オブジェクトをこれに適用されるスケーリング技法およびスケーリングファクタでスケーリングするステップと、

配置および配線を行って、前記スケーリングされた問題オブジェクトを用いた前記集積回路設計レイアウトのアセンブリを行うステップと、をその順序で実行する方法。

## 【請求項 2】

前記配置および配線を行うステップは、各問題オブジェクトに対して正しいレイアウトを生成するために、最適化ベースの階層的スケーリングを使用する請求項1に記載の方法

。

**【請求項 3】**

前記スケーリングファクタは、補正係数、新しい基本寸法、およびスケーリング乗数のうち少なくとも 1 つである請求項 1 に記載の方法。

**【請求項 4】**

前記識別するステップは、

前記設計レイアウトを製造することと、

前記製造された設計レイアウトを試験し、問題となる少なくとも 1 つの問題オブジェクトを識別することと、

前記製造情報を生成すること、

を含む請求項 1 に記載の方法。

**【請求項 5】**

前記設計レイアウトを試験するステップは、オブジェクトの製造をいかにうまく行えるかを示すデータを取得することによって、動作を特徴付け、かつ前記少なくとも 1 つの問題オブジェクトを識別することを含む請求項 4 に記載の方法。

**【請求項 6】**

前記製造情報を生成するステップは、前記問題オブジェクトに対してスケーリング目標を生成することを含む請求項 4 に記載の方法。

**【請求項 7】**

前記スケーリングされたオブジェクトを含む新しい設計レイアウトが、予想される挙動を実現するかどうかを評価するステップをさらに有する請求項 1 ないし 6 のいずれか一項に記載の方法。

**【請求項 8】**

集積回路設計レイアウトの層、領域またはセルであるオブジェクトを選択的にスケーリングするシステムであって、

大きなサイズまたはピッチに拡大スケーリングされるべき層、小さなサイズまたはピッチへの縮小スケーリングが可能な層、大きなサイズに拡大スケーリングされるべき領域、小さなサイズへの縮小スケーリングが可能な領域、互いに隣接して配置できないセル、または互いに近接して配置するために修正を必要とするセルを示す製造情報に基づいて、前記集積回路設計レイアウトのうち問題を生じている問題オブジェクトを識別する手段と

、

各問題オブジェクトに対する基本寸法および制約を定義する手段と、

各問題オブジェクトに対してスケーリングファクタを確定する手段と、

複数のスケーリング技法のうちのどの 1 つの技法が、各問題オブジェクトに適用されるかを判定し、各問題オブジェクトをこれに適用されるスケーリング技法およびスケーリングファクタでスケーリングする手段と、

配置および配線を行って、前記スケーリングされた問題オブジェクトを用いた前記集積回路設計レイアウトのアセンブリを行う手段と、

を有するシステム。

**【請求項 9】**

前記配置および配線を行う手段は、各問題オブジェクトに対して正しいレイアウトを生成するために、最適化ベースの階層的スケーリングを使用する請求項 8 に記載のシステム。

**【請求項 10】**

前記スケーリングファクタは、補正係数、新しい基本寸法、およびスケーリング乗数のうち少なくとも 1 つである請求項 8 に記載のシステム。

**【請求項 11】**

前記識別する手段は、

前記設計レイアウトを製造することと、

前記製造された設計レイアウトを試験し、問題となる少なくとも 1 つの問題オブジェク

10

20

30

40

50

トを識別することと、

前記製造情報を生成すること、

を含む請求項 8 に記載のシステム。

**【請求項 1 2】**

前記設計レイアウトを試験する手段は、オブジェクトの製造をいかにうまく行えるかを示すデータを取得することによって、動作を特徴付け、かつ前記少なくとも 1 つの問題オブジェクトを識別することを含む請求項 1 1 に記載のシステム。

**【請求項 1 3】**

前記製造情報を生成する手段は、前記問題オブジェクトに対してスケーリング目標を生成することを含む請求項 1 1 に記載のシステム。

10

**【請求項 1 4】**

前記スケーリングされたオブジェクトを含む新しい設計レイアウトが、予想される挙動を実現するかどうかを評価する手段をさらに有する請求項 8 ないし 1 3 のいずれか一項に記載のシステム。

**【請求項 1 5】**

集積回路設計レイアウトの層、領域またはセルであるオブジェクトを選択的にスケーリングするためのコンピュータプログラムであって、コンピュータに、

大きなサイズまたはピッチに拡大スケーリングされるべき層、小さなサイズまたはピッチへの縮小スケーリングが可能な層、大きなサイズに拡大スケーリングされるべき領域、小さなサイズへの縮小スケーリングが可能な領域、互いに隣接して配置できないセル、または互いに近接して配置するために修正を必要とするセルを示す製造情報に基づいて、前記集積回路設計レイアウトのうち問題を生じている問題オブジェクトを識別するステップと、

20

各問題オブジェクトに対する基本寸法および制約を定義するステップと、

各問題オブジェクトに対してスケーリングファクタを確定するステップと、

複数のスケーリング技法のうちのどの 1 つの技法が、各問題オブジェクトに適用されるかを判定し、各問題オブジェクトをこれに適用されるスケーリング技法およびスケーリングファクタでスケーリングするステップと、

配置および配線を行って、前記スケーリングされた問題オブジェクトを用いた前記集積回路設計レイアウトのアセンブリを行うステップと、をその順序で実行させるプログラム。

30

**【請求項 1 6】**

前記配置および配線を行うステップは、各問題オブジェクトに対して正しいレイアウトを生成するために、最適化ベースの階層的スケーリングを使用する請求項 1 5 に記載のプログラム。

**【請求項 1 7】**

前記スケーリングファクタは、補正係数、新しい基本寸法、およびスケーリング乗数のうち少なくとも 1 つである請求項 1 5 に記載のプログラム。

**【請求項 1 8】**

前記識別するステップは、

40

前記設計レイアウトを製造することと、

前記製造された設計レイアウトを試験し、問題となる少なくとも 1 つの問題オブジェクトを識別することと、

前記製造情報を生成すること、

を含む請求項 1 5 に記載のプログラム。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、概して、集積回路の設計に関し、より詳細には、階層構造が保持されるようには、初期プロセスでの歩留まりを向上させるため、層、領域、またはセル、あるいはそれ

50

らの組み合わせによって、集積回路の設計レイアウトを選択的にスケーリングすることに

関する。

#### 【背景技術】

##### 【0002】

製造歩留まりを上げるために、既存の超大規模集積(VLSI)回路設計を修正する一

方法として、ワイヤスプレッディング、冗長ビアの追加を行って、クリティカルエリアを

減らし、ビアの信頼性を上げるものがある。しかし、新たな製造プロセスの初期段階では

、こうしたレイアウト後の修正だけでは、所望の歩留まり改善を達成するのに不十分な場

合がある。既存のレイアウトに対する別の歩留まり改善のための修正法として、スペーシ

ングおよび幅の許容範囲を緩和するものがあり、これは、幾何学的スケーリング法によ

って実現できる。しかし、このスケーリングを、ある設計層のみに対し、かつ、ある他の幾

何学的制約のもとで、または、階層構造があるなかで実施しようとした場合に、問題が生

じる。たとえば、バックエンドオブライൻ(BEOL)層が、スケーリングの対象になる

場合がある。(ただし、デバイスサイズを変更せずに、最上部の配線から集積回路パッケ

ージまでの接続位置が固定された状態になっていなければならない)。

10

##### 【0003】

スケーリングされる層とスケーリングされない層との間で接続性が維持される場合、単

純な線形幾何学的スケーリング(すなわち、設計データベース内の全てのオブジェクトの

座標を、一定スケーリングファクタで乗算すること)を行うことは、明らかに不適切である。

階層的スケーリングの問題は、それ自体解決するのが難しい。その解決法の一つが、

同時継続中の「A Practical Method for Hierarchical-Preserving Layout Optimiza

tion of Integrated Circuit Layout(集積回路レイアウトの階層を保持したまま

レイアウト最適化を行う実用的方法)」という名称の米国特許出願第10/438,62

5号(現在、係属中)に記載されている。この米国特許出願は、ここでの言及において本

明細書に引用したものとする。また、別の手法として選択的スケーリングがあり、その一

例が、Reganの米国特許第6,756,242号に開示されている。ただし、Reganは、X

方向とY方向に、異なるスケーリングファクタで設計全体をスケーリングすることを教示

しており、これもまた、層間で接続性が維持される場合、不適切である。

20

##### 【0004】

半導体製造において、設計レイアウトは、製造組織によって設計者に提供される一定の

基本寸法を備えている。この基本寸法は、製造可能なものについてのプロセスおよびリソ

グラフィの最良推定値を表している。基本寸法では、ウェハ上のチップ密度(積極性)と

、確実に製造できるもの(慎重性)との均衡を図っている。技術プロセスまたは設計の期

間中、最終製品に関して、また、製造ラインにおいて、故障解析を通じて、「学習」が行

われる。その場合、この学習が、歩留まりの改善につながることがある。たとえば、基本

寸法を、歩留まりの学習を反映したものに変更されてもよい。しかし、変更のたびに、設

計者を介在させて、設計の修正を行い新たな基本寸法を反映させなければならないため、

いずれの変更を行っても費用がかかることから、頻繁な変更、または、大幅な変更は、通常

不可能であり、都合が悪い。さらに重要な点は、いずれの設計修正も、通常、非常に高

価な新しいマスクを必要とすることである。そのため、設計変更は、これまで、あまり行

われてこなかった。ただし、歩留まりに関連する設計変更の追加は、機能変更により新

しいマスクを必要とする場合(すなわち、新たな設計の反復を必要とする、機能または性能

に関する問題が存在する場合)、または、コスト目標を達成するうえで、新たな設計の反

復を行わざるを得ないような、深刻な歩留まりの問題が存在する場合に、行われることが

ある。

30

##### 【0005】

しかし、将来の製造および設計環境には、このプロセスを大幅に改善し得る重要な側面

がいくつかある。第1に、実現した場合に、設計変更のためのマスクセットの追加コスト

を必要としない、マスクレスリソグラフィが、次世代の技術に向けて提案されている。第

2に、アルゴリズム、並列処理、およびシステムアーキテクチャの改良によって、改良型

40

50

シミュレーションおよび検証機能により、設計のより「完全な」シミュレーションを行える可能性がある。このように、設計期間中に、プロセスおよび歩留まりのフィードバックを行う製造ラインと密接に結びついたフィードバックループ内で、選択的スケーリングが適用される可能性がある。現在の製造および設計環境においては、マスク寿命が限定されていることから、設計期間中に、定期的にレイアウトを更新する機会がある。

【特許文献 1】米国特許出願第 10 / 438,625 号

【特許文献 2】米国特許第 6,756,242 号

【特許文献 3】米国特許出願第 10 / 707,287 号

【発明の開示】

【発明が解決しようとする課題】

10

【0006】

上記を考慮して、関連技術の問題に対処する必要性が当技術分野に存在する。

【課題を解決するための手段】

【0007】

本発明は、層、領域、またはセル、あるいはそれらの組み合わせによって、集積回路 (IC) の設計を選択的にスケーリングするための、方法、システム、およびプログラム製品を含む。階層構造が保持されるように、初期プロセスでの歩留まりを向上させるため、設計期間中に、プロセスおよび歩留まりのフィードバックを行う製造システムと結びついたフィードバックループ内で、本選択的スケーリング技法を適用することができる。本発明によって、歩留まりの改善にあたって設計者を介在させる必要性がなくなる。

20

【0008】

本発明の第 1 の態様は、集積回路設計レイアウトを選択的にスケーリングする方法を対象とし、この方法は、製造情報に基づいて、設計レイアウトの少なくとも 1 つの問題オブジェクトに対してスケーリング目標を識別するステップと、各問題オブジェクトに対して技術上の基本寸法および方法制約を定義するステップと、各問題オブジェクトに対してスケーリングファクタを確定するステップと、複数のスケーリング技法のうちの、少なくともどの 1 つの技法が、各問題オブジェクトに適用されるかを判定し、各問題オブジェクトを、それぞれの少なくとも 1 つのスケーリング技法およびスケーリングファクタでスケーリングするステップと、アセンブリを必要とする場合に、配置および配線を行って、スケーリングされた問題オブジェクトを用いた設計のアセンブリを行うステップと、を有する。

30

【0009】

第 2 の態様は、集積回路設計レイアウトを選択的にスケーリングするシステムを対象とし、このシステムは、製造情報に基づいて、設計レイアウトの少なくとも 1 つの問題オブジェクトに対してスケーリング目標を識別する手段と、各問題オブジェクトに対して技術上の基本寸法および方法制約を定義する手段と、各問題オブジェクトに対してスケーリングファクタを確定する手段と、複数のスケーリング技法のうちの、少なくともどの 1 つの技法が、各問題オブジェクトに適用されるかを判定し、各問題オブジェクトを、それぞれの少なくとも 1 つのスケーリング技法およびスケーリングファクタでスケーリングする手段と、アセンブリを必要とする場合に、配置および配線を行って、スケーリングされた問題オブジェクトを用いた設計のアセンブリを行う手段と、を有する。

40

【0010】

第 3 の態様は、集積回路設計レイアウトを選択的にスケーリングするための、コンピュータ読み取り可能プログラムコードを内部に組み入れたコンピュータ利用可能媒体を有するコンピュータプログラム製品を対象とし、このプログラム製品は、製造情報に基づいて、設計レイアウトの少なくとも 1 つの問題オブジェクトに対してスケーリング目標を識別するように構成されたプログラムコードと、各問題オブジェクトに対して技術上の基本寸法および方法制約を定義するように構成されたプログラムコードと、各問題オブジェクトに対してスケーリングファクタを確定するように構成されたプログラムコードと、複数のスケーリング技法のうちの、少なくともどの 1 つの技法が、各問題オブジェクトに適用さ

50

れるかを判定し、各問題オブジェクトを、それぞれの少なくとも1つのスケーリング技法およびスケーリングファクタでスケーリングするように構成されたプログラムコードと、アセンブリを必要とする場合に、配置および配線を行って、スケーリングされた問題オブジェクトを用いた設計のアセンブリを行うように構成されたプログラムコードと、を有する。

#### 【0011】

第4の態様は、製造中に集積回路設計レイアウトの歩留まりを改善する方法を対象とし、この方法は、製造された設計レイアウトを試験し、問題となる少なくとも1つの問題オブジェクトを識別するステップと、試験中に取得される製造情報を生成するステップと、

設計レイアウトの選択的なスケーリングのために、システムに製造情報をフィードバックするステップであって、これにより、製造情報に基づき設計レイアウトの少なくとも1つの問題オブジェクトに対するスケーリング目標を使用して歩留まりを改善する、フィードバックするステップと、を有する。10

#### 【0012】

本発明の第5の態様は、製造中に集積回路設計レイアウトの歩留まりを改善するシステムを対象とし、このシステムは、製造された設計レイアウトを試験し、問題となる少なくとも1つの問題オブジェクトを識別する手段と、各問題オブジェクトに対するスケーリング目標を含む製造情報を生成する手段と、設計レイアウトの選択的なスケーリングのために、システムに製造情報をフィードバックする手段であって、これにより、製造情報に基づき設計レイアウトの少なくとも1つの問題オブジェクトに対するスケーリング目標を使用して歩留まりを改善する、フィードバックする手段と、を有する。20

#### 【0013】

本発明の第6の態様は、製造中に集積回路設計レイアウトの歩留まりを改善するための、コンピュータ読み取り可能プログラムコードを内部に組み入れたコンピュータ利用可能媒体を有するコンピュータプログラム製品を対象とし、このプログラム製品は、製造された設計レイアウトを試験し、問題となる少なくとも1つの問題オブジェクトを識別するよう構成されたプログラムコードと、各問題オブジェクトに対するスケーリング目標を含む製造情報を生成するよう構成されたプログラムコードと、設計レイアウトの選択的なスケーリングのために、システムに製造情報をフィードバックして、製造情報に基づき設計レイアウトの少なくとも1つの問題オブジェクトに対するスケーリング目標を使用して歩留まりを改善するよう構成されたプログラムコードと、を有する。30

#### 【0014】

本発明の前記ならびに他の特徴は、本発明の実施形態に関する、以下のより詳細な説明から明らかになるであろう。

#### 【0015】

本発明の実施形態について、同じ名称は同じ要素を示す以下の図面を参照しながら、詳細に説明する。

#### 【発明を実施するための最良の形態】

#### 【0016】

構成の目的上、説明は、以下の表題、すなわち、I. システム概要、II. 動作手順、III. 結論により構成される。40

#### 【0017】

#### I. システム概要

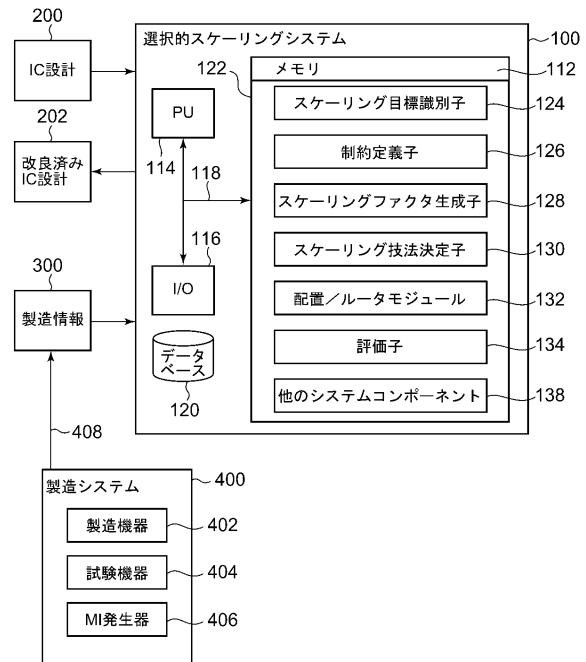

添付図面を参照すると、図1は、本発明の一実施形態による、集積回路（IC）の設計用選択的スケーリングシステム100のブロック図である。システム100は、メモリ112、処理ユニット（PU）114、入力／出力デバイス（I/O）116、およびバス118を含む。さらに、データベース120が、処理タスクに対するデータの記憶用に設けられている。メモリ112は、プログラム製品122を含み、プログラム製品122は、PU114によって実行されると、以下でさらに詳細に述べられる種々の機能を有する。メモリ112（およびデータベース120）は、磁気媒体、光媒体、ランダムアクセス

メモリ( RAM )、読み出し専用メモリ( ROM )、データオブジェクトなどを含む、任意の周知のタイプのデータ記憶システムおよび/または伝送媒体を有してもよい。さらに、メモリ 112( およびデータベース 120 )は、1つまたは複数のタイプのデータストレージを有する单一の物理的位置に存在してもよく、または、複数の物理システムにわたって分散してもよい。PU114 は、同様に、単一の処理ユニット、または、1つまたは複数のロケーションにわたって分散した複数の処理ユニットを有してもよい。I/O116 は、ネットワークシステム、モデム、キーボード、マウス、スキャナ、音声認識システム、CRT、プリンタ、ディスクドライブなどを含む、任意の周知のタイプの入力/出力デバイスを有していてもよい。キャッシングメモリ、通信システム、システムソフトウェアなどの付加的なコンポーネントもまた、システム 100 内に組み込まれてもよい。システム 100 は、修正の対象となる IC 設計 200 を受信し、改善された IC 設計 202 を出力する。システム 100 は、より大型の IC 設計システムの一部として組み込まれてもよく、または、別個のシステムとして設けられてもよい。

#### 【 0018 】

図 1 に示すように、プログラム製品 122 は、スケーリング目標識別子 124 、制約定義子 126 、スケーリングファクタ生成子 128 、スケーリング技法決定子 130 、配置ノルータモジュール 132 、評価子 134 、および他のシステムコンポーネント 138 を備えている。他のシステムコンポーネント 138 は、本明細書では特に記載されていない、その他の必要な機能を含んでいてもよい。

#### 【 0019 】

システム 100 は、スタンドアローンシステムとして示されたが、より大型の IC 設計システムの一部またはより大型の IC 設計システムの周辺機器として含まれていてもよい。IC 設計 200 は、システム 100 に入力され、改良された IC 設計 202 が、システム 100 から出力される。

#### 【 0020 】

製造システム 400 について、以下において更に詳細に説明する。

#### 【 0021 】

##### I I . 動作手順

###### A . 概要

「A Practical Method for Hierarchical-Preserving Layout Optimization of Integrated Circuit Layout」という名称の同時係属中の米国特許出願第 10 / 438,625 号では、いわゆる、「引き離し」を起こさずに、すなわち、スケーリングされた後に、同じ層上の 2 つの接触する形状が接触しない状況を作ることなく、異なるスケーリングファクタによって、集積回路( IC )設計レイアウト内に異なる層をスケーリングする方法が記載されている。本出願では、階層設計レベル間のインターフェースに対する制約を指定することによって、また、階層的要素( たとえば、ライブラリまたはマクロ )の配置を、スケーリング中にどのように指定できるかを示すことによって、階層設計に対してこれらの技法を適用するための方法を教示している。さらに、本発明によって、設計全体に埋め込まれた異なる機能コンポーネントを様々にスケーリングすることができ、逆アセンブリおよび再アセンブリを行う必要もない。さらに、本発明は、任意の選択基準、たとえば、パターンマッチング、階層構造、名前などに基づいて、チップ全体までの任意のサイズの選択領域によってスケーリングを行う際に用いることができる。したがって、本発明により、以下のことが可能になる。すなわち、a ) スケーリング自体を、最適化プロセスにすることが可能になる( この場合、一部のスケーリング目標が達成され、一部が達成されない )。これによって、設計者は、一定の方法上の制約( ピンロケーションなど )を課し、それに従うことができるようになる。b ) スケーリングの結果として、下位回路が大きくなる場合、回路の配置は、レイアウトトポロジを保持するために修正される。c ) 設計の構築時に、スケーリングをコンポーネントごとに適用するか、または、最後に、完全に構築された( 配置され、配線された )設計に対してスケーリングを施すことが可能となる。d ) コンポーネントごと、層ごと、または、さらにロケーションごとに、スケーリングを適用するか、または、最後に、完全に構築された( 配置され、配線された )設計に対してスケーリングを施すことが可能となる。

10

20

30

40

50

リングに対して、非常に精密な制御が可能になる。

#### 【0022】

さらに、本発明は、当初の設計者を介在させずに、当初の設計までさかのぼる製造歩留まり改善ループ（図2、図3）を備えている。このループは、製造環境においてリアルタイムに実行することができ、あるいは、マスクを新たに組み込む場合に適用することもできる。このフローの利点は、製造／設計のフィードバックループを、現在よりも、タイトな、的を絞ったループにしている点にある。ある設計に対し、コスト目標を設定することができ、レイアウトのサイズ（ウェハ当たりのチップ）対歩留まりは、その目標を達成するために、設計およびプロセスの期間にわたって自動的に調整することができる。

#### 【0023】

「マスクレスリソグラフィ」業界において、この最適化は、製造のバッチ間で適用されることが考えられる。また、「マスク」業界では、この最適化は、新しいマスクセットが必要とされるときには必ず用いられるはずである。マスク寿命が限られていることを考慮すれば、長期にわたる設計の場合、複数のマスクセットを使用することも考えられる。

#### 【0024】

##### B. 選択的スケーリング方法

基本寸法が正しい階層IC設計レイアウト、および周知の問題を示す製造からのフィードバックを考慮して、設計レイアウトは、各オブジェクトごとのスケーリングファクタ、すなわち、層、領域および／またはセル固有の値によってスケーリングされる。

#### 【0025】

##### 1. スケーリング技法

選択的スケーリングでは、スケーリングされる PARTS に応じて異なるスケーリング技法を実施してもよい。本発明の目的上、3つの異なるスケーリング技法について説明する。ただし、現在周知の他のスケーリング技法、または、後に開発されるスケーリング技法が、実施されてもよい。3つのスケーリング技法とは、フラットスケーリング、最小摂動圧縮、およびカスタム回路のスケーリングである。これらのスケーリング技法はそれぞれ、他の米国特許出願に詳細に記載されているか、あるいは当業者に周知であることから、ここでは、その詳細な説明を省略する。

#### 【0026】

##### a) フラットスケーリング

ライブラリ要素のフラットスケーリングは、「A Practical Method for Hierarchical-Preserving Layout Optimization of Integrated Circuit Layout」という名称の米国特許出願第10/438,625号に記載される技法を使用して、異なる層／領域について適切なスケールファクタを使用してデータがスケーリングされる。

#### 【0027】

##### b) 最小摂動圧縮

定義された境界を持つ（たとえば、RLM、ビットスタック）回路の場合、最小摂動（以下、「Minpert」）圧縮と呼ばれる最長経路解析は、それぞれのサブセルが大きくなる量を計算するのに使用されてもよい。Minpert圧縮は、「Circuit Area Minimization Using Scaling（スケーリングによる回路領域最小化）」という名称の米国特許出願第10/707,287号に記載され、この米国特許出願は、ここでの参照により組み込まれたものとする。この技法では、それぞれのサブセルの配置ロケーションは、拡大後に、境界形状が隣接するように修正される。こうして、それぞれのマクロ回路が、階層的にスケーリングされる。

#### 【0028】

##### c) カスタム回路のスケーリング

純正のカスタム回路について言えば、マクロ回路は、通常、2つのパスでスケーリングされる。第1パスのスケーリングでは、形状およびトランスマッピングを修正する。「トランスマッピング」とは、X値、Y値、ミラー値、および回転値による回路のロケーションのことを言う。たとえば、回路は、X軸の周りにミラーリングした、 $X = 5$ 、

10

20

30

40

50

$Y = 4$ 、および $90^\circ$ 回転値のロケーションを有してもよい（この例では、点5, 4の形状頂点は、最初に、ミラーリングにより5, -4に移動し、次に、 $+90^\circ$ 回転したときに、4, 5に移動する）。トランスフォームロケーション修正により、形状の輪郭が変更され、したがって、その近傍に対する位置が変化する。第2パスでは、トランスフォームロケーションは、整数値に丸められ、レイアウトオプティマイザを使用して、すなわち、近傍形状要求に対処するために、基本寸法フィックスアップが実行される。

#### 【0029】

##### 2. 選択的スケーリング技法

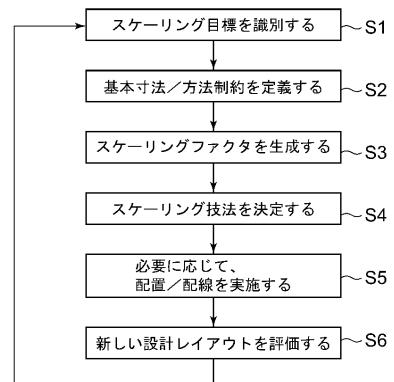

図2を参照し、本発明の一実施形態によるシステム100の動作手順について以下に説明する。ステップS1において、製造からの情報に基づき、設計レイアウトの少なくとも1つのオブジェクトに対する少なくとも1つのスケーリング目標が、スケーリング目標識別子126によって識別される。本明細書で使用される「オブジェクト」は、設計レイアウトの層、領域、および/またはセル（すなわち、1つまたは複数の層、1つまたは複数の領域、1つまたは複数のセル、あるいは、それらの組み合わせ）を意味する。また、本明細書で用いられているように、「セル」は、マクロ、セル、サブセルなどと呼ばれることがある、IC設計の任意の配置可能なパートである。さらに、場合によっては、「オブジェクト」は、チップ全体を含んでいてもよい。このステップは、たとえば、製造プロセスおよび歩留まりの問題に精通した人による、層、領域、および/またはセルの手動識別を含んでいてもよい。あるいは、このステップは、歩留まりの問題を引き起こし、スケーリングの対象となるような、層、領域、および/またはユニットを識別できる、現在周知の、または、後に開発される、任意の自動故障解析システムによって実行されてもよい。さらに、ステップS1では、どの程度のスケーリングが、理想的に必要とされるかを判定する。「製造情報」は、オブジェクトに対するスケーリング目標を識別するのに有効な任意の情報である。製造情報については、以下により詳細に説明する。製造が困難なことで知られている、設計に関連するレイアウトパターン、あるいは、プロセスに関連する欠陥、たとえば、うまく印刷されない、回路、ビア、または特定レベルの他の構造体に関連するかどうかに関わらず、問題のあるオブジェクトが識別される。

#### 【0030】

ステップS2において、技術上の基本寸法は、スケーリング目標を有する各オブジェクトに対して定義される。このステップは、スケーリングが単なる層以上のものに適用されることから、必要である。たとえば、配線またはピンなどのオブジェクトに適用するスペーシングの基本寸法が、定義され、これに従わなければならない。さらに、方法制約が定義される。たとえば、拡大、ピン形状、ピン位置、配線トラックなどを制限するセル境界が定義される。

#### 【0031】

ステップS3では、スケーリング目標を有する各オブジェクトに対し、スケーリングファクタが求められる。「スケーリングファクタ」は、現在周知の、または、後に開発される設計を変更する任意の形態を探ることができる。たとえば、スケーリングファクタは、補正係数（たとえば、このユニットを3%だけ大きくする）、新規の基本寸法（たとえば、この層についての間隔を2nmだけ変更する）、スケーリング乗数（たとえば、この層上のユニットを0.011の倍率で縮小する）などのうちの1つまたは複数であってよい。

#### 【0032】

ステップS4では、複数のスケーリング技法のうちの、少なくともどの1つの技法が、各オブジェクトに適用されるか判定が行われる。たとえば、階層構造の無いフラットセル（たとえば、ライブラリセル）の場合、オブジェクトは、フラットスケーリング技法を使用してスケーリングされてもよい。すなわち、領域は、フラットスケーリング技法に従って、平坦化され、階層構造を確定し、スケーリングが行われる。オブジェクトは、たとえば、X-Y空間を有する領域であってよい。オブジェクトは、スケーリングが施されるあるロケーションやスケーリングが施されない別のロケーションに配置されてもよく、ある

10

20

30

40

50

いは、別のスケーリングファクタによってスケーリングされてもよいことから、各オブジェクトが、個々に評価されることが分かる。別の例では、隣接する境界形状を有するサブセルのインスタンスから構成される、境界方法に制約のあるセルがある。この場合、Min Pert圧縮スケーリング技法が適切と考えられる。純正のカスタム回路は、純正回路スケーリング技法により、すなわち、2パスでスケーリングされる。

#### 【0033】

ステップS5では、上述した方法が、a)リアセンブルされたオブジェクトおよびチップに適用されるか、または、b)アセンブルされた回路全体に適用されるかに応じて、2つの異なる操作が行われる。前者の場合、標準的な配置および配線技術を用いて、スケーリングされたオブジェクトをアセンブルする。一実施形態によれば、このステップにおいて、各オブジェクトに対して正しいレイアウトを生成するために、最適化ベースの階層プログラムを使用する。後者の場合、選択的スケーリングが、アセンブルされた回路全体に適用される。すなわち、チップがオブジェクトであり、配置および配線を再実行する必要性がなくなる。

#### 【0034】

ステップS6は、任意選択のステップを表し、このステップでは、評価子134によって新規の設計レイアウトを評価して、予想される挙動が得られるかどうかを判定する。評価子134は、新規の設計レイアウトを古い設計レイアウトと比較するソフトウェアおよび/またはハードウェアと、設計意図情報（以下に定義する）を提供するシミュレータと、予想される挙動が得られることを検証するチェックツールを含んでいてもよい。このステップは、新しい設計層が、事実上生成された後、または、製造実行後に実行される。その後、このプロセスは、図2に示すように繰り返される。

#### 【0035】

##### 3. 実施例

以下の実施例は、包括的なものではなく、したがって、添付した特許請求の範囲を限定するものではない。第1実施例では、設計内の特定のライブラリセルが、ある一定レベルのスケーリングを必要とする。第2実施例では、特定の冗長ビアセルが含まれている。たとえば、特定のビア配列により、歩留まりの問題（おそらく、光近接効果補正（OPC）の問題による）が発生することが明らかになった場合、この特定モデルのスペーシングまたは配列を、その発生ごとに変更することができる（OPCは、マスクが作られる直前に適用される、形状の印刷を改善するための技法である。OPCでは、光作用および使用される短い光波長のために印刷が難しい構造体に対して加算または減算を行う。たとえば、「L」の屈曲部のような内角は、印刷時にわずかに潰れる傾向があるため、こうした角部は、小さなノッチが切り抜かれる。回線の端部のような外角は、丸くなる傾向があるため、外角には、小さな余分のバンプが追加される。）。第3実施例は、チップ内の特定の金属層（たとえば、M1）のみに関する問題が観測される場合である。この場合、その金属層だけのチップ幅スケーリングが必要である。

#### 【0036】

##### C. 歩留まり学習に対する選択的スケーリングの適用

上述した方法は、連続的に、または、新しいマスクが、以下の方法により生成されるときに、製造システム400内で歩留まり学習に使用することができる。以下の方法は、上述したステップS1の一部として発生する。製造システム400は、スケーリングシステム100として、同様なコンピュータベースのサブシステム構造（すなわち、PU、I/O、バス、プログラム製品など）を含んでいてもよい。

#### 【0037】

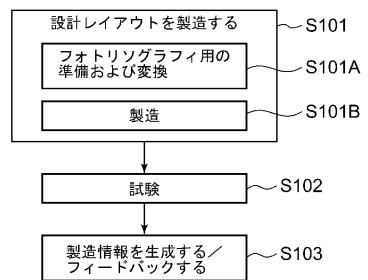

図3を参照すると、ステップS101において、設計レイアウトが、従来の製造機器402によって製作される。このステップは、フォトリソグラフィ用に設計レイアウトを準備するサブステップS101A、すなわち、ツール用のマスクまたはマスクレスデータのための従来のデータ準備および変換を含む。このステップは、製造組織に対する設計者による設計「意図」情報の提供を含んでいてもよい。この意図情報は、実際のレイアウト形

10

20

30

40

50

状に対する変更のシミュレーション中に使用され、これにより、小さなレイアウト変更が行われる場合に正しい性能および機能が確保される。たとえば、性能 / 調整情報および / または電力情報を提供することができる。特に、レイアウトは、I C がどのように動的に機能するかではなく、I C がどのように静的に働くか、すなわち、クロック周期において、どれほど速く、または、どれほど多く、電力が消費されるかを示す。意図情報は、レイアウトからの静的挙動推論や、性能および電力などの予想される動的挙動に関するデータを含んでいてもよい。さらに、隣接回路に対する雑音または回路のグループ化は、1 つの意図情報になり得る。回路のグループ化は、回路が、全て同時に切り換わらないように構成されていることを示している。これは、回路が全て同時に切り換わった場合、特定の電力バス上で大幅な電圧降下が生じるため、一部の回路が正常に機能しなくなる場合があるからである。サブステップ S 101B において、パーツが製造される。ステップ S 102 では、従来の試験機器 404 によって、試験が行われる。一実施形態において、試験では、オブジェクトまたはフィーチャを、いかにうまく製造できるかを示すデータを取得することによって、動作の特徴づけを行う。たとえば、ラインモニタ（たとえば、カーフまたは特別なウェハ）により、埋め込まれた回線を特定のピッチで印刷するプロセスの能力を測定してもよい。別の例では、カーフ構造により、印刷適性について、ある一定の種類のビアの組み合わせの性能を監視することができる。

#### 【 0038 】

ステップ S 103 にて、製造情報は、製造情報（M I）発生器 406 によって生成され、現在周知の、または、後に開発される任意の通信機構 408、たとえば、ネットワークによって、システム 100 にフィードバックされる。M I 発生器 406 は、たとえば、一定のパラメータが閾値を一つ超えるかを判定する機構を含む、製造情報を生成する任意の機構を含んでいてもよい。パラメータによって、製造情報は、たとえば、a) 層上の許容できない欠陥のために、より大きなサイズまたはピッチに拡大スケーリングされるべき層、b) 予想外に製造容易性が良好であるために、より小さなサイズまたはピッチへの縮小スケーリングが可能な層、c) 特定の領域内のシステムティック欠陥を最小化するために、より大きなサイズに拡大スケーリングされるべき設計の領域、d) 領域内で欠陥密度が予想外に低いために、より小さなサイズへの縮小スケーリングが可能な設計の領域、e) 不適切な相互作用のために、互いに隣接して配置できないセル、および / または、f) 近傍セルとより無関係であるか、または、近傍セルに耐性があるように、互いに隣接して配置されるために、修正を必要とするセルを含んでもよい。ラインモニタが、埋め込まれた回線を特定のピッチで印刷するプロセスの能力を測定する上述した例について言えば、印刷可能なピッチがわずかにドリフトする場合、上記の選択的スケーリングを使用して、設計に用いられる実際のピッチを狭めたり広げたりすることができるよう、製造情報を生成することができる（次のステップ）。行われる変更の増分は、非常に小さく、すなわち、通常、基本寸法の変更を考慮した増分（たとえば、~10 nm）を下回る。同様に、カーフ構造により、印刷適性について、ある一定の種類のビアの組み合わせの性能を監視する場合、製造情報により、プロセスの変更に応じて、ビアの変更、たとえば、微妙な拡大またはスペーシングの変更が必要であることを示すことができる。製造情報は、フィードバックされ、上述した選択的スケーリング方法により製造された現行のレイアウトに適用される。先に説明したように、製造情報は、問題のあるオブジェクトに対してスケーリング目標を識別するのに用いられる。

#### 【 0039 】

この歩留まり学習プロセスは、設計を新しい第 2 の作製設備に移行させる場合に、特に役立つ場合がある。第 2 の作製設備は、一部の基本寸法値について、「最適」点が微妙に異なる可能性が高い。時間の経過に伴い、このような最適点が検出され、パーツが、このような別の作製設備に対して最適化されるようになる。

#### 【 0040 】

##### I I I . 結論

先の説明では、説明した方法ステップは、メモリに記憶された、プログラム製品 122

10

20

30

40

50

の命令を実行する、システム 100 の P U 114 などのプロセッサによって実行されることが理解されるであろう。本明細書に述べる、種々のデバイス、モジュール、機構、およびシステムは、ハードウェア、ソフトウェア、またはハードウェアとソフトウェアの組み合わせにおいて実現されてもよく、また、図示する以外の方法で区分化されてもよいことが理解される。それらは、任意のタイプのコンピュータシステム、または、本明細書に述べる方法を実行するように構成された他の装置によって実現されてもよい。ハードウェアとソフトウェアの代表的な組み合わせは、コンピュータプログラムを有する汎用コンピュータシステムでもよい。また、このコンピュータプログラムは、ロードされ実行されると、コンピュータシステムが本明細書に述べる方法を実行するように、コンピュータシステムを制御する。あるいは、本発明の機能タスクの 1 つまたは複数を実行する特殊なハードウェアを含む特殊用途のコンピュータを利用してよい。本発明はまた、コンピュータプログラム製品内に組み込むことができ、コンピュータプログラム製品は、本明細書に述べる方法および機能の実施を可能にする全ての特徴を有し、また、コンピュータシステム内にロードされると、これらの方法および機能を実行することができる。コンピュータプログラム、ソフトウェアプログラム、プログラム、プログラム製品、またはソフトウェアは、本文脈において、情報処理機能を有するシステムに、直接、あるいは、( a ) 別の言語、コード、または記号への変換後、かつ / または、( b ) 異なる素材形態での再生後に、特定の機能を実行させることを目的とした一連の命令に関する、任意の言語、コード、または記号での、任意の表現を意味している。

#### 【 0 0 4 1 】

本発明は、先に概説した特定の実施形態に関連して述べられたが、多くの代替、修正、および変形が可能なことは、当業者に明らかである。したがって、先に述べた本発明の実施形態は、例示のために示されたものであり、限定的に解釈されるものではない。添付特許請求項に規定される本発明の趣旨および範囲から逸脱することなく、種々の変更が行われてもよい。

#### 【 図面の簡単な説明 】

#### 【 0 0 4 2 】

【 図 1 】本発明の一実施形態による、選択的スケーリングシステムおよびスケーリングシステムから利益を得る製造システムのブロック図である。

【 図 2 】図 1 のシステムの動作方法のフロー図である。

【 図 3 】図 1 の製造システムの動作のフロー図である。

10

20

30

【図1】

【図2】

【図3】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 ヘン、フルン

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ パーク・レーン 1265

(72)発明者 ハイベラー、ジェイソン、ディー

アメリカ合衆国 05495 ヴァーモント州ウィリストン サドラー・レーン 47

(72)発明者 マクレン、ケヴィン、ダブリュ

アメリカ合衆国 05452 ヴァーモント州エセックス・ジャンクション ブライア・レーン 6

4

(72)発明者 ナラヤン、ラニ、アール

アメリカ合衆国 95120 カリフォルニア州サンノゼ クワイル・クリーク・サークル 1087

(72)発明者 ランヨン、スティーヴン、エル

アメリカ合衆国 78660 テキサス州フルーガヴィル セイジ・ブート・ドライブ 402

(72)発明者 ウォーカー、ロバート、エフ

アメリカ合衆国 05495 ヴァーモント州セント・ジョージ マウント・プリチャード・レーン

235

審査官 大嶋 洋一

(56)参考文献 特開 2004-031676 (JP, A)

特開 2003-031661 (JP, A)

国際公開第 00/079595 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82

G03F 1/08