(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4577497号

(P4577497)

(45) 発行日 平成22年11月10日(2010.11.10)

(24) 登録日 平成22年9月3日(2010.9.3)

(51) Int.Cl.

H01L 33/00 (2010.01)

F 1

H01L 33/00

Z

請求項の数 21 (全 22 頁)

(21) 出願番号 特願2005-14734 (P2005-14734)

(22) 出願日 平成17年1月21日 (2005.1.21)

(65) 公開番号 特開2006-66863 (P2006-66863A)

(43) 公開日 平成18年3月9日 (2006.3.9)

審査請求日 平成19年3月16日 (2007.3.16)

(31) 優先権主張番号 特願2004-26102 (P2004-26102)

(32) 優先日 平成16年2月2日 (2004.2.2)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2004-217715 (P2004-217715)

(32) 優先日 平成16年7月26日 (2004.7.26)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000106276

サンケン電気株式会社

埼玉県新座市北野3丁目6番3号

(74) 代理人 100072154

弁理士 高野 則次

(72) 発明者 佐藤 純治

埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内

(72) 発明者 大塚 康二

埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内

(72) 発明者 李 哲次

埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内

最終頁に続く

(54) 【発明の名称】半導体発光素子と保護素子との複合半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の主面と該第1の主面に対向する第2の主面とを有し且つ導電性を有している基板と、

光取り出し可能な第1の主面と該第1の主面に対向し且つ前記基板の前記第1の主面に電気的及び機械的に結合されている第2の主面とを有し、且つ半導体発光素子を構成するための複数の半導体層を含む主半導体領域であって、該主半導体領域の前記第1の主面から該主半導体領域の前記第2の主面に至る孔を有している主半導体領域と、

前記主半導体領域の前記第1の主面に接触し且つ前記主半導体領域から放射された光を取り出すことができるよう形成されている第1の部分と、平面的に見て前記第1の部分に隣接していると共に前記主半導体領域の前記孔を覆っており且つ前記第1の部分に接続され且つ前記主半導体領域に支持され且つパッド電極機能を有している第2の部分とを備えている第1の電極と、

前記基板の前記第1の主面又は前記基板の前記第2の主面に接続された第2の電極と、前記基板の一部を使用して形成された過電圧保護素子、又は前記主半導体領域の前記孔の中に配置された個別の過電圧保護素子、又は前記基板の一部と該一部の上に配置された半導体膜とか成る過電圧保護素子であって、平面的に見て前記第1の電極の前記第2の部分に覆われ、且つ前記主半導体領域に形成された前記半導体発光素子に対して並列に接続されている保護素子と

を備えていることを特徴とする半導体発光素子と保護素子との複合半導体装置。

**【請求項 2】**

前記基板は半導体基板であり、

前記保護素子は、前記半導体基板に設けられたショットキーバリアダイオード形成領域と、前記ショットキーバリアダイオード形成領域にショットキー接触し且つ前記第1の電極に接続され且つ前記第1の電極の前記第2の部分と前記基板の第1の主面との間に配置されている金属層とから成ることを特徴とする請求項1記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 3】**

前記基板は半導体基板であり、

前記保護素子は前記半導体基板に形成された1つのp n接合を含むダイオードであり、

前記ダイオードは第1導電型半導体領域と、前記第1導電型半導体領域の中に島状に形成され且つ前記半導体基板の前記第1の主面に露出する表面を有している第2導電型半導体領域とから成り、

前記第2導電型半導体領域の少なくとも一部が前記第1の電極の前記第2の部分と前記半導体基板の前記第2の主面との間に配置され、

前記第1の電極の前記第2の部分は前記第2導電型半導体領域にオーミック接触していることを特徴とする請求項1記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 4】**

前記基板は半導体基板であり、

前記保護素子は前記半導体基板に形成された2つのp n接合を含む3層ダイオードであり、

前記3層ダイオードは、第1導電型を有する第1の半導体領域と、前記第1の半導体領域の中に島状に形成され且つ前記半導体基板の前記第1の主面に露出する表面を有し且つ第2導電型を有している第2の半導体領域と、前記第2の半導体領域の中に島状に形成され且つ前記半導体基板の前記第1の主面に露出する表面を有し且つ第1導電型を有している第3の半導体領域とから成り、

前記第3の半導体領域の少なくとも一部が前記第1の電極の前記第2の部分と前記半導体基板の前記第2の主面との間に配置され、

前記第1の電極の前記第2の部分は前記第3の半導体領域にオーミック接触していることを特徴とする請求項1記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 5】**

前記保護素子は前記第1の電極の前記第2の部分と前記基板の第1の主面との間に配置されていることを特徴とする請求項1記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 6】**

前記保護素子は前記基板の第1の主面上に配置されコンデンサ機能を有する誘電体層であり、前記誘電体層の一方の主面は前記基板に接触し、前記誘電体層の他方の主面は前記第1の電極の前記第2の部分に接触していることを特徴とする請求項5記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 7】**

前記保護素子は、更に、前記誘電体層の一方の主面と他方の主面との少なくとも一方にコンデンサ電極を有することを特徴とする請求項6記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 8】**

前記保護素子は前記半導体基板の第1の主面上に配置されバリスタ機能を有する半導体層であり、前記バリスタ機能を有する半導体層の一方の主面は前記基板に接触し、前記バリスタ機能を有する半導体層の他方の主面は前記第1の電極の前記第2の部分に接触していることを特徴とする請求項5記載の半導体発光素子と保護素子との複合半導体装置。

**【請求項 9】**

前記保護素子は、更に、前記バリスタ機能を有する半導体層の一方の主面と他方の主面と

10

20

30

40

50

の少なくとも一方にバリスタ電極を有することを特徴とする請求項 8 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 0】

前記保護素子はバリスタ機能とコンデンサ機能との両方を有する素子であることを特徴とする請求項 5 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 1】

前記基板は第 1 導電型を有する半導体基板であり、

前記保護素子は、前記半導体基板の一部と、前記半導体基板の前記一部の上に形成され且つ前記第 1 の導電型と反対の第 2 導電型を有する半導体薄膜とから成ることを特徴とする請求項 1 記載の半導体発光素子と保護素子との複合半導体装置。

10

【請求項 1 2】

前記基板は第 1 導電型を有する半導体基板であり、

前記保護素子は、前記半導体基板の上に形成された第 1 導電型半導体薄膜と、この第 1 導電型半導体薄膜の上に形成され且つ前記第 1 の電極の前記第 2 の部分に接続された第 2 導電型半導体薄膜とから成ることを特徴とする請求項 1 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 3】

前記基板は第 1 導電型の半導体基板であり、

前記保護素子は、前記半導体基板の上に配置された第 1 導電型の第 1 の半導体薄膜と、前記第 1 の半導体薄膜の上に配置された第 2 導電型の第 2 の半導体薄膜と、前記第 2 の半導体薄膜と前記第 1 の電極の前記第 2 の部分との間に配置された第 1 導電型の第 3 の半導体薄膜とから成ることを特徴とする請求項 1 記載の半導体発光素子と保護素子との複合半導体装置。

20

【請求項 1 4】

前記基板は第 1 導電型半導体基板であり、

前記保護素子は、前記半導体基板の前記第 1 の主面に露出するように前記半導体基板の一部に形成された第 2 導電型半導体領域と、前記第 2 導電型半導体領域と前記第 1 の電極の第 2 の部分との間に配置された第 1 導電型半導体薄膜とから成ることを特徴とする請求項 1 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 5】

30

前記第 1 の電極の前記第 2 の部分の少なくとも一部が前記孔の中に配置されていることを特徴とする請求項 1 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 6】

前記第 1 の電極の前記第 1 の部分は前記主半導体領域の前記第 1 の主面に接続された光透過性を有する導電膜であることを特徴とする請求項 1 乃至 1\_4 のいずれかに記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 7】

前記第 1 の電極の前記第 1 の部分は前記主半導体領域の前記第 1 の主面の一部に接続されていることを特徴とする請求項 1 乃至 1\_4 のいずれかに記載の半導体発光素子と保護素子との複合半導体装置。

40

【請求項 1 8】

前記第 1 の電極の前記第 1 の部分は前記主半導体領域の前記第 1 の主面の一部に接続された帯状導体であることを特徴とする請求項 1 乃至 1\_4 のいずれかに記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 1 9】

前記主半導体領域の前記孔の壁面と前記第 1 の電極の前記第 2 の部分との間に絶縁膜が配置されていることを特徴とする請求項 1\_5 記載の半導体発光素子と保護素子との複合半導体装置。

【請求項 2 0】

前記主半導体領域の第 1 の主面に対して垂直な方向から見て、前記保護素子の面積の 7

50

0～100%の部分が前記孔の範囲を超えないように配置されていることを特徴とする請求項1乃至14のいずれかに記載の半導体発光素子と保護素子との複合半導体装置。

#### 【請求項21】

前記基板はシリコン又はシリコン化合物から成り、前記主半導体領域は複数の3～5族化合物半導体層から成ることを特徴とする請求項1乃至14のいずれかに記載の半導体発光素子と保護素子との複合半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は半導体発光素子とこれを保護するための保護素子との複合半導体装置に関する。 10

##### 【背景技術】

##### 【0002】

近年、半導体発光素子として、窒化物半導体材料を使用した発光素子が注目されている。この発光素子によれば、365nm～550nm程度の範囲内の波長の光を発光させることができる。

##### 【0003】

ところで、この種の窒化物半導体材料を使用した発光素子は、静電破壊耐量が比較的小さく、例えば100Vよりも高いサージ電圧が印加されると、破壊に到ることがある。静電保護の為、発光素子と共にダイオードやコンデンサ等の保護素子を同-パッケージ内に搭載することが考えられるが、部品点数が増大する。この問題を解決するために、単一の半導体基板内に発光素子と保護素子を集積化することが特許文献1及び特許文献2において提案されている。即ち、特許文献1には、サファイア基板上に発光素子と保護用ダイオードとを設け、保護用ダイオードを発光素子に並列接続することが開示されている。また、特許文献2には、サファイア基板上に形成された発光素子の上に保護用コンデンサを配置し、保護用コンデンサを発光素子に並列接続することが開示されている。 20

##### 【0004】

しかし、特許文献1及び2に記載の半導体発光装置では、保護素子を構成する領域が非発光領域となるため、半導体素子に占める有効発光面積が小さくなる。換言すれば、所望の発光強度を有する半導体発光装置を得るためにには、素子の平面サイズが大きくなる。 30

また、発光素子と保護素子とを電気的に接続するための配線導体が必要であり、素子構造が複雑になる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0005】

本発明が解決しようとする課題は、保護素子を伴なった半導体発光装置の小型化を図ることが困難なことである。

##### 【課題を解決するための手段】

##### 【0006】

上記課題を解決するための本発明は、

一方の主面と他方の主面と有し且つ導電性を有している基板と、 40

光取り出し可能な第1の主面と前記第1の主面に対向し且つ前記基板の前記一方の主面に電気的及び機械的に結合されている第2の主面とを有し且つ半導体発光素子を構成するための複数の半導体層を含んでいる主半導体領域と、

前記主半導体領域の前記第1の主面に接触し且つ前記主半導体領域から放射された光を取り出すことができるよう形成されている第1の部分と前記第1の部分に接続され且つパッド電極機能を有している第2の部分とを備えている第1の電極と、

前記基板に接続された第2の電極と、

前記第1の電極の前記第2の部分と前記基板の他方の主面との間に配置され且つ前記第1の電極と前記第2の電極との間に電気的に接続されている保護素子と

50

を備えていることを特徴とする半導体発光素子と保護素子との複合半導体装置に係わるものである。

本発明における光は前記主半導体領域から放射する光を意味する。また、前記パッド電極とはワイヤ等の導体を接続するための電極を意味する。

【0007】

なお、前記基板は半導体基板又は導電性を有する基板であることが望ましく、シリコン基板であることが最も望ましい。

また、前記保護素子は、ショットキーバリアダイオード、1つのpn接合を含むダイオード、2つのpn接合を含む3層ダイオード、コンデンサ、及びバリスタから選択された1つ又は複数から成ることが望ましい。前記保護素子は、例えば、個別素子、半導体基板、厚膜誘電体、厚膜半導体、厚膜コンデンサ、厚膜導体、薄膜誘電体、薄膜半導体、薄膜コンデンサ、及び薄膜導体から選択された1つ又は複数で形成することができる。10

また、前記保護素子を前記基板の内部に設けるか、又は前記第1の電極の前記第2の部分と前記基板の一方の主面との間に配置することが望ましい。

また、前記主半導体領域は、前記主半導体領域の前記第1の主面から前記第2の主面に至る孔を有し、前記第1の電極の前記第2の部分の少なくとも一部が前記孔の中に配置されていることが望ましい。また、前記主半導体領域の前記孔の中に保護素子の一部又は全部を配置することができる。

また、前記第1の電極の前記第1の部分は前記主半導体領域の第1の主面に接続された光透過性を有する導電膜であることが望ましい。20

また、前記第1の電極の前記第1の部分を、前記主半導体領域の第1の主面の一部に接続された導体、例えば前記第1の電極のパッド電極機能を有する前記第2の部分の外周側の下部、とすることができます。

また、前記第1の電極の前記第1の部分を、前記主半導体領域の第1の主面の一部に接続された帯状導体とすることができます。また、前記第1の電極の前記第1の部分を光取り出し可能な種々のパターンにすることができます。

また、前記主半導体領域の前記孔の壁面と前記第1の電極との間に絶縁膜が配置されていることが望ましい。

また、前記主半導体領域の第1の主面に対して垂直な方向から見て、前記保護素子の面積の70～100%が第1の電極の前記第2の部分の内側に配置されていることが望ましい。30

また、前記半導体基板はシリコン又はシリコン化合物から成り、前記主半導体領域は複数の3-5族化合物半導体層から成ることが望ましい。

【発明の効果】

【0008】

本発明は次の効果を有する。

(1) 保護素子の少なくとも一部が、平面的に見て、即ち基板の一方の主面に対して垂直な方向から見て、第1の電極のパッド電極機能を有している第2の部分の下に配置されている。従って、半導体発光素子の光取り出し面積の低減を抑制して保護素子を形成することができ、半導体発光素子と保護素子との複合半導体装置の小型化を図ることができる。40

(2) 第1の電極のパッド電極機能を有している第2の部分は半導体発光素子の外部接続部分として機能する他と共に、半導体発光素子と保護素子との相互接続部分としても機能するので、半導体発光素子の一方の端と保護素子の一方の端との相互接続が容易に達成される。従って、半導体発光素子と保護素子との複合半導体装置の構成が単純化され、小型化及び低コスト化が達成せれる。

(3) 導電性を有している基板が使用されているので、基板によって半導体発光素子の他方の端と保護素子の他方の端との相互接続が容易に達成される。従って、半導体発光素子と保護素子との複合半導体装置の構成が単純化され、小型化及び低コスト化が達成せれる。

## 【発明を実施するための最良の形態】

## 【0009】

次に、図1～図17を参照して本発明の実施形態を説明する。

## 【実施例1】

## 【0010】

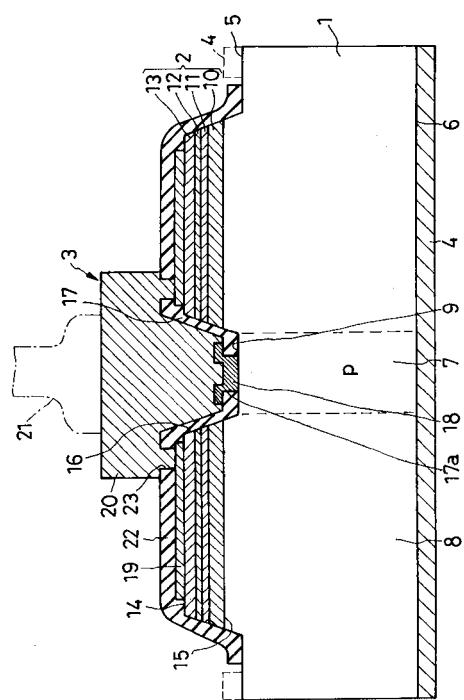

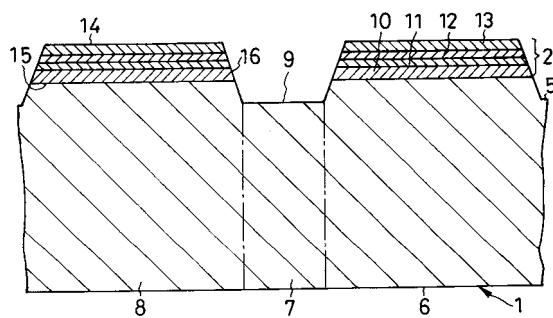

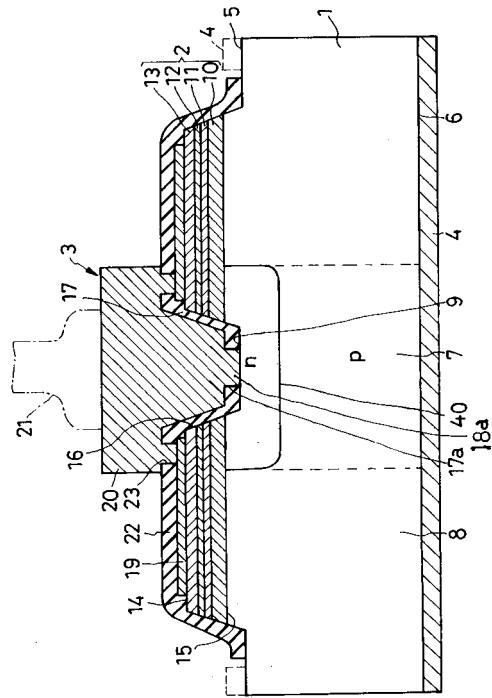

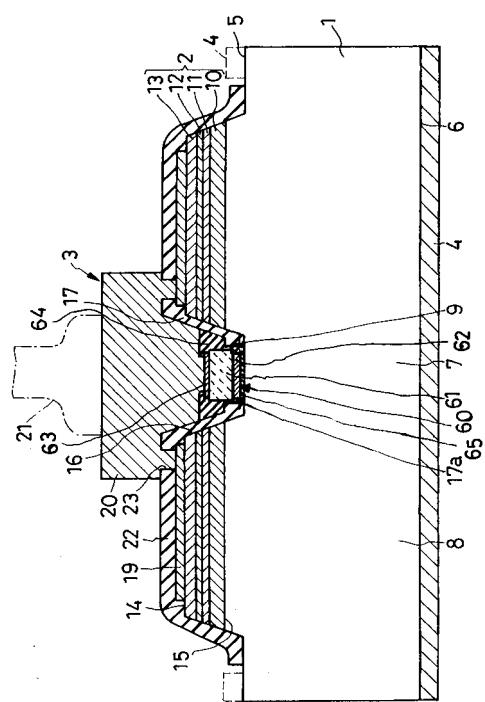

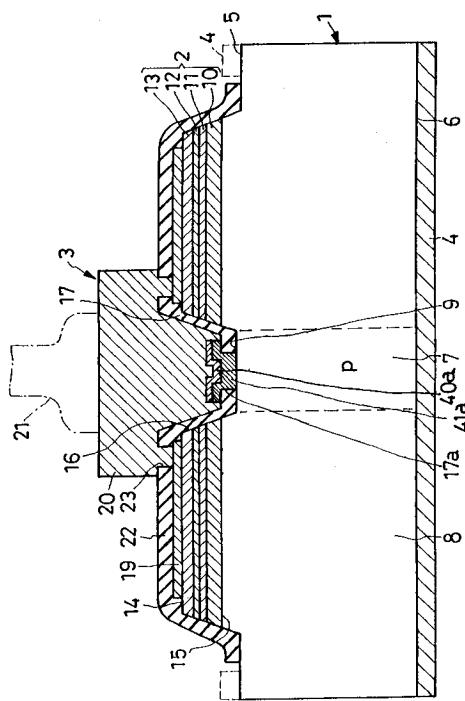

図1に示す本発明の実施例1に従う発光素子としての発光ダイオードと保護素子としてのショットキーバリヤダイオードとの複合半導体装置は、半導体基板1と、発光素子を構成するための主半導体領域2と、第1の電極3と、第2の電極4とを備えている。半導体基板1の外側領域8と主半導体領域2と第1の電極3と第2の電極4とから成る部分を発光素子部又は発光素子と呼び、且つ半導体基板1の保護素子形成領域7とショットキー接觸金属層18とから成る部分を保護素子部又は保護素子と呼ぶことができる。10

## 【0011】

半導体基板1は導電型決定用不純物としてボロン等の3族元素を含むp型単結晶シリコン基板から成り、一方の正面5と他方の正面6とを有し且つほぼ中央に保護素子形成領域7を有している。半導体基板1の主半導体領域2側の一方の正面5は、ミラー指数で示す結晶の面方位において(111)ジャスト面である。半導体基板1のp型不純物濃度は、例えば $5 \times 10^{18} \sim 5 \times 10^{19} \text{ cm}^{-3}$ 程度あり、抵抗率は0,0001 · cm ~ 0.01 · cm程度である。

従って、半導体基板1は導電性基板であり、発光素子及び保護素子の電流通路として機能する。即ち、半導体基板1の中央の保護素子形成領域7はショットキーバリヤダイオードの本体部としても機能すると共にこの電流通路として機能し、また半導体基板1の保護素子形成領域7を囲む外側領域8は発光素子の電流通路として機能する。更に、半導体基板1は、主半導体領域2のエピタキシャル成長のための基板としての機能、及び発光素子を構成するための主半導体領域2と第1の電極3との支持体としての機能を有する。半導体基板1の好ましい厚みは比較的厚い200~500 μmである。なお、図1及び図3から明らかなように半導体基板1の一方の正面5の外周部分に段差が形成され且つ中央に凹部9が形成されているが、半導体基板1の一方の正面5の全部を平坦にすることができる。また、半導体基板1の導電型をn型にすることができる。また、半導体基板1の外側領域8の不純物濃度を保護素子形成領域7よりも高くし、これにより、外側領域8の抵抗率を保護素子形成領域7よりも低くし、発光素子の動作時の外側領域8における電圧降下を低減することができる。30

## 【0012】

発光素子の主要部を構成するための主半導体領域2は、シリコン半導体基板1と異種の3-5族化合物半導体から成る複数の層を有し、シリコン半導体基板1の上に周知の気相成長法によって形成されている。更に詳細には、主半導体領域2は、ダブルヘテロ接合発光ダイオードを構成するためにn型バッファ層10とn型半導体層11と活性層12とp型半導体層13とを順次に有している。なお、n型半導体層11をn型クラッド層と呼び、p型半導体層13をp型クラッド層と呼ぶことがある。発光ダイオードは原理的にn型半導体層11とp型半導体層13のみで構成できる。従って、主半導体領域2からn型バッファ層10と活性層12とのいずれか一方又は両方を省くことができる。また、必要に応じて周知の電流拡散層又はオーミックコンタクト層等を主半導体領域2に付加することができる。主半導体領域2の第1の正面14及び第2の正面15は半導体基板1に平行に延びている。主半導体領域2の第1の正面14は活性層12で発生した光を外部に取り出す面としての機能を有する。主半導体領域2の第2の正面15は半導体基板1に電気的及び機械的に結合されている。40

## 【0013】

図1では図示を簡単にするためにn型バッファ層10が1つの層で示されているが、実際には複数の第1の層と複数の第2の層とから成り、第1の層と第2の層とが交互に配置されている。なお、n型バッファ層10の最も下に第1の層が配置される。

n型バッファ層10の第1の層は、A1(アルミニウム)を含む窒化物半導体であることが望ましく、例えば、50

ここで、前記Mは、In (インジウム) とB (ボロン) とから選択された少なくとも1種の元素、

$$\begin{aligned} \text{前記 } x \text{ 及び } y \text{ は、 } 0 < x & \leq 1, \\ 0 & \leq y < 1, \\ x + y & \leq 1 \end{aligned}$$

を満足する数値、

で示される材料に不純物を添加したものから成る。即ち、第1の層は、例えばAlN (窒化アルミニウム)、AlInN (窒化インジウム、アルミニウム)、AlGaN (窒化ガリウム アルミニウム)、AlInGaN (窒化ガリウム インジウム アルミニウム)、AlBN (窒化ボロン アルミニウム)、AlBGaN (窒化ガリウム ボロン アルミニウム) 及びAlBInGaN (窒化ガリウム インジウム ボロン アルミニウム) から選択された材料から成る。アルミニウムを含む第1の層の格子定数及び熱膨張係数は第2の層よりもシリコン半導体基板1に近い。

第2の層は、バッファ層10の緩衝機能を更に高めるためのものであって、Alを含まないか又はAlの割合が第1の層のAlの割合よりも小さいn型窒化物半導体から成る。この条件を満足させることができると第2の層は、例えば、

ここで、前記MはIn (インジウム) とB (ボロン) とから選択された少なくとも1種の元素、

$$\begin{aligned} \text{前記 } a \text{ 及び } b \text{ は、 } 0 & \leq a < 1, \\ 0 & \leq b < 1, \\ a + b & \leq 1, \\ a & < x \end{aligned}$$

を満足させる数値、

で示される材料にn型不純物を添加したものから成る。即ち、第2の層は、例えばGaN (窒化ガリウム)、AlInN (窒化インジウム、アルミニウム)、AlGaN (窒化ガリウム アルミニウム)、AlInGaN (窒化ガリウム インジウム アルミニウム)、AlBN (窒化ボロン アルミニウム)、AlBGaN (窒化ガリウム ボロン アルミニウム) 及びAlBInGaN (窒化ガリウム インジウム ボロン アルミニウム) から選択された材料から成る。第2の層におけるAl (アルミニウム) の増大により発生する恐れのあるクラックを防ぐためにAlの割合を示すaの値を0 < a < 0.2、即ち0又は0よりも大きく且つ0.2よりも小さくすることが望ましい。

第1の層の好ましい厚みは、0.5nm～5nmである。第1の層の厚みが0.5nm未満の場合には上面に形成される主半導体領域2の平坦性が良好に保てなくなる。第1の層の厚みが5nmを超えると、量子力学的トンネル効果が得られなくなる。第2の層の好ましい厚みは、0.5nm～200nmである。第2の層の厚みが0.5nm未満の場合には上面に形成されるn型半導体層11と活性層12とp型半導体層13の平坦性が良好に保てなくなる。第2の層の厚みが200nmを超えると、バッファ層10にクラックが発生する恐れがある。

この実施例ではp型のシリコン半導体基板1に対してn型のバッファ層10が接触しているが、シリコン半導体基板1とバッファ層10とはヘテロ接合であり且つ両者間に合金化領域(図示せず)が生じているので、順方向バイアス電圧が両者に印加された時のシリコン半導体基板1とバッファ層10との接合部における電圧降下は小さい。なお、p型シリコン半導体基板1の代わりn型シリコン半導体基板を使用し、n型シリコン半導体基板の上にn型のバッファ層10を形成することも勿論可能である。また、バッファ層10を多層構造にしないで、1つの層で形成することも勿論可能である。

【0014】

バッファ層10の上に配置されたn型半導体層11は、

10

20

30

40

50

ここで、前記MはIn(インジウム)とB(ボロン)とから選択された少なくとも1種の元素、

$$\begin{aligned} \text{前記 a 及び b は、 } & 0 \leq a \leq 1, \\ & 0 \leq b < 1, \\ & a + b \leq 1 \\ & a < x \end{aligned}$$

を満足させる数値、

で示される窒化物半導体から成ることが望ましく、GaN等のn型窒化ガリウム系化合物半導体から成ることが更に望ましい。

【0015】

10

n型半導体層11の上に配置された活性層12は、

化学式  $Al_xIn_yGa_{1-x-y}N$ 、

ここでx及びyは  $0 \leq x < 1$ 、

$0 \leq y < 1$ 、を満足する数値、

で示される窒化物半導体から成ることが望ましい。なお、図1では活性層12が1つの層で概略的に示されているが、実際には周知の多重量子井戸構造を有している。勿論、活性層12を1つの層で構成することもできる。また、この実施例では活性層12に導電型決定不純物がドーピングされていないが、p型又はn型不純物をドーピングすることができる。

【0016】

20

活性層12の上に配置されたp型半導体層13は、

化学式  $Al_xIn_yGa_{1-x-y}N$ 、

ここでx及びyは  $0 \leq x < 1$ 、

$0 \leq y < 1$ 、を満足する数値、

で示される窒化物半導体にp型不純物をドーピングしたものから成ることが望ましい。この実施例では、p型半導体層13が厚さ500nmのp型GaNで形成されている。

【0017】

30

主半導体領域2は、第1の主面14から第2の主面15に貫通する孔16をそのほぼ中央に有している。この孔16はシリコン半導体基板1の凹部9に連続している。孔16及び凹部9は、凹部9を形成する前のシリコン半導体基板1の上に主半導体領域2をエピタキシャル成長させた後にエッティングによって形成される。このため、シリコン半導体基板1と主半導体領域2との間に生じた合金化層は除去され、シリコン半導体基板1の凹部9の表面にシリコンが露出する。また、孔16及び凹部9の壁面は主半導体領域2の第1の主面14から第2の主面15に向って先細になるように傾斜している。なお、シリコン半導体基板1の凹部9は保護素子形成領域7に設けられている。また、孔16及び凹部9の壁面を覆うように絶縁膜17が形成されている。

【0018】

30

第1の電極3は、第1の部分としての光透過性導電膜19と、第2の部分としてのボンディングパッド部分20とから成る。ボンディングパッド部分20は光透過性導電膜19に接続されていると共にショットキー接觸金属層18にも接続されている。従って、第2の部分としてのボンディングパッド部分20は外部接続機能の他に光透過性導電膜19と金属層18との相互接続機能を有する。

40

第1の電極3の第2の部分としてのボンディングパッド部分20の外周下部を光透過性導電膜19を介さないで主半導体領域2の第1の主面14にオーミック接觸させ、光透過性導電膜19を省くこともできる。このようにボンディングパッド部分20を主半導体領域2の第1の主面14にオーミック接觸させる場合には、光透過性導電膜19を省いても主半導体領域2に第1の電極3から電流を流すことができる。光透過性導電膜19が省かれる場合には、ボンディングパッド部分20の外周下部が第1の電極3の第1の部分として機能する。光透過性導電膜19は主半導体領域2の全領域に電流を均一に流すために有効である。しかし、光透過性導電膜19の光透過率を100%にすくことは困難又は不可能

50

であり、光透過性導電膜 19 で光の吸収が生じる。また、光透過性導電膜 19 を設けると、必然的に半導体発光素子がコスト高になる。従って、発光効率及びコストを勘案して光透過性導電膜 19 を設けるか否かを決定する。

第1の電極 3 の第1の部分としての光透過性導電膜 19 は発光素子接続部分として機能し、主半導体領域 2 の第1の正面 14 即ち p 型半導体層 13 の表面のほぼ全部に配置され、ここにオーミック接觸している。従って、既に説明したように光透過性導電膜 19 は主半導体領域 2 に電流を均一に流すために寄与し、且つ主半導体領域 2 から放射された光の取り出しを可能にする。光透過性導電膜 19 は厚さ 100 nm 程度の ITO 即ち酸化インジウムと酸化錫との混合物からなる。なお、光透過性導電膜 19 を Ni、Pt、Pd、Rh、Ru、Os、Ir、Au から選択された1種の金属膜、又はこれらから選択された2種の合金膜によっても形成できる。 10

ショットキー電極として機能する金属層 18 は例えば Ti、Pt、Cr、Al、Sm、PtSi、Pd<sub>2</sub>Si 等から成り、絶縁膜 17 の孔 17a を介してシリコン半導体基板 1 の凹部 9 の表面にショットキー接觸している。保護素子としてのショットキーダイオードは半導体基板 1 の保護素子形成領域 7 と金属層 18 とによって形成されている。

第1の電極 3 の第2の部分としてのボンディングパッド部分 20 は主半導体領域 2 の表面積よりも小さい表面積を有するように形成され且つ破線で示す A1 又は A2 から成る外部接続用ワイヤ 21 を結合することができる金属からなり、光透過性導電膜 19 に接続されていると共に金属層 18 にも接続されている。即ち、ボンディングパッド部分 20 は、光透過性導電膜 19 の上面及び主半導体領域 2 の傾斜側面を覆うように形成された光透過性及び絶縁性を有する保護膜 22 の孔 23 を介して光透過性導電膜 19 に接続され、且つ主半導体領域 2 の孔 16 の中に配置されたショットキー電極として機能する金属層 18 に接続されている。ボンディングパッド部分 20 は、平面的に見て、即ち半導体基板 1 の一方の正面に対して垂直な方向から見て、保護素子形成領域 7 の少なくとも一部を覆い且つ主半導体領域 2 の少なくとも一部を覆わないように配置され且つ第1の部分としての光透過性導電膜 19 とショットキー電極としての金属層 18 とを電気的に接続するように形成されている。図 1 の実施例では、ボンディングパッド部分 20 が主半導体領域 2 の孔 16 の外側部分の上にも配置されている。なお、主半導体領域 2 の孔 16 の壁面と第1の電極 3 とは絶縁膜 17 で電気的に分離されている。ボンディングパッド部分 20 の上面は外部接続用ワイヤ 21 を結合できる面積を有し、且つ外部接続用ワイヤ 21 の接続を容易にするために保護膜 22 よりも上に突出している。 20

ボンディングパッド部分 20 は外部接続用ワイヤ 21 のボンディングに耐えることができる厚み(例えば 100 nm ~ 100 μm)を有する。従って、ボンディングパッド部分 20 を光が透過することはできない。もし、光がわずかに透過するようにボンディングパッド部分 20 を形成しても、ボンディングパッド部分 20 に外部接続用ワイヤ 21 等が結合されると、ボンディングパッド部分 20 を介して光を取り出すことは不可能又は困難になる。

この実施例では図 2 から明らかなようにボンディングパッド部分 20 の平面形状は円形であるが、これを4角形又は多角形等の別の形状にすることができる。また、半導体基板 1 の平面形状を円形等に変形することができる。 40

図 1 において、主半導体領域 2 の側面とボンディングパッド部分 20 との間を絶縁するために主半導体領域 2 の孔 16 の中に設けられた絶縁膜 17 は孔 16 の外の保護膜 22 と同時に形成することができる。

保護素子形成領域 7 は、平面的に見て、即ち主半導体領域 2 の第1の正面 14 又はシリコン半導体基板 1 の一方の正面 5 に対して垂直な方向から見て、ボンディングパッド部分 20 の内側に配置されている。保護素子形成領域 7 が平面的に見てボンディングパッド部分 20 の外側にはみ出ても保護素子の機能が低下することはない。しかし、平面的に見て保護素子形成領域 7 の面積が大きくなると、必然的に主半導体領域 2 の面積が小さくなる。このため、平面的に見て保護素子形成領域 7 の表面面積の 70 ~ 100 %、より望ましくは全部がボンディングパッド部分 20 の内側に配置される。 50

## 【0019】

第2の電極4は金属層からなり、半導体基板1の他方の主面6の全面に形成されている。即ち、第2の電極4は半導体基板1の保護素子形成領域7及び外周側領域8の両方の下面にオーミック接触している。なお、第2の電極4を図1で点線で示すように半導体基板1の一方の主面5の外周側に配置することもできる。

## 【0020】

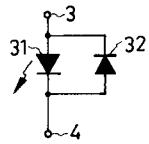

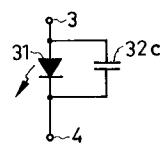

第1の電極3のボンディングパッド部分20は発光素子の外部接続電極としての機能の他にショットキーバリアダイオードの金属層8を発光素子に接続する機能を有する。第2の電極4は発光素子とショットキーバリアダイオードと両方の電極として機能する。従って、図1に示す複合半導体装置は、図4に示す発光素子としての発光ダイオード31と保護素子としてのショットキーバリアダイオード32との逆並列接続回路として機能する。ショットキーバリアダイオード32は、発光ダイオード31に所定値以上の逆方向の過電圧(例えばサージ電圧)が印加された時に導通する。これにより、発光ダイオード31の電圧はショットキーバリアダイオード32の順方向電圧に制限され、発光ダイオード31が静電気等に基づく逆方向の過電圧から保護される。ショットキーバリアダイオード32の順方向の導通開始電圧は発光ダイオード31の許容最大逆方向電圧以下に設定される。即ち、ショットキーバリアダイオード32の順方向の導通開始電圧は、発光ダイオード31が破壊される恐れのある電圧よりも低い値に設定される。なお、ショットキーバリアダイオード32の順方向の導通開始電圧は、正常時に発光ダイオード31に印加される逆方向の電圧よりも高く且つ発光ダイオード31が破壊される恐れのある電圧よりも低いことが望ましい。

## 【0021】

本実施例1は次の効果を有する。

(1) 保護素子形成領域7が平面的に見てボンディングパッド部分20の下に配置されている。従って、発光素子の光取り出し面積の低減を抑制して保護素子を形成することができ、保護素子内蔵の発光素子の小型化を図ることができる。

(2) ボンディングパッド部分20及び第2の電極4は発光ダイオード31とショットキーバリアダイオード32との相互接続部分として機能していると共に外部接続導体として機能しているので、複合半導体装置の構成が単純化され、小型化及び低コスト化を達成できる。

(3) 保護素子形成領域7が半導体基板1内に設けられているので、保護素子としてのショットキーバリアダイオード32を容易かつ低コストに得ることができる。

## 【実施例2】

## 【0022】

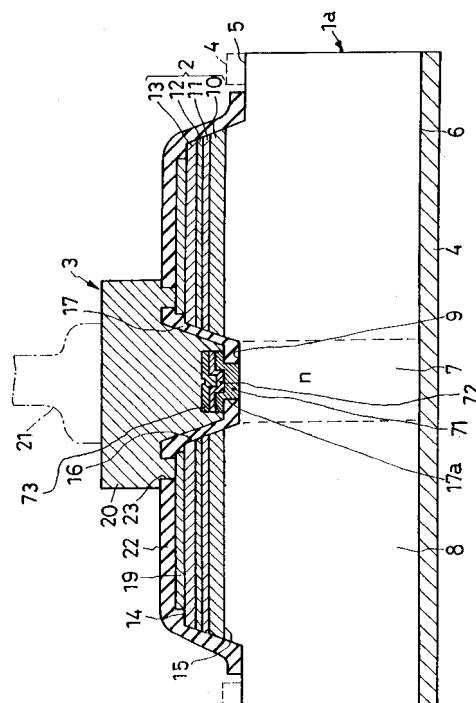

次に、図5に示す実施例2に係わる複合半導体装置を説明する。但し、図5及び後述する図6～図17において、図1～図4と実質的に同一の部分、及び図5～図17において相互に同一の部分には同一の符号を付してその説明を省略する。

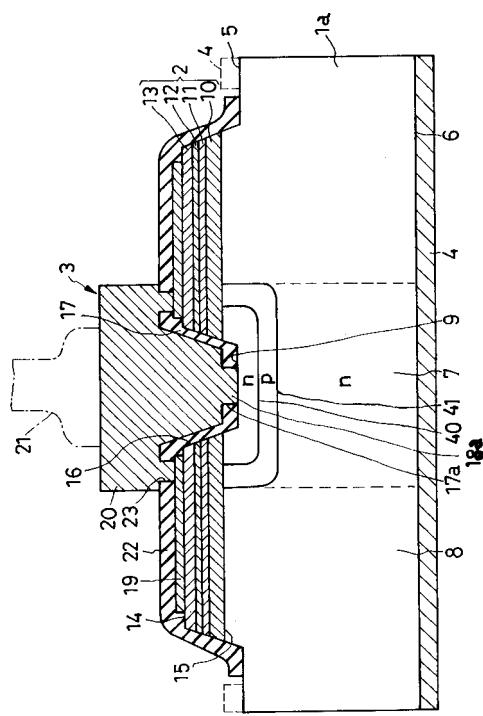

## 【0023】

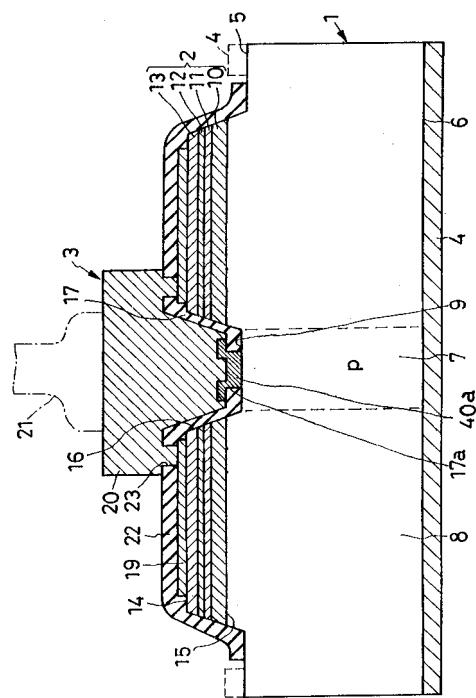

図5の複合半導体装置は、シリコン半導体基板1の保護素子形成領域7にpn接合ダイオードを構成するためのn型半導体領域40を形成し且つ図1の金属層18を省き、この他は図1と実質的に同一に形成したものである。

即ち、図5の複合半導体装置の保護素子は半導体基板1に形成された1つのpn接合を含む保護ダイオードから成る。この保護ダイオードは、第1導電型半導体領域としてのp型半導体基板1と、このp型半導体基板1の保護素子形成領域7の中に島状に形成され且つ半導体基板1の一方の主面5に露出する表面を有している第2導電型半導体領域としてのn型半導体領域40とから成る。n型半導体領域40はp型シリコン半導体基板1にn型不純物を拡散することによって形成されており、p型シリコン半導体基板1との間にpn接合を形成している。n型半導体領域40は保護素子形成領域7の表面の凹部9に露出するように配置されている。ボンディングパッド部分20の先端部分18aはn型半導体領域40にオーミック接触している。なお、オーミック接触を良くするための金属層をボンディン

10

20

30

40

50

グパッド部分 20 と n 型半導体領域 40 との間に配置することができる。n 型半導体領域 40 は、平面的に見て、即ち主半導体領域 2 の一方の正面 14 又はシリコン半導体基板 1 の一方の正面 5 に対して垂直な方向から見て、ボンディングパッド部 20 の内側に配置されている。

【 0 0 2 4 】

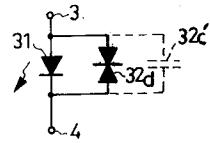

第 1 の電極 3 は発光素子及び p n 接合ダイオードの一方の電極として機能し、第 2 の電極 4 は発光素子及び p n 接合ダイオードの他方の電極として機能する。従って、図 5 に示す複合半導体装置は、図 6 に示す発光素子としての発光ダイオード 31 と保護素子としての p n 接合ダイオード 32a との逆並列接続回路を第 1 の電極 3 と第 2 の電極 4 との間に接続した回路と等価な機能を有する。p n 接合ダイオード 32a は整流ダイオード又は定電圧ダイオードに構成される。p n 接合ダイオード 32a は発光ダイオード 31 に所定値以上の逆方向の過電圧が印加された時に導通する。これにより、発光ダイオード 31 に印加される電圧は p n 接合ダイオード 32a の順方向電圧に制限される。従って、p n 接合ダイオード 32a によって発光ダイオード 31 を静電気等に基づくサージ電圧等の逆方向の過電圧から保護することができる。p n 接合ダイオード 32a の順方向の導通開始電圧は発光ダイオード 31 の許容最大逆方向電圧以下に設定される。なお、p n 接合ダイオード 32a の順方向の導通開始電圧は正常時に発光ダイオード 31 に対して逆方向に印加される電圧よりも高く且つ発光ダイオード 31 が破壊される恐れのある電圧よりも低いことが望ましい。

p n 接合ダイオード 32a がツェナーダイオード等の定電圧ダイオードに構成されている場合には、定電圧ダイオードから成る p n 接合ダイオード 32a の逆方向降伏電圧が発光ダイオード 31 の正常動作範囲の順方向電圧と許容最大順方向電圧との間に設定される。これにより、定電圧ダイオード成る p n 接合ダイオード 32a はサージ電圧等の順方向の過電圧から発光ダイオード 31 を保護する。定電圧ダイオードの順方向の導通開始電圧は正常時に発光ダイオード 31 に対して逆方向に印加される電圧よりも高く且つ発光ダイオード 31 が破壊される恐れのある電圧よりも低いことが望ましい。

上述から明らかなように、図 5 の実施例 2 によれば、サージ電圧等の過電圧から保護された発光素子を提供することができ、図 1 の実施例 1 と同様な効果を得ることができる。なお、図 5 において、半導体基板 1 の外側領域 8 の一部の不純物濃度を保護素子形成領域 7 よりも高くし、これにより、外側領域 8 の一部の抵抗率を保護素子形成領域 7 よりも低くし、発光素子の動作時の外側領域 8 における電圧降下を低減するように変形することができる。

【 実施例 3 】

【 0 0 2 5 】

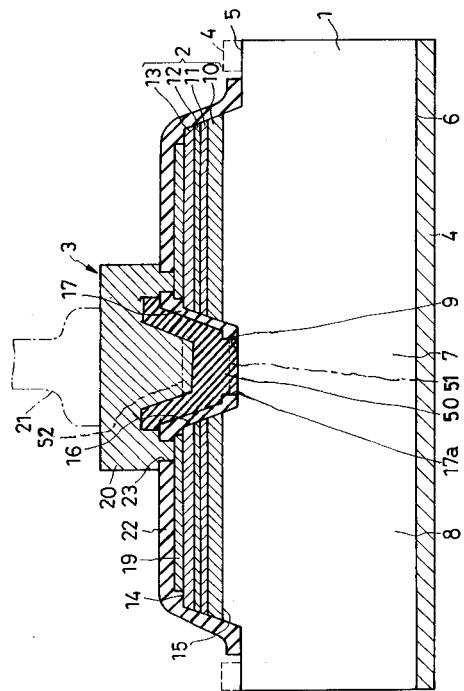

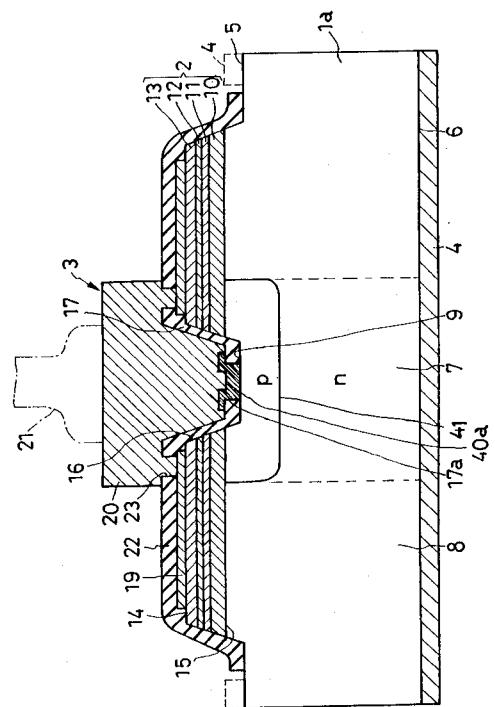

図 7 に示す実施例 3 に係わる複合半導体装置は、図 1 の p 型シリコン半導体基板 1 の代わりに n 型シリコン半導体基板 1a を使用し、この n 型シリコン半導体基板 1a の保護素子形成領域 7 に n p n 3 層ダイオード、即ち一般にダイアック (DIA) と呼ばれている双方向性ダイオードを形成するための n 型半導体領域 40 と p 型半導体領域 41 とを形成し且つ図 1 の金属層 18 を省き、この他は図 1 と実質的に同一に形成したものである。即ち、図 7 に示す実施例 3 に係わる複合半導体装置における保護素子は半導体基板 1a の保護素子形成領域 7 に形成された n p n 3 層ダイオードから成る。この 3 層ダイオードは、第 1 導電型を有する第 1 の半導体領域としての n 型シリコン半導体基板 1a と、n 型シリコン半導体基板 1a の中に島状に形成され且つ半導体基板 1a の一方の正面 5 に露出する表面を有し且つ第 2 導電型を有している第 2 の半導体領域としての p 型半導体領域 41 と、p 型半導体領域 41 の中に島状に形成され且つ半導体基板 1a の一方の正面 5 に露出する表面を有し且つ第 1 導電型を有している第 3 の半導体領域としての n 型半導体領域 40 とから成る。

【 0 0 2 6 】

図 7 の n 型半導体領域 40 は図 5 の n 型半導体領域 40 よりも少し小さく形成されている。p 型半導体領域 41 は n 型半導体領域 40 をこの表面を除いて囲むように配置されている。p

10

20

30

40

50

型半導体領域41はn型シリコン半導体基板1aにp型不純物を拡散することによって形成されており、n型シリコン半導体基板1aとの間にpn接合を形成している。n型半導体領域40はp型半導体領域41にn型不純物を拡散することによって形成されており、p型半導体領域41との間にpn接合を形成している。n型半導体領域40は保護素子形成領域7の表面の凹部9に露出するように配置されている。第1の電極3のボンディングパッド部分20の先端部分18aはn型半導体領域40にオーミック接触している。なお、オーミック接触を良くするための金属層をボンディングパッド部分20とn型半導体領域40との間に配置することができる。p型半導体領域41は、平面的に見て、即ち主半導体領域2の一方の正面14又はシリコン半導体基板1の一方の正面5に対して垂直な方向から見て、ボンディングパッド部分20の内側に配置されている。

10

## 【0027】

図7の第1の電極3は発光素子及びn p n 3層ダイオードの一方の電極として機能し、第2の電極4は発光素子及びn p n 3層ダイオードの他方の電極として機能する。従って、図7に示す複合半導体装置は図8に示す発光素子としての発光ダイオード31と保護素子としてのn p n 3層ダイオード32bとの並列接続回路を第1の電極3と第2の電極4との間に接続した回路と等価な機能を有する。n p n 3層ダイオード32bは図8に示すように逆方向ダイオードD1と順逆方向ダイオードD2との直列回路と等価である。なお、n p n 3層ダイオード32bは逆方向ダイオードD1と順逆方向ダイオードD2との逆並列回路で示されることもある。n p n 3層ダイオード32bの順方向及び逆方向の降伏電圧は発光ダイオード31の正常動作範囲の電圧と許容最大電圧との間であることが望ましい。これにより、許容最大電圧よりも高いサージ電圧等の過電圧から発光ダイオード31を保護することができる。

20

従って、図7の実施例2に係わる複合半導体装置は図1の実施例1と同様な効果を有する。

## 【実施例4】

## 【0028】

図9に示す実施例4の複合半導体装置は、図1の保護素子としてのショットキーバリアダイオードの代わりにコンデンサを設け、この他は図1と同一に形成したものである。

## 【0029】

図9の主半導体領域2の孔16の中に厚膜コンデンサを形成するための誘電体層50が配置されている。誘電体層50は絶縁膜17を形成するSiO<sub>2</sub>の比誘電率よりも大きい比誘電率、例えば1200～2000、を有する誘電体磁器材料からなる。この誘電体磁器材料は2族の金属と4族の金属の酸化物である例えばBaTiO<sub>3</sub>（チタン酸バリウム）又はSrTiO<sub>3</sub>（チタン酸ストロンチウム）等の主成分と、3族又は5族又はこれらの両方から成る副成分（添加成分）とから成る。3族の金属酸化物は、例えばNd<sub>2</sub>O<sub>3</sub>、La<sub>2</sub>O<sub>3</sub>、Dy<sub>2</sub>O<sub>3</sub>、Sm<sub>2</sub>O<sub>3</sub>、Pr<sub>2</sub>O<sub>3</sub>、Gd<sub>2</sub>O<sub>3</sub>、Ho<sub>2</sub>O<sub>3</sub>から選択された1つ又は複数であり、5族の金属酸化物、例えばNb<sub>2</sub>O<sub>5</sub>、Ta<sub>2</sub>O<sub>5</sub>から選択された1つ又は複数である。誘電体層50は有機バインダを伴った誘電体磁器材料のペーストを選択的に塗布して焼成する方法、又は誘電体磁器材料の生シート（グリーンシート）を張り付けて焼成する方法等で形成される。誘電体層50の一方の正面はシリコン基板1に接触し、他方の正面は第1の電極3の第2の部分としてのボンディングパッド部分20に接触している。従って、シリコン基板1と誘電体層50と第1の電極3のボンディングパッド部分20とによってコンデンサが形成されている。

30

## 【0030】

図9の複合半導体装置は図10の等価回路から明らかなように、主半導体領域2に基づく発光素子としての発光ダイオード31とここに並列接続された保護素子としてのコンデンサ32cとから成る。誘電体層50に基づくコンデンサ32cは発光ダイオード31の正常動作範囲の電圧よりも高いサージ電圧等の過電圧から発光素子31を保護する。

40

## 【0031】

図9の実施例4の複合半導体装置においても、保護用コンデンサ32cを構成するため

50

の誘電体層 50 は第 1 の電極 3 のボンディングパッド部分 20 と導電性シリコン基板 1 の一方の表面との間に配置され且つ平面的に見てボンディングパッド部分 20 の内側に配置されされているので、主半導体領域 2 の第 1 の主面 14 の有効光取り出し面積の低減無しに保護素子を配置することができる。また、誘電体層 50 は主半導体領域 2 の孔 16 の中に配置されているので、複合半導体装置の厚みの増大を抑制することができる。従って、実施例 4 によっても実施例 1 と同様に小型化、低コスト化の効果を得ることができる。

【0032】

なお、図 9において、鎖線 51 で示すように誘電体層 50 の一方の主面にコンデンサ電極を設けることができる。また、誘電体層 50 の他方に主面に鎖線 52 で示すように、コンデンサ電極を設けることができる。また、誘電体層 50 の代りに、チップ状コンデンサ素子を第 1 の電極 3 のボンディングパッド部分 20 とシリコン基板 1 の一方の主面 5 との間に配置することができる。

【実施例 5】

【0033】

図 11 に示す実施例 5 の複合半導体装置は、図 1 のショットキー接合用金属層 18、又は図 9 の誘電体層 50 の代わりに保護素子としてチップ状のバリスタ素子 60 を配置し、この他は図 1 又は図 9 と同一に形成したものである。バリスタ素子 60 は半導体磁器層 61 とこの一方の主面に配置された一方の電極 62 とこの他方の主面に配置された他方の電極 63 とから成る。半導体磁器層 61 は、 $BaTiO_3$ 、 $SrTiO_3$ 、 $ZnO$ 等から成る主成分に  $Nb_2O_5$ 、 $Pr_6O_{11}$  等の周知の副成分を添加した半導体磁器材料から成る。図 11 では第 1 の電極 3 のボンディングパッド部分 20 と一方の電極 62 との間の絶縁を確保するために、これらの間に絶縁物 64 が配置されている。バリスタ素子 60 の一方の電極 62 はシリコン基板 1 の一方の主面 5 に形成されたオーミック電極 65 に対して図示が省略された周知の導電性接合材で結合され、他方の電極 63 はボンディングパッド部分 20 に接続されている。このバリスタ素子 60 は例えば 10V 程度のバリスタ電圧を有する。

【0034】

図 11 の複合半導体装置は、図 12 の等価回路から明らかなように主半導体領域 2 に基づく発光素子としての発光ダイオード 31 とここに並列接続された保護素子としてのバリスタ 32d とから成る。図 11 のバリスタ素子 60 に対応する図 12 のバリスタ 32d は図 8 の 3 層ダイオードと同様に双方向ダイオードとしての機能を有する。バリスタ 32d のバリスタ電圧即ち導通開始電圧は、発光ダイオード 31 の順方向及び逆方向の正常動作範囲の電圧と許容最大電圧との間であることが望ましい。これにより、許容最大電圧よりも高いサージ電圧等の過電圧から発光素子 31 を保護することができる。

なお、半導体磁器層 61 は誘電体層としても機能するので、等価的に図 12 で点線で示すコンデンサ 32c' が発光素子 31 に並列に接続され、このコンデンサ 32c' も過電圧保護し、サージ破壊耐量を向上させるために寄与する。

【0035】

図 11 の実施例 5 の複合半導体装置においても保護素子を形成するバリスタ素子 60 が第 1 の電極 3 のボンディングパッド部分 20 とシリコン基板 1 の一方の主面 5 との間に配置されているので、実施例 1 と同様に小型化及び低コスト化の効果を得ることができる。

【0036】

図 11 のチップ状バリスタ素子 60 の代りに、電圧非直線特性を有する抵抗体層即ちバリスタ特性を有する半導体磁器層を第 1 の電極 3 のボンディングパッド部分 20 とシリコン基板 1 の一方の主面 5 との間に配置することができる。このバリスタ特性を有する半導体磁器層は、バリスタ特性を有する半導体磁器材料のペーストを図 9 の誘電体層 50 の形成時と同様に塗布し、焼成することによって形成することができる。この半導体磁器層の一方の主面は第 1 の電極 3 のボンディングパッド部分 20 に接触させ、この他方の主面はシリコン基板 1 の一方の主面 5 に接触させる。

【実施例 6】

【0037】

10

20

30

40

50

図13に示す実施例6の複合半導体装置は、図1の金属層18の代わりに薄膜半導体即ちn型半導体薄膜40aを設け、この他は図1と同一に形成したものである。

第2導電型半導体領域としてのn型半導体薄膜40aは、p型半導体基板1とボンディングパッド部分20との間に配置されている。このn型半導体薄膜40aは、蒸着、又はCVD(Chemical Vapor Deposition)、又はスパッタ、又は印刷(塗布)等の周知の方法で形成され、例えば1nm~1μm程度の厚みを有する。

#### 【0038】

n型半導体薄膜40aの材料として、例えば、アモルファス(非晶質)シリコン、一般にITOと呼ばれている酸化インジウム( $In_2O_3$ )と酸化錫( $SnO_2$ )との混合物、 $ZnO$ 、 $SnO_2$ 、 $In_2O_3$ 、 $ZnS$ 、 $ZnSe$ 、 $ZnSb_2O_6$ 、 $CdO$ 、 $CdIn_2O_4$ 、 $MgIn_2O_4$ 、 $ZnGa_2O_4$ 、 $CdGa_2O_4$ 、 $Ga_2O_3$ 、 $GaInO_3$ 、 $CdSnO_4$ 、 $InGaMgO_4$ 、 $InGaZnO_4$ 、 $Zn_2In_2O_5$ 、 $AgSbO_3$ 、 $Cd_2Sb_2O_7$ 、 $Cd_2GeO_4$ 、 $AgInO_2$ 、 $CdS$ 及び $CdSe$ から選択されたものを使用することができる。10

#### 【0039】

図13の複合半導体装置のn型半導体薄膜40aは図5のn型半導体領域40と同様に機能し、p型半導体基板1との間にpn接合を形成する。従って、半導体基板1の中央の保護素子形成領域7とn型半導体薄膜40aとによって図6の過電圧保護素子としてのpn接合ダイオード32aと同様な機能を有するダイオードが形成され、実施例6によっても実施例1及び2と同様な効果を得ることができる。

#### 【実施例7】

#### 【0040】

図14の実施例7の複合半導体装置は、図1の金属層18の代わりに、第1導電型半導体領域としてのp型半導体薄膜41aと第2導電型半導体領域としてのn型半導体薄膜40aとを設け、この他は図1と同一に構成したものである。別の観点から見ると、この図14の複合半導体装置は、図13のn型半導体薄膜40aとp型半導体基板1との間にp型半導体薄膜41aを追加したものに相当する。なお、p型半導体薄膜41aをp型薄膜半導体と呼ぶこともできる。

#### 【0041】

p型半導体薄膜41aは、周知の蒸着、又はCVD、又はスパッタ、又は印刷(塗布)法によって形成され、例えば1nm~1μm程度の厚さを有する。このp型半導体薄膜41aの材料としてp型アモルファスシリコン、 $NiO$ 、 $Cu_2O$ 、 $FeO$ 、 $CuAlO_2$ 、 $CuGaO_2$ 、及び $SrCu_2O_2$ から選択されたものを使用することができる。30

#### 【0042】

n型半導体薄膜40aとp型半導体薄膜41aとの間にpn接合が形成され、且つp型半導体薄膜41aはp型半導体基板1にオーミック接触し、n型半導体薄膜40aはボンディングパッド部分20にオーミック接触している。従って、図14のn型半導体薄膜40aとp型半導体薄膜41aとから成る薄膜ダイオードは図6のpn接合ダイオード32aと同一機能を有する過電圧保護素子を提供する。この実施例7によっても図5の実施例2と同様な効果を得ることができる。

#### 【実施例8】

#### 【0043】

図15に示す実施例8の複合半導体装置は、図1のp型半導体基板1を図7と同様にn型(第1導電型)半導体基板1aに置き換え、図1の金属層18の代わりに、第1の半導体領域としてのn型の第1の半導体薄膜71と第2の半導体領域としてのp型(第1導電型)の第2の半導体薄膜72と第3の半導体領域としてのn型の第3の半導体薄膜73とを設け、この他は、図1と同一に構成したものに相当する。

#### 【0044】

図15のn型の第1の半導体薄膜71はn型半導体基板7aにオーミック接触し、図13のn型半導体薄膜40aと同様な材料を使用して同様な方法で形成されている。n型の第1の半導体薄膜71の上に配置されたp型の第2の半導体薄膜72は図14のp型半導体薄膜41aと同一の材料を使用して同一の方法で形成される。p型の第2の半導体薄膜

10

20

30

40

50

7 2 の上に配置された n 型の第 3 の半導体薄膜 7 3 は図 1 3 の n 型半導体薄膜 4 0 a と同様な材料から成り、且つボンディングパッド部分 2 0 にオーミック接觸している。

【 0 0 4 5 】

第 1 の半導体薄膜 7 1 と第 2 の半導体薄膜 7 2 と第 3 の半導体薄膜 7 3 とから成る薄膜 3 層ダイオードは、図 8 の保護素子としての npn 3 層ダイオード 3 2 b と同一の機能を有する。従って、この実施例 8 によっても図 8 の実施例 3 と同様な効果を得ることができる。

【 実施例 9 】

【 0 0 4 6 】

図 1 6 に示す実施例 9 の複合半導体装置は、図 7 の n 型半導体領域 4 0 の代わりに、n 型半導体基板 1 a の上に第 1 導電型半導体領域としての n 型半導体薄膜 4 0 a を設け、この他は図 7 と同一に構成したものに相当する。図 1 6 の n 型半導体薄膜 4 0 a は、図 1 3 において同一符号で示すものと同一の材料を使用して同一方法で形成される。この n 型半導体薄膜 4 0 a は p 型半導体領域 4 1 との間に p n 接合を形成し、またボンディングパッド部分 2 0 にオーミック接觸している。従って、n 型半導体基板 1 a と p 型半導体領域 4 1 と n 型半導体薄膜 4 0 a とによって図 8 の npn 3 層ダイオード 3 2 b と同一の機能を得ることができる。この実施例 9 によっても図 8 の実施例 3 と同様な効果を得ることができる。

10

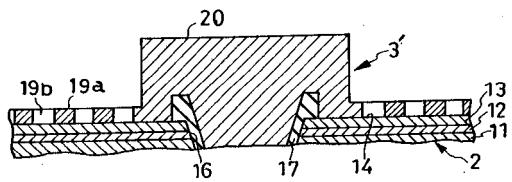

【 実施例 1 0 】

【 0 0 4 7 】

図 1 7 に一部が示されている実施例 1 0 に係わる複合半導体装置は、図 1 又は図 5 又は図 7 又は図 9 又は図 1 1 又は図 1 3 ~ 図 1 6 のいずれかの光透過性導電膜 1 9 の代わりに帯状導体 1 9 a を有する第 1 の電極 3' を設け、この他は図 1 又は図 5 又は図 7 又は図 9 又は図 1 1 又は図 1 3 ~ 図 1 6 と同一に形成したものである。図 1 3 の第 1 の電極 3' の第 1 の部分としての帯状導体 1 9 a は、第 2 の部分としてのボンディングパッド部 2 0 に接続され、且つ格子状又は網目状又はストライプ上等のパターンを有して主半導体領域 2 の一方の正面 1 4 即ち p 型半導体層 1 3 の表面上に配置され、ここにオーミック接觸している。即ち、複数の孔 1 9 b を伴った帯状導体 1 9 a はボンディングパッド部 2 0 よりも薄く形成され且つボンディングパッド部 2 0 の外周に配置され且つ主半導体領域 2 の一方の正面 1 4 にほぼ均一に分布している。主半導体領域 2 で発生した光は主半導体領域 2 の一方の正面 1 4 の帯状導体 1 9 a が形成されていない部分即ち孔 1 9 b から外部に取り出される。なお、第 1 の電極 3' の第 1 の部分としての帯状導体 1 9 a の形状を主半導体領域 2 から放射された光を取り出すことができる任意の形状に変形することができる。

20

ボンディングパッド部分 2 0 は帯状導体 1 9 a のほぼ中央に配置されているので、ボンディングパッド部分 2 0 を通る電流は帯状導体 1 9 a を介して主半導体領域 2 の外周側に分散される。従って、帯状導体 1 9 a は光透過性導電膜 1 9 と同様な機能を有する。

30

図 1 7 において、第 1 の電極 3' の第 2 の部分としてのボンディングパッド部分 2 0 の外周下部が主半導体領域 2 の第 1 の正面 1 4 にオーミック接觸している。このため、帯状導体 1 9 a を省いても主半導体領域 2 に第 1 の電極 3' から電流を流すことができる。帯状導体 1 9 a が省かれた場合には、ボンディングパッド部分 2 0 の外周部又は外周下部が第 1 の電極 3' の第 1 の部分として機能し、前記外周下部よりも内側の中央部分、又は前記外周下部の上の部分と中央部分が第 2 の部分として機能する。帯状導体 1 9 a を省くと、主半導体領域 2 の全領域に電流を均一に流すことが困難になる。しかし、帯状導体 1 9 a による光取り出しの妨害が無くなり、光取り出し効率が向上し、且つ帯状導体 1 9 a の製造工程が不用になる分だけ半導体発光素子のコストが低減される。従って、帯状導体 1 9 a を設けるか否かは発光効率及びコストを勘案して決定する。

40

上述から明らかなように、図 1 7 の実施例 1 0 に係わる第 1 の電極 3' の構造を図 1 又は図 5 又は図 7 又は図 9 又は図 1 1 又は図 1 3 ~ 図 1 6 のいずれかの実施例の複合半導体装置に適用した場合においても、図 1 又は図 5 又は図 7 又は図 9 又は図 1 1 又は図 1 3 ~ 図 1 6 のいずれかの実施例と同様な効果を得ることができる。

【 0 0 4 8 】

本発明は上述の実施例に限定されるものではなく、例えば次の変形が可能なものである。

50

(1) 図5及び図7及び図9及び図11及び図13～図17の実施例においても、第2の電極4を半導体基板1又は1aの一方の主面5に配置することができる。

(2) シリコン半導体基板1又は1aを単結晶シリコン以外の多結晶シリコン又はSiC等のシリコン化合物、又は3-5族化合物半導体とすることができる。また、図9及び図11及び図14及び図15の実施例においては、シリコン半導体基板1を金属基板とすることができる。

(3) シリコン半導体基板1又は1a及び主半導体領域2の各層及び保護素子の各層又は各膜の導電型を実施例と逆にすることができます。

(4) 主半導体領域3に、周知の電流拡散用半導体層及びコンタクト用半導体層を設けることができる。

(5) 図1、図5、図7に示す半導体基板1又は1aの中の保護素子と図9、図11、図14及び図15の半導体基板1の上の保護素子との両方を1つの複合半導体装置に設けることができる。

(6) 図11の保護素子としての磁器バリスタ素子60の代わりにシリコンバリスタ素子、定電圧ダイオード、整流ダイオード、3層ダイオード等のチップ状保護素子を配置することができる。また、半導体薄膜40a、41a、71, 72, 73を半導体厚膜に変形することができる。

(7) ボンディングパッド部分20にワイヤ21以外の棒状又は板状等の別の導体部材を接続することができる。

(8) 半導体基板1又は1aの上に主半導体領域2を気相成長させる代わりに、半導体基板1又は1a又は金属基板に主半導体領域2を熱圧着等で貼り合わせることができます。

(9) 主半導体領域2から基板1又は1a側に放射された光を主半導体領域2の第1の主面14側に反射させる光反射を設けることができる。

#### 【産業上の利用可能性】

#### 【0049】

本発明は、半導体発光素子と保護素子との複合半導体装置に利用可能である。

#### 【図面の簡単な説明】

#### 【0050】

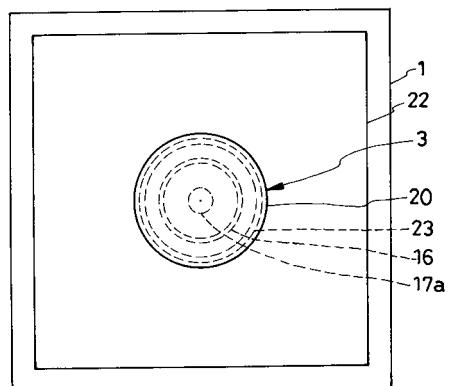

【図1】本発明の実施例1に従う複合半導体装置を概略的に示す中央縦断面図である。

【図2】図1の複合半導体装置を縮小して示す平面図である。

【図3】図1の主半導体領域と半導体基板の一部とを示す断面図である。

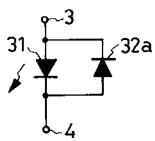

【図4】図1の複合半導体装置の電気回路図である。

【図5】実施例2の複合半導体装置を概略的に示す中央縦断面図である

【図6】図5の複合半導体装置の電気回路図である。

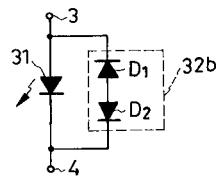

【図7】実施例3の複合半導体装置を概略的に示す中央縦断面図である

【図8】図7の複合半導体装置の電気回路図である。

【図9】実施例4の複合半導体装置を概略的に示す中央縦断面図である

【図10】図9の複合半導体装置の電気回路図である。

【図11】実施例5の複合半導体装置を概略的に示す中央縦断面図である

【図12】図11の複合半導体装置の電気回路図である。

【図13】実施例6の複合半導体装置を概略的に示す中央縦断面図である

【図14】実施例7の複合半導体装置を概略的に示す中央縦断面図である。

【図15】実施例8の複合半導体装置を概略的に示す中央縦断面図である

【図16】実施例9の複合半導体装置を概略的に示す中央縦断面図である

【図17】実施例10の複合半導体装置の一部を概略的に示す断面図である

#### 【符号の説明】

#### 【0051】

1, 1a シリコン半導体基板

2 主半導体領域

3, 3' 第1の電極

10

20

30

40

50

4 第2の電極

7 保護素子形成領域

20 ボンディングパッド部分

【図1】

【図2】

【図3】

【 図 4 】

## 【 図 5 】

【図6】

【圖 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

【図15】

### 【図16】

## 【図17】

---

フロントページの続き

(72)発明者 加藤 隆志

埼玉県新座市北野三丁目 6 番 3 号 サンケン電気株式会社内

(72)発明者 丹羽 愛玲

埼玉県新座市北野三丁目 6 番 3 号 サンケン電気株式会社内

(72)発明者 神井 康宏

埼玉県新座市北野三丁目 6 番 3 号 サンケン電気株式会社内

審査官 山村 浩

(56)参考文献 特開平 10 - 135519 (JP, A)

特公昭 53 - 037197 (JP, B1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 33 / 00