(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-106109

(P2015-106109A)

(43) 公開日 平成27年6月8日(2015.6.8)

(51) Int.Cl.

G02F 1/1345 (2006.01)

G09F 9/30 (2006.01)

F 1

G02F 1/1345

G09F 9/30

テーマコード(参考)

2H092

5C094

審査請求 未請求 請求項の数 11 O L (全 19 頁)

(21) 出願番号

特願2013-248933 (P2013-248933)

(22) 出願日

平成25年12月2日 (2013.12.2)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100116665

弁理士 渡辺 和昭

(72) 発明者 藤川 紳介

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 2H092 GA33 GA44 GA50 GA59 HA25

JA24 RA05

5C094 BA27 BA43 BA75 CA19 DB02

EA04 HA06 HA08 JA08

(54) 【発明の名称】電気光学装置、及び電子機器

## (57) 【要約】

【課題】高品位画像を可能にする事。

【解決手段】電気光学装置200は、表示領域40を有する素子基板62を備え、素子基板62には、第1行目の端子PAD1と、第2行目の端子PAD2と、第1行目の端子PAD1に接続する第1の配線W1と、第2行目の端子PAD2に接続する第2の配線W2とが形成されており、第1行目の端子PAD1は、表示領域40と素子基板62の外周の一辺67との間に配置され、第2行目の端子PAD2は、第1行目の端子PAD1と外周の一辺67との間に配置され、第1の配線W1は、表示領域40と外周の一辺67との間に延在し、第2の配線W2は、表示領域40と第2行目の端子PAD2の間に延在する。第1の配線W1が有する容量と第2の配線W2が有する容量とを同程度となるので、表示ムラが抑制された高精細画像を表示する電気光学装置を実現する事ができる。

【選択図】図6

## 【特許請求の範囲】

## 【請求項 1】

表示領域を有する素子基板を備え、

前記素子基板には、第1行目の端子と、第2行目の端子と、前記第1行目の端子に接続する第1の配線と、前記第2行目の端子に接続する第2の配線とが形成されており、

前記第1行目の端子は、前記表示領域と前記素子基板の外周の一辺との間に配置され、

前記第2行目の端子は、前記第1行目の端子と前記外周の一辺との間に配置され、

前記第1の配線は、前記表示領域と前記外周の一辺との間に延在し、

前記第2の配線は、前記表示領域と前記第2行目の端子との間に延在する事を特徴とする電気光学装置。

10

## 【請求項 2】

前記第2の配線は、前記表示領域と前記外周の一辺との間に延在する事を特徴とする請求項1に記載の電気光学装置。

## 【請求項 3】

少なくとも互いに隣接する前記第1の配線の長さと前記第2の配線の長さとがほぼ等しい事を特徴とする請求項1又は2に記載の電気光学装置。

## 【請求項 4】

前記第1の配線と前記第2の配線とが直線である事を特徴とする請求項1乃至3のいずれか一項に記載の電気光学装置。

20

## 【請求項 5】

前記第2の配線の幅は、前記第2行目の端子との接続部に於いて、前記第2の配線の幅の平均値よりも大きい事を特徴とする請求項4に記載の電気光学装置。

## 【請求項 6】

表示領域と駆動回路とを有する素子基板を備え、

前記駆動回路は、前記表示領域と前記素子基板の外周の一辺との間に配置され、

前記素子基板には、第1行目の端子と、第2行目の端子と、前記第1行目の端子に接続する第1の配線と、前記第2行目の端子に接続する第2の配線とが形成されており、

前記第1行目の端子は、前記駆動回路と前記素子基板の外周の一辺との間に配置され、

前記第2行目の端子は、前記第1行目の端子と前記外周の一辺との間に配置され、

前記第1の配線は、前記駆動回路と前記外周の一辺との間に延在し、

前記第2の配線は、前記駆動回路と前記第2行目の端子との間に延在する事を特徴とする電気光学装置。

30

## 【請求項 7】

前記第2の配線は、前記駆動回路と前記外周の一辺との間に延在する事を特徴とする請求項6に記載の電気光学装置。

## 【請求項 8】

少なくとも互いに隣接する前記第1の配線の長さと前記第2の配線の長さとがほぼ等しい事を特徴とする請求項6又は7に記載の電気光学装置。

## 【請求項 9】

前記第1の配線と前記第2の配線とが直線である事を特徴とする請求項6乃至8のいずれか一項に記載の電気光学装置。

40

## 【請求項 10】

前記第2の配線の幅は、前記第2行目の端子との接続部に於いて、前記第2の配線の幅の平均値よりも大きい事を特徴とする請求項9に記載の電気光学装置。

## 【請求項 11】

請求項1乃至10のいずれか一項に記載の電気光学装置を備えた事を特徴とする電子機器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

50

本発明は、電気光学装置、及び電子機器に関する。

【背景技術】

【0002】

表示機能が付いた電子機器では、透過型電気光学装置や反射型電気光学装置が使用されている。これらの電気光学装置に光が照射され、電気光学装置により変調された透過光や反射光が表示画像となったり、或いはスクリーンに投影されて投射画像となったりしている。この様な電子機器に使用される電気光学装置としては液晶装置が知られており、これは液晶の誘電異方性と液晶層に於ける光の旋光性を利用して画像を形成する物である。液晶装置では、画像表示領域に走査線と信号線とが配置されて、これらの交点に画素が行列状に配置されている。画素には画素トランジスターが設けられ、画素トランジスターを介して各画素に画像信号を供給する事で画像が形成される。

10

【0003】

電気光学装置では、表示品質を高めるべく、画素の高精細化が進められている。これに伴い電気光学装置が有する実装端子数が増加し、電気光学装置のサイズに対して充分な実装端子の配置領域を確保し難い状況が生じて来ている。この課題を解決する方法が、例えば特許文献1に記載されている。特許文献1では、実装端子の配列方向に対して直角の方向に別の実装端子群が配置されている。要するに特許文献1の電気光学装置では、実装端子が2行に渡って配置されている。

20

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011-138101号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載されている電気光学装置では、表示された画像に表示ムラが視認される事があった。換言すると、従来の電気光学装置では、高精細画像を表示ムラが発生せぬ様に表示する事が困難であると云う課題があった。

【課題を解決するための手段】

【0006】

本発明は、前述の課題の少なくとも一部を解決する為になされたものであり、以下の形態又は適用例として実現する事が可能である。

30

【0007】

(適用例1) 本適用例に係わる電気光学装置は、表示領域を有する素子基板を備え、素子基板には、第1行目の端子と、第2行目の端子と、第1行目の端子に接続する第1の配線と、第2行目の端子に接続する第2の配線とが形成されており、第1行目の端子は、表示領域と素子基板の外周の一辺との間に配置され、第2行目の端子は、第1行目の端子と外周の一辺との間に配置され、第1の配線は、表示領域と外周の一辺との間に延在し、第2の配線は、表示領域と第2行目の端子との間に延在する事を特徴とする。

40

この構成によると、第1の配線が有する容量(第1の配線容量)と第2の配線が有する容量(第2の配線容量)とを同程度とする事ができる。従って、第1の配線に於ける信号伝達の時定数(第1の配線時定数)と第2の配線に於ける信号伝達の時定数(第2の配線時定数)とが同程度となり、第1の配線時定数と第2の配線時定数との相違に起因する表示ムラを抑制する事ができる。この結果、表示ムラが抑制された高精細画像を表示する電気光学装置を実現する事ができる。

【0008】

(適用例2) 上記適用例1に記載の電気光学装置に於いて、第2の配線は、表示領域と外周の一辺との間に延在する事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる。

【0009】

50

(適用例3) 上記適用例1又は2に記載の電気光学装置に於いて、少なくとも互いに隣接する第1の配線の長さと第2の配線の長さとがほぼ等しい事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる。

#### 【0010】

(適用例4) 上記適用例1乃至3のいずれか一項に記載の電気光学装置に於いて、第1の配線と第2の配線とが直線である事が好ましい。

この構成によると、第1の配線と第2の配線とで屈曲部が解消されているので、屈曲部に於ける信号反射の影響を回避する事ができる。この結果、配線に高速で信号を伝送する事ができる。

#### 【0011】

(適用例5) 上記適用例4に記載の電気光学装置に於いて、第2の配線の幅は、第2行目の端子との接続部に於いて、第2の配線の幅の平均値よりも大きい事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる上、配線抵抗が下がるので、第2の配線時定数の増大を抑制する事ができる。

#### 【0012】

(適用例6) 本適用例に係わる電気光学装置は、表示領域と駆動回路とを有する素子基板を備え、駆動回路は、表示領域と素子基板の外周の一辺との間に配置され、素子基板には、第1行目の端子と、第2行目の端子と、第1行目の端子に接続する第1の配線と、第2行目の端子に接続する第2の配線とが形成されており、第1行目の端子は、駆動回路と素子基板の外周の一辺との間に配置され、第2行目の端子は、第1行目の端子と外周の一辺との間に配置され、第1の配線は、駆動回路と外周の一辺との間に延在し、第2の配線は、駆動回路と第2行目の端子との間に延在する事を特徴とする。

この構成によると、第1の配線が有する容量(第1の配線容量)と第2の配線が有する容量(第2の配線容量)とを同程度とする事ができる。従って、第1の配線に於ける信号伝達の時定数(第1の配線時定数)と第2の配線に於ける信号伝達の時定数(第2の配線時定数)とが同程度となり、第1の配線時定数と第2の配線時定数との相違に起因する表示ムラを抑制する事ができる。この結果、表示ムラが抑制された高精細画像を表示する電気光学装置を実現する事ができる。

#### 【0013】

(適用例7) 上記適用例6に記載の電気光学装置に於いて、第2の配線は、駆動回路と外周の一辺との間に延在する事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる。

#### 【0014】

(適用例8) 上記適用例6又は7に記載の電気光学装置に於いて、少なくとも互いに隣接する第1の配線の長さと第2の配線の長さとがほぼ等しい事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる。

#### 【0015】

(適用例9) 上記適用例6乃至8のいずれか一項に記載の電気光学装置に於いて、第1の配線と第2の配線とが直線である事が好ましい。

この構成によると、第1の配線と第2の配線とで屈曲部が解消されているので、屈曲部に於ける信号反射の影響を回避する事ができる。この結果、配線に高速で信号を伝送する事ができる。

#### 【0016】

(適用例10) 上記適用例9に記載の電気光学装置に於いて、第2の配線の幅は、第2行目の端子との接続部に於いて、第2の配線の幅の平均値よりも大きい事が好ましい。

この構成によると、第1の配線容量と第2の配線容量とを同程度とする事ができる上、配線抵抗が下がるので、第2の配線時定数の増大を抑制する事ができる。

#### 【0017】

(適用例11) 上記適用例1乃至10のいずれか一項に記載の電気光学装置を備えた事を特徴とする電子機器。

この構成によると、表示ムラが抑制された高精細画像を表示する電気光学装置を備えた電子機器を実現する事ができる。

【図面の簡単な説明】

【0018】

【図1】電子機器の一例である投射型表示装置の模式図。

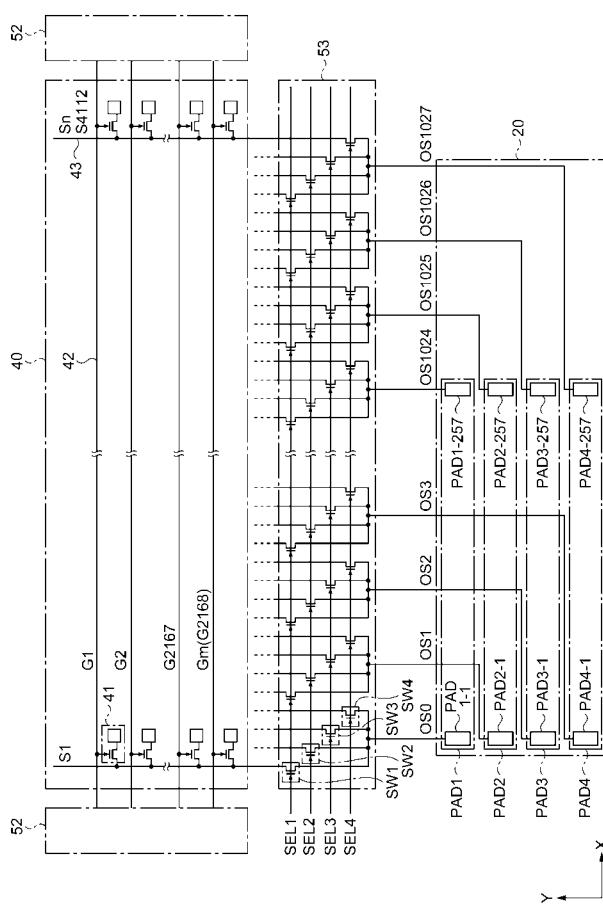

【図2】電気光学装置の回路ブロック図。

【図3】各画素の回路図。

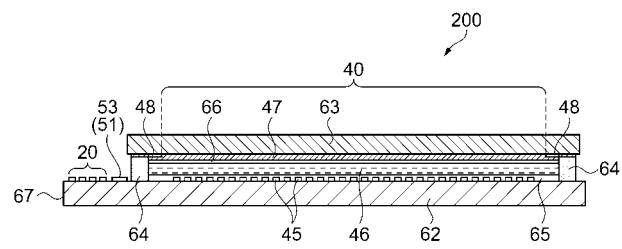

【図4】液晶装置の模式断面図。

【図5】実施形態1に係わる信号線駆動回路の回路構成と実装領域の構成とを説明した図。

10

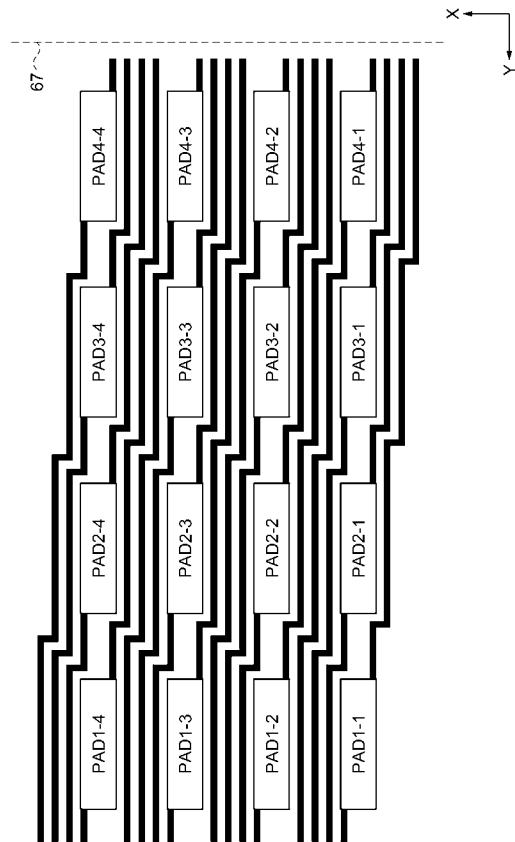

【図6】実施形態1に係わる配線形状を説明する図。

【図7】実施形態1に係わる配線形状を説明する図。

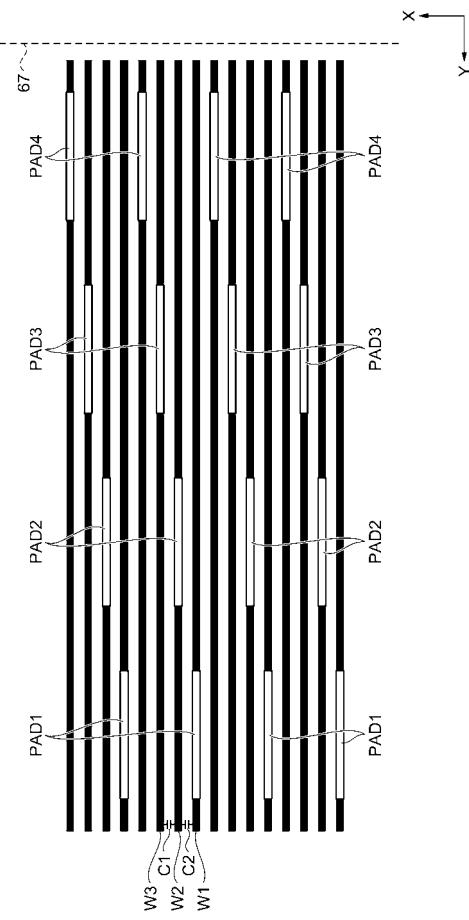

【図8】本発明の原理を説明する図。

【図9】実施形態2に係わる配線形状を説明する図。

【図10】実施形態2に係わる配線形状を説明する図。

【図11】実施形態3に係わる配線形状を説明する図。

【図12】実施形態4に係わる電気光学装置の回路構成と実装領域の構成とを説明した図。

【図13】変形例1に係わる配線形状を説明する図。

【図14】比較例に係わる配線形状を説明する図。

20

【発明を実施するための形態】

【0019】

以下、本発明の実施形態について、図面を参照して説明する。尚、以下の各図においては、各層や各部材を認識可能な程度の大きさにするため、各層や各部材の尺度を実際とは異ならせしめている。

【0020】

(実施形態1)

「電子機器の概要」

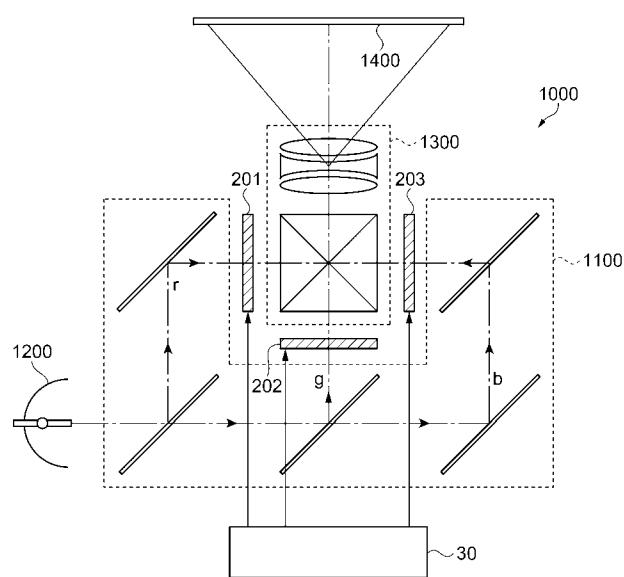

図1は、電子機器の一例である投射型表示装置(3板式のプロジェクター)の模式図である。以下、図1を参照して電子機器の構成を説明する。

30

【0021】

電子機器(投射型表示装置1000)は、3枚の電気光学装置200(図2参照、以下、第一パネル201、第二パネル202、第三パネル203と略称する)と、これら電気光学装置200に制御信号を供給する制御装置30と、を少なくとも有している。第一パネル201と第二パネル202と第三パネル203とは、相異なる表示色(赤色や緑色、青色)に対応する3個の電気光学装置200である。以下、特に第一パネル201と第二パネル202と第三パネル203とを区別する必要がなければ、これらを纏めて単に電気光学装置200と称する。

【0022】

照明光学系1100は、照明装置(光源)1200からの出射光のうち赤色成分 $r$ を第一パネル201に供給し、緑色成分 $g$ を第二パネル202に供給し、青色成分 $b$ を第三パネル203に供給する。各電気光学装置200は、照明光学系1100から供給される各色光を表示画像に応じて変調する光変調器(ライトバルブ)として機能する。投射光学系1300は、各電気光学装置200からの出射光を合成して投射面1400に投射する。

【0023】

「電子機器の回路構成」

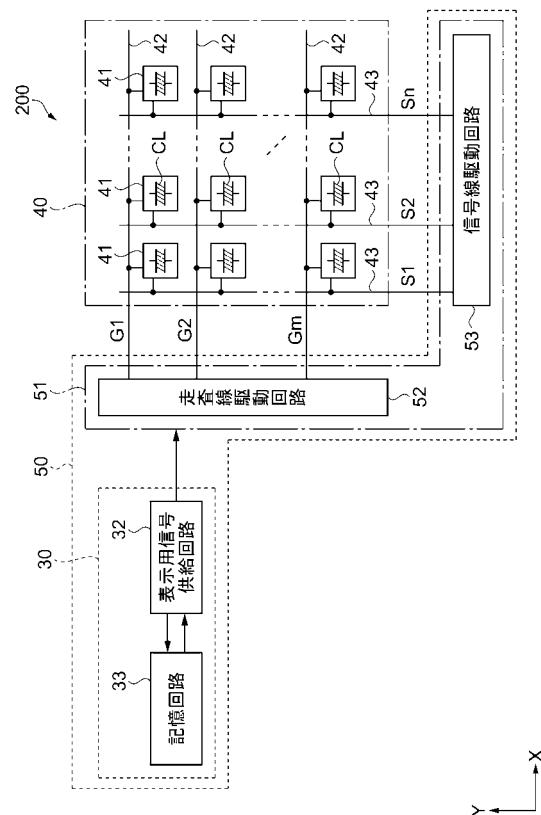

図2は、電気光学装置の回路ブロック図である。次に、図2を参照して電気光学装置200の回路ブロック構成を説明する。

【0024】

図2に示す様に、電気光学装置200は表示領域40と駆動部50とを少なくとも具備

40

50

している。更に電気光学装置 200 は実装領域 20 (図 6 参照) を備えている。電気光学装置 200 の表示領域 40 には、相交差する複数の走査線 42 と複数の信号線 43 とが形成され、走査線 42 と信号線 43 との各交差に対応して画素 41 が行列状に配列されている。走査線 42 は行方向に延在しており、信号線 43 は列方向に延在している。本明細書では、行方向を X 軸に平行な方向とし、列方向を Y 軸に平行な方向としている。尚、走査線 42 の内で i 行目の走査線 42 を特定する際には、走査線 G i と表記し、信号線 43 の内で (j k + p) 列目の信号線 43 を特定する際には、信号線 S j k + p と表記する (j、k、p については後に詳述する)。表示領域 40 には、m 本の走査線 42 と n 本の信号線 43 とが形成されている (m は 2 以上の整数、n は 2 以上の整数)。尚、本実施形態では、m = 2168 で、n = 4112 を例として、電気光学装置 200 を説明する。この場合、2168 行 × 4112 列の表示領域 40 に対し、2160 行 × 4096 行の所謂 4K 画像が表示される。

10

## 【0025】

表示領域 40 には駆動部 50 から各種信号が供給され、画像が表示領域 40 に表示される。即ち、駆動部 50 は、複数の走査線 42 と複数の信号線 43 とに駆動信号を供給する。具体的に、駆動部 50 は、各画素 41 を駆動する駆動回路 51 と、駆動回路 51 に表示用信号を供給する表示用信号供給回路 32 と、フレーム画像を一時的に記憶する記憶回路 33 と、を含んで構成される。記憶回路 33 に記憶されたフレーム画像から、表示用信号供給回路 32 は表示用信号 (画像信号やクロック信号等) を作製し、これを駆動回路 51 に供給する。表示用信号供給回路 32 はプリチャージ信号も作製し、これを駆動回路 51 に供給する。

20

## 【0026】

駆動回路 51 は走査線駆動回路 52 と信号線駆動回路 53 とを含んで構成される。走査線駆動回路 52 は画素を行方向に選択又は非選択する走査信号を各走査線 42 に出力し、走査線 42 はこの走査信号を画素 41 に伝える。言い換えると、走査信号は選択状態と非選択状態とを有しており、走査線 42 は、走査線駆動回路 52 からの走査信号を受けて、適宜選択され得る。走査線駆動回路 52 は不図示のシフトレジスター回路を備えており、シフトレジスター回路をシフトする信号が、一段毎にシフト出力信号として出力される。このシフト出力信号を用いて走査信号が形成される。信号線駆動回路 53 は、走査線 42 の選択に同期して n 本の信号線 43 の各々にプリチャージ信号や画像信号を供給する事ができる。

30

## 【0027】

一枚の表示画像は 1 フレーム期間に形成される。1 フレーム期間には各走査線 42 が少なくとも一度は選択される。通常は、各走査線 42 が一度ずつ選択される。一つの走査線が選択される期間を水平走査期間と呼ぶので、1 フレーム期間には少なくとも m 個の水平走査期間が含まれる。1 行目走査線 G 1 から順に m 行目の走査線 G m まで (或いは、m 行目走査線 G m から順に 1 行目の走査線 G 1 まで) 順次走査線 42 が選択されて 1 フレーム期間が構成されるので、フレーム期間を垂直走査期間とも呼ぶ。

## 【0028】

本実施形態では電気光学装置 200 は素子基板 62 (図 4 参照) を用いて形成され、駆動回路 51 はこの素子基板 62 に薄膜トランジスター等の薄膜素子を用いて形成されている。表示用信号供給回路 32 と記憶回路 33 とが制御装置 30 に含まれており、制御装置 30 は単結晶半導体基板に形成される半導体集積回路で構成されている。素子基板 62 には実装領域 20 が設けられており、実装領域 20 に配置された端子 PAD とフレキシブルプリント基板 (Flexible Printed Circuits; FPC) とを介して制御装置 30 から表示用信号が駆動回路 51 に供給される。

40

## 【0029】

## 「画素の構成」

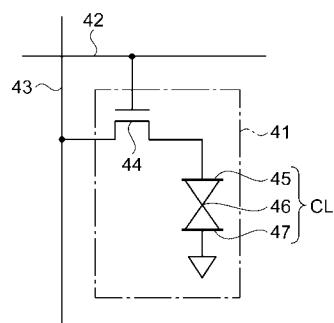

図 3 は、各画素の回路図である。次に、図 3 を参照して画素 41 の構成を説明する。

## 【0030】

50

本実施形態の電気光学装置 200 は液晶装置であり、電気光学材料は液晶 46 となる。図 3 に示す様に、各画素 41 は、液晶素子 CL と画素トランジスター 44 を含んで構成される。液晶素子 CL は、相対向する画素電極 45 と共通電極 47 を有し、これら両電極間に電気光学材料の液晶 46 が配置された電気光学素子である。画素電極 45 と共通電極 47 の間に印加される電界に応じて液晶 46 を通過する光の透過率が変化する。尚、電気光学材料としては、液晶 46 に代わり、電気泳動材料を用いても良い。その場合、電気光学装置 200 は電気泳動装置となり、電子書籍などに使用される。或いは、電気光学材料としては、液晶 46 に代わり、有機 EL 材料を用いても良い。その場合、電気光学装置 200 は有機 EL 装置となり、スマートフォンやタブレット端末などに使用される。

## 【0031】

画素トランジスター 44 は、走査線 42 にゲートが接続された N 型の薄膜トランジスターで構成され、液晶素子 CL と信号線 43 との間に介在して両者の電気的な接続（導通 / 非導通）を制御する。従って、画素 41（液晶素子 CL）は、画素トランジスター 44 がオン状態とされた際に信号線 43 へ供給されている電位（画像信号）に応じた表示を行う。尚、液晶素子 CL に対して並列に接続される補助容量等の図示は省略されている。又、電気光学装置 200 が有機 EL 装置で有る場合、有機 EL 装置の画素 41 の構成は図 3 に示す構成とは若干異なり、不図示の駆動トランジスターを更に有する。この際に、画素トランジスター 44 の出力が駆動トランジスターのゲートに電気的に接続され、駆動トランジスターのソースドレインの一方が電源に接続され、駆動トランジスターのソースドレインの他方が画素電極 45 に接続される。

10

20

## 【0032】

## 「液晶装置の構造」

図 4 は液晶装置の模式断面図である。以下、液晶装置の断面構造を、図 4 を参照して説明する。尚、以下の形態において、「上に」と記載された場合、「の上に接する様に配置される場合、又は、「の上に他の構成物を介して配置される場合、又は、「の上に一部が接する様に配置され一部が他の構成物を介して配置される場合、を表すものとする。

30

## 【0033】

電気光学装置 200（液晶装置）では、一対の基板を構成する素子基板 62 と対向基板 63 とが、平面視で略矩形枠状に配置されたシール材 64 にて貼り合わされている。液晶装置は、シール材 64 に囲まれた領域内に液晶 46 が封入された構成になっている。液晶 46 としては、例えば、正の誘電率異方性を有する液晶材料が用いられる。液晶装置は、シール材 64 の内周近傍に沿って遮光性材料からなる平面視矩形枠状の遮光膜 48 が対向基板 63 に形成されており、この遮光膜 48 の内側の領域が表示領域 40 となっている。遮光膜 48 は、例えば、遮光性材料であるアルミニウム（Al）で形成されており、対向基板 63 側の表示領域 40 の外周を区画する様に、更に、上記した様に、表示領域 40 内で走査線 42 と信号線 43 に対向して設けられている。

30

## 【0034】

図 4 に示す様に、素子基板 62 の液晶 46 側には、複数の画素電極 45 が形成されており、これら画素電極 45 を覆う様に第 1 配向膜 65 が形成されている。画素電極 45 は、インジウム錫酸化物（ITO）等の透明導電材料からなる導電膜である。一方、対向基板 63 の液晶 46 側には、格子状の遮光膜 48 が形成され、その上に平面ベタ状の共通電極 47 が形成されている。そして、共通電極 47 上には、第 2 配向膜 66 が形成されている。共通電極 47 は、ITO 等の透明導電材料からなる導電膜である。

40

## 【0035】

液晶装置は透過型であって、素子基板 62 及び対向基板 63 における光の入射側と出射側とにそれぞれ偏光板（図示せず）等が配置されて用いられる。尚、液晶装置の構成は、これに限定されず、反射型や半透過型の構成であってもよい。

## 【0036】

この様に、電気光学装置 200 は、表示領域 40 と駆動回路 51（図 4 では、信号線駆

50

動回路 5 3 が図示) と実装領域 2 0 とを有する素子基板 6 2 を備えている。実装領域 2 0 は、表示領域 4 0 と素子基板 6 2 の外周の一辺 6 7 との間に配置されている。駆動回路 5 1 は表示領域 4 0 と素子基板 6 2 の外周の一辺 6 7 との間に配置されると共に、表示領域 4 0 と実装領域 2 0 との間に配置されている。即ち、表示領域 4 0 の外側に駆動回路 5 1 が配置され、駆動回路 5 1 の更に外側に実装領域 2 0 が形成されている。

### 【0037】

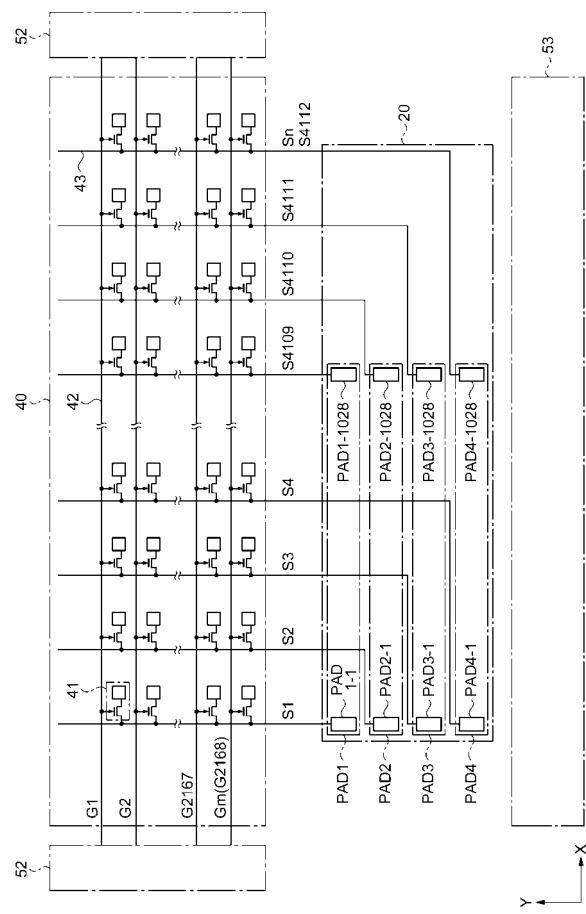

#### 「信号線駆動回路及び実装領域」

図 5 は、実施形態 1 に係わる信号線駆動回路の回路構成と実装領域の構成とを説明した図である。次に、図 5 を参照して信号線駆動回路 5 3 及び実装領域 2 0 の構成を説明する。

10

### 【0038】

信号線駆動回路 5 3 は、 $n$  本の信号線 4 3 の各々にプリチャージ信号と画像信号とを供給する事ができる。まず、 $n$  本の信号線 4 3 は  $k$  個の信号線群に分類される ( $k$  は 2 以上の整数)。即ち、系列信号が  $k$  種類あり、これに応じて、 $n$  本の信号線 4 3 は、第 1 系列の信号線 (第 1 系列信号線群と称す) から第  $k$  系列の信号線 (第  $k$  系列信号線群と称す) まで、 $k$  種類の信号線群に分類される。 $(j k + p)$  列目の信号線  $S_{j k + p}$  にて  $p$  は 1 から  $k$  迄のいずれかの値を取り、 $(j k + p)$  列目の信号線  $S_{j k + p}$  は第  $p$  系列信号線群に属する。又、パラメーター  $j$  は 0 から  $q$  までのいずれかの整数値を取り得る。数値  $q$  はパラメーター  $j$  の最大値で、信号線 4 3 の本数  $n$  を系列数  $k$  にて除した値から 1 を減じた値である ( $q = n / k - 1$ ) である。本実施形態では、一例として、 $n = 4112$  とし、 $k = 4$  としているので、パラメーター  $j$  が取り得る最大値  $q$  は 1027 ( $q = 1027$ ) である。従って、第 1 系列信号線群は  $(j k + 1)$  列目の信号線  $S_{j k + 1}$  の集合体であり、具体的には、 $j = 0$  の 1 列目の信号線  $S_1$ 、 $j = 1$  の 5 列目の信号線  $S_5$ 、 $j = 2$  の 9 列目の信号線  $S_9$ 、 $\dots$ 、 $j = 1027$  の 4109 列目の信号線  $S_{4109}$ 、迄の 1028 本の信号線 4 3 が含まれる。同様に、第 2 系列信号線群は  $(j k + 2)$  列目の信号線  $S_{j k + 2}$  の集合体であり、具体的には、 $j = 0$  の 2 列目の信号線  $S_2$ 、 $j = 1$  の 6 列目の信号線  $S_6$ 、 $j = 2$  の 10 列目の信号線  $S_{10}$ 、 $\dots$ 、 $j = 1027$  の 4110 列目の信号線  $S_{4110}$ 、迄の 1028 本の信号線 4 3 が含まれる。以下同様にして、第  $k$  系列信号線群は  $(j k + k)$  列目の信号線  $S_{j k + k}$  の集合体であり、具体的には、 $j = 0$  の  $k$  列目の信号線  $S_k$ 、 $j = 1$  の  $2k$  列目の信号線  $S_{2k}$ 、 $j = 2$  の  $3k$  列目の信号線  $S_{3k}$ 、 $\dots$ 、 $j = q$  の  $(q + 1)k$  列目の信号線  $S_{(q + 1)k}$  (今の例では、 $j = 1028$  の 4112 列目の信号線  $S_{4112}$ ) の 1028 本の信号線 4 3 が含まれる。

20

30

40

### 【0039】

信号線駆動回路 5 3 には、 $k$  種類の系列信号に対応する  $k$  本の系列線と、 $(q + 1)$  本の元信号線が配線されている。第  $p$  系列線には第  $p$  系列信号  $S_{E L p}$  が供給される ( $p$  は 1 から  $k$  迄の任意の整数)。例えば、第 1 系列線には第 1 系列信号  $S_{E L 1}$  が供給され、第 2 系列線には第 2 系列信号  $S_{E L 2}$  が供給され、以下同様にして、第  $k$  系列線には第  $k$  系列信号  $S_{E L k}$  が供給される。第  $j$  元信号線には第  $j$  元信号  $O S_j$  が供給される。例えば、第 0 元信号線には第 0 元信号  $O S_0$  が供給され、第 1 元信号線には第 1 元信号  $O S_1$  が供給され、以下同様にして、第  $q$  元信号線には第  $q$  元信号  $O S_q$  が供給される。

40

### 【0040】

信号線駆動回路 5 3 には、 $q + 1$  個 (即ち、 $n / k$  個) の第 1 スイッチ  $S_{W1}$  から  $q + 1$  個 (即ち、 $n / k$  個) の第  $k$  スイッチ  $S_{Wk}$  が含まれている。第 1 スイッチ  $S_{W1}$  から第  $k$  スイッチ  $S_{Wk}$  は、画素トランジスター 4 4 と同様に、薄膜トランジスターで形成されている。第  $p$  スイッチ  $S_{Wp}$  の一端 (ソースとドレインとの一方) は  $(j k + p)$  列目の信号線  $S_{j k + p}$  に電気的に接続され、第  $p$  スイッチ  $S_{Wp}$  の他端 (ソースとドレインとの他方) は第  $j$  元信号線に電気的に接続され、第  $p$  スイッチ  $S_{Wp}$  のゲートは第  $p$  系列線に電気的に接続されている。従って、第  $p$  系列信号  $S_{E L p}$  が選択信号となれば、第  $p$  スイッチ  $S_{Wp}$  はオン状態となり、 $(j k + p)$  列目の信号線  $S_{j k + p}$  には、プリチャージ信号又は画像信号として、第  $j$  元信号  $O S_j$  が供給される。例えば、第 1 系列信号線

50

群に属する1列目の信号線S1と第0元信号線との間に第1スイッチSW1が配置され、第1スイッチSW1のゲートは第1系列線に電気的に接続されている。その為に、第1系列信号SEL1が選択信号となれば、第1スイッチSW1はオン状態となり、1列目の信号線S1には、プリチャージ信号又は画像信号として、第0元信号OS0が供給される。同様に、例えば、第4系列信号線群に属する4112列目の信号線S4112と第1027元信号線との間に第4スイッチSW4が配置され、第4スイッチSW4のゲートは第4系列線に電気的に接続されている。その為に、第4系列信号SEL4が選択信号となれば、第4スイッチSW4はオン状態となり、4112列目の信号線S4112には、プリチャージ信号又は画像信号として、第1027元信号OS1027が供給される。

【0041】

10

尚、本明細書にて、端子1と端子2とが電気的に接続されているとは、端子1と端子2とが同じ論理状態（設計概念上の電位）になり得る事を意味している。具体的には、端子1と端子2とが配線により直に接続されている場合の他に、抵抗素子やスイッチング素子等を介して接続されている場合を含む。即ち、端子1での電位と端子2での電位とが多少異なっていても、回路上で同じ論理を持たせる場合、端子1と端子2とは電気的に接続されている事になる。従って、例えば、図5に示す様に、1列目の信号線S1と第0元信号線との間に第1スイッチSW1が配置された場合も、第1スイッチSW1がオン状態では、第0元信号が1列目の信号線S1に供給されるので、1列目の信号線S1と第0元信号線とは電気的に接続されている事になる。

【0042】

20

$q + 1$ 本の元信号線（第0元信号線から第 $q$ 元信号線）は其々実装領域20にて端子PADに接続する。一本の元信号線に対して一つの端子が形成されるので、端子PADの数は $q + 1$ 個と非常に多くなる。そこで、実装領域20では $q + 1$ 個の端子PADをs行t列の行列状に配置する（sは2以上の整数、 $t = (q + 1) / s$ ）。本実施形態では、 $q + 1 = 1028$ であるので、 $s = 4$ 、 $t = 257$ として、端子PADを4行257列の行列状に配置している。例えば、第0元信号線は1行1列の端子PAD1-1に電気的に接続され、第1元信号線は1行2列の端子PAD1-2に電気的に接続され、以下同様にして、第1027元信号線は4行257列の端子PAD4-257に電気的に接続されている。尚、1行1列の端子PAD1-1から1行257列の端子PAD1-257迄が第1行目の端子PAD1である。同様に、2行1列の端子PAD2-1から2行257列の端子PAD2-257迄が第2行目の端子PAD2であり、3行1列の端子PAD3-1から3行257列の端子PAD3-257迄が第3行目の端子PAD3であり、4行1列の端子PAD4-1から4行257列の端子PAD4-257迄が第4行目の端子PAD4である。

30

【0043】

制御装置30と駆動回路51とは不図示のFPCを介して接続されている。FPCの接続部には接続領域が設けられており、接続領域には実装領域20に配置された端子PADと同じピッチで対応する接続端子が形成されている。FPCの接続端子と実装領域20の端子PADとは異方性導電フィルム（Anisotropic Conductive Film；ACF）や異方性導電ペースト（Anisotropic Conductive Paste；ACP）を用いて接続される。

40

【0044】

尚、端子PADと配線とはアルミニウムや銅などの金属で形成され、これら金属は酸化珪素膜等の絶縁膜に覆われている。端子PADでは、FPCへの接触用に絶縁膜に開口部が設けられている。更に、端子PADの信頼性を増す為に、画素電極45を構成する導電材料（インジウム錫酸化物等）にて開口部を覆っていても良い。

【0045】

「配線形状」

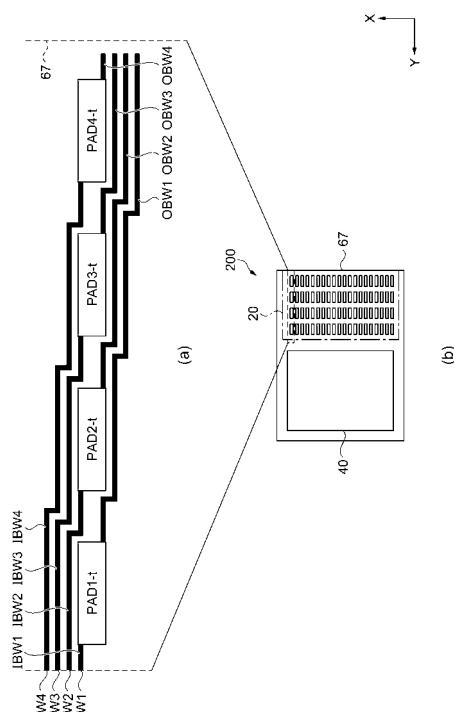

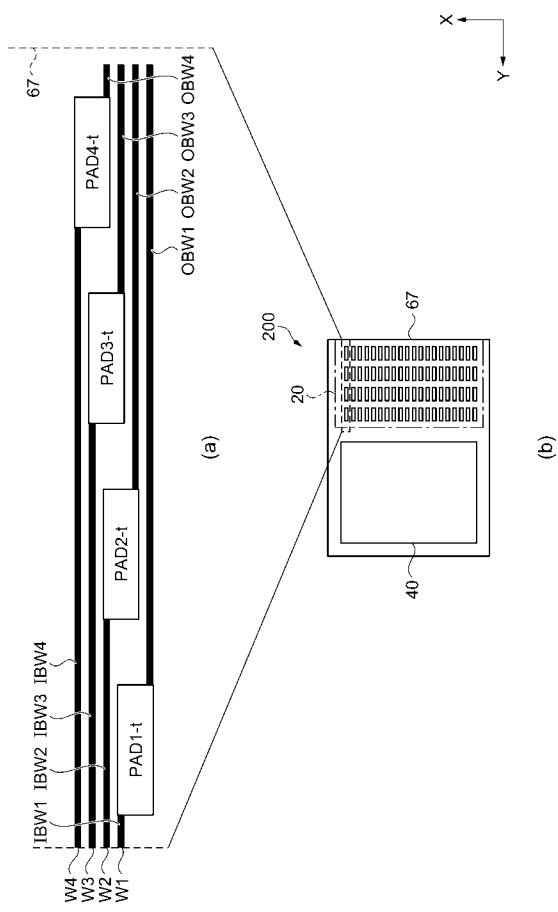

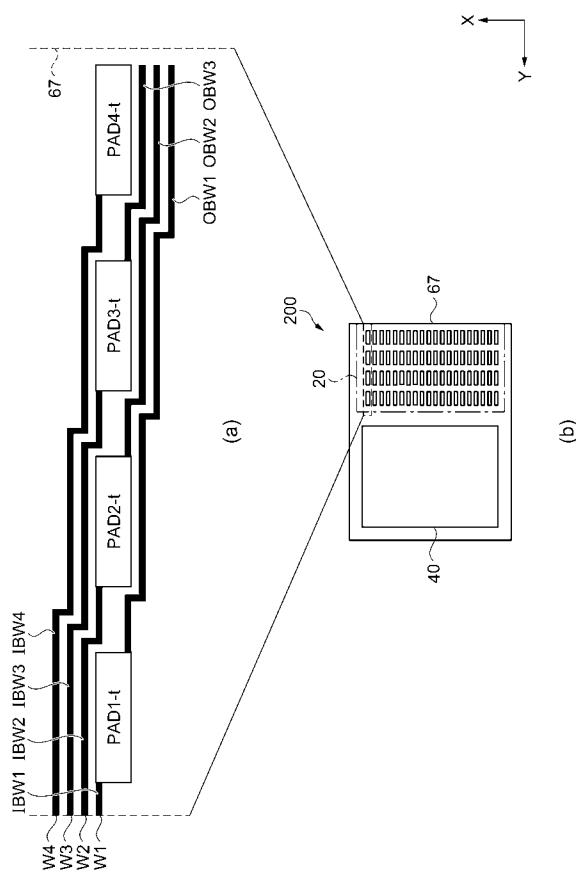

図6は、実施形態1に係わる配線形状を説明する図で、（a）は一列分の端子に係わる配線形状を説明する図で、（b）は電気光学装置の構成を説明する概略平面図である。又

50

、図7は、実施形態1に係わる配線形状を説明する図で、複数列分の端子に係わる配線形状を説明する図である。図8は、本発明の原理を説明する図である。図14は、比較例に係わる配線形状を説明する図で、(a)は一列分の端子に係わる配線形状を説明する図で、(b)は電気光学装置の構成を説明する概略平面図である。次に、図6乃至8と図14とを参照して、配線形状及び本発明の原理を説明する。尚、図14は従来技術に相当する比較例を説明する図であるが、説明を分かり易くする為に、本実施形態と同種類の構成には同じ符号や表記を用いている。

#### 【0046】

図5は回路構成を説明する等価回路図であるので、電気光学装置200に於ける実際の配線形状はこれとは異なっている。まず、図6と図7とを参照して、実装領域20に於ける配線形状を説明する。

10

#### 【0047】

図6(b)に示す様に、実装領域20は、素子基板62の表示領域40と素子基板62の外周の一辺67との間に配置されている。図6(a)は実装領域20の一部を拡大して描いたもので、具体的には実装領域20に於けるt列目の端子PAD(1行t列の端子PAD1-tから4行t列の端子PAD4-t迄の端子PAD)とそれに接続する配線とを説明している。図6(a)に示す様に、第1行目の端子PAD1は、表示領域40と素子基板62の外周の一辺67との間に配置され、第2行目の端子PAD2は、第1行目の端子PAD1と外周の一辺67との間に配置され、以下同様にして、第s行目の端子PADsは、第s-1行目の端子PADs-1と外周の一辺67との間に配置される。即ち、第1行目の端子PAD1が最も内側に位置して表示領域40に最も近く、第s行目の端子PADsが最も外側(素子基板62の外周の一辺67側)に位置して表示領域40から最も離れている。

20

#### 【0048】

図6(a)に示す様に、実装領域20には、第1行目の端子PAD1に接続する第1の配線W1と、第2行目の端子PAD2に接続する第2の配線W2と、以下同様に第s行目の端子PADsに接続する第sの配線Wsとが形成されている。第1の配線W1は、表示領域40と外周の一辺67との間に延在している。即ち、第1の配線W1は、第1行目の端子PAD1から表示領域40に向かう第1のインバウンド配線IBW1と、第1行目の端子PAD1から素子基板62の外周の一辺67に向かう第1のアウトバウンド配線OBW1とを有している。第1のインバウンド配線IBW1は表示領域40と第1行目の端子PAD1の間に延在しており、第1のアウトバウンド配線OBW1は第1行目の端子PAD1と素子基板62の外周の一辆67との間に延在している。

30

#### 【0049】

同様に、第2の配線W2は、表示領域40と外周の一辆67との間に延在している。即ち、第2の配線W2は、第2行目の端子PAD2から表示領域40に向かう第2のインバウンド配線IBW2と、第2行目の端子PAD2から素子基板62の外周の一辆67に向かう第2のアウトバウンド配線OBW2とを有している。第2のインバウンド配線IBW2は表示領域40と第2行目の端子PAD2の間に延在しており、第2のアウトバウンド配線OBW2は第2行目の端子PAD2と素子基板62の外周の一辆67との間に延在している。

40

#### 【0050】

以下同様にして、第sの配線Wsは、表示領域40と外周の一辆67との間に延在している。即ち、第sの配線Wsは、第s行目の端子PADsから表示領域40に向かう第sのインバウンド配線IBWsと、第s行目の端子PADsから素子基板62の外周の一辆67に向かう第sのアウトバウンド配線OBWsとを有している。第sのインバウンド配線IBWsは表示領域40と第s行目の端子PADsの間に延在しており、第sのアウトバウンド配線OBWsは第s行目の端子PADsと素子基板62の外周の一辆67との間に延在している。

#### 【0051】

50

第1行目の端子 P A D 1 は表示領域 4 0 に最も近い位置に配置されているので、第1のインバウンド配線 I B W 1 はその他のインバウンド配線 I B W よりも短い。反対に、第 s 行目の端子 P A D s は表示領域 4 0 から最も離れた位置に配置されているので、第 s のインバウンド配線 I B W s はその他のインバウンド配線 I B W よりも長い。これに対して、第1行目の端子 P A D 1 は表示領域 4 0 に最も近い位置に配置されているので、第1のアウトバウンド配線 O B W 1 はその他のアウトバウンド配線 O B W よりも長い。反対に、第 s 行目の端子 P A D s は表示領域 4 0 から最も離れた位置に配置されているので、第 s のアウトバウンド配線 O B W s はその他のアウトバウンド配線 O B W よりも短い。この様に、インバウンド配線 I B W の長さは第1行目の端子 P A D 1 から第 s 行目の端子 P A D s へと行毎に長くなり、反対に、アウトバウンド配線 O B W の長さは第1行目の端子 P A D 1 から第 s 行目の端子 P A D s へと行毎に短くなる。この結果、第1の配線 W 1 から第 s の配線 W s 迄、総ての配線の長さ（第1の配線 W 1 の長さと第2の配線 W 2 の長さと、と続き、第 s の配線 W s の長さと）がほぼ等しくなっている。実際には、第1の配線 W 1 から第 s の配線 W s 迄、総ての配線の長さがほぼ等しくなる様に第1のアウトバウンド配線 O B W 1 から第 s のアウトバウンド配線 O B W s 迄が配置される。

10

## 【0052】

各インバウンド配線 I B W は、隣り合うインバウンド配線 I B W 間の距離がほぼ等しくなる様に配置される。具体的には、第1のインバウンド配線 I B W 1 とその隣に位置する第2のインバウンド配線 I B W 2 との距離と、第2のインバウンド配線 I B W 2 とその隣に位置する第3のインバウンド配線 I B W 3 との距離と、第3のインバウンド配線 I B W 3 とその隣に位置する第4のインバウンド配線 I B W 4 との距離と、第4のインバウンド配線 I B W 4 とその隣に位置する第1のインバウンド配線 I B W 1 との距離とは、ほぼ等しくなっている。

20

## 【0053】

又、各アウトバウンド配線 O B W は、隣り合うアウトバウンド配線 O B W 間の距離がほぼ等しくなる様に配置される。具体的には、第1のアウトバウンド配線 O B W 1 とその隣に位置する第2のアウトバウンド配線 O B W 2 との距離と、第2のアウトバウンド配線 O B W 2 とその隣に位置する第3のアウトバウンド配線 O B W 3 との距離と、第3のアウトバウンド配線 O B W 3 とその隣に位置する第4のアウトバウンド配線 O B W 4 との距離と、第4のアウトバウンド配線 O B W 4 とその隣に位置する第1のアウトバウンド配線 O B W 1 との距離とは、ほぼ等しくなっている。加えて、隣り合うインバウンド配線 I B W 間の距離と、隣り合うアウトバウンド配線 O B W 間の距離とは、ほぼ等しくなっている。

30

## 【0054】

インバウンド配線 I B W は、実装領域 2 0 から信号線駆動回路 5 3 へと、隣り合うインバウンド配線 I B W 間の距離をほぼ等しく保った直線にて接続され、元信号線となる。具体的に数例を述べると、1行1列の端子 P A D 1 - 1 のインバウンド配線 I B W ( 1 列目の第1のインバウンド配線 I B W 1 ) はそのまま第0元信号線となり、2行1列の端子 P A D 2 - 1 のインバウンド配線 I B W ( 1 列目の第2のインバウンド配線 I B W 2 ) はそのまま第1元信号線となり、4行257列の端子 P A D 4 - 2 5 7 のインバウンド配線 I B W ( 2 5 7 列目の第4のインバウンド配線 I B W 4 ) はそのまま第1027元信号線となる。又、アウトバウンド配線 O B W は、以下に述べる寄生容量を揃える効果の他には回路上の機能はなく、所謂ダミー配線である。

40

## 【0055】

図7は、上述の構成とした際に、複数列分の端子とそれに係わる配線の形状を説明している。各配線の長さがほぼ等しく、隣り合う配線との間隔の関係も総ての配線で同等となっている。即ち、第1の配線 W 1 と第2の配線 W 2 と第3の配線 W 3 と第4の配線 W 4 とでは、総て配線長がほぼ等しく、且つ、隣り合う配線間の距離（配線間隔）もほぼ等しくなっている。

## 【0056】

図8は上述の構成がもたらす効果を定性的に説明した図で、総ての配線に関して、配線

容量が同程度となっている事を表している。上述の構成とすると、具体的には、第1の配線W1が有する容量（第1配線容量）と第2の配線W2が有する容量（第2配線容量）と第3の配線W3が有する容量（第3配線容量）と第4の配線W4が有する容量（第4配線容量）とは同程度となる。図8に示す様に、例えば、第2の配線W2に関しては、上隣の第3の配線W3との間に上側寄生容量C1を有し、下隣の第1の配線W1との間に下側寄生容量C2を有し、これらの上側寄生容量C1と下側寄生容量C2とは、ほぼ等しくなる。上側寄生容量C1と下側寄生容量C2とが等しい関係は第1の配線W1に対しても、第2の配線W2に対しても、第3の配線W3に対しても、第4の配線W4に対しても、総ての配線に対して成り立つ。その結果、第1配線容量と第2配線容量と第3配線容量と第4配線容量とは（総ての配線容量は）ほぼ等しくなる。又、配線抵抗もほぼ等しくされているので、第1の配線W1に於ける信号伝達の時定数（第1配線の時定数）と第2の配線W2に於ける信号伝達の時定数（第2配線の時定数）と第3の配線W3に於ける信号伝達の時定数（第3配線の時定数）と第4の配線W4に於ける信号伝達の時定数（第4配線の時定数）とが、総て皆、同程度となる。この結果、第1配線の時定数と第2配線の時定数と第3配線の時定数と第4配線の時定数との相違に起因する表示ムラを抑制する事ができる。この様にして、表示ムラが抑制された高精細画像を表示する電気光学装置200を実現する事ができる。

10

## 【0057】

一般に、FPCの制約や端子PAD面積の確保等の理由により、端子PADの行間の距離が数mm程度に及び、例えば四行の実装であれば全体で10mm弱程度に及ぶ状況である。斯うした場合、図14に示される比較例では、各配線（元信号線）に付随する配線容量（隣接配線間容量等）に大きな差異が生じ、大きな配線容量差が生じ得る事となる。配線（元信号線）に配線容量差がある場合、その差異に起因して表示画像にムラが視認される場合があるが、本実施形態の構成は、この課題を確実に改善する事ができる。

20

## 【0058】

尚、厳密には、制御装置30の出力ピンから駆動回路51迄の時定数が総ての配線で揃う事が均一な画像表示を実現する。従って、FPCに於ける配線の時定数とインバウンド配線IBWの時定数との和が揃う必要がある。但し、FPCでの配線はパネルでの配線よりも十分に太くて低抵抗であり、FPCでの配線間の距離も大きいために配線間の寄生容量も小さく、FPCの配線での時定数は、インバウンド配線IBWの時定数に比較して非常に小さい。従って、電気光学装置200の端子PADで元信号を受ける際には、信号遅延にはらつきは殆ど問題にならない（非常に小さい）。図14に示される従来技術では、電気光学装置200での配線の配線容量が異なる為に、信号遅延にはらつきが発生し、表示ムラが現れる事もあった。これに対して、本実施形態では、第1配線の時定数も第2配線の時定数も第3配線の時定数も第4配線の時定数も皆同程度に揃う為、信号遅延に起因する表示ムラを抑制する事ができる。

30

## 【0059】

又、本明細書にて「ほぼ等しい」とは、設計概念上等しい事を意味する。即ち、多少の誤差等が生じっていても、設計概念で意図的に異ならせた他は「ほぼ等しい」と言える。

40

## 【0060】

## 「他の電子機器」

電気光学装置200は上述の構成をなすが、この電気光学装置200を組み込んだ電子機器としては、図1を参照して説明したプロジェクターの他にも、リアプロジェクション型テレビ、直視型テレビ、携帯電話、携帯用オーディオ機器、パソコンコンピューター、ビデオカメラのモニター、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、ディジタルスチルカメラなどを挙げる事ができる。

## 【0061】

## (実施形態2)

## 「配線形状が異なる形態1」

50

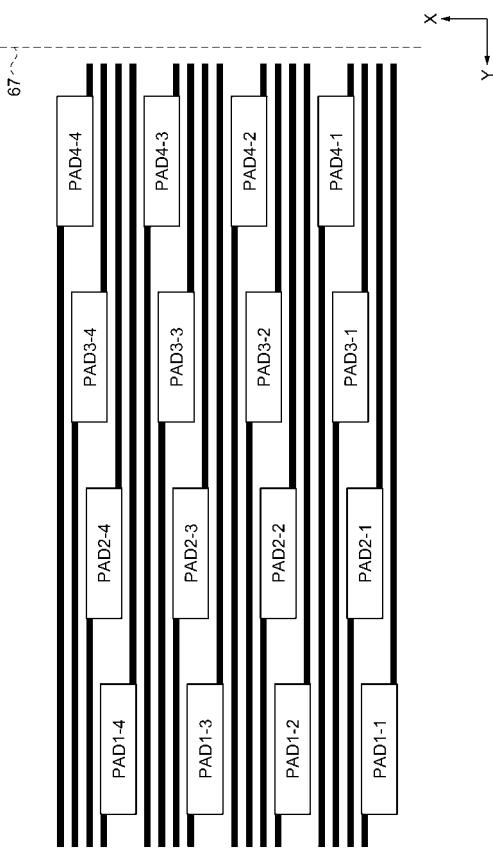

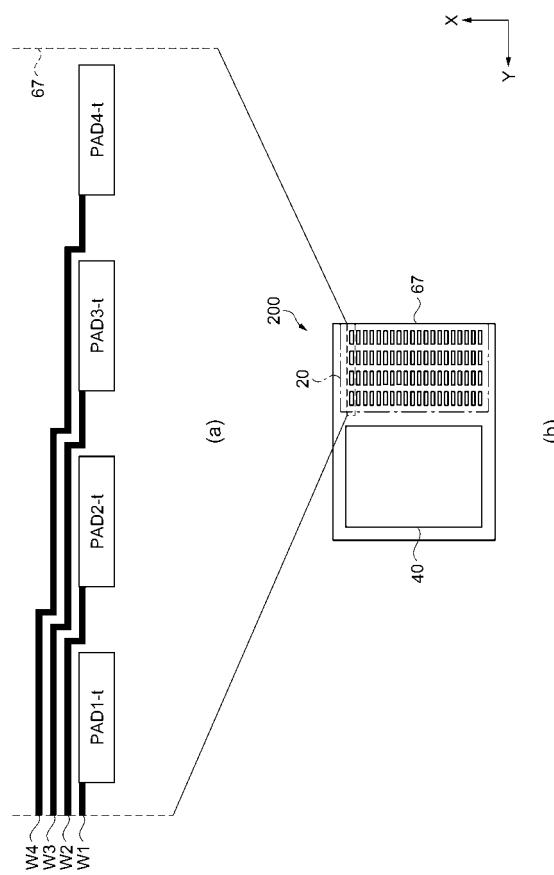

図9は、実施形態2に係わる配線形状を説明する図で、(a)は一列分の端子に係わる配線形状を説明する図で、(b)は電気光学装置の構成を説明する概略平面図である。又、図10は、実施形態2に係わる配線形状を説明する図で、複数列分の端子に係わる配線形状を説明する図である。次に、図9乃至10を参照して、実施形態2に係わる電気光学装置200を説明する。尚、実施形態1と同一の構成部位については、同一の符号を附し、重複する説明は省略する。

#### 【0062】

図9に示す本実施形態の電気光学装置200は、図6に示された実施形態1の電気光学装置200と比べて、実装領域20に於ける配線形状が異なっている。それ以外の構成は、実施形態1とほぼ同様である。

10

#### 【0063】

実施形態1の電気光学装置200(図6)では、配線が約90°曲がる屈曲部が見られた。これに対して、図9に示す様に、本実施形態の電気光学装置200は、端子PADに接続する総ての配線(第1の配線W1と、第2の配線W2と、と続き、第sの配線Wsと迄、本実施形態ではs=4)が、少なくとも実装領域20に於いては、直線である。更に、少なくとも実装領域20に於いては、各配線の長さ(インバウンド配線IBWの長さとアウトバウンド配線OBWの長さとの和)が等しくなっている。斯うした構成を為す結果、総ての配線(第1の配線W1と第2の配線W2と第3の配線W3と第4の配線W4)とで屈曲部が解消されているので、屈曲部に於ける信号反射の影響を回避する事ができる。この結果、配線に高速で信号を伝送する事ができる様になる。

20

#### 【0064】

図7に示す実施形態1では、s行t列に配列された端子PADは、行方向の位置が揃うと共に列方向の位置も揃っていた。一方、図10に示す様に、本実施形態の電気光学装置200では、s行t列に配列された端子PADは、行方向(X軸に平行な方向で、インバウンド配線IBWの延在方向に直交する方向)では行毎に位置が揃っているものの(各行で端子PADのY座標がほぼ等しい)、列方向(Y軸に平行な方向で、インバウンド配線IBWの延在方向)の位置に関しては、行毎に一定のオフセット量を以てずれている(同じ列のs個の端子で端子PADのX座標が一定量ずつずれている)。例えば、同じ列に関して、2行目の端子PAD2は1行目の端子PAD1に対してX座標の値が所定量ずれており、3行目の端子PAD3は2行目の端子PAD2に対してX座標の値が先の所定量と同じ量ずれており、4行目の端子PAD4は3行目の端子PAD3に対してX座標の値が先の所定量と同じ量ずれており、その隣の列の1行目の端子PAD1は前の列のs行目の端子PADsに対してX座標の値が先の所定量と同じ量ずれている。この様に行毎に端子の列方向の座標が同じ量だけずれている。斯うする事で、端子PADに接続する総ての配線(第1の配線W1と、第2の配線W2と、と続き、第sの配線Wsと迄、本実施形態ではs=4)が、少なくとも実装領域20に於いては、直線となっている。なお実施形態2において、実装時のアライメントに使用するマーク(図示せず)のX座標を各実装端子行において同一にしておけば、FPCの貼り付け時における取り違い(所謂ポカミス)を回避することもできる。

30

#### 【0065】

(実施形態3)

40

「配線形状が異なる形態2」

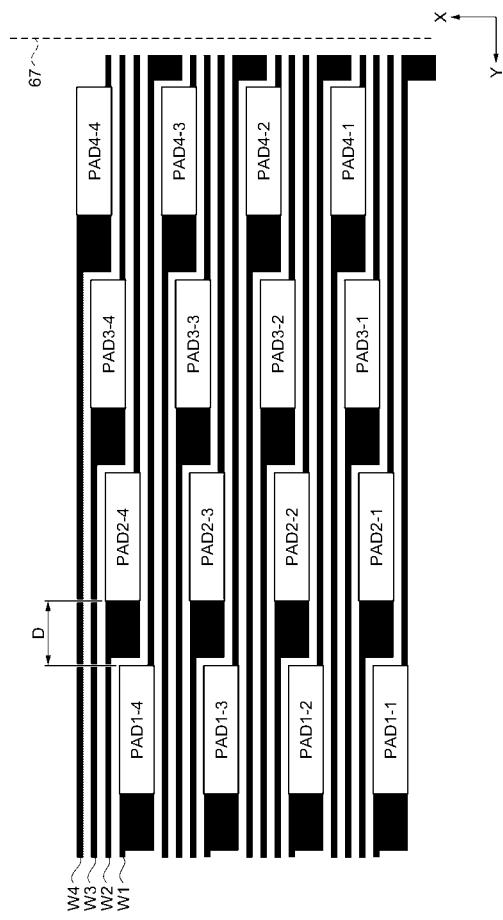

図11は、実施形態3に係わる配線形状を説明する図で、複数列分の端子に係わる配線形状を説明する図である。次に、図11を参照して、実施形態3に係わる電気光学装置200を説明する。尚、実施形態2と同一の構成部位については、同一の符号を附し、重複する説明は省略する。

#### 【0066】

図11に示す本実施形態の電気光学装置200は、図10に示された実施形態2の電気光学装置200と比べて、実装領域20に於ける配線形状が異なっている。それ以外の構成は、実施形態2とほぼ同様である。

50

## 【0067】

実施形態2の電気光学装置200(図10)では、列方向に隣り合う端子PADの間が広がっていた。例えば、1行4列のPAD1-4と2行4列のPAD2-4との間には配線のない平面空間が広がっていた。この為に、この平面空間に於いては第1のアウトバウンド配線OBW1と第2のインバウンド配線IBW2との距離は、インバウンド配線IBW間の距離よりも大きくなっている。この部分では第1のアウトバウンド配線OBW1と第2のインバウンド配線IBW2との容量値が小さくなっていた。これに対して、本実施形態では、図11に示す様に、各インバウンド配線IBWの幅は、そのインバウンド配線IBWが接続する端子PADとの接続部に於いて、インバウンド配線IBWの幅の平均値よりも大きくなっている。例えば、1行4列のPAD1-4と2行4列のPAD2-4との間(図11にてDで示す部位)で、第2の配線W2の幅は、第2行目の端子PAD2との接続部に於いて、第2の配線W2の幅の平均値よりも大きくなっている。より具体的には、各インバウンド配線IBWの幅は、そのインバウンド配線IBWが接続する端子PADとの接続部に於いては、インバウンド配線IBWの幅(インバウンド配線IBWの行方向の長さ)と端子PADの幅(端子PADの行方向の長さ)とがほぼ一致している。斯うすると、総ての配線間距離がほぼ等しくなる。例えば、1行4列のPAD1-4と2行4列のPAD2-4との間(図11にてDで示す部位)にも太い第2の配線W2が形成されている。この為に、図11にてDで示す部位に於いても第1のアウトバウンド配線OBW1と第2のインバウンド配線IBW2との距離は、インバウンド配線IBW間の距離やアウトバウンド配線OBW間の距離にはほぼ等しくなり、第1配線容量と第2配線容量とを同程度とする事ができる。即ち、端子PADに接続する総ての配線容量を同程度とする事ができる。更に、図11にてDで示す部位のインバウンド配線IBWが太くなり、インバウンド配線IBWの配線抵抗が下がるので、総ての配線に於いて配線時定数(第1配線の時定数から第s配線の時定数)の増大を抑制する事ができる。

10

20

30

## 【0068】

(実施形態4)

「接続関係が異なる形態」

図12は、実施形態4に係わる電気光学装置の回路構成と実装領域の構成とを説明した図である。次に、図12を参照して、実施形態4に係わる信号線駆動回路53及び実装領域20の構成を説明する。尚、実施形態1乃至3と同一の構成部位については、同一の符号を附し、重複する説明は省略する。

40

## 【0069】

図12に示す本実施形態の電気光学装置200は、図5に示された実施形態1の電気光学装置200と比べて、端子PADと回路との配置関係が異なっている。それ以外の構成は、実施形態1とほぼ同様である。

## 【0070】

実施形態1乃至3(図5)では、信号線駆動回路53が薄膜素子にて素子基板62に形成されていた。これに対して、本実施例では、信号線駆動回路53は単結晶半導体基板に形成される半導体集積回路で構成されている。この為に、端子の数は画素41の列数nとなる。端子PADは実装領域20にてs行t列(s t = n)に配列され、各端子PADからのインバウンド配線IBWは信号線43となる。本実施形態では、n = 4112で、s = 4、t = 1028である。信号線駆動回路53と端子PADとは不図示のFPCを介して接続されている。

50

## 【0071】

実装領域20は表示領域40の外側で表示領域40に沿って形成され、表示領域40と外周の一辺67との間に配置される。各端子PADには信号線駆動回路53より、不図示のFPCを介して、プリチャージ信号や画像信号が供給され、プリチャージ信号や画像信号は、n本の信号線43に供給される。各端子PADに於いて、インバウンド配線IBWとアウトバウンド配線OBWとの関係は実施形態1乃至3と同様である。

## 【0072】

本発明は上述した実施形態に限定されず、上述した実施形態に種々の変更や改良などを加えることが可能である。変形例を以下に説明する。

【0073】

(変形例1)

「アウトバウンド配線が異なる形態」

図13は、変形例1に係わる配線形状を説明する図で、(a)は一列分の端子に係わる配線形状を説明する図で、(b)は電気光学装置の構成を説明する概略平面図である。次に、図13を参照して、変形例1に係わる電気光学装置200を説明する。尚、実施形態1乃至4と同一の構成部位については、同一の符号を附し、重複する説明は省略する。

10

【0074】

図13に示す本変形例の電気光学装置200は、図6に示された実施形態1の電気光学装置200と比べて、アウトバウンド配線OBWが異なっている。それ以外の構成は、実施形態1とほぼ同様である。

【0075】

実施形態1(図6)では、s行目端子PADsにも第sのアウトバウンド配線OBWsが配置されていた。これに対し、本変形例では、s行目の端子PADsにはアウトバウンド配線OBWが形成されていない。表示領域40から最も離れ、素子基板62の外周の一辺67に最も近い最終行(s行目)の端子PADsにはアウトバウンド配線OBWを形成しなくても良い。この場合も、少なくとも実装領域20に於いては、各端子に関し、インバウンド配線IBWの長さとアウトバウンド配線OBWの長さとの和が、等しくなる様にする。本変形例の様にs=4であれば、第1のインバウンド配線IBW1の長さと第1のアウトバウンド配線OBW1の長さとの和が、第2のインバウンド配線IBW2の長さと第2のアウトバウンド配線OBW2の長さとの和に等しく、更に、第3のインバウンド配線IBW3の長さと第3のアウトバウンド配線OBW3の長さとの和に等しく、更に、第4のインバウンド配線IBW4の長さに等しくする。斯うした構成としても、実施形態1乃至4と同じ効果が得られる。

20

【0076】

(変形例2)

「アウトバウンド配線の延在する終点が異なる形態」

これまでの実施例ではアウトバウンド配線OBWについては外周の一辺67の手前(表示領域40側)を終点としているが、外周の一辺67に到達していてもよい。あるいは外周の一辺67を超えて延在させて形成し、その後の製造工程で外周の一辺67の位置で切断する過程を経てもよい。

30

【符号の説明】

【0077】

Gi...i行目の走査線、IBW1...第1のインバウンド配線、IBW2...第2のインバウンド配線、IBW3...第3のインバウンド配線、IBW4...第4のインバウンド配線、OSj...第j元信号、OBW1...第1のアウトバウンド配線、OBW2...第2のアウトバウンド配線、OBW3...第3のアウトバウンド配線、OBW4...第4のアウトバウンド配線、PAD1...第1行目の端子、PAD2...第2行目の端子、PAD3...第3行目の端子、PAD4...第4行目の端子、SEL1...第1系列信号、SEL2...第2系列信号、SEL3...第3系列信号、SEL4...第4系列信号、Sjk+p...(jk+p)列目の信号線、SW1...第1スイッチ、SW2...第2スイッチ、SW3...第3スイッチ、SW4...第4スイッチ、W1...第1の配線、W2...第2の配線、W3...第3の配線、W4...第4の配線、20...実装領域、30...制御装置、32...表示用信号供給回路、33...記憶回路、40...表示領域、41...画素、42...走査線、43...信号線、44...画素トランジスター、45...画素電極、46...液晶、47...共通電極、48...遮光膜、50...駆動部、51...駆動回路、52...走査線駆動回路、53...信号線駆動回路、62...素子基板、63...対向基板、64...シール材、65...第1配向膜、66...第2配向膜、67...外周の一辺、200...電気光学装置、201...第一パネル、202...第二パネル、203...第三パネル、100

40

50

0 … 投射型表示装置、 1 1 0 0 … 照明光学系、 1 3 0 0 … 投射光学系、 1 4 0 0 … 投射面。

。

【図1】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

(b)

【図 1 4】

(b)