(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7680860号**

**(P7680860)**

(45)発行日 令和7年5月21日(2025.5.21)

(24)登録日 令和7年5月13日(2025.5.13)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 25/78 (2023.01)  | H 0 4 N | 25/78  |

| H 0 4 N | 25/633 (2023.01) | H 0 4 N | 25/633 |

| H 0 4 N | 25/60 (2023.01)  | H 0 4 N | 25/60  |

請求項の数 22 (全29頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-42595(P2021-42595)   |

| (22)出願日  | 令和3年3月16日(2021.3.16)        |

| (65)公開番号 | 特開2022-142433(P2022-142433) |

|          | A)                          |

| (43)公開日  | 令和4年9月30日(2022.9.30)        |

| 審査請求日    | 令和6年3月12日(2024.3.12)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 100094112<br>弁理士 岡部 譲                      |

| (74)代理人  | 100101498<br>弁理士 越智 隆夫                     |

| (74)代理人  | 100106183<br>弁理士 吉澤 弘司                     |

| (74)代理人  | 100136799<br>弁理士 本田 亜希                     |

| (72)発明者  | 山崎 和男<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 審査官      | 廣田 健介                                      |

最終頁に続く

(54)【発明の名称】 光電変換装置及び撮像システム

**(57)【特許請求の範囲】****【請求項1】**

光電変換素子を各々が有する複数の画素が複数の列をなすように配された画素アレイ部と、

前記複数の列に対応して設けられた複数のA D変換回路と、

前記複数のA D変換回路を制御する制御回路と、を有し、

前記複数の画素は、前記複数の列のうちの第1の列に配され、前記光電変換素子が遮光された第1の画素と、前記複数の列のうちの前記第1の列とは異なる第2の列に配され、前記光電変換素子に光が入射する第2の画素と、を有し、

前記複数のA D変換回路は、前記第1の画素の信号を受ける第1の比較器を有する第1のA D変換回路と、前記第2の画素の信号を受ける第2の比較器を有する第2のA D変換回路と、を有し、

前記第1の画素の信号が前記第1の比較器に入力されるタイミングと、前記第2の画素の信号が前記第2の比較器に入力されるタイミングと、は同じであり、

前記制御回路は、同じレベルである前記第1の画素の信号および前記第2の画素の信号に対し、前記第1の比較器から出力される信号値が、前記第2の比較器から出力される信号値よりも先に変化するように、前記第1の比較器及び前記第2の比較器を制御するよう構成されている

ことを特徴とする光電変換装置。

**【請求項2】**

10

20

前記制御回路は、前記第1の画素の信号及び前記第2の画素の信号をA/D変換する際に、前記第1の比較器におけるスルーレートが前記第2の比較器におけるスルーレートよりも高くなるように、前記第1の比較器及び前記第2の比較器を制御することを特徴とする請求項1記載の光電変換装置。

#### 【請求項3】

前記第1の比較器及び前記第2の比較器は差動増幅回路を有し、

前記制御回路は、前記第1の比較器の前記差動増幅回路のテイル電流源の電流値が前記第2の比較器の前記差動増幅回路のテイル電流源の電流値よりも大きくなるように、前記第1の比較器及び前記第2の比較器を制御することを特徴とする請求項2記載の光電変換装置。

10

#### 【請求項4】

前記第1の比較器及び前記第2の比較器は、スルーレートを切り替え可能に構成された遅延回路を有し、

前記制御回路は、前記第1の比較器におけるスルーレートが前記第2の比較器におけるスルーレートよりも高くなるように、前記遅延回路を制御することを特徴とする請求項2記載の光電変換装置。

#### 【請求項5】

前記第1の比較器及び前記第2の比較器は、対応する列の画素から出力される画素信号と、時間の経過に応じてレベルが変化する参照信号と、を比較し、前記画素信号と前記参照信号との差が閾値電圧よりも小さい場合と大きい場合とで異なるレベルを示す比較信号を出力するように構成されており、

20

前記制御回路は、前記第1の画素の信号及び前記第2の画素の信号をA/D変換する際に、前記第2の比較器の閾値電圧が前記第1の比較器の閾値電圧よりも大きくなるように、前記第1の比較器及び前記第2の比較器をリセットすることを特徴とする請求項1記載の光電変換装置。

#### 【請求項6】

前記第1の比較器をリセットする際の前記参照信号のレベルと、前記第2の比較器をリセットする際の前記参照信号のレベルと、が異なっていることを特徴とする請求項5記載の光電変換装置。

#### 【請求項7】

前記第1の比較器及び前記第2の比較器は、対応する列の画素から出力される画素信号と、時間の経過に応じてレベルが変化する参照信号と、を比較し、前記画素信号と前記参照信号との差が閾値電圧よりも小さい場合と大きい場合とで異なるレベルを示す比較信号を出力するように構成されており、

30

前記制御回路は、前記第1の画素の信号及び前記第2の画素の信号をA/D変換する際に、前記画素信号を受ける第1の入力端子と前記参照信号を受ける第2の入力端子との間の電位差が、前記第1の比較器よりも前記第2の比較器の方が小さくなるように、前記第1の比較器の前記第1の入力端子のレベル及び前記第2の比較器の前記第1の入力端子のレベルを制御することを特徴とする請求項1記載の光電変換装置。

40

#### 【請求項8】

前記制御回路は、同じレベルである前記第1の画素の信号および前記第2の画素の信号に対して、A/D変換が開始してから前記第1の比較器から出力される信号値が変化するまでの時間が、A/D変換が開始してから前記第2の比較器から出力される信号値が変化するまでの時間よりも短くなるように、前記第1の比較器および前記第2の比較器を制御することを特徴とする請求項1乃至7のいずれか1項に記載の光電変換装置。

#### 【請求項9】

前記第1のA/D変換回路は、A/D変換の結果を保持する第1のメモリを有し、前記第2のA/D変換回路は、A/D変換の結果を保持する第2のメモリを有し、

前記制御回路は、前記第1のメモリが前記第2のメモリよりも先にA/D変換の結果を保

50

持するように、前記第1のメモリおよび前記第2のメモリを制御することを特徴とする請求項1乃至8のいずれか1項に記載の光電変換装置。

**【請求項10】**

前記制御回路は、前記第1のメモリに保持された前記A/D変換の結果および前記第2のメモリに保持された前記A/D変換の結果が順番に出力されるように、前記第1のメモリおよび前記第2のメモリを制御することを特徴とする請求項9記載の光電変換装置。

**【請求項11】**

前記第1の画素および前記第2の画素は、ノイズ信号および光電変換信号をそれぞれ出力し、

前記制御回路は、前記第1の画素から出力された前記ノイズ信号に対応して前記第1の比較器から出力される信号、前記第2の画素から出力された前記ノイズ信号に対応して前記第2の比較器から出力される信号、前記第1の画素から出力された前記光電変換信号に対応して前記第1の比較器から出力される信号、前記第2の画素から出力された前記光電変換信号に対応して前記第2の比較器から出力される信号、の順番でそれぞれの信号値が変化するように、前記第1の比較器および前記第2の比較器を制御することを特徴とする請求項1乃至10のいずれか1項に記載の光電変換装置。

**【請求項12】**

前記第1の比較器及び前記第2の比較器は、対応する列の画素から出力される画素信号と、時間の経過に応じてレベルが変化する参照信号と、を比較し、前記画素信号と前記参照信号との差が閾値電圧よりも小さい場合と大きい場合とで異なるレベルを示す比較信号を出力するように構成されており、

前記制御回路は、前記第1の比較器が前記第2の比較器よりも先に前記比較が完了するよう、前記第1の比較器および前記第2の比較器を制御することを特徴とする請求項1記載の光電変換装置。

**【請求項13】**

光電変換素子を各々が有する複数の画素が複数の列をなすように配された画素アレイ部と、

前記複数の列に対応して設けられた複数のA/D変換回路と、を有し、

前記複数の画素は、前記複数の列のうちの第1の列に配され、前記光電変換素子が遮光された第1の画素と、前記複数の列のうちの前記第1の列とは異なる第2の列に配され、前記光電変換素子に光が入射する第2の画素と、を有し、

前記複数のA/D変換回路は、前記第1の画素の信号を受ける第1の比較器を有する第1のA/D変換回路と、前記第2の画素の信号を受ける第2の比較器を有する第2のA/D変換回路と、を有し、

前記第1の比較器におけるスルーレートは、前記第2の比較器におけるスルーレートよりも高いことを特徴とする光電変換装置。

**【請求項14】**

前記第1の比較器及び前記第2の比較器は差動增幅回路を有し、前記第1の比較器の前記差動增幅回路のテイル電流源の電流値は、前記第2の比較器の前記差動增幅回路のテイル電流源の電流値よりも大きいことを特徴とする請求項13記載の光電変換装置。

**【請求項15】**

前記第1の比較器及び前記第2の比較器は、スルーレートを切り替え可能に構成された遅延回路を有する

ことを特徴とする請求項13記載の光電変換装置。

**【請求項16】**

前記第2の比較器は、前記第1の比較器よりもスルーレートを低くするための遅延回路を有する

10

20

30

40

50

ことを特徴とする請求項 13 記載の光電変換装置。

**【請求項 17】**

前記第1の比較器及び前記第2の比較器は、差動増幅回路と、前記差動増幅回路の後段に設けられたソース接地増幅回路と、を有し、前記遅延回路は、前記差動増幅回路の出力端子と前記ソース接地増幅回路の入力端子との間に設けられている

ことを特徴とする請求項 15 又は 16 記載の光電変換装置。

**【請求項 18】**

前記第1の画素及び前記第2の画素は、共通の制御信号により同時に制御される

ことを特徴とする請求項 1 乃至 17 のいずれか 1 項に記載の光電変換装置。

**【請求項 19】**

前記第1の列と前記第2の列とは隣り合っている

ことを特徴とする請求項 1 乃至 18 のいずれか 1 項に記載の光電変換装置。

**【請求項 20】**

請求項 1 乃至 19 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理部と

を有することを特徴とする撮像システム。

**【請求項 21】**

移動体であって、

請求項 1 乃至 19 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく視差画像から、対象物までの距離情報を取得する

距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と

を有することを特徴とする移動体。

**【請求項 22】**

請求項 1 乃至 19 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置に対応する光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報に基づいて制御される機械装置、

前記光電変換装置で得られた情報を表示する表示装置、及び、

前記光電変換装置で得られた情報を記憶する記憶装置、の少なくともいずれかと

を備えることを特徴とする機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、光電変換装置及び撮像システムに関する。

**【背景技術】**

**【0002】**

C M O S イメージセンサなどの光電変換装置の中には、画素信号をアナログデジタル (A D) 変換して出力するものがある。これらの光電変換装置では、画素列に対応して設けられた複数の比較器の各々が、対応する列の画素から出力された画素信号と参照信号とを比較し、比較の結果に応じた比較信号を出力する。比較信号が出力されたタイミングでカウンタのデジタル値をメモリに取り込むことで、画素信号の A D 変換が可能となる。特許文献 1 には、各列に設けられた比較器の出力レベルが一齊に反転することに起因して生じるノイズを抑制する技術が記載されている。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】** 特開 2014 - 096670 号公報

**【発明の概要】**

10

20

30

40

50

**【発明が解決しようとする課題】**

**【0004】**

比較器の出力レベルの一斉反転に起因して生じるノイズの影響は水平OB画素において特に顕著であり、画質への影響も大きい。しかしながら、特許文献1では、水平OB画素と有効画素とにおける区別はなされていなかった。そのため、特許文献1の技術では、必ずしも画質の改善が十分に図られているとは言えなかった。

**【0005】**

本発明の目的は、比較器の出力レベルの一斉反転に起因して生じるノイズの影響を効果的に抑制しうる光電変換装置を提供することにある。

**【課題を解決するための手段】**

**【0006】**

本明細書の一開示によれば、光電変換素子を各々が有する複数の画素が複数の列をなすように配された画素アレイ部と、前記複数の列に対応して設けられた複数のAD変換回路と、前記複数のAD変換回路を制御する制御回路と、を有し、前記複数の画素は、前記複数の列のうちの第1の列に配され、前記光電変換素子が遮光された第1の画素と、前記複数の列のうちの前記第1の列とは異なる第2の列に配され、前記光電変換素子に光が入射する第2の画素と、を有し、前記複数のAD変換回路は、前記第1の画素の信号を受ける第1の比較器を有する第1のAD変換回路と、前記第2の画素の信号を受ける第2の比較器を有する第2のAD変換回路と、を有し、前記第1の画素の信号が前記第1の比較器に入力されるタイミングと、前記第2の画素の信号が前記第2の比較器に入力されるタイミングと、は同じであり、前記制御回路は、同じレベルである前記第1の画素の信号および前記第2の画素の信号に対し、前記第1の比較器から出力される信号値が、前記第2の比較器から出力される信号値よりも先に変化するように、前記第1の比較器及び前記第2の比較器を制御するように構成されている光電変換装置が提供される。

**【0007】**

また、本明細書の他の一開示によれば、光電変換素子を各々が有する複数の画素が複数の列をなすように配された画素アレイ部と、前記複数の列に対応して設けられた複数のAD変換回路と、を有し、前記複数の画素は、前記複数の列のうちの第1の列に配され、前記光電変換素子が遮光された第1の画素と、前記複数の列のうちの前記第1の列とは異なる第2の列に配され、前記光電変換素子に光が入射する第2の画素と、を有し、前記複数のAD変換回路は、前記第1の画素の信号を受ける第1の比較器を有する第1のAD変換回路と、前記第2の画素の信号を受ける第2の比較器を有する第2のAD変換回路と、を有し、前記第1の比較器におけるスルーレートは、前記第2の比較器におけるスルーレートよりも高い光電変換装置が提供される。

**【発明の効果】**

**【0008】**

本発明によれば、比較器の出力レベルの一斉反転に起因して生じるノイズを効果的に抑制することができる。

**【図面の簡単な説明】**

**【0009】**

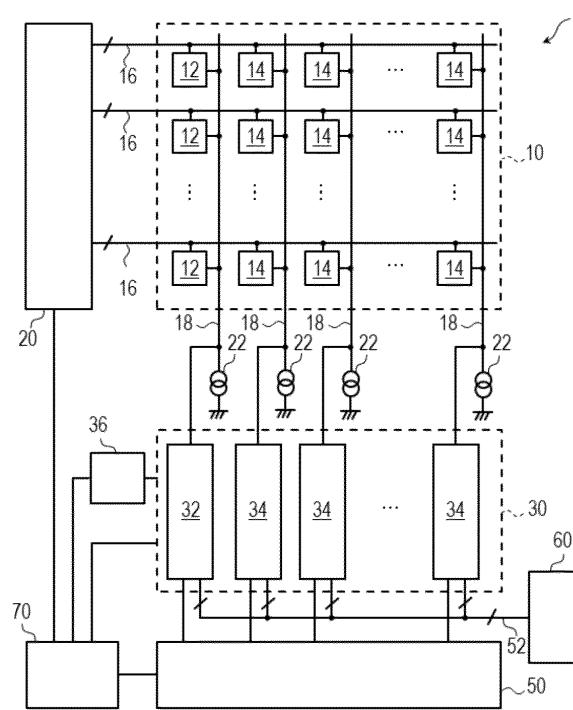

**【図1】**本発明の第1実施形態による光電変換装置の概略構成を示すブロック図である。

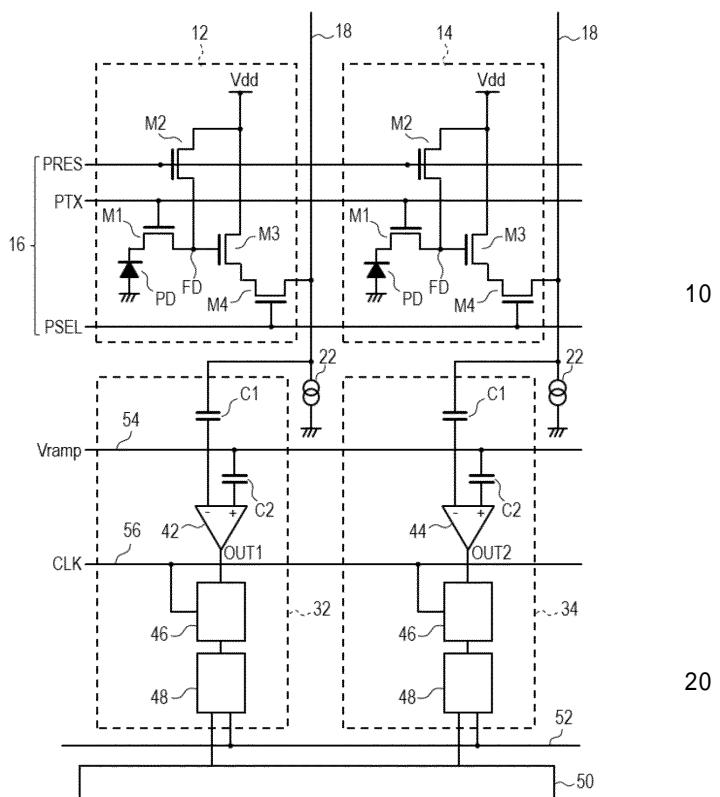

**【図2】**本発明の第1実施形態による光電変換装置における画素及び列回路の構成例を示す回路図である。

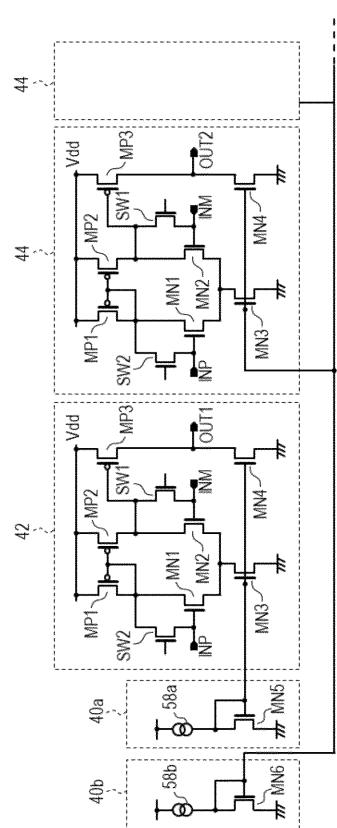

**【図3】**本発明の第1実施形態による光電変換装置における比較器の構成例を示す回路図である。

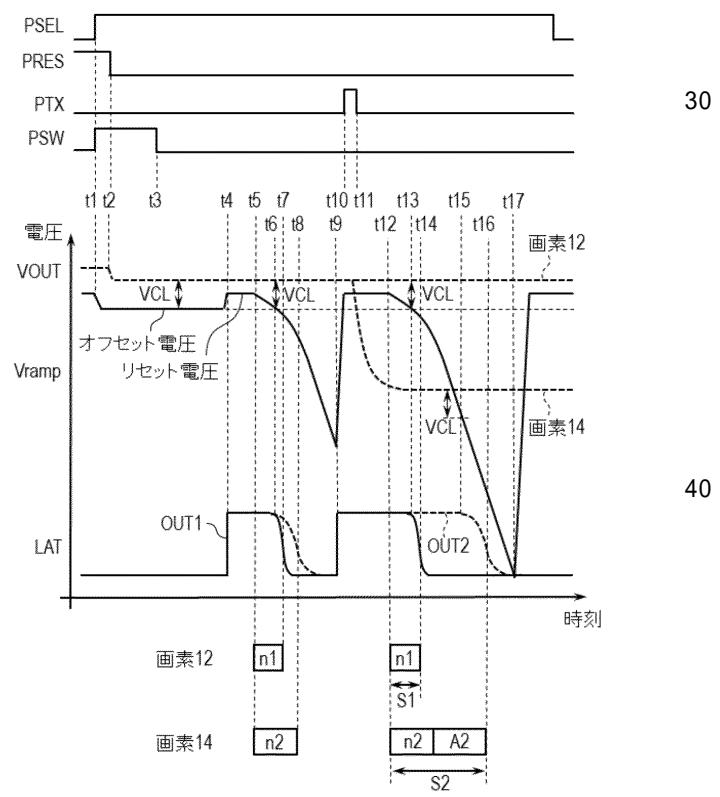

**【図4】**本発明の第1実施形態による光電変換装置の動作を示すタイミング図である。

**【図5】**本発明の第2実施形態による光電変換装置における比較器の構成例を示す回路図である。

**【図6】**本発明の第3実施形態による光電変換装置の動作を示すタイミング図である。

**【図7】**本発明の第4実施形態による光電変換装置における画素及び列回路の構成例を示す回路図である。

10

20

30

40

50

す回路図である。

【図 8】本発明の第 4 実施形態による光電変換装置の動作を示すタイミング図である。

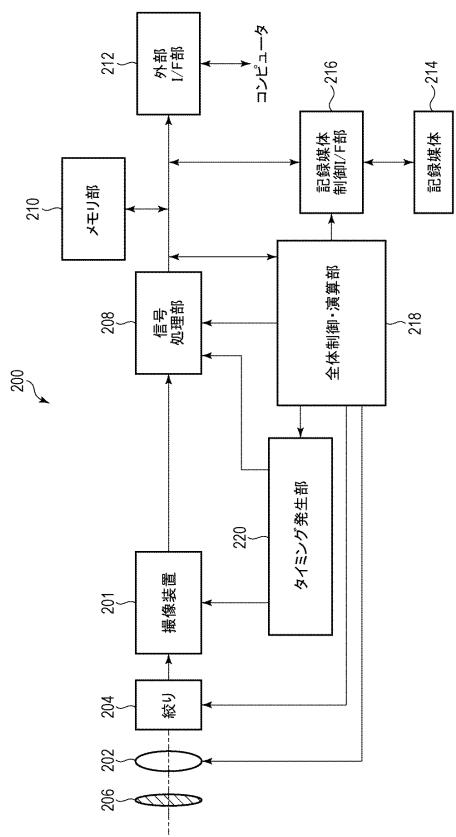

【図 9】本発明の第 5 実施形態による撮像システムの概略構成を示すブロック図である。

【図 10】本発明の第 6 実施形態による撮像システム及び移動体の構成例を示す図である。

【図 11】本発明の第 7 実施形態による機器の概略構成を示すブロック図である。

【発明を実施するための形態】

【0010】

[第 1 実施形態]

本発明の第 1 実施形態による光電変換装置及びその駆動方法について、図 1 乃至図 4 を用いて説明する。図 1 は、本実施形態による光電変換装置の概略構成を示すブロック図である。図 2 は、本実施形態による光電変換装置における画素及び列回路の構成例を示す回路図である。図 3 は、本実施形態による光電変換装置における比較器の構成例を示す回路図である。図 4 は、本実施形態による光電変換装置の動作を示すタイミング図である。

10

【0011】

はじめに、本発明の第 1 実施形態による光電変換装置の概略構成について、図 1 を用いて説明する。

【0012】

本実施形態による光電変換装置 100 は、図 1 に示すように、画素アレイ部 10 と、垂直走査回路 20 と、読み出し回路 30 と、参照信号生成回路 36 と、水平走査回路 50 と、デジタル信号処理回路 60 と、タイミングジェネレータ 70 と、により構成され得る。

20

【0013】

画素アレイ部 10 には、複数の行及び複数の列に渡って行列状に配された複数の画素 12, 14 が設けられている。画素 12, 14 の各々は、フォトダイオード等の光電変換素子からなる光電変換部を含む。画素 14 は、光電変換素子に光が入射し、光電変換素子への入射光の光量に応じた画素信号を出力する有効画素である。画素 12 は、光電変換素子が遮光されたオプティカルブラック画素 (OB 画素) であり、その出力信号は黒レベルの基準として用いられる。

【0014】

画素 12 は、画素アレイ部 10 を構成する複数の行及び複数の列のうちの一部の行及び / 又は一部の列、一般的には画素アレイ部 10 の周囲の 2 辺に接する行及び列に配される。画素 12 のみが配された列を水平 OB 画素領域、水平 OB 画素領域に配された画素を水平 OB 画素と呼ぶことがある。また、画素 12 のみが配された行を垂直 OB 画素領域、垂直 OB 画素領域に配された画素を垂直 OB 画素と呼ぶことがある。図 1 には、図面の簡略化のため、画素アレイ部 10 の複数の列のうち最も左側の列 (第 1 列) に画素 12 を配し、その他の列 (第 2 列から第 N 列) に画素 14 を配した例を示しているが、典型的には水平 OB 画素領域は複数列で構成される。

30

【0015】

画素アレイ部 10 の複数の行の各々には、少なくとも 1 つの画素 12 と、複数の画素 14 と、が配される。画素 12 から出力される基準信号は、同じ行の画素 14 から出力される画素信号の補正処理に用いられる。

40

【0016】

画素アレイ部 10 の各行には、第 1 の方向 (図 1 において横方向) に延在して、制御線 16 が配されている。制御線 16 の各々は、第 1 の方向に並ぶ画素 12, 14 にそれぞれ接続され、これら画素 12, 14 に共通の信号線をなしている。制御線 16 の延在する第 1 の方向は、行方向或いは水平方向と呼ぶことがある。制御線 16 は、垂直走査回路 20 に接続されている。

【0017】

画素アレイ部 10 の各列には、第 1 の方向と交差する第 2 の方向 (図 1 において縦方向) に延在して、出力線 18 が配されている。出力線 18 の各々は、第 2 の方向に並ぶ画素 12 又は画素 14 にそれぞれ接続され、これら画素 12 又は画素 14 に共通の信号線をな

50

している。出力線 18 の延在する第 2 の方向は、列方向或いは垂直方向と呼ぶことがある。出力線 18 の各々は、電流源 22 と読み出し回路 30 とに接続されている。

#### 【 0 0 1 8 】

垂直走査回路 20 は、タイミングジェネレータ 70 から出力される制御信号を受け、画素 12, 14 を駆動するための制御信号を生成し、制御線 16 を介して画素 12, 14 に供給する機能を備える制御回路である。垂直走査回路 20 には、シフトレジスタやアドレスデコーダといった論理回路が用いられ得る。垂直走査回路 20 は、画素アレイ部 10 の画素 12, 14 を行単位で駆動する。行単位で画素 12, 14 から読み出された信号は、画素アレイ部 10 の各列に設けられた出力線 18 を介して読み出し回路 30 に入力される。

#### 【 0 0 1 9 】

読み出し回路 30 は、画素アレイ部 10 の各列に対応して設けられた複数の列回路 32, 34 を有する。列回路 32 は、画素 12 が配された列（第 1 列）の出力線 18 に接続されている。列回路 34 は、画素 14 が配された列（第 2 列から第 N 列）の出力線 18 に接続されている。列回路 32, 34 の各々は、対応する列の出力線 18 から出力されたアナログ画素信号を A/D 変換する A/D 変換回路としての機能と、A/D 変換後のデジタル画素信号を保持するデジタル信号保持部としての機能を備える。

10

#### 【 0 0 2 0 】

参照信号生成回路 36 は、タイミングジェネレータ 70 から出力される制御信号を受け、列回路 32, 34 に供給する参照信号を生成する回路である。参照信号は、所定の振幅を有する信号であり、例えば時間の経過にともなって信号レベル（信号の大きさ）が変化する信号であり得る。参照信号は、典型的にはランプ信号である。ランプ信号とは、時間の経過にともなって信号レベルが単調に変化する信号であり、例えば出力電圧が時間の経過とともに単調減少し或いは単調増加する信号である。なお、参照信号は、A/D 変換に適用可能な振幅を有するものであれば、特に限定されるものではない。

20

#### 【 0 0 2 1 】

水平走査回路 50 は、読み出し回路 30 で処理された画素信号を列毎に順次、デジタル信号処理回路 60 に転送するための制御信号を読み出し回路 30 に供給する制御回路である。水平走査回路 50 は、シフトレジスタやアドレスデコーダを用いて構成され得る。

#### 【 0 0 2 2 】

デジタル信号処理回路 60 は、読み出し回路 30 から転送されるデジタル画素信号に対して所定の処理を行う処理回路である。デジタル信号処理回路 60 が行う信号処理には、例えば、デジタル相關二重サンプリングによる補正処理や增幅処理などが挙げられる。

30

#### 【 0 0 2 3 】

タイミングジェネレータ 70 は、垂直走査回路 20、読み出し回路 30、参照信号生成回路 36、水平走査回路 50 に、これらの動作やタイミングを制御する制御信号を供給するための制御回路である。垂直走査回路 20、読み出し回路 30、参照信号生成回路 36、水平走査回路 50 に供給する制御信号の少なくとも一部は、光電変換装置 100 の外部から供給されてもよい。

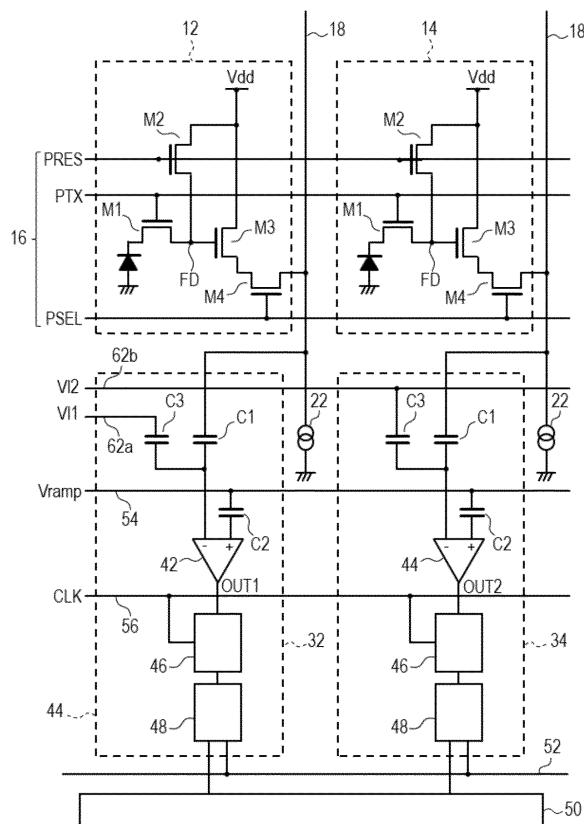

#### 【 0 0 2 4 】

次に、本実施形態による光電変換装置における画素 12, 14 及び列回路 32, 34 の構成例について、図 2 を用いて説明する。

40

#### 【 0 0 2 5 】

図 2 には、画素アレイ部 10 を構成する複数の画素 12, 14 のうち、同じ行に配された画素 12, 14 を 1 つずつ抜き出して示している。また、図 2 には、当該画素 12 に接続された列回路 32 と、当該画素 14 に接続された列回路 34 と、を示している。

#### 【 0 0 2 6 】

画素 12, 14 の各々は、例えば図 2 に示すように、光電変換素子 P/D と、転送トランジスタ M1 と、リセットトランジスタ M2 と、増幅トランジスタ M3 と、選択トランジスタ M4 と、により構成され得る。

#### 【 0 0 2 7 】

50

光電変換素子 P D は、例えばフォトダイオードであり、アノードが接地ノードに接続され、カソードが転送トランジスタ M 1 のソースに接続されている。転送トランジスタ M 1 のドレインは、リセットトランジスタ M 2 のソース及び増幅トランジスタ M 3 のゲートに接続されている。転送トランジスタ M 1 のドレイン、リセットトランジスタ M 2 のソース及び増幅トランジスタ M 3 のゲートが接続されるノード F D は、いわゆる浮遊拡散（フローティングディフェュージョン）部である。浮遊拡散部は、容量成分（浮遊拡散容量）を含み、電荷保持部としての機能を備える。浮遊拡散容量には、P N 接合容量や配線容量などが含まれる。

#### 【 0 0 2 8 】

リセットトランジスタ M 2 のドレイン及び増幅トランジスタ M 3 のドレインは、電圧 V<sub>d d</sub> が供給される電源電圧ノードに接続されている。増幅トランジスタ M 3 のソースは、選択トランジスタ M 4 のドレインに接続されている。選択トランジスタ M 4 のソースは、出力線 1 8 に接続されている。10

#### 【 0 0 2 9 】

画素 1 2 と画素 1 4 とは、図 2 に示すように回路構成は同じである。画素 1 2 は、図示しない遮光膜によって光電変換素子 P D が遮光されている点で、画素 1 4 とは異なっている。

#### 【 0 0 3 0 】

画素 1 2 に接続された出力線 1 8 には、電流源 2 2 と列回路 3 2 とが接続されている。画素 1 4 に接続された出力線 1 8 には、電流源 2 2 と列回路 3 4 とが接続されている。電流源 2 2 は、電流値が切り替え可能な電流源であってもよいし、電流値が一定の定電流源であってもよい。20

#### 【 0 0 3 1 】

図 2 の画素構成の場合、各行の制御線 1 6 は、転送トランジスタ M 1 のゲートに接続された信号線と、リセットトランジスタ M 2 のゲートに接続された信号線と、選択トランジスタ M 4 のゲートに接続された信号線と、を含む。転送トランジスタ M 1 のゲートには、垂直走査回路 2 0 から制御信号 P T X が供給される。リセットトランジスタ M 2 のゲートには、垂直走査回路 2 0 から制御信号 P R E S が供給される。選択トランジスタ M 4 のゲートには、垂直走査回路 2 0 から制御信号 P S E L が供給される。同じ行の画素 1 2 と画素 1 4 は、共通の信号線に接続されており、共通の制御信号により同時に制御される。30

#### 【 0 0 3 2 】

なお、本実施形態では、光入射によって光電変換素子 P D で生成される電子正孔対のうち、電子を信号電荷として用いる場合を想定して説明を行う。信号電荷として電子を用いる場合、画素 1 2 , 1 4 を構成する各トランジスタは、N 型 M O S トランジスタによって構成され得る。各トランジスタが N 型 M O S トランジスタで構成される場合、垂直走査回路 2 0 から H i g h レベルの制御信号が供給されると対応するトランジスタがオンになる。また、垂直走査回路 2 0 から L o w レベルの制御信号が供給されると対応するトランジスタがオフになる。ただし、信号電荷は電子に限られるものではなく、正孔を信号電荷として用いてもよい。信号電荷として正孔を用いる場合、各トランジスタの導電型は、本実施形態で説明するものとは逆導電型となる。また、M O S トランジスタのソース及びドレインの呼称はトランジスタの導電型や着目する機能によって異なることがある。本実施形態において使用するソース及びドレインの名称の一部又は全部は、逆の名称で呼ばれることがある。

#### 【 0 0 3 3 】

列回路 3 2 は、容量素子 C 1 , C 2 と、比較器 4 2 と、カウンタ回路 4 6 と、メモリ部 4 8 と、を有する。容量素子 C 1 の一方の電極は、出力線 1 8 に接続されている。容量素子 C 1 の他方の電極は、比較器 4 2 の反転入力端子に接続されている。容量素子 C 2 の一方の電極は、信号線 5 4 に接続されている。容量素子 C 2 の他方の電極は、比較器 4 2 の非反転入力端子に接続されている。カウンタ回路 4 6 は、2 つの入力端子と 1 つの出力端子を有する。比較器 4 2 の出力端子は、カウンタ回路 4 6 の第 1 の入力端子に接続されて40

10

20

30

40

50

いる。カウンタ回路46の第2の入力端子は、信号線56に接続されている。メモリ部48は、2つの入力端子と1つの出力端子を有する。カウンタ回路46の出力端子は、メモリ部48の第1の入力端子に接続されている。メモリ部48の第2の入力端子は、水平走査回路50に接続されている。メモリ部48の出力端子は、出力線52に接続されている。

#### 【0034】

信号線54は、参照信号生成回路36に接続されている。信号線54には、参照信号生成回路36から参照信号V<sub>ram p</sub>が供給される。信号線56は、タイミングジェネレータ70に接続されている。信号線56には、タイミングジェネレータ70からクロック信号C<sub>LK</sub>が供給される。

#### 【0035】

列回路34は、図2に示すように回路構成は列回路32と同じである。後の説明の便宜上、列回路32の比較器を符号42で表し、列回路34の比較器を符号44で表すものとする。

#### 【0036】

次に、画素12, 14及び列回路32, 34の動作の概略について、図2を用いて説明する。なお、ここでは画素14及び列回路34の動作を説明するが、画素12及び列回路32の動作についても同様である。

#### 【0037】

光電変換素子PDは、入射光をその光量に応じた量の電荷に変換（光電変換）する。転送トランジスタM1は、オンになることにより光電変換素子PDが保持する電荷をノードFDに転送する。光電変換素子PDから転送された電荷は、ノードFDの容量（浮遊拡散容量）に保持される。その結果、ノードFDは、浮遊拡散容量による電荷電圧変換によって、光電変換素子PDから転送された電荷の量に応じた電位となる。

#### 【0038】

選択トランジスタM4は、オンになることにより増幅トランジスタM3を出力線18に接続する。増幅トランジスタM3は、ドレインに電圧V<sub>dd</sub>が供給され、ソースに選択トランジスタM4を介して電流源22からバイアス電流が供給される構成となっており、ゲートを入力ノードとする増幅部（ソースフォロワ回路）を構成する。これにより増幅トランジスタM3は、ノードFDの電圧に基づく信号を、選択トランジスタM4を介して出力線18に出力する。この意味で、増幅トランジスタM3及び選択トランジスタM4は、ノードFDに保持された電荷の量に応じた画素信号を出力する出力部である。

#### 【0039】

リセットトランジスタM2は、電荷保持部としてのノードFDをリセットするための電圧（電圧V<sub>dd</sub>）のFDノードへの供給を制御する機能を備える。リセットトランジスタM2は、オンになることによりノードFDを電圧V<sub>dd</sub>に応じた電圧にリセットする。

#### 【0040】

画素14から出力線18を介して列回路34に入力される画素信号は、容量素子C1を介して比較器44の反転入力端子に入力される。また、参照信号生成回路36から出力される参照信号V<sub>ram p</sub>は、信号線54及び容量素子C2を介して比較器44の非反転入力端子に入力される。比較器44は、画素信号の信号レベルと参照信号生成回路36から供給される参照信号V<sub>ram p</sub>の信号レベルとを比較する比較動作を行い、画素信号の信号レベルと参照信号V<sub>ram p</sub>の信号レベルとが所定の関係を満たしたタイミングでラッチ信号を出力する。比較器44の出力信号は、カウンタ回路46に入力される。

#### 【0041】

カウンタ回路46は、比較器44における画素信号の信号レベルと参照信号V<sub>ram p</sub>の信号レベルとの比較動作の開始と同期して、タイミングジェネレータ70から信号線56を介して供給されるクロック信号C<sub>LK</sub>に重畠するパルスの計数を開始する。カウンタ回路46は、比較器44からラッチ信号を受信すると、ラッチ信号を受信したタイミングにおいて保持しているカウント値をメモリ部48に出力する。メモリ部48は、カウンタ回路46から受信したカウント値を、画素信号のデジタルデータとして保持する。

**【 0 0 4 2 】**

水平走査回路 5 0 は、タイミングジェネレータ 7 0 による制御のもと、各列の列回路のメモリ部 4 8 に順次、制御信号を出力する。水平走査回路 5 0 から制御信号を受信したメモリ部 4 8 は、画素信号のデジタルデータを出力線 5 2 に出力する。

**【 0 0 4 3 】**

次に、本実施形態による光電変換装置における比較器 4 2 , 4 4 の構成例について、図 3 を用いて説明する。

**【 0 0 4 4 】**

比較器 4 2 は、P 型トランジスタ M P 1 , M P 2 , M P 3 と、N 型トランジスタ M N 1 , M N 2 , M N 3 , M N 4 と、により構成され得る。

10

**【 0 0 4 5 】**

P 型トランジスタ M P 1 , M P 2 , M P 3 のソースは、電源電圧ノード（電圧 V d d ）に接続されている。P 型トランジスタ M P 1 , M P 2 のゲート及び P 型トランジスタ M P 1 のドレインは、N 型トランジスタ M N 1 のドレインに接続されている。P 型トランジスタ M P 2 のドレインは、P 型トランジスタ M P 3 のゲート及び N 型トランジスタ M N 2 のドレインに接続されている。N 型トランジスタ M N 1 , M N 2 のソースは、N 型トランジスタ M N 3 のドレインに接続されている。N 型トランジスタ M N 3 のソースは、基準電圧ノードに接続されている。P 型トランジスタ M P 3 のドレインは、N 型トランジスタ M N 4 のドレインに接続されている。N 型トランジスタ M N 4 のソースは、基準電圧ノードに接続されている。

20

**【 0 0 4 6 】**

N 型トランジスタ M N 1 のゲートは、比較器 4 2 の非反転入力端子（ I N P ）である。N 型トランジスタ M N 2 のゲートは、比較器 4 2 の反転入力端子（ I N M ）である。また、P 型トランジスタ M P 3 のドレインと N 型トランジスタ M N 4 のドレインとの間の接続ノードは、比較器 4 2 の出力端子（ O U T 1 ）である。

**【 0 0 4 7 】**

比較器 4 2 の反転入力端子（ I N M ）と、P 型トランジスタ M P 2 のドレイン、P 型トランジスタ M P 3 のゲート及び N 型トランジスタ M N 2 のドレインの接続ノードと、の間には、スイッチ S W 1 が接続されている。比較器 4 2 の非反転入力端子（ I N P ）と、P 型トランジスタ M P 1 , M P 2 のゲート、P 型トランジスタ M P 1 のドレイン及び N 型トランジスタ M N 1 のドレインの接続ノードと、の間には、スイッチ S W 2 が接続されている。スイッチ S W 1 , S W 2 は、タイミングジェネレータ 7 0 から供給される制御信号により制御されるスイッチであり、例えば N 型トランジスタにより構成され得る。

30

**【 0 0 4 8 】**

比較器 4 4 は、図 3 に示すように回路構成は比較器 4 2 と同じである。なお、後の説明の便宜上、比較器 4 2 の出力端子を符号 O U T 1 で表し、比較器 4 4 の出力端子を符号 O U T 2 で表すものとする。

**【 0 0 4 9 】**

比較器 4 2 の N 型トランジスタ M N 3 , M N 4 のゲートは、電流源回路 4 0 a に接続されている。電流源回路 4 0 a は、電流源 5 8 a と、N 型トランジスタ M N 5 と、を有する。電流源 5 8 a の一方の端子は、電源電圧ノードに接続されている。電流源 5 8 a の他方の端子は、N 型トランジスタ M N 5 のドレイン及びゲートに接続されている。N 型トランジスタ M N 5 のソースは、基準電圧ノードに接続されている。電流源 5 8 a と、N 型トランジスタ M N 5 のドレイン及びゲートとの接続ノードが、比較器 4 2 の N 型トランジスタ M N 3 , M N 4 のゲートに接続される電流源回路 4 0 a の出力端子である。

40

**【 0 0 5 0 】**

比較器 4 4 の N 型トランジスタ M N 3 , M N 4 のゲートは、電流源回路 4 0 b に接続されている。電流源回路 4 0 b は、電流源 5 8 b と、N 型トランジスタ M N 6 と、を有する。電流源 5 8 b の一方の端子は、電源電圧ノードに接続されている。電流源 5 8 b の他方の端子は、N 型トランジスタ M N 6 のドレイン及びゲートに接続されている。N 型トラン

50

ジスタMN6のソースは、基準電圧ノードに接続されている。電流源58bと、N型トランジスタMN6のドレイン及びゲートとの接続ノードが、比較器44のN型トランジスタMN3,MN4のゲートに接続される電流源回路40bの出力端子である。

#### 【0051】

比較器42,44の各々において、N型トランジスタMN1,MN2,MN3及びP型トランジスタMP1,MP2,MP3は、差動增幅回路を構成している。N型トランジスタMN1のゲートが差動增幅回路の+側入力端子であり、N型トランジスタMN2のゲートが差動増幅回路の-側入力端子である。P型トランジスタMP1のゲートと、P型トランジスタMP2のゲートと、P型トランジスタMP1のドレインと、N型トランジスタMN1のドレインとの接続ノードが、差動增幅回路の-側出力端子である。また、P型トランジスタMP2のドレインとN型トランジスタMN2のドレインとの接続ノードが、差動増幅回路の+側出力端子である。N型トランジスタMN3は、差動増幅回路のテイル電流源を構成している。

10

#### 【0052】

また、比較器42,44の各々において、P型トランジスタMP3及びN型トランジスタMN4は、ソース接地増幅回路を構成している。P型トランジスタMP3のゲートがソース接地増幅回路の入力端子であり、P型トランジスタMP3のドレインとN型トランジスタMN4のドレインとの間の接続ノードがソース接地増幅回路の出力端子である。N型トランジスタMN4は、ソース接地増幅回路のテイル電流源を構成している。ソース接地増幅回路の入力端子は、差動増幅回路の+側出力端子に接続されている。ソース接地増幅回路の出力端子が、比較器42,44の出力端子である。

20

#### 【0053】

このように、比較器42,44は、差動増幅回路と、差動増幅回路の後段に接続されたソース接地増幅回路と、の2段増幅回路により構成されている。

#### 【0054】

比較器42のN型トランジスタMN3,MN4の各々は、電流源回路40aのN型トランジスタMN5とカレントミラー回路を構成しており、定電流源（テイル電流源）として動作する。同様に、比較器44のN型トランジスタMN3,MN4の各々は、電流源回路40bのN型トランジスタMN6とカレントミラー回路を構成しており、定電流源（テイル電流源）として動作する。

30

#### 【0055】

ここで、電流源回路40a,40bは、N型トランジスタMN5に流れる電流をI1、N型トランジスタMN6に流れる電流をI2として、電流I1が電流I2よりも大きくなるように駆動される。これにより、比較器42のN型トランジスタMN3に流れる電流は比較器44のN型トランジスタMN3に流れる電流よりも大きくなり、比較器42のスルーレートは比較器44のスルーレートよりも高くなる。その結果、比較器42の反転遅延時間は、比較器44の反転遅延時間よりも短くなる。

#### 【0056】

なお、電流源回路40aのN型トランジスタMN5に流れる電流I1及び電流源回路40bのN型トランジスタMN6に流れる電流I2は、タイミングジェネレータ70により制御可能に構成されていてもよいし、固定値であってもよい。

40

#### 【0057】

比較器42,44の差動増幅回路の入力ノードと出力ノードとの間に接続されたスイッチSW1,SW2は、比較器42,44のオートゼロを決めるためのスイッチ（リセットスイッチ）である。スイッチSW1,SW2は、共通の制御信号PSWによって制御される。

#### 【0058】

次に、本実施形態による光電変換装置の動作について、図4を用いて説明する。図4には、画素12,14の制御信号PSEL, PRES, PTX、スイッチSW1,SW2の制御信号PSW、出力線18の信号VOUT、参照信号Vramp、比較器42,44の

50

出力信号（信号 L A T）のレベルを示している。なお、転送トランジスタ M 1、リセットトランジスタ M 2、選択トランジスタ M 4、スイッチ SW 1, SW 2 は、High レベルの制御信号を受けてオン（導通状態）になり、Low レベルの制御信号を受けてオフ（非導通状態）になるものとする。

#### 【0059】

時刻 t 1 の直前において、制御信号 PSEL, PTX, PSW は Low レベルであり、制御信号 PRES は High レベルである。画素 12, 14 のリセットトランジスタ M 2 はオンになっており、画素 12, 14 のノード FD は、電圧 Vdd に応じたリセットレベルの電圧（リセット電圧）にリセットされている。

#### 【0060】

時刻 t 1 において、垂直走査回路 20 は、制御信号 PSEL を Low レベルから High レベルへと制御する。これにより、画素 12, 14 の選択トランジスタ M 4 がオンになり、画素 12, 14 の増幅トランジスタ M 3 が選択トランジスタ M 4 を介して出力線 18 に接続される。その結果、出力線 18 及び選択トランジスタ M 4 を介して電流源 22 から増幅トランジスタ M 3 にバイアス電流が供給され、ノード FD のリセット電圧に応じた信号が選択トランジスタ M 4 を介して出力線 18 に出力される。

#### 【0061】

同じく時刻 t 1 において、タイミングジェネレータ 70 は、制御信号 PSW を Low レベルから High レベルへと制御する。これにより、列回路 32, 34 のスイッチ SW 1, SW 2 がオンになり、比較器 42, 44 がリセットされる。より具体的には、スイッチ SW 1, SW 2 がオンからオフに切り替わったときにおける、信号 VOUT と参照信号 Vrampとの間の電位差に相当する電圧に、比較器 42, 44 のオフセット電圧（閾値電圧）がリセットされる。また、参照信号 Vramp はリセット電圧からオフセット電圧に変化する。

#### 【0062】

続く時刻 t 2 において、垂直走査回路 20 は、制御信号 PRES を High レベルから Low レベルへと制御する。これにより、画素 12, 14 のリセットトランジスタ M 2 がオフになり、画素 12, 14 のノード FD のリセット状態が解除される。制御信号 PRE が High レベルから Low レベルに遷移するとき、リセットトランジスタ M 2 で生じるチャージインジェクションによってノード FD の電位が変化し、これに伴って出力線 18 の信号レベルも変化する。リセットトランジスタ M 2 がオフした後に出力線 18 に出力されている信号が、画素 12, 14 がリセット状態のときの画素信号（ノイズ信号）である。この画素信号を N 信号と表記するものとする。

#### 【0063】

続く時刻 t 3 において、タイミングジェネレータ 70 は、制御信号 PSW を High レベルから Low レベルへと制御する。これにより、スイッチ SW 1, SW 2 がオフになり、比較器 42, 44 のリセット状態が解除される。また、列回路 32, 34 の容量素子 C1 には N 信号がクランプされ、列回路 32, 34 の容量素子 C2 には比較器 42, 44 のオフセット電圧がクランプされる。このときの信号 VOUT のレベルと参照信号 Vramp のレベルとの差を電圧 VLC と表記するものとする。

#### 【0064】

続く時刻 t 4 において、参照信号生成回路 36 は、参照信号 Vramp のレベルをオフセット電圧のレベルからリセット電圧のレベルに戻す。これにより、出力線の信号 VOUT のレベルと参照信号 Vramp のレベルとの差が電圧 VLC よりも小さくなり、比較器 42, 44 の出力は Low レベルから High レベルへと遷移する。

#### 【0065】

続く時刻 t 5 から、参照信号生成回路 36 は、参照信号 Vramp のレベルを時間の経過に伴って単調に減少させる。同じく時刻 t 5 から、列回路 32, 34 のカウンタ回路 46 は、クロック信号 CLK に重畳するパルスの計数を開始する。比較器 42, 44 は、容量素子 C1 を介して出力線 18 から反転入力端子に入力される信号のレベルと、容量素子

10

20

30

40

50

C 2 を介して信号線 5 4 から非反転入力端子に入力される信号のレベルとの比較動作を行う。

#### 【 0 0 6 6 】

続く時刻 t 6において、出力線の信号 V O U T のレベルと参照信号 V r a m p のレベルとの差が電圧 V C L よりも大きくなったものとする。すると、容量素子 C 1 を介して比較器 4 2 , 4 4 の反転入力端子に入力される信号のレベルと、容量素子 C 2 を介して比較器 4 2 , 4 4 の非反転入力端子に入力される信号のレベルとの大小関係が逆転する。これにより、比較器 4 2 , 4 4 から出力される信号 L A T が H i g h レベルから L o w レベルへと変化を開始する。

#### 【 0 0 6 7 】

比較器 4 2 は、時刻 t 6 に対して一定の遅延時間有する。これにより、比較器 4 2 から出力される信号 L A T は反転閾値に達した時刻 t 7 のタイミングにおいて L o w レベルとなり、カウンタ回路 4 6 におけるカウント動作を停止する（図 4 に実線で示す）。時刻 t 5 から時刻 t 7 までの期間における計数値（n 1）が、画素 1 2 から出力されたアナログ信号（N 信号）を A D 変換（N 変換）したデジタル信号（デジタル N 信号）である。このように生成されたデジタル N 信号は、列回路 3 2 のメモリ部 4 8 に保持される。

10

#### 【 0 0 6 8 】

比較器 4 4 も、比較器 4 2 と同様、時刻 t 6 に対して一定の遅延時間有する。ただし、図 3 を用いて説明したように、比較器 4 4 のテイル電流源の電流値は比較器 4 2 のテイル電流源の電流値よりも小さいため、比較器 4 4 の遅延時間は比較器 4 2 の遅延時間よりも大きい。これにより、比較器 4 4 から出力される信号 L A T は、時刻 t 7 よりも遅い時刻 t 8 のタイミングにおいて反転閾値に達して L o w レベルとなり、カウンタ回路 4 6 におけるカウント動作を停止する（図 4 に破線で示す）。時刻 t 5 から時刻 t 8 までの期間における計数値（n 2）が、画素 1 4 から出力されたアナログ信号（N 信号）を A D 変換（N 変換）したデジタル信号（デジタル N 信号）である。このように生成されたデジタル N 信号は、列回路 3 4 のメモリ部 4 8 に保持される。

20

#### 【 0 0 6 9 】

このようにテイル電流源の電流値の異なる 2 つの比較器 4 2 , 4 4 を用いることで、画素 1 2 の信号を変換したデジタル N 信号が出力されるタイミングと、画素 1 4 の信号を変換したデジタル N 信号が出力されるタイミングと、をずらすことができる。

30

#### 【 0 0 7 0 】

続く時刻 t 9 において、参照信号生成回路 3 6 は、参照信号 V r a m p のレベルの降下を終了し、再びリセット電圧のレベルまで戻す。

#### 【 0 0 7 1 】

このようにして、時刻 t 4 から時刻 t 9 の期間における動作によって、画素 1 2 , 1 4 から出力線 1 8 に出力されたアナログ信号（N 信号）は、デジタル信号（デジタル N 信号）に変換（A D 変換）される。このようにして得られたデジタル N 信号は、比較器 4 2 , 4 4 の列ごとの特性ばらつきの成分を主とする信号である。デジタル N 信号には、ノード F D をリセットトランジスタ M 2 によりリセットする際のノイズや、比較器 4 2 , 4 4 のオフセット信号などが含まれ得る。

40

#### 【 0 0 7 2 】

本実施形態において、計数値 n 1 は O B 画素（画素 1 2 ）から出力された N 信号を A D 変換（N 変換）したデジタル信号の値であり、計数値 n 2 は有効画素（画素 1 4 ）から出力された N 信号を A D 変換（N 変換）したデジタル信号の値である。計数値 n 1 が決定される時刻（時刻 t 7 ）は、計数値 n 2 が決定される時刻（時刻 t 8 ）よりも早い。

#### 【 0 0 7 3 】

仮にこの順番が逆転し、計数値 n 2 が先に決定され、その後に計数値 n 1 が決定される場合を想定する。この場合、画素 1 4 の画素信号の A D 変換において比較器 4 4 が一斉反転することにより生じるノイズが、その後に行われる画素 1 2 の画素信号の A D 変換に影響を与え、計数値 n 1 に誤差を生じる虞がある。

50

**【 0 0 7 4 】**

この点、本実施形態では計数値  $n_1$  を先に決定し、その後に計数値  $n_2$  を決定するため、比較器 4 4 が一斉反転することにより生じるノイズに起因する計数値  $n_1$  の誤差を低減することができる。

**【 0 0 7 5 】**

一方、本実施形態では、比較器 4 2 が一斉反転することにより生じるノイズに起因して計数値  $n_2$  に誤差を生じる可能性はある。しかしながら、計数値  $n_2$  に生じる誤差は計数値  $n_1$  に生じる誤差と比較して画質の悪化の要因とはなりにくい。これは、計数値  $n_1$  は黒レベルの基準となるためノイズの影響があると基準レベルがずれないと誤判定されるのに対して、計数値  $n_2$  は基準レベルに影響しないからである。また、前記ノイズは有効画素に光が照射した状態において発生する現象であるため、光電変換信号の影響（光ショットノイズや感度ばらつき）によってノイズが目立たなくなることも画質の悪化になりにくい要素として考えられる。

10

**【 0 0 7 6 】**

このように本実施形態では、比較器 4 2 で N 変換したデジタル信号の値と比較器 4 4 で N 変換したデジタル信号の値とを分散させ、比較器 4 2 で N 変換したデジタル信号を比較器 4 4 で N 変換したデジタル信号よりも先に出力している。したがって、ノイズの影響の少ない良好な画像を得ることができる。

**【 0 0 7 7 】**

続く時刻  $t_{10}$  から時刻  $t_{11}$  の期間において、垂直走査回路 2 0 は、制御信号 P T X を Low レベルから High レベルへと制御する。これにより、画素 1 2, 1 4 の転送トランジスタ M 1 がオンになり、画素 1 2, 1 4 の光電変換素子 P D が保持する電荷がノード F D へと転送される。ノード F D は、浮遊拡散容量による電荷電圧変換によって光電変換素子 P D から転送された電荷の量に応じた電位となる。増幅トランジスタ M 3 は、ノード F D の電位に応じた画素信号を、選択トランジスタ M 4 を介して出力線 1 8 に出力する。転送トランジスタ M 1 がオフした後に出力線 1 8 に出力されている信号が、光電変換素子 P D で生成された電荷の量に応じた画素信号（光電変換信号）である。この画素信号には光電変換素子 P D で生成された電荷の量に応じた成分に加え、N 信号の成分も含まれているため、S + N 信号と表記するものとする。

20

**【 0 0 7 8 】**

これにより、画素 1 4 に接続された出力線 1 8 の信号 V O U T のレベルは、光電変換素子 P D から転送された電荷の量に応じた所定のレベルに低下する。一方、画素 1 2 の光電変換素子 P D は遮光されているため、画素 1 2 に接続された出力線 1 8 の信号 V O U T のレベルは変化しない。出力線 1 8 に出力された画素信号は、N 信号をクランプしている容量素子 C 1 を介して比較器 4 2, 4 4 の反転入力端子に入力される。

30

**【 0 0 7 9 】**

続く時刻  $t_{12}$  から、参照信号生成回路 3 6 は、参照信号 V r a m p のレベルを時間の経過に伴って単調に減少させる。同じく時刻  $t_{12}$  から、列回路 3 2, 3 4 のカウンタ回路 4 6 は、クロック信号 C L K に重畠するパルスの計数を開始する。比較器 4 2, 4 4 は、容量素子 C 1 を介して出力線 1 8 から反転入力端子に入力される信号のレベルと、容量素子 C 2 を介して信号線 5 4 から非反転入力端子に入力される信号のレベルとの比較動作を行う。

40

**【 0 0 8 0 】**

続く時刻  $t_{13}$  において、画素 1 2 に接続された出力線 1 8 の信号 V O U T のレベルと参照信号 V r a m p のレベルとの差が電圧 V C L よりも大きくなったものとする。すると、容量素子 C 1 を介して比較器 4 2 の反転入力端子に入力される信号のレベルと、容量素子 C 2 を介して比較器 4 2 の非反転入力端子に入力される信号のレベルとの大小関係が逆転する。これにより、比較器 4 2 から出力される信号 L A T が High レベルから Low レベルへと変化を開始する。

**【 0 0 8 1 】**

50

比較器 4 2 は、時刻  $t_{13}$  に対して一定の遅延時間有する。これにより、比較器 4 2 から出力される信号 L A T は反転閾値に達した時刻  $t_{14}$  のタイミングにおいて L o w レベルとなり、カウンタ回路 4 6 におけるカウント動作を停止する（図 4 に実線で示す）。時刻  $t_{12}$  から時刻  $t_{14}$  までの期間における計数値  $S_1 (= n_1 + A_1)$  が、画素 1 2 から出力されたアナログ信号（S + N 信号）を A D 変換（S 変換）したデジタル信号（デジタル S 信号）である。なお、計数値  $S_1$  は、典型的には計数値  $n_1$  と同じである。このように生成されたデジタル S 信号は、列回路 3 4 のメモリ部 4 8 に保持される。

#### 【 0 0 8 2 】

続く時刻  $t_{15}$  において、画素 1 4 に接続された出力線 1 8 の信号 V O U T のレベルと参照信号 V r a m p のレベルとの差が電圧 V C L よりも大きくなつたものとする。すると、容量素子 C 1 を介して比較器 4 4 の反転入力端子に入力される信号のレベルと、容量素子 C 2 を介して比較器 4 4 の非反転入力端子に入力される信号のレベルとの大小関係が逆転する。これにより、比較器 4 4 から出力される信号 L A T が H i g h レベルから L o w レベルへと変化を開始する。

10

#### 【 0 0 8 3 】

比較器 4 4 は、時刻  $t_{15}$  に対して一定の遅延時間有する。これにより、比較器 4 4 から出力される信号 L A T は反転閾値に達した時刻  $t_{16}$  のタイミングにおいて L o w レベルとなり、カウンタ回路 4 6 におけるカウント動作を停止する（図 4 に点線で示す）。時刻  $t_{12}$  から時刻  $t_{16}$  までの期間における計数値  $S_2 (= n_2 + A_2)$  が、画素 1 4 から出力されたアナログ信号（S + N 信号）を A D 変換（S 変換）したデジタル信号（デジタル S 信号）である。このように生成されたデジタル S 信号は、列回路 3 4 のメモリ部 4 8 に保持される。

20

#### 【 0 0 8 4 】

続く時刻  $t_{17}$  において、参照信号生成回路 3 6 は、参照信号 V r a m p のレベルの下降を終了し、再びリセット電圧のレベルまで昇圧する。

#### 【 0 0 8 5 】

このようにして、時刻  $t_{10}$  から時刻  $t_{17}$  の期間における動作によって、各列の画素 1 2, 1 4 から出力されたアナログ信号（S + N 信号）は、デジタル信号（デジタル S 信号）に変換（A D 変換）される。

30

#### 【 0 0 8 6 】

この後、水平走査回路 5 0 は、各列の列回路 3 2, 3 4 のメモリ部 4 8 を順次選択し、メモリ部 4 8 が保持するデジタル N 信号及びデジタル S 信号を、出力線 5 2 を介してデジタル信号処理回路 6 0 へと転送する。

#### 【 0 0 8 7 】

デジタル信号処理回路 6 0 では、デジタル S 信号とデジタル N 信号との差分処理が行われる。これにより、デジタル S 信号に重畠するノイズ成分を除去し、信号 V O U T の変化に応じた信号を取得することができる。

40

#### 【 0 0 8 8 】

なお、比較器 4 2, 4 4 の遅延時間は回路定数や電流値等によって定まる数値のため、N 変換時の遅延時間と S 変換時の遅延時間とは等しい。したがって、デジタル S 信号とデジタル N 信号との差分処理を行うことで比較器 4 2, 4 4 の遅延時間の影響はキャンセルされ、差分処理後の計数値  $A_1, A_2$  の値は比較器 4 2, 4 4 の遅延時間とは関係のない信号 V O U T の変化に応じた値となる。

#### 【 0 0 8 9 】

したがって、比較器 4 4 で N 変換したデジタル信号の値と比較器 4 2 で N 変換したデジタル信号の値とを分散させ、比較器 4 2 で N 変換したデジタル信号を比較器 4 4 で N 変換したデジタル信号よりも先に出力する動作が画質に影響することはない。

50

#### 【 0 0 9 0 】

また、画素 1 4（OB 画素）の A D 変換結果を画素 1 4（有効画素）の A D 変換結果よりも先に出力することで、仮に画素 1 2 の出力信号のレベルと画素 1 4 の出力信号のレベ

ルとの間に段差が発生したとしても、この現象は補正可能である。

#### 【0091】

例えば、画素アレイ部10に、総ての列に画素14が配された画素行と、画素12と画素14とを含む画素行とを設ける。こうすることで、画素12, 14が配された行の画素12の出力信号のレベルと画素14の出力信号のレベルとの間に段差が発生した場合には、画素14のみが配された行の画素14の出力信号のレベルにも同様の段差が発生する。したがって、画素14のみが配された行の画素信号を用いることで、列間で生じる画素12の出力信号のレベルと画素14の出力信号のレベルとの間の段差を補正することができる。

#### 【0092】

このように、本実施形態によれば、比較器42, 44の出力レベルの一斉反転に起因して生じるノイズを効果的に抑制することができる。これにより、画素12から取得する基準信号に重畠するノイズを低減し、画質の良好な画像を取得することができる。

#### 【0093】

なお、本実施形態では遅延時間の異なる2種類の比較器42, 44を用いたが、遅延時間の異なる比較器は2種類に限定されるものではなく、3種類以上であってもよい。この場合にも、OB画素(画素14)のAD変換結果が他の画素(画素14)のAD変換結果よりも先に出力されるように構成することにより、本実施形態と同様の効果を得ることができる。

#### 【0094】

また、各列の比較器42, 44のテイル電流源の電流量をアナログ的に変化させ、列ごとに少しずつ比較器42, 44の遅延時間が異なる構成としてもよい。このように構成することによっても、本実施形態と同様の効果を得ることができる。

#### 【0095】

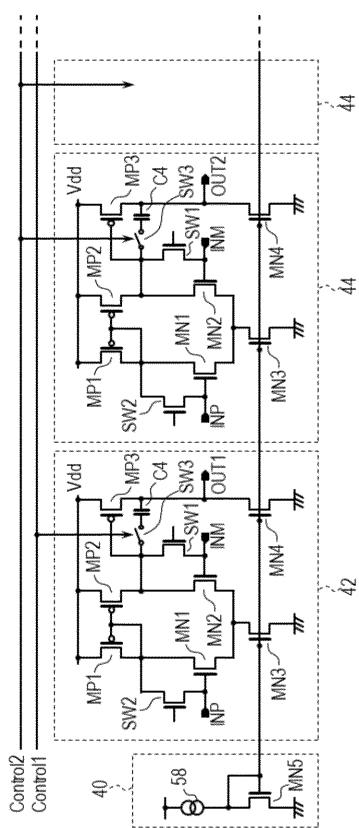

##### [第2実施形態]

本発明の第2実施形態による光電変換装置及びその駆動方法について、図5を用いて説明する。第1実施形態と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。図5は、本実施形態による光電変換装置における比較器の構成例を示す回路図である。

#### 【0096】

本実施形態による光電変換装置は、比較器42, 44の構成が第1実施形態による光電変換装置とは異なっている。

#### 【0097】

すなわち、本実施形態による光電変換装置の比較器42, 44は、図5に示すように、差動增幅回路の+側出力端子とソース接地増幅回路の出力端子との間に、スイッチSW3と容量素子C4とが直列に接続されている。比較器42のスイッチSW3は、タイミングジェネレータ70から供給される制御信号Control1により制御されるスイッチである。比較器44のスイッチSW3は、タイミングジェネレータ70から供給される制御信号Control2により制御されるスイッチである。

#### 【0098】

また、本実施形態による光電変換装置の比較器42, 44のN型トランジスタMN3, MN4の各々は、電流源回路40のN型トランジスタMN5とカレントミラー回路を構成しており、定電流源として動作する。比較器42のN型トランジスタMN3に流れる電流と、比較器44のN型トランジスタMN3に流れる電流とは同じである。また、比較器42のN型トランジスタMN4に流れる電流と、比較器44のN型トランジスタMN4に流れる電流とは同じである。

#### 【0099】

本実施形態による光電変換装置のその他の構成は、第1実施形態による光電変換装置と同様である。

#### 【0100】

10

20

30

40

50

比較器 42, 44 の差動増幅回路の+側出力端子とソース接地増幅回路の出力端子との間に直列に接続された容量素子 C4 とスイッチ SW3 とは、比較器 42, 44 の遅延時間を切り替え可能な遅延回路を構成する。すなわち、スイッチ SW3 によって容量素子 C4 の接続の有無を選択することにより、比較器 42, 44 の遅延時間を変えることができる。なお、遅延時間を切り替え可能な遅延回路を比較器 42, 44 に設ける代わりに、比較器 44 に選択的に遅延回路を設けてもよい。

#### 【0101】

本実施形態では、制御信号 Control11, Control12 が High レベルのときにスイッチ SW3 がオン（導通状態）になり、容量素子 C4 が接続された状態（遅延時間大）になるものとする。また、制御信号 Control11, Control12 が Low レベルのときにスイッチ SW3 がオフ（非導通状態）になり、容量素子 C4 が切り離された状態（遅延時間小）になるものとする。この場合、制御信号 Control11 を Low レベルに制御し、制御信号 Control12 を High レベルに制御することで、比較器 42 のスルーレートは比較器 44 のスルーレートよりも高くなる。つまり、比較器 44 の遅延時間は比較器 42 の遅延時間よりも長くなる。

#### 【0102】

これにより、第 1 実施形態において比較器 42 のテイル電流源の電流値を比較器 44 のテイル電流源の電流値よりも大きくした場合と同様、OB 画素の画素信号の AD 変換を有効画素の画素信号の AD 変換よりも先に終えることができる。したがって、ノイズの影響の少ない良好な画質を得ることができる。

#### 【0103】

このように、本実施形態によれば、比較器 42, 44 の出力レベルの一斉反転に起因して生じるノイズを効果的に抑制することができる。これにより、画素 12 から取得する基準信号に重畳するノイズを低減し、画質の良好な画像を取得することができる。

#### 【0104】

なお、本実施形態では容量素子 C4 を用いて比較器 42, 44 の遅延時間を制御したが、比較器 42, 44 の遅延時間を制御する方法はこれに限定されるものではない。例えば、比較器 42, 44 とで配線抵抗やトランジスタの閾値電圧を変化させることにより、遅延時間を制御するようにしてもよい。また、容量素子の配置も本実施形態に限定されるものではなく、対 GND や電源などの容量素子を用いて遅延回路を構成してもよい。

#### 【0105】

また、本実施形態では遅延時間の異なる 2 種類の比較器 42, 44 を用いたが、遅延時間の異なる比較器は 2 種類に限定されるものではなく、3 種類以上であってもよい。この場合にも、OB 画素（画素 14）の AD 変換結果が他の画素の AD 変換結果よりも先に出力されるように構成することにより、本実施形態と同様の効果を得ることができる。

#### 【0106】

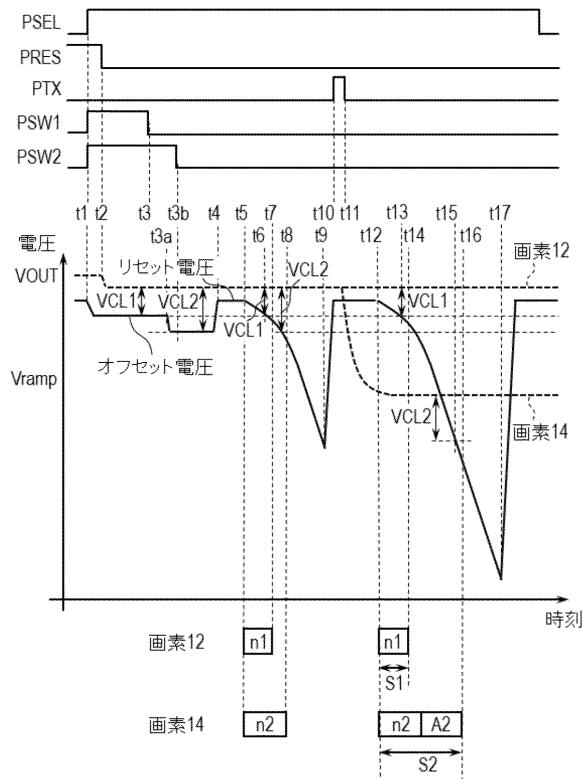

##### 〔第 3 実施形態〕

本発明の第 3 実施形態による光電変換装置の駆動方法について、図 6 を用いて説明する。第 1 実施形態と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。図 6 は、本実施形態による光電変換装置の動作を示すタイミング図である。

#### 【0107】

本実施形態では、第 1 実施形態による光電変換装置の他の駆動方法を説明する。

第 1 実施形態では、比較器 44 に接続されたスイッチ SW1, SW2 と比較器 42 に接続されたスイッチ SW1, SW2 と同じタイミングで駆動した。本実施形態では、比較器 44 に接続されたスイッチ SW1, SW2 と比較器 42 に接続されたスイッチ SW1, SW2 と異なるタイミングで駆動する。

#### 【0108】

図 6 には、画素 12, 14 の制御信号 PSEL, PRES, PTX、比較器 42 のスイッチの制御信号 PSW1、比較器 44 のスイッチの制御信号 PSW2、出力線 18 の信号 VOUT、参照信号 Vramp のレベルを示している。

10

20

30

40

50

**【0109】**

時刻  $t_1$  の直前において、制御信号 PSEL, PTX, PSW1, PSW2 は Low レベルであり、制御信号 PRES は High レベルである。画素 12, 14 のリセットトランジスタ M2 はオンになっており、画素 12, 14 のノード FD は、電圧 Vdd に応じたリセットレベルの電圧（リセット電圧）にリセットされている。

**【0110】**

時刻  $t_1$  において、垂直走査回路 20 は、制御信号 PSEL を Low レベルから High レベルへと制御する。これにより、画素 12, 14 の選択トランジスタ M4 がオンになり、画素 12, 14 の増幅トランジスタ M3 が選択トランジスタ M4 を介して出力線 18 に接続される。その結果、出力線 18 及び選択トランジスタ M4 を介して電流源 22 から増幅トランジスタ M3 にバイアス電流が供給され、ノード FD のリセット電圧に応じた信号が選択トランジスタ M4 を介して出力線 18 に出力される。10

**【0111】**

同じく時刻  $t_1$  において、タイミングジェネレータ 70 は、制御信号 PSW1, PSW2 を Low レベルから High レベルへと制御する。これにより、列回路 32, 34 のスイッチ SW1, SW2 がオンになり、比較器 42, 44 がリセットされる。また、参照信号 Vramp はリセット電圧からオフセット電圧に変化する。

**【0112】**

続く時刻  $t_2$  において、垂直走査回路 20 は、制御信号 PRES を High レベルから Low レベルへと制御する。これにより、画素 12, 14 のリセットトランジスタ M2 がオフになり、画素 12, 14 のノード FD のリセット状態が解除される。出力線 18 には、画素 12, 14 がリセット状態のときの画素信号（N 信号）が出力される。20

**【0113】**

続く時刻  $t_3$  において、タイミングジェネレータ 70 は、制御信号 PSW1 を High レベルから Low レベルへと制御する。これにより、比較器 42 のスイッチ SW1, SW2 がオフになり、比較器 42 のリセット状態が解除される。また、列回路 32 の容量素子 C1 には画素 14 の N 信号がクランプされ、列回路 32 の容量素子 C2 には電圧 VLC1 がクランプされる。

**【0114】**

続く時刻  $t_{3a}$  において、参照信号生成回路 36 は、信号 VOUT に対する参照信号 Vramp のレベルの差が電圧 VLC1 よりも大きい電圧 VLC2 になるように、参照信号 Vramp のレベルを制御する。30

**【0115】**

続く時刻  $t_{3b}$  において、タイミングジェネレータ 70 は、制御信号 PSW2 を High レベルから Low レベルへと制御する。これにより、比較器 44 のスイッチ SW1, SW2 がオフになり、比較器 44 のリセット状態が解除される。また、列回路 34 の容量素子 C1 には画素 14 の N 信号がクランプされ、列回路 34 の容量素子 C2 には電圧 VLC2 がクランプされる。

**【0116】**

続く時刻  $t_4$  において、参照信号生成回路 36 は、参照信号 Vramp のレベルをリセット電圧のレベルに戻す。これにより、比較器 42, 44 の非反転入力端子の電圧が反転入力端子の電圧よりも高くなり、比較器 42, 44 の出力は Low レベルから High レベルへと遷移する。40

**【0117】**

この後、時刻  $t_5$  から時刻  $t_9$  の期間において、第 1 実施形態と同様に N 信号の AD 変換を行う。

**【0118】**

時刻  $t_6$  において、出力線の信号 VOUT のレベルと参照信号 Vramp のレベルとの差が電圧 VLC1 よりも大きくなったものとする。すると、容量素子 C1 を介して比較器 42 の反転入力端子に入力される信号のレベルと、容量素子 C2 を介して比較器 42 の非

反転入力端子に入力される信号のレベルとの大小関係が逆転する。これにより、時刻  $t_6$  から所定の遅延時間の後の時刻  $t_7$  において、比較器 4 2 から出力される信号 L A T が H i g h レベルから L o w レベルに遷移し、時刻  $t_5$  から時刻  $t_7$  までの期間における計数値 (n 1) が列回路 3 2 のメモリ部 4 8 に保持される。

#### 【 0 1 1 9 】

また、時刻 6 よりも後のタイミングにおいて、出力線の信号 V O U T のレベルと参照信号 V r a m p のレベルとの差が電圧 V C L 2 よりも大きくなつたものとする。すると、容量素子 C 1 を介して比較器 4 4 の反転入力端子に入力される信号のレベルと、容量素子 C 2 を介して比較器 4 4 の非反転入力端子に入力される信号のレベルとの大小関係が逆転する。これにより、所定の遅延時間の後の時刻  $t_8$  において、比較器 4 4 から出力される信号 L A T が H i g h レベルから L o w レベルに遷移し、時刻  $t_5$  から時刻  $t_8$  までの期間における計数値 (n 2) が列回路 3 4 のメモリ部 4 8 に保持される。10

#### 【 0 1 2 0 】

このように、本実施形態では、列回路 3 4 の容量素子 C 2 にクランプする電圧 V C L 2 を列回路 3 2 の容量素子 C 2 にクランプする電圧 V C L 1 よりも大きくすることで、比較器 4 4 が反転するタイミングを比較器 4 2 が反転するタイミングよりも遅くしている。

#### 【 0 1 2 1 】

これにより、第 1 実施形態において比較器 4 2 のテイル電流源の電流値を比較器 4 4 のテイル電流源の電流値よりも大きくした場合と同様、O B 画素の画素信号の A D 変換を有効画素の画素信号の A D 変換よりも先に終えることができる。したがって、ノイズの影響の少ない良好な画質を得ることができる。20

#### 【 0 1 2 2 】

このように、本実施形態によれば、比較器 4 2 , 4 4 の出力レベルの一斉反転に起因して生じるノイズを効果的に抑制することができる。これにより、画素 1 2 から取得する基準信号に重畳するノイズを低減し、画質の良好な画像を取得することができる。

#### 【 0 1 2 3 】

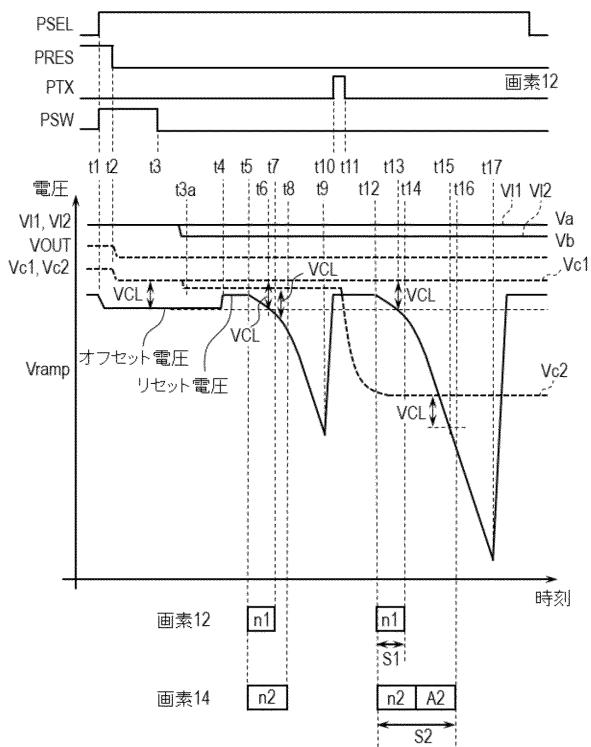

##### [ 第 4 実施形態 ]

本発明の第 4 実施形態による光電変換装置及びその駆動方法について、図 7 及び図 8 を用いて説明する。第 1 実施形態と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。図 7 は、本実施形態による光電変換装置における画素及び列回路の構成例を示す回路図である。図 8 は、本実施形態による光電変換装置の動作を示すタイミング図である。30

#### 【 0 1 2 4 】

本実施形態による光電変換装置は、列回路 3 2 , 3 4 の構成が第 1 実施形態による光電変換装置とは異なっている。すなわち、本実施形態による光電変換装置の列回路 3 2 , 3 4 は、図 7 に示すように、容量素子 C 3 を更に有している。

#### 【 0 1 2 5 】

列回路 3 2 の容量素子 C 3 の一方の電極は、比較器 4 2 の反転入力端子に接続されている。列回路 3 2 の容量素子 C 3 の他方の電極は、信号線 6 2 a を介してタイミングジェネレータ 7 0 に接続されている。信号線 6 2 a には、タイミングジェネレータ 7 0 から信号 V 1 1 が供給される。40

#### 【 0 1 2 6 】

列回路 3 4 の容量素子 C 3 の一方の電極は、比較器 4 4 の反転入力端子に接続されている。列回路 3 4 の容量素子 C 3 の他方の電極は、信号線 6 2 b を介してタイミングジェネレータ 7 0 に接続されている。信号線 6 2 b には、タイミングジェネレータ 7 0 から信号 V 1 2 が供給される。

#### 【 0 1 2 7 】

本実施形態による光電変換装置のその他の構成は、第 1 実施形態による光電変換装置と同様である。

#### 【 0 1 2 8 】

次に、本実施形態による光電変換装置の動作について、図8を用いて説明する。図8には、画素12, 14の制御信号PSEL, PRES, PTX、スイッチSW1, SW2の制御信号PSW、信号V11, V12のレベルを示している。また、図8には、出力線18の信号VOUT、比較器42の反転入力端子の電圧Vc1、比較器44の反転入力端子の電圧Vc2、参照信号Vrampのレベルを示している。

#### 【0129】

時刻t1の直前において、制御信号PSEL, PTX, PSWはLowレベルであり、制御信号PRESはHighレベルである。画素12, 14のリセットトランジスタM2はオンになっており、画素12, 14のノードFDは、電圧Vddに応じたリセットレベルの電圧(リセット電圧)にリセットされている。また、信号線62aの信号V11及び信号線62bの信号V12は、ともに電圧Vaである。10

#### 【0130】

時刻t1において、垂直走査回路20は、制御信号PSELをLowレベルからHighレベルへと制御する。これにより、画素12, 14の選択トランジスタM4がオンになり、画素12, 14の増幅トランジスタM3が選択トランジスタM4を介して出力線18に接続される。その結果、出力線18及び選択トランジスタM4を介して電流源22から増幅トランジスタM3にバイアス電流が供給され、ノードFDのリセット電圧に応じた信号が選択トランジスタM4を介して出力線18に出力される。

#### 【0131】

同じく時刻t1において、タイミングジェネレータ70は、制御信号PSWをLowレベルからHighレベルへと制御する。これにより、列回路32, 34のスイッチSW1, SW2がオンになり、比較器42, 44がリセットされる。また、参照信号Vrampはリセット電圧からオフセット電圧に変化する。20

#### 【0132】

続く時刻t2において、垂直走査回路20は、制御信号PRESをHighレベルからLowレベルへと制御する。これにより、画素12, 14のリセットトランジスタM2がオフになり、画素12, 14のノードFDのリセット状態が解除される。出力線18には、画素12, 14がリセット状態のときの画素信号(N信号)が出力される。

#### 【0133】

続く時刻t3において、タイミングジェネレータ70は、制御信号PSWをHighレベルからLowレベルへと制御する。これにより、比較器42, 44のスイッチSW1, SW2がオフになり、比較器42, 44のリセット状態が解除される。また、列回路32, 34の容量素子C1には画素14のN信号がクランプされ、列回路32, 34の容量素子C2には電圧VCLがクランプされる。30

#### 【0134】

続く時刻t3aにおいて、タイミングジェネレータ70は、信号線62bの信号V12のレベルを電圧Vaから電圧Vbに制御する。この信号V12の電圧変化に応じて、比較器44の反転入力端子の電圧Vc2も低下する。なお、信号V11は電圧Vaのままであるため、比較器42の反転入力端子の電圧Vc1は変化しない。

#### 【0135】

続く時刻t4において、参照信号生成回路36は、参照信号Vrampのレベルをリセット電圧のレベルに戻す。これにより、比較器42, 44の非反転入力端子の電圧が反転入力端子の電圧よりも高くなり、比較器42, 44の出力はLowレベルからHighレベルへと遷移する。40

#### 【0136】

この後、時刻t5から時刻t9の期間において、第1実施形態と同様にN信号のAD変換を行う。

#### 【0137】

時刻t6において、電圧Vc1のレベルと参照信号Vrampのレベルとの差が電圧VCLよりも大きくなり、比較器42の反転入力端子と非反転入力端子とに入力される信号

10

20

30

40

50

のレベルの差が比較器 4 2 の反転閾値を超えたものとする。これにより、時刻  $t_6$  から所定の遅延時間の後の時刻  $t_7$  において、比較器 4 2 から出力される信号 L A T が H i g h レベルから L o w レベルに遷移し、時刻  $t_5$  から時刻  $t_7$  までの期間における計数値 (  $n_1$  ) が列回路 3 2 のメモリ部 4 8 に保持される。

#### 【 0 1 3 8 】

また、時刻  $t_6$  よりも後のタイミングにおいて、電圧 V c 2 のレベルと参照信号 V r a m p のレベルとの差が電圧 V C L よりも大きくなり、比較器 4 4 の反転入力端子と非反転入力端子とに入力される信号のレベルの差が比較器 4 4 の反転閾値を超えたものとする。これにより、所定の遅延時間の後の時刻  $t_8$  において、比較器 4 4 から出力される信号 L A T が H i g h レベルから L o w レベルに遷移し、時刻  $t_5$  から時刻  $t_8$  までの期間における計数値 (  $n_2$  ) が列回路 3 4 のメモリ部 4 8 に保持される。10

#### 【 0 1 3 9 】

このように、本実施形態においては、比較器 4 4 の反転入力端子の電圧を比較器 4 2 の反転入力端子の電圧よりも低くすることで、比較器 4 4 が反転するタイミングを比較器 4 2 が反転するタイミングよりも遅くしている。

#### 【 0 1 4 0 】

これにより、第 1 実施形態において比較器 4 2 のテイル電流源の電流値を比較器 4 4 のテイル電流源の電流値よりも大きくした場合と同様、O B 画素の画素信号の A D 変換を有効画素の画素信号の A D 変換よりも先に終えることができる。したがって、ノイズの影響の少ない良好な画質を得ることができる。20

#### 【 0 1 4 1 】

このように、本実施形態によれば、比較器 4 2 , 4 4 の出力レベルの一斉反転に起因して生じるノイズを効果的に抑制することができる。これにより、画素 1 2 から取得する基準信号に重畳するノイズを低減し、画質の良好な画像を取得することができる。

#### 【 0 1 4 2 】

なお、本実施形態では、比較器 4 2 の反転入力端子の電圧よりも低くなるように比較器 4 4 の反転入力端子の電圧を制御したが、比較器 4 4 の反転入力端子の電圧よりも高くなるように比較器 4 2 の反転入力端子の電圧を制御してもよい。或いは、比較器 4 2 の反転入力端子の電圧が比較器 4 4 の反転入力端子の電圧よりも低くなるように、比較器 4 2 の反転入力端子の電圧及び比較器 4 4 の反転入力端子の電圧を制御してもよい。30

#### 【 0 1 4 3 】

##### [ 第 5 実施形態 ]

本発明の第 5 実施形態による撮像システムについて、図 9 を用いて説明する。図 9 は、本実施形態による撮像システムの概略構成を示すプロック図である。

#### 【 0 1 4 4 】

上記第 1 乃至第 4 実施形態で述べた光電変換装置 1 0 0 は、種々の撮像システムに適用可能である。適用可能な撮像システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図 9 には、これらのうちの一例として、デジタルスチルカメラのプロック図を例示している。40

#### 【 0 1 4 5 】

図 9 に例示した撮像システム 2 0 0 は、撮像装置 2 0 1 、被写体の光学像を撮像装置 2 0 1 に結像させるレンズ 2 0 2 、レンズ 2 0 2 を通過する光量を可変にするための絞り 2 0 4 、レンズ 2 0 2 の保護のためのバリア 2 0 6 を有する。レンズ 2 0 2 及び絞り 2 0 4 は、撮像装置 2 0 1 に光を集光する光学系である。撮像装置 2 0 1 は、第 1 乃至第 4 実施形態のいずれかで説明した光電変換装置 1 0 0 であって、レンズ 2 0 2 により結像された光学像を画像データに変換する。

#### 【 0 1 4 6 】

撮像システム 2 0 0 は、また、撮像装置 2 0 1 より出力される出力信号の処理を行う信50

号処理部 208 を有する。信号処理部 208 は、撮像装置 201 が output するデジタル信号から画像データの生成を行う。また、信号処理部 208 は必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。撮像装置 201 は、信号処理部 208 で処理されるデジタル信号を生成する A/D 変換部を備えうる。A/D 変換部は、撮像装置 201 の光電変換部が形成された半導体層（半導体基板）に形成されていてもよいし、撮像装置 201 の光電変換部が形成された半導体層とは別の半導体基板に形成されていてもよい。また、信号処理部 208 が撮像装置 201 と同一の半導体基板に形成されていてもよい。

#### 【0147】

撮像システム 200 は、更に、画像データを一時的に記憶するためのメモリ部 210、外部コンピュータ等と通信するための外部インターフェース部（外部 I/F 部）212 を有する。更に撮像システム 200 は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体 214、記録媒体 214 に記録又は読み出しを行うための記録媒体制御インターフェース部（記録媒体制御 I/F 部）216 を有する。なお、記録媒体 214 は、撮像システム 200 に内蔵されていてもよく、着脱可能であってもよい。

10

#### 【0148】

更に撮像システム 200 は、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部 218、撮像装置 201 と信号処理部 208 に各種タイミング信号を出力するタイミング発生部 220 を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム 200 は少なくとも撮像装置 201 と、撮像装置 201 から出力された出力信号を処理する信号処理部 208 とを有すればよい。

20

#### 【0149】

撮像装置 201 は、撮像信号を信号処理部 208 に出力する。信号処理部 208 は、撮像装置 201 から出力される撮像信号に対して所定の信号処理を実施し、画像データを出力する。信号処理部 208 は、撮像信号を用いて、画像を生成する。

#### 【0150】

このように、本実施形態によれば、第 1 乃至第 4 実施形態による光電変換装置 100 を適用した撮像システムを実現することができる。

#### 【0151】

##### [第 6 実施形態]

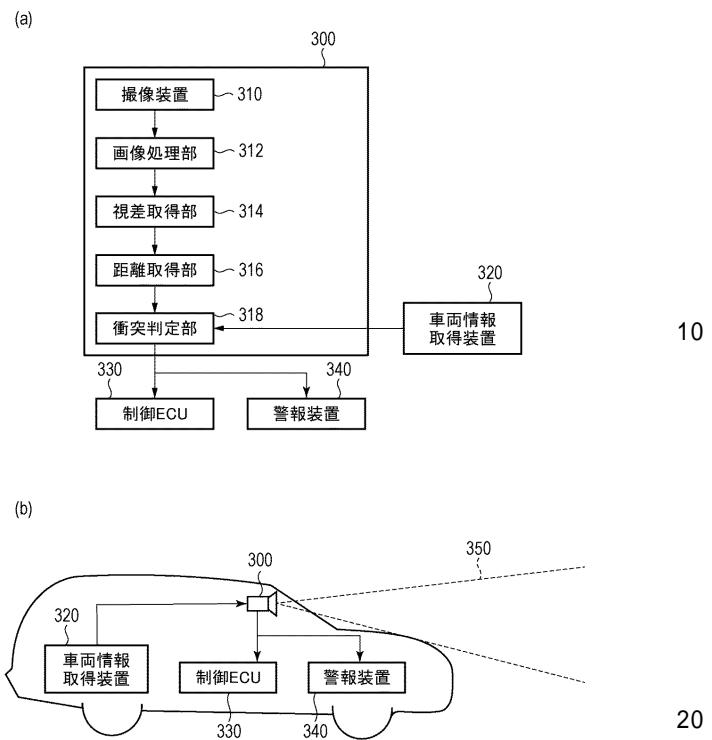

本発明の第 6 実施形態による撮像システム及び移動体について、図 10 を用いて説明する。図 10 は、本実施形態による撮像システム及び移動体の構成を示す図である。

30

#### 【0152】

図 10 (a) は、車載カメラに関する撮像システムの一例を示したものである。撮像システム 300 は、撮像装置 310 を有する。撮像装置 310 は、上記第 1 乃至第 4 実施形態のいずれかに記載の光電変換装置 100 である。撮像システム 300 は、撮像装置 310 により取得された複数の画像データに対し、画像処理を行う画像処理部 312 と、撮像システム 300 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部 314 を有する。また、撮像システム 300 は、算出された視差に基づいて対象物までの距離を算出する距離取得部 316 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 318 と、を有する。ここで、視差取得部 314 や距離取得部 316 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

40

#### 【0153】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部

50

318での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御E C U 330が接続されている。また、撮像システム300は、衝突判定部318での判定結果に基づいて、ドライバーへ警報を発する警報装置340とも接続されている。例えば、衝突判定部318の判定結果として衝突可能性が高い場合、制御E C U 330はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突回避、被害を軽減する車両制御を行う。警報装置340は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0154】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム300で撮像する。

図10(b)に、車両前方(撮像範囲350)を撮像する場合の撮像システムを示した。車両情報取得装置320が、撮像システム300ないしは撮像装置310に指示を送る。このような構成により、測距の精度をより向上させることができる。

10

#### 【0155】

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体(移動装置)に適用することができる。加えて、移動体に限らず、高度道路交通システム(ITS)等、広く物体認識を利用する機器に適用することができる。

20

#### 【0156】

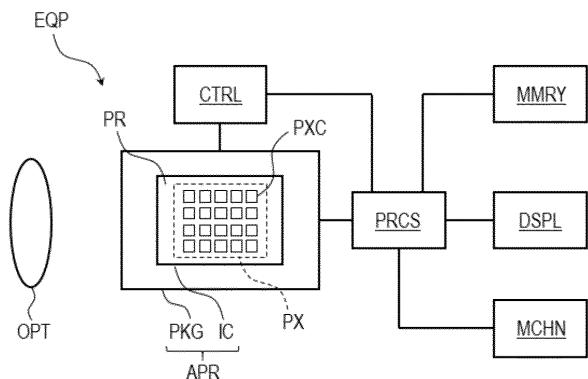

##### [第7実施形態]

本発明の第7実施形態による機器について、図11を用いて説明する。図11は、本実施形態による機器の概略構成を示すブロック図である。

#### 【0157】

図11は、光電変換装置A P Rを含む機器E Q Pを示す模式図である。光電変換装置A P Rは、第1乃至第4実施形態のいずれかの光電変換装置100の機能を備える。光電変換装置A P Rの全部又は一部が、半導体デバイスI Cである。本例の光電変換装置A P Rは、例えば、イメージセンサやA F(Auto Focus)センサ、測光センサ、測距センサとして用いることができる。半導体デバイスI Cは、光電変換部を含む画素回路P X Cが行列状に配列された画素エリアP Xを有する。半導体デバイスI Cは画素エリアP Xの周囲に周辺エリアP Rを有することができる。周辺エリアP Rには画素回路以外の回路を配置することができる。

30

#### 【0158】

光電変換装置A P Rは、複数の光電変換部が設けられた第1半導体チップと、周辺回路が設けられた第2半導体チップとを積層した構造(チップ積層構造)を有していてもよい。第2半導体チップにおける周辺回路は、それぞれ、第1半導体チップの画素列に対応した列回路とすることができる。また、第2半導体チップにおける周辺回路は、それぞれ、第1半導体チップの画素あるいは画素ブロックに対応したマトリクス回路とすることもできる。第1半導体チップと第2半導体チップとの接続は、貫通電極(T S V)、銅等の導電体の直接接合によるチップ間配線、チップ間のマイクロバンプによる接続、ワイヤボンディングによる接続などを採用することができる。

40

#### 【0159】

光電変換装置A P Rは、半導体デバイスI Cの他に、半導体デバイスI Cを収容するパッケージP K Gを含みうる。パッケージP K Gは、半導体デバイスI Cが固定された基体と、半導体デバイスI Cに対向するガラス等の蓋体と、基体に設けられた端子と半導体デバイスI Cに設けられた端子とを接続するボンディングワイヤやバンプ等の接続部材と、を含みうる。

#### 【0160】

機器E Q Pは、光学装置O P T、制御装置C T R L、処理装置P R C S、表示装置D S

50

P L、記憶装置 M M R Y 及び機械装置 M C H N のうちの少なくともいずれかを更に備えうる。光学装置 O P T は、光電変換装置としての光電変換装置 A P R に対応するものであり、例えばレンズやシャッター、ミラーである。制御装置 C T R L は、光電変換装置 A P R を制御するものであり、例えば A S I C などの半導体デバイスである。処理装置 P R C S は、光電変換装置 A P R から出力された信号を処理するものであり、A F E (アナログフロントエンド)あるいはD F E (デジタルフロントエンド)を構成する。処理装置 P R C S は、C P U (中央処理装置)やA S I C (特定用途向け集積回路)などの半導体デバイスである。表示装置 D S P L は、光電変換装置 A P R で得られた情報(画像)を表示する、E L 表示装置や液晶表示装置である。記憶装置 M M R Y は、光電変換装置 A P R で得られた情報(画像)を記憶する、磁気デバイスや半導体デバイスである。記憶装置 M M R Y は、S R A M やD R A M などの揮発性メモリ、或いは、フラッシュメモリやハードディスクドライブなどの不揮発性メモリである。機械装置 M C H N は、モーターやエンジン等の可動部あるいは推進部を有する。機器 E Q P では、光電変換装置 A P R から出力された信号を表示装置 D S P L に表示したり、機器 E Q P が備える通信装置(不図示)によって外部に送信したりする。そのために、機器 E Q P は、光電変換装置 A P R が有する記憶回路部や演算回路部とは別に、記憶装置 M M R Y や処理装置 P R C S を更に備えることが好ましい。

10

#### 【0161】

図11に示した機器 E Q P は、撮影機能を有する情報端末(例えばスマートフォンやウエアラブル端末)やカメラ(例えばレンズ交換式カメラ、コンパクトカメラ、ビデオカメラ、監視カメラ)などの電子機器でありうる。カメラにおける機械装置 M C H N はズーミングや合焦、シャッター動作のために光学装置 O P T の部品を駆動することができる。また、機器 E Q P は、車両や船舶、飛行体などの輸送機器(移動体)でありうる。また、機器 E Q P は、内視鏡やC T スキャナーなどの医療機器でありうる。また、機器 E Q P は、内視鏡やC T スキャナーなどの医療機器でありうる。

20

#### 【0162】

輸送機器における機械装置 M C H N は移動装置として用いられる。輸送機器としての機器 E Q P は、光電変換装置 A P R を輸送するものや、撮影機能により運転(操縦)の補助及び/又は自動化を行うものに好適である。運転(操縦)の補助及び/又は自動化のための処理装置 P R C S は、光電変換装置 A P R で得られた情報に基づいて移動装置としての機械装置 M C H N を操作するための処理を行うことができる。

30

#### 【0163】

本実施形態による光電変換装置 A P R は、その設計者、製造者、販売者、購入者及び/又は使用者に、高い価値を提供することができる。そのため、光電変換装置 A P R を機器 E Q P に搭載すれば、機器 E Q P の価値も高めることができる。よって、機器 E Q P の製造、販売を行う上で、本実施形態の光電変換装置 A P R の機器 E Q P への搭載を決定することは、機器 E Q P の価値を高める上で有利である。

#### 【0164】

##### [変形実施形態]

本発明は、上記実施形態に限らず種々の変形が可能である。

40

例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【0165】

また、図2に示した画素12, 14の回路構成は一例であり、適宜変更が可能である。例えば、各々の画素12, 14が2つ以上の光電変換素子を備えていてもよい。また、画素12, 14は、必ずしも選択トランジスタM4を有する必要はない。

#### 【0166】

また、上記第1乃至第4実施形態では、画素14(OB画素)のA D変換結果を画素12(有効画素)のA D変換結果よりも先に確定しているが、1つの行に複数の画素14が存在する場合、必ずしも総ての画素14のA D変換結果を先に確定する必要はない。

50

**【0167】**

例えば、画素14のA/D変換を列回路32で行い、画素12の一部のA/D変換を列回路32で行い、画素12の他の一部のA/D変換を列回路34で行ってもよい。このような場合も、列回路34でA/D変換を行う画素12の数が列回路32でA/D変換を行う画素12の数よりも十分に多ければ、上記実施形態で説明した効果を得ることができる。

**【0168】**

また、比較器42, 44の一斉反転に起因するノイズは、隣り合う列への影響が特に大きい。したがって、画素14のA/D変換結果を、少なくとも画素14の近傍に位置する画素12のA/D変換結果よりも先に確定するようにすれば、上記実施形態で説明した効果を得ることができる。

10

**【0169】**

また、上記第1乃至第4実施形態では、差動增幅回路とソース接地增幅回路とにより構成される比較器42, 44を示したが、比較器42, 44の回路構成はこれに限定されるものではない。例えば、比較器42, 44は、必ずしもソース接地增幅回路を有する必要はなく、差動增幅回路の1段構成であってもよい。

**【0170】**

また、上記第5及び第6実施形態に示した撮像システムは、本発明の光電変換装置を適用しうる撮像システム例を示したものであり、本発明の光電変換装置を適用可能な撮像システムは図9及び図10に示した構成に限定されるものではない。

20

**【0171】**

なお、上記実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

**【符号の説明】****【0172】**

10 ... 画素アレイ部

12, 14 ... 画素

16 ... 制御線

18 ... 出力線

30

20 ... 垂直走査回路

22, 58, 58a, 58b ... 電流源

30 ... 読み出し回路

32, 34 ... 列回路

36 ... 参照信号生成回路

40a, 40b ... 電流源回路

42, 44 ... 比較器

46 ... カウンタ回路

48 ... メモリ部

50 ... 水平走査回路

40

52 ... 出力線

54, 54, 62a, 62b ... 信号線

60 ... デジタル信号処理回路

70 ... タイミングジェネレータ

100 ... 光電変換装置

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図9】

【図10】

【図11】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 米国特許出願公開第2015/0162925(US, A1)

特開2020-205517(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79