OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 354 748**

(51) Int. Cl.:

**G06F 13/40** (2006.01)

**G06F 13/362** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Número de solicitud europea: **06801345 .7**

(96) Fecha de presentación : **11.08.2006**

(97) Número de publicación de la solicitud: **1922629**

(97) Fecha de publicación de la solicitud: **21.05.2008**

(54) Título: **Comutador de dirección no bloqueante con colas superficiales por agente.**

(30) Prioridad: **11.08.2005 US 201581**

(73) Titular/es: **APPLE Inc.**

**1 Infinite Loop**

**Cupertino, California 95014, US**

(45) Fecha de publicación de la mención BOPI:

**17.03.2011**

(72) Inventor/es: **Subramanian, Sridhar P.;**

**Keller, James B.;**

**Yiu, George Kong;**

**Wadhawan, Ruchi y**

**Gunna, Ramesh**

(45) Fecha de la publicación del folleto de la patente:

**17.03.2011**

(74) Agente: **Fàbrega Sabaté, Xavier**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

**DESCRIPCIÓN****ANTECEDENTES****Campo de la invención**

5 Esta invención se relaciona con el campo de los circuitos integrados y, más concretamente, con mecanismos de arbitraje para la interconexión dentro de y/o entre circuitos integrados.

**Descripción de los Antecedentes de la Técnica**

10 Los circuitos integrados en un sistema, o varios circuitos dentro de un circuito integrado, tienen por lo general una necesidad de comunicarse entre sí. En muchos casos, los comunicadores en el sistema/circuito integrado pueden comunicarse a través de diversas direcciones en un mapa de memoria. Es decir, se asignan direcciones a diversos comunicadores dentro del mapa de memoria, y se utilizan lecturas/escrituras a las direcciones para comunicarse. Por lo general, tales comunicadores utilizan transacciones de lectura/escritura transmitidas por una interconexión entre los comunicadores. Por ejemplo, es común tener un bus de direcciones por el cual la dirección, la orden, y otra información de transacción se transmite para iniciar una transacción. Además, un bus de datos puede utilizarse para transmitir los datos correspondientes a la transacción, de haberla. Si se implementa coherencia de memoria cache para las transacciones, puede proporcionarse una interfaz de respuesta para mantener los estados de coherencia de acuerdo con el esquema de coherencia implementado por los comunicadores.

20 En la medida en que la interconexión, o una parte de la misma, se comparte entre los comunicadores, se necesita algún mecanismo para el arbitraje entre los comunicadores para el uso de la interconexión. En el pasado, se han utilizado mecanismos de arbitraje centralizado y distribuido. En un mecanismo de arbitraje centralizado, todos los comunicadores transmiten una señal de solicitud a un árbitro central, que determina a qué comunicador se le concederá el uso de la interconexión (el "ganador del arbitraje"). El árbitro central devuelve una señal de concesión al comunicador concedido, y a continuación el comunicador concedido acciona su transacción en la interconexión. En un esquema de arbitraje distribuido, cada comunicador implementa un árbitro local (o se incluye cerca un árbitro local). Cada comunicador afirma su señal de solicitud a todos los árbitros locales. Los árbitros locales están diseñados para determinar de manera independiente el mismo ganador del arbitraje. El árbitro local del comunicador concedido informa al comunicador concedido, que acciona su transacción en la interconexión.

30 El mecanismo de arbitraje centralizado es por lo general más fácil de implementar que el mecanismo de arbitraje distribuido. Sin embargo, el mecanismo de arbitraje centralizado también es por lo general un mecanismo de latencia superior. El mecanismo de arbitraje centralizado incluye una transmisión potencialmente de larga distancia de una señal de solicitud, seguido de una transmisión igualmente de larga distancia de una señal de concesión, seguido del comunicador concedido accionando su transacción. Por otra parte, el esquema de arbitraje distribuido más complejo sólo puede implicar una transmisión de larga distancia (de una señal de solicitud a cada uno de los árbitros locales). Las complejidades en el mecanismo de arbitraje distribuido incluyen por lo general un "aparcamiento" más complejo de la concesión en un comunicador concreto, complejidades en el control del flujo de los comunicadores, y asignación de búferes en comunicadores de destino basado en por fuente-comunicador.

40 Una versión de la especificación base PCI Express se presenta en "PCI express base specification", Rev. 1.0, 29 de abril de 2002, páginas 1-416.

45 EP-A-1.308.862 divulga un diseño de un circuito digital síncrono que comprende una serie de dispositivos de almacenamiento temporizado y una serie de elementos lógicos combinatorios que definen unas rutas combinatorias entre por lo menos algunos de los dispositivos de almacenamiento temporizado. Cada ruta combinatoria desde una salida de un dispositivo de almacenamiento temporizado hasta una entrada de otro tiene un valor de retardo mínimo (Dmin) y un valor de retardo máximo (Dmax). El retardo real de la ruta adopta un valor entre los valores de retardo mínimo y máximo. Un procedimiento comprende las etapas de identificar la ruta con la mayor diferencia entre el valor de retardo máximo (Dmax) y el valor de retardo mínimo (Dmin), y reducir la diferencia aumentando el valor de retardo mínimo para la ruta con la mayor diferencia.

**RESUMEN DE LA INVENCIÓN**

50 La invención se define en las reivindicaciones.

En una forma de realización, se configura un conmutador para ser acoplado a una interconexión. El conmutador comprende una pluralidad de ubicaciones de almacenamiento y un circuito de control de árbitro acoplado a la pluralidad de ubicaciones de almacenamiento. La pluralidad de ubicaciones de almacenamiento se configura para almacenar una pluralidad de solicitudes transmitidas por una pluralidad de agentes. El circuito de control de árbitro se configura para arbitrar entre la pluralidad de solicitudes almacenadas en la pluralidad de ubicaciones de almacenamiento. Una solicitud seleccionada es la ganadora del arbitraje, y el conmutador se configura para transmitir la solicitud seleccionada de una de la pluralidad de

ubicaciones de almacenamiento en la interconexión. En otra forma de realización, un sistema comprende una pluralidad de agentes, una interconexión, y el conmutador acoplado a la pluralidad de agentes y la interconexión.

En todavía otra forma de realización, un procedimiento comprende poner en cola las solicitudes de una pluralidad de agentes en una pluralidad de ubicaciones de almacenamiento; arbitrar entre las solicitudes en la pluralidad de ubicaciones de almacenamiento para seleccionar una solicitud de la pluralidad de solicitudes; y transmitir la solicitud seleccionada en una interconexión.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

Se describen unas formas de realización de ejemplo de la invención con respecto a los dibujos adjuntos..

La Fig. 1 es un diagrama de bloques de una forma de realización de un circuito integrado.

La Fig. 2 es un diagrama de bloques de una forma de realización de un árbitro/conmutador de dirección mostrado en la Fig. 1.

La Fig. 3 es un diagrama de flujo que ilustra el funcionamiento de una forma de realización de una unidad de control de árbitro que se muestra en la Fig. 2 para arbitrar entre solicitudes.

La Fig. 4 es una tabla que ilustra las reglas de ordenamiento para una forma de realización.

La Fig. 5 es un diagrama de flujo de alto nivel de un procedimiento de comunicación de solicitudes en una interconexión de dirección.

#### **DESCRIPCIÓN DETALLADA**

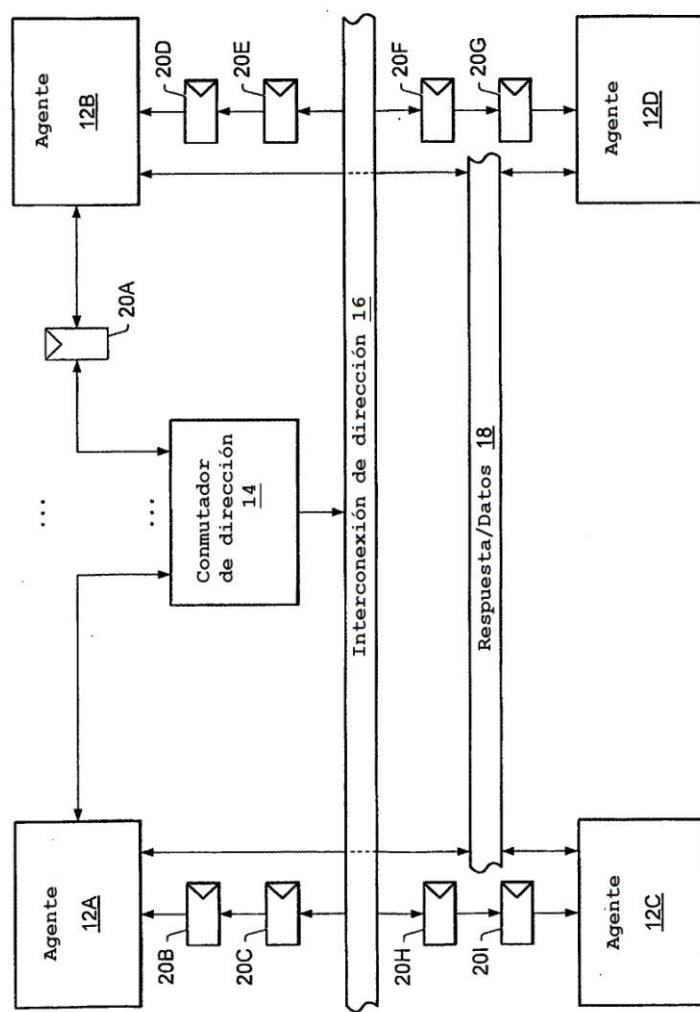

A continuación volviendo a la Fig. 1, se muestra un diagrama de bloques de una forma de realización de un sistema 10. En la forma de realización ilustrada, el sistema 10 incluye una pluralidad de agentes como los agentes 12A-12D. El sistema también incluye un conmutador de dirección 14, una interconexión de dirección 16, y una interconexión de respuesta/datos 18. Los agentes 12A-12B se acoplan al conmutador de dirección 14 (donde el agente 12B se acopla a través de un flop 20A en la forma de realización ilustrada). El conmutador de dirección 14 se acopla adicionalmente a la interconexión de dirección 16, que se acopla a los agentes 12A-12D (a través de unos flops 20B-20I en la forma de realización ilustrada). Visto de otra manera, los flops 20B-20I pueden ser parte de la interconexión de dirección 16. Los agentes 12A-12D también se acoplan a la interconexión de respuesta/datos 18. En una forma de realización, el sistema 10 puede integrarse en un chip de circuito integrado único. En otras formas de realización, pueden implementarse diversos componentes del sistema 10 en circuitos integrados diferentes. Puede utilizarse cualquier nivel de integración en diversas formas de realización.

Los agentes 12A-12B se configuran para transmitir las solicitudes que se van a transmitir en la interconexión de dirección 16 para el conmutador de dirección 14. Cada solicitud puede incluir la dirección de la transacción y la orden (que identifica la transacción a llevar a cabo). Pueden soportarse diversas órdenes, como órdenes de escritura y lectura coherentes, órdenes de escritura y lectura no coherentes, órdenes de propiedad coherentes, órdenes de sonda, órdenes de sincronización, órdenes de gestión de memoria cache, etc. Las solicitudes también pueden incluir otra información en diversas formas de realización. Por ejemplo, en una forma de realización descrita con más detalle más adelante, las solicitudes pueden incluir un nivel de prioridad de la solicitud (para el arbitraje) y una indicación de si también el dato para esta solicitud va a copiarse o no a la memoria cache de nivel 2.

Los agentes 12A-12B pueden referirse a un agentes de origen, puesto que pueden iniciar las transacciones en el sistema 10 transmitiendo una solicitud para la interconexión de dirección 16. Agentes de origen de ejemplo pueden incluir procesadores, memorias cache de respuesta externas (cuya fuente escribe transacciones para escribir bloques de memoria cache desalojados que se han modificado a la memoria) y puentes de entrada/salida (I/O) (cuya fuente tramita en nombre de los dispositivos periféricos a los que se acoplan). Como se ilustra mediante las elipses de la Fig. 1, diversas formas de realización pueden incluir más de dos agentes de origen (o agentes de origen/destino, descritos más adelante). Otros agentes pueden no originar transacciones, pero pueden ser el destino de una transacción (es decir, el agente que recibe la transacción y es responsable de los datos de la transacción). Tales agentes se denominan agentes de destino. Para leer las transacciones, el agente de destino suministra los datos a menos que otro agente tenga una copia en memoria cache más reciente (modificada) de los datos. Para las transacciones de escritura, el agente de destino recoge los datos de escritura suministrados por el agente de origen. Agentes de destino pueden incluir, por ejemplo, controladores de memoria y puentes de I/O. Algunos agentes pueden ser un agente de origen para algunas transacciones y un agente de destino para otras transacciones. Agentes de origen/destino de ejemplo pueden incluir el puente de I/O o la memoria cache externa mencionada anteriormente. Generalmente, un agente puede comprender cualquier circuito que se configure para comunicarse a través de transacciones en la interconexión de dirección 16 y la interconexión de respuesta/datos 18.

5 Cada agente de origen 12A-12B (o agente de origen/destino, aunque se utilizará agente de origen por razones de brevedad en esta descripción) puede utilizar una señal de solicitud para indicar que el agente de origen 12A-12B está transmitiendo una solicitud. El conmutador de dirección 14 también puede afirmar una señal de concesión a un agente de origen dado 12A-12B para indicar que se ha concedido una solicitud transmitida por ese agente de origen 12A-12B a la interconexión de dirección 16.

10 El conmutador de dirección 14 puede incluir una pluralidad de ubicaciones de almacenamiento configuradas para almacenar las solicitudes transmitidas por los agentes de origen hasta que las solicitudes se concedan a la interconexión de dirección 16. En una forma de realización, las ubicaciones de almacenamiento pueden comprender una pluralidad de colas. Cada cola puede corresponderse con un agente de origen concreto, y puede dedicarse a almacenar las solicitudes transmitidas por ese agente de origen. Es decir, puede haber una correspondencia uno a uno entre colas y agentes de origen. La cola para un agente de origen dado puede almacenar una pluralidad de solicitudes transmitidas al conmutador de dirección 14 por el agente de origen dado. Cada agente de origen puede conocer el número de entradas de cola en la cola correspondiente a dicho agente de origen, y no puede transmitir más solicitudes que hay 15 entradas de cola.

20 El conmutador de dirección 14 también puede configurarse para arbitrar entre las solicitudes en las colas para seleccionar una solicitud para la transmisión en la interconexión de dirección 16. Puede emplearse cualquier esquema de arbitraje. Por ejemplo, en algunas formas de realización, cada solicitud puede tener un nivel de prioridad asignado a él. El sistema de arbitraje puede ser un esquema de prioridad estricto (que selecciona la solicitud de mayor prioridad) con mecanismos de prevención de inanición para evitar la inanición de solicitudes de prioridad más baja. El conmutador de dirección 14 puede accionar la solicitud seleccionada en la interconexión de dirección 16.

25 De esta manera, el conmutador de dirección 14 puede emplear un arbitraje centralizado para la interconexión de dirección 16. Sin embargo, dado que las solicitudes se transmiten al conmutador de dirección 14 y son accionadas a la interconexión de dirección 16 por el conmutador de dirección 14, puede reducirse la latencia asociada con la devolución de una concesión al agente de origen seleccionado para ganar el arbitraje (y el agente de origen que acciona la interconexión de dirección 16 en respuesta a la concesión), en algunas formas de realización. El conmutador de dirección 14 puede devolver una concesión al agente de origen en paralelo con accionar la solicitud seleccionada a la dirección de conducción de interconexión 16. Además, en algunas formas de realización, el circuito de arbitraje en el conmutador de dirección 14 puede tener más información acerca de las solicitudes ya que las propias solicitudes están en cola en el conmutador de dirección 14 (p. ej. en comparación con una estructura de solicitud/concesión implementada por lo general en un árbitro centralizado convencional).

35 Cuando un agente de origen recibe una concesión del conmutador de dirección 14, el agente de origen es informado de que hay una entrada de cola disponible para almacenar otra solicitud. En una forma de realización, las solicitudes de un agente de origen dado pueden concederse en el orden transmitido. De esta manera, el agente de origen que recibe una concesión puede asociar la concesión con la solicitud correspondiente. En otras formas de realización, el conmutador de dirección 14 puede configurarse para reordenar las solicitudes en algunos casos (transmitiendo una solicitud recibida más tarde de un agente de origen por delante de, o antes de, una solicitud recibida más temprano desde el mismo agente de origen). En tales formas de realización, los agentes de origen pueden acoplarse a la interconexión de dirección 16, y 40 pueden recibir las solicitudes transmitidas en la misma para determinar qué solicitud fue concedida. Por ejemplo, en algunas formas de realización, el agente de origen puede marcar cada solicitud con una marca de origen y el agente de origen puede recibir la marca de origen de la interconexión de dirección 16 para 45 determinar qué solicitud fue concedida.

50 La interconexión de dirección 16 puede comprender cualquier medio de comunicación, en diversas formas de realización. Por ejemplo, la interconexión de dirección 16 puede comprender una interfaz de paquetes, en la que una solicitud se transmite como un paquete sobre uno o más ciclos de reloj en la interconexión de dirección 16. En concreto, en una forma de realización, el paquete de dirección puede transmitirse en un ciclo de reloj en la interconexión de dirección 16. Tales formas de realización pueden aislar el conmutador de dirección 14, un poco, del protocolo de la fase de dirección de una transacción. Otras formas de realización pueden implementar la dirección de interconexión 16 como un bus, con una dirección transferida junto con diversas señales de control para indicar la orden y otra información de control transferida durante la fase de dirección.

55 Las solicitudes se emiten a los agentes 12A-12D en la interconexión de dirección 16. En algunas formas de realización, el tiempo de vuelo en la interconexión de dirección 16 hasta el agente más alejado 12A-12D (en términos de distancia física) puede exceder un ciclo de reloj del reloj asociado con la interconexión de dirección 16. Pueden utilizarse los flops 20B-20I para capturar la solicitud y continuar su propagación a los agentes 12A-12D. De esta manera, el número de flops 20B-20I incluidos entre el conmutador de dirección 14 y un agente 12A-12B dado puede basarse en el tiempo de vuelo para el agente más lejano (en números de ciclos de reloj de la señal de reloj utilizada para la interconexión de dirección 16). En la forma de realización ilustrada, el tiempo de vuelo supera dos ciclos de reloj y por tanto se utilizan dos

flops. Otras formas de realización pueden incluir cero flops (si el tiempo de vuelo es inferior a un ciclo de reloj), un flop (si el tiempo de vuelo supera un ciclo de reloj pero es inferior a dos ciclos de reloj), o más de dos flops (dependiendo del tiempo de vuelo). Para asegurar que una solicitud dada es recibida lógicamente por cada agente 12A-12D en el mismo ciclo de reloj, puede proporcionarse un número igual de flops 20B-20I entre el conmutador de dirección 14 y cada agente 12A-12D incluso aunque algunos agentes puedan estar físicamente más cerca del conmutador de dirección 14 y la solicitud pueda ser físicamente capaz de llegar al agente más cercano en un tiempo de vuelo menor. Los flops 20B-20I a los agentes más lejanos pueden distribuirse físicamente a lo largo de la distancia entre el conmutador de dirección 14 y los agentes más lejanos. La Fig. 1 no intenta ilustrar la distribución física de los flops 20B-20I, por razones de simplicidad en el dibujo.

Dado que cada agente 12A-12D recibe lógicamente las solicitudes transmitidas en la interconexión de dirección 16 en el mismo ciclo de reloj, la interconexión de dirección 16 puede, en algunas formas de realización, ser el punto de coherencia en el espacio para las transacciones coherentes. Es decir, el orden de las solicitudes transmitidas con éxito en la interconexión de dirección 16 puede definir el orden de las transacciones para fines de coherencia.

De manera similar, en algunas formas de realización, un tiempo de vuelo de una solicitud desde un agente de origen 12A-12B al conmutador de dirección 14 puede superar un ciclo de reloj. En algunas formas de realización, puede colocarse físicamente el conmutador de dirección 14 lo más cerca de los agentes de origen que se espera que tengan el mayor ancho de banda de solicitudes (p. ej., los agentes de procesador pueden por lo general tener mayor ancho de banda de solicitud que los agentes de memoria cache son agentes I/O). En la forma de realización de la Fig. 1, el tiempo de vuelo de las solicitudes desde el agente de origen 12B puede superar un ciclo de reloj, y por lo tanto el flop 20A puede utilizarse para capturar la solicitud y continuar su propagación al conmutador de dirección 14. De manera similar, la señal de concesión devuelta por el conmutador de dirección 14 puede ser capturada por el flop 20A y propagada en el siguiente ciclo de reloj.

Ya que, en la presente forma de realización, la interconexión de dirección 16 es el punto de coherencia para las transacciones coherentes (y también puede definir el orden de las solicitudes en su conjunto), no hay ningún ordenamiento entre las solicitudes transmitidas al conmutador de dirección 14 desde diferentes agentes. Por consiguiente, si se utiliza un flop como el flop 20A durante un tiempo de vuelo desde un agente de origen, no se necesita insertar flops para otros agentes cuyo tiempo de vuelo para las solicitudes sea menor que un ciclo de reloj.

Como se ha mencionado anteriormente, los agentes de origen pueden recibir solicitudes en la interconexión de dirección 16, en algunas formas de realización, para determinar qué solicitud de varias solicitudes pendientes en el conmutador de dirección 14 desde un agente dado se concedió realmente a la interconexión de dirección 16. Además, en algunas formas de realización, los agentes de origen que también pueden almacenar en memoria cache datos (y por tanto pueden participar en una transacción coherente) también pueden examinar las solicitudes de otro agente de origen en la interconexión de dirección 16 para fines de coherencia. Los agentes de destino, como los agentes 12C-12D, se acoplan a la interconexión de dirección 16 para recibir las solicitudes para las que son el destino.

En una forma de realización, el conmutador de dirección 14 también puede configurarse para gestionar el control de flujo a diversos agentes de destino 12C-12D. Por ejemplo, el conmutador de dirección 14 puede configurarse para determinar a qué agente de destino se dirige cada solicitud (p. ej. a través de la decodificación poco detallada de la dirección de solicitud y el mapeo de la dirección a un agente de destino basado en la decodificación). El conmutador de dirección 14 puede conocer la cantidad de solicitudes que pueden ponerse en cola en un agente de destino (después de la recepción de las solicitudes desde la interconexión de dirección 16) y puede asegurarse de que las colas de entrada del agente de destino no se desbordan con las solicitudes. Si una solicitud dada es destinada a un agente de destino dado cuya cola de entrada está llena, el conmutador de dirección 14 puede asegurar que la solicitud dada no se selecciona como la ganadora del arbitraje hasta que haya una entrada a la cola de entrada disponible en el agente de destino dado. El conmutador de dirección 14 puede ser de no bloqueo de otras solicitudes en una situación de este tipo. Es decir, el conmutador de dirección 14 todavía puede ser capaz de seleccionar otra solicitud destinada a otro agente de destino si una solicitud anterior o una solicitud de prioridad más alta no son elegibles para ganar el arbitraje debido a que el agente de destino no puede recibir la solicitud. En algunas formas de realización, el conmutador de dirección 14 puede también intentar implementar imparcialidad u optimizar el acceso a un agente de destino entre los agentes de origen.

Los agentes 12A-12D también pueden acoplarse a una interconexión de respuesta/datos 18 para comunicar la fase de respuesta y la fase de datos de las transacciones iniciadas a través de las solicitudes en la interconexión de dirección 16. Algunas transacciones pueden no incluir una fase de datos, en diversas formas de realización. La fase de respuesta puede incluir, por ejemplo, respuestas de los agentes de almacenamiento en memoria cache para transacciones coherentes. Las respuestas pueden proporcionar información que indica qué estado de coherencia debería establecerse en el receptor de datos correspondiente a una transacción. La fase de datos de la transacción implica la transferencia de datos al

agente de origen (para una lectura) o el agente de destino (para una escritura). La interconexión de respuesta/datos 18 puede comprender un medio de comunicación, en diversas formas de realización.

Aunque las ubicaciones de almacenamiento en el conmutador de dirección 14 se describen como colas por agente en algunas formas de realización anteriores, otras formas de realización pueden implementar las ubicaciones de almacenamiento de otras maneras. Por ejemplo, las ubicaciones de almacenamiento pueden ser una única cola en la que los agentes de origen almacenan las solicitudes. Las entradas de cola pueden ser asignadas con flexibilidad a los agentes de origen por el conmutador de dirección 14, y puede haber una señalización adicional para indicar el número de entradas de cola disponibles para cada agente de origen (p. ej. señalización del conmutador de dirección 14 a cada agente indicando el número de entradas de cola, o que por lo menos hay una entrada de cola adicional disponible para el agente, etc.). Los agentes pueden agruparse y pueden compartir las colas, o pueden asignarse colas en base al destino de cada solicitud.

Hay que reseñar que, aunque en la forma de realización de la Fig. 1 se ilustran los flops 20A-20I, generalmente puede utilizarse cualquier dispositivo de almacenamiento temporizado como los dispositivos 20A-20I. Por ejemplo, pueden utilizarse registros, circuitos interruptores, etc. Un dispositivo de almacenamiento temporizado puede comprender cualquier dispositivo de almacenamiento que se configura para capturar un valor para el almacenamiento sensible a una señal de reloj. En la presente forma de realización, la entrada de la señal de reloj para los flops 20A-20I puede ser el reloj utilizado para la interconexión de dirección 16. Algunos agentes pueden operar internamente en múltiplos del reloj. También pueden implementarse otros flops descritos en la presente memoria con cualquier dispositivo de almacenamiento temporizado. Generalmente, cada flop 20A-20I puede tener un ancho de bits igual al ancho de su entrada. Por ejemplo, el flop 20A puede ser el ancho de la solicitud/interfaz de concesión al conmutador de dirección 14 y el ancho de los flops 20B-20I puede ser el ancho de la interconexión de dirección 16.

Aunque se utiliza anteriormente un esquema de arbitraje de prioridad estricta como un ejemplo, otras formas de realización pueden implementar otros esquemas de arbitraje. Por ejemplo, otros esquemas de arbitraje pueden incluir round-robin, round-robin de prioridad ponderada, combinaciones de round-robin y esquemas de prioridad, etc.

Aunque el análisis anterior se refiere a un conmutador de dirección que recibe solicitudes para la interconexión de dirección 16 y arbitra entre las solicitudes para determinar que una ganadora del arbitraje se transmita en la interconexión de dirección 16, otras formas de realización pueden implementar un conmutador similar para la interconexión de datos. Las solicitudes al conmutador de datos pueden recibirse desde fuentes de datos. Las solicitudes pueden incluir los datos para una transacción, junto con una marca que identifique la solicitud de dirección a la que corresponden los datos. Las solicitudes pueden incluir una prioridad, que puede ser la misma prioridad que la solicitud de dirección o una prioridad diferente, en diversas formas de realización. El conmutador de datos puede arbitrar entre las solicitudes de datos en cola para seleccionar una ganadora del arbitraje a llevar en la interconexión de datos.

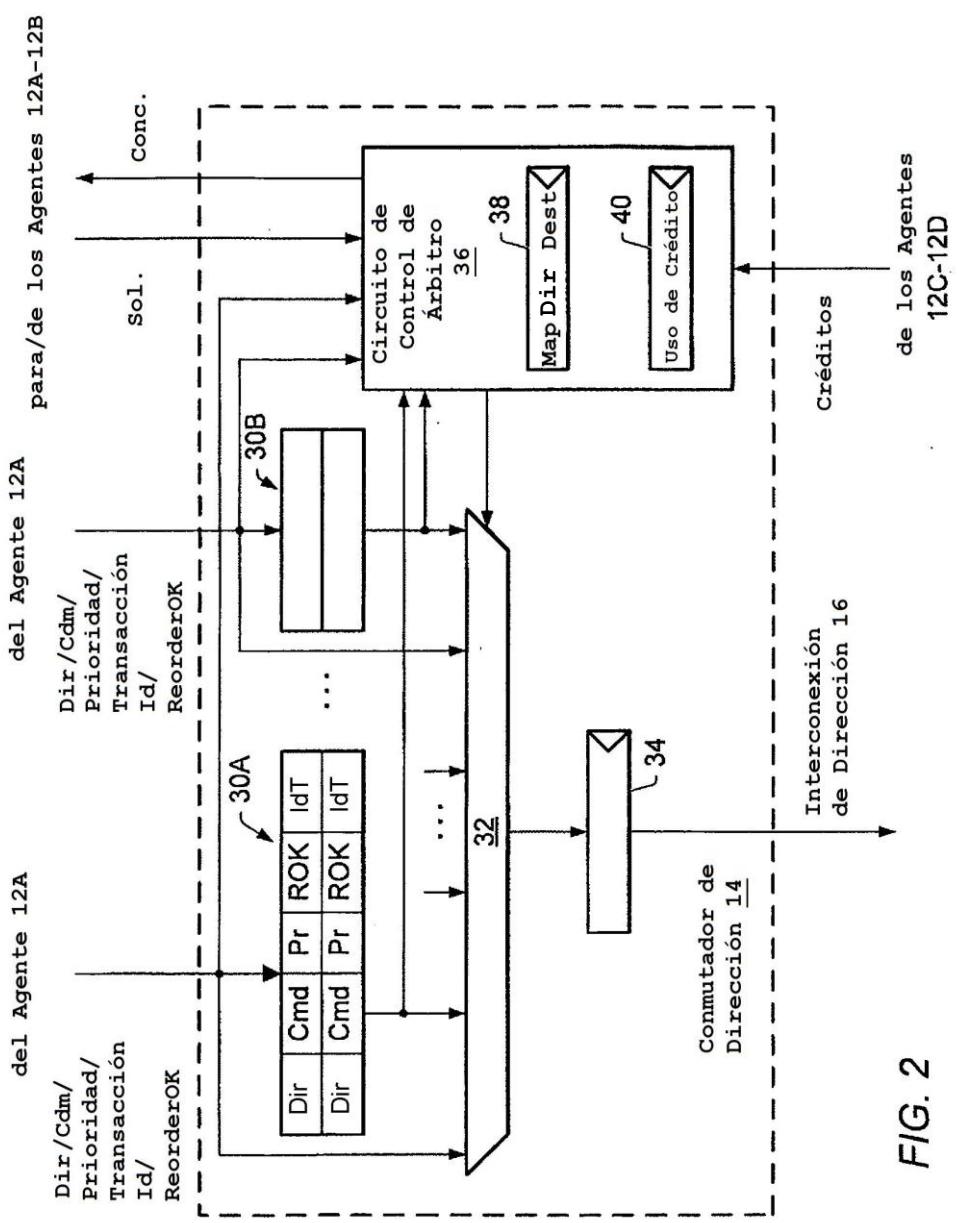

A continuación, volviendo a la Fig. 2, se muestra un diagrama de bloques de una forma de realización del conmutador de dirección 14. En la forma de realización ilustrada, el conmutador de dirección 14 incluye colas como las colas 30A y 30B correspondientes a los agentes 12A y 12B, respectivamente. El conmutador de dirección 14 incluye adicionalmente un multiplexor (mux) 32, un flop de salida 34, y un circuito de control de árbito 36. Las colas 30A-30B se acoplan para recibir una solicitud de sus respectivos agentes 12A-12B. Además, el circuito de control de árbito 36 y el mux 32 se acoplan para recibir las solicitudes en la forma de realización ilustrada. Las colas 30A-30B se acoplan adicionalmente al circuito de control de árbito 36 y el mux 32. En las formas de realización que incluyen agentes de origen adicionales, el mux 32 y el circuito de control de árbito 36 pueden acoplarse adicionalmente para recibir las solicitudes y las salidas de las colas correspondientes en el conmutador de dirección 14. El circuito de control de árbito 36 se acopla para recibir las señales de la solicitud desde los agentes 12A-12B, y para proporcionar señales de concesión a los agentes 12A-12B. El circuito de control de árbito 36 se acopla adicionalmente para proporcionar un control de selección al mux 32. La salida del mux 32 se acopla al flop de salida 34, que se acopla adicionalmente a la interconexión de dirección 16. El circuito de control de árbito 36 se acopla adicionalmente para recibir indicaciones de crédito de los agentes 12C-12D (y otros agentes de destino o agentes de origen/destino, en algunas formas de realización).

En la forma de realización ilustrada, cada solicitud puede incluir una dirección (Dir), una orden (Cmd), una prioridad (Pr), una transacción ID (TId), y un bit ReorderOK (ROK). Las colas 30A-30B pueden configurarse para almacenar la solicitud. Es decir, cada entrada de cola puede incluir almacenamiento suficiente para almacenar la solicitud. En la forma de realización ilustrada, cada cola 30A-30B incluye dos entradas. En otras formas de realización, pueden incluirse más entradas en cada cola 30A-30B. La dirección es la dirección en el mapa de memoria que se ve afectada por la solicitud, e identifica al agente de destino. La orden identifica la transacción que se está iniciando. La prioridad indica el nivel de prioridad de la solicitud. En una forma de realización, se utilizan tres niveles de prioridad. El nivel de prioridad más alto puede utilizarse cuando la latencia de la solicitud es crítica. Por ejemplo, en una forma de realización, algunos puentes de I/O que se acoplan a interfaces de paquetes como interfaces Ethernet pueden utilizar el nivel de

5 prioridad más alto para leer los descriptores o datos por paquetes cuando los búferes en el puente o el circuito que acciona las interfaces de paquetes van lentos. El nivel de prioridad medio puede ser utilizado para lecturas del procesador y lecturas del descriptor de acceso directo a memoria (DMA) por puentes de I/O. La prioridad media también puede utilizarse para escrituras si los búferes de escritura del agente de origen están casi llenos. El nivel de prioridad baja puede utilizarse para todas las demás solicitudes (p. ej. escrituras del procesador, escrituras y lecturas de ancho de banda alto como lecturas y escrituras DMA, etc.). Otras formas de realización pueden utilizar más o menos niveles de prioridad. El bit reorderOK puede utilizarse para indicar si la solicitud puede reordenarse por delante de una solicitud anterior desde el mismo agente, si la solicitud anterior está todavía en la cola del agente 30A-30B (es decir, la solicitud anterior todavía no ha sido concedida a la interconexión de dirección 16). El agente de origen puede generar el bit reorderOK de acuerdo con un conjunto de reglas de ordenamiento implementadas por el agente. Un ejemplo se ilustra en la Fig. 4 y se analiza con más detalle más adelante.

10 15 Los agentes 12A-12B pueden afirmar una señal de solicitud correspondiente al transmitir una solicitud al comutador de dirección 14. Es decir, la señal de solicitud afirmada puede servir como un bit válido para la solicitud, para escribir la cola 30A-30B correspondiente al agente 12A-12B y para indicar la solicitud al circuito de control de árbito 36. El circuito de control de árbito 36 también puede generar una señal de concesión (una para cada agente de origen 12A-12B). El circuito de control de árbito 36 puede afirmar la señal de concesión a un agente de origen dado 12A-12B para indicar que una solicitud de ese agente de origen 12A-12B ha sido concedida y será accionada en la interconexión de dirección 16. La señal de concesión afirmada puede indicar al agente 12A-12B que una entrada de cola en la cola del agente 30A-30B se está liberando para aceptar otra solicitud.

20 25 Cada agente 12A-12B puede configurarse para transmitir hasta un número de solicitudes igual al número de entradas de cola en su cola 30A-30B (dos, en la forma de realización ilustrada). En una forma de realización, cada agente 12A-12B puede limitar el número de solicitudes pendientes en la cola 30A-30B al número de entradas. Es decir, el agente puede transmitir dos solicitudes, y a continuación inhibir la transmisión de las solicitudes adicionales hasta que una señal de concesión afirmada indique que una entrada de cola está siendo liberada. En otra forma de realización, cada agente 12A-12B puede llenar su cola 30A-30B y transmitir una solicitud más, que el agente 12A-12B puede seguir transmitiendo hasta que se conceda una solicitud anterior y por tanto la solicitud afirmada se escribe a una entrada de cola.

30 35 El circuito de control de árbito 36 puede arbitrar entre las solicitudes en las colas 30A-30B y seleccionar una solicitud para ser transmitida en la interconexión de dirección 16. El circuito de control de árbito 36 puede generar el control de selección para el mux 32 para seleccionar la solicitud y proporcionar la solicitud seleccionada al flop de salida 34. El flop de salida 34 acciona la solicitud a la interconexión de dirección 16. El flop de salida 34 puede proporcionarse para asegurar que la solicitud se acciona a la interconexión de dirección 16 al comienzo del ciclo de reloj. En otras formas de realización, puede eliminarse el flop de salida 34 y la solicitud puede accionarse tras la selección a través del mux 32. La solicitud seleccionada también se elimina de su cola 30A-30B, y el circuito de control de árbito 36 puede afirmar la señal de concesión al agente de origen correspondiente 12A-12B.

40 45 50 55 El circuito de control de árbito 36 puede implementar cualquier esquema de arbitraje para seleccionar entre las solicitudes. Por ejemplo, como se ha mencionado anteriormente, el circuito de control de árbito 36 puede implementar una selección de prioridad estricta con prevención de inanición. En un esquema de este tipo, la solicitud de prioridad más alta normalmente se selecciona como la ganadora del arbitraje. Sin embargo, si numerosas solicitudes de prioridad más alta están causando que solicitudes de prioridad más baja permanezcan en las colas 30A-30B durante un período prolongado (es decir, las solicitudes de menor prioridad están "en inanición"), puede seleccionarse una solicitud de prioridad más baja. El mecanismo de prevención de inanición puede implementarse de una variedad de maneras. Por ejemplo, cada solicitud puede tener un temporizador asociado con él, o un sello de tiempo, lo que indica cuánto tiempo ha estado la solicitud en las colas 30A-30B. Si la solicitud ha estado en las colas 30A-30B más que un período de tiempo umbral (que puede ser fijo o programable), puede seleccionarse la solicitud. De hecho, la prioridad de la solicitud puede aumentarse debido a su antigüedad en las colas 30A-30B. En otro ejemplo, si un número definido de solicitudes de prioridad más alta se seleccionan de forma consecutiva (donde el número puede ser fijo o programable), puede seleccionarse automáticamente una solicitud de prioridad más baja. Si más de una solicitud tiene la máxima prioridad en las colas 30A-30B para un arbitraje dado, puede utilizarse cualquier mecanismo para seleccionar entre las solicitudes (p. ej. prioridad fija entre los agentes de origen, round-robin entre los agentes de origen, la solicitud más antigua puede seleccionarse, etc.). Otras formas de realización pueden implementar otros esquemas de arbitraje (p. ej. round-robin sin prioridad, round-robin ponderado en base a la prioridad, etc.).

60 Si una solicitud de alta prioridad está en una cola 30A-30B "detrás" de otra solicitud, esa solicitud de alta prioridad puede ser no elegible para el arbitraje si no se establece el bit ReorderOK para esa solicitud de alta prioridad para indicar que el reordenamiento de la solicitud por delante de una solicitud anterior es admisible. Es decir, el circuito de control de árbito 36 no puede seleccionar la solicitud de alta prioridad por delante de una solicitud anterior de prioridad más baja en la misma cola si el bit ReorderOK no indica que el reordenamiento es permisible. Si la reordenación por delante de una solicitud anterior es

admissible, como se indica mediante el bit ReorderOK, puede seleccionarse la solicitud de alta prioridad si la solicitud de prioridad más alta está detrás de una solicitud de prioridad más baja en la cola. Es decir, la solicitud de prioridad más baja puede haber sido transmitida por el agente al conmutador de dirección antes de transmitir la solicitud de prioridad alta.

En algunas formas de realización, el circuito de control de árbito 36 también puede implementar un control de flujo para cada agente de destino (p. ej. agentes 12C-12D, en la forma de realización de la Fig. 1). El circuito de control de árbito 36 puede determinar el agente de destino para cada solicitud (p. ej. utilizando la dirección en la forma de realización actual). El circuito de control de árbito 36 puede ser programable con un mapeo de direcciones a los agentes de destino. Por ejemplo, uno o más registros 38 pueden programarse para mapear el espacio de direcciones a los agentes de destino. En base al mapeo de direcciones, el circuito de control de dirección 36 puede llevar a cabo una decodificación poco detallada de determinados bits de dirección más significativos para determinar el agente de destino. La decodificación es poco detallada en la presente forma de realización porque se espera que los intervalos de direcciones contiguas relativamente grandes se programen para el mismo agente de destino. Otras formas de realización pueden utilizar una decodificación más detallada. Además, aunque la decodificación es programable en esta forma de realización, otras formas de realización pueden tener un mapa de direcciones fijas y el circuito de control de árbito 36 puede decodificar las direcciones de acuerdo con el mapa de direcciones fijas.

Cada agente de destino puede tener la capacidad de aceptar hasta un determinado número de transacciones (p. ej. de acuerdo con el número de búferes implementado en el agente de destino). En algunas formas de realización, las transacciones pueden agruparse por tipo de transacción y puede especificarse el número de cada grupo de transacciones para cada agente de destino. Por ejemplo, en una forma de realización, las transacciones pueden agruparse como lecturas coherentes, escrituras coherentes, órdenes no coherentes no remitidas, y órdenes no coherentes remitidas. Cada agente de destino puede implementar un determinado número de búferes para cada uno de los grupos anteriores de transacciones.

El circuito de control de árbito 36 puede configurarse para implementar un control de flujo a los agentes de destino, para garantizar que los búferes del agente de destino no se desborden. Por ejemplo, puede utilizarse un sistema basado en el crédito en el que cada buffer está representado por un crédito para el tipo de transacción correspondiente. El circuito de control de árbito 36 puede realizar un seguimiento de los créditos disponibles (p. ej. utilizando uno o más registros 40 en la Fig. 2). Si el circuito de control de árbito 36 selecciona una solicitud de un tipo dado y dirigido a un agente de destino dado, el circuito de control de árbito 36 puede reducir el conteo de créditos correspondientes en uno. Los agentes de destino también pueden comunicar la devolución de créditos cuando los búferes estén libres (mostrados como créditos en la Fig. 2). De esta manera, en cualquier instante en el tiempo dado, el circuito de control de árbito 36 puede conocer la disponibilidad de búfer en cada agente de destino para cada tipo de transacción. El circuito de control de árbito 36 puede evitar la selección de una solicitud si el crédito que podría ser consumido por esa solicitud no está disponible. Otra solicitud (incluso una solicitud de prioridad más baja) puede seleccionarse en su lugar si el crédito correspondiente para esta otra solicitud está disponible.

En algunas formas de realización, el circuito de control de árbito 36 puede intentar también garantizar imparcialidad de acceso por parte de los agentes de origen a un agente de destino dado. El circuito de control de árbito 36 puede hacer un seguimiento de la utilización global de créditos de diversos tipos para cada agente de destino, así como la utilización de créditos por cada agente de origen. Si la utilización global de créditos para un agente de destino es alta (lo que indica que el agente de destino está "ocupado" con las transacciones) y un agente de origen concreto se está comunicando a un ritmo elevado con ese agente de destino (indicado por su utilización de créditos para ese agente de destino), el circuito de control de árbito 36 puede limitar el uso de créditos por ese par agente de destino/agente de origen para permitir un mejor acceso al agente de destino por otros agentes de origen.

Como se ilustra en la forma de realización de la Fig. 2, el mux 32 y el circuito de control de árbito 36 se acoplan para recibir la solicitud que está siendo transmitida actualmente por un agente 12A-12B al conmutador de dirección 14. El circuito de control de árbito 36 puede configurarse para circunvalar las colas 30A-30B para una solicitud dada, y seleccionar la solicitud a través del mux 32, si las colas 30A-30B están vacías cuando se transmite la solicitud (y el crédito correspondiente para el agente de destino está disponible para el consumo). La latencia de pasar a través de la cola puede evitarse en tales casos. En otras formas de realización, la circunvalación puede ser proporcionada sólo para un agente de origen, o un subconjunto de agentes de origen (p. ej. los procesadores pueden tener la circunvalación y los demás agentes no). En todavía otras formas de realización, no puede implementarse la circunvalación y pueden eliminarse la conexión de las solicitudes entrantes para el mux 32 y el circuito de control de árbito 36.

Hay que reseñar que, aunque la presente forma de realización utiliza el bit ReorderOK para indicar si una solicitud dada puede reordenarse por delante de una solicitud transmitida anteriormente desde el mismo agente, otras formas de realización pueden utilizar otras indicaciones. Por ejemplo, si se implementan más de dos entradas de cola en una cola 30A-30B, puede haber un bit ReorderOK correspondiente a cada entrada en la cola. Cada bit ReorderOK puede indicar si la solicitud puede

reordenarse con respecto a la solicitud en la entrada de cola correspondiente. De manera alternativa, el circuito de control de árbitro 36 puede implementar el conjunto de reglas de ordenamiento que se aplican al agente para determinar si una solicitud dada puede reordenarse por delante de las solicitudes transmitidas anteriormente.

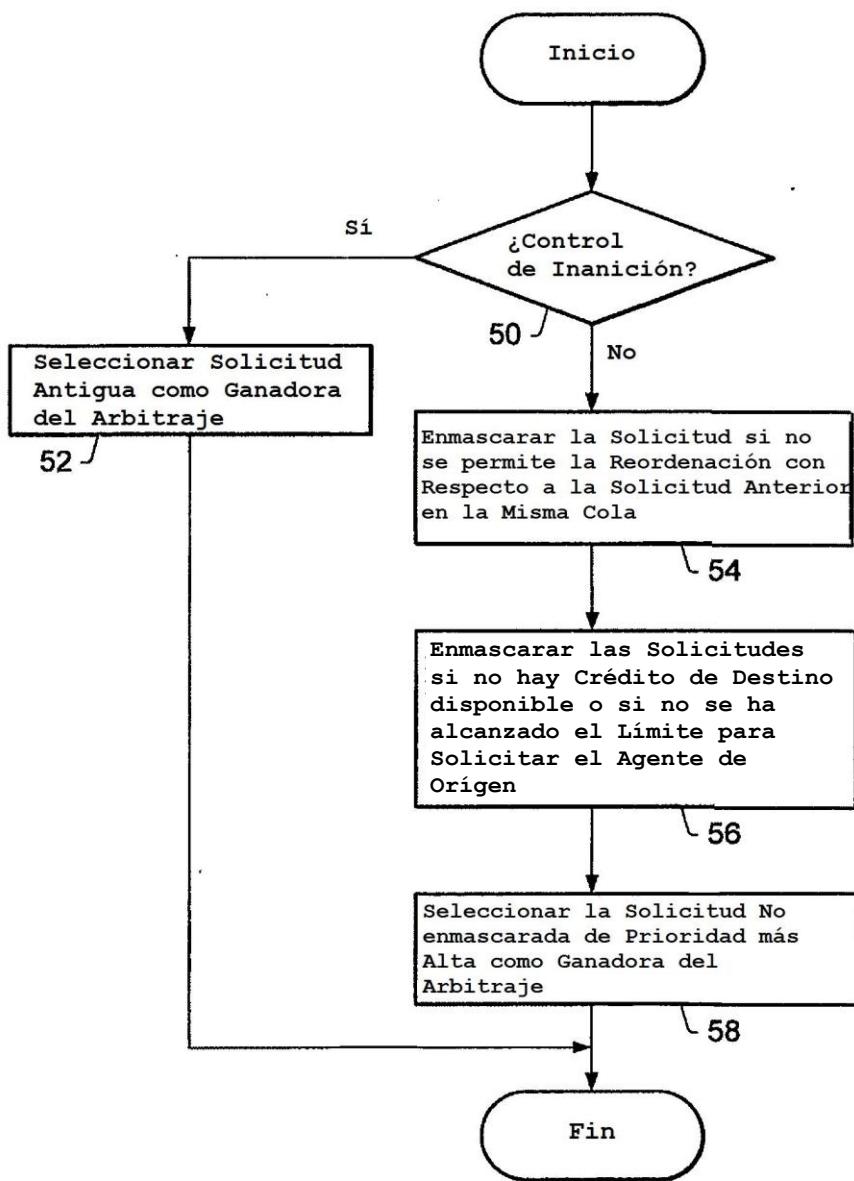

La Fig. 3 es un diagrama de flujo que ilustra el funcionamiento de una forma de realización del circuito de control de arbitraje 36. Aunque los bloques se muestran en un orden específico para facilitar la comprensión, puede utilizarse cualquier orden. Además, pueden implementarse diversos bloques en paralelo mediante circuitos de lógica combinatoria en el circuito de control de arbitraje 36. Otros bloques, combinaciones de bloques, o el diagrama de flujo en su conjunto pueden ser ejecutados mediante la técnica de "pipelining" durante ciclos de reloj múltiples, como se deseé.

El circuito de control de arbitraje 36 puede anular el arbitraje "normal" (p. ej., basado en la prioridad) si se está activando el control de inanición para el ciclo de arbitraje actual (bloque de decisión 50). Como se ha mencionado anteriormente, el control de inanición puede activarse si una solicitud de prioridad más baja dada ha estado en la cola durante un período prolongado. De manera alternativa, el control de inanición puede activarse si se seleccionan solicitudes de prioridad alta en un número de arbitrajes consecutivos. Si se ha activado el control de inanición (bloque de decisión 50, ramificación "sí"), el circuito de control de árbitro 36 puede seleccionar la solicitud antigua (o una solicitud de prioridad más baja) como la ganadora del arbitraje (bloque 52).

Si no se ha activado el control de inanición (bloque de decisión 50, ramificación "no"), el circuito de control de árbitro 36 puede enmascarar diversas solicitudes como no elegibles para el arbitraje, y puede arbitrar entre las solicitudes que no han sido enmascaradas. Por ejemplo, si una solicitud en la cola tiene su bit ReorderOK que indica que no está permitida la reordenación, y hay una solicitud anterior en la misma cola, la solicitud puede ser enmascarada para evitar que se seleccione antes que la solicitud anterior (p. ej. si esa solicitud tiene prioridad más alta que la solicitud anterior) (bloque 54). Además, si una solicitud se dirige a un agente de destino para el cual no hay disponible crédito del tipo adecuado para la solicitud, la solicitud puede ser enmascarada (bloque 56). Si el circuito de control de arbitraje 36 está limitando los créditos que pueden ser consumidos por el agente de origen correspondiente a una solicitud y se ha alcanzado el límite, la solicitud también puede ser enmascarada aunque pueda haber créditos disponibles para el consumo (bloque 56). El circuito de control de arbitraje 36 puede seleccionar la solicitud no enmascarada de prioridad más alta (bloque 58) como la ganadora del arbitraje.

El circuito de control de arbitraje 36 puede seleccionar la ganadora del arbitraje a través del mux 32 en la interconexión de dirección 16. Además, el circuito de control de arbitraje 36 puede afirmar la señal de concesión al agente de origen que dio origen a la solicitud seleccionada, y puede eliminar la solicitud seleccionada de la cola 30A-30B.

La Fig. 4 es un diagrama de bloques de una forma de realización de un conjunto de reglas de ordenamiento que pueden ser implementadas por un agente de origen, o el circuito de control de arbitraje 36, o ambos, en diversas formas de realización. Los tipos de transacción se muestran en la parte superior de una tabla y a la izquierda de la tabla. En la intersección de la fila y la columna está la regla sobre si se permite o no que una transacción del tipo en esa fila pueda reordenarse por delante de una transacción anterior del tipo en esa columna.

Por consiguiente, las solicitudes de escritura y lectura coherentes pueden reordenarse libremente siempre que no haya ninguna coincidencia de dirección. En este contexto, se ha detectado una coincidencia de dirección en el nivel de detalle para el que se mantiene la coherencia (p. ej. un bloque de memoria cache). Una solicitud de lectura coherente puede reordenarse por delante de una solicitud remitida no coherente y una finalización no coherente, pero una solicitud no remitida no coherente (fila lectura coherente y columnas remitidas no coherentes, no remitidas no coherentes, y finalización no coherente). En algunos casos, si una solicitud puede ser reordenada o no depende del caso concreto de una solicitud (las intersecciones que incluyen las respuestas a) y b)). El tipo de solicitud para a) y b) se define debajo de la tabla de la Fig. 5. S/N significa que la reordenación es admisible, pero no requiere que sea permitida. De esta manera, pueden reordenarse las solicitudes si la Fig. 4 indica sí o S/N.

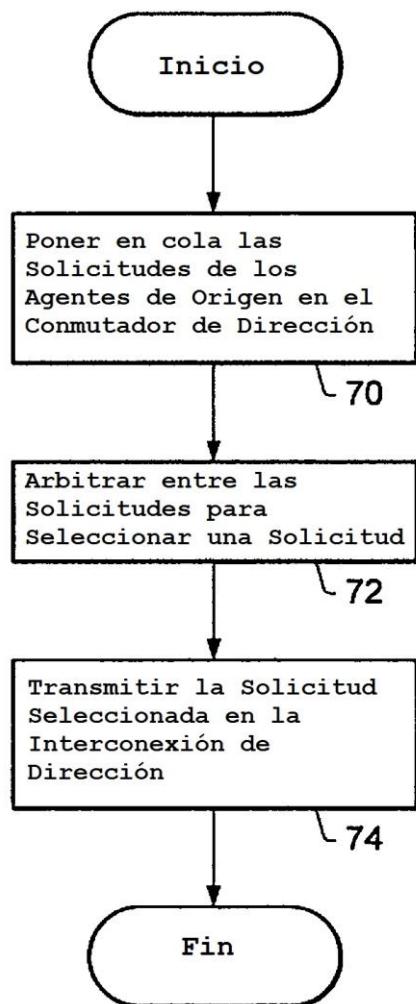

A continuación, volviendo a la Fig. 5, se muestra un diagrama de flujo de alto nivel de un procedimiento de comunicación de solicitudes en una interconexión de dirección. Las solicitudes de los agentes de origen están en cola en un comutador de dirección (bloque 70). El comutador de dirección arbitra entre las solicitudes en cola para seleccionar una solicitud (bloque 72). La solicitud seleccionada se transmite en la interconexión de dirección (bloque 74).

## REIVINDICACIONES

1. Un sistema (10) que comprende:

- una pluralidad de agentes (12A-12D);

- una interconexión (16); y

- 5 un conmutador (14) acoplado a la pluralidad de agentes y a la interconexión, en el que el conmutador comprende una pluralidad de ubicaciones de almacenamiento (30A-30B), y en el que la pluralidad de ubicaciones de almacenamiento se configuran para almacenar una pluralidad de solicitudes transmitidas por la pluralidad de agentes al conmutador, y en el que el conmutador se configura para arbitrar entre la pluralidad de solicitudes almacenadas en la pluralidad de ubicaciones de almacenamiento, y en el que el conmutador se configura para transmitir en la interconexión una solicitud seleccionada, en el que la solicitud seleccionada es una ganadora del arbitraje; **caracterizado porque:**

- 10 la interconexión incluye uno o más dispositivos de almacenamiento temporizado (20B-20I) acoplados entre el conmutador y cada uno de la pluralidad de agentes que recibe las solicitudes en la interconexión, y en el que una serie de uno o más dispositivos de almacenamiento temporizado se basa en un tiempo de vuelo de la solicitud al agente receptor más alejado del conmutador, y en el que un número igual de dispositivos de almacenamiento temporizado se incluye entre el conmutador y cada uno de la pluralidad de agentes, incluso aunque por lo menos uno de la pluralidad de agentes tenga un tiempo de vuelo más corto del conmutador para las solicitudes.

- 15 2. El sistema según la reivindicación 1 en el que la pluralidad de ubicaciones de almacenamiento comprende una pluralidad de colas, en el que cada una de la pluralidad de colas (30A-30B) se corresponde con un agente respectivo de la pluralidad de agentes y se configura para almacenar las solicitudes transmitidas por el agente respectivo, en el que cada una de la pluralidad de colas comprende por lo menos dos de la pluralidad de ubicaciones de almacenamiento.

- 20 3. El sistema según la reivindicación 1 en el que el conmutador se configura para seleccionar una primera solicitud transmitida por un primer agente de la pluralidad de agentes como la solicitud seleccionada antes de seleccionar una segunda solicitud, en el que la segunda solicitud es transmitida por el primer agente antes de la primera solicitud.

- 25 4. El sistema según la reivindicación 3 en el que cada solicitud tiene una prioridad correspondiente, y en el que el conmutador se configura para seleccionar la primera solicitud antes de seleccionar la segunda solicitud si la primera solicitud tiene una prioridad más alta que la segunda solicitud.

- 30 5. El sistema según la reivindicación 3 en el que el conmutador se configura para seleccionar la primera solicitud antes de seleccionar la segunda solicitud si las solicitudes primera y segunda son reordenables según un conjunto de reglas de ordenamiento, y en el que el conmutador se configura para no seleccionar la primera solicitud por delante de la segunda solicitud si las solicitudes primera y segunda no son reordenables según el conjunto de reglas de ordenamiento incluso si la primera solicitud tiene una prioridad más alta que la segunda solicitud.

- 35 6. El sistema según la reivindicación 5 en el que el primer agente se configura para transmitir una indicación con la primera solicitud indicativa de si la primera solicitud es reordenable o no con la segunda solicitud, y en el que el conmutador se configura para seleccionar la primera solicitud antes de seleccionar la segunda solicitud si la indicación indica que la primera solicitud es reordenable con la segunda solicitud.

- 40 7. El sistema según la reivindicación 1 en el que el conmutador se configura para determinar un agente de destino de la pluralidad de agentes para cada solicitud de la pluralidad de solicitudes, y en el que, si una solicitud de la pluralidad de solicitudes se basa en bloques en el agente de destino de la solicitud, el conmutador se configura para seleccionar otra solicitud a otro agente de destino como la solicitud seleccionada.

- 45 8. El sistema según la reivindicación 7 en el que el conmutador se configura para decodificar una parte de una dirección de cada solicitud de la pluralidad de solicitudes para determinar el agente de destino para la solicitud.

- 50 9. El sistema según la reivindicación 1 en el que un primer agente (12A) de la pluralidad de agentes se acopla al conmutador a través de una primera ruta separada de la interconexión para transmitir solicitudes al conmutador, en el que la primera ruta tiene un primer tiempo de vuelo para las solicitudes inferior al ciclo de reloj y la primera ruta excluye los dispositivos de almacenamiento temporizado, y en el que un segundo agente de la pluralidad de agentes se acopla al conmutador a través de una segunda ruta separada de la interconexión y la primera ruta para transmitir solicitudes

- al conmutador, en el que la segunda ruta tiene un segundo tiempo de vuelo para las solicitudes superior al ciclo de reloj y la segunda ruta incluye por lo menos un dispositivo de almacenamiento temporizado (20A).

- 5        10. El sistema según la reivindicación 1 en el que un primer agente de la pluralidad de agentes se configura para transmitir una pluralidad de solicitudes al conmutador, y en el que el primer agente se acopla para recibir la solicitud seleccionada transmitida por el conmutador de la interconexión, y en el que el primer agente se configura para determinar cuál de la pluralidad de solicitudes transmitidas por el primer agente al conmutador es la solicitud seleccionada en respuesta a la recepción de la solicitud seleccionada en la interconexión.

- 10      11. Un procedimiento que comprende:

- poner en cola (70) las solicitudes de una pluralidad de agentes (12A-12D) en una pluralidad de ubicaciones de almacenamiento (30A, 30B);

- arbitrar (72) entre las solicitudes en la pluralidad de ubicaciones de almacenamiento para seleccionar una solicitud seleccionada de la pluralidad de solicitudes; y

- transmitir (74) la solicitud seleccionada en una interconexión (16), **caracterizado porque** la interconexión

- 15      20. comprende uno o más dispositivos de almacenamiento temporizado (20B-20I) acoplados entre un conmutador (14) y cada uno de la pluralidad de agentes que recibe solicitudes en la interconexión, y **porque** una serie de uno o más dispositivos de almacenamiento temporizado se basa en un tiempo de vuelo de la solicitud a un agente receptor más alejado del conmutador (14), y en el que un número igual de dispositivos de almacenamiento temporizado se incluye entre el conmutador (14) y cada uno de la pluralidad de agentes (12A-12D), incluso aunque por lo menos uno de la pluralidad de agentes (12A-12D) tenga un tiempo de vuelo más corto del conmutador (14) para las solicitudes.

- 25      12. El procedimiento según la reivindicación 11 en el que un primer agente (12A) de la pluralidad de agentes se acopla al conmutador a través de una primera ruta separada de la interconexión para transmitir solicitudes al conmutador, en el que la primera ruta tiene un primer tiempo de vuelo para las solicitudes inferior al ciclo de reloj y la primera ruta excluye los dispositivos de almacenamiento temporizado, y en el que un segundo agente (12B) de la pluralidad de agentes se acopla al conmutador a través de una segunda ruta separada de la interconexión y la primera ruta para transmitir solicitudes al conmutador, en el que la segunda ruta tiene un segundo tiempo de vuelo para las solicitudes superior al ciclo de reloj y la segunda ruta incluye por lo menos un dispositivo de almacenamiento temporizado (20A).

- 30      13. El procedimiento según la reivindicación 11 que comprende adicionalmente:

- un primer agente de la pluralidad de agentes que transmiten una pluralidad de solicitudes al conmutador;

- el primer agente que recibe la solicitud seleccionada transmitida por el conmutador de la interconexión; y

- el primer agente que determina cuál de la pluralidad de solicitudes transmitidas por el primer agente al conmutador es la solicitud seleccionada en respuesta a la recepción de la solicitud seleccionada de la interconexión.

- 35      40. 14. El procedimiento según la reivindicación 11 que comprende adicionalmente:

- el conmutador que selecciona una primera solicitud transmitida por un primer agente de la pluralidad de agentes como la solicitud seleccionada antes de seleccionar una segunda solicitud, en el que la segunda solicitud es transmitida por el primer agente antes de la primera solicitud;

- el primer agente que transmite una indicación con la primera solicitud indicativa de si la primera solicitud es reordenable o no con la segunda solicitud, en el que el conmutador que selecciona la primera solicitud antes de seleccionar la segunda solicitud es sensible a la indicación que indica que la primera solicitud es reordenable con la segunda solicitud.

- 45      50. 15. El procedimiento según la reivindicación 11 que comprende adicionalmente el conmutador que selecciona una primera solicitud transmitida por un primer agente de la pluralidad de agentes como la solicitud seleccionada antes de seleccionar una segunda solicitud, en el que la segunda solicitud es transmitida por el primer agente antes de la primera solicitud, y en el que cada solicitud tiene una prioridad correspondiente, y el conmutador que selecciona la primera solicitud antes de seleccionar

- 55

la segunda solicitud sensible teniendo la primera solicitud una prioridad más alta que la segunda solicitud.

FIG. 1

FIG. 2

FIG. 3

| <b>Tipo de Transacción</b>       | <b>Lectura Coherente</b>              | <b>Escritura Coherente</b>            | <b>No Coherente Remitido</b> | <b>No Coherente Remitido</b> | <b>Finalización No Coherente</b> |

|----------------------------------|---------------------------------------|---------------------------------------|------------------------------|------------------------------|----------------------------------|

| <b>Lectura Coherente</b>         | Sí<br>(si no hay coincidencia de Dir) | Sí<br>(si no hay coincidencia de Dir) | Sí                           | No                           | Sí                               |

| <b>Escritura Coherente</b>       | Sí<br>(si no hay coincidencia de Dir) | Sí<br>(si no hay coincidencia de Dir) | No                           | Sí                           | Sí                               |

| <b>No Coherente Remitido</b>     | Sí                                    | No                                    | a) No<br>b) S/N              | Sí                           | a) S/N<br>b) Sí                  |

| <b>No Coherente No Remitido</b>  | No                                    | No                                    | No                           | S/N                          | S/N                              |

| <b>Finalización No Coherente</b> | Sí                                    | No                                    | a) No<br>b) S/N              | Sí                           | a) S/N                           |

FIG. 4

- a) Leer Solicitud

b) Escribir IO, Escribir Config, Escribir CR

FIG. 5